Skyworth 8M51B Service Manual

SERVICE MANUAL

8M51B CHASSIS

Description:

MODEL.

Engineering Dept:

Artwork By:

Checked By:

Approved By:

Brand Name:

JOB NO.

Date:

Date:

Date:

SERVICE MANUAL 8M51B

2012-5-23

SKYWORTH

SIZE:A5

Design and specifications are subject to change without prior notice.

(Only Referrence)

12

3

4

5

6

789

FREEZE

POWER

MENU

.

MUTE

P.P

S.M

OK

SLEEP

HOME

ZOOM

REC CH.LIST FAV EPG

INDEX

INFO

EXIT

MTSCC

AUDIO

SUBTITLE

SOURCE

0

T.SHIFT

RETURN

CH

VOL

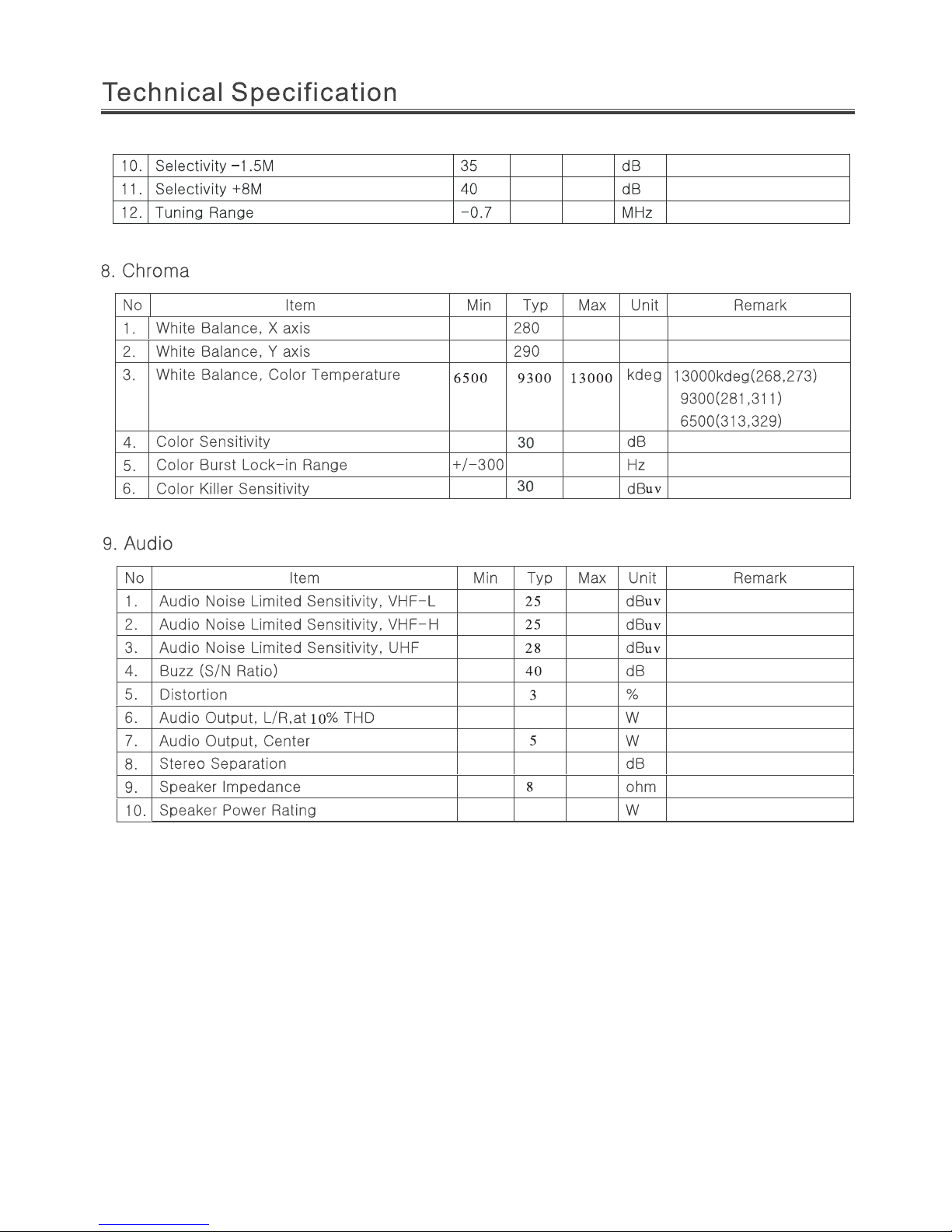

Content--------------------------------------------------------------2

11-17

18

19-20

21-28

29-45

46-49

50-57

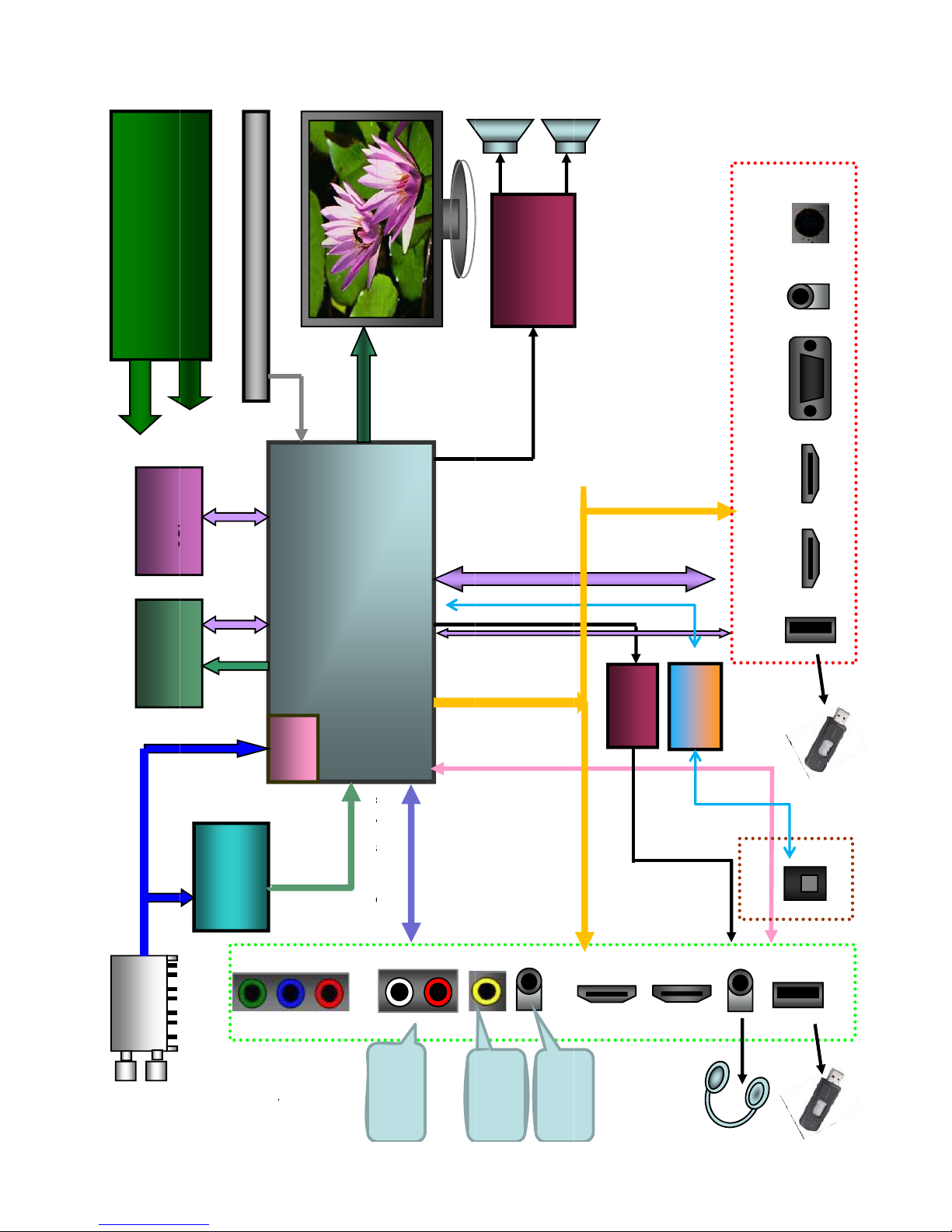

LED 8M51B

TOSHIBA CODE

Component

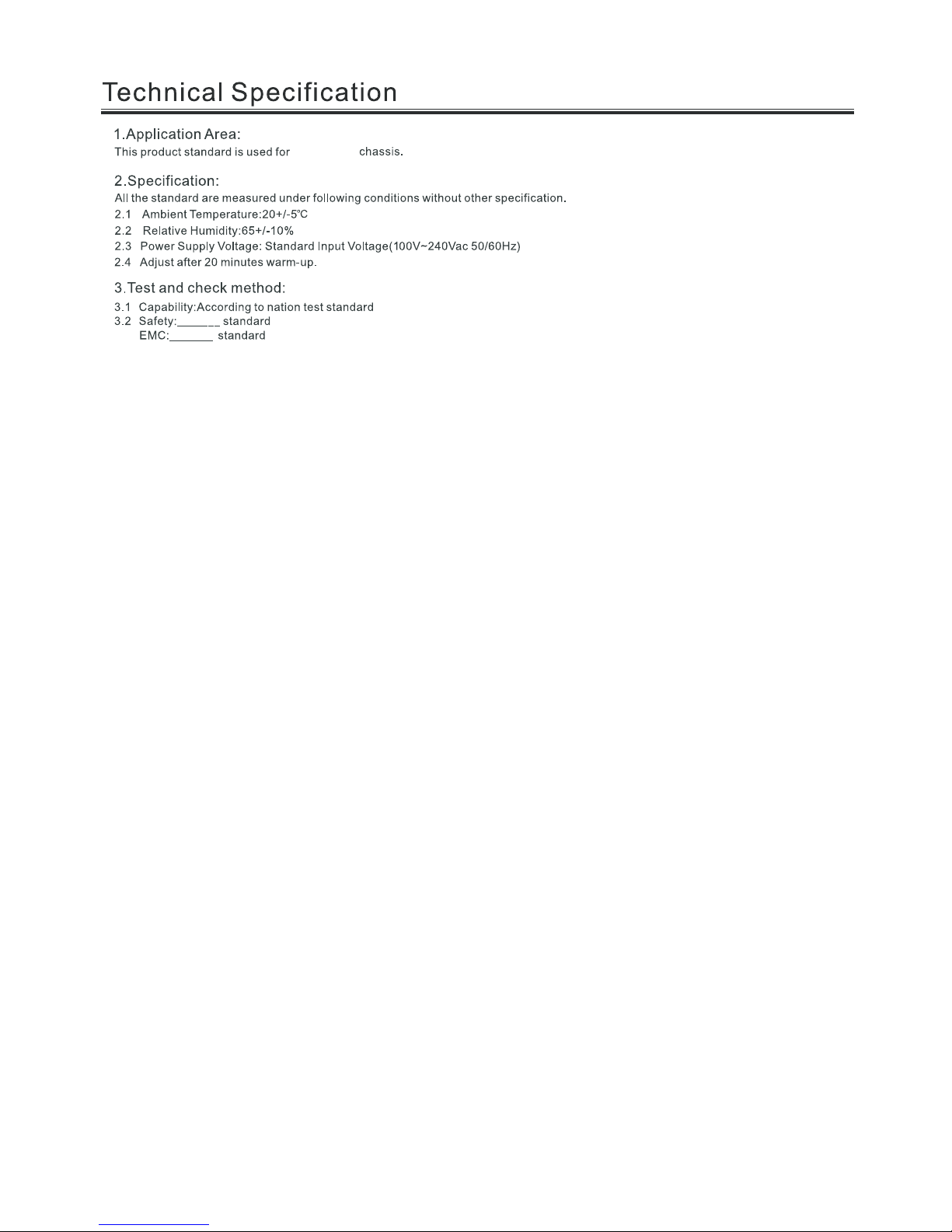

NTSC-M PAL-M PAL-N

VHF LOW 2~B

VHF HIGH C~W+11

VHF W+12~69

55.25MHz ~ 127.25MHz

133.25MHz ~ 311.25MHz

367MHz ~ 801.25MHz

65

120

140

For 32” LED

For 42” LED

For 47” LED

8

8

6

40

40

3

2

1

4.2

50

0.5

80

40

3

12000

(26inches is 8 ohm)

3.3

3.3

DC Voltage, PANEL(12)

12

40

YES

8

6

46

46

NO

NO

Standard

Spanish

Standard

20

4

2

4

0 40 7 0

0 40 7 0

0 40

40 85

-Y 0 5 0

30000

ISDB-T

Analog IF

DDRIII

FLASH

SYSTEM

IF+/-

IF+/-

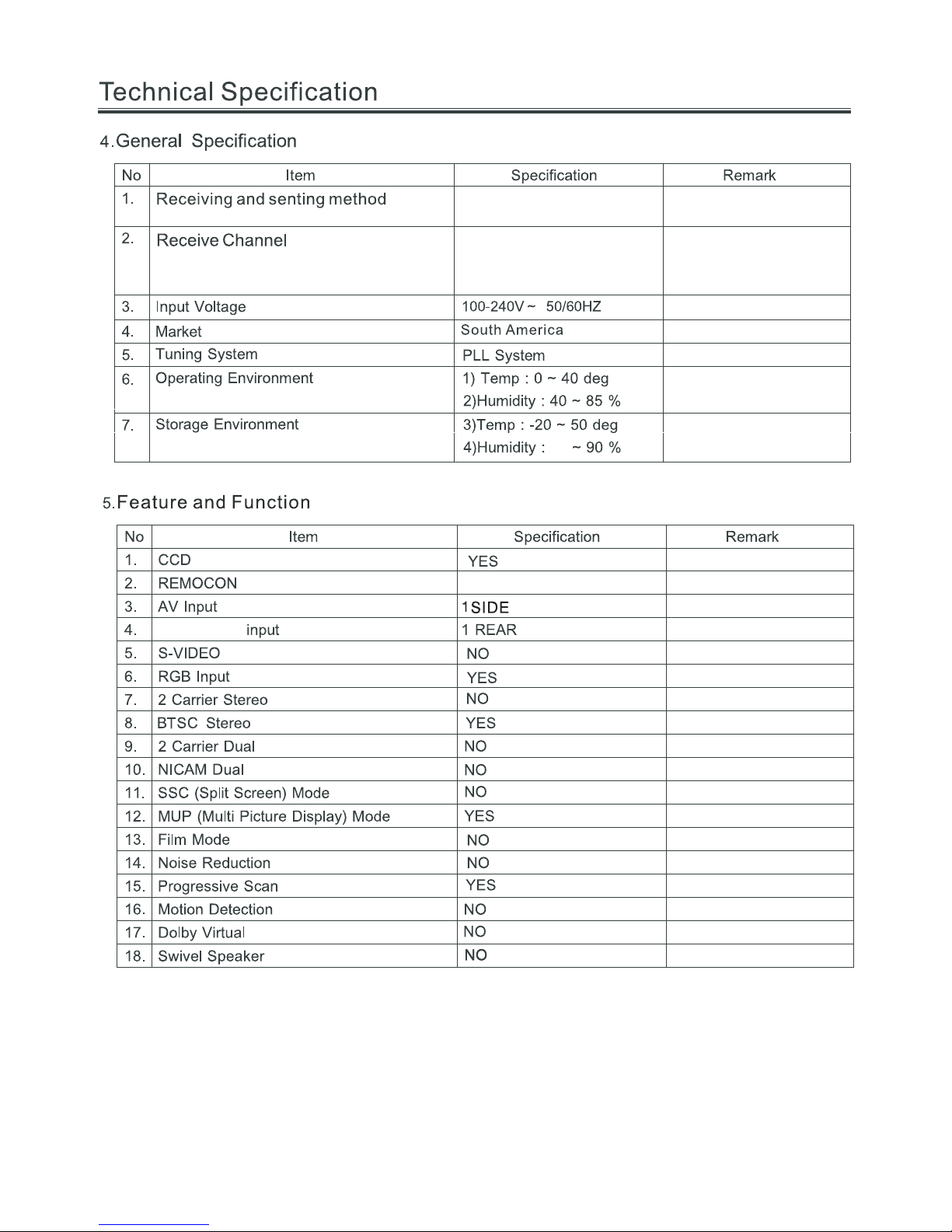

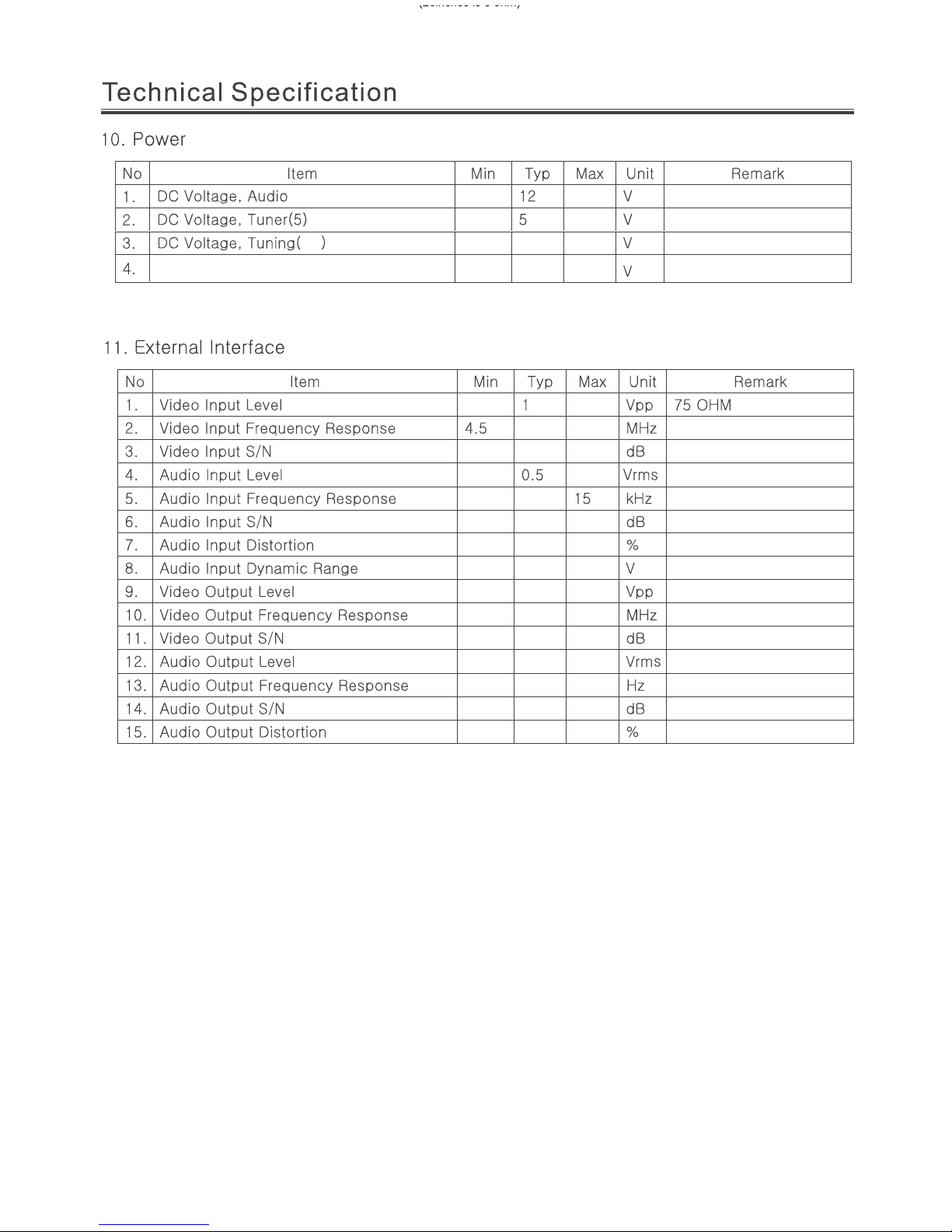

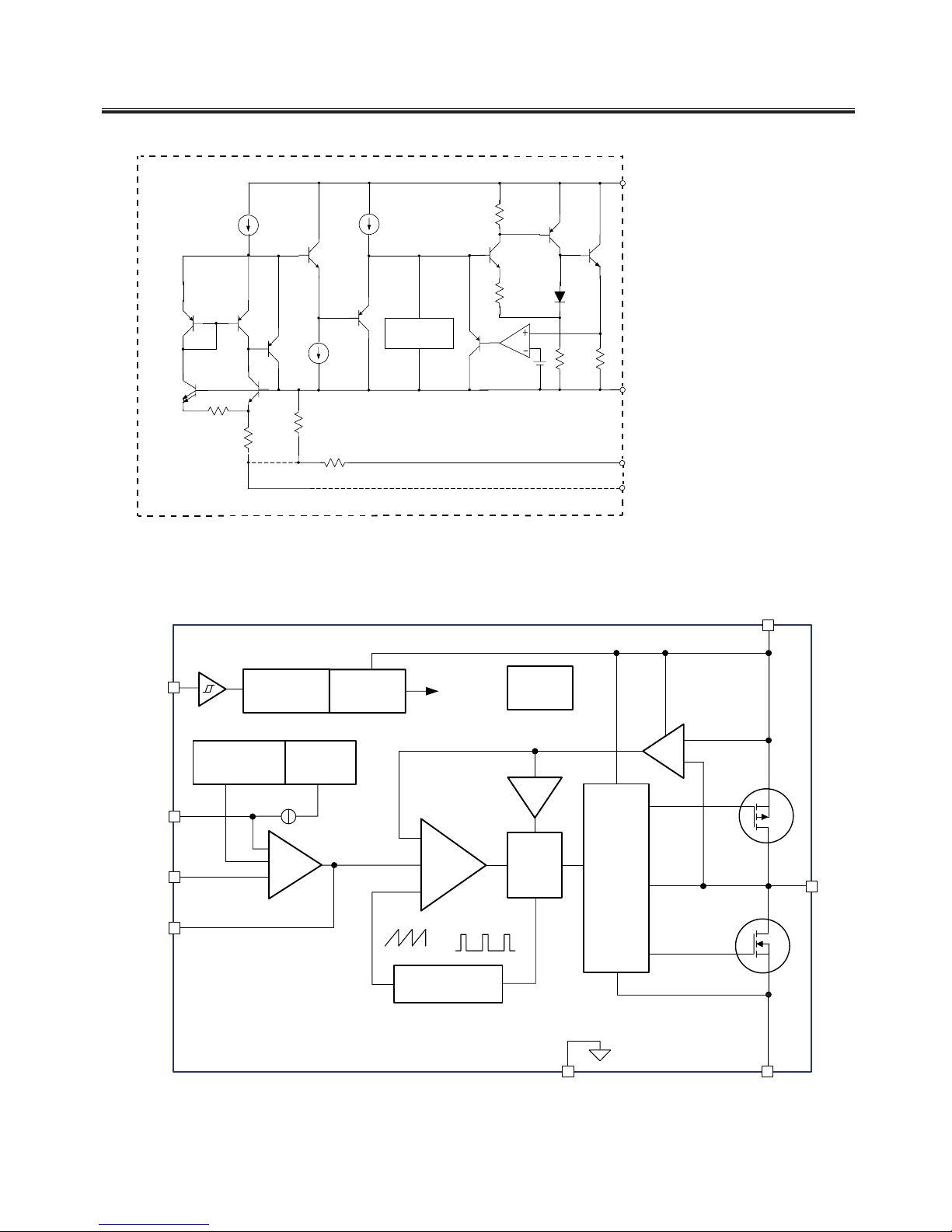

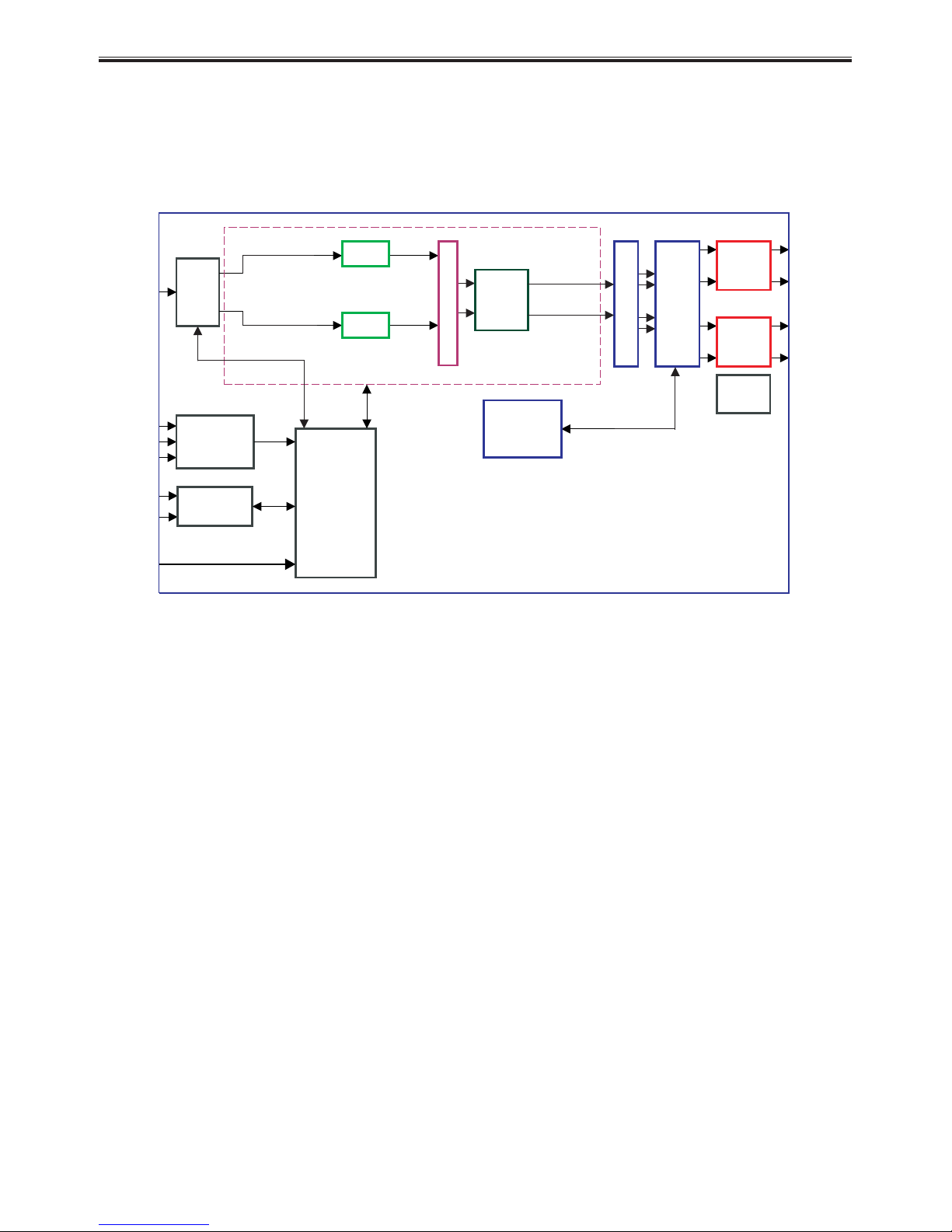

Block Diagram for 8M51B series

2Gbx1+1Gbx1

TC90527

ISDB-T

Demodulator

Side Terminal

KEY PAD, IR Receiver

TUNER

Com

p

onent

MSD6329

Ultra high speed 32-bi RISC CPU

IF Demo. Build in

MPEG1/2/4 /H.264 Decoder

Analog

Demo

Serial TS

CitAdi

LED

PANEL

JPEG MP3 Decoder

C

ompos

it

e +

A

u

di

o

L/R

Audio L/R

AMP5707

8W + 8W

I

2

S

HDMI data

USB2

USB1

Composite

Composite

HP AMP.

BH3544

.

HDMI4

R/L

8M51B

Rear Terminal

HDMI3

-

LAN

VGA-Audio

Transformer

IP101A

HDMI1

USB1

HDMI2

USB2

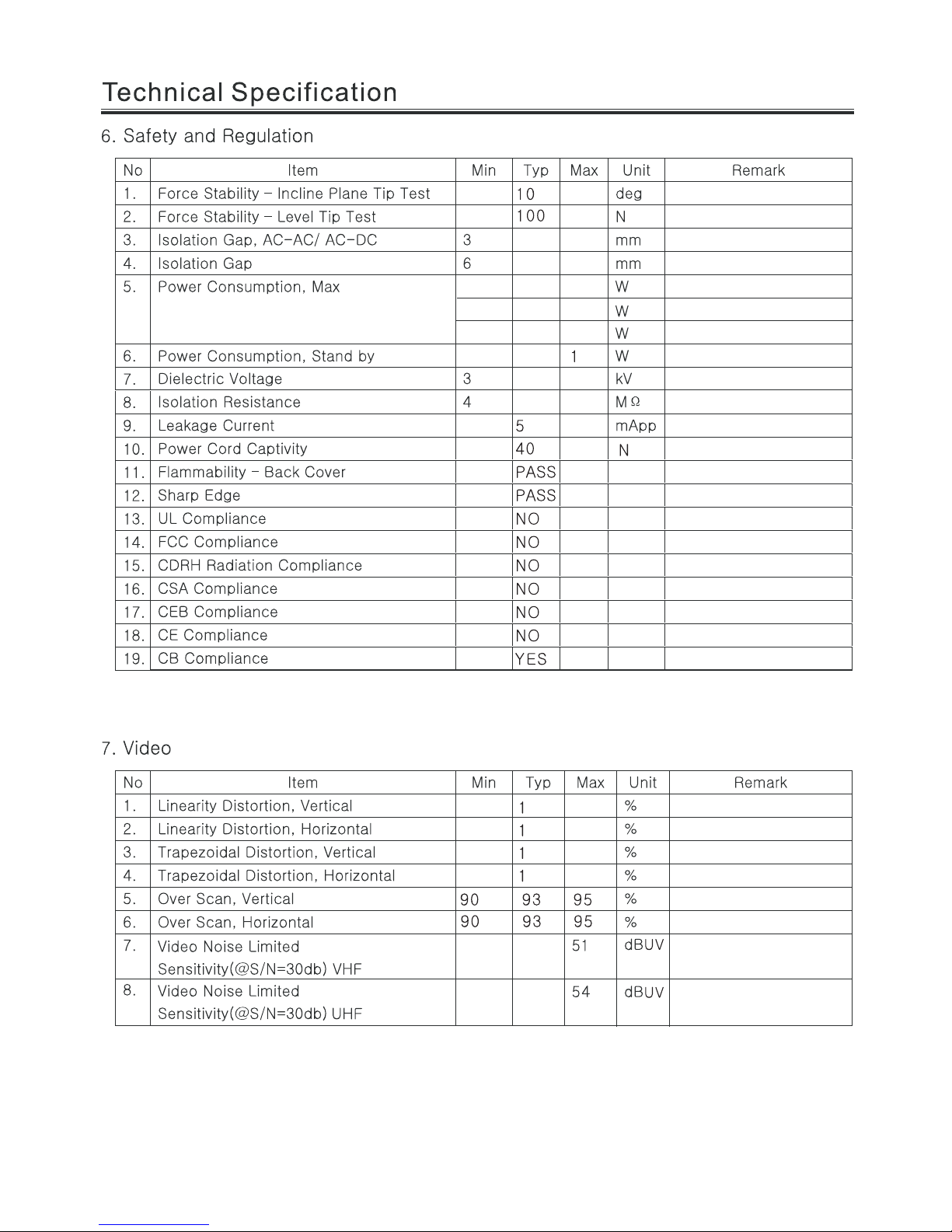

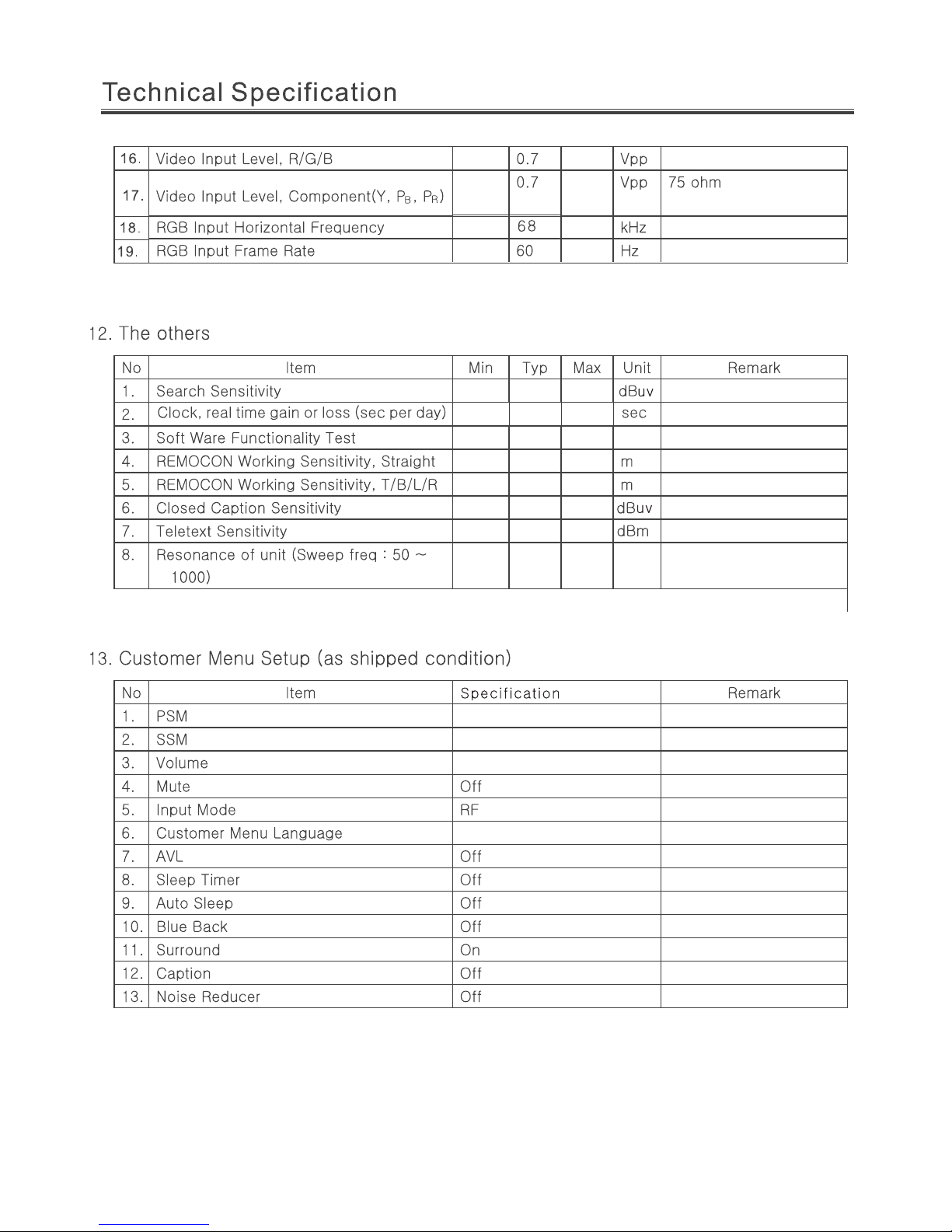

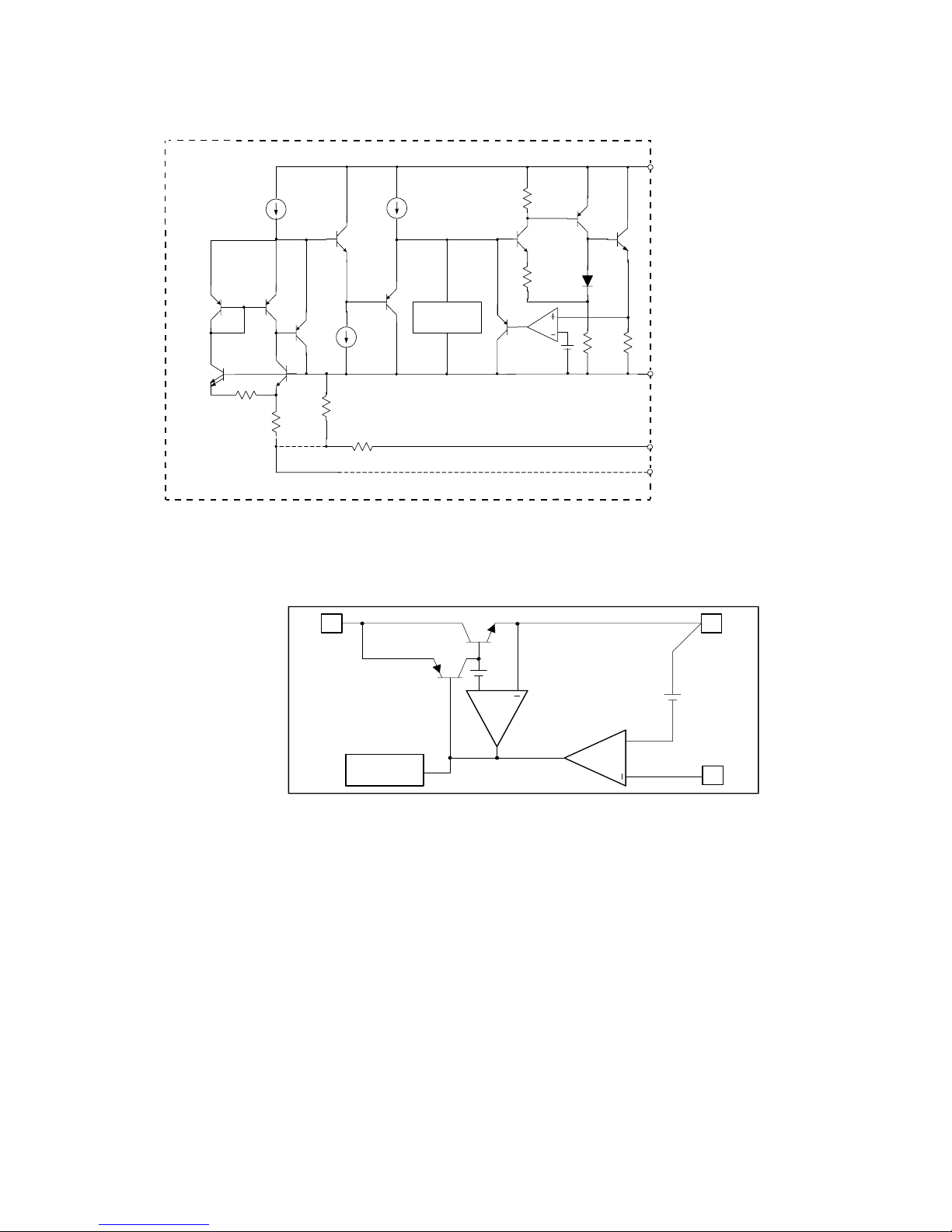

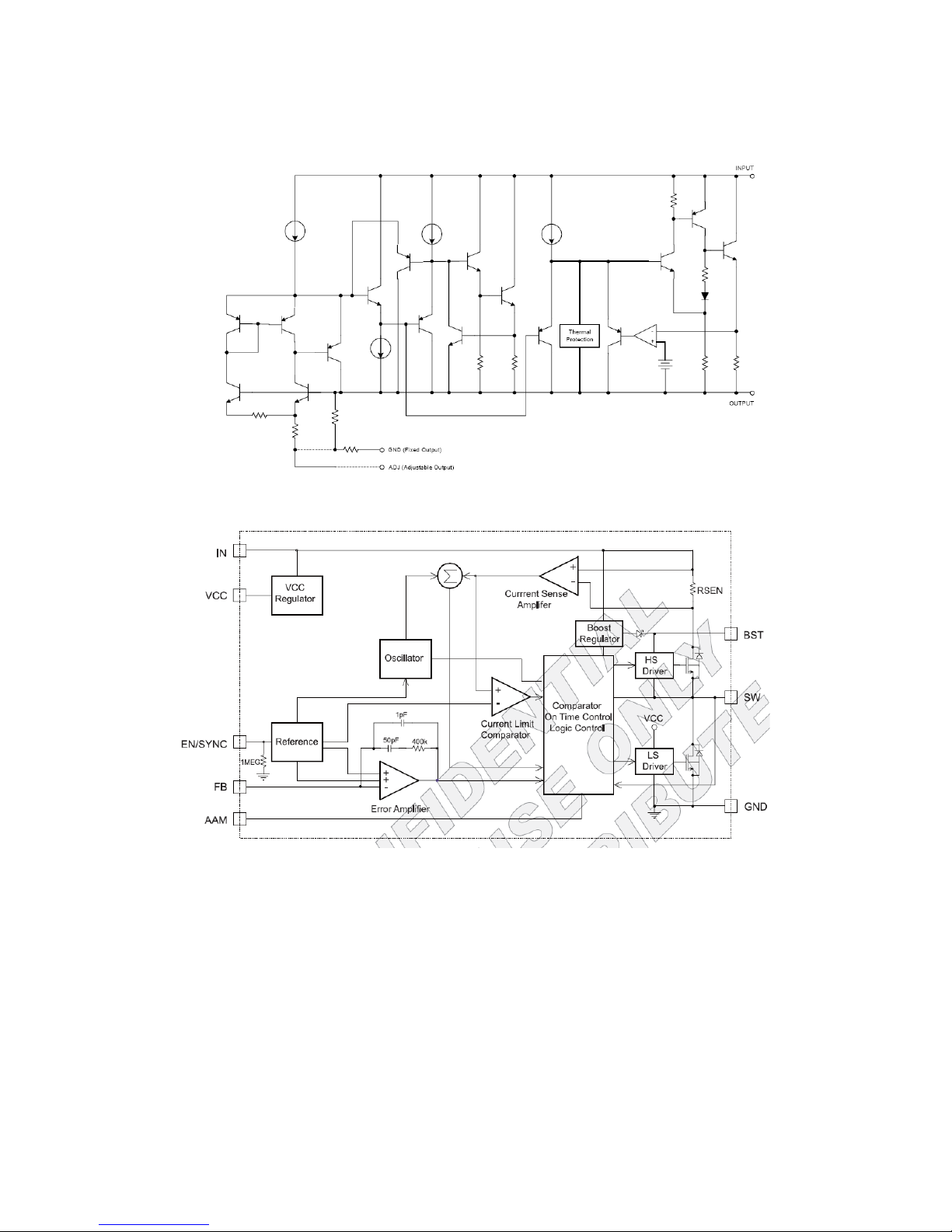

IC Block Diagram

-

U2(3.3V/1A 3-TERMINAL POSITIVE VOL TAGEREGULATOR) LD1117-3.3 SOT-223

GND (Fixed Output)

ADJ (Adjustable Output)

Thermal

Shutdown

Ou t

+

-

INPUT

OUTPUT

U50 (1.1V/3A LOW DROPOUT LINEARAR REGULATOR)AOZ1051PI SO-8

500kHz

Oscillator

AGND

PGND

VIN

EN

FB

SS

COMP

LX

OTP

Internal

+5V

ILimit

PWM

Control

Logic

5V LDO

Regulator

UVLO

& POR

Softstart

Reference

& Bias

0.8V

SS

5μA

Q1

Q2

PWM

Comp

Level

Shifter

+

FET

Driver

ISen

EAmp

+

–

+

–

+

–

+

U3 (2.5V/1A )AS1117L-ADJ A1 SOT-223

U19 (1.2V/1A)AP1122EG-13 SOT223-3L

GND (Fixed Output)

ADJ (Adjustable Output)

Thermal

Shutdown

Out

+

-

INPUT

OUTPUT

3

Thermal

Shutdown

1

2 Vout

GND

1.2V

+

+

CURRENT

LIMIT

Vin

+

+

MSD6329SV

DVB Digita l T e l evision System -on -Chip

Preliminary P inDiagram /De scrip tion an d Me chan ical D im ension s Vers ion 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

PIN DIAGR AM (M SD 632 9SV)

Top V iew

12345678910111213

A NC LVB0N LVB1P LVBCKN LVB3P LVA 0N LVA 1P LVACKN LVA 3P GN D G ND GN D

B USB0_DM N C N C LVB1N LVB2P LVB3N LVB4P LVA 1N LVA2P LVA3N

A_DD R3_

A[1]

A_DD R3_

A[14]

A_M C LKZ

C USB0_DP NC NC LVB0P LVB2N LVBCKP LVB4N LVA 0P LVA2N LVACKP LVA 4P

A_DD R3_

A[12]

A_DD R3_

BA[1]

D NC RTC_XIN

RT C _X OU

T

GPIO 204 GND GPIO 197 GPIO 194 GPIO 190 GPIO 202 GPIO 187 LVA4N

A_DD R3_

A[11]

A_DD R3_

A[6]

E HW RESET

GPIO _PM

[5 ]

GPIO _PM

[8 ]

GPIO 203 GPIO 185 GN D GND GPIO 199 GPIO189 GPIO 186 GPIO 188

A_DD R3_

A[8]

A_DD R3_

A[4]

F SDO

GPIO _PM

[6 ]/S C Z 1

SCZ0 G PIO200 GPIO192 G PIO196 GN D G N D G PIO 191 G PIO 201 GPIO184 GN D GN D

G SD I S C K BIN0P SPD IFO S PD IFI G PIO 198 G PIO 193 GN D GN D G PIO 195 G PIO 183 GN D GN D

H B IN 0M S O G IN0 GIN 0P

GPIO _PM

[1 0 ]

ET_REF_

CLK

ET_TX D [0]ET_TX_E

N

GN D GN D GN D GN D GN D GN D

J GIN 0M R IN0P R IN0M

GPIO _PM

[1 3 ]

ET_TX D [1

]

ET_M D IO

ET_CR S_

DV

GN D GN D GN D GN D GN D GN D

K B IN1 P B IN1M SO G IN1

GPIO _PM

[4 ]

ET_M DC

ET_RX D [0]GPIO _PM

[0 ]

GN D GN D GN D GN D GN D GN D

L GIN 1 P GIN 1M R IN1P

GPIO _PM

[2 ]

ET_RX D [1]GPIO _PM

[1 ]

GPIO _PM

[1 2 ]

GN D GN D GN D GN D GN D GN D

M R IN 1M B IN2 P B IN 2M IRIN A V _LINK

GPIO _PM

[3 ]

DD CA _D A/

UART0_TX

GN D GN D GN D GN D GN D GN D

N SO G IN2 GIN 2P GIN 2M VS Y N C0 H S Y N C0 S A R2

DD CA _ CK/

UART0_RX

GN D GN D GN D GN D GN D GN D

P R IN 2P R IN 2M C V BS5 SA R0 SA R1 V SY N C 1 SA R 3 G N D GN D G N D GN D G N D GN D

R C V B S2 CV BS4 C V B S3 H SY N C1 N C N C PG A_ C OM B YPA SS GN D G N D GN D G N D GN D

T CV BS1 VCO M CVBS0 AUR0 AU L0

AVD D _M

OD33

AVD D _PG

A25

NC

AVD D _AU

33

VD D C GN D GN D GN D

U

CVBSO UT0CVBSO UT

1

AUVRP

AVD D _RE

F25

AVD D _AD

C25

AVD D _AD

C25

NC

AVD D _AL

IV E

AVDD _EA

R33

GN D GN D GN D

V AUVRM AUVAG AUL2

AVD D _DV

I_ U S B

AVD D _DV

I_ U S B

AVD D _DV

I_ U S B

AVD D _MPLLAVD D _D

MP LL

GN D G N D GN D

W AUR2 A U L3 AUR3 G N D GN D G N D N C G N D

Y AUL4 AUR4 AU L1

DDCDC_CKDDCDC_DADD CD A_DAHOTPLUGBTS0DATA

[6 ]

TS1DATA

[1 ]

TS 1V A LID T S1 CLK G P IO 137

PCMA D R[1

2]/CI_A[12

]

AA AUR1 AUO UTL1 AUOUTR1

HOTPLUGCDDCDB_C

K

TS2VALID

TS2DATA

[0 ]

TS0DATA

[4 ]

TS1DATA

[0 ]

TS1DATA

[3 ]

TS1DATA

[5 ]

TS0DATA

[2 ]

TS0DATA

[1 ]

AB AUO UT L0 AU O UTR0

EAR _O UTLDDCDD_CKDDCDB_DADD CD A_C

K

TS2CLK TS2SYNC TS1SYNC

TS1DATA

[2 ]

TS0VA LID TS0CLK

TS0DATA

[0 ]

AC

EAR_O UT

R

XIN XO UT

DDCDD_

DA

IF_AGC A R C 0

TS0DATA

[3 ]

TS0DATA

[5 ]

TS0DATA

[7 ]

TS1DATA

[4 ]

TS1DATA

[6 ]

TS1DATA

[7 ]

TS0SYNC

AD GPIO 180 GPIO 181 GPIO 182

RF_AGC/

TAGC

NC

HOTPLUG

D

RX CC KN RX C 0P RX C 2N RX D C KP RX D 1N RX D 2P RX B 0N

AE G PIO 179 IP VIFM SIFM N C N C

HOTPLUG

A

RX C 0N RX C1P RX D C KN RX D 0P RX D 2N RX B C KP

AF IM VIFP SIFP NC NC CEC RXCCKP RX C1N RXC2P RXD0N RXD1P RXBCKN

12345678910111213

D o c.N o .:20120 10163

IC Block Diagram

U9(LCDTV CONTROLLER WITH VIDEO ECODE)MSD6329SV-Z1-SVN MSTAR

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

14 15 16 1 7 18 19 20 21 22 23 24 25 2 6

GN D G N D GN D G N D GN D GN D GN D GN D GN D GN D GN D GN D G N D A

A_M C LK

A_DD R3_

DQL[5]

A_DD R3_

DQL[1]

A_DD R3_

DQU[2]

A_DD R3_

DQU[6]

A_DD R3_

DQSBU

A_DD R3_

DQSU

A_DD R3_

DQU[1]

A_DD R3_

DQU[7]

A_DD R3_

DQMU

A_DD R3_

DQL[0]

A_DD R3_

DQL[4]

B_M CLKZ B

A_M CLKE

A_DD R3_

DQL[7]

A_DD R3_

DQL[3]

A_DD R3_

DQML

A_DD R3_

DQU[0]

A_DD R3_

DQU[4]

A_DD R3_

DQSBL

A_DD R3_

DQSL

A_DD R3_

DQU[3]

A_DD R3_

DQU[5]

A_DD R3_

DQL[2]

A_DD R3_

DQL[6]

B_M CLK C

A_DD R3_

A[10]

A_RASZ A_CA SZ

A_DD R3_

BA[0]

A_DD R3_

A[5]

A_RESET

A_DD R3_

A[13]

A_DD R3_

A[2]

A_DD R3_

A[0]

A_DD R3_

BA[2]

B_DD R3_

DQL[7]

B_DD R3_

DQL[5]

GND D

A_O DT A_W EZ

A_DD R3_

A[3]

A_DD R3_

A[7]

A_DD R3_

A[9]

B_M C LKE

B_DD R3_

DQL[3]

B_DD R3_

DQL[1]

GND E

GN D G N D GN D G N D GN D GN D GN D GN D

B_DD R3_

DQML

B_DD R3_

DQU[2]

GND F

GN D G N D GN D G N D GN D GN D GN D GN D

B_DD R3_

A[14]

B_DD R3_

A[1]

B_DD R3_

DQU[0]

B_DD R3_

DQU[6]

GND G

GN D G N D GN D G N D GN D GN D GN D GN D

B_DD R3_

A[8]

B_DD R3_

A[11]

B_DD R3_

DQU[4]

B_DD R3_

DQSBU

GND H

GN D G N D GN D G N D GN D GN D GN D GN D

B_DD R3_

A[4]

B_DD R3_

A[6]

B_DD R3_

DQSBL

B_DD R3_

DQSU

GND J

GN D G N D

AVD D _DDR0AVD D _DDR0AVD D _DDR0AVD D _DD

R0

GN D GN D

B_DD R3_

BA[1]

B_DD R3_

A[12]

B_DD R3_

DQSL

B_DD R3_

DQU[1]

GND K

GN D G N D GN D

AVD D _DDR0AVD D _DDR1AVD D _DD

R1

GN D GN D

B_DD R3_

A[10]

B_DD R3_

DQU[3]

B_DD R3_

DQU[7]

GND L

GN D G N D GN D

AVD D _DDR1AVD D _DD

R1

GN D GN D GN D

B_DD R3_

A[3]

B_DD R3_

BA[0]

B_DD R3_

DQU[5]

B_DD R3_

DQMU

GND M

GN D G N D GN D

AVD D _DD

R1

GN D G N D GN D GN D

B_DD R3_

A[7]

B_DD R3_

A[5]

B_DD R3_

DQL[2]

B_DD R3_

DQL[0]

GND N

GN D G N D GN D G N D GN D GN D GN D GN D

B_DD R3_

A[9]

B_RESET

B_DD R3_

DQL[6]

B_DD R3_

DQL[4]

GND P

GN D G N D GN D G N D GN D GN D GN D

BY P ASS_

VCO RE

B_DD R3_

A[2]

B_DD R3_

A[13]

B_ODT B_RASZ GND R

GN D G N D GN D G N D GN D VD D C GN D GN D

B_DD R3_

BA[2]

B_DD R3_

A[0]

B_ W EZ B_ C A SZ GND T

GN D G N D GN D G N D GN D

DVDD_D

DR

GN D GN D GN D GN D N C N C

I2 S _ O U T

_SD

U

VDDC VDDC

DVDD_D

DR

GN D GN D GN D GN D

I2 S _ O U T

_BCK

I2 S _ O U T

_WS

I2 S _ O U T

_M CK

V

GN D G N D GN D G N D GN D VD D C A V D D _11

AVD D _LP

LL

GN D GN D G P IO 102

I2 S _ I N _ SDI2 S _ I N _ B

CK

W

PCMA D R [1

4]/CI_A[14

]

NF_AD[1]/P

CMA D R[1]/

CI_A[1]

NF_AD[0]/P

CMA D R[0]/

CI_A[0]

NF_CEZ NF_CEZ1 GN D VD DC N C VD D P VD D P

I2 S _ I N _ W

S

DDCR_CK DD CR_DA Y

GPIO 138

NF_AD[4]/P

CMA D R[4]/

CI_A[4]

NF_AD[2]/P

CMA D R[2]/

CI_A[2]

NF_AD[3]/P

CMA D R[3]/

CI_A[3]

NF _R EZ GN D VD D C V D D C V D D C V D D C PW M2 PW M4 P W M1 AA

NF _ W PZ G PIO 140

NF_AD[7]/P

CMA D R[7]/

CI_A[7]

NF_AD[6]/P

CMA D R[6]/

CI_A[6]

NF_RBZ NF_ALE GPIO40 NC VDDC VDDC PW M3 PW M0 USB1_DP AB

PCMA D R [1

1]/CI_A[11

]

PCMR EG/

CI_CLK

NF_AD[5]/P

CMA D R[5]/

CI_A[5]

GPIO 139

PCMA D R[1

3]/CI_A[13

]

NF _ C LE NF _W EZ GP IO 39

GPIO 42/U

ART1_TX

GPIO 41/U

ART1_RX

USB1_DM USB2_DP U SB2_DM AC

RX B 1P RX AC KN RX A 0P RX A 2N

PCM IRQ/

CI_INT

PCM IO R/

CI_RD

GPIO 45

PCMA D R [5]

/CI_A[5]

PCMA D R [2]

/CI_A[2]

PCMA D R [3]

/CI_A[3]

PCMA D R [8]

/CI_A[8]

PCMA D R [1

0]/CI_A[10

]

GPIO 38 AD

RX B 1N RX B2P RX A 0N RX A1P

PCM W AIT

/C I_ W A C

K

PCM IO W/

CI_WR

PCM CEN/

CI_CS

PCMA D R [0]

/CI_A[0]

PCMA D R [6]

/CI_A[6]

PCMA D R [4]

/CI_A[4]

PCMA D R [7]

/CI_A[7]

CI_CD

PCMA D R [9]

/CI_A[9]

AE

RX B 0P RX B 2N RX AC KP RX A 1 N RX A 2P PC M W EN PC M O EN

GPIO 44/U

ART2_RX

PCMA D R [1]

/CI_A[1]

CI_RST G PIO 141

GPIO 43/UA

RT2_TX

AF

14 15 16 1 7 18 19 20 21 22 23 24 25 2 6

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

Pin N ame Pin Type Fun ction Pin

G PIO [40:38 ] I/O w / 5V -tolerant GeneralPurpose Input/O utput; 4m A driving strength A B20,A C21,

AD26

G PIO _P M[ 13:12] I/O w / 5V-tolerant GeneralPurpose Input/O utput; 4m A driving strength J4,L7

GPIO_PM[10] I/O w/ 5V-tolerant GeneralPurpose Input/O utput; 4m A driving strength H 4

G PIO _PM[ 8] I/O w / 5V -tolerant G eneralPurpose Input/O utput; 4m A driving strength E3

G PIO _PM[ 6]/

SCZ1

I/O w / 5 V -tol erant G eneralPurpose Input/O utput; 4m A driving strength /

ExternalSPI Flash C hipSelect

F2

G PIO _P M[ 5:0] I/O w / 5V-tolerant G eneralPurpose Input/O utput; 4m A driving strength E2,K4, M 6,L4,

L6, K7

PW M 4 O utput PulseWidth M odulation O utput; 4m A driving streng th

AA25

PW M 3 O utput PulseWidth M odulation O utput; 4m A driving streng th AB 24

PW M 2 O utput PulseWidth M odulation O utput; 4m A driving streng th AA 24

PW M 1 O utput PulseWidth M odulation O utput; 4m A driving streng th AA 26

PW M 0 O utput PulseWidth M odulation O utput; 4m A driving streng th AB 25

SAR3 Analog Input SAR Low Speed AD C Input 3;

G eneralPurpose Input/O utput

P7

SAR2 Analog Input SAR Low Speed AD C Input 2;

G eneralPurpose Input/O utput

N6

SAR1 Analog Input SAR Low Speed AD C Input 1;

G eneralPurpose Input/O utput

P5

SAR0 Analog Input SAR Low Speed AD C Input 0;

G eneralPurpose Input/O utput

P4

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

DR AM Interface

Pin N ame Pin Type Fun ction Pin

A_DD R3_A

[1 4 :0]

O utput D RAM M em ory Address B12,D20,C12,

D 12, D 14,E19,

E12,E18,D 13,

D 18 , E1 3, E17,

D21,B11,D22

A_DD R3_BA

[2 :0]

O utput D R A M M em ory Bank Address D 23 , C 13, D 17

A_M CLKE O utput D R A M M em ory C lock Enable C14

A_O D T I/O Reserved for future O n-D ieTermination E15

A_W EZ O utput W rite Enable; active low E16

A_R ASZ O utput Row Address Strobe; active low D 15

A_CASZ O utput Column A d d ress Strobe; active low D 16

A_M CLK O utput D RAM M em ory Positiv e D iffe re n t i alClock B1 4

A_M CLKZ Output DRAM M em ory Negative D ifferen tialClock B13

A_DD R3_D Q MU O utput D ata M ask forLow Byte;active high B 2 3

A_DD R3_D Q ML O utput Data M ask forLow Byte;active high C 17

A_DD R3_D Q SU I/O D ata Strobe B20

A_DD R3_D Q SL I/O Data Strobe C21

A_DD R3_D Q SBU I/O Data Strobe Inverse B19

A_DD R3_D Q SBL I/O Data Strobe Inverse C 20

A_DD R3_D QU

[7 :0]

I/O DRAM M em ory D ata Bus B22,B18,C23,

C19,C22,B17,

B21, C18

A_DD R3_D QL

[7 :0]

I/O D R A M M e m o ry D a ta B u s C 1 5 , C 2 5 , B 1 5 ,

B25, C16,C 24,

B16, B24

A_R ESET Input D R A M M em ory R eset; active low D 19

B_D DR 3_A

[1 4 :0]

O utput D RA M M em ory Address G 22, R2 3,K23,

H 23, L23, P22,

H22,N22,J23,

N23,J22,M 22,

R22,G 23,T23

B_D DR 3_BA

[2 :0]

O utput D R A M M em ory B ank A ddress T22,K22,M 23

B_M CLKE O utput D R A M M em ory C lock Enable E23

B_O D T I/O Reserved for future O n-D ieTermination R 24

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

Pin N ame Pin Type Fun ction Pin

B_W EZ O utput W rite Enable; active low T 24

B_R ASZ O utput R ow Address Strobe; active low R 25

B_CASZ O utput Column A d d ress Strobe; active low T25

B_M CLK Output D RAM M em ory Positiv e D ifferen tialC lock C 26

B_ M CLK Z O utpu t D R A M M em ory N egative Differen tialClock B26

B_D D R 3_D Q MU O utput D ata M ask for Low B yte;active high M 25

B_DDR3_DQML Output Data Mask forLow Byte;active high F24

B_DDR3_DQSU I/O Data Strobe J25

B_DDR3_DQSL I/O Data Strobe K24

B_DDR3_DQSBU I/O Data Strobe Inverse H 25

B_DDR3_DQSBL I/O Data Strobe Inverse J24

B_D DR 3_DQU

[7 :0]

I/O D R A M M em ory D ata Bus L25, G 2 5, M 24,

H 24 , L24, F25,

K25,G24

B_D DR 3_DQL

[7 :0]

I/O D RA M M em ory D ata B us D 24,P24,D 25,

P25,E24,N 24,

E25,N 25

B_ RE SET In put D R A M M em ory R eset; active low P23

Ethernet RM IIInterface

Pin N ame Pin Type Fun ction Pin

ET_CR S_D V I/O w / 5V-tolerant E th ernet M AC Ca rrier Sense/R eceive D ata Valid J7

ET_TXD [1:0] O utput w / 5V -tolerant Eth ernet M A C Transm itD ata Bus J5, H6

ET_TX_EN O utput w / 5V-toleran t Eth ernet M A C Transm itEnable H7

ET _R EF_C LK Input w / 5V-tolerant EthernetM AC Synchronous C lock R eference for R eceive,

Transm itand ControlIn terface

H5

ET_R XD [1:0] Input w / 5V-tolerant Ethern et M AC Receive Da ta Bus L5 , K6

ET_M D C O utput w / 5V-tolerant Eth ernet M A C M anagem en t Da ta Clock K5

ET_M D IO I/O w / 5V-tolerant EthernetM AC M anagem ent D ata B us J6

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

USB Interface

Pin N ame Pin Type Fun ction Pin

USB0_DP Analog I/O U SB N on Inverting D ata Input/O utput for Port0 C1

USB0_DM Analog I/O U SB In verting Da ta Input/O utput for Port 0 B1

USB1_DP Analog I/O U SB N on Inverting D ata Input/O utput for Port1 A B26

USB1_DM Analog I/O U SB In verting Da ta Input/O utput for Port 1 AC 24

USB2_DP Analog I/O U SB N on Inverting D ata Input/O utput for Port2 A C25

USB2_DM Analog I/O U SB In verting Da ta Input/O utput for Port 2 AC 26

UART Interface

Pin N ame Pin Type Fun ction Pin

GPIO44/

U ART2_RX

I/O w / 5 V -tol erant G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronou s R eceiver 2

AF21

GPIO43/

U ART2_TX

I/O w / 5 V -tol erant G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronou s T ransm itte r 2

AF25

GPIO42/

U ART1_TX

I/O w / 5 V -tol erant

G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchronous Transm itte r 1

AC22

GPIO41/

U ART1_RX

I/O w / 5 V -tol erant

G eneralPurpose Input/O utput; 4m A driving strength /

UniversalAsynchron ous R eceiver 1

AC23

D D CA _DA/

U ART0_TX

I/O w / 5 V -tol erant DDC D ata for A n alog port /

UniversalAsynchronous Transm itte r 0

M7

DDCA_CK/

U ART0_RX

I/O w / 5 V -tol erant DDC C lock for An alog port /

UniversalAsynchron ous R eceiver 0

N7

VIF Interface

Pin N ame Pin Type Fun ction Pin

VIFM Analog Inpu t N egative Video IF Input AE3

VIFP Analog Inpu t P ositive Video IF Input AF3

RF_AGC/

TAGC

Analog O utput R F A G C /

Tun erA utom aticG ainControlO utput

AD4

PGA_CO M Analog Input VIF PG A Negative Source R7

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-C hip

Preliminary PinDiagram /De scription an d Me chanical D im ension s Version 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

Misc. I nterface

Pin N ame Pin Type Fun ction Pin

D D CA _DA/

U ART0_TX

I/O w / 5 V -tol eran t D DC Da ta for A nalog port /

UniversalAsynchronous Transm itte r 0

M7

DDCA_CK/

U ART0_RX

I/O w / 5 V -tol erant D DC Clock for A n alog port /

UniversalAsynchronous R eceiver 0

N7

D D CDA _DA I/O w / 5V -tolerant H DC P SerialBusData /DDC Data ofDVI/HDMIPort A Y6

D D CDA _C K Input w / 5V-tolerant HDC P SerialBu s C lock / D D C C lockofDVI/HDMIPortA AB6

DDCDB_DA I/O w/5V-tolerant H DC P SerialBu s D ata / D D C Da ta ofD V I/H D M I Po rt B AB5

DDCDB_CK Inputw/5V-tolerant H DC P S erialBu s C lock / D D C C lockofDVI/HDMIPortB AA5

D D CDC _DA I/O w / 5V-tolerant HDC P SerialBus D ata / D D C Da ta of D VI/H D M I Port C Y5

D D CDC _CK Input w / 5V-tolerant H DC P SerialBu s C lock / D D C C lockofDVI/HDMIPortC Y4

D D CDD _DA I/O w / 5V -tolerant H DC P SerialBu s D ata / D D C Da ta of D VI/H D M I Port D AC4

D D CDD _CK Input w / 5V -toleran t H DC P SerialBus C lock / D D C C lockofDVI/HDMIPortD AB4

HOTPLUGA I/O w /5V-tolerant H ot-plug controlforDVI/HDM IPortA AE7

H O T P LU GB I/O w / 5V -tolerant H ot-plug controlfor D VI/H D M I Port B Y7

HOTPLUGC I/O w /5V-tolerant H ot-plug controlforDVI/HDM IPortC AA4

HOTPLUGD I/O w /5V-tolerant H ot-plug controlforDVI/HDM IPortD AD6

D D C R _DA I/O w / 5V-tolerant D DC Da ta fo r R O M Y 26

D D C R _CK I/O w / 5V-tolerant DDC Clock for RO M Y25

XIN C rystalO scillator Inpu t CrystalO scillator In put A C2

XO UT C rystalO scillator O utput C rystalO scillator O utput A C3

RTC_XOU T CrystalO scillator O utput R T C 32KH z C rystalO utput D3

RTC_XIN CrystalO scillator Input RT C 32KH z CrystalIn p ut D2

IR IN Input w / 5V-toleran t IR ReceiverInput M4

H W R ESET Schm ittTrigger Inputw /

5V-tolerant

Hardware Reset;active high E1

BYP A SS For ExternalBypass Capacito r R 8

IF_AG C O utput w / 5V -tolerant IF AG C A C5

RF_AGC/

TAGC

O utput w / 5V -tolerant R F A G C /

Tun erA utom aticG ainControlO u tp ut

AD4

CEC I/O Consum erElectronicsControl AF7

AV_LINK

I/O

AV Link

M5

BYP ASS_VCO RE

Output

In ternal VC O R E V olta g e T e st ing Point

R21

Doc.No.:

20120 10163

MSD6329SV

DVB Digita l T e l evision System -on-Chip

Preliminary P inDiagram /De scription an d Me chan ical D im e nsions Vers ion 0.2

1/25/2011

Copyright

2011 M Star Sem icond uct or,Inc. A l lr i gh ts re s e rv e d .

Pow er Pins

Pin N ame Pin Type Fun ction Pin

AVDD _LPLL 3 .3 V P ow er LPLL P ow er W 21

A V DD _D M PLL 3.3V P ow er CrystalPow er V8

A V DD _M PLL 3.3V Pow er M PLL Pow er V7

AVDD _ALIVE 3.3V Pow er Alive D om a inIO Power U8

AV DD _D VI_U SB 3.3V Pow er DV I U SB Pow er V4-V6

AV DD _EAR 33 3.3V Pow er Earphone D rive r Pow er U 9

A V DD _A U 33 3.3 V Pow er Au dio Pow er T9

AV DD _AD C25 2.5V Pow er V ideo AD C Pow er U5, U6

AV DD _REF25 2.5V Pow er D em od AD C Pow er U 4

AV DD _M O D 33 3.3V Pow er M O D 3.3V Pow er T6

AV DD _PG A25 2.5V Pow er Dem od PG A Pow er T7

AVDD _11 1.1V Pow er Analog 1.1V Pow er W 20

AVDD _DD R0 1.5V Pow er D D R3 Pow er K1 6-K 19, L17

AVDD _DD R1 1.5V Pow er D D R3 Pow er L18, L19, M 17, M 18, N 17

D V DD _DDR 1.1V Pow er D D R 1.1V Pow er U19,V 19

VD DP 3.3V Pow er D igitalInput/O utputPow er Y22,Y 23

VDDC 1.1V Pow er D igitalCore Pow er T 10,T19,V14, V16, W 19,Y20,

AA20-AA23,AB22,AB23

G ND G round G round A 11-A26,D 5,D 26,E6,E7,E26,F7,

F8, F12-F21, F26, G 8, G 9, G 12-G 2 1,

G26,H8-H21,H26,J8-J21,J26,

K8-K15,K 20,K21,K26, L8-L16,L20,

L21 , L26, M 8-M 16 , M 19-M 2 1, M 2 6 ,

N 8-N 16,N 18-N 21,N 26,P8-P21, P2

6,

R 9-R 20, R 2 6, T 11 -T18,T 2 0, T 21,

T26,U10,U12-U18,U20-U23,

V 9 -V 1 1 , V 2 0 -V 2 3 , W 9 - W 1 1 ,

W 13-W 18,W 22,W 23,Y19,AA 19

No Connects

Pin N ame Pin Type Fun ction Pin

NC No conn ect A2,B2,B3,C2,C3,D1,R5,R6,T8,

U 7,U24,U 25,W 12,Y21,AB21,

AD5 ,

A E5, A E 6, AF 5, A F6

Doc.No.:

20120 10163

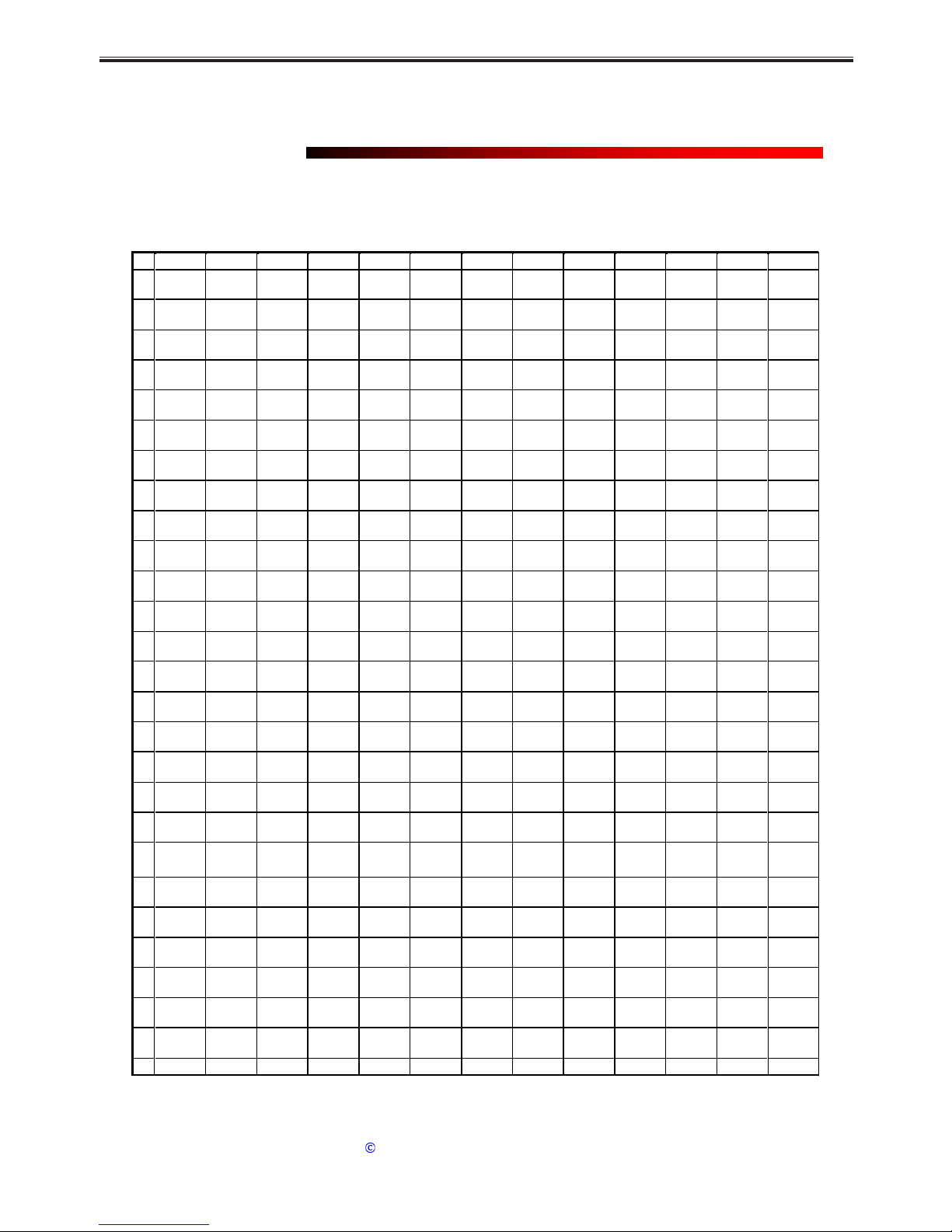

U1(DUAL BTLCLASS D AUDIO AMPLIFIER) TAS5707

IC Block Diagram

SDIN

MCLK

SCLK

LRCLK

Serial

Audio

Port

7BQ

L

R

V

O

L

U

M

E

DRC

Protection

Logic

Click and Pop

Control

7BQ

SDA

SCL

4

Order

th

Noise

Shaper

and

PWM

S

R

C

mDAP

Sample Rate

Autodetect

and PLL

Serial

Control

Microcontroller

Based

System

Control

Terminal Control

OUT_A

OUT_B

2HB´

FET Out

OUT_C

OUT_D

2HB´

FET Out

U4 ˄1.5V/5A˅AS1084R/TRͲLFADJUSTABLETOͲ252

U52 ǃU59˄5V/2A˅MP1494DJͲLFͲZTSOT Ͳ23Ͳ8

U18 ˄3.3V/5A˅AS1084RͲ3.3/TRͲLFTOͲ252

Loading...

Loading...