Page 1

SERVICE MANUAL

8M48A CHASSIS

Design and specifications are subject to change without prior notice.

(Only Referrence)

SIZE:A5

Description:

MODEL.

JOB NO.

Engineering Dept:

Artwork By:

Checked By:

Approved By:

SERVICE MANUAL 8M48A

Brand Name:

SKYWORTH

Date:

Date:

Date:

2012-02-28

Page 2

Content--------------------------------------------------------------2

11-17

18

19-20

21-29

30-47

48-51

52-59

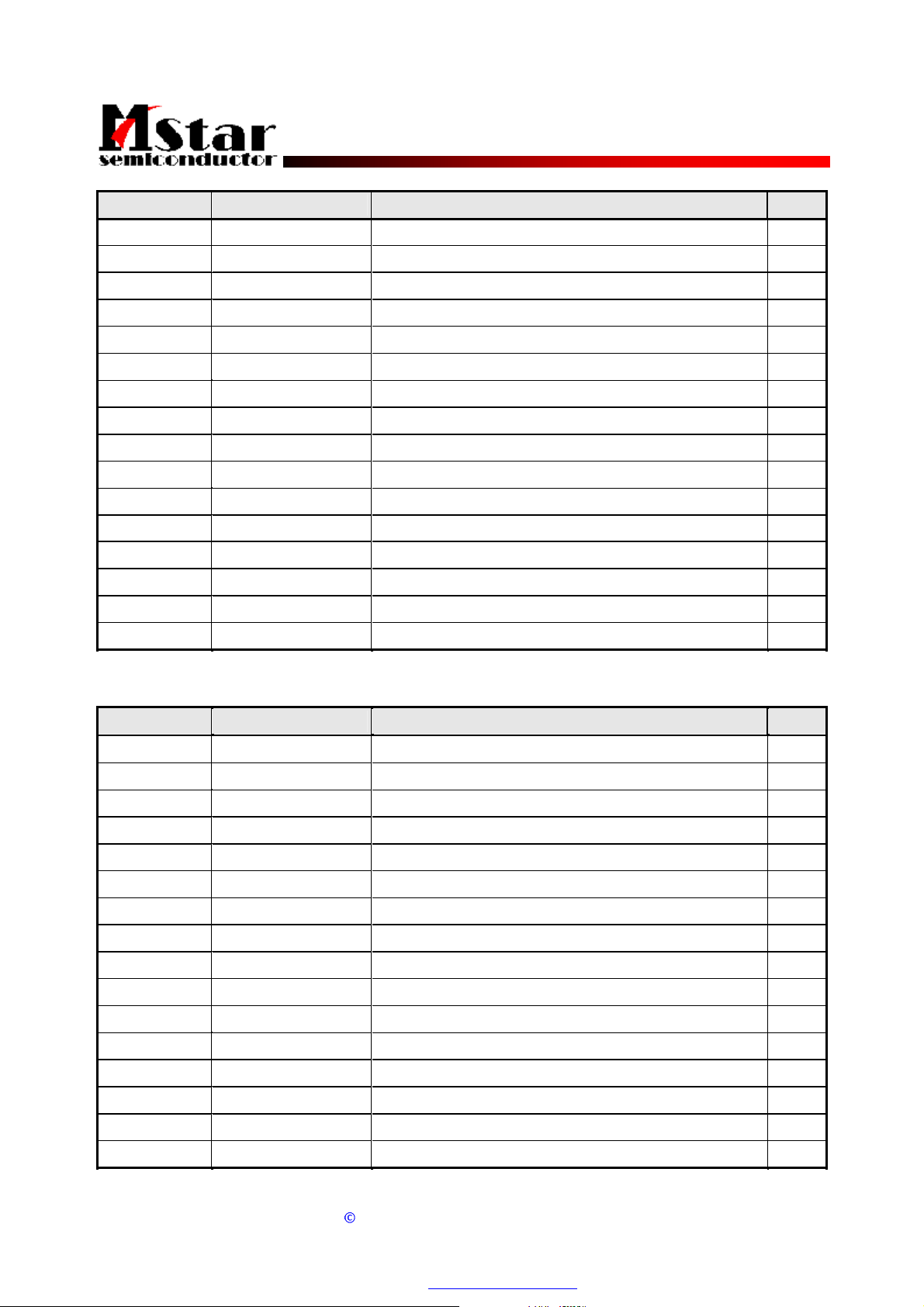

Page 3

LED 8M26A

Page 4

TOSHIBA CODE

Component

PAL SECAM / BG DK PAL / I

NTSC / M

VHF LOW K1~S6

VHF HIGH S7~S36

VHF S37~DS57

44.25MHz ~ 140.25MHz

147.25MHz ~ 423.25MHz

431.25MHz ~ 863.25MHz

Asia\Europe

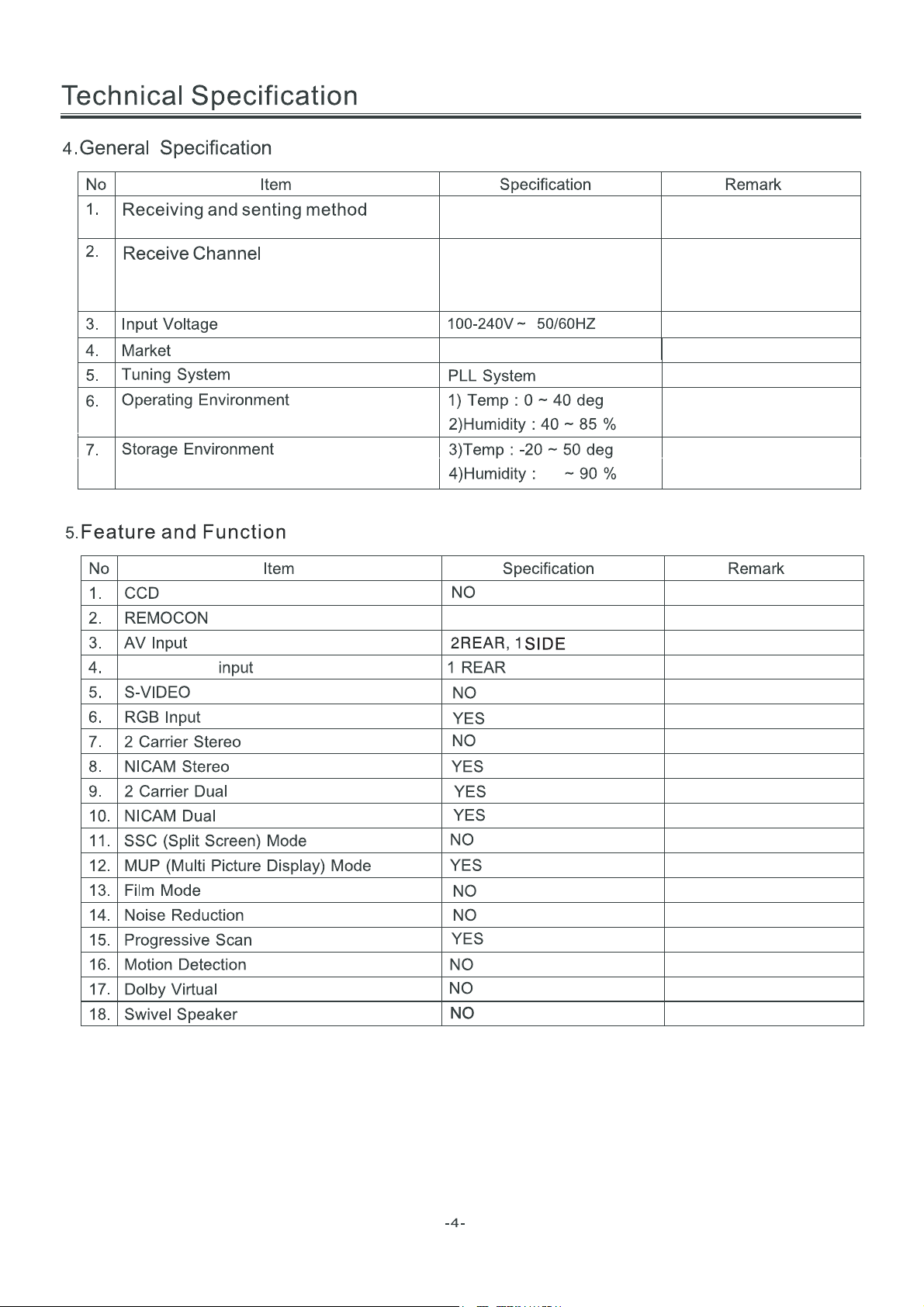

Page 5

40

55

80

For 22” LED

For 24” LED

For 32” LED

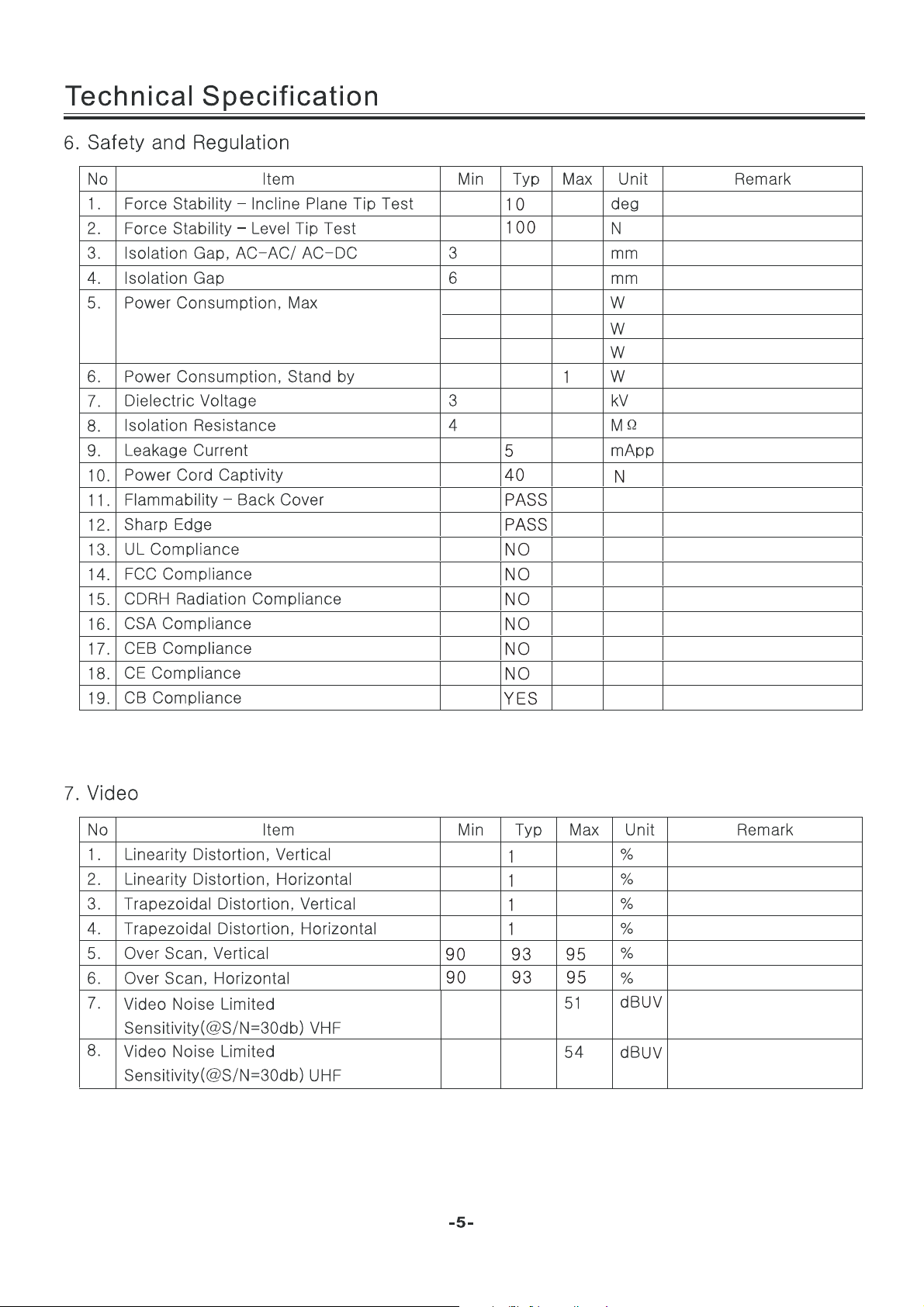

Page 6

(24 inches is 4 ohm)

(24 inches is 3W)

Page 7

80

(26inches is 8 ohm)

40

40

3

2

1

4.2

50

0.5

12000

40

3

Page 8

Standard

Standard

20

40

NO

YES

8

6

46

46

NO

Spanish

Page 9

4

2

4

0 40 7 0

0 40 7 0

0 40

40 85

-Y 0 5 0

30000

Page 10

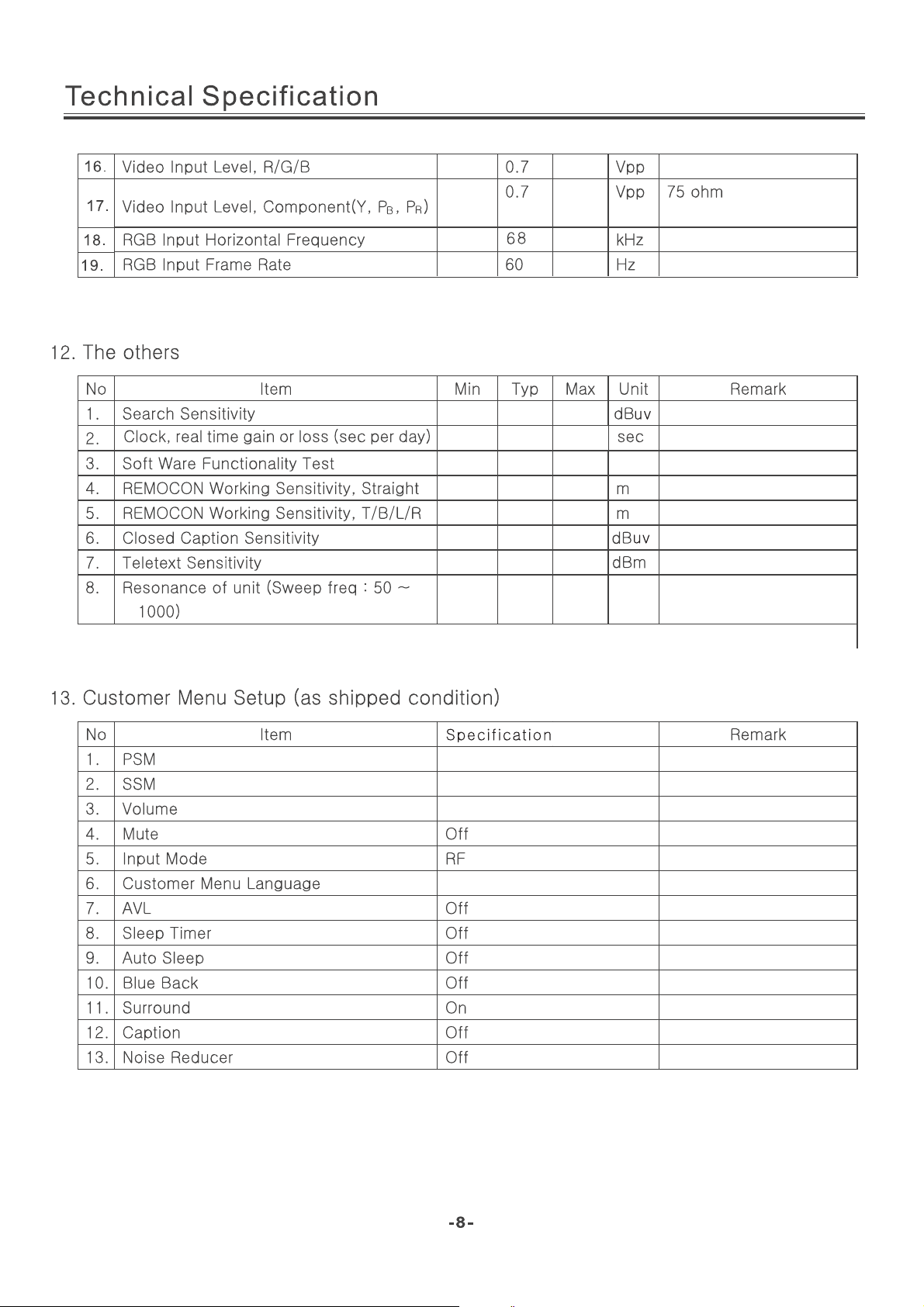

D

C

B

P12

SPEAKER

1

EARPHONE

TU2

TUNER

1

U29

U42

FLASH

2

M13S2561616A-5TG2K ESMT

U7 U1

TPA1517NE

SDA

SCL

P7

S/PDIP

2

3

4

LVDS OUT

U10

MST6E181VS

BH3544F-E2 TPA3113D2/

U19

PS331TQFP64G

P13

2P3P1P

P6

AV OUT

YPbPr AV2 INHDMI 1 VGA

PC

AUDIO

HDMI 2

3

4

MEDIA 2

5

AV1 IN

CON11

C

B

A A

D

CON10

CON6 MEDIA 1

5

Page 11

ʳ

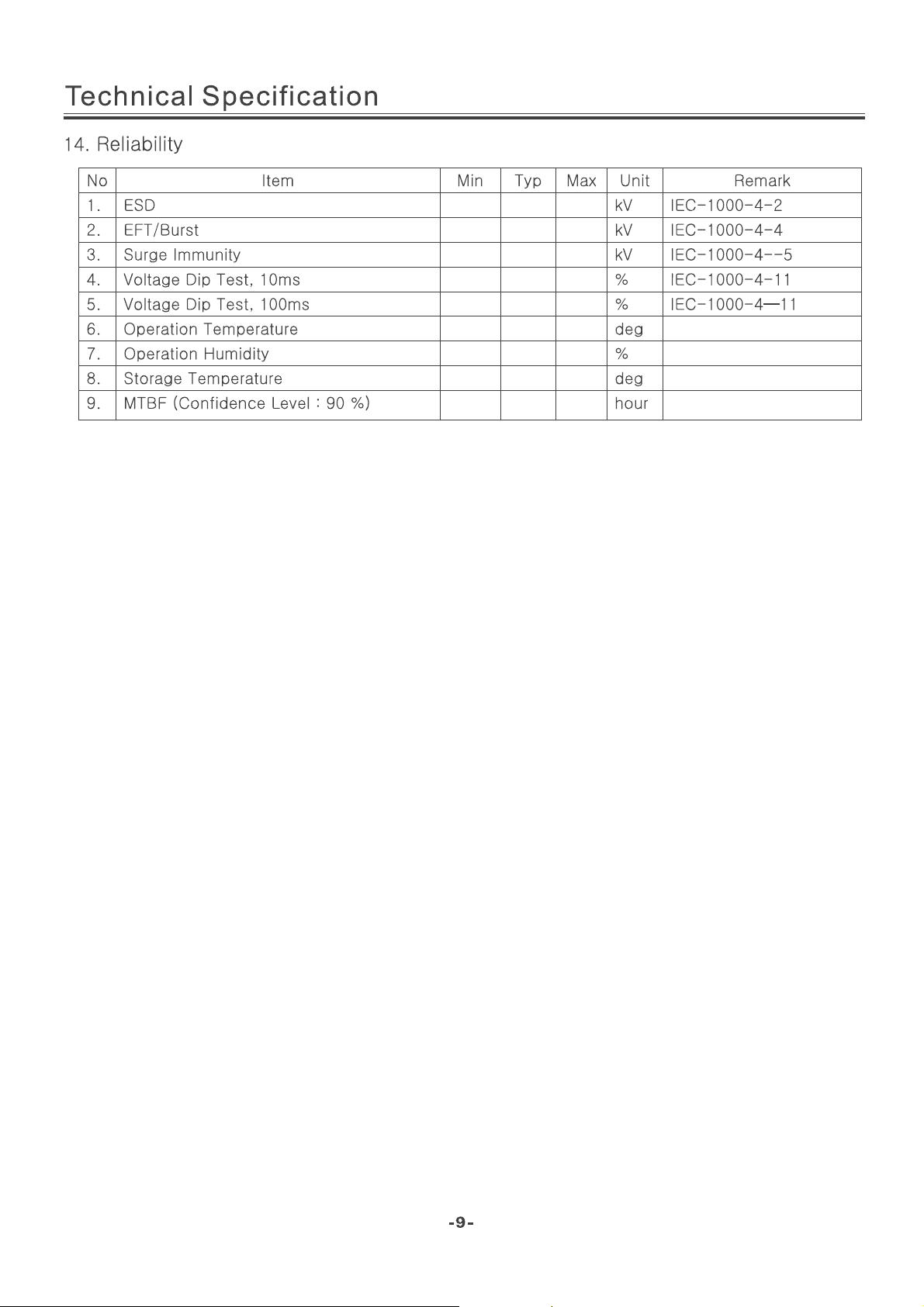

Typical Application Circuit ʳ

AP1117

1A LOW DROPOUT POSITIVE ADJUSTABLE OR

FIXED-MODE REGULATOR

5V

C1

10uF

V

in

V

out

GND

Tab is V

out

( 5V/3.3V fixed output ) ʳ

ʳ

Connection Diagramʳ

ʳ

ʳ

3 PIN SOT223 3 PIN TO252 / TO263

C2

22uF

3.3V/1A

5V

Tab is V

V

out

V

out

Adj

C1

10uF

in

( 5V/2.5V ADJ output ) ʳ

Note:

(1VV

REFo

R1

121

R2

121

R

R

V

o

2.5V/1A

C2

ȍ

22uF

ȍ

2

)

1

(

Top View )

3

2

1

Tab is V

out

3 PIN SOT89

3

2

1

Tab is V

out

V

in

V

out

Adj ( GND)

V

in

V

out

Adj ( GND)

(

Top View )

3

2

1

Tab is V

out

3 PIN TO220

3

2

1

Tab is V

out

V

V

out

Adj ( GND)

in

V

in

V

out

Adj ( GND)

ʳ

ʳ

AP1117 Rev. 3 2 of 11 SEPTEMBER 2006

www.diodes.com © Diodes Incorporated

Page 12

ʳ

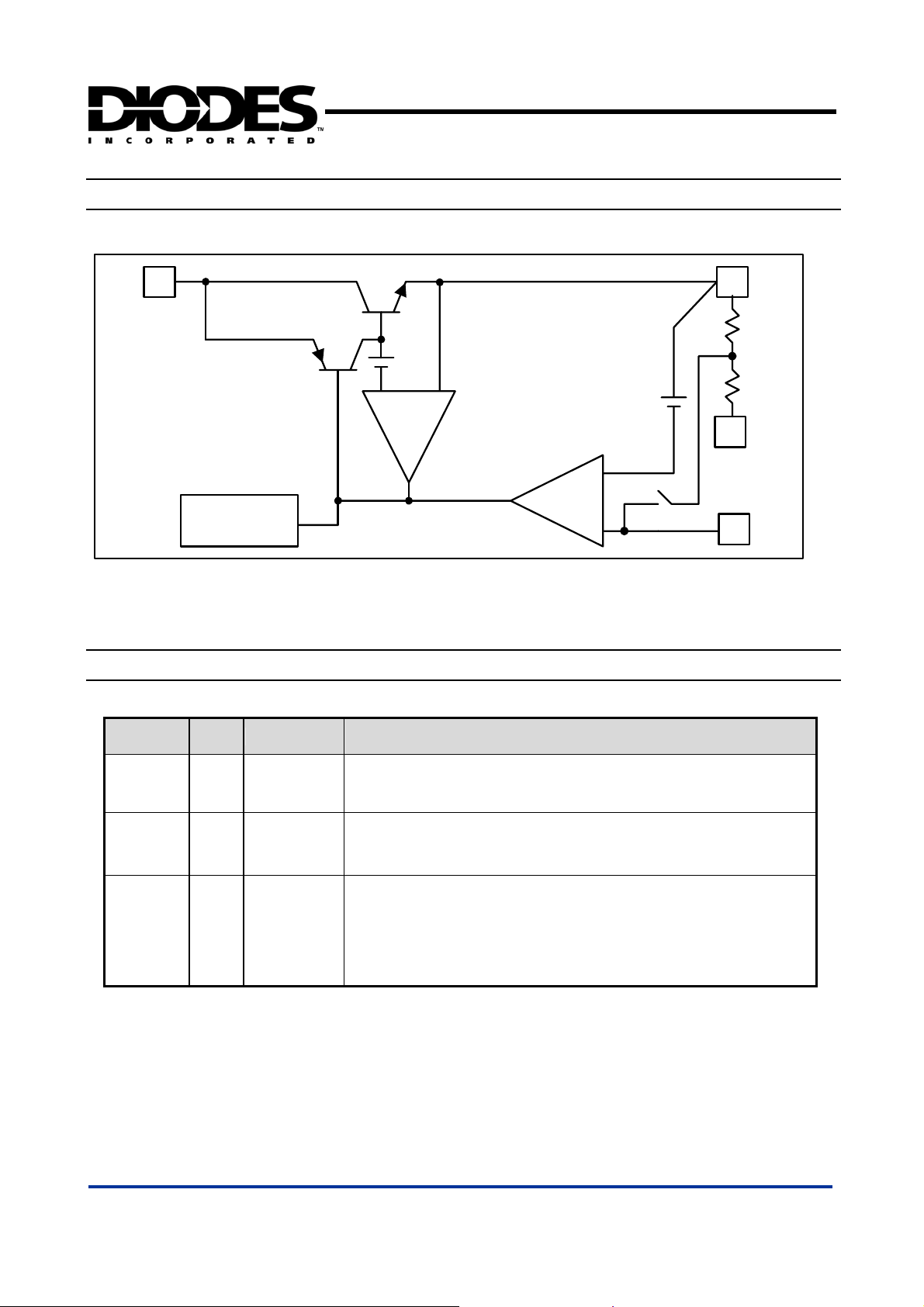

Block Diagramʳ

AP1117

1A LOW DROPOUT POSITIVE ADJUSTABLE OR

FIXED-MODE REGULATOR

3

V

in

Thermal

Shutdown

Pin Descriptionsʳ

2

V

out

+

+

-

1.25V

CURRENT

LIMIT

+

-

+

1

GND

(FIXED)

1

Adj

NAME I/O PIN # FUNCTION

Adj (GND) I 1

V

out

V

in

O 2

I 3

A resistor divider from this pin to the V

(Ground only for Fixed-Mode).

The output of the regulator. A minimum of 10uF capacitor (0.15ȍ ESR 20ȍ)

must be connected from this pin to ground to insure stability.

The input pin of regulator. Typically a large storage capacitor (0.15ȍ ESR 20ȍ)

is connected from this pin to ground to insure that the input voltage does not sag

below the minimum dropout voltage during the load transient response. This pin

must always be 1.3V higher than V

pin and ground sets the output voltage

out

in order for the device to regulate properly.

out

ʳ

AP1117 Rev. 3 3 of 11 SEPTEMBER 2006

www.diodes.com © Diodes Incorporated

Page 13

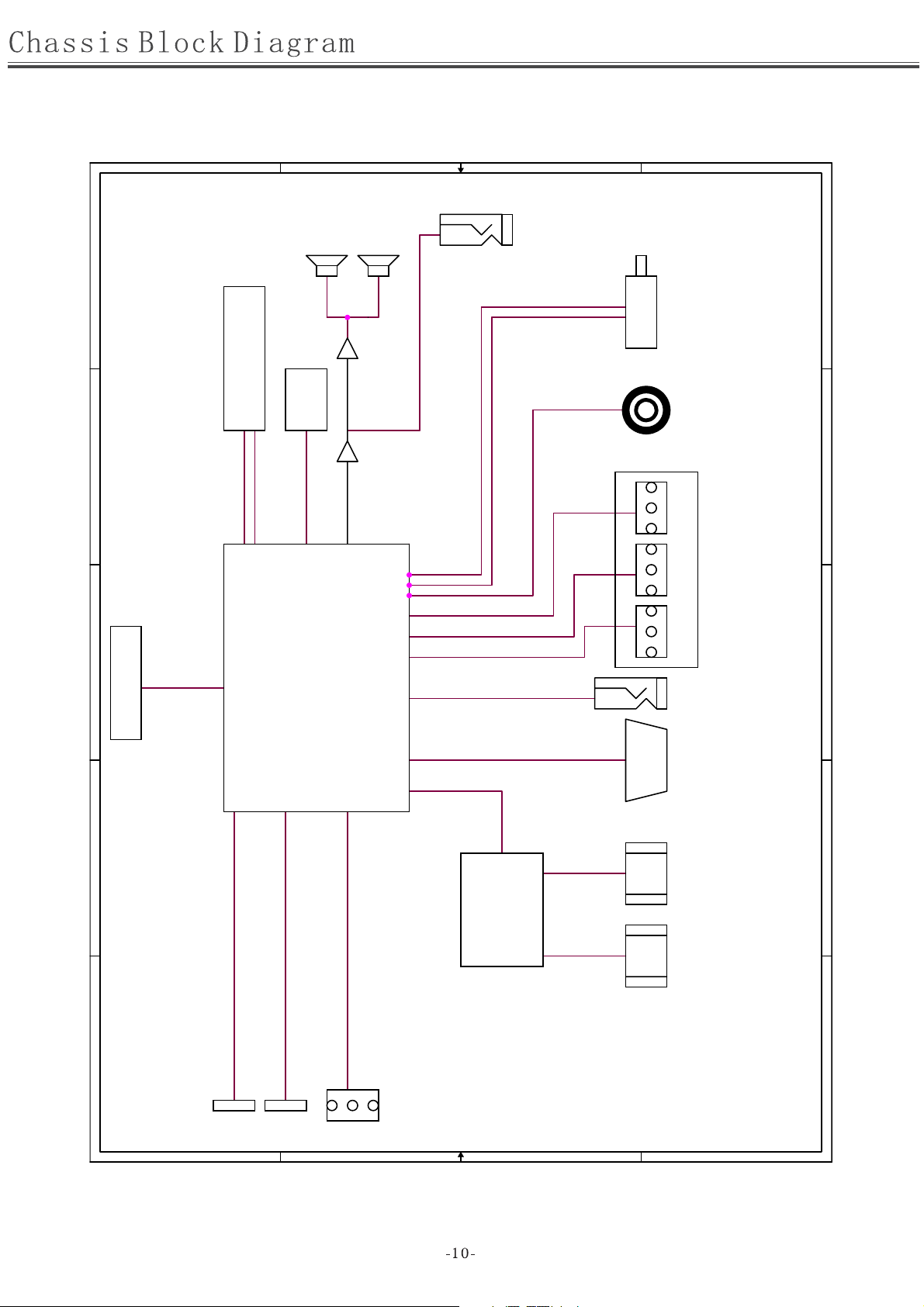

A1semi 1A Fixed and Adjustable Low

A1

A1

A1

Electronics Ltd Dropout Linear Regulator(LDO)

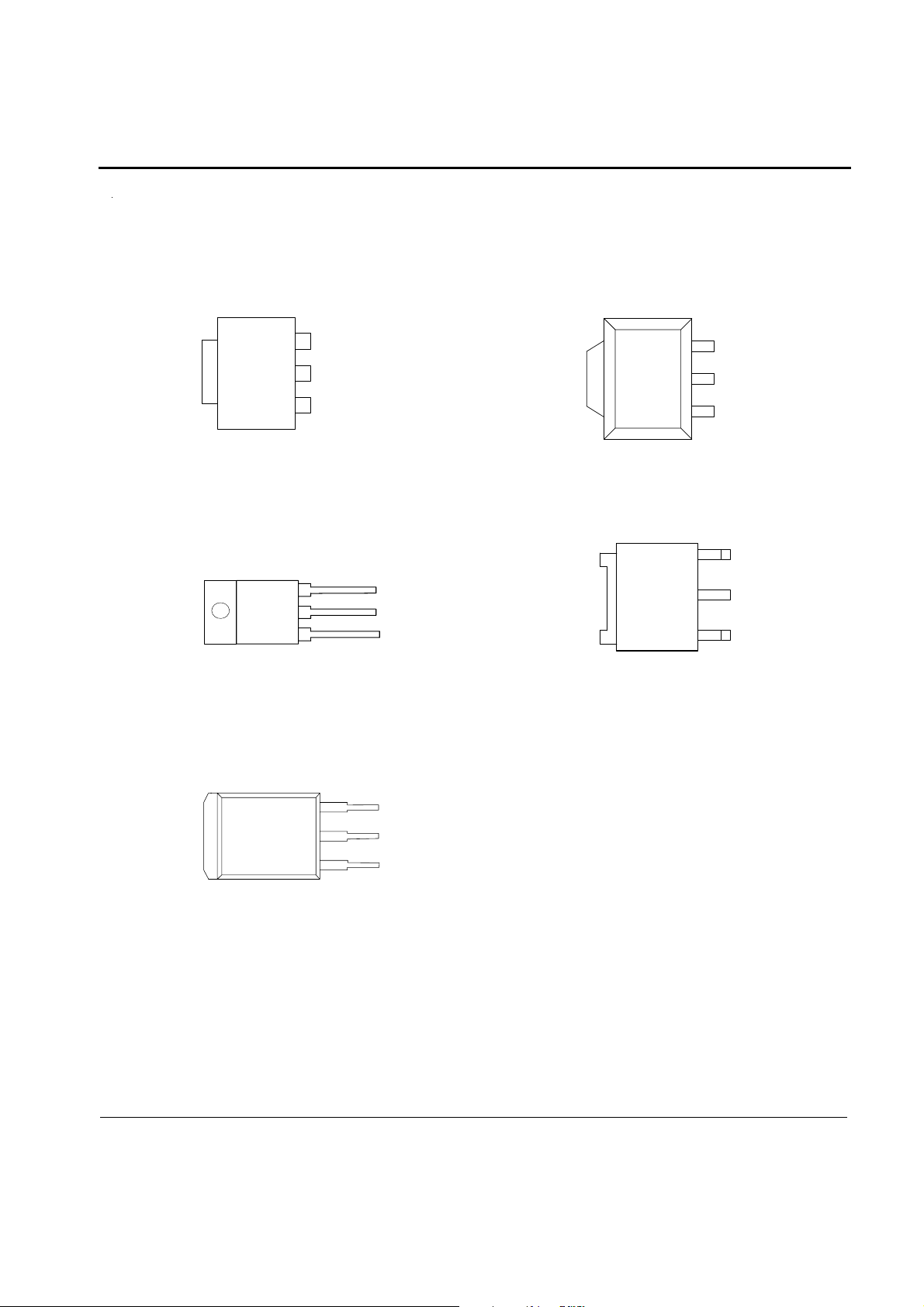

Pin Configurations

L Package

(SOT-223)

V

OUT

T Package

(TO-220) (TO-252)

AS1117

U Package

(SOT-89)

3

INPUT

2

OUTPUT

1

ADJ/GND

V

OUT

3

2

1

R Package

3

INPUT

OUTPUT

ADJ/GND

INPUT

V

OUT

S Package

(TO-263)

V

OUT

3

2

1

3

2

1

INPUT

OUTPUT

ADJ/GND

INPUT

OUTPUT

ADJ/GND

Figure 2. Pin Configurations of AS111 7

V

OUT

2

1

OUTPUT

ADJ/GND

AI SEMI ELECTRONICS LTD. 2

http://www.a1semi.com

Page 14

A1semi 1A Fixed and Adjustable Low

A1

A1

A1

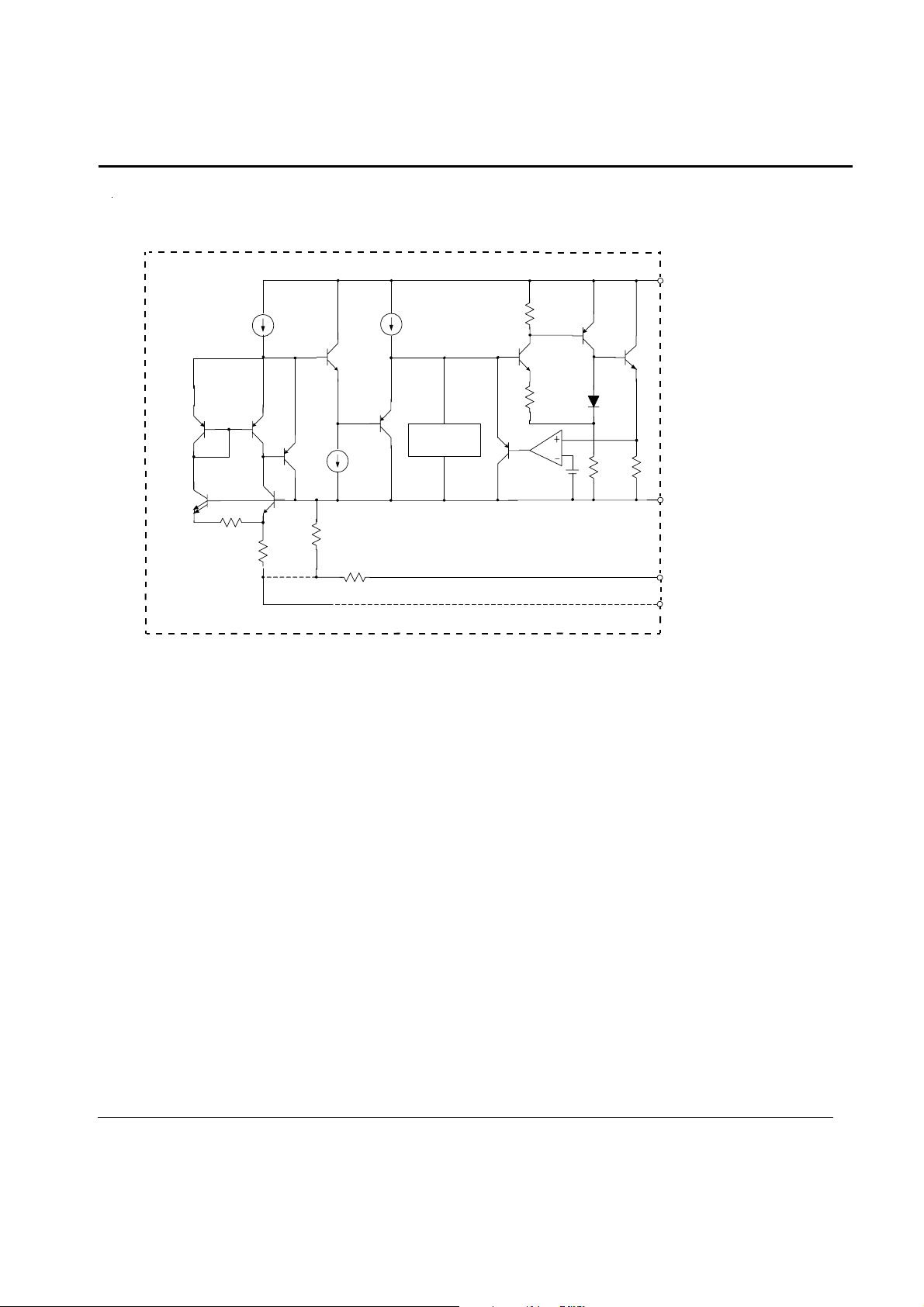

Functional Block Diagram

Electronics Ltd Dropout Linear Regulator(LDO)

Thermal

Shutdown

AS1117

INPUT

Out

+

-

OUTPUT

GND (Fixed Output)

Figure 3. Functional Block Diagram of AS1117

ADJ (Adjustable Output)

A1 SEMI ELECTRONICS LTD. 3

http://www.a1semi.com

Page 15

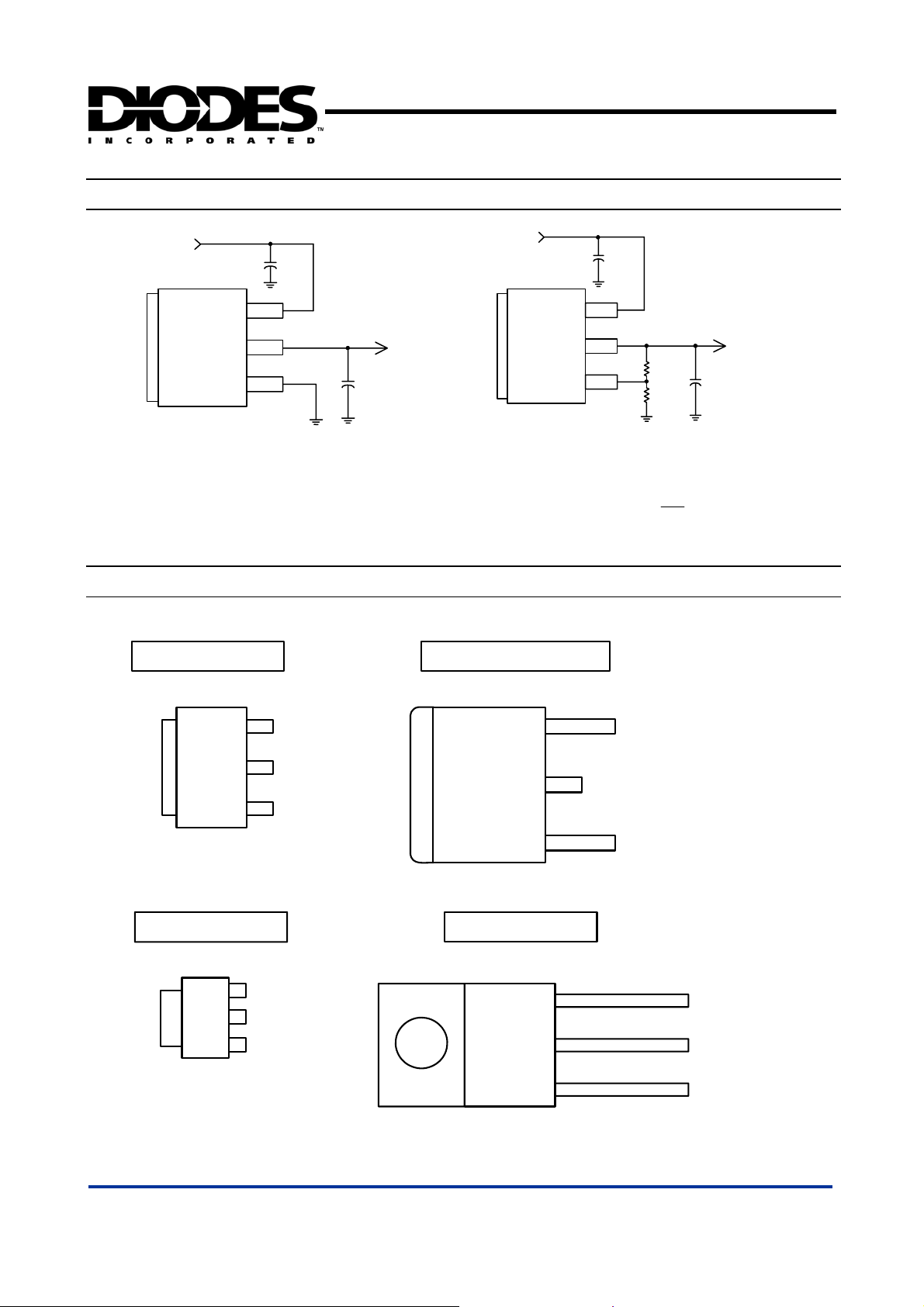

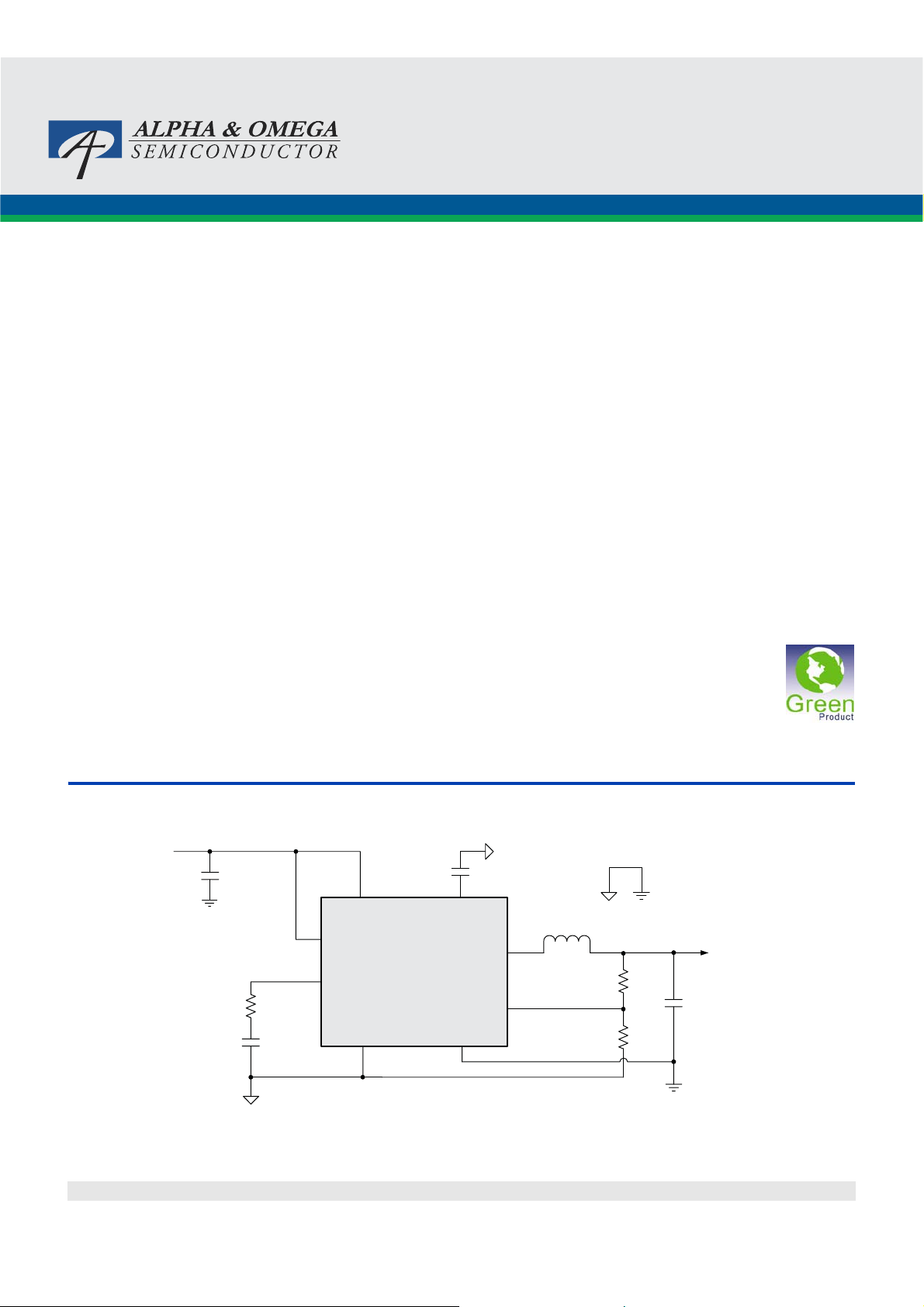

AOZ1051PI

EZBuck™ 3 A Synchronous Buck Regulator

General Description

The AOZ1051PI is a high efficiency, easy to use, 3 A

synchronous buck regulator. The AOZ1051PI works from

4.5 V to 18 V input voltage range, and provides up to 3 A

of continuous output current with an output voltage

adjustable down to 0.8 V.

The AOZ1051PI comes in an exposed pad SO-8

package and is rated over a -40 °C to +85 °C operating

ambient temperature range.

Features

z 4.5 V to 18 V operating input voltage range

z Synchronous Buck: 70 m internal high-side switch

and 40 m internal low-side switch (at 12 V)

z Up to 95 % efficiency

z External soft start

z Output voltage adjustable to 0.8 V

z 3 A continuous output current

z 500 kHz PWM operation

z Cycle-by-cycle current limit

z Pre-bias start-up

z Short-circuit protection

z Thermal shutdown

z Exposed pad SO-8 package

Applications

z Point of load DC/DC converters

z LCD TV

z Set top boxes

z DVD and Blu-ray players/recorders

z Cable modems

Typical Application

VIN

C1

10μF

VIN

EN

AOZ1051PI

COMP

R

C

C

C

Figure 1. 3.3 V 3 A Synchronous Buck Regulator, Fs = 500 kHz

Rev. 1.0 June 2011 www.aosmd.com Page 1 of 14

AGND

SS

PGND

C

SS

L1 4.7μH

LX

R1

FB

R2

VOUT

C2, C3

22μF

Page 16

AOZ1051PI

A

Ordering Information

Part Number Ambient Temperature Range Package Environmental

AOZ1051PI -40 °C to +85 °C EPAD SO-8 Green Product

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant.

Please visit www.aosmd.com/web/quality/rohs_compliant.jsp for additional information.

Pin Configuration

PGND

VIN

GND

FB

1

2

3

4

PAD

(LX)

8

NC

7

SS

6

EN

5

COMP

Exposed Pad SO-8

(Top View)

Pin Description

Pin Number Pin Name Pin Function

1 PGND Power ground. PGND needs to be electrically connected to AGND.

2 VIN Supply voltage input. When VIN rises above the UVLO threshold and EN is logic high,

the device starts up.

3 AGND Analog ground. AGND is the reference point for controller section. AGND needs to be

electrically connected to PGND.

4 FB Feedback input. The FB pin is used to set the output voltage via a resistive voltage divider

between the output and AGND.

5 COMP External loop compensation pin. Connect a RC network between COMP and AGND to

compensate the control loop.

6 EN Enable pin. Pull EN to logic high to enable the device. Pull EN to logic low to disable the

device. If on/off control in not needed, connect EN to VIN and do not leave it open.

7 SS Soft-start pin. 5 μA current charging current.

8 NC No Connect Pin. Pin 8 is not internally connected. Connect this pin externally to LX and

use it for better thermal performance.

Exposed pad LX Switching node. LX is the drain of the internal PFET. LX is used as the thermal pad of the

power stage.

Rev. 1.0 June 2011 www.aosmd.com Page 2 of 14

Page 17

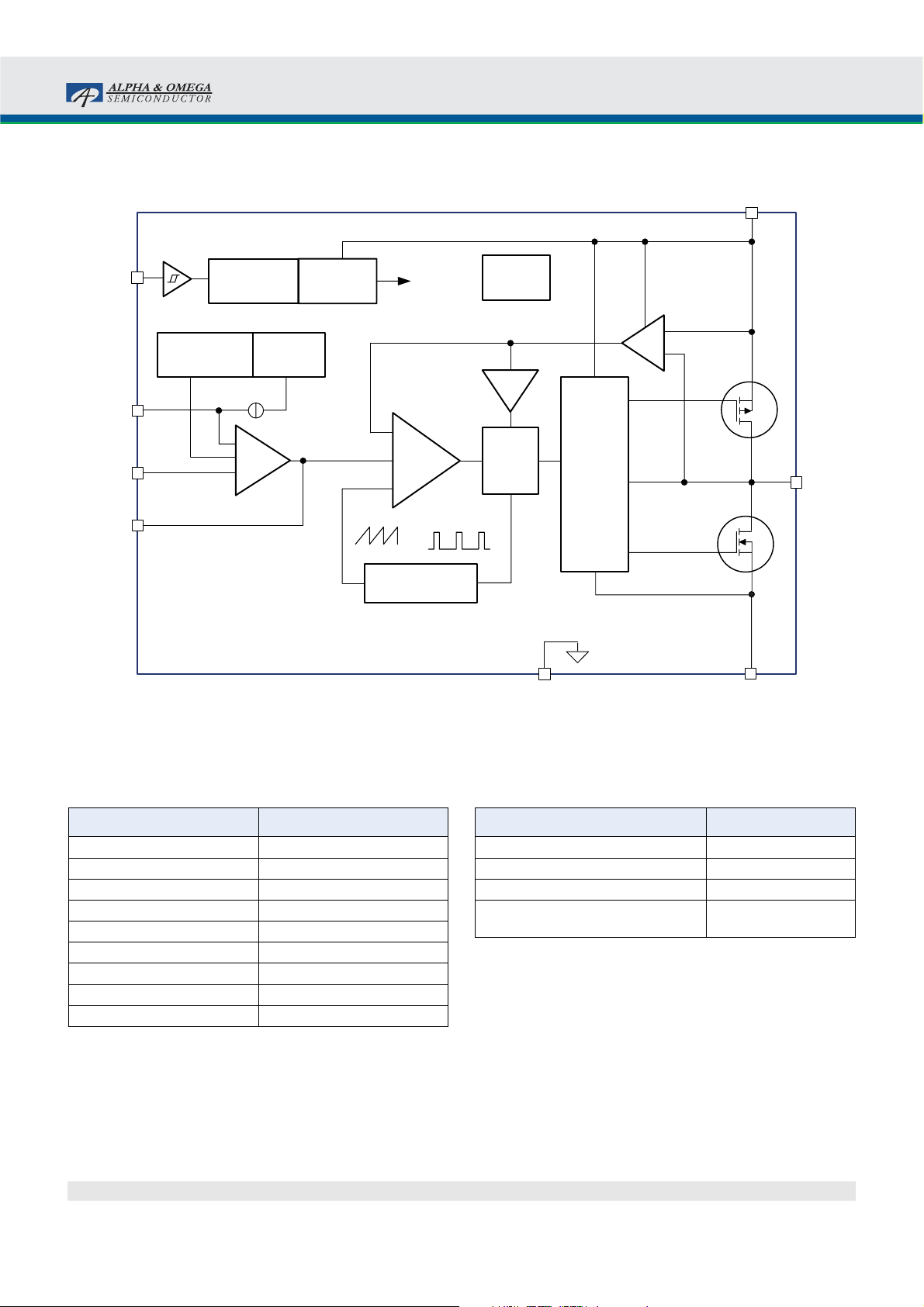

Block Diagram

AOZ1051PI

VIN

EN

SS

FB

COMP

Reference

& Bias

0.8V

UVLO

& POR

+

EAmp

–

Softstart

5μA

SS

5V LDO

Regulator

Internal

+5V

+

PWM

–

Comp

+

500kHz

Oscillator

OTP

ILimit

PWM

Control

Logic

Level

Shifter

FET

Driver

AGND

+

ISen

–

Q1

+

LX

Q2

PGND

Absolute Maximum Ratings

Exceeding the Absolute Maximum Ratings may damage the

device.

Parameter Rating

Supply Voltage (VIN) 20 V

LX to AGND -0.7 V to V

LX to AGND (20 ns) -5 V to 22 V

EN to AGND -0.3 V to V

FB, SS, COMP to AGND -0.3 V to 6.0 V

PGND to AGND -0.3 V to +0.3 V

Junction Temperature (T

Storage Temperature (T

ESD Rating

Note:

1. Devices are inherently ESD sensitive, handling precautions are

required. Human body model rating: 1.5 k

Rev. 1.0 June 2011 www.aosmd.com Page 3 of 14

(1)

) +150 °C

J

) -65 °C to +150 °C

S

in series with 100 pF.

+0.3 V

IN

+0.3 V

IN

2.0 kV

Recommended Operating Conditions

The device is not guaranteed to operate beyond the Maximum

Recommended Operating Conditions.

Parameter Rating

Supply Voltage (VIN) 4.5 V to 18 V

Output Voltage Range 0.8 V to 0.85 • V

Ambient Temperature (TA) -40 °C to +85 °C

Package Thermal Resistance

Exposed Pad SO-8 (4

Note:

2. The value of

FR-4 board with 2 oz. Copper, in a still air environment with

T

= 25 °C. The value in any given application depends on the

A

user’s specific board design.

4

is measured with the device mounted on a 1-in

JA

JA

(2)

)

50 °C/W

IN

2

Page 18

SY8086

Package Code

Package Code

High Efficiency 1.4MHz, 1A

Synchronous Step Down Regulator

Preliminary Specification

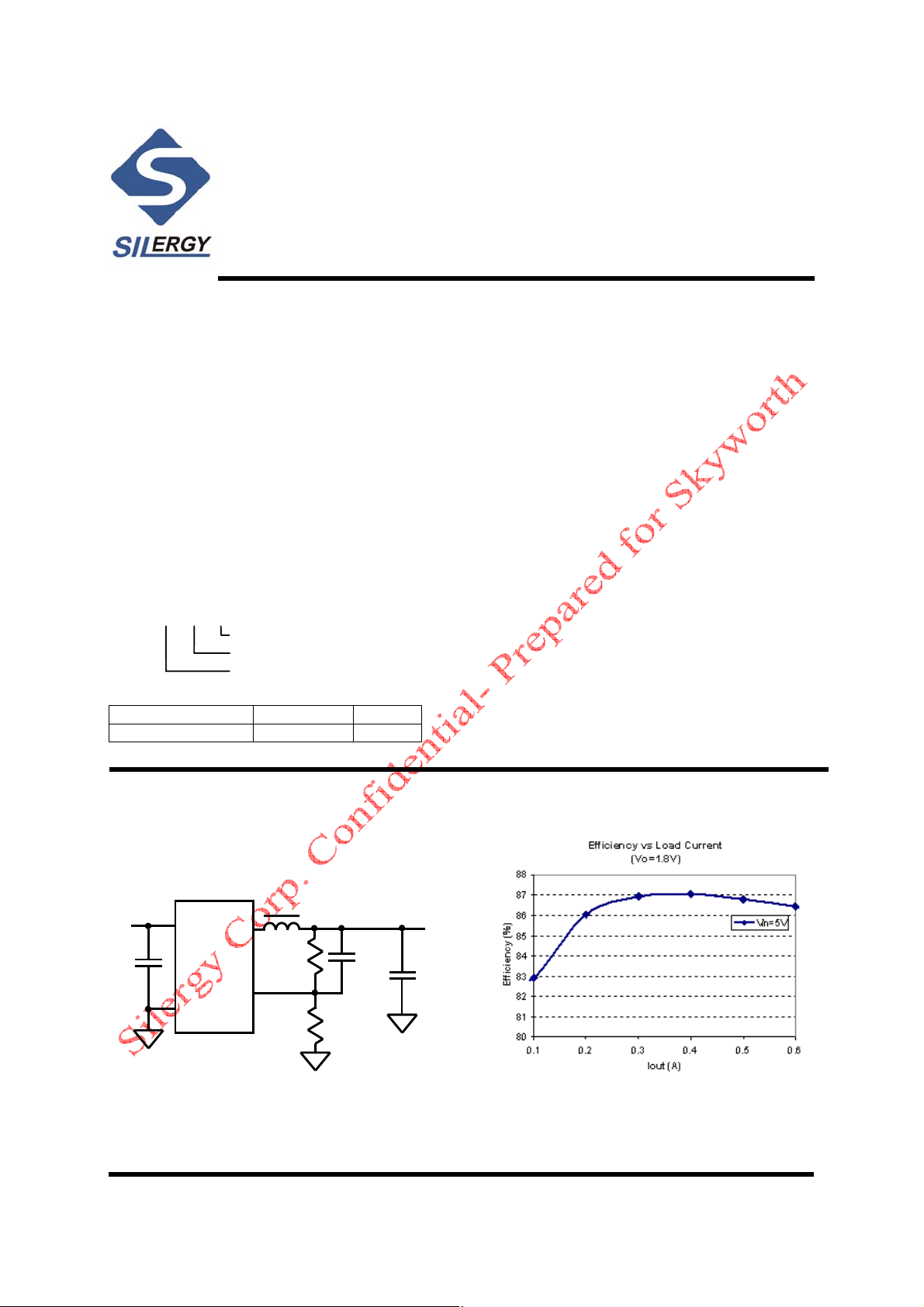

General Description

The SY8086 is a high-efficiency 1.4MHz synchronous

step-down DC-DC regulator ICs capable of delivering

up to 1A output current. The SY8086 operates over a

wide input voltage range from 2.5V to 5.5V and

integrate main switch and synchronous switch with

very low R

Low output voltage ripple and s mall external indu ctor

and capacitor sizes are achieved with 1.4MHz

switching frequency. This along with small SOT-23

footprint prov ides small PCB area a pplication.

to minimize the conduction loss.

DS(ON)

Ordering Information

SY8086

SY8086

Temperature Range: -40

ƶƶƶƶ(ƶƶ

ƶƶ)ƶƶƶƶ

ƶƶƶƶ(ƶƶ

ƶƶ)ƶƶƶƶ

ƶƶƶƶ

ƶƶƶƶ

Temperature Code

Temperature Code

Optional Spec Code

Optional Spec Code

e

C to 85eC

Ordering Number Package type Note

SY8086AAC SOT23-5 1A

Featur es

•

Low R

250m

2.5-5.5V input voltage range

•

•

1.4MHz switching frequency minimizes the

external components

•

Internal softstart limits the inrush current

•

RoHS Compliant and Halogen Free

•

Compact package: SOT23 5 pin

for inter n al switche s (t op/ bottom):

DS(ON)

Ω

/200m

Ω

Applications

•

Portable Navigation Device

•

Smart phone

•

USB Dongle

•

Set Top Box

•

Media Player

Typical Applications

V

IN

C

IN

EN

IN

LX

FB

GND

Figure 1. Schematic Diagram Figure2 Efficiency vs Load Current

SY8086 Rev. 0.11 Silergy Corp. Confidential- Prepared for Customer Use Only 1

L

R

R

C1(opt.)

1

2

V

OUT

C

OUT

Page 19

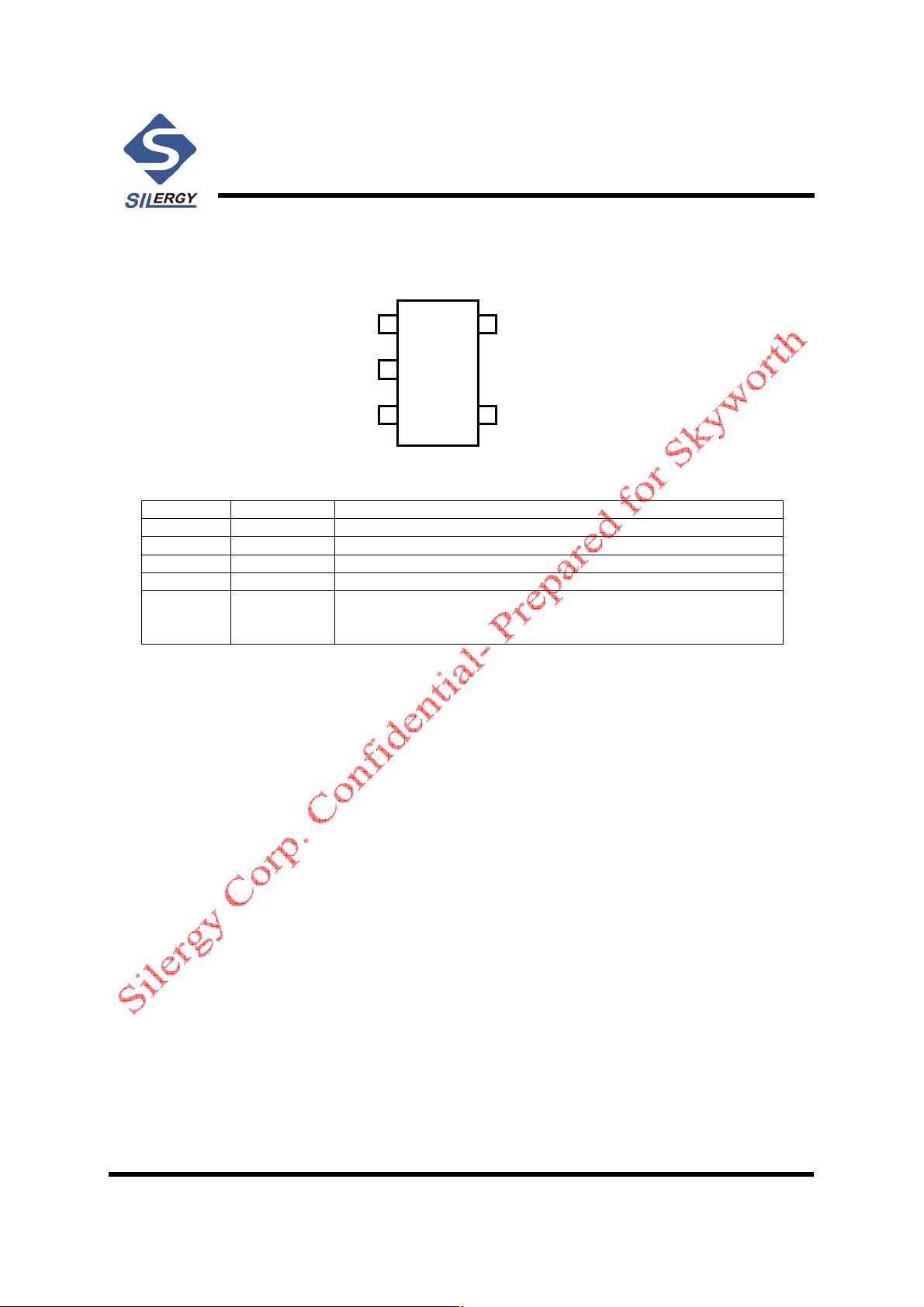

Pinout (top view)

SY8086

EN

EN

GND

GND

LX

LX

Top mark:

Pin Name Pin Number Pin Description

EN 1 Enable control. Pull high to turn on. Do not float.

GND 2 Ground pin

LX 3 Inductor pin. Connect this pin to the switching node of inductor

IN 4 Input pin. Decouple this pin to GND pin with at least 1uF ceramic cap

FB 5 Output Feedback Pin. Connect this pin to the center p oint of the output

BE

xyz

(Device code: BE, x=year code, y=wee k code , z = lot number code )

resistor divider (as shown in Figure 1) to progra m th e output voltage:

Vout=0.6*(1+R

Absolute Maximu m Ratings

Supply Input Voltage --------------------------------------------------------------------------------------------- 6.0V

Enable, FB Voltage------------------------------------------------------------------------------------------------ V

Power Dissipation, P

Package Thermal Resistance (Note 2)

SOT23-5,

SOT23-5,

Junction Temperature Range ------------------------------------------------------------------------------------ 150°C

Lead Temperature (Soldering, 10 sec.) ------------------------------------------------------------------------- 260°C

Storage Temperature Range ------------------------------------------------------------------------------------ESD Susceptibility (Note 2)

HBM (Human Body Mode) -------------------------------------------------------------------------------------- 2kV

MM (Machine Mode) ----------------------------------------------------------------------------------------------200V

D

@ TA = 25°C SOT-23-5 -------------------------------------------------------------- 0.4W

θ

JA

------------------------------------------------------------------------------------------ 250°C/W

θ

JC

-------------------------------------------------------------------------------------------130°C/W

1

1

2

2

3

3

SOT23-5

1/R2

(Note 1)

5

5

FB

FB

4

4

IN

IN

)

IN

+ 0.6V

-

65°C to 150°C

Recommended Operating Conditions

Supply Input Voltage -------------------------------------------------------------------------------------------- 2.5V to 5.5V

Junction Temperature Range ---------------------------------------------------------------------------------- -40°C to 125°C

Ambient Temperature Range ----------------------------------------------------------------------------------

(Note 3)

-

40°C to 85°C

SY8086 Rev. 0.11 Silergy Corp. Confidential- Prepared for Customer Use Only 2

Page 20

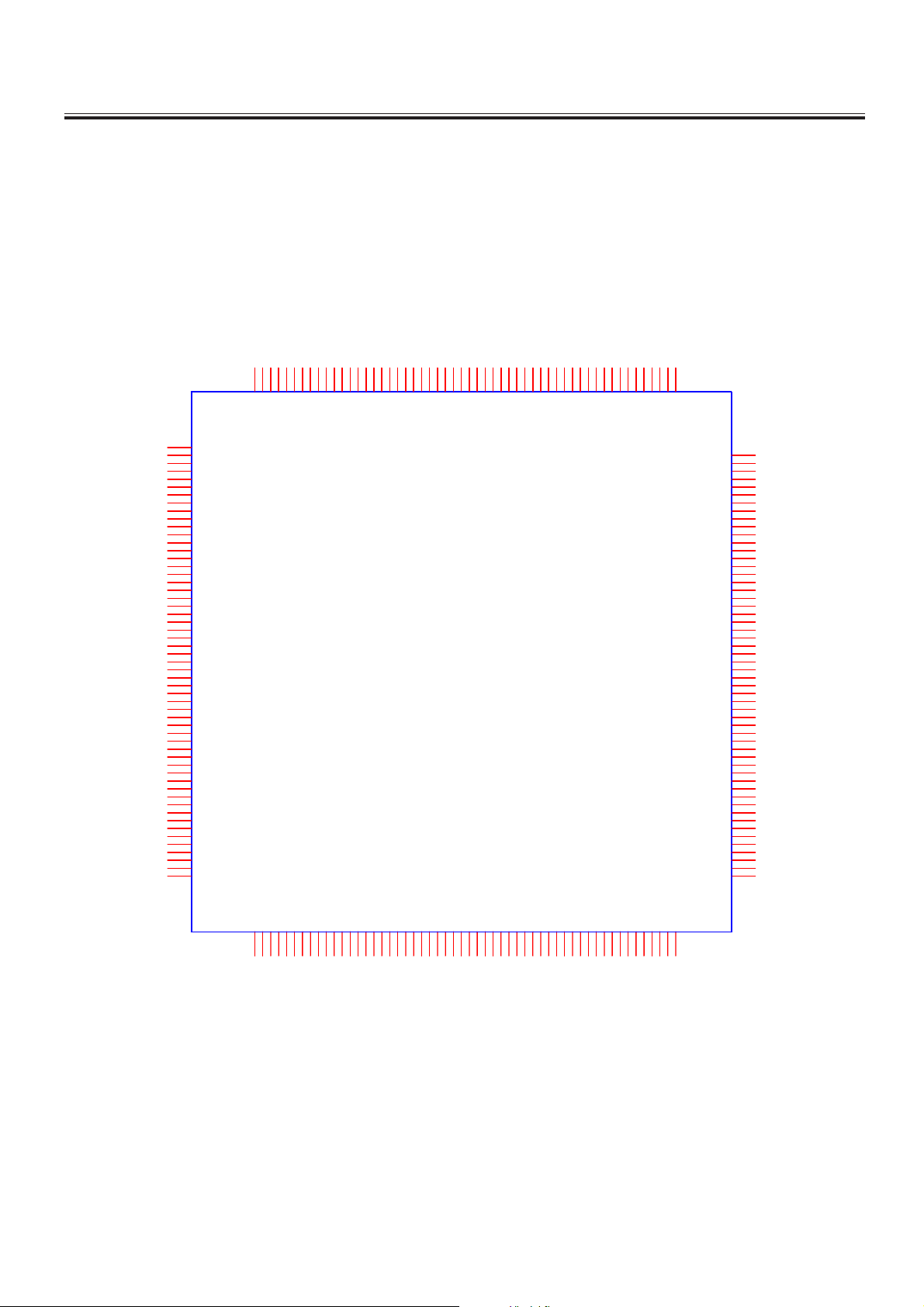

IC Block Diagram

U10(LCDTV CONTROLLER WITH VIDEO ECODE)MST6E181VS

PIN DIAGRAM (MST6E181VS)

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

NC

NC

LDQS0

LDQM0

A_DDR1_BA0

DVDD_DDR_1.2V

A_DDR1_DQ8

A_DDR1_DQ9

AVDDIO_2.5V

A_DDR1_DQ10

A_DDR1_DQ11

A_DDR1_DQ12

A_DDR1_DQ13

A_DDR1_DQ14

AVDDIO_2.5V

A_DDR1_DQ15

A_DDR1_MCLKZ

AVDDIO_2.5V

A_DDR1_MCLK

A_DDR1_CKE

A_DDR1_A12

A_DDR1_A11

A_DDR1_A9

AVDDIO_2.5V

A_DDR1_A8

A_DDR1_A7

A_DDR1_A6

A_DDR1_A5

A_DDR1_A4

AVDD_NODIE

DVDD_NODIE

GND_EFUSE

GPIO11/SAR0

GPIO12/SAR1

GPIO13/SAR2

GPIO10/PMGPIO

GPIO6/PM1/TX

GPIO8/PM5/RX

GPIO9/PM6/CS1

AVDDIO_2.5V

GPIO7/PM4/POWER_ON

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216

217

AVDD_PLL

UDQM0

UDQS0

A_MVREF

NC

VDDC

DDCR_DA

VDDP_3

DDCR_CK

TESTPIN

DM_P0

DP_P0

DM_P1

DP_P1

SPI_CK

SPI_DI

SPI_DO

SPI_CZ

DDCA_CK

DDCA_DA

E-pad

AVDDIO_2.5V

A_DDR1_DQ4

A_DDR1_DQ7

A_DDR1_DQ6

A_DDR1_DQ5

AVDDIO_2.5V

A_DDR1_DQ3

A_DDR1_DQ2

A_DDR1_DQ1

A_DDR1_DQ0

AVDDIO_2.5V

A_DDR1_CAS

A_DDR1_RAS

A_DDR1_WEZ

A_DDR1_BA1

A_DDR1_A0

A_DDR1_A1

A_DDR1_A2

A_DDR1_A3

A_DDR1_A10

NC

NC

VDDC

VDDP_2

GPIO21/PWM1

GPIO20/PWM0

GPIO77/I2S_OUT_MUTE/PWM3/LVSYNC

MST6E181VS

128

127

126

125

124

123

122

121

120

119

118

117

116

115

VDDC

AVDD_LPLL

R_ODD7/RXO0-

R_ODD5/RXO1-

AVDD2P5_MOD

GPIO75/I2S_IN_SD/PWM5/TX3/LDE

GPIO74/I2S_IN_WS/PWM4/RX3/LCK

GPIO76/I2S_IN_BCK/PWM2/LHSYNC

R_ODD3/RXO2-

R_ODD1/RXOC-

R_ODD6/RXO0+

R_ODD4/RXO1+

R_ODD2/RXO2+

114

113

112

111

110

G_ODD3/RXE0-

G_ODD7/RXO3-

G_ODD5/RXO4-

G_ODD6/RXO3+

G_ODD4/RXO4+

R_ODD0/RXOC+

109

G_ODD2/RXE0+

AVDD2P5_MOD

108

G_ODD1/RXE1-

107

G_ODD0/RXE1+

106

B_ODD7/RXE2-

105

B_ODD6/RXE2+

104

B_ODD5/RXEC-

103

B_ODD4/RXEC+

102

B_ODD3/RXE3-

101

B_ODD2/RXE3+

100

B_ODD1/RXE4-

99

B_ODD0/RXE4+

98

NC

97

GPIO49

96

GPIO47

95

GPIO45

94

GPIO38

93

GPIO37

92

GPIO36

91

GPIO32/I2S_OUT_BCK

90

GPIO30/I2S_OUT_MCK

89

GPIO28

88

VDDP_1

87

VDDC

86

GPIO27/SPDIF_OUT

85

GPIO26/SPDIF_IN/RX1/PWM3

84

GPIO25/TUNER_SDA

83

GPIO24/TUNER_SCL

82

GPIO23/I2S_OUT_SD/TX2

81

GPIO22/I2S_OUT_WS/RX2

80

TAGC

79

SIFM

78

SIFP

77

AVDD25_PGA

76

VIFP

75

VIFM

74

AVSS_PGA

73

AVDD25_REF

72

AVDD_DMPLL

71

XTAL_OUT

70

XTAL_IN

69

NC

68

NC

67

NC

66

LINEOUT_R0

65

LINEOUT_L0

64

LINEOUT_R3

63

LINEOUT_L3

62

AVDD_AU33

61

LINEIN_R5

60

LINEIN_L5

59

LINEIN_R4

58

LINEIN_L4

57

LINEIN_R3

56

LINEIN_L3

55

U?

IRIN

2

1

9876543

10

RX1N

AVDD_DVI_3.3V

RX0P

RX0N

RXCP

RXCN

HOTPLUGA

RESET

CEC

HSYNC0

VDDC

NC

NC

SOGIN0

BIN0P

2726252423222120191817161514131211

GIN0M

GIN0P

VSYNC0

RIN0P

SOGIN1

BIN1P

AVDD2P5_ADC

AVDD1P2

GIN1P

GIN1M

CVBS2

CVBS3

CVBS4

AVDD3P3_ADC

RIN1P

CVBS0

CVBS1

4443424140393837363534333231302928

CVBS_OUT1

VCOM

45

LINEIN_L1

LINEIN_R0

LINEIN_L0

VRP

VRM

LINEIN_R1

AVDD_AU25

VAG

545352515049484746

NCNCNCNCNC

ARC

DDCDA_CK

RX2P

RX2N

DDCDA_DA

RX1P

-13-

Page 21

PDF "pdfFactory Pro" www.fineprint.cn

Page 22

PDF "pdfFactory Pro" www.fineprint.cn

Page 23

PDF "pdfFactory Pro" www.fineprint.cn

Page 24

PDF "pdfFactory Pro" www.fineprint.cn

Page 25

PDF "pdfFactory Pro" www.fineprint.cn

Page 26

PDF "pdfFactory Pro" www.fineprint.cn

Page 27

PDF "pdfFactory Pro" www.fineprint.cn

Page 28

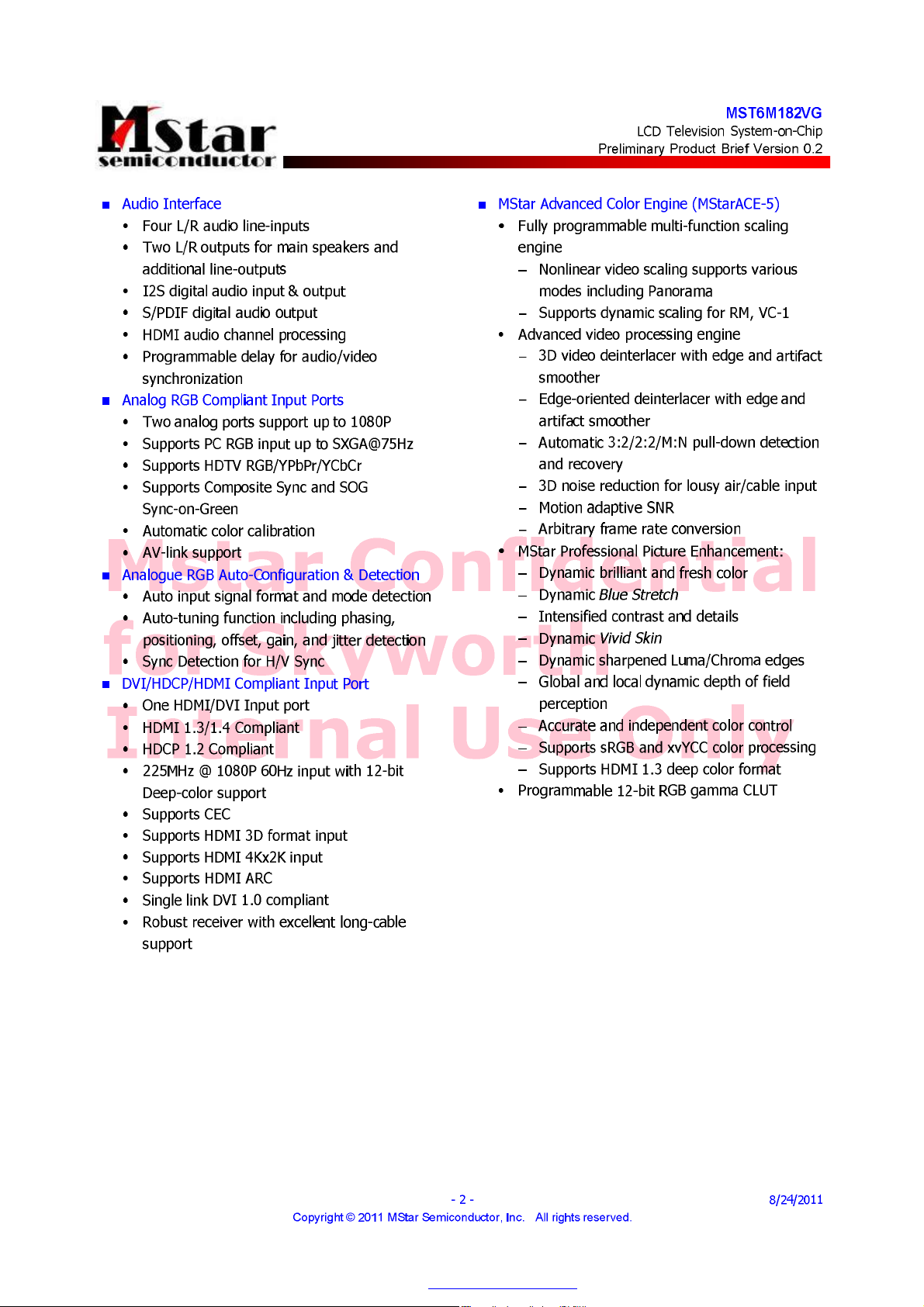

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

PIN DIAGRAM (MST6M181VG/MST6M182VG)

1 2 3 4 5 6 7 8 9 10111213141516

A RXCKP RXCKN NC NC HWRESET GPIO7 GPIO6 GND USB1_DM USB0_DP USB0_DM A

B RX1N RX 0P RX0 N NC NC NC NC IRIN GPIO8 SAR0 PWM0 USB1_DP DDCR_CK SCZ SDO B

C RX2N RX2P RX1P NC NC NC NC GPIO9 SAR2 SA R1 PW M1 GND DDCR_DA SCK SDI C

D DDCD_CK ARC

ESOGIN0BIN0PHSYNC0

DDCD_DAHOTPLUG

A

NC CEC B YPASS

MStar Confidential

F RIN0P GIN0M GIN0P VSYNC0 GND

G GND GN D GND

for Skyworth

H SOGIN1 BIN1P

J RIN1P GIN1M GIN1P AVDD_33

K CV BS2 CVBS1 N C

Internal Use Only

L CVBS0 VCOM AUVAG AUVRP

M CVBSOU T AUL0 AUL3 GND

AVDD_AL

IVE

AVDD_D

MPLL

AVDD_ME

MPLL

AVDD_MODAVDD_ RE

AVDD_M

OD

AVDD_AU

33

AVDD_126DVDD_D

AVDD_25

AVDD_AU

VDDC VDDC GND GND GND

25

VDDC VDDC GND GND GND MVREF

F

VDDP VD DC VDDC FLK2 GCLK6 RLV2P L

VDDP

AVDD_D

DR

DR

AVDD_D

DDCA_CK DDC A_DA GPIO10 GND LEDON HCON DPM D

DR

GND GND GND

AVDD_ DDRAVDD_D

DR

AVDD_DDRSCAN_BL

GND SAR3 OPT_N GCLK4 G

K

SCAN_BL

K1

GSP/

VST

GSP_R/

GCLK1

VGH_OD

D

RLVCKM RLVCKP RLV2M M

GOE/

POL

GCLK2

WPWM OPT_P F

SOE FLK3 H

GSC/

GCLK 3

GCLK 5

FLK J

VGH_EVE

N

E

K

N AUR0 AUL1 AUR3 AUOUTL1

PAUR1 AUL2AUOUTR1 GND PGA_COM GND GND

RAUR2AUOUTL0 XOUT GND GND VIFM GND

T AUOUTR0 XIN TAGC GND VIFP GND

1 2 3 4 5 6 7 8 9 10111213141516

Doc. No.:

AVDD_PG

Copyright

GND NC NC RLV1M RLV1P RLV0M RLV0P RLV3M RLV3 P N

A

I2S_OUT

I2S_OUT

I2S_OUT

2011 MStar Semiconductor, Inc. All rights reserved.

SPDIFI LLV5M LLV4M LLV3P LLV2M LLV1M RLV4M RLV4 P P

_SD

I2S_OUT

_MCK

_BCK

SPDIFO LLV3M LLVCKM LLV0M LLV0P T

_WS

- 1 - 8/29/2011

PDF "pdfFactory Pro" www.fineprint.cn

LLV5P LLV4P LLV CKP LLV2P LLV1P RLV5 M RLV5 P R

Page 29

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

PIN DESCRIPTION

Analog Interface

Pin Name Pin Type Function Pin

HSYNC0 Schmitt Trigger Input

w/ 5V-tolerant

VSYNC0 Schmitt Trigger Input

w/ 5V-tolerant

BIN0P Analog Input Analog Blue Input from Channel 0 E3

SOGIN0 Analog Input Sync On Green Input from Channel 0 E2

GIN0P Analog Input Analog Green Input from Channel 0 F3

GIN0M Analog Input Reference Ground for Analog Green Input from Channel 0 F2

RIN0P Analog Input Analog Red Input from Channel 0 F1

MStar Confidential

BIN1P Analog Input Analog Blue Input from Channel 1 H3

SOGIN1 Analog Input Sync On Green Input from Channel 1 H2

GIN1P Analog Input Analog Green Input from Channel 1 J3

GIN1M Analog Input Reference Ground for Analog Green Input from Channel 1 J2

RIN1P Analog Input Analog Red Input from Channel 1 J1

HSYNC / Composite Sync for VGA Input from channel 0 E4

VSYNC for VGA Input from channel 0 F4

for Skyworth

Analog Video Input/Output Interface

Pin Name Pin Type Function Pin

CVBS2 Analog Input CVBS (Composite) Video Input Channel 2 K1

CVBS1 Analog Input CVBS (Composite) Video Input Channel 1 K2

Internal Use Only

CVBS0 Analog Input CVBS (Composite) Video Input Channel 0 L1

VCOM Analog Input CVBS Input Reference Ground L2

CVBSOUT Analog Output CVBS (Composite) Video Output Channel M1

Analog Audio Input/Output Interface

Pin Name Pin Type Function Pin

I2S_OUT_WS I/O w/ 5V-tolerant Word Select Output; 4mA driving strength /

Universal Asynchronous Receiver 2 (UART2_RX)

I2S_OUT_SD I/O w/ 5V-tolerant Audio Serial Data Output; 4mA driving strength /

Universal Asynchronous Transmitter 2 (UART2_TX)

SPDIFI Input w/ 5V-tolerant S/PDIF Audio Input /

Pulse Width Modulation Output; 4mA driving strength

(PWM3)

SPDIFO Output S/PDIF Audio Output; 4mA driving strength T9

Doc. No.:

Copyright

2011 MStar Semiconductor, Inc. All rights reserved.

- 2 - 8/29/2011

T8

P8

P9

PDF "pdfFactory Pro" www.fineprint.cn

Page 30

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

Pin Name Pin Type Function Pin

I2S_OUT_MCK Output w/ 5V-tolerant Audio Master Clock Output R8

I2S_OUT_BCK Output w/ 5V-tolerant Audio Bit Clock Output R9

AUL0 Analog Input Audio Line Input Left Channel 0 M2

AUR0 Analog Input Audio Line Input Right Channel 0 N1

AUL1 Analog Input Audio Line Input Left Channel 1 N2

AUR1 Analog Input Audio Line Input Right Channel 1 P1

AUL2 Analog Input Audio Line Input Left Channel 2 P2

AUR2 Analog Input Audio Line Input Right Channel 2 R1

AUL3 Analog Input Audio Line Input Left Channel 3 M3

AUR3 Analog Input Audio Line Input Right Channel 3 N3

AUVRP Analog Output Positive Reference Voltage for Audio ADC L4

MStar Confidential

AUVAG Analog Output Reference Voltage for Audio Common Mode L3

AUOUTL1 Analog Output Main Audio Output Left Channel 1 N4

AUOUTR1 Analog Output Main Audio Output Right Channel 1 P3

AUOUTL0 Analog Output Main Audio Output Left Channel 0 R2

AUOUTR0 Analog Output Main Audio Output Right Channel 0 T2

for Skyworth

Mini-LVDS Interface

Pin Name Pin Type Function Pin

LLV5M Output Mini-LVDS L-Link Channel 5 Negative Data Output P10

LLV5P Output Mini-LVDS L-Link Channel 5 Positive Data Output R10

Internal Use Only

LLV4M Output Mini-LVDS L-Link Channel 4 Negative Data Output P11

LLV4P Output Mini-LVDS L-Link Channel 4 Positive Data Output R11

LLV3M Output Mini-LVDS L-Link Channel 3 Negative Data Output T11

LLV3P Output Mini-LVDS L-Link Channel 3 Positive Data Output P12

LLV2M Output Mini-LVDS L-Link Channel 2 Negative Data Output P13

LLV2P Output Mini-LVDS L-Link Channel 2 Positive Data Output R13

LLV1M Output Mini-LVDS L-Link Channel 1 Negative Data Output P14

LLV1P Output Mini-LVDS L-Link Channel 1 Positive Data Output R14

LLV0M Output Mini-LVDS L-Link Channel 0 Negative Data Output T14

LLV0P Output Mini-LVDS L-Link Channel 0 Positive Data Output T15

LLVCKM Output Mini-LVDS L-Link Negative Clock Output T12

LLVCKP Output Mini-LVDS L-Link Positive Clock Output R12

RLV5M Output Mini-LVDS R-Link Channel 5 Negative Data Output R15

RLV5P Output Mini-LVDS R-Link Channel 5 Positive Data Output R16

Doc. No.:

Copyright

PDF "pdfFactory Pro" www.fineprint.cn

2011 MStar Semiconductor, Inc. All rights reserved.

- 3 - 8/29/2011

Page 31

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

Pin Name Pin Type Function Pin

RLV4M Output Mini-LVDS R-Link Channel 4 Negative Data Output P15

RLV4P Output Mini-LVDS R-Link Channel 4 Positive Data Output P16

RLV3M Output Mini-LVDS R-Link Channel 3 Negative Data Output N14

RLV3P Output Mini-LVDS R-Link Channel 3 Positive Data Output N15

RLV2M Output Mini-LVDS R-Link Channel 2 Negative Data Output M16

RLV2P Output Mini-LVDS R-Link Channel 2 Positive Data Output L16

RLV1M Output Mini-LVDS R-Link Channel 1 Negative Data Output N10

RLV1P Output Mini-LVDS R-Link Channel 1 Positive Data Output N11

RLV0M Output Mini-LVDS R-Link Channel 0 Negative Data Output N12

RLV0P Output Mini-LVDS R-Link Channel 0 Positive Data Output N13

RLVCKM Output Mini-LVDS R-Link Negative Clock Output M14

MStar Confidential

RLVCKP Output Mini-LVDS R-Link Positive Clock Output M15

TCON Interface

Pin Name Pin Type Function Pin

POL Output Polarity Control Single E15

SOE Output Source Output Enable H15

GSP/

VST

GCLK6 Output Gate Clock for GIP Panel L15

GCLK5 Output Gate Clock for GIP Panel K15

Internal Use Only

GCLK4 Output Gate Clock for GIP Panel G16

GSC/

GCLK3

GOE/

GCLK2

GSP_R/

GCLK1

SCAN_BLK1 Output Scan Backlight Control Signal 1 F14

SCAN_BLK Output Scan Backlight Control Signal E14

OPT_N Output The Output Pin to Indicate Reverse State G15

for Skyworth

Output Gate Start Pulse for LTD Panel /

Vertical start pulse for GIP Panel

Output Gate Shift Clock for LTD Panel /

Gate Clock for GIP Panel

Output Gate Clock for GIP Panel /

Gate Output Enable for LTD Panel

Output Right Gate Start Pulse for LTD Panel /

Gate Clock for GIP Panel

H14

J15

E16

J14

OPT_P Output The Output Pin to Indicate Reverse State F16

FLK3 Output Gate Modulation Signal H16

FLK2 Output Gate Modulation Signal L14

FLK Output Gate Modulation Signal J16

Doc. No.:

Copyright

2011 MStar Semiconductor, Inc. All rights reserved.

- 4 - 8/29/2011

PDF "pdfFactory Pro" www.fineprint.cn

Page 32

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

Pin Name Pin Type Function Pin

WPWM Output PWM Output for Wavy Noise F15

HCON Output H Inversion Control Signal on DPC D15

DPM Output Power Sequence Control Signal D16

LEDON Output LED On D14

VGH_ODD Output VGH Odd for GIP Panel K14

VGH_EVEN Output VGH Even for GIP Pane K16

DVI/HDMI Interface

Pin Name Pin Type Function Pin

RXCKN DVI/HDMI Input Negative DVI/HDMI Input for A Link Clock Channel A3

RXCKP DVI/HDMI Input Positive DVI/HDMI Input for A Link Clock Channel A2

MStar Confidential

RX0N DVI/HDMI Input Negative DVI/HDMI Input for A Link Data Channel 0 B3

RX0P DVI/HDMI Input Positive DVI/HDMI Input for A Link Data Channel 0 B2

RX1N DVI/HDMI Input Negative DVI/HDMI Input for A Link Data Channel 1 B1

RX1P DVI/HDMI Input Positive DVI/HDMI Input for A Link Data Channel 1 C3

RX2N DVI/HDMI Input Negative DVI/HDMI Input for A Link Data Channel 2 C1

RX2P DVI/HDMI Input Positive DVI/HDMI Input for A Link Data Channel 2 C2

ARC DVI/HDMI Output Audio Return Channel D2

for Skyworth

Serial Flash Interface

Internal Use Only

Pin Name Pin Type Function Pin

SCK

SDI

SDO Input w/ 5V-tolerant SPI Flash Serial Data Output B16

SCZ

IRIN Input w/ 5V-tolerant IR Receiver Input B9

Output

Output

Output

SPI Flash Serial Clock C15

SPI Flash Serial Data Input C16

SPI Flash Chip Select B15

GPIO Interface

Pin Name Pin Type Function Pin

GPIO10 I/O w/ 5V-tolerant

GPIO9 I/O w/ 5V-tolerant General Purpose Input/Output; 4mA driving strength C9

GPIO8 I/O w/ 5V-tolerant General Purpose Input/Output /

GPIO7 I/O w/ 5V-tolerant General Purpose Input/Output; 4mA driving strength

Doc. No.:

Copyright

General Purpose Input/Output; 4mA driving strength

Universal Asynchronous Receiver 0 (UART0_RX)

For Power Management Only

- 5 - 8/29/2011

2011 MStar Semiconductor, Inc. All rights reserved.

PDF "pdfFactory Pro" www.fineprint.cn

D12

B10

A10

Page 33

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

Pin Name Pin Type Function Pin

GPIO6 I/O w/ 5V-tolerant General Purpose Input/Output /

Word Select Output; 4mA driving strength (I2S_OUT_WS) /

Universal Asynchronous Transmitter 0 (UART0_TX)

PWM1 Output w/ 5V-tolerant Pulse Width Modulation Output; 4mA driving strength C12

PWM0 Output w/ 5V-tolerant Pulse Width Modulation Output; 4mA driving strength B12

SAR3 Analog Input SAR Low Speed ADC Input 3 G14

SAR2 Analog Input SAR Low Speed ADC Input 2 C10

SAR1 Analog Input SAR Low Speed ADC Input 1 C11

SAR0 Analog Input SAR Low Speed ADC Input 0 B11

A11

USB Interface

MStar Confidential

Pin Name Pin Type Function Pin

USB0_DP Analog I/O USB Non Inverting Data Input/Output for Port 0 A14

USB0_DM Analog I/O USB Inverting Data Input/Output for Port 0 A15

USB1_DP Analog I/O USB Non Inverting Data Input/Output for Port 1 B13

USB1_DM Analog I/O USB Inverting Data Input/Output for Port 1 A13

for Skyworth

VIF Interface

Pin Name Pin Type Function Pin

VIFM Analog Input Negative Video IF Input R6

VIFP Analog Input Positive Video IF Input T6

Internal Use Only

TAGC Analog Output Tuner Automatic Gain Control Output T4

PGA_COM Analog Input VIF PGA Negative Source P5

Misc. Interface

Pin Name Pin Type Function Pin

HWRESET Schmitt Trigger Input

w/ 5V-tolerant

DDCD_DA I/O w/ 5V-tolerant HDCP Serial Bus Data / DDC Data of DVI/HDMI D3

DDCD_CK Input w/ 5V-tolerant HDCP Serial Bus Clock / DDC Clock of DVI/HDMI D1

DDCR_DA I/O w/ 5V-tolerant DDC Data for ROM C14

DDCR_CK Input w/ 5V-tolerant DDC Clock for ROM B14

HOTPLUGA I/O w/ 5V-tolerant Hot-plug control for DVI/HDMI D4

DDCA_DA I/O w/ 5V-tolerant DDC Data for Analog port D11

Hardware Reset; active high A9

DDCA_CK I/O w/ 5V-tolerant DDC Clock for Analog port D10

Doc. No.:

Copyright

PDF "pdfFactory Pro" www.fineprint.cn

2011 MStar Semiconductor, Inc. All rights reserved.

- 6 - 8/29/2011

Page 34

MST6M181VG/MST6M182VG

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

Pin Name Pin Type Function Pin

XIN Crystal Oscillator Input Crystal Oscillator Input T3

XOUT Crystal Oscillator

Output

BYPASS For External Bypass Capacitor D7

CEC I/O Consumer Electronics Control D6

MVREF Input Reference Voltage for DDR SDRAM Interface K13

Crystal Oscillator Output R3

Power Pins

Pin Name Pin Type Function Pin

AVDD_33 3.3V Power Analog 3.3V Power J4

AVDD_25 2.5V Power Analog 2.5V Power H6

MStar Confidential

AVDD_126 1.26V Power Analog 1.26V Power H7

AVDD_AU25 2.5V Power Audio 2.5V Power J6

AVDD_AU33 3.3V Power Audio 3.3V Power M5

AVDD_DMPLL 3.3V Power Crystal Power K4

AVDD_REF 2.5V Power Demod ADC Power K6

AVDD_PGA 2.5V Power Demod PGA Power N5

AVDD_MOD 3.3V Power MOD Power K5, L5

AVDD_MEMPLL 3.3V Power PLL Power J5

AVDD_DDR 1.8V Power DDR Power D9, E13, G8, M10, M11

for Skyworth

DVDD_DDR 1.26V Power DDR 1.26V Power H8

Internal Use Only

AVDD_ALIVE 3.3V Power Alive Domain IO Power H4

VDDC 1.26V Power Digital Core Power J7, J8, K7, K8, L7, L8

VDDP 3.3V Power Digital Input/Output Power L6, M6

GND Ground Ground A12, C13, D13, F13, G1-G3, G13,

H9-H11, J9-J11, K9-K11, M4, N6, P4,

P6, P7, R4, R5, R7, T5, T7

No Connects

Pin Name Pin Type Function Pin

NC No connect A5, A6, B4-B7, C4-C7, D5, K3, N8, N9

Doc. No.:

Copyright

2011 MStar Semiconductor, Inc. All rights reserved.

- 7 - 8/29/2011

PDF "pdfFactory Pro" www.fineprint.cn

Page 35

MST6M181VG/MST6M182VG

prop

malfunctio

performance degradation.

2012010018

2012010018

LCD Television System-on-Chip

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

Doc. No.:

DISCLAIMER

MSTAR SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE

TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. NO

RESPONSIBILITY IS ASSUMED BY MSTAR SEMICONDUCTOR ARISING OUT OF THE APPLICATION

OR USER OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY

LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

Electrostatic charges accumulate on both test equipment and human bodyand can dischargewithout

detection. MST6M181VG/MST6M182VG comes with ESD protection circuitry; however, the device

may be permanently damaged when subjected to high energy discharges. The device should be

handled with

er ESDprecautions toprevent

nand

REVISION HISTORY

Document Description Date

MST6M181VG/MST6M182VG_pin_v01 Initial release Aug 2011

MST6M181VG/MST6M182VG_pin_v02 Added Ball Diameter to Mechanical Dimensions Aug 2011

MStar Confidential

for Skyworth

Internal Use Only

Doc. No.:

Copyright

PDF "pdfFactory Pro" www.fineprint.cn

2011 MStar Semiconductor, Inc. All rights reserved.

- 8 - 8/29/2011

Page 36

Preliminary Pin Diagram/Description and Mechanical Dimensions Version 0.2

2012010018

2012010018

Doc. No.:

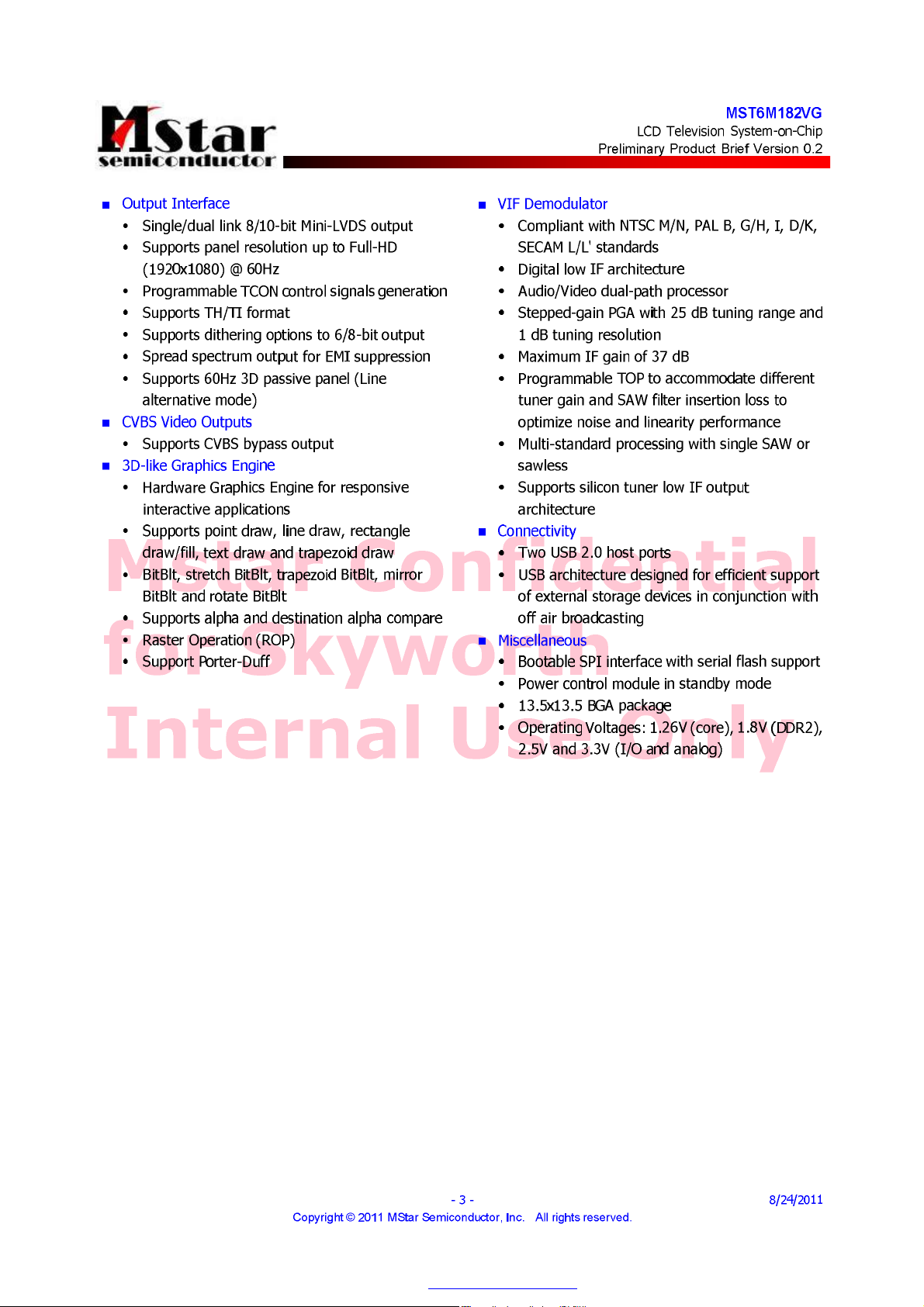

MECHANICAL DIMENSIONS

MST6M181VG/MST6M182VG

LCD Television System-on-Chip

D

E

M

S

MStar Confidential

A1

A

10

12

14

16

15

11

13

82

7

for Skyworth

Internal Use Only

E1

e

4

6

5

19

3

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

Symbol

A - - 1.40 - - 0.055

A1 0.27 - 0.37 0.011 - 0.015

M 0.70 REF 0.028 REF

S 0.22 0.26 0.30 0.009 0.010 0.012

D - 13.50 - - 0.531 -

E - 13.50 - - 0.531 -

D1 - 12.00 - - 0.472 -

E1 - 12.00 - - 0.472 -

e - 0.80 - - 0.031 -

Ball

Diameter

Millimeter Inch

Min. Nom. Max. Min. Nom. Max.

- 0.40 - - 0.016 -

b (200x)

- 9 - 8/29/2011

Doc. No.:

e

D1

Copyright

2011 MStar Semiconductor, Inc. All rights reserved.

PDF "pdfFactory Pro" www.fineprint.cn

Page 37

IC Block Diagram

8᧤0%,7&0266(5,$/)/$6+᧥623

Address

Generator

MemoryArray

P age B uffer

SI/SIO0

SO /SIO1

CS#,

WP#,

HOLD#

S CLK Clock G enerator

Data

Register

SRAM

B uffer

M ode

Logic

S tate

Machine

Y-D ecoder

Sense

Am plifier

HV

Generator

Output

B uffer

-15-

Page 38

IC Block Diagram

U19(HDMI SWITCH) PS331TQFP64G

SiI9185 Pin Mapping

POW_SINK

HPD3

SDA3

SCL3

B31

A31

POW3

B32

A32

GND

B33

A33

VCC

B34

A34

CEXT

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

SDA_SINK

48 47

Z1

SCL_SINK

46

HPD_SINK

Y1

Y2

Z2

45 44 43 42 41

GND

Z4

Z3

Y3

VCC

Y4

PS331

1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

I2C_ADDR

SCL_CTL

SDA_CTL

3334353637383940

POWDN

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

REXT

A14

B14

NC

A13

B13

GND

A12

B12

VCC

A11

B11

SCL1

SDA1

I2C_RST

B21

SDA2

HPD2

SCL2

A21

B22

POW2

A22

GND

B23

A23

B24

VCC

A24

HPD1

POW1

-16-

Page 39

)RU6N\ZRUWK(YDOXDWLRQ2QO\

Parade Technologies Inc.

PS331 HDMI/DVI SWITCH

Table1. Pin Descriptions

Name I/O Description

Axy I x = 1, 2, 3 for TMDS input channel number

y = 1, 2, 3, 4 for TMDS positive differential data or clock inputs

Bxy I x = 1, 2, 3 for TMDS input channel number

y = 1, 2, 3, 4 for TMDS negative differential data or clock inputs

Yx O x = 1, 2, 3, 4 for TMDS positive differential outputs

Zx O x = 1, 2, 3, 4 for TMDS negative differential outputs

HPDx O x = 1, 2, 3 for Hot Plug Detection output to source devices

HPD_SINK I Hot Plug Detection input from sink device; internal pull-down at ~80K ohm

Each port’s HPD can be set independently by I2C registers. See the Register Definition Table for

details

SCLx, SDAx I/O SCLx: I2C bus clock lines, SDAx: I2C bus data lines; x = 1, 2, 3; 5 V tolerant; internal pull-down

at ~1.1M ohm

SCL_SINK I/O Sink side I2C clock line

SDA_SINK I/O Sink side I2C data line

I

SDA_CTL

SCL_CTL

I2C_ADDR

REXT I Bias Current setting by External resistor, 500 ohm 1% to GND

POW_SINK O A 3.3 V CMOS output which indicates the selected port being connected to the corresponding

I2C_RST

POWDN

POW1

POW2

POW3

CEXT I/O An external capacitor is connected for supply regulation.

GND Ground connection

VCC Power supply at 3.3 V

TEL: 408-329-5540

FAX: 408-329-5541

Email: Sales@paradetech.com

I2C_ADDR: I2C control bus address LSB

SDA_CTL: I2C control data; SCL_CTL: I2C control clock

SCL_CTL / SDA_CTL control is described in the Register Definition Table

Source port

POW_SINK is the status for the selected Port Source Connection Detection. When the selected

port 5 V Source Supply is detected, POW_SINK will output HIGH to indicate the Source is

connected

For each port, the Port Source Connection status can also be accessed by I2C registers

I/O I2C_RST assertion will reset the I2C control logic; POWDN assertion will power down the chip.

PS331 power-on reset and subsequent operation are controlled automatically by on-chip

configuration logic. There is usually no need to reset the I2C control logic unless for the system

debugging and development purpose. The power down control provides a tool for system to

manage the PS331 power for power sensitive applications

I Source Connection Detection Inputs

These pins shall be connected to HDMI connector Source DC 5 V supply pins through a 37K

ohm resistor respectively. If the Source Connection Detection is not used, these pins shall be

connected to local VCC (3.3 V)

The Source Connection Detection status for each port is accessible through I2C registers

The capacitor should be 2.2 uF or larger for power noise filtering

For Customer Internal Use Only 7

Page 40

TAS5707

SLOS556A–NOVEMBER 2008 –REVISED APRIL 2009 .................................................................................................................................................

48-TERMINAL, HTQFP PACKAGE (TOP VIEW)

PHP Package

(Top View)

PVDD_B

OUT_A

PVDD_A

PVDD_A

BST_A

GVDD_OUT

SSTIMER

OC_ADJ

NC

AVSS

PLL_FLTM

PLL_FLTP

VR_ANA

484746

1

2

3

4

5

6

7

8

9

10

11

12

13

PVDD_B

PGND_AB

PGND_AB

OUT_B

45 44

15 161718 19 20

14

BST_B

43 42 41 40 39 38 37

TAS5707

BST_C

PVDD_C

PVDD_C

PGND_CD

OUT_C

21 222324

PGND_CD

36

35

34

33

32

31

30

29

28

27

26

25

OUT_D

PVDD_D

PVDD_D

BST_D

GVDD_OUT

VREG

AGND

GND

DVSS

DVDD

STEST

RESET

www.ti.com

AVDD

FAULT

MCLK

OSC_RES

DVSSO

VR_DIG

PDN

LRCLK

SCLK

SDIN

SDA

P0075-01

SCL

PIN FUNCTIONS

PIN

NAME NO.

AGND 30 P Analog ground for power stage

AVDD 13 P 3.3-V analog power supply

AVSS 9 P Analog 3.3-V supply ground

BST_A 4 P High-side bootstrap supply for half-bridge A

BST_B 43 P High-side bootstrap supply for half-bridge B

BST_C 42 P High-side bootstrap supply for half-bridge C

BST_D 33 P High-side bootstrap supply for half-bridge D

DVDD 27 P 3.3-V digital power supply

DVSSO 17 P Oscillator ground

DVSS 28 P Digital ground

GND 29 P Analog ground for power stage

GVDD_OUT 5, 32 P Gate drive internal regulator output

LRCLK 20 DI 5-V Pulldown Input serial audio data left/right clock (sample rate clock)

MCLK 15 DI 5-V Pulldown Master clock input

(1) TYPE: A = analog; D = 3.3-V digital; P = power/ground/decoupling; I = input; O = output

(2) All pullups are weak pullups and all pulldowns are weak pulldowns. The pullups and pulldowns are included to assure proper input logic

levels if the pins are left unconnected (pullups ĺ logic 1 input; pulldowns ĺ logic 0 input).

6 Submit Documentation Feedback

TYPE 5-V TERMINATION

(1)

TOLERANT

(2)

Product Folder Link(s): TAS5707

DESCRIPTION

Copyright © 2008–2009, Texas Instruments Incorporated

Page 41

TAS5707

www.ti.com

................................................................................................................................................. SLOS556A –NOVEMBER 2008 –REVISED APRIL 2009

PIN FUNCTIONS (continued)

PIN

NAME NO.

NC 8 – No connection

OC_ADJ 7 AO Analog overcurrent programming. Requires resistor to ground.

OSC_RES 16 AO Oscillator trim resistor. Connect an 18.2-k 1% resistor to DVSSO.

OUT_A 1 O Output, half-bridge A

OUT_B 46 O Output, half-bridge B

OUT_C 39 O Output, half-bridge C

OUT_D 36 O Output, half-bridge D

PDN

PGND_AB 47, 48 P Power ground for half-bridges A and B

PGND_CD 37, 38 P Power ground for half-bridges C and D

PLL_FLTM 10 AO PLL negative loop filter terminal

PLL_FLTP 11 AO PLL positive loop filter terminal

PVDD_A 2, 3 P Power supply input for half-bridge output A

PVDD_B 44, 45 P Power supply input for half-bridge output B

PVDD_C 40, 41 P Power supply input for half-bridge output C

PVDD_D 34, 35 P Power supply input for half-bridge output D

RESET

SCL 24 DI 5-V I

SCLK 21 DI 5-V Pulldown Serial audio data clock (shift clock). SCLK is the serial audio port input

SDA 23 DIO 5-V I

SDIN 22 DI 5-V Pulldown Serial audio data input. SDIN supports three discrete (stereo) data

SSTIMER 6 AI Controls ramp time of OUT_X to minimize pop. Leave this pin floating

STEST 26 DI Factory test pin. Connect directly to DVSS.

FAULT

VR_ANA 12 P Internally regulated 1.8-V analog supply voltage. This pin must not be

VR_DIG 18 P Internally regulated 1.8-V digital supply voltage. This pin must not be

VREG 31 P Digital regulator output. Not to be used for powering external circuitry.

TYPE 5-V TERMINATION

(1)

TOLERANT

(2)

DESCRIPTION

19 DI 5-V Pullup Power down, active-low. PDN prepares the device for loss of power

supplies by shutting down the noise shaper and initiating PWM stop

sequence.

25 DI 5-V Pullup Reset, active-low. A system reset is generated by applying a logic low

to this pin. RESET is an asynchronous control signal that restores the

DAP to its default conditions, and places the PWM in the hard mute

state (tristated).

2

C serial control clock input

data bit clock.

2

C serial control data interface input/output

formats.

for BD mode. Requires capacitor of 2.2 nF to GND in AD mode. The

capacitor determines the ramp time.

14 DO Backend error indicator. Asserted LOW for over temperature, over

current, over voltage, and under voltage error conditions. De-asserted

upon recovery from error condition.

used to power external devices.

used to power external devices.

Copyright © 2008–2009, Texas Instruments Incorporated Submit Documentation Feedback 7

Product Folder Link(s): TAS5707

Page 42

-18-

Page 43

Page 44

Page 45

8M48A/S Factory Adjust Menu

(V0.0)

1. Description

Enter factory mode:

Open source menu,and then press digital button “3”, “1”, “9” , “5” in

turns to enter the factory menu. Press ↑ and ↓ button to choose the

item, press OK button enter the submenu, press MENU to ruturn to

upper menu , press ← and → button to adjust the value,

Leave factory mode:

Press menu button to back to upper menu until leave factory mode。

Software information:

Enter factory mode, you can get the software information from the

bottom of the menu.

Panel information:

Enter factory mode, enter “Panel SETTING” item, you can get the

panel information from the bottom of this menu.

Aging mode:

You can press the shortcut key in the factory remote control to open

or close the aging mode.

ADC adjusts:

YPBPR source ADC:

Switch to YPBPR source, input 100% color bar pattern, enter

Page 46

factory, select “AUTO ADC” item in the “ADC CALIBRATION”

menu, press → button to begin auto adjust. When it is finish, it will

show “OK” or “FAILE”. If “FAILE” is showed, you need to try

again.

NOTE: YPBPR ADC need to do twice by use 576P and 720P

signal separate.

VGA source ADC:

Switch to PC source, input tessellated white and black signal,

enter factory, select “AUTO ADC” item in the “ADC CALIBRATION”

menu, press → button to begin auto adjust. When it is finish, it will

show “OK” or “FAILE”. If “FAILE” is showed, you need to try again.

Page 47

White balance:

Enter factory mode, enter “W/B ADJUST” item, you can adjust white

balance in this menu.

Over scanning:

Enter factory mode, enter “Panel SETTING” submenu, enter

“OVERSCAN” submenu, you can adjust the over scan in these menu.

OutFactory reset:

Enter factory mode, enter “SYSTEM SETTING” item, select “OUT

FACTORY SET” item and press OK button to reset the flash memory.

TV set will restart when it is finish.

INIT EEPROM:

Enter factory mode, enter “SYSTEM SETTING” item, select “FAC

RESET DEFAULT” item and press OK button to reset the EEPROM.

TV set will restart when it is finish.

Page 48

Update software (by USB):

Copy the new software (name by “MERGE.bin”) to the root directory

of USB drive. Plug the drive to the USB2 socket (if there are two USB

socket, make sure you use the socket 2). Enter factory, select “Software

Update (USB)” item and press OK button to begin update. TV set will

restart when finish. Note, you need to restart the TV set again by AC

power.

We suggest you need to do “INIT EEPROM” and “Factory reset”

after software updat

Page 49

2. More information

FACTORY MENU Default Value Remark

ADC ADJUST

MODE Select source

R-GAIN Red gain

G-GAIN Green gain

B-GAIN Blue gain

R-OFFSET Red offset

G-OFFSET Green offset

B-OFFSET Blue offset

AUTO ADC Auto ADC calibration

W/B ADJUST

MODE Select source

TEMPERATURE Select Neutral/Warm/Cool/Personal

R-GAIN Red gain

G-GAIN Green gain

B-GAIN Blue gain

R-OFFSET Red offset

G-OFFSET Green offset

B-OFFSET Blue offset

COPY ALL Copy there values to all source!

PANEL SETTING

TI MODE 1 LVDS data format

LVDS PORT 0 LVDS data interface

Page 50

LVDS BIT 8BitPanel

PWMFREQUENCY 0

PWM DUTY

OVERSCAN

OVERSCAN_RESLUTION

HPOSITION Horizontal position

VPOSITION Vertical position

HSIZE Horizontal size

VSIZE Vertical size

SYSTEM SETTING

FACHOTKEY OFF Factory hot key enable

TTX BRI 170 Logo enable

WHILE PATTERN Off NO USED

POWER REMIND 10 Preset the no signal standby time

BULE SCREEN ON Blue or Black screen when no signal

VIDEO AGC ON

DLC ON DLC enable

WHILE BLACK STRENCH Off White/black strength enable

POWER CONDITION Off Power state remember

FAC RESET DEFAULT Reset the EEPROM

OUT FACTORY RESET Reset the flash memory

AGING MODE off

If you set this item on, put the “stop”

key on the

remote control can exit aging mode .

CHANNEL PRESET Reset channel to default

Page 51

Channel Preset Reset channel to default

NO SIGNAL MUTE AMP

OUT FAC SOUND SYS BG

AGC GAIN 19

LANGUAGE SETTING

S-CHINESE

SPANISH

FRENCH

PORTUGUESE

RUSSIAN

BIG CHINESE

BULGARIAN

SLOVAK

FINNISH

INDONESIA

ARABIC

Arabic

FARSI

HEBREW

THAI

VIETNAM

TURKISH

SOURCE SETTING

TV On

繁体中文

西班牙语

法语

葡萄牙语

俄罗斯语

繁体中文

保加利亚语

斯洛伐克语

芬兰语

印度尼西亚

阿拉伯语

阿拉伯语

波斯语

希伯来语

泰语

越南文

土耳其文

Page 52

AV1 Off

SCART Off

HDMI1 On

HDMI2 On

HDMI3 On

YPbPr1 On

USB1 On

USB2 On

AGALOG CURVE

MODE

PICTURE MODE

BRIGHTNESS CURVE

CONTRAST CURVE

SATURATION CURVE

HUE CURVE

SHARPNESS CURVE

VOLUME CURVE

BACKLIGHT 100

HOTEL FUNCTION

HOTEL MODE off Hotel mode enable

IR LOCK off

LOCAL KEY LOCK off

USER SETTING SAVE On

VOLUME FIXED off

POWER ON VOL VALUE 10

Page 53

MAX VOLUME 30

POWER ON SOURCE TV

SCALE LOCK off

CHANNEL SEARCH LOCK off

OTHER OPTION

SSC LVDS and DDR frequency setting

UART DEBUG HK NO USED

SPECIAL NO USED

VIF1 VIF1 VIF setting

VIF2 VIF-AGC-VGA-BASE item is used for adjust the

TUNER AGC

VIF3

POWER ON LOGO NONE

WDT On

Teletext On NO USED

Nicam On

LOGO SET IN USB

USB SRC NAME USB

Backlight display control

3D Key control On

Equalizer off

Software Update(USB)

Page 54

Instruction Manual

Size:A5

42E65

Description:

MANUAL(8M48A)

Job No.

MODEL:

32E65

REV:2

Engineering Dept:

Artwork By:

Checked By:

Approved By:

Brand Name:

P/No.

Scale:

SKYWORTH

Date:

2012-01-17

Date:

Date:

Page 55

CONTENT

CONTENT ............................................................................................................ 1

WARNING AND PRECAUTION ........................................................................ 2-3

INTRODUCTION, FUNCTIONS AND FEATURES .............................................. 4

PREPARATION .................................................................................................... 5

Positioning The TV Set ................................................................................. 5

Antenna And Power Connections ................................................................. 5

Inserting Batteries In The Remote Control Handset ..................................... 5

EXTERNAL SCHEMATIC AND INSTALLATION ............................................. 6-11

Front Panel ................................................................................................... 6

Back Panel ................................................................................................... 7

Antenna/Cable Connection .......................................................................... 8

Remote Control .........................................................................................9-11

MENU CONTROL ..........................................................................................12-16

Basic Operation ...........................................................................................12

Picture Settings ............................................................................................12

Sound Settings ............................................................................................13

Installation Settings .....................................................................................14

Setup Settings ............................................................................................15

Advanced Settings ..................................................................................... 15

PC Settings........... ..................................................................................... 16

USB CONTROL ............................................................................................ 17-22

Gentle Reminder When Using The USB Player.......................................... 17

Caution ...................................................................................................... 17

USB File Playback Support ........................................................................ 17

Remote Control .......................................................................................... 18

USB Menu .................................................................................................. 18

Video Menu ................................................................................................ 19

Music Menu ............................................................................................... 20

Photo Menu ............................................................................................... 21

Text Menu .................................................................................................. 22

TROUBLESHOOTING ...................................................................................... 23

SPECIFICATIONS ........................................................................................... 24

-1-

Page 56

WARNING AND PRECAUTION

Read all of the instructions before operating the set. Keep these instructions well

for later use.

PRODUCT

The ventilation should not be impeded by covering the ventilation

openings with items, such as newspaper, table-cloths, curtains, etc.

Do not push any objects of any kind into this unit through the cabinet slots

as they could touch the current carrying parts or short-circuit parts, resulting

in fire, electric shock, or damage to the unit.

Unplug the set when it is not used for a long period of time.

Do not dismantle this product by yourself as this may cause damage.

Do not touch the screen surface with fingers as this may scratch or mar the

LED screen.

Do not impact the LED screen with hard pressure as this may damage the

LED screen severely.

The battery (battery or batteries or battery pack) shall not be exposed

to excessive heat such as sunshine, fire or the like.

POWER

Please use the core plug as required.

PLUG

Unplug the set under the following conditions:

If the set will not be used for a long period of time.

If the power cord or the power outlet/plug is damaged.

Follow the instructions to install and adjust the product. Adjust those

controls that are covered in this operating instructions as improper

adjustment of other controls may result in damage. If this happens, unplug

the set and refer to the service personnel.

If the set is subject to impact or has been dropped to have the cabinet

damaged.

POWER CORD & SIGNAL CABLE

Protect the power cord & signal cable from being trampled.

Do not overload the power cord or power outlet.

Do not expose the power cord & signal cable to moisture.

Please protect the power cord or signal cable and do not stomp, twist and

squeeze it. Careful inspect to the power cord and signal cable.

-2-

Page 57

WARNING AND PRECAUTION

USE ENVIRONMENT

Do not install this equipment in a confined space such as a book

case or similar unit. To prevent injury, this apparatus must be securely

attached to the wall mount fastened on the wall.

Place the set on a place that allows good ventilation.

Do not use the set near damp, and cold areas, protect the set from

overheating.

Keep away from direct sunlight.

The apparatus shall not be exposed to dripping or splashing and

that no objects filled with liquids, such as vases, shall be placed

on the apparatus.

Do not use the set near dust place.

To reduce the risk of fire or electric shock, do not expose this appliance

to rain or moisture.

No naked flame sources, such as lighted candles, should be placed on

the apparatus.

CLEANING

Dust the set by wiping the screen and cabinet with a soft, clean cloth.

Do not apply excessive force to the screen when cleaning.

Do not use water or other chemical cleaner to clean the screen as this

may damage the surface of the LED screen.

COMMENT

Time function of this TV set is only a reference. It is not an exact

real-time clock.

This manual is only a guide to operate the TV set. We may change

some items of the model. But the change will not affect your normal

use. If there are any differences between the Manual and the TV set,

please take the TV set as the standard.

-3-

Page 58

INTRODUCTION, FUNCTIONS AND FEATURES

BRIEF INTRODUCTION:

Thanks for your purchase of our digital high-definition LED television! This product with

diverse functions is designed to fulfill the optimum requirements from commercial, industrial

and household uses. LED television possesses the display function of both TV and PC. It

features advanced picture performance, smaller in size and lighter in weight, meanwhile,

consumes less power and makes no radiation. The new generation LED provides you with

comfortable, safe and environmental protection feeling. Some description could be little

different base on different model.

BASIC FUNCTION

1. Auto and manual tuning.

2. AV and YPbPr inputs are available.

3. Full-function infrared remote control.

4. Sleep timer and program recall shortcut.

5. Narrow design of ultra-thin ultra-light.

6. A wealth of reception(TV / AV / YPbPr / PC / HDMI / USB).

7. Digital Still Function.

PC MONITOR FUNCTIONS

1. Auto resizing & centering, perfect geometric graphic.

2. Supports PC sound source input.

3. Supports 640x480,800x600,1024x768,1280x1024, PC formats, refresh rate is 60Hz.

FEATURES

1. Embedded digital color gain control circuit, provides better brightness and reality.

2. Embedded 5-line comb filter.

3. Black/white Level Stretch Circuit.

4. High class LCD screen features, high brightness, high contrast and wide viewing angle,

responding fast.

Component input supports 1080P high definition signal formats.

5.

. Support HDMI input.

6

7. This TV can be used as a high-performance PC monitor for it has a VGA interface.

Computer sound source can also be supported to realize the multimedia function.

8. Low power consumption in standby mode to save energy.

9. Latest high integrated digital processor chip.

-4-

Page 59

PREPARATION

Positioning The TV Set

Install Display on solid horizontal surface such

as a table or desk. For ventilation, leave a space

of at least 10cm free all around the set. To

prevent any fault and unsafe situations, please

do not place any objects on top of the set. This

apparatus can be used in tropical and/or

moderate climates.

10CM

10CM

10CM

Antenna And Power Connections

1.Connect the antenna cable into the antenna

input terminal at the rear panel and wall

antenna socket.

Insering Batteries In The

Remote Control Handset

Remove the battery cover located on the back

of the handset by gently pulling up-wards from

be indicated part.

Insert two AAA Alkaline or equivalent batteries.

Following the +/- marking in the battery

compartment.

Replace the battery cover.

Precautions when using batteries

Do not use old and new batteries together.

Do not use different types of batteries (for

example, Manganese and Alkaline batteries)

together.

Note that there are chargeable and non chargeable batteries. Do not attempt to charge

non-chargeable batteries.

Remove the batteries from the remote control

unit if you do not intend to use the unit for a

long time.

Note:

Do not drop the remote control unit.

Do not subject the remote control unit

to physical shocks.

Keep the remote control unit dry. Wetting

it may cause the unit to malfunction.

Replace the batteries with new ones when

operation of the unit deteriorates.

2.Connect the power plug into the wall outlet.

(The type of power plug provided may be

different from the above picture for some

countries.)

-5-

Page 60

EXTERNAL SCHEMATIC AND INSTALLATION

350MM350MM

Front Panel

Note: The graphics are for representation only.

3

2

3

1

7

8

6

5

1.Power Button

2.Power Indicator / Remote Sensor

3.Speakers

4.Program Up/Down Button

5.Volume Up/Down Button

6.Menu Button

7.Source Button

8.Standby Button

-6-

4

Page 61

EXTERNAL SCHEMATIC AND INSTALLATION

Back Panel

Note: The graphics are for representation only.

YP

b

P

6

YPbPr IN

r

LEFT

7

AV IN

VIDEO RIGHT

HDMI3

USB2

5V 500mA

1

HDMI IN

2

HDMI2

PC

AUDIO IN

PC IN RF IN

4 5

3

9

USB1

USB1

1

5V 500mA

8

2

HDMI1

S/PDIF

1. USB1\USB2: USB port.

2. HDMI1\HDMI2\HDMI3:Connect HDMI input signal from signal source such as DVD.

3. PC IN: Connect a PC via a VGA cable.

4. PC AUDIO IN: Audio input for PC and Audio input for HDMI when the signal is DVI timing.

5. RF IN: Connect a coaxial cable to receive signal from the antenna or cable.

6. Y Pb Pr(Component input): Connect YPbPr signal from signal source such as DVD.

Share the same AUDIO input with AV IN.

7. AV IN: Connect AUDIO and VIDEO input signal from signal source such as DVD.

8. EARPHONE: Audio output, speakers will be muted when earphone plugged.

9. S/PDIF: Use a digital optical cable to connect your TV to a compatible audio receiver.

-7-

Page 62

EXTERNAL SCHEMATIC AND INSTALLATION

Antenna /Cable Connection

There are two kinds of antenna in use.

VHF TV ANTENNA

UHF TV ANTENNA

U/V MIXER

TWO KINDS OF ANTENNA

COAXIAL ANTENNA

FLAT CABLE

No need to install adapter

(Note 1)

Need to install adapter

(Note 2)

To TV VHF/UHF

ANTENNA jack

VHF/UHF

(75 )

1. Connect the plug of the antenna cable or CATV cable to the cable (not provided

with this unit), then connect to the antenna input of this unit for best reception.

2. If the antenna cable in your home is other than the above two, or you have

problems in installing the antenna, please contact your dealer.

Notes:

1. Current outdoor antenna or cable TV usually use 75 OHM coaxial antenna cable.

For better using this kind of antenna cable.

reception, we suggest

2. Flat cable or indoor antenna are old designed, the reception may not be good enough.

-8-

Page 63

EXTERNAL SCHEMATIC AND INSTALLATION

Remote Control

1. Standby( )

Press to turn the TV on or off(standby).

2. Auto

Press to adjust the picture automatically in

PC mode.

3.Zoom

Press to select the desired picture aspect ratio.

4. Picture Mode( P.P )

Press to select the desired picture

mode.

5. Sound Mode( S.M )

Press to select the desired sound mode.

6. Program Select (0-9)

Press to select the TV channel directly.

7.Return

Button

Press to return to the previously viewed channel.

8. Freeze( )

Press to freeze or unfreeze the picture.

Note: This button is unable in USB channel.

9.Mute( )

Press to mute or restore the volume.

10.

Program Up/Down (P / )

Press to select previous/next channel.

11.Volume Up/Down (V+/V-)

Press to adjust the volume.

12.Nicam (Option)

Press to select a different sound when the

source is different.

13.Menu

Press to enter or exit from the TV menu.

14. Sleep

Press to set the time to switch the TV to

standby mode.

15.OK

Press to confirm and execute the selection.

10

12

13

15

1

2

3

6

7

9

5

4

8

11

14

-9-

Page 64

EXTERNAL SCHEMATIC AND INSTALLATION

Remote Control

16. Up/Down/Left/Right Cursor

( / / / )

Press to select or adjust the desired item

on the menu.

Note: IN USB mode, Press " / / / "

curser can return previous menu.

17.Source

Press to select the input source mode.

18.INFO

Press to display relevant information such as

screen format, source, etc.

19.USB

Press to to the USB1 or USB2 channel.enter

20.Fast Backward Button( )

Press to fast reverse in USB mode.

21.Fast Forward ( )

Press to fast forward in USB mode.

22.Previous ( )

17

19

20

24

22

16

18

21

25

23

Press to play the previous

mode.

USB

23.Next ( )

Press to play the next

USB .

mode

24.Play & Pause ( )

Press to pause playback in USB mode,

press again to continue playback.

25.Stop ( )

Press to

USB

stop the music or movie in

mode.

music or movie in

music or movie in

-10-

Page 65

EXTERNAL SCHEMATIC AND INSTALLATION

Remote Control

26.Text ( )(Option)

Press to enter the teletext menu.

27. Cancel ( )(Option)

Press this button to return to TV

program temporarily while searching for

a Teletext page. When the search is

done, the page number will be displayed

on the upper left of the screen.

Press again to return to the Teletext page.

28. SUB-PAGE ( )(Option)

Press this button to enter or exit

subpage mode (if subpage is available).

Press Red / Green buttons to select the

desired subpage.

29. Subtitle ( )(Option)

Press this button to access subtitle

service directly (if the channel has the

subtitle service broadcasting).

30. Index ( )(Option)

Press this button to display index page.

31. Mix ( )(Option)

Press this button to superimpose the

teletext over the TV program.

Press again to return to normal teletext

mode.

32. Reveal ( )(Option)

Press this button to display concealed

27

26

30 31

32 33

34

29

28

information, such as solutions to riddles

or puzzles. Press again to remove the

information from the display.

33. Size ( )(Option)

Enlarge the teletext display: Press this

button once to enlarge upper half of the

screen.Press this button again to

enlarge lower half of the screen.Press

this button again to resume to normal

screen size.

34. Colour

(Red/Green/Yellow/Blue)

Press these buttons that corresponds to

the desired menu or page number.

-11-

Page 66

MENU CONTROL

This section explains the menus of your TV. Each menu is outlined and detailed to help you

get the most from your TV.

Basic Operation

1. Press MENU on the remote control or on the TV key

panel to display the main menu.

2. Press / and / to highlight the desired menu/item.

3. Press / to change the setting.

4. Press MENU to save setting and go back to last menu.

Note:

Button on the key panel have the same functions

as the corresponding buttons on the remote control.

The scheme and description are in TV mode as below, there will be a note if there is exception.

Picture Settings

Picture Mode

Adjusts the picture mode: Personal, Bright, Normal,

Soft four kinds of image mode.

Brightness

Adjusts the brightness of the picture, and usually is

adjusted together with Contrast.

Contrast

Adjusts the difference between the light and dark areas

of the picture. To get better picture value, Contrast should

be adjusted to the proper value.

Color

Adjusts the richness of colour. This function is not available

in PC mode.

Tint

A

djust the tint of the picture.

Only can be done under the NTSC system.

Sharpness

Adjusts the sharpness of the picture. This function is not

available in PC mode.

Color Temperature

Press OK button to enter the color temperature sub menu.

Color Temperature Adjusts the colour temperature of the

picture, to select the option:

Cool, Neutral, Warm, Personal

as you desired.

PICTURE

Picture Mode

Brightness

Contrast

Color

Tint

Sharpness

Color Temperature

PICTURE

Display Mode

DNR

Backlight

PICTURE

Color Temperature

Red

Green

Blue

Personal

LOW

High

Soft

16:9

55

50

20

50

50

50

50

50

-12-

Page 67

MENU CONTROL

Neutral: Keep the original white

Warm: Red

Personal: The user may customize the color temperature.(Red/Green/Blue).

Cold: Blue.

Display Mode

To select five modes are available including: Panorama, Movie, Caption, 16:9, 4:3 and Auto.

Note: In PC channel only 16:9 and 4:3 display mode can be selected.

In HDMI channel including: Panorama, Just-Scan, Movie, Caption, 16:9, 4:3 and Auto

display mode can be selected.

DNR

To select four modes of digital noise reduction are available including Off, Low, Middle and High.

Backlight (Option)

Adjust peak brightness of the backlight (Low / Middle / High).

Sound Settings

Sound Mode

Select the most suitable sound mode according to

your watching contents(Personal, Standard, Music,