Page 1

M68/M64 Module Data Sheet

This document describes the M68/M64, a family of Network Synchronization

based on the Silicon Labs AccuTime™ technology. Besides its local oscillator, these modules can use multiple reference time and

frequency sources to generate precision time and frequency including PPS and ToD as well as IEEE Std 1588-2008. IEEE Std

1588-2008 defines the Precision Time Protocol (PTP) version 2

(PTPv2). In this manual, we will use PTP to refer to this standard.

They implement both a Grandmaster and an Ordinary PTP clock.

The M68 is a superset of the M64 and also implements both a

transparent or boundary clock.

The M68/M64 features full connectivity to gigabit networks with wirespeed passthrough technology allowing for new applications.

This document describes how to design with the M68/M64 module and how to use it in

an embedded application. The integration section includes the pinout of the module

and other physical aspects like the options of power supply. It also describes how to

connect the necessary key components which are a prerequisite for proper operation.

This document applies to software Release 3.0 of the M64/M68. Modules can be updated to Release 3.0 by following the directions in 23. Appendix 8: Firmware Upgrade.

Modules for packet network timing applications

KEY FEATURES

• Low power microprocessor technology

with hardware timestamping

•

8 Mbytes SDRAM memory, 2 Mbytes flash

memory

• 10/100/1000 Ethernet PHY

• RGMII interface to Host, or to an external

PHY

• Timing interface including PPS, TOD,

syntonized frequency

• Comprehensive IEEE 1588-2008

implementation and SyncE support

• Communication servers for serial ports,

Telnet and SSH

• Edge pads for surface mount to host

boards

• RoHS compliant

• Built-in SNTP server

• Wirespeed pass-through eliminating the

need for a switch in many applications

silabs.com | Building a more connected world. Rev. 0.1

Page 2

Table of Contents

General Description .............................8

1.

1.1 Key Feature ...............................8

1.2 Host Interface ..............................8

1.3 Communication Interfaces ..........................8

1.4 JSON Machine-to-Machine Communications ....................8

1.5 Block Diagram ..............................9

2. Packaging ...............................10

2.1 Dimensions ...............................10

2.2 Recommended Land Pattern .........................10

2.3 Soldering and Handling ...........................11

2.4 Tape and Reel ..............................11

2.4.1 Pin 1 Orientation ............................12

2.4.2 Tape and Reel Specification ........................13

3. LED Description .............................14

4. Pin List ................................15

4.1 Pin Descriptions .............................17

4.1.1 Analog Control of Oscillator ........................17

4.1.2 Write Protection ............................17

4.1.3 Serial Ports..............................17

4.1.4 PF3/LOCK Pin ............................17

4.2 Clocking ................................18

4.3 Power Supply ..............................18

4.3.1 Digital Power Supply ..........................18

4.4 Time I/O ................................19

4.4.1 Reference Time Input ..........................19

4.4.2 Precision Time Output ..........................19

5. Specifications ..............................20

5.1 Metrics ................................20

5.2 Absolute Maximum Ratings..........................20

5.3 Recommended Operating Conditions ......................20

5.4 DC Electrical Characteristics .........................21

5.5 AC Electrical Characteristics .........................21

6. PCB Design Considerations .........................22

6.1 Land Pattern...............................22

6.2 Power .................................22

6.2.1 Required Voltage............................22

6.2.2 Decoupling Capacitors ..........................23

silabs.com | Building a more connected world. Rev. 0.1 | 2

Page 3

6.3 Clock Signal MCLKOUT1 ..........................23

6.4 Ethernet Interface .............................23

6.4.1 Magnetics ..............................23

6.5 RGMII Interface..............................24

7. Application Software ...........................25

7.1

System Access ..............................25

7.2 System Files...............................25

7.3 Module Shell Environment ..........................25

7.3.1 High-Level Initialization..........................25

7.3.2 System Commands ...........................25

7.3.3 Communication Servers .........................25

7.4 Passthrough ...............................26

7.5 VLAN .................................27

7.6 MDIO .................................27

7.7 Link Speed ...............................28

7.8 PHY Reset ...............................28

7.9 SyncE .................................28

7.10 SFP .................................29

8. IEEE 1588/PTP Engine ...........................30

8.1 General Features .............................30

8.2 PTP Software Implementation .........................30

8.2.1 Protocol Layer.............................30

8.2.2 OS Abstraction Layer ..........................30

8.3 GNSS Driver...............................31

8.4 AccuTime Software ............................31

8.5 PTP API ................................31

8.5.1 Starting/Stopping the PTP Engine ......................32

8.5.2 Pulse Train ..............................32

8.5.3 Human Machine Interface .........................33

9. Network Subsystem ............................38

9.1 TCP/IP Stack Architecture ..........................38

9.2 Application Layer Components ........................38

9.2.1 DHCP Client .............................38

9.2.2 DNS Client ..............................38

9.3 BSD Sockets API .............................38

9.4 Network Initialization ............................39

10. Using the AccuTime Software .......................40

10.1 PTP Engine Modes ............................40

10.1.1 Mode 0...............................40

10.1.2 Mode 1...............................40

silabs.com | Building a more connected world. Rev. 0.1 | 3

Page 4

10.1.3 Mode 2...............................40

10.1.4 Mode 3...............................40

10.1.5 Mode 4...............................41

10.1.6 Slave-Only Mode ...........................41

10.2 GNSS Interface .............................41

10.3 PTP Clock States ............................41

10.3.1 FREE State .............................41

10.3.2 SYNTONIZING State ..........................41

10.3.3 SYNCHRONIZING State.........................42

10.3.4 HOLDOVER State ...........................42

10.4 PPS/TOD Output.............................43

10.5

Managing the Two Interfaces (M68 Only) ....................43

10.6 Unicast Operations ............................43

10.6.1 Unicast Master ............................44

10.6.2 Limiting the Total Message Rate ......................46

10.6.3 Unicast Slave ............................47

10.6.4 Unicast Both .............................49

10.6.5 Message Transmission Duration ......................50

10.6.6 Discovery Query Interval .........................50

10.6.7 Monitoring Unicast Operations .......................50

10.7 Gateway and Boundary Clock (M68 Only) ....................50

10.7.1 The Gateway Clock ..........................51

10.7.2 Managing the Two Ports .........................52

10.7.3 Unicast...............................52

10.8 Performance Optimization..........................53

10.8.1 Direct Connection ...........................54

10.8.2 Low Traffic Network ..........................54

10.8.3 High Traffic Network ..........................54

10.8.4 ITU-T G.8261, G.8265.1, G.8275.2 Settings ..................54

10.8.5 ITU-T G.8273.2, G.8275.1 settings .....................54

10.9 Power Profile ..............................55

10.10 ITU-T G.8265 Profile ...........................55

10.11 ITU-T G.8275.1 Profile ..........................56

10.12 ITU-T G.8275.2 Profile ..........................57

11. Command Reference ........................... 58

11.1 Shell Commands .............................58

11.1.1 ptp2 start ..............................58

11.1.2 ptp2 stop ..............................58

11.1.3 ptp2 hmi ..............................58

11.1.4 ptp2 config .............................59

11.1.5 ptp2 ................................59

12. JSON Usage ..............................60

12.1 Enabling JSON .............................61

silabs.com | Building a more connected world. Rev. 0.1 | 4

Page 5

13. Product Documentation ..........................62

14. Part Numbers ..............................63

15. Customer and Technical Support ......................64

16. Appendix 1: System Files .........................65

17. Appendix 2: System CLI Commands .....................68

18. Appendix 3: PTP Command Reference ....................108

19. Appendix 4: Troubleshooting LED Error Codes .................123

20. Appendix 5: Command Shell Limitations ...................124

21. Appendix 6: Environment Variable ......................125

22. Appendix 7: Clock Setup .........................128

Appendix 8: Firmware Upgrade .......................132

23.

24. Appendix 9: JSON Interface Definition ....................133

24.1 Clock Commands ...........................134

24.1.1 "clock info" ............................135

24.1.2 "clock type" ............................135

24.1.3 "clock twostep" ...........................136

24.1.4 "clock slaveonly" ..........................136

24.1.5 "clock domain" ...........................136

24.1.6 "clock priority" ...........................136

24.1.7 "clock quality" ...........................137

24.1.8 "clock profile" ...........................137

24.2 Port Commands ............................137

24.2.1 "port state" ............................137

24.2.2 "port announce" ...........................138

24.2.3 "port receipt" ............................138

24.2.4 "port sync" ............................138

24.2.5 "port delay" ............................138

24.2.6 "port pdelay" ............................138

24.2.7 "port mechanism" ..........................139

24.2.8 "port protocol" ...........................139

24.2.9 "port compatibility" ..........................139

24.2.10 "port asymmetry" ..........................139

24.2.11 "port unicast" ...........................139

24.2.12 "port profile" ...........................140

24.3 Unicast Commands ...........................140

24.3.1 "unicast status" ...........................140

24.3.2 "unicast negotiation" .........................140

24.3.3 "unicast query" ...........................141

24.3.4 "unicast duration" ..........................141

24.3.5 "unicast timeout" ..........................141

24.3.6 "unicast limit"............................141

24.3.7 "unicast filter" ...........................142

silabs.com | Building a more connected world. Rev. 0.1 | 5

Page 6

24.3.8 "unicast node" ...........................144

24.4 Power Profile Commands .........................145

24.4.1 "power gmid" ............................145

24.4.2 "power inacc" ...........................145

24.5 G8265 Profile Commands .........................145

24.6 G8275 Profile Commands .........................145

24.6.1 "g8275 priority" ...........................146

24.6.2 "g8275 steps" ...........................146

24.6.3 "g8275 [port_number] priority" ......................146

24.6.4 "g8275 [port_number] masteronly" ....................146

24.7 Dataset Commands ...........................146

24.7.1 "dataset default" ..........................147

24.7.2 "dataset current" ..........................147

24.7.3 "dataset parent" ...........................148

24.7.4 "dataset time" ...........................149

24.7.5 "dataset port [port_number]" ......................150

24.7.6 "dataset foreign [port_number]" .....................151

24.7.7 "dataset unicast [port_number]" .....................153

24.7.8 "dataset power" ...........................154

24.7.9 Dataset g8275 Commands .......................154

24.8 Time Commands ............................155

24.8.1 "time info" .............................156

24.8.2 "time sync" ............................156

24.8.3 "time arb|ptp|utc|ntp" .........................157

24.8.4 "time offset" ............................157

24.8.5 "time leap" ............................158

24.8.6 "time leap save" ...........................158

24.8.7 "time leap load" ...........................158

24.8.8 "time leap 59" ...........................158

24.8.9 "time leap 61" ...........................158

24.8.10 "time leap 59|61 YYYY-MM-DD" .....................159

24.8.11 "time timescale" ..........................159

24.8.12 "time update" ...........................159

24.8.13 "time holdover" ..........................159

24.9 Frequency Commands ..........................160

24.9.1 "freq status" ............................160

24.9.2 "freq option" ............................160

24.9.3 "freq ref" .............................160

24.9.4 "freq prefer" ............................161

24.9.5 "freq input [input_number]" .......................162

24.10 SyncE Commands ...........................163

24.10.1 "synce status" ...........................163

24.10.2 "synce esmc" ...........................163

24.10.3 "synce quality" ...........................164

24.11 GPS (PPS/TOD-Input) Commands .....................164

24.11.1 "gps status" ............................165

silabs.com | Building a more connected world. Rev. 0.1 | 6

Page 7

24.11.2 "gps ppsin" ............................165

24.11.3 "gps todin" ............................166

24.11.4 "gps delay" ............................166

24.11.5 "gps class" ............................166

24.11.6 "gps interface" ...........................166

24.11.7 "gps format" ...........................167

24.11.8

"gps void" ............................167

24.11.9 "gps message"...........................167

24.11.10 "gps cm" ............................168

24.11.11 "gps nmea" ...........................169

24.12 Pulsetime (PPS/TOD-Output) Commands ...................169

24.12.1 "pulsetime status"..........................169

24.12.2 "pulsetime mode" ..........................170

24.12.3 "pulsetime error" ..........................170

24.12.4 "pulsetime auto" ..........................170

24.12.5 "pulsetime pulse" ..........................170

24.12.6 "pulsetime todout" .........................171

24.12.7 "pulsetime delay" ..........................171

24.12.8 "pulsetime interface" .........................171

24.12.9 "pulsetime format" .........................171

24.12.10 "pulsetime void" ..........................172

24.12.11 "pulsetime zone" .........................172

24.12.12 "pulsetime cm" ..........................173

24.12.13 "pulsetime stop" ..........................173

24.12.14 "pulsetime start" ..........................174

24.13 Nettime (SNTP Service) Commands .....................174

24.13.1 "nettime status" ..........................174

24.13.2 "nettime mode" ..........................175

24.13.3 "nettime poll" ...........................175

24.13.4 "nettime stop" ...........................175

24.13.5 "nettime start" ...........................175

24.14 Engine Commands ..........................175

24.14.1 "engine json on|off|ver" ........................176

24.14.2 "engine init <key>" .........................176

24.14.3 "engine nvm" ...........................176

24.14.4 "engine debug" ..........................176

24.14.5 "engine verbose" ..........................177

24.14.6 "engine monitor" ..........................177

24.14.7 "engine port [port_number]" ......................177

24.14.8 "engine asymmetry [port_number]" ....................178

24.14.9 "engine freqout" ..........................178

25. EULA .................................179

silabs.com | Building a more connected world. Rev. 0.1 | 7

Page 8

M68/M64 Module Data Sheet

General Description

1. General Description

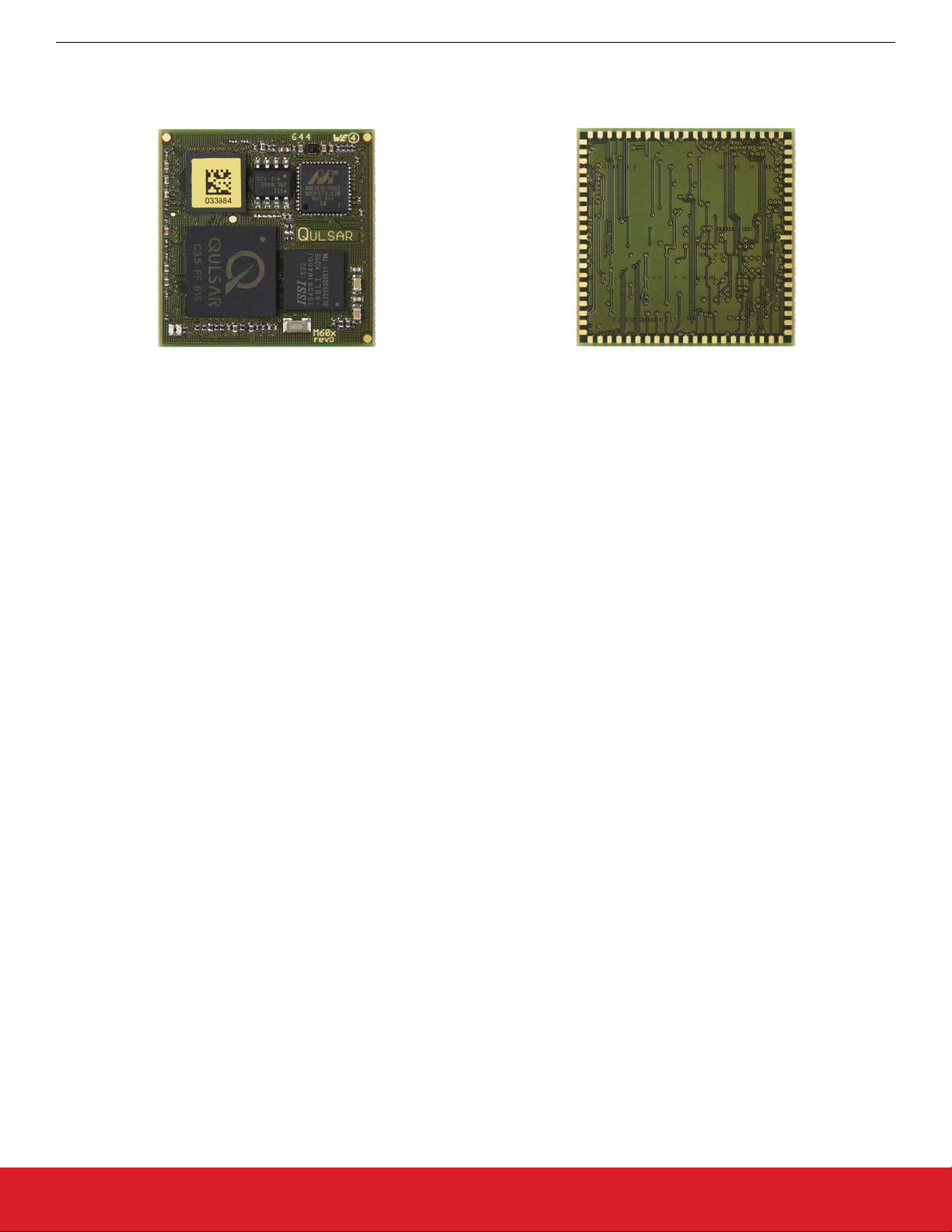

This section shows the M68/M64 module in approximately two times the actual size. The M68 adds an oscillator to the module.

Figure 1.1. Top Side and Bottom Side Views

1.1 Key Feature

•

Low power microprocessor technology with hardware timestamping

• 8 Mbytes SDRAM memory, 2 Mbytes flash memory

• 10/100/1000 Ethernet PHY with full PTP functionality

• RGMII interface to Host, or to an external PHY. For the M68 this includes full PTP functionality.

• Timing interface including PPS, TOD, syntonized frequency

• Comprehensive IEEE 1588-2008 implementation and SyncE support

• Communication servers for serial ports, Telnet and SSH

• Edge pads for surface mount to host boards

• RoHS and WEE compliant

• Built-in SNTP server

• Wirespeed pass-through eliminating the need for a switch in many applications

1.2 Host Interface

The RGMII Host Interface of the module is intended to be connected directly to a generic RGMII interface offered by the host, or an

RGMII PHY. The designer can choose voltage levels for adaptation to his RGMII port of the host system.

For applications with host processors offering only an SGMII interface, a PHY IC such as the 88E1512 from Marvell that converts between SGMII and RGMII needs to be added.

1.3 Communication Interfaces

The M68/M64 offers three asynchronous serial ports besides the two Ethernet ports. Advanced users with the Development Kit will also

have access to other serial and parallel interfaces including an analog section to connect to other peripherals outside the module.

1.4 JSON Machine-to-Machine Communications

New with Firmware release 3.0 is the addition of JavaScript Object Notation (JSON) structured configuration information. This greatly

simplifies the development of software on host systems to interface with the M64/M68.

silabs.com | Building a more connected world. Rev. 0.1 | 8

Page 9

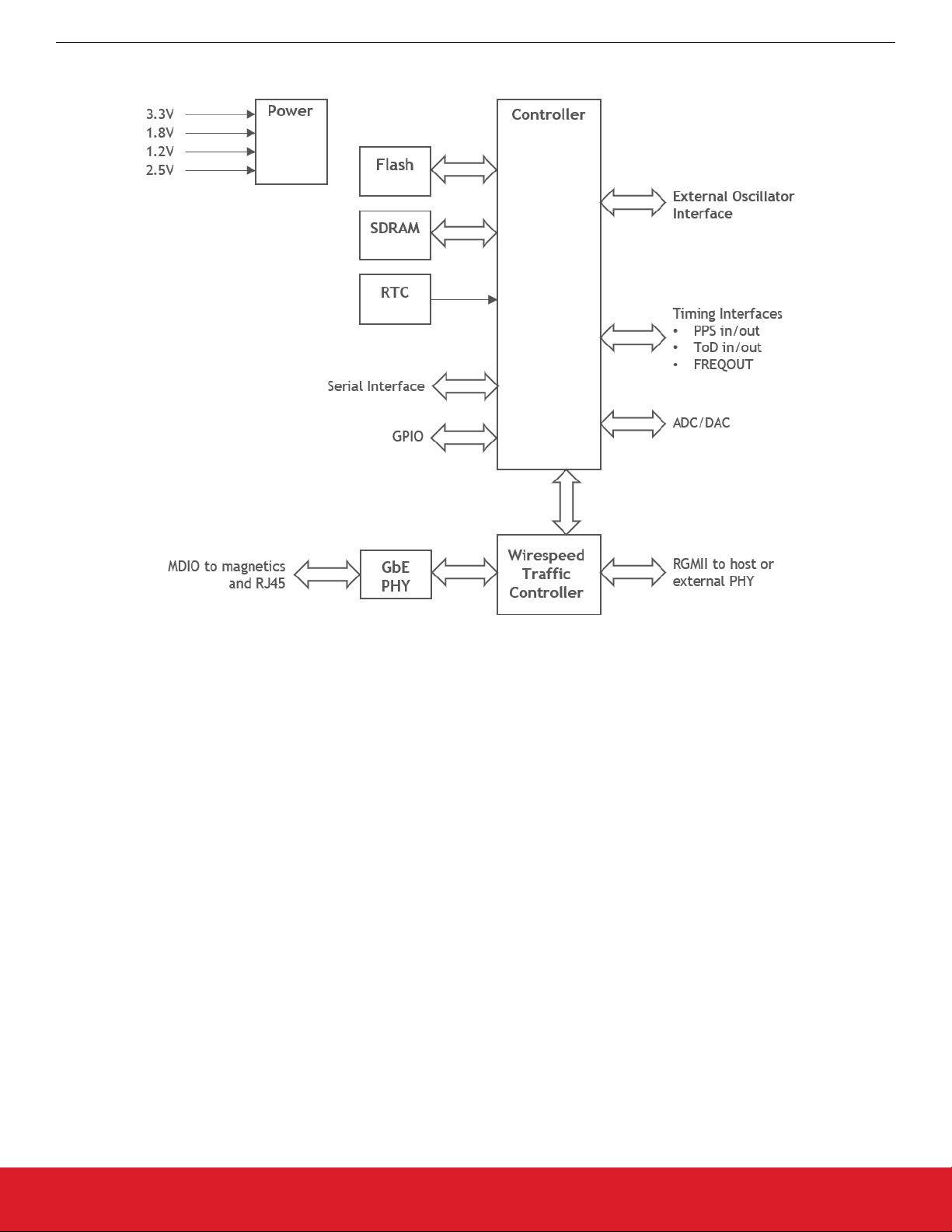

1.5 Block Diagram

M68/M64 Module Data Sheet

General Description

Figure 1.2. M68/M64 Block Diagram

silabs.com | Building a more connected world. Rev. 0.1 | 9

Page 10

M68/M64 Module Data Sheet

Packaging

2. Packaging

2.1 Dimensions

The module dimensions match the standard for a LGA-84 package, with exception for the height. The height varies over the module

surface, with maximum and minimum values given below.

When soldered directly to the motherboard, the module’s distance to that board depends on the amount of solder used but can usually

be considered to be zero.

Figure 2.1. Dimensions for M68/M64 (unit: mm)

Note: The height may vary with component vendor specification.

2.2 Recommended Land Pattern

This is the recommended PCB land pattern for direct soldering of the M68/M64 module to a host board for all designs.

Figure 2.2. Recommended Land Pattern (unit: mm)

silabs.com | Building a more connected world. Rev. 0.1 | 10

Page 11

M68/M64 Module Data Sheet

2.3 Soldering and Handling

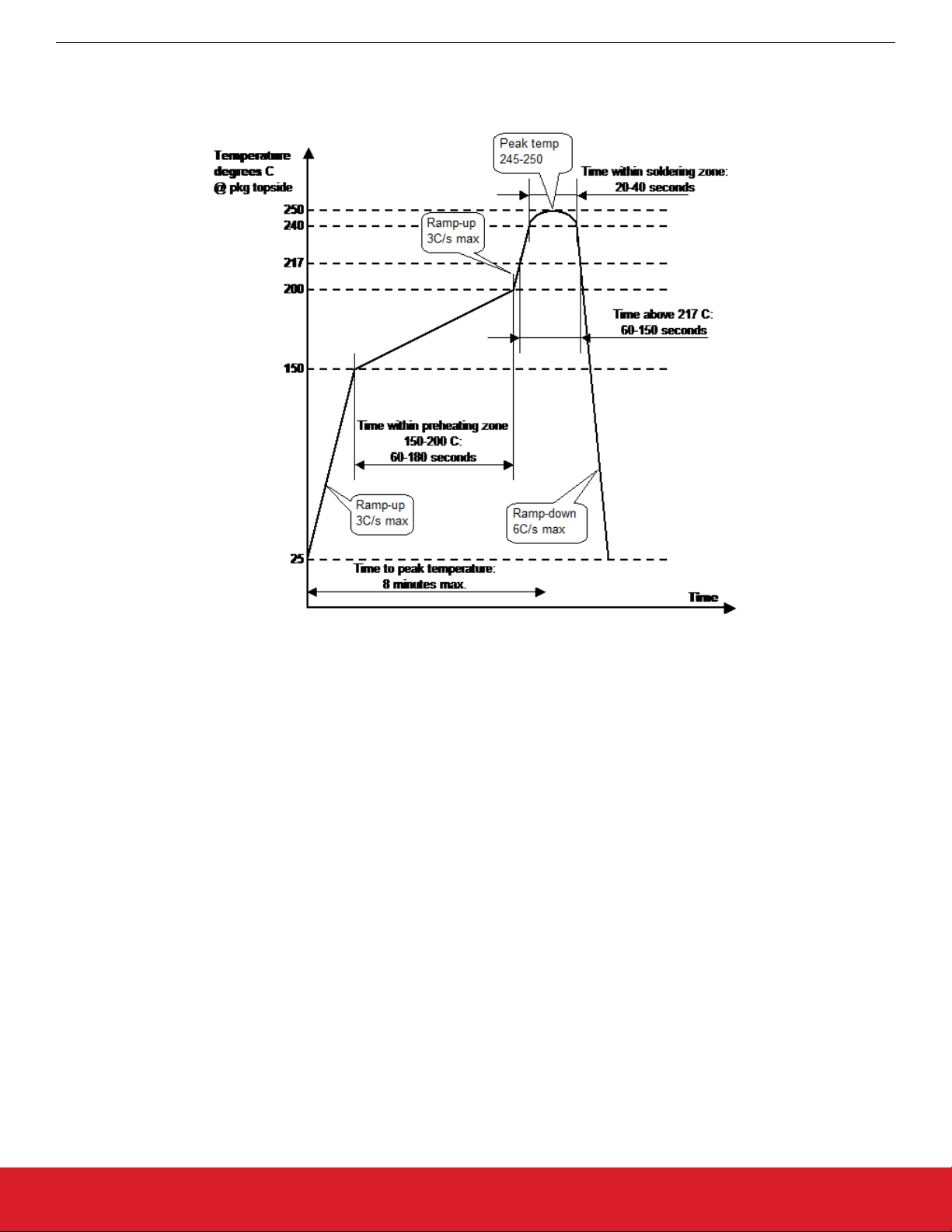

the M68/M64 is a RoHS-compliant device, it is designed to tolerate lead-free soldering processes. The diagram below shows the

Since

recommended soldering profile for the device.

Packaging

Figure 2.3. Reflow Soldering Profile

The M68/M64 is classified as MSL 3.

2.4 Tape and Reel

M68/M64 is delivered on tape and reel and this section describes the orientation of the LGA components and the tape used for its

The

packaging.

silabs.com | Building a more connected world. Rev. 0.1 | 11

Page 12

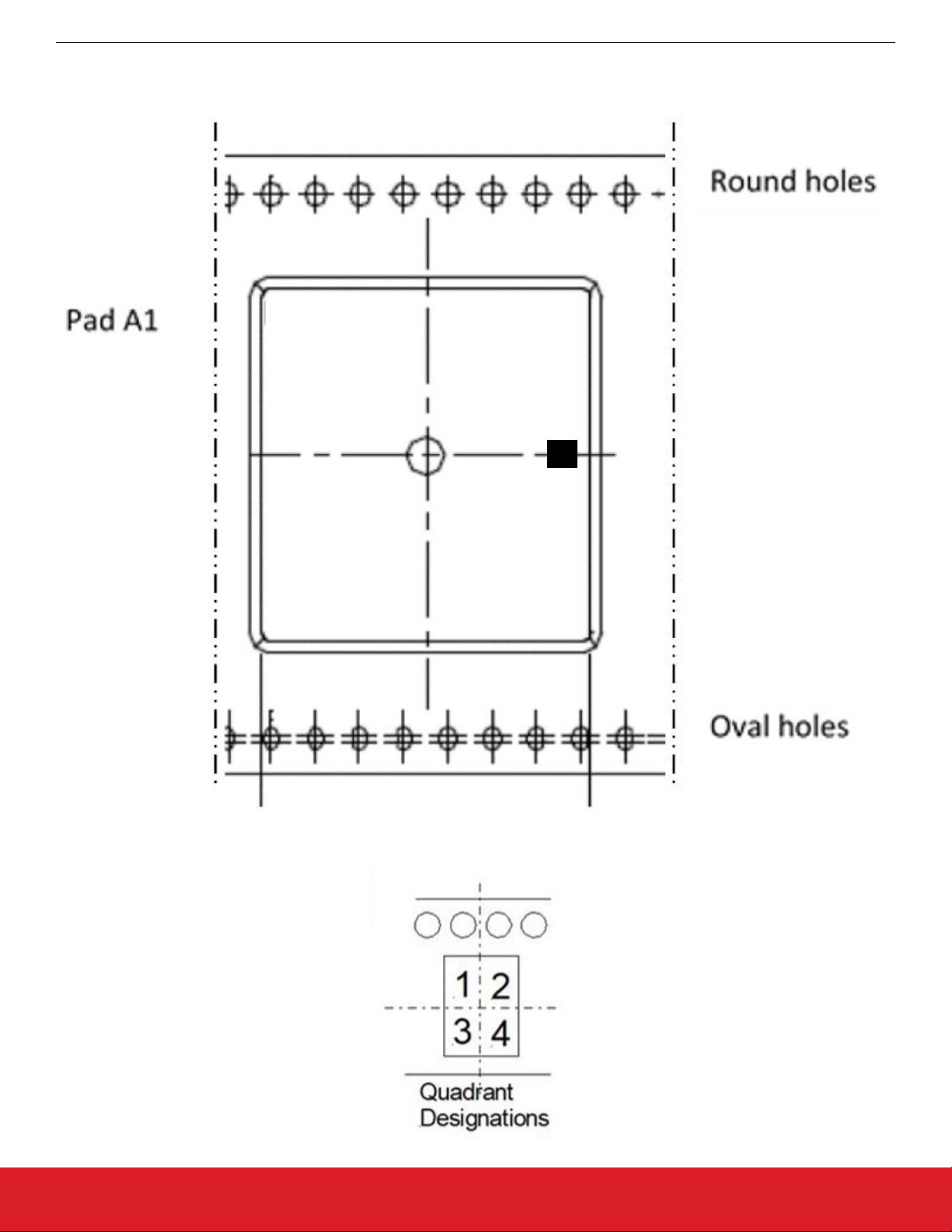

2.4.1 Pin 1 Orientation

Part orientation for tape and reel is illustrated below. The Pin 1 marker is between quadrants 3 and 4.

M68/M64 Module Data Sheet

Packaging

silabs.com | Building a more connected world. Rev. 0.1 | 12

Page 13

2.4.2 Tape and Reel Specification

M68/M64 Module Data Sheet

Packaging

Package Tape width

(mm)

Pitch

(mm)

Reel size

(mm)

Devices

per reel

LGA84 44 36 330 250

silabs.com | Building a more connected world. Rev. 0.1 | 13

Page 14

M68/M64 Module Data Sheet

LED Description

3. LED Description

The module has two on-board LEDs. See 19. Appendix 4: Troubleshooting LED Error Codes for more information. One LED is green

which shows the status of the boot sequence. This LED can be controlled by the user using firmware. The other LED is red and will light

up briefly at the start-up of the system. If the red LED keeps being lit, the system is not operating properly. This LED is not user controllable.

silabs.com | Building a more connected world. Rev. 0.1 | 14

Page 15

M68/M64 Module Data Sheet

Pin List

4. Pin List

The term “pin” used in the following table and throughout this document refers to one of the 84 pads on the bottom side of the module.

Pin 1 is located in the middle of the left side of the module when viewed from the top, see Figure 2.1 Dimensions for M68/M64 (unit:

mm) on page 10. The rest of the pins are enumerated counter-clockwise around the module from this pin.

The codes in the Type column below are: I for Input, O for Output, B for Bidirectional, P for Power, (PU) for Pull Up, and (PD) for Pull

Down.

Most pins have 3.3 Volts signaling levels. In the Description column pins not belonging to the 3.3 Volts region, e.g., those pins powered

by the External RGMII interface, are noted.

Pin Group Pin # Pin Name Type Description

RGMII 2 MIRQ0 I Ext. GbE PHY Interrupt

Powered by VCC_RGMII

3 MCKOUT1 O 25 MHz Clock.

3.3 Volts output.

Not suitable for clocking external

PHY.

Misc. 4 MRXOUT O RTC test / Active high power supply

wake-up output

5 MWAKE I (PD) Active high wake-up input

Clock 6 CPUCLK I External clock input (1.8 V level)

Misc. 7 MRSTOUT O Active low reset output

Time 8 TODIN I Time of day in

9 TODOUT O Time of day out

GPIO 10 PF2 B Port F GPIO

11 PF1 B

12 PF5 B

13 PF4 B

14 PF7 B

15 PF0 B

16 PF3/LOCK B

17 PF6 B

Analog 19-21, 23 ACH0-ACH2, ACH3 I Analog to Digital Converter multi-

plexer inputs

24, 25 AOUT0, AOUT1 O Digital to Analog Converter outputs

26 EXTREF I Optional external voltage reference

input for ADC

GPIO/Async.

Serial ports

silabs.com | Building a more connected world. Rev. 0.1 | 15

27-30 PJ0_UTX1, PJ1_URX1,

PJ2_URTS1, PJ3_UCTS1

31-34 PE0_UTX2, PE1_URX2,

PE2_URTS2, PE3_UCTS2

B Port J bits 0-3 / Serial port 1

B Port E bits 0-3 / Serial port 2

Page 16

Pin Group Pin # Pin Name Type Description

M68/M64 Module Data Sheet

Pin List

GPIO / SPI / Generic Serial

Interface

35-38 PE4_UTX3, PE5_URX3,

PE6_URTS3, PE7_UCTS3

B Port E bits 4-7 / Serial port 3

39 PB7_PC0 B See Pin descriptions

40 PD5_GSIIN B Port D bit 5 / SPI MISO / GSI input

41 PD7_GSICK B Port D bit 7 / SPI clock / GSI clock

42 PD6_GSIIO B Port D bit 6 / SPI MOSI / GSI bidir-

ectional

Ethernet 44,45 LED2,LED1 O RJ45 LED´s

46,47

48,49

50,51

52,53

MDI_A+,MDI_AMDI_B+,MDI_BMDI_C+,MDI_CMDI_D+,MDI_D-

B Ethernet, direct connection to mag-

netics

Debug 54 MSDIN I (PU) Serial debug data in

55 MSDOUT O Serial debug data out

56 MRESET I (PU) Active low reset input

57 MIRQOUT O Active low debug interrupt

58 MIRQ1 I Shared Interrupt

59 MCKOUT0 O Debug clock

62 WP I (PD) Active low flash write protect

Time & Frequency 66 FREQOUT_2 O Secondary Frequency out. Identical

signal to FREQOUT

67 FREQOUT O Frequency out

68 PPSIN I Pulse per second in

69 PPSOUT O Pulse per second out

RGMII

70 PB1_MDIO B Ext. GbE PHY Control (MDIO)

Powered by VCC_RGMII

All pins Powered

71 PB2_MDC O Ext. GbE PHY Control (MDC)

by VCC_RGMII

Supply

73,74 TXD0-TXD1 O TX Data

Powered by VCC_RGMII

75 TX_CTL O RGMII control

76 TX_CLK O TX Clock

77,78 TXD2-TXD3 O TX Data

79-80 RXD0-RXD1 I RX Data

81 RX_CTL I RGMII control

82 RX_CLK I RX Clock

83,84 RXD2-RXD3 I RX Data

silabs.com | Building a more connected world. Rev. 0.1 | 16

Page 17

Pin Group Pin # Pin Name Type Description

M68/M64 Module Data Sheet

Pin List

Supply 1,22,

GND P Ground

43,64

18 VBAT P 3V battery backup

60 VCC33 P 3.3V power supply

61 VCC25 P 2.5V power supply

Can be connected to 3.3 V power

supply at the cost of slightly higher

power consumption.

63 VCC18 P 1.8V power supply

65 VCC12 P 1.2V power supply

72 VCC_RGMII P RGMII power supply. Connect to

same voltage as the external PHY.

4.1 Pin Descriptions

Here are pin descriptions for designing with the module.

4.1.1 Analog Control of Oscillator

• (M68) AOUT1: Analog output used for controlling the frequency of the crystal oscillator. If an external voltage controlled frequency

source is used, this signal should be used to control it.

• (M64) AOUT1: Analog output used for controlling the frequency of the external voltage controlled frequency source.

• ACH0: Analog input used to measure the control voltage on external TCXO/OCXO.

• PB7: Connected together with PC0 on the module. Intended for use as SPI slave select, interconnection is for backwards compatibility. Only one of the GPIOs should be used to control this pin, the other should be tristated.

4.1.2 Write Protection

WP: This pin is connected to the write-protect pin of the on-board flash device. When pulled low or left open, the boot sector of the flash

is write-protected. Typically, only pulled high to do initial flash programming during manufacturing.

4.1.3 Serial Ports

There are three asynchronous serial ports. The identical ports are named COM1, COM2 and COM3 and are located on pins 24 – 38 of

the module.

The serial ports have hardware flow control using RTS/CTS, support several communication options with different combinations of parity, stop bits and character length, and are capable of baud rates from 300 bit/s up to 921,600 bits/s.

4.1.4 PF3/LOCK Pin

The PF3/LOCK pin can be configured to indicate that the PTP loop is locked. See the ptp2 lock command.

silabs.com | Building a more connected world. Rev. 0.1 | 17

Page 18

M68/M64 Module Data Sheet

4.2 Clocking

default the M68/M64 supports an external oscillator of 20 MHz. If another frequency is used, the PLL register (designated Configura-

By

tion Block Register 4, CRB4) needs to be changed.

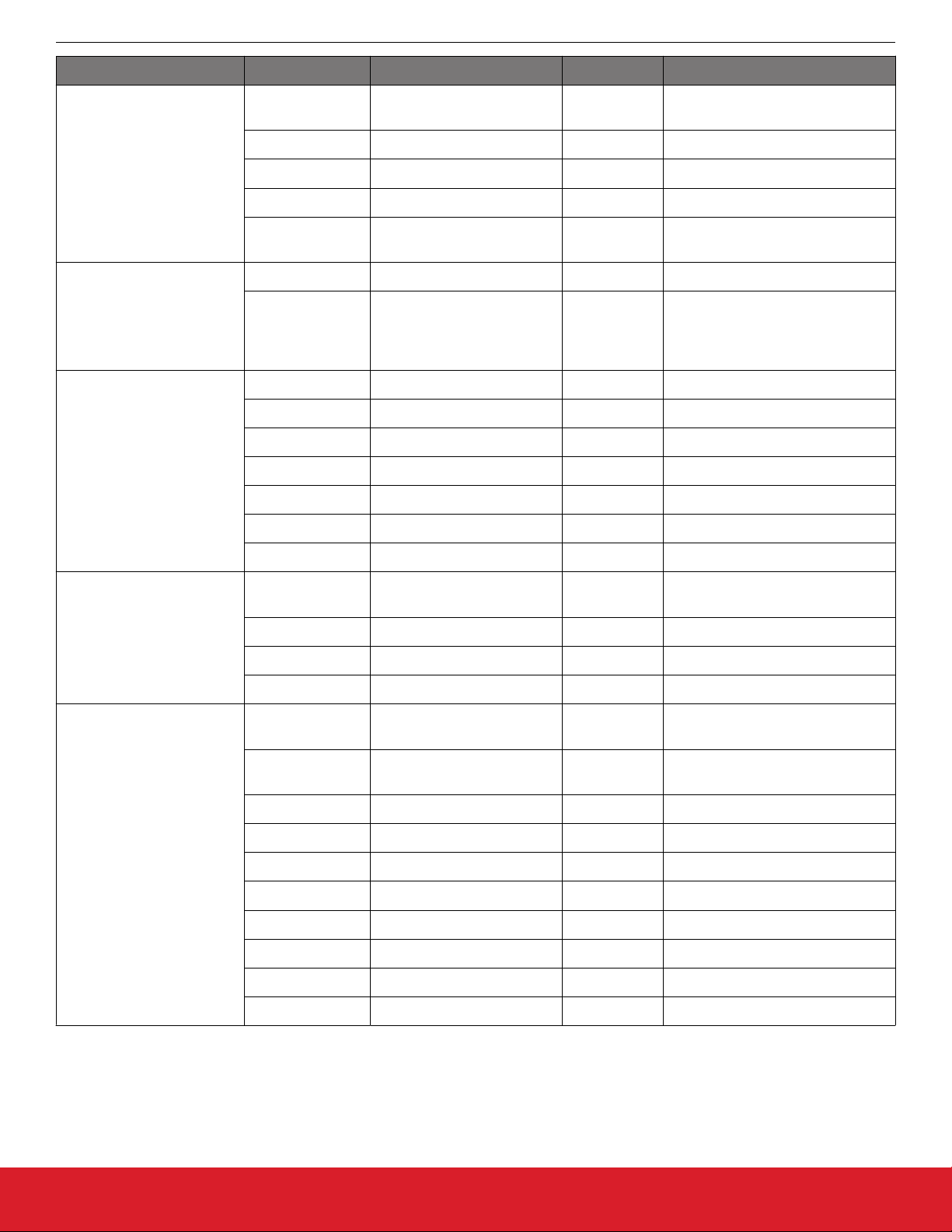

The CRB4 register has 3 fields, as shown in the following table:

CRB4 Bits Description Allowable Values

Bit 7 Pll_frange Should be set to 1

Pin List

Bits 6-2 pll_n - PLL frequency multiplication factor

0 – sets dividend to 32

dividend.

1 – sets dividend to 1

2 – sets dividend to 2

:

:

31 – sets dividend to 31

Bits 1-0 Pll_m – PLL frequency multiplication factor

0 – sets divisor to 5

divisor.

1 – sets divisor to 1

2 – sets divisor to 2

3 – sets divisor to 3

The output frequency is calculated as the external oscillator frequency x ( pll_n / pll_m). The resulting output frequency must be 150

MHz and the external oscillator frequency multiplied by 4 may not exceed 167 MHz.

The PLL register can be set using the “out crb4 0xNN” command in the system.ini file, and which will be run at powerup.

Example

CRB4 setting for 20 MHz external oscillator, “out crb4 0xbe”, which sets pll_n/pll_m to 15/2, and the resulting output frequency

of 150 MHz.

Example CRB4 setting for 10 MHz external oscillator, “out crb4 0xbd”, which sets pll_n/pll_m to 15/1, and the resulting output frequency

of 150 MHz.

One important characteristic to remember when using an external oscillator other than 20 MHz: The communication with the M68/M64

might be difficult before the proper PLL settings are in place. For example, when using an external 10 MHz oscillator, the serial port

communications would occur at 57600 baud, instead of 115,200.

NOTE: CPUCLK is a 1.8 V level pin. It must not be connected directly to a 3.3 V level oscillator output. A resistor or capacitive voltage

divider is enough to ensure that the voltage doesn’t exceed 1.8 V.

If the external oscillator has voltage control, it can be connected to the AOUT1 analog output. The control range of this pin is from 0.8 V

to 2 V. Fixed-frequency external oscillators can also be used, but then the FREQOUT frequency will not be syntonized.

4.3 Power Supply

4.3.1 Digital Power Supply

The module has five different power pins. Required power sources are 3.3, 1.8 and 1.2 Volts.

The use of an optional 2.5 V source will slightly decrease the power consumption. Otherwise the VCC25 pin must be connected to

VCC33.

The RGMII interface is powered by the user's system and the VCC_RGMII pin shall be connected to the systems power source. In the

case the RGMII interface is not intended to be used, the VCC_RGMII pin still must be connected to a power source. VCC33 is the best

choice.

silabs.com | Building a more connected world. Rev. 0.1 | 18

Page 19

M68/M64 Module Data Sheet

Pin List

4.4 Time I/O

4.4.1 Reference Time Input

consists of signals PPSIN and TODIN, and is intended for connection to an external time source like a GNSS receiver or similar. If

It

one or both signals are not used, they can be left unconnected.

PPSIN expects a pulse-per-second signal with LVTTL levels. Rising edge should be on second boundary, the pulse width is not critical.

TODIN should receive time-of-day information, for example in NMEA 0183 format. The levels must be LVTTL and polarity will be detected. The current FW supports 4800 or 9600 baud 8N1 on the TODIN pin.

4.4.2 Precision Time Output

The interface consists of signals PPSOUT, TODOUT, FREQOUT and SYNTFREQ.

PPSOUT outputs a pulse-per-second signal with LVTTL levels. Pulse width, frequency, phase and polarity of this signal can be controlled by software. For more information, see 18. Appendix 3: PTP Command Reference.

TODOUT outputs time-of-day at LVTTL levels, for example in NMEA 0183 format. Baudrate can be set to 4800 or 9600 baud 8N1. For

more information, see 18. Appendix 3: PTP Command Reference.

(M64) FREQOUT outputs a syntonized frequency in the MHz range and at LVTTL levels. The frequency is software selectable

5/10/20/25 MHz. The frequency will only be syntonized (kept in phase with PTP or GNSS time) if the external oscillator is voltage controlled by analog output AOUT1 from the module.

(M68) FREQOUT outputs a syntonized frequency in the MHz range and at LVTTL levels. The frequency is software selectable

5/10/20/25 MHz. The frequency will only be syntonized (kept in phase with PTP or GNSS time) if the internal crystal oscillator is used or

if the external oscillator is voltage controlled by analog output AOUT1 from the module.

The SYNTFREQ is the same as the FREQOUT.

silabs.com | Building a more connected world. Rev. 0.1 | 19

Page 20

M68/M64 Module Data Sheet

5. Specifications

5.1 Metrics

Metric Value

Dimensions 29.2 x 29.2 x 3.3 mm

Weight 3.0 g

Operating temperature -40°C – +85°C, ambient

Storage temperature -40 – +150 °C

5.2 Absolute Maximum Ratings

Parameter Symbol Min Max

Specifications

Supply voltage 3.3 V V

Supply voltage 2.5 V V

Supply voltage VCC_RGMII V

Supply voltage 1.8 V V

Supply voltage 1.2 V V

RTC battery backup supply V

I/O voltage (CPUCLK pin) V

I/O voltage (all other pins) V

ESD tolerance (Ethernet differential pairs, human body model) V

ESD tolerance (all other pins, human body model) V

CC33

CC25

CC_RGMII

CC18

CC12

BAT

IO18

IO33

ESDE

ESD

-0.3 V 3.6 V

-0.3 V 3.6 V

-0.3 V 3.6 V

-0.3 V 2.5 V

-0.3 V 1.32 V

-0.3 V 4.0 V

-0.3 V 2.16 V

-0.3 V 4.0 V

6 kV

2 kV

Permanent device damage may occur if the absolute maximum ratings are exceeded. These are stress ratings only, and functional

operation should be restricted to within the conditions detailed in the next section.

Exposure to absolute maximum rating conditions for extended periods may affect the device’s reliability.

5.3 Recommended Operating Conditions

Parameter Symbol Min Typ Max

Supply voltage 3.3 V V

Supply voltage 2.5 V V

Supply voltage VCC_RGMII V

CC33

CC25

CC_RGMII

3.15 V 3.3 V 3.45 V

2.38 V 2.5 V 2.62 V

3.15 V 3.3 V 3.45 V

2.38 V 2.5 V 2.62 V

1.71 V 1.8 V 1.89 V

1.43 V 1.5 V 1.57 V

1.14 V 1.2 V 1.26 V

Supply voltage 1.8 V V

Supply voltage 1.2 V V

RTC battery backup supply V

I/O voltage (CPUCLK pin) V

silabs.com | Building a more connected world. Rev. 0.1 | 20

CC18

CC12

BAT

IO18

1.71 V 1.8 V 1.89 V

1.14 V 1.2 V 1.26 V

2.7 V 3.63 V

0 V 1.98 V

Page 21

M68/M64 Module Data Sheet

Specifications

Parameter Symbol Min Typ Max

I/O voltage (RGMII pins) V

IO_RGMII

-0.3 V V

CC_RGMII

V

CC_RGMII

0.5V

I/O voltage (all other pins) V

IO33

0 V 3.63 V

5.4 DC Electrical Characteristics

Parameter Symbol Min Typ Max

Power consumption 1060 mW

Supply current I

RTC backup current (V

= 3.0 V,

BAT

CCxx

I

BAT

(see table below)

5.5 µA

VCC = 0 V)

Input low voltage (except CPUCLK) V

Input high voltage (except CPUCLK) V

IL

IH

2.0 V

0.8 V

Input/tristate leakage current |II| 1 µA 10 µA

Output low voltage (|IOL| = max) V

Output high voltage (|IOH| = max) V

OL

OH

2.4 V

0.4 V

Output drive current (GPIO pins) |IOL|,|IOH| 2/8 mA

+

Supply currents per voltage for different choice of host RGMII voltages. These are preliminary values for a gigabit speed connected

module:

1.8 V RGMII option

V mA

1.2 138

1.8 115

2.5 15

3.3 200

Note: The final power consumption will depend on how the user designs his PCB. The numbers given in the table are maximum values

for

a well-designed board with a 1.8 V feed of the external RGMII port. Increasing this to 3.3 V is optional, but this will increase the total

power consumption.

Note: When planning to use the module in an existing design, the module contains a network side PHY. The existing PHY must be

removed, also when calculating power consumption as the PHY consumes the majority of the total.

5.5 AC Electrical Characteristics

Parameter Symbol Min Typ Max

(M68) On-board main oscillator frequency f

On-board RTC oscillator frequency f

OSC

RTC

20 MHz

32768 Hz

Core & SDRAM frequency (must be typical value for Ether-

f

CORE

20 MHz 150 MHz 167 MHz

net operation)

External oscillator frequency on CPUCLK f

silabs.com | Building a more connected world. Rev. 0.1 | 21

EXT

5 MHz 41.7 MHz

Page 22

M68/M64 Module Data Sheet

PCB Design Considerations

6. PCB Design Considerations

This chapter should be read before starting a new design.

6.1 Land Pattern

See section 2.2 Recommended Land Pattern and Accepted Land Pattern for further information.

6.2 Power

The module has five connections for five different voltages. Three of those voltages are mandatory, two power pins can be joined to the

cost of slightly increased power dissipation. One voltage is used for an optional PHY. The module also comprises four connections to

GND. An optional backup battery, for the RTC, can be connected to the module.

6.2.1 Required Voltage

For Maximum and Operating Voltage Levels see sections 5.2 Absolute Maximum Ratings and 5.3 Recommended Operating Condi-

tions.

Maximum Supply Currents during operation are listed in 5.4 DC Electrical Characteristics. During start-up, the current consumption can

momentarily be higher.

Pin Name Voltage Description

VCC33 3.3 V This voltage is used for driving signals on the module and for the /O’s of

the module.

VCC25 2.5 V or 3.3 V If connected to 3.3 V there will be slightly higher power dissipation.

VCC18 1.8 V Used for the PHY located on the module.

VCC12 1.2 V Power for the devices on the module.

VCC_RGMII 1.2 V to 3.3 V If an optional external PHY is used this pin must be connected to the same

voltage source as the PHY’s RGMII interface. The pin must not be left unconnected. If no external PHY used this pin should be connected to

VCC33.

This power pin is used only to drive the external RGMII interface.

VBAT 3 V If backup is required, this pin shall be connected to a 3 V lithium coin cell

battery. No current is drawn from the battery when power is available on

pin VCC33.

silabs.com | Building a more connected world. Rev. 0.1 | 22

Page 23

M68/M64 Module Data Sheet

PCB Design Considerations

6.2.2 Decoupling Capacitors

is important that the selected decoupling capacitors are specified correctly, are placed close to the module and, to minimize induc-

It

tance, are connected with as wide tracks as possible. The use of power planes is of course the ideal solution.

Decoupling capacitors on the module itself are placed very close to the on-module circuits. Those capacitors will provide for the immediate current requirement. Bulk capacitance must be placed external to the module. All 4.7µF capacitors mentioned below shall be

placed as close as possible to the corresponding module connection. The larger capacitors, 100µF, can be placed further away from

the module.

Pin Name Decoupling Capacitors

VCC33 Connect one 4.7 µF and one 100 µF capacitor to this pin.

VCC25 Connect one 4.7 µF and one 100 µF capacitor to this pin.

VCC18 Connect one 4.7 µF and one 100 µF capacitor to this pin.

VCC12 Connect two 4.7 µF capacitors to this pin.

VCC_RGMII Connect one 4.7 µF and one 100 µF capacitor to this pin.

The decoupling capacitors must have the following specifications:

Ceramic X7R or X5R, 6.3 V.

•

• 100 µF: max size 1210, ESLmax 5nH, 10 mOhm < ESR <60 mOhm.

• 4.7 µF: max size 0805, ESLmax 2nH, 10 mOhm < ESR <60 mOhm.

6.3 Clock Signal MCLKOUT1

Clock signals must be treated with great care, with signal integrity in mind. For this reason, MCLKOUT1 has a series termination resistor placed on the module, no further termination is required. The trace from the module must not have any stubs. If more than one load,

those loads should preferably be placed close to each other. The trace shall preferably have 50-65 ohm line impedance.

This clock signal was intended to drive an external PHY. However, it has been shown that it is not suited for this purpose due to jitter.

We suggest using an external 25 MHz oscillator to drive the external PHY instead.

6.4 Ethernet Interface

The four pairs of differential signals driving the magnetics are placed close to each other on one side of the module. The length of the

traces for each pair shall be as equal as possible and so should the length of the four pairs.

Drivers for the LEDs, signaling connection status, are of Open Collector type. A resistor of nominally 470 ohms shall be placed between

VCC33 and the anode side of the LEDs.

6.4.1 Magnetics

The following is a list of magnetics that can be used with the module. The list is not complete, and all magnetics listed are not tested

together with the module. All listed magnetics are single port RJ-45 connectors with integrated magnetics of 3 wire choke type.

Manufacturer Part Number

Link-PP Electronics LPJK2065AONL

LPJK0036AINL

Pulse Electronics JK0-0136NL

JK0654219

Foxconn JFM38010-01S1-4F

Belfuse 0813-1X1Y-43

SI61021F

silabs.com | Building a more connected world. Rev. 0.1 | 23

Page 24

M68/M64 Module Data Sheet

PCB Design Considerations

6.5 RGMII Interface

interface is clocked at 125 MHz, when running GbE. Needless to say great care must be taken during design. Connections to the

This

two channels, TX and RX, are adjacent on the module, having respectively clock in the center of the connections.

RGMII clocking is source synchronous, what is the RX clock is generated by the PHY and the TX clock by the module. All traces within

a channel must have the same length. Delay of the clock, sampling in the middle of the data-eye, is taken care of by the external PHY

and the RGMII interface on the module.

silabs.com | Building a more connected world. Rev. 0.1 | 24

Page 25

M68/M64 Module Data Sheet

Application Software

7. Application Software

The M64 and M68 are quite similar. In the CLI commands that follow, the M68 commands are given. The full details of a command are

available via help commands in the CLI.

For the M64 the parameter, "port_number" is always 1. For the M68, "port_number" is either 1 or 2, the default is 1.

For the M64 the parameter, "iface" is always enet0. For the M68, it is either enet0 or enet1.

7.1 System Access

See the Quick Start Guide for setting up communication to the module in a P60 Evaluation Kit. To logon to the system the username is

“root”, with password “root” as the initial credentials.

You can change them later with the passwd command and add or delete users in the database, see the passwd.ini section.

On entering the system, you will see a prompt and an identifier for the system. The interface is very similar to UNIX.

7.2 System Files

The system directory A:/system contains firmware files and a number of system initialization and configuration files. These are listed in

the Appendix 1 for reference. The files most applications should check and modify are the system.ini and startup.ini to setup the module

in its environment and give the PTP engine the parameters for the synchronization scheme.

7.3 Module Shell Environment

The shell, called ISH, is responsible for the high-level system initialization, for execution of various servers and for providing a UNIX-like

command interface.

7.3.1 High-Level Initialization

The shell startup code completes initialization and configuration of the system performing the following tasks:

• Initializes the serial port interface

• Registers stdout and stderr functions

• Reads the Hardware Identification String from the flash memory

• Reads and processes a shell configuration file ish.ini.

• Reads and processes a system configuration file system.ini

• Initializes and starts a Serial server

• Configures a hostname

• Initializes and configures TCP/IP stack software

• Starts FTP and Telnet servers

• Sets the Time Zone and Daylight Saving

• Reads and executes startup file startup.ini

7.3.2 System Commands

The shell includes Serial server, Telnet server and FTP server. The shell starts them automatically during startup, if specified in the

system configuration file. Otherwise they can be started and stopped manually using startserver and stopserver commands.

7.3.3 Communication Servers

The shell includes Serial server, Telnet server and FTP server. The shell starts them automatically during startup, if specified in the

system configuration file. Otherwise they can be started and stopped manually using startserver and stopserver commands.

7.3.3.1 Serial Server CLI

The Serial server provides the command-line user interface over a serial channel. The serial port number and port parameters can be

specified though environment variables.

silabs.com | Building a more connected world. Rev. 0.1 | 25

Page 26

M68/M64 Module Data Sheet

Application Software

7.3.3.2 Telnet Server CLI

Telnet server provides the command-line user interface over a TCP/IP communication channel. The TCP port number and the

The

server priority can be specified though the environment variable.

7.3.3.3 SSH Server

The SSH server is not started by default but has to be started manually using the command:

startserver –d

Note: For the current implementation, initialization takes about 30 seconds and establishing the connection about another 60 seconds.

7.3.3.4 FTP Server

The FTP server provides a remote access to the local file system. It supports both get and put operations. The number of simultaneous

connections and the server priority can be specified through environment variables.

7.3.3.5 JSON

The command interface (default is COM3) can be used in either CLI/HMI command mode or JSON mode. The JSON mode is turned on

or off with the following commands:

ptp2 engine json on

ptp2 engine json off

See 12. JSON Usage

for more details.

7.4 Passthrough

The passthrough mode allows a system with two Ethernet interfaces to act as a "synchronization gateway" for non-PTP hosts.

On its primary Ethernet port such "gateway" is connected to a network which transports data and PTP synchronization. To its secondary Ethernet port, the non-PTP system is connected. The "gateway" participates in PTP activity acting as a PTP slave and synchronizing its local clock. The PTP traffic is filtered out while non-PTP data is passed through to the host along with PPS/TOD/FREQ-out synchronization signals.

The command to turn on and off pass-through is:

ifconfig frwd [on|off]

On the M68 the secondary (host-side), Ethernet is available for user or applications such as a general-purpose network interface.

On M64, the secondary (host-side), Ethernet interface is not available for user or applications as a general-purpose network interface, it

is used only for pass-through and it is completely transparent from either host or network side.

silabs.com | Building a more connected world. Rev. 0.1 | 26

Page 27

M68/M64 Module Data Sheet

Application Software

7.5 VLAN

M68/M64 supports VLAN tagging. If VLAN is used in combination with PTP, the VLAN needs to be set before the PTP engine is

The

started.

To enable VLAN on the interface, use the command:

ifconfig [iface] vlan [parameters]

where [iface] is the interface name. If not given, 'enet0' will be used.

[parameters] can be

off - send and receive untagged frames only

none - send untagged frames, receive untagged and priority tagged frames

0 [prio_code] - send priority-tagged frames, receive untagged and priority tagged frames

<vlan_id> [prio_code] - send and receive vlan-tagged frames only

For example:

ifconfig vlan 1588 0

To disable VLAN on the interface, use the command:

ifconfig enet1 vlan off

7.6 MDIO

The M68/M64 supports the possibility to control and monitor equipment such as a PHY connected over MDIO. To enable MDIO mode,

use the command

ifconfig mdio

This will disable all other access to the MDIO registers to avoid conflicting writes to the page register. To then read from MDIO registers

use the command

<reg>

And to write to a MDIO register in the exclusive MDIO mode use

<reg> <value>

To exit from the exclusive MDIO mode, type “q”.

For example, to enter MDIO mode and write 0x4885 to register 18 on page 3 (reg 22 is page register):

A:/root> ifconfig mdio

Enter exclusive MDIO mode on enet0

22 3

22: 0x0003

18

18: 0x4b85

18 0x4885

18: 0x4885

q

Quit exclusive MDIO mode on enet0

A:/root>

It is also possible to read or write directly to a MDIO register without entering the exclusive mode:

ifconfig mdio <reg> <value>

but beware any page register settings.

simplify for the user, some common operations on the PHY has been defined as specific commands: to manage link speed and

To

duplex, to reset the PHY and to manage SyncE master/slave behavior.

silabs.com | Building a more connected world. Rev. 0.1 | 27

Page 28

7.7 Link Speed

The PHY link speed and duplex can be controlled by the command

ifconfig [iface] link [parameters]

where [iface] is the interface name. If not given, 'enet0' will be used.

M68/M64 Module Data Sheet

Application Software

[parameters]

can be one of the following modes: 1000F, 1000H, 100F, 100H, 10F, 10H which disables autonegotiation and force the

interface into the desired speed and duplex (F – full, H – half) or auto [mode_mask] which will enable autonegotiation and optionally set

advertised modes. If mode_mask is not given all supported modes will be advertised, i.e. 1000F|1000H|100F|100H|10F|10H

For example, to set 100Mb/s Full duplex:

ifconfig link 100F

or set interface 0 to autonegotiation with only 1000Mb/s and 100Mb/s full duplex supported.

Ifconfig enet0 link auto 1000F|100F

7.8 PHY Reset

It is possible to reset the PHY with the following command:

ifconfig [iface] reset [options]

Where [iface] is interface name. If not given, 'enet0' will be used.

[options] can be either sw, noinit or not given at all.

If no option is given, a HW reset is performed, i.e. the reset pin of the PHY is pulled after which initialization is done.

If the option “noinit” is given also a HW reset is performed, but no initialization of the PHY is performed. This can be used when PHY

needs to be configured manually using MDIO.

The option “sw” sets the reset bit in the MDIO registers, performing a SW reset. This is of course only relevant if the PHY's MDIO interface lines are connected.

For example, to perform a HW reset of the PHY:

ifconfig reset

7.9 SyncE

For PHY devices supporting SyncE it is possible to define the direction of frequency on a link. This is only valid for 1000Base-T interfaces.

ifconfig [iface] synce [parameters]

Where [iface] is the interface name. If not given, 'enet0' will be used.

[parameters] can be

• master|slave which will disable autonegotiation and force the interface into either master or slave mode or

• auto master|slave which will enable autonegotiation with either master or slave preference

If no parameter is given, current resolved state will be reported.

For example, setting the module to be preferred SyncE master:

ifconfig synce auto master

silabs.com | Building a more connected world. Rev. 0.1 | 28

Page 29

7.10 SFP

There is support for managing an SFP connected to the specified network interface.

ifconfig [iface] sfp [parameters]

Where [iface] is the interface name. If not given, 'enet0' will be used.

[parameters] can be

raw, which prints SFP information in raw hex format

state, which shows state of LOS, enable, presence and fault

enable will enable the SFP transmitter

disable will disable the SFP transmitter

mdio <reg> will perform single read from MDIO register in SFP PHY

mdio <reg> <value> will perform single write to MDIO register in SFP PHY

If no parameter is given, prints formatted SFP information.

M68/M64 Module Data Sheet

Application Software

silabs.com | Building a more connected world. Rev. 0.1 | 29

Page 30

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

8. IEEE 1588/PTP Engine

The M64 and M68 are quite similar. In the CLI commands that follow, the M68 commands are given. The full details of a command are

available via help commands in the CLI.

For the M64 the parameter, "port_number" is always 1. For the M68, "port_number" is either 1 or 2, the default is 1.

For the M64 the parameter, "iface" is always enet0. For the M68, it is either enet0 or enet1.

8.1 General Features

The IEEE 1588/PTP Engine (PTP Engine) has the following features:

• Implements an ordinary clock in accordance with IEEE Std 1588™-2008

• M68 implements boundary clock in accordance with IEEE Std 1588™-2008

• Fully flexible to comply with Default Telecom and Power Profiles

• Supports both GNSS and PTP as the primary and backup time source

• Built-in SNTP server

• Supports 5 different operational modes

• Provides the command-line interface (can be configured and monitored either locally via Terminal or over the network via Telnet or

SSL)

• Supports PTP Management interface (can be configured and monitored over the network from a PTP Management station)

• Provides a rich set of APIs

• Uses high-precision hardware timestamp engine

• Can be partially customized by the customer

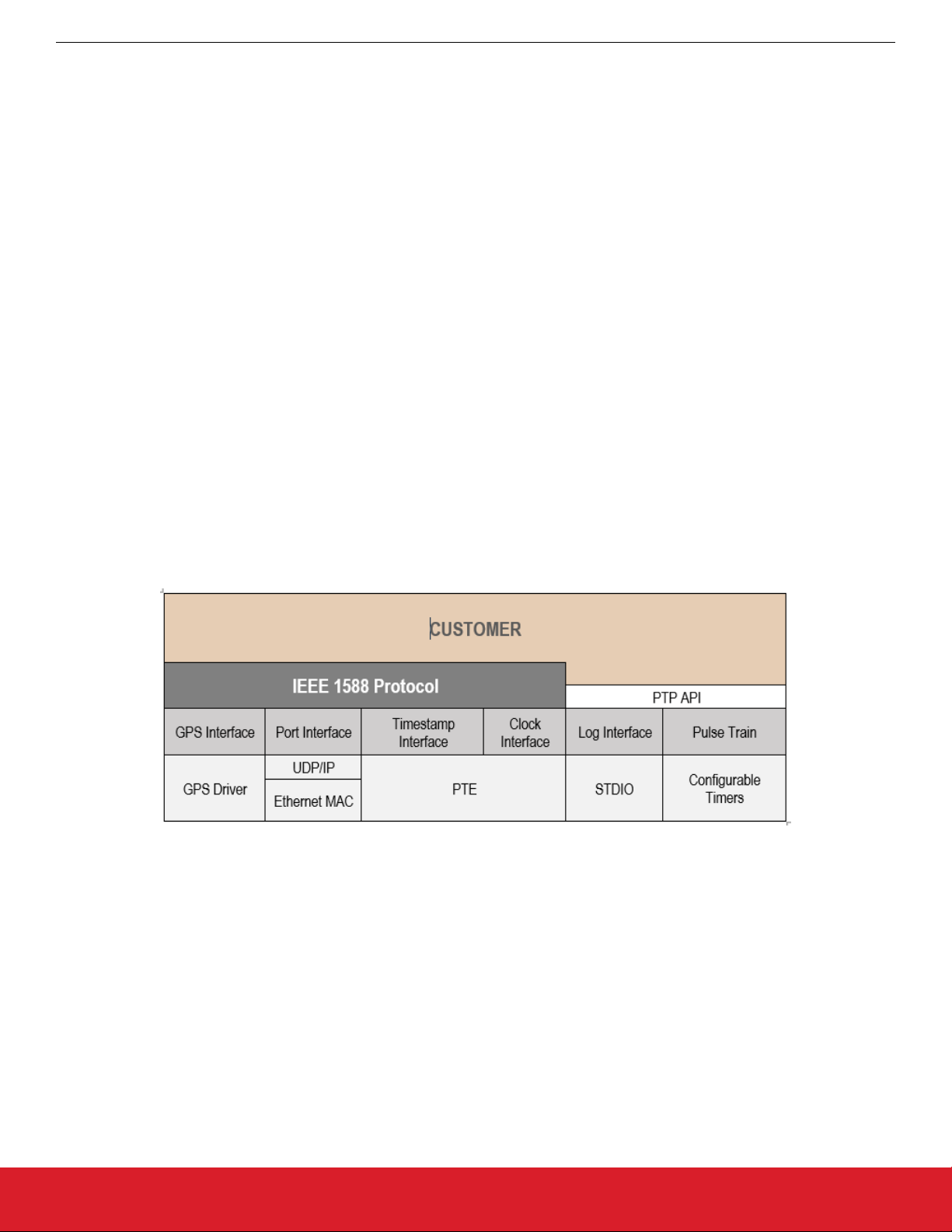

8.2 PTP Software Implementation

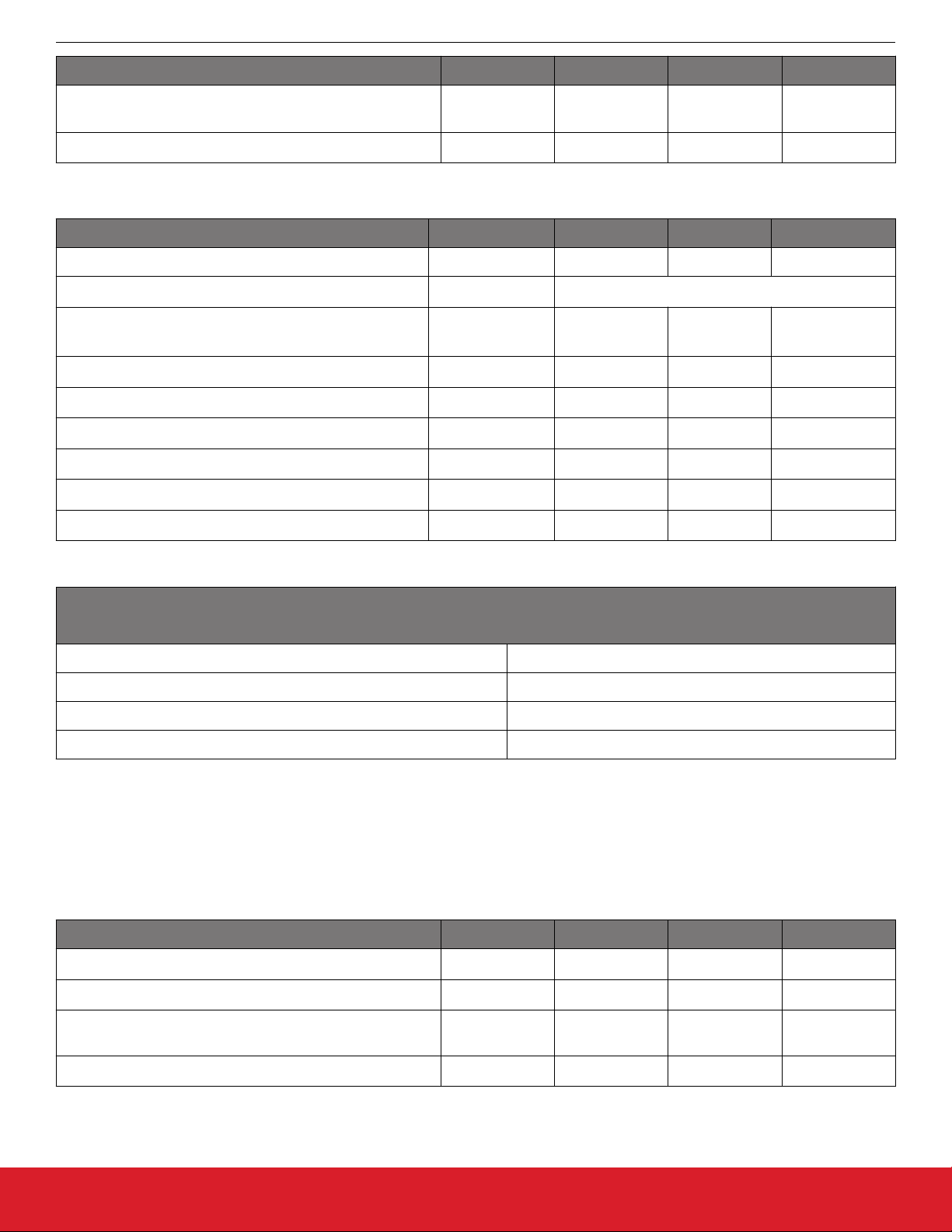

PTP software is divided into three layers; Protocol Layer, OS Abstraction Layer and the OS Layer.

Figure 8.1. PTP Layers

8.2.1 Protocol Layer

protocol layer contains the PTP engine which is implemented according to the IEEE 1588-2008 standard. The protocol engine en-

The

capsulates a number of functions necessary to run the PTP clock. Among those functions are best master clock algorithm, PTP message handling and maintaining of PTP clock data sets.

8.2.2 OS Abstraction Layer

The OS abstraction layer implements a number of interfaces between the protocol engine and the underlying operating system.

8.2.2.1 GNSS Interface

The GNSS interface contains functionality for GNSS synchronization. This interface is used when running the grandmaster clock.

silabs.com | Building a more connected world. Rev. 0.1 | 30

Page 31

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

8.2.2.2 PTP Interface

interface PTP encapsulates the functions of the PTP environment and therefore only provides the functions that must be callable

The

from the outside of the protocol engine. PTP is a wrapper of PTP environment – it represents the API of the PTP protocol.

8.2.2.3 Port Interface

The port interface is used to send and receive PTP messages. It makes use of the functions the OS provides (e.g. sockets) in order to

communicate over the network.

8.2.2.4 Timestamp Interface

The time stamp interface is used to pass time stamps for Sync and Delay_Req messages to the PTP protocol engine. It also implements the connection which is used to read the timestamps from the timestamp unit.

8.2.2.5 Clock Interface

The clock interface provides functions to read, write and configure the local clock. The clock interface uses the clock driver functions

(set time, get time, drift compensation etc.) in order to access the clock.

8.2.2.6 Log Interface

Through the log interface the protocol engine can output log information. The log provides human readable information that shows current settings and current state of the protocol engine. This log information can be monitored either via a serial port or TCP/IP.

Log output is initiated and controlled though the Human Machine Interface.

8.3 GNSS Driver

The GNSS driver consists of a PPS Receiver unit and a GNSS Time Receiver.

When a PPS signal from the attached GNSS unit is received by the GNSS Receiver, the signal is timestamped by the PTP timestamp

unit. The timestamp is then delivered to the GNSS Interface where it is put in an event queue for processing by the protocol stack.

The GNSS Time Receiver receives time of day information from the GNSS unit. This time information specifies the date and time of the

PPS signals.

8.4 AccuTime Software

AccuTime software consists of configurable timers and MAC hardware with timestamp capabilities.

The MAC hardware reports timestamps for all incoming or outgoing Ethernet frames.

The PTP engine receives and sends PTP messages through the TCP/IP stack using a socket interface. It accesses the timestamp list

to get timestamps for these messages.

The MAC hardware is augmented with input timestampers and output coincidence triggers to allow it to set timestamps at input events

and cause output events at certain times.

8.5 PTP API

The PTP engine provides a rich set of C API calls that the application programmer can use to start and control the engine. This C API is

only open to customers which have the Developer IDE software installed.

silabs.com | Building a more connected world. Rev. 0.1 | 31

Page 32

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

8.5.1 Starting/Stopping the PTP Engine

PTP engine runs as a separate thread and there can only be one instance of the PTP engine running at one time. An application

The

can start the PTP engine by a call to the function PTP2_Start().

As the parameter to that function, a pointer to the configuration structure is passed. In this structure one can specify whether a pulsetrain needs to be enabled and a mode for the PTP engine operations (see detail below).

The PTP engine can also be automatically started at boot time by the Shell, ISH. For more information about ISH see the ISH documentation in the Profile Help.

To stop the PTP engine, use the PTP2_Stop() function or the corresponding shell command.

8.5.2 Pulse Train

A pulse-train can be generated by the PTP engine. The pulse-train can be continuous or a specified number of pulses can be generated. The user can also specify the width and period of the pulse-train as well as the starting time for the pulse-train.

silabs.com | Building a more connected world. Rev. 0.1 | 32

Page 33

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

8.5.3 Human Machine Interface

PTP engine has a command interface that the user can use to manually change settings and issue different printouts from the

The

engine’s current state. The Human Machine Interface (HMI) commands can be entered either manually (from a Terminal or Telnet console) or issued by the application with the PTP2_hmi() function.

To find exact syntax of each command simply type (or send from a program) “h” – stands for Help.

When using the HMI commands, you can type either the command word or use the letter(s) in the parentheses before the command.

For example, to disable unicast negotiation, type unicast n off or type u n off. To see a list of the command set, first make sure

you are in HMI mode by typing ptp2 hmi at the prompt. Next, type help and the commands display.

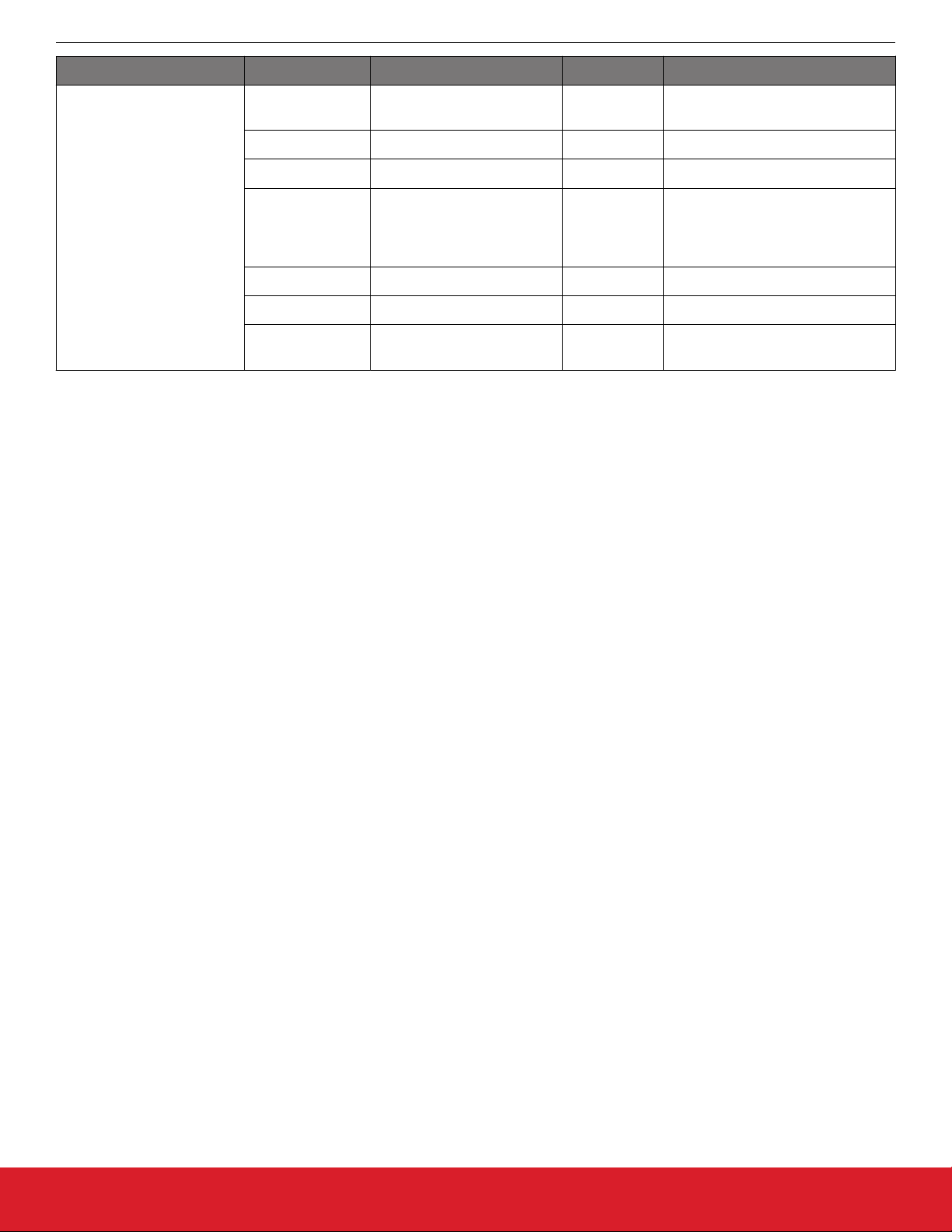

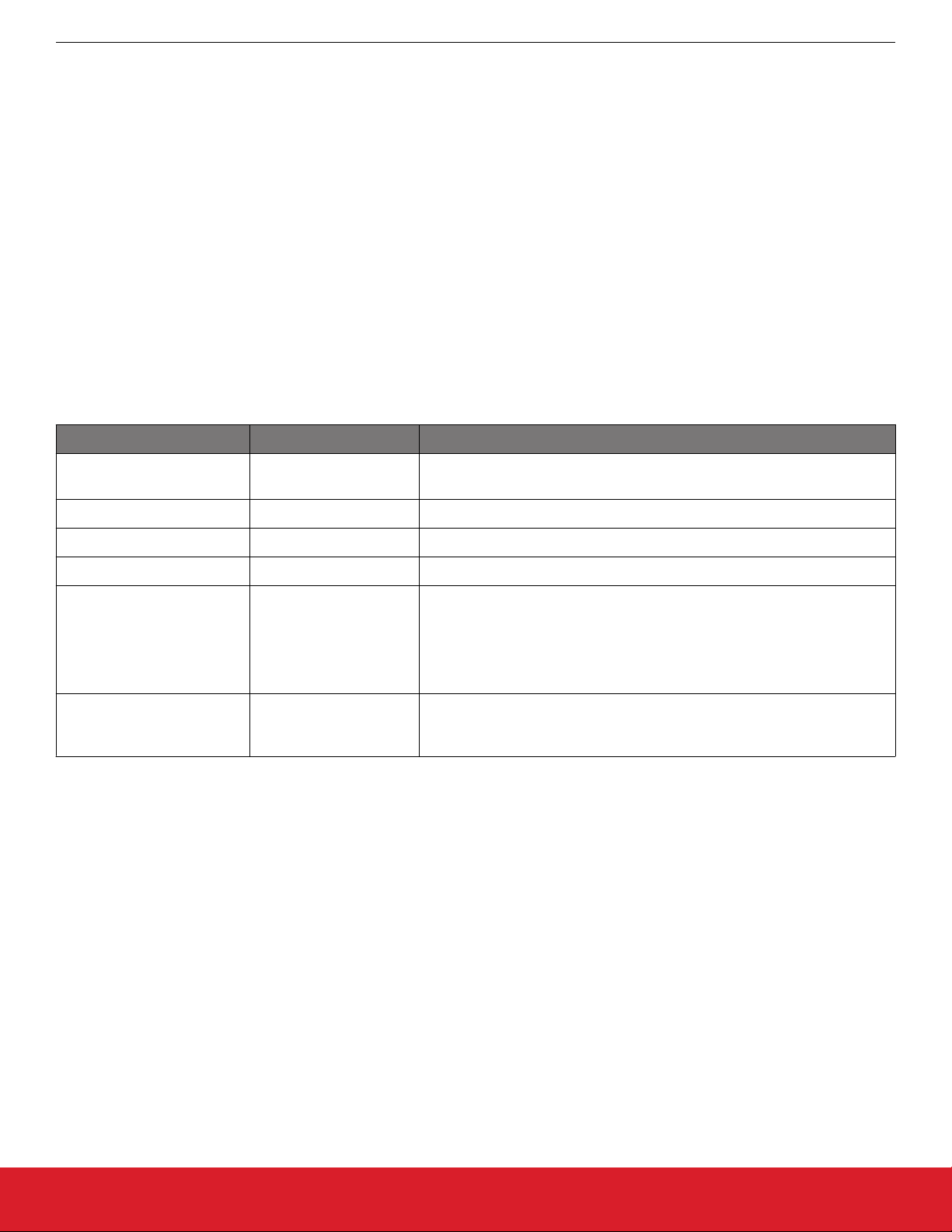

The following table shows the structure of the commands

Command Example Results

command unicast or u Prints a list of subcommands.

Command subcommand unicast n or u n Prints current value of associated parameter.

Command subcommand value

unicast n off or u n off

Sets associated parameter to a different value.

The next series of tables describe each command and its associated subcommands and values. The last table shows command examples.

Clock Command Subcommand & Parameters Description

(c)clock (i)info Print clock description.

(u)user <string> Change user description.

(f)profile <default|g8265|g8275.1|

g8275.2|power [v2]>

(m)mode <oc|bc> Change clock type mode (M68 only)

(t)twostep <on|off> Change two-step mode.

(q)quality <class> <accuracy>

<variance>

Change clock profile.

Change clock quality.

(p)priority 1|2 <value> Change priority 1 or 2.

(d)domain <number> Change domain number.

(s)slaveonly <on|off> Change slave-only mode.

silabs.com | Building a more connected world. Rev. 0.1 | 33

Page 34

Port Command Subcommand & Parameters Description

(p)port <port_number> (s)state Print port state.

(m)mechanism <e2e|p2p|disable> Change or disable delay mechanism.

(p)protocol <udp|eth|udp6> Change network protocol.

(c)compatibility <on|off|auto [timeout]> Change V1 HW compatibility mode.

(a)asymmetry <value> Change delay asymmetry.

(si)sync <value> Change log sync interval.

(di)delay <value> Change min log delay request interval.

(pi)pdelay <value> Change min log pdelay request interval.

(ai)announce <value> Change log announce interval.

(rt)receipt <value> Change the announce receipt timeout.

(u)unicast <master|slave|both|disable> Enable/disable unicast operation for the

master and slave clocks.

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

(f)profile <default|g8265|g8275.1|g8275.2|power

[v2]>

(d)dscp <value> Set DSCP in PTP messages.

Change PTP profile.

Unicast Command Subcommand & Parameters Description

(u)unicast <port_number> (s)status Print port unicast information.

(n)negotiation <on|off> Enable/disable unicast negotiation.

node (m)master [add|del] <address> [clock_id]

<priority> <si|x> <di|x> [domain]

node (s)slave [add|del] <address> <ai|x> <si|

x> <di|x>

(q)query <interval> Change unicast discovery query interval.

(d)duration <value> Change unicast transmission duration.

(t)timeout <value> Change cancel acknowledge receipt time-

Change unicast master discovery table.

Change static unicast slave table.

out.

(l)limit <value> Change total unicast messages rate limit.

(f)filter (m)master [add|del] <address|*>

[clock_id] [x | [priority] [si] [di|x]]

(f)filter (s)slave [add|del] <address|*>

[clock_id] [x | [ai] [si] [di|x]

Change acceptable unicast master table.

Change acceptable unicast slave table.

Power Profile Command Subcommand & Parameters Description

(pw)power (g)gmid <0..65535> Change grandmaster ID.

(i)inacc <grandmaster> <network> Change grandmaster and network time in-

accuracy.

G.8275 Profile Command Subcommand & Parameters Description

(g2)g8275 <port_number> (p)priority <1..255> Change clock local priority.

(s)steps <1..255> Change max steps removed.

<port_number> (m)masteronly <on|off> Change port master-only attribute

silabs.com | Building a more connected world. Rev. 0.1 | 34

Page 35

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

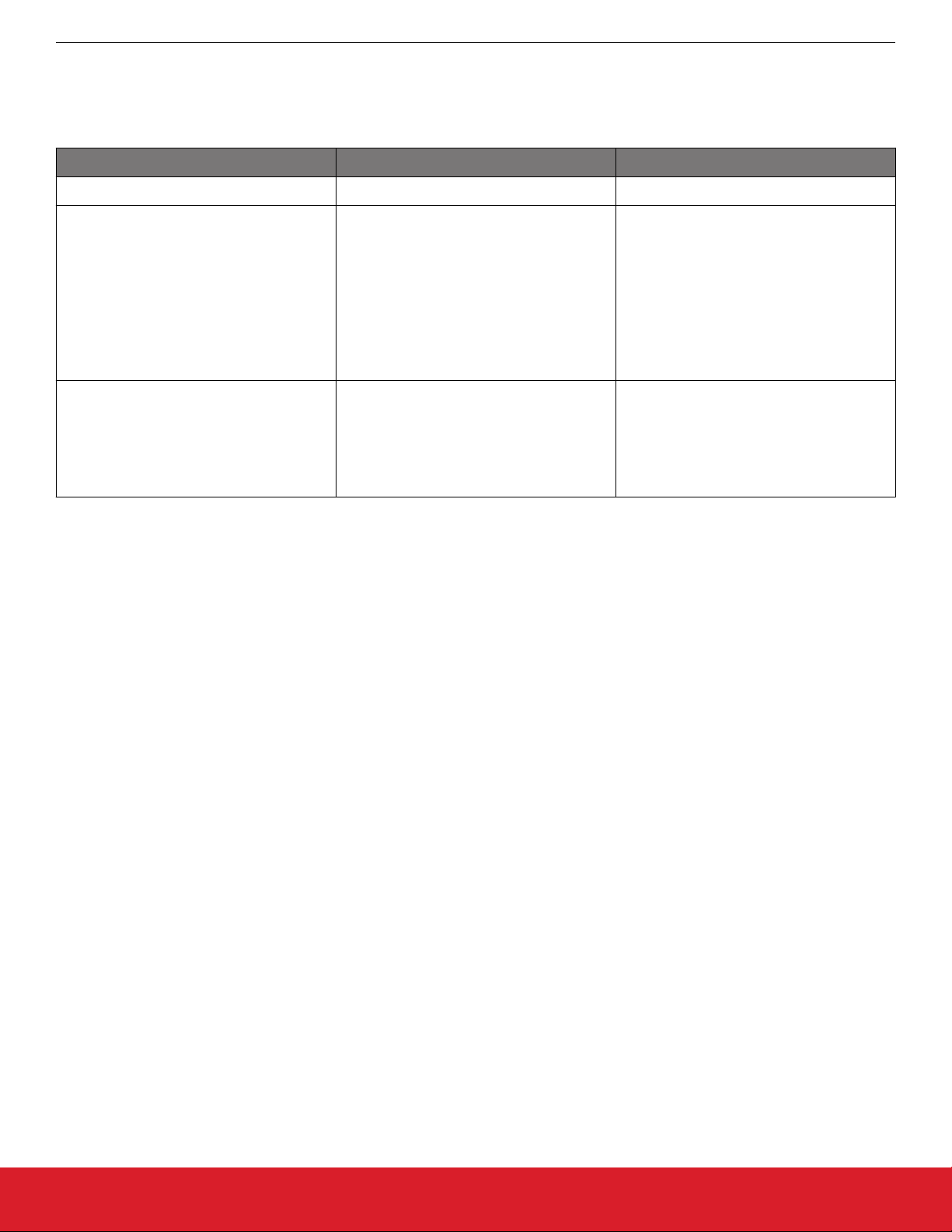

Dataset Command Subcommand & Parameters Description

(d)dataset (d)default Print default dataset.

(c)current Print current dataset.

(m)parent|master Print parent dataset.

(t)time Print time properties dataset.

(p)port Print port dataset.

(f)foreign Print foreign master dataset.

(u)unicast Print unicast master or slave node dataset.

(pw)power Print power profile dataset.

(g1)g8265 Print G.8265 profile dataset.

(g2)g8275 Print G.8275 profile default dataset.

(g2)g8275 <port_number> Print G.8275 profile port dataset.

Time Command Subcommand & Parameters Description

(t)time (i)info Print time and synchronization information.

(s)sync Print synchronization status.

arb <time> Print or set time in +/-

SSSSSSSSS.NNNNNNNNN format.

ptp <time> Print or set time in YYYY-MM-DD

HH:MM:SS.NNNNNNNNN format.

utc <time> Print or set time in UTC YYYY-MM-DD

HH:MM:SS.NNNNNNNNN format.

ntp <server> Print or set time from NTP server specified

by name or IP address.

(t)timescale <ptp|arb> Change timescale.

(o)offset <value> Change UTC offset.

(l)leap <save|load> Print UTC leap table or save/load it into/from

file.

(l)leap 59|61 <0|1> Change leap seconds flags.

(u)update <on|off> Turn on/off automatic update of RTC time

from PTP time.

(h)holdover <value> Change period of holdover state.

silabs.com | Building a more connected world. Rev. 0.1 | 35

Page 36

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

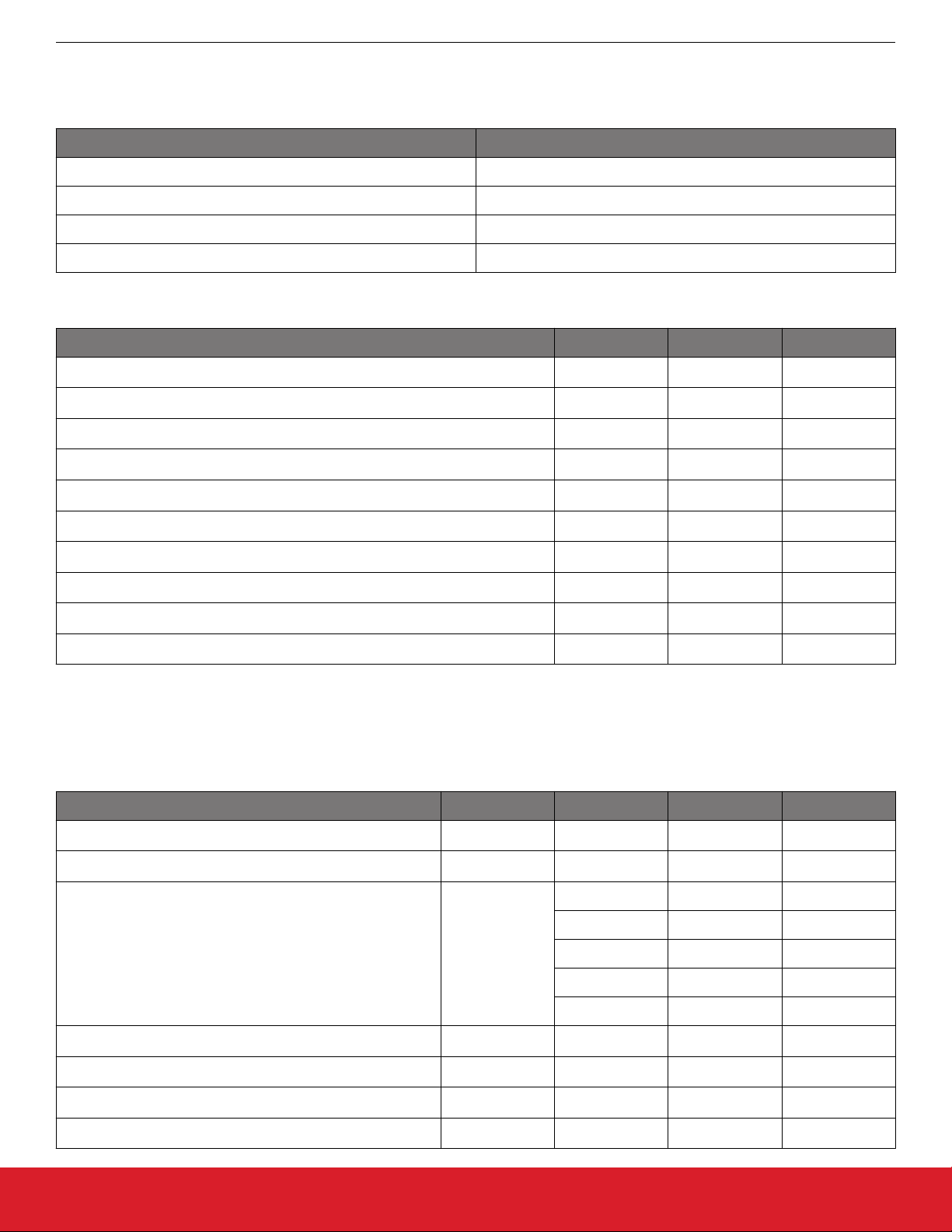

GPS Command Subcommand & Parameters Description

(g)gps (s)status Print GPS interface information.

(n)nmea Print NMEA position/satellites information.

(p)ppsin <enable|disable> Enable/disable PPS input reception.

(t)todin <enable|disable> Enable/disable TOD input reception.

(c)class <active> <holdover> <free> Change clock state to clock class mapping.

(t)todin <required|optional> Change non-present or invalid TOD-in handling.

(d)delay <value> Change PPS-in cable delay compensation.

(f)format <nmea|ascii|cm> Change TOD-in message format.

(v)void <ignore|syntonize|holdover> Changes NMEA RMC void flag handling.

(i)interface <default|com[n]> <baudrate> Change TOD-in interface.

(m)message <string> Send message to GPS receiver via TOD interface.

cm <status> <class> <accuracy>

<variance> <source> <tt> <ft>

Change CM status to clock properties mapping.

Pulsetime Command Subcommand & Parameters Description

(pt)pulsetime (s)status Print PPS-TOD status and configuration.

(p)pulse <period> <width> Change PPS-out pulse parameters.

(d)delay <value> Change TOD-out delay after PPS-out rising

edge.

(f)format <nmea [rmc|zda|both]|ascii [utc|

local]|cm|custom>

(v)void <never|free|holdover> Change NMEA RMC Active/Void flag be-

Change TOD-out message format.

havior.

(z)zone <none|tz|dst> Change NMEA ZDA timezone/daylight

field.

cm <class> <status> Change clock class to CM status mapping.

(i)interface <default|com[n]> <baudrate> Change TOD-out interface.

(t)todout <enable|disable> Enable/disable TOD output.

(m)mode <1|2|3> Change PPS-TOD output mode (sync,

holdover, always)

1= sync

2= holdover

3= always

(e)error <value> Change error tolerance.

(a)autorestart <on|off> Turn on/off automatic restart.

start <time> <count> Start/schedule PPS-TOD output.

stop Stop/cancel PPS-TOD output.

silabs.com | Building a more connected world. Rev. 0.1 | 36

Page 37

M68/M64 Module Data Sheet

IEEE 1588/PTP Engine

Nettime Command Subcommand & Parameters Description

(nt)nettime (s)status Print SNTP server status and configuration.

(m)mode <1..4> Change server mode (unicast, manycast, broadcast,

and mixed).

1= unicast

2= manycast

3= broadcast

4= mixed

(pi)poll <0..64> Change poll/broadcast interval.

start Start SNTP server.

stop Stop SNTP server.

Engine Command Subcommand & Parameters Description

(e)engine (i)init default|nvm Reinitialize clock. Currently not supported.

(p)port <enable|disable> Change port operational status.

(e)esmc <auto|0..15|off> Enable ESMC message transmission.

(e)esmc map <class> <ssm> Change clock class to SSM code mapping.

(n)nvm save|reset Change configuration in non-volatile storage. Current-

ly not supported.

(d)debug <on|off> Turn on/off debug output.

(v)verbose <level> Change verbose level for debug output.

(m)monitor <on com[n]|off> Enable output for PTP monitor program.

(f)freqout <5|10|20|25> Change frequency output (5, 10, 20, 25 MHz).

(a)asymmetry <value> Change PHY asymmetry compensation.

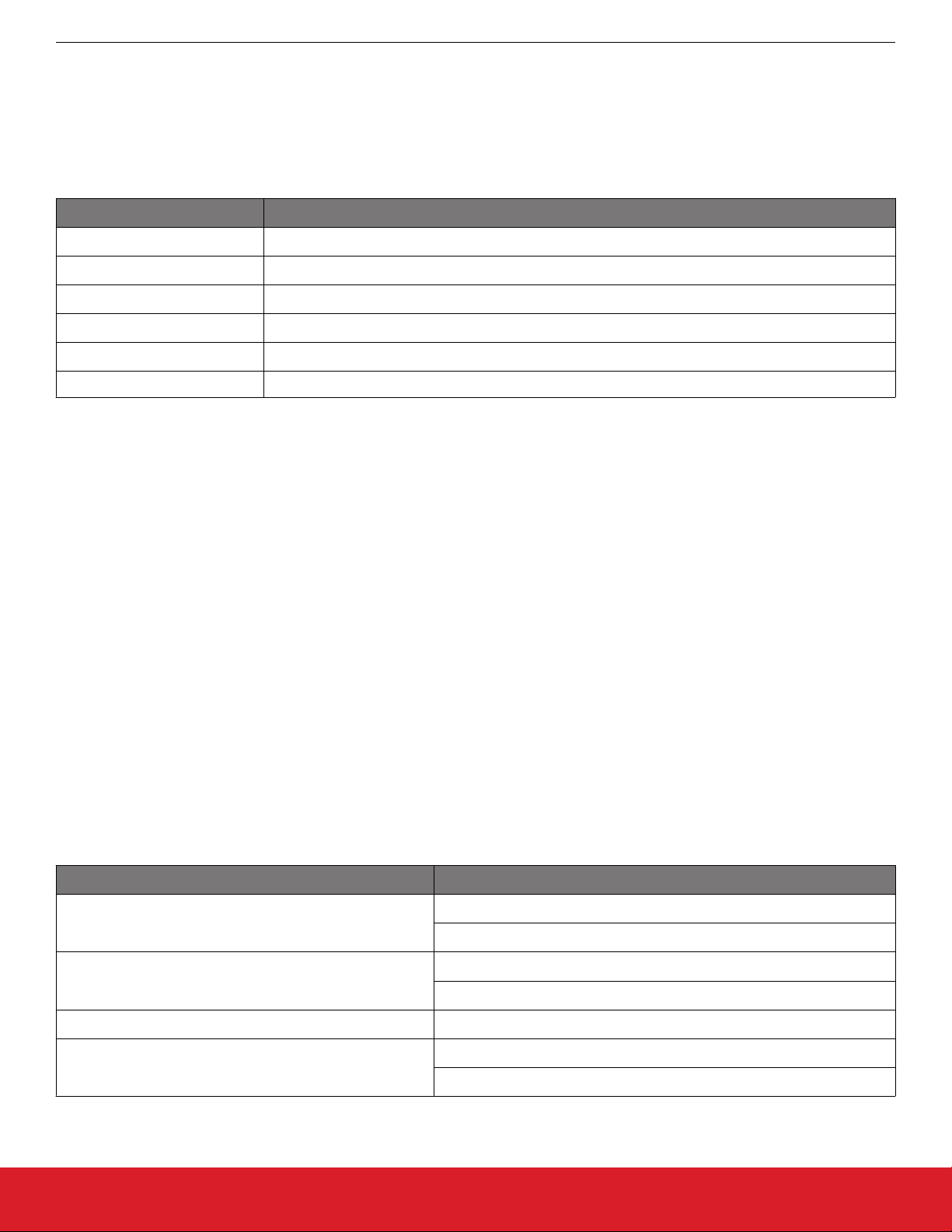

Examples

Function Command

Set the sync rate to -6 p si -6

Set the delay rate to -6 p di -6

Start PPS pt start

Print list of clock subcommands c

Print value of priority1 c p 1

Set value of priority1 to 130. c p 1 130

Print value of log sync interval. p si

Set value of log sync interval to -2 (4 sync per sec). p si -2

Print content of parent dataset. d m

Print content of port dataset. d p

Print list of debug output levels. e v

Enable clock monitor program on COM3. e m 3

silabs.com | Building a more connected world. Rev. 0.1 | 37

Page 38

M68/M64 Module Data Sheet

Network Subsystem

9. Network Subsystem

The Network Subsystem, as a part of the System Software is responsible for the networking support and network communications. Its

major part is TCP/IP protocol stack software, which provides the support for TCP/IP environment and TCP/IP communications over

Ethernet and serial links.

The TCP/IP stack software was designed to be fully reentrant and multithreaded safe, as well as scalable and highly configurable. It is

compliant with standards and has a rich application programming interface (API).

9.1 TCP/IP Stack Architecture

In general, functional architecture of the TCP/IP stack is the same as in any other TCP/IP implementations. It comprises four major

layers: link layer, network layer, transport layer and application layer. These layers interact with each other via well-defined interfaces.

A Link layer provides an abstract view of a network interface device (or adapter) and isolates its details from upper layers. Link layer

includes device drivers for real or virtual (pseudo) hardware and implementations of underlying physical network protocols. Currently,

TCP/IP link layer software provides following components: driver for internal loopback adapter (pseudo-device), driver for the Ethernet

Adapter and implementations of loopback and Ethernet II protocols.

A Network layer provides the basic packet transmission service as well as addressing and routing services. It uses the link layer interfaces to communicate with network devices. The TCP/IP network layer software includes an implementation of Internet Protocol (IP), as

the major protocol for packet transmission, and an implementation of Address Resolution Protocol (ARP) as the protocol for the remote

host’s hardware address discovery. Note that architecturally ARP is implemented as the network layer module, while it’s functionally

belongs rather to the link layer than to the network layer.

A Transport layer provides for applications a number of various transport services to exchange data over network. It uses network layer

interfaces to request an address, routing and control information, a packet transmission and so on. The most common transports are: a

datagram transport, which provides mechanisms for unreliable datagram exchange, and a stream transport, which provides reliable and

sequential data transfer. The TCP/IP software implements User Datagram Protocol (UDP) as datagram transport and Transmission

Control Protocol (TCP) as stream transport. It also implements Internet Control Message Protocol (ICMP) and Internet Group Management Protocol (IGMP) as “raw” transport modules. Any application can send and receive data in ICMP and IGMP format. An additional

transport module called “raw wildcard” transport allows applications to access packet transmission services of the IP module, i.e. to

send and receive raw IP datagrams.

An Application layer provides unified access to the transport layer features, independently of underlying transport protocol’s semantics

and hides each protocol implementation details. The TCP/IP software includes reach protocol-independent application programming interface, compatible with BSD sockets. All network applications using this API also belong to the application layer.

9.2 Application Layer Components

The TCP/IP software also includes a number of application layer components. They implement application layer protocols which are

parts of a TCP/IP suite, such as Dynamic Host Configuration Protocol and Domain Name System.

9.2.1 DHCP Client

The DHCP Client plays an important role in the system initialization. To operate in the TCP/IP environment the system needs to know

its IP address, network mask and, optionally, a default gateway. This information can be configured manually or distributed through the

DHCP server. So, the DHCP client dynamically obtains these parameters from the DHCP server and automatically configures TCP/IP

stack software thus eliminating the need for manual configuration. In the absence of a DHCP server on the network the system is connected to, the DHCP client uses a so-called Zero-Config protocol to select an IP address from a well-known address range and negotiate this selection with other nodes on the network.

9.2.2 DNS Client

Any node on the TCP/IP network is identified by its unique IP address. But it is more convenient to use for identification a human-readable name instead of an IP address. The node name to the node address translation is performed by a DNS client. In order to perform

this translation the DNS client interacts with one or more DNS servers, which store and maintain a distributed global name-to-address

mapping database.

9.3 BSD Sockets API

An application can access communication facilities of the network subsystem through the well-known BSD Sockets application programming interface. This interface is based on the concept of a socket – a communication endpoint – which is quite similar to the file

descriptor.

silabs.com | Building a more connected world. Rev. 0.1 | 38

Page 39

M68/M64 Module Data Sheet

Network Subsystem

9.4 Network Initialization

communication facilities can be used, the network subsystem must be initialized and configured. Normally it is done during the

Before

initialization of the shell environment. The shell startup code reads configuration files and initializes the TCP/IP stack software. When

the target system does not require the shell to be running it can initialize and configure the network subsystem by using a network

initialization routine. It will do the following:

• If TCP/IP configuration parameters were not provided, it tries to read them from a permanent storage such as on-board flash memory.

• It initializes the link layer by calling each network interface driver’s entry point.

• It initializes the network layer by invoking IP and ARP initialization routines.

• It initializes the transport layer by calling each transport module initialization routine.

• It configures the internal loopback interface.

• It either configures the Ethernet interface manually if configuration parameters were specified, or requests the DHCP client to configure it dynamically.

• Finally it sets the hostname and parameters for a name resolution client.

This routine has to be called after the OS has been initialized and started.

silabs.com | Building a more connected world. Rev. 0.1 | 39

Page 40

M68/M64 Module Data Sheet

Using the AccuTime Software

10. Using the AccuTime Software

The M64 and M68 are quite similar. In the CLI commands that follow, the M68 commands are given. The full details of a command are

available via help commands in the CLI.

For the M64, the parameter "port_number" is always 1. For the M68, "port_number" is either 1 or 2, the default is 1.

For the M64, the parameter "iface" is always enet0. For the M68, it is either enet0 or enet1.

10.1 PTP Engine Modes

The PTP Engine is capable of operating in five different modes. The operational mode defines the functionality supported by the engine, PTP clock behavior and its properties in different operating conditions. The operational mode is specified upon startup and can

only be changed by restarting the engine.

• Mode 0 – PTP-only mode;

• Mode 1 – GNSS-only mode;

• Mode 2 – GNSS-primary, PTP-secondary;

• Mode 3 – PTP-primary, GNSS-secondary;

• Mode 4 – PTP-only, GNSS-debug;

In addition to Mode 0-4 a Slave-only mode is supported. The clock can be switched to the slave-only mode and back at any time and

from any of above operational modes.

10.1.1 Mode 0

This is an ordinary PTP master-slave mode. The GNSS interface is disabled.

In this mode the clock normally acts as a PTP slave, but may also become a PTP master if no better clock exists on the network.