Bottom View

PRELIMINARY DATA SHEET

SiPHY™ OC-192/STM-64 TRANSMITTER

Features

Si5540

Complete SONET/SDH transmitter for OC-192/STM-64 data rates with integrated

16:1 multiplexer and DSPLL

Data Rates Supported: OC-192/STM-64,

10GbE, and 10.7 Gbps FEC

Low Power Operation 0.6 W (typ)

Small Footprint: 99-Pin BGA Package

(11 x 11mm)

DSPLL™ Based Clock Multiplier Unit

w/ selectable loop filter bandwidths

™

based clock multiplier unit:

OIF SFI-4 Compliant Interface

Output Clock Powerdown

Operates with 155 or 622 MHz

Reference Sources

Optional 3.3 V Supply Pin for

LVTTL Compatible Outputs

Single 1.8 V Supply Operation

Applications

Sonet/SDH/ATM Routers

Add/Drop Multiplexers

Digital Cross Connects

Optical Transceiver Modules

Sone t / S D H Test E qu ipm en t

Description

The Si5540 is a fully integrated low-power transmitter for high-speed serial

communication systems. It combines high speed clock generation with a 16:1

multiplexer to serialize data for OC-192/STM-64 applications. The Si5540 is based

on Silicon Laboratories’ DSPLL

filter components required by traditional clock multiplier units. In addition,

selectable loop filter bandwidths are provided to ensure superior jitter performance

while relaxing the jitter requirements on external clock distribution subsystems.

Support for data streams up to 10.7 G bps is also provided for applications that

employ forward error correction (FEC).

The Si5540 represents a new standard in low jitter, low power and small size for

10 Gbps serial transmitters. It operates from a single 1.8 V supply over the

industrial t em perature range (–40°C to 85°C).

™

technology which eliminates the external loop

Si5364

Ordering Information:

See pa ge17.

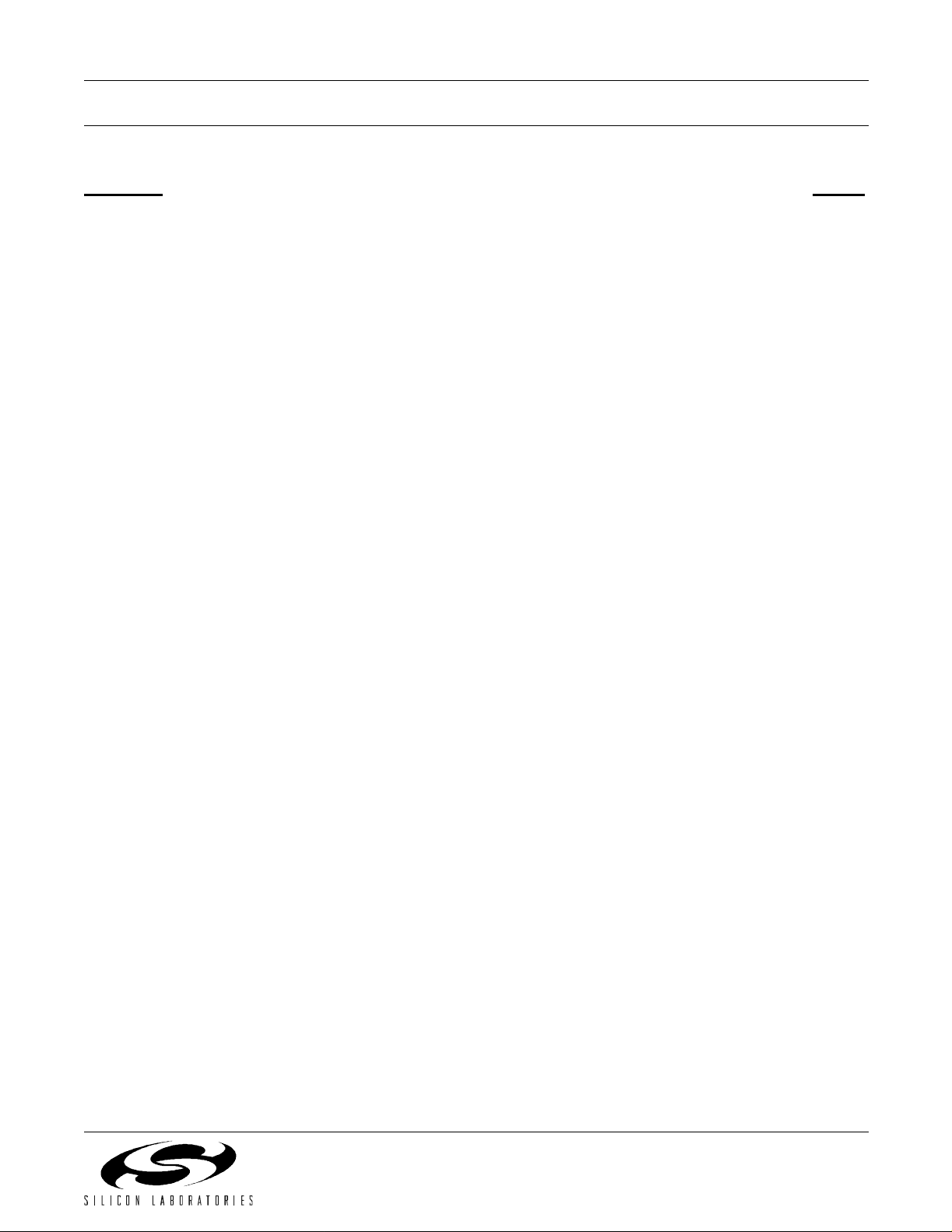

Functional Block Diagram

REFSEL

REFC LK

TXLOL

BWSEL

TXCLKD SBL

TXCLKOUT

TXDOUT

Preliminary Rev. 0.31 8/ 01 Copyright © 2001 by Silicon Labora tories Si5540-DS031

This in formation applies to a product under devel opment. I ts characteristics and specifications are subject to change without notice.

2

TXCLK16IN

2

2

Bias

REXT

DSPLL

CMU

Reset

Control

RESET

TM

TXSQLCH

TXMSBSEL

÷

16:1

16

MUX

FIFOERR

REFRATE

2

32

FIFO

2

TXCLK16OUT

TXCLK16IN

TXDIN[15:0]

FIFORST

Si5540

2 Preliminary Rev. 0.31

Si5540

TABLE OF CONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

DSPLL™ Clock Multiplier Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reference Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Serialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Clock Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Si5540 Pinout: 99-Pin BGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Pin Descriptions: Si5540 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Preliminary Rev. 0.31 3

Si5540

Electrical Specifications

Table 1. Recommended Operating Conditions

Parameter Symbol Test Condition Min* Typ

Ambient Tem peratur e T

LVTTL Output Supply Voltage V

Si5540 Supply Voltage V

*Note: All minimum and maximum speci ficat i ons are guaranteed and apply across the recommended operating condi tions.

T ypi cal val ues appl y at nominal supply voltages and an operat in g temperature of 25

A

DD33

DD

–40 25 85 °C

1.71 — 3.47 V

1.71 1.8 1.89 V

°C unless otherwise stated.

Max*

Unit

V

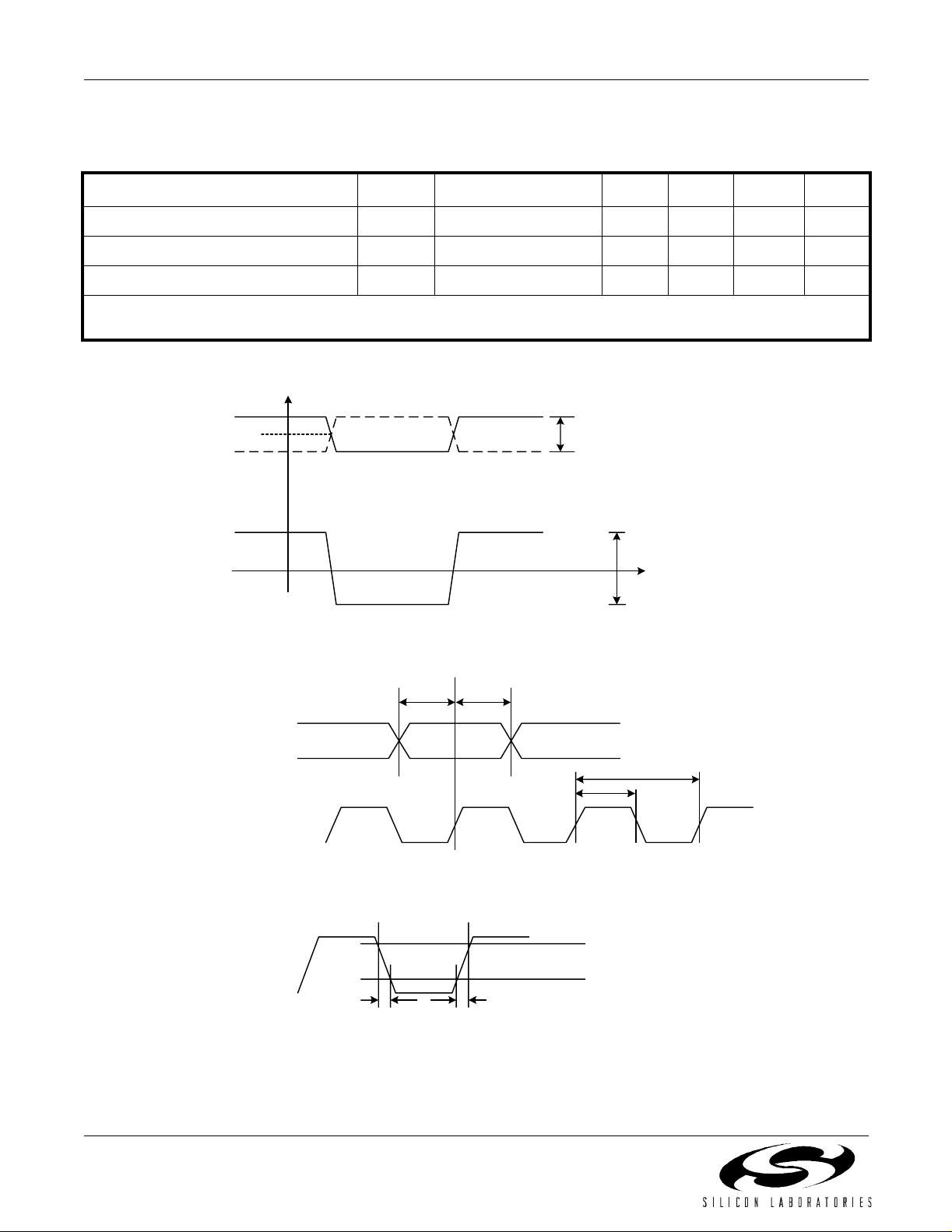

SIGNAL +

Differential

I/Os

V

ICM

SIGNAL –

, V

OCM

V

IS

Single Ended Voltage

(SIGNAL +) – (SIGNAL –)

Differential

Voltage Swing

VID,VOD (V

= 2VIS)

ID

Differential Peak-to-Peak Voltage

t

Figure 1. Differential Voltage Measurement (TXDIN, TXDOUT, TXCLK16IN, TXCLK16OUT)

TXDOUT,

TXDIN

TXCLKOUT,

TXCLK16IN

All Differential

IOs

t

su

t

hd

Figure 2. Data to Clock Delay

80%

20%

t

F

t

R

Figure 3. Rise/Fall Time Measurement

t

t

CH

CP

4 Preliminary Rev. 0.31

Si5540

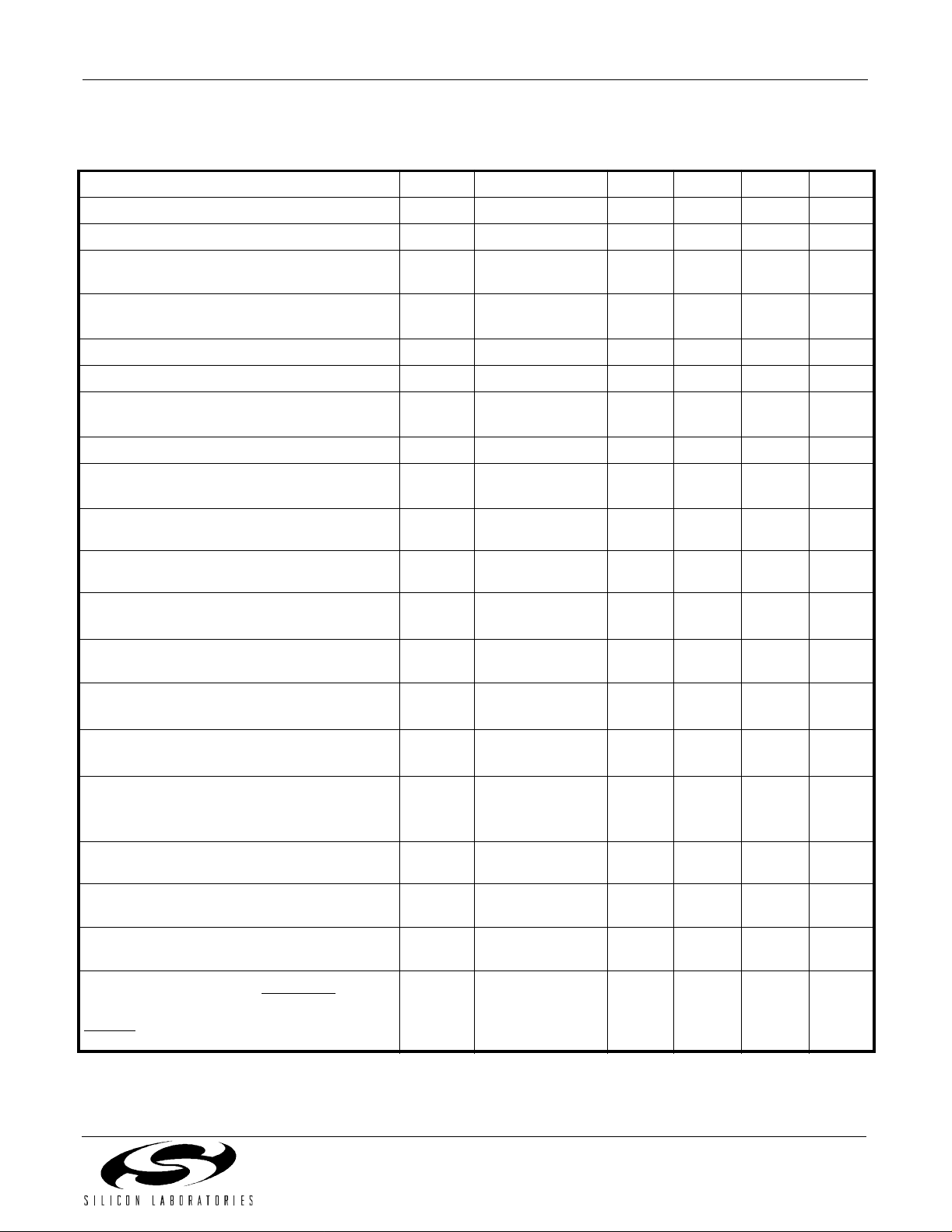

Table 2. DC Characteristics, VDD = 1.8 V

(VDD = 1.8 V ±5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Supply Current I

Power Dissipation P

Common Mode Output Voltage

V

(TXDOUT,TXCLKOUT)

Differential Output Voltage Swing

V

(TXDOUT, TX CLKOUT), Differential pk-pk

L VPECL Input Voltage High (REFCLK) V

L VPECL Input Voltage Low (REFCLK) V

L VPECL Input Voltage Swing (REFCLK),

V

Differential pk-pk

LVPECL Input Common Mode (REFCLK) V

Input Impedance

R

(REFCLK, TXDIN, TXCLK16IN)

L VDS Input High Voltage (TXDIN,

V

TXCLK16IN)

L VDS Input Low Voltage (TXDIN,

TXCLK16IN)

LVDS Input Voltage, Single Ended pk-pk

V

(TXDIN, TXCLK 1 6 IN)

DD

D

OCM

OD

IH

IL

ID

ICM

IN

IH

V

IL

ISE

See Figure 1 800 1000 1200 mV

Each in p ut to

common mode

— 333 TBD mA

—0.6TBDW

.8 0.9 1.0 V

(pk-pk)

1.975 2.3 2.59 V

1.32 1.6 1.99 V

250 — 2600 mV

(pk-pk)

1.65 1.95 2.30 V

42 50 58 Ω

——2.4V

0.0 — — V

100 — 600 mV

(pk-pk)

LVDS Input Common Mode Voltage

(TXDIN, TXCLK 1 6 IN)

LVDS Output High Voltage

(TXCLK16OUT)

LVDS Output Low Voltage

(TXCLK16OUT)

L VDS Output Voltage, Single Ended pk-pk

(TXCLK16OUT)

LVDS Output Common Mode Voltage

(TXCLK16OUT)

Output Short to GND

(TXCLK16OUT, TXDOUT, TXCLKOUT)

Output Short to V

DD

(TXCLK16OUT, TXDOUT, TXCLKOUT)

L VTTL Input Voltage Low

(TXCLK D S BL, FIFO R ST, TXSQLCH

,

BWSEL, REFRATE, REFSEL, TXMSBSE L,

RESET

)

V

V

V

V

V

I

I

V

ICM

OH

OL

OSE

OCM

SC–

SC+

IL2

100 Ω Load

Line-to-Line

100 Ω Load

Line-to-Line

100 Ω Load

Line-to-Line, See

Figure 1

.8 2.0 2.4 V

TBD — 1.475 V

0.925 — TBD V

250 400 550 mV

(pk-pk)

1.125 1.20 1.275 V

—25TBDmA

TBD –100 — µA

——0.8V

Preliminary Rev. 0.31 5

Si5540

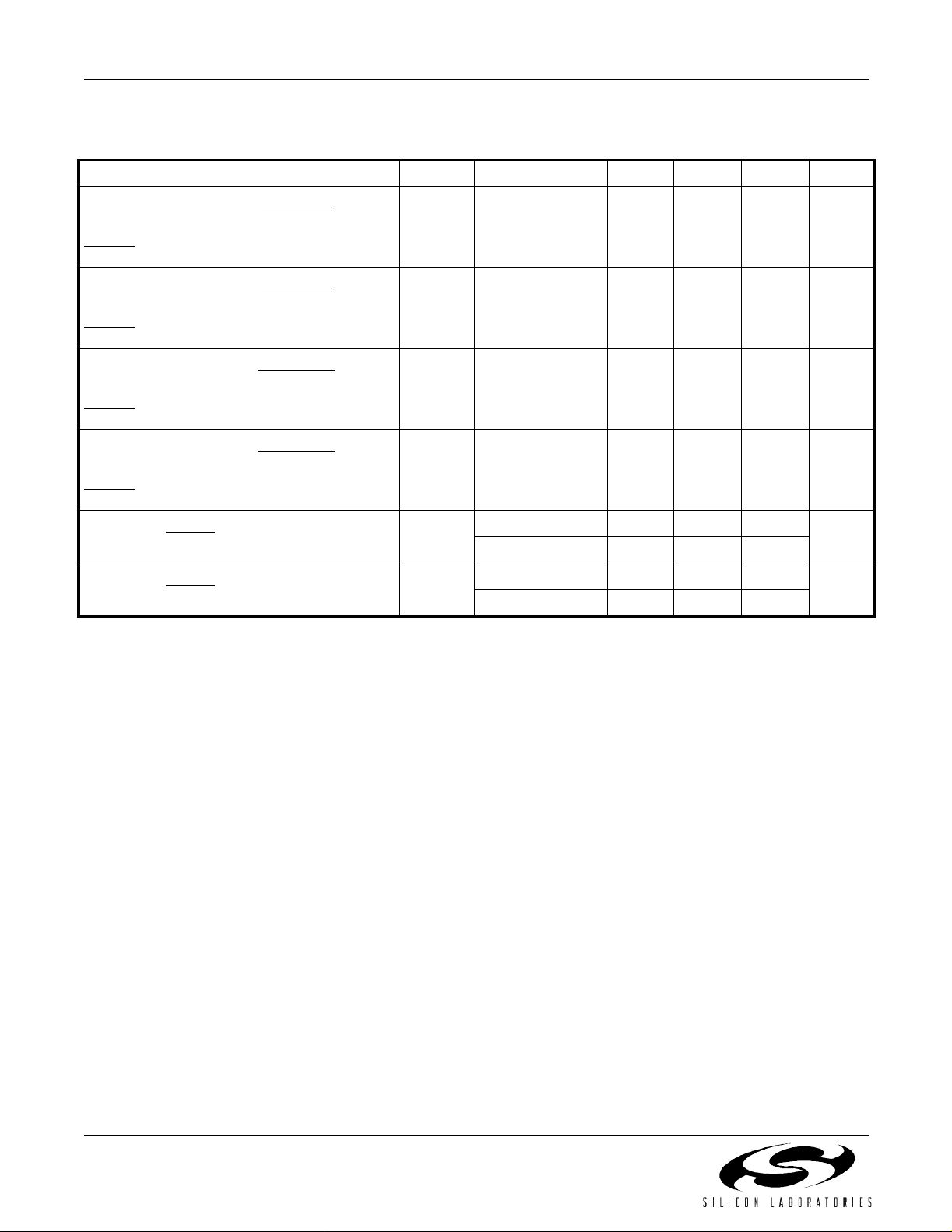

Table 2. DC Characteristics, VDD = 1.8 V (Continued)

(VDD = 1.8 V ±5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ M ax Unit

Input Voltage High

(TXCLK D S BL, FIFO R ST, TXSQLCH

,

BWSEL, REFRATE, REFSEL, TXMSBSE L,

RESET

)

Input Low Current

(TXCLK D S BL, FIFO R ST, TXSQLCH

,

BWSEL, REFRATE, REFSEL, TXMSBSE L,

RESET

)

Input Hi g h Curre n t

(TXCLK D SBL, FIFORST, TXSQL C H

,

BWSEL, REFRATE, REFSEL, TXMSBSE L,

RESET

)

Input Impedance

(TXCLK D SBL, FIFORST, TXSQL C H

,

BWSEL, REFRATE, REFSEL, TXMSBSE L,

RESET

)

LVTTL Output Voltage Low

(FIFOERR, TXLOL

)

LVTTL Output Voltage High

(FIFOERR, TXLOL

)

V

V

V

I

I

R

OH2

IH2

IL

IH

IN

OL2

2.0 — — V

——10µA

——10µA

10 — — kΩ

VDD33 = 1.8 V — — 0.4 V

VDD33 = 3.3 V — — 0.4

VDD33 = 1.8 V 1.4 — — V

VDD33 = 3.3 V 2.4 — —

6 Preliminary Rev. 0.31

Loading...

Loading...