Preliminary Rev. 0.31 8/ 01 Copyright © 2001 by Silicon Labora tor ies Si5530-DS031

This information applies to a product under development. Its char acteristics and spe c ifications are subject to change without notice.

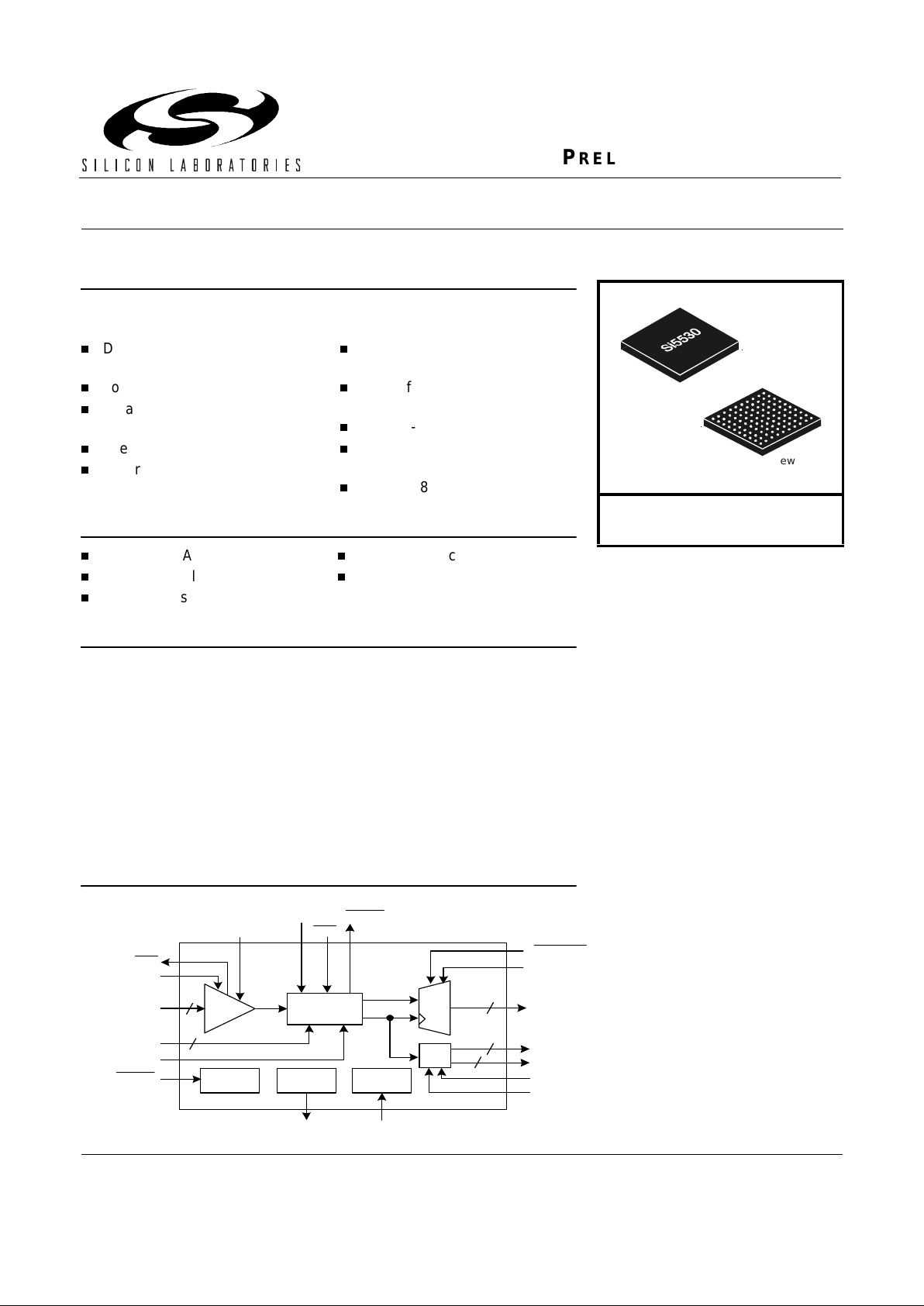

Si5530

SiPHY™ OC-192/STM-64 SONET/SDH RECEIVER

Features

Complete low power, high speed, receiver with integrated limiting amplifier,

clock and data recovery (CDR), and 1:16 demultiplexer:

Applications

Description

The Si5530 is a fully integrated low-power receiver for high-speed serial

communication systems. It combines post amplification, clock and data

recovery, and a 1:16 deserialization as required in OC-192/STM-64

applications. Support for data streams up to 10.7 Gbps is also provided for

applications that employ forward error correction (FEC). A fully integrated

clock and data recovery unit with integrated loop filter ensures optimal jitter

performance while reducing design complexity.

The Si5530 represents a new standard in low power and small size for

high-speed serial receivers. It operates from a single 1.8 V supply over the

industrial temperature range (–40°C to 85°C).

Functional Block Diagram

Data Rates Supported: OC-192/

STM-64, 10GbE, 10.7 Gbps FEC

Low Power Operation 0.6 W (typ)

Small Footprint 99-Pin BGA

Package (11 x 11 mm)

Integrated Limiting Amplifier

Programmable Slicing Level and

Sampling Phase

SFI-4 Compliant LVDS Low

Speed Interface

Loss-of-Signal and Loss-of-Lock

Detection

Lock-to-Reference Control

Optional 3.3 V Supply Pin for

LVTTL Compatible Outputs

Single 1.8 V Supply Operation

Sonet/SDH/ATM Routers

Add/Drop Multiplexers

Digital Cross Connects

Optical Transceiver Modules

Sonet/SDH Test Equipment

RXDOUT[15:0]

RXCLK1

RXCLK2

RXCLK2DIV

1:16

DEMUX

RXSQLCH

RXMSBSE L

32

2

2

RXCLK2DSBL

RXDIN

REFCLK

Limiting

AMP

LOSLVL

LOS

LTR

CDR

2

2

SLICE_LVL

PHASE_ADJ RXLOL

REFRATE

RESET

Reset

Control

Voltage

Ref

VREF

Bias

REXT

÷

Ordering Information:

See pa ge16.

Si5364

Bottom View

PRELIMINARY DATA SHEET

Si5530

2 Preliminary Rev. 0.31

Si5530

Preliminary Rev. 0.31 3

TABLE OF CONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Limiting Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Loss-of-Signal Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Slicing Level Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Clock and Data Recovery (CDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Sample Phase Adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Lock Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Lock-to-Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reference Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Deserialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Serial Input to Parallel Output Relationship . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Auxiliary Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Data Squelch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Voltage Reference Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Si5530 Pinout: 99-Pin BGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Pin Descriptions: Si5530 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Si5530

4 Preliminary Rev. 0.31

Electrical Specifications

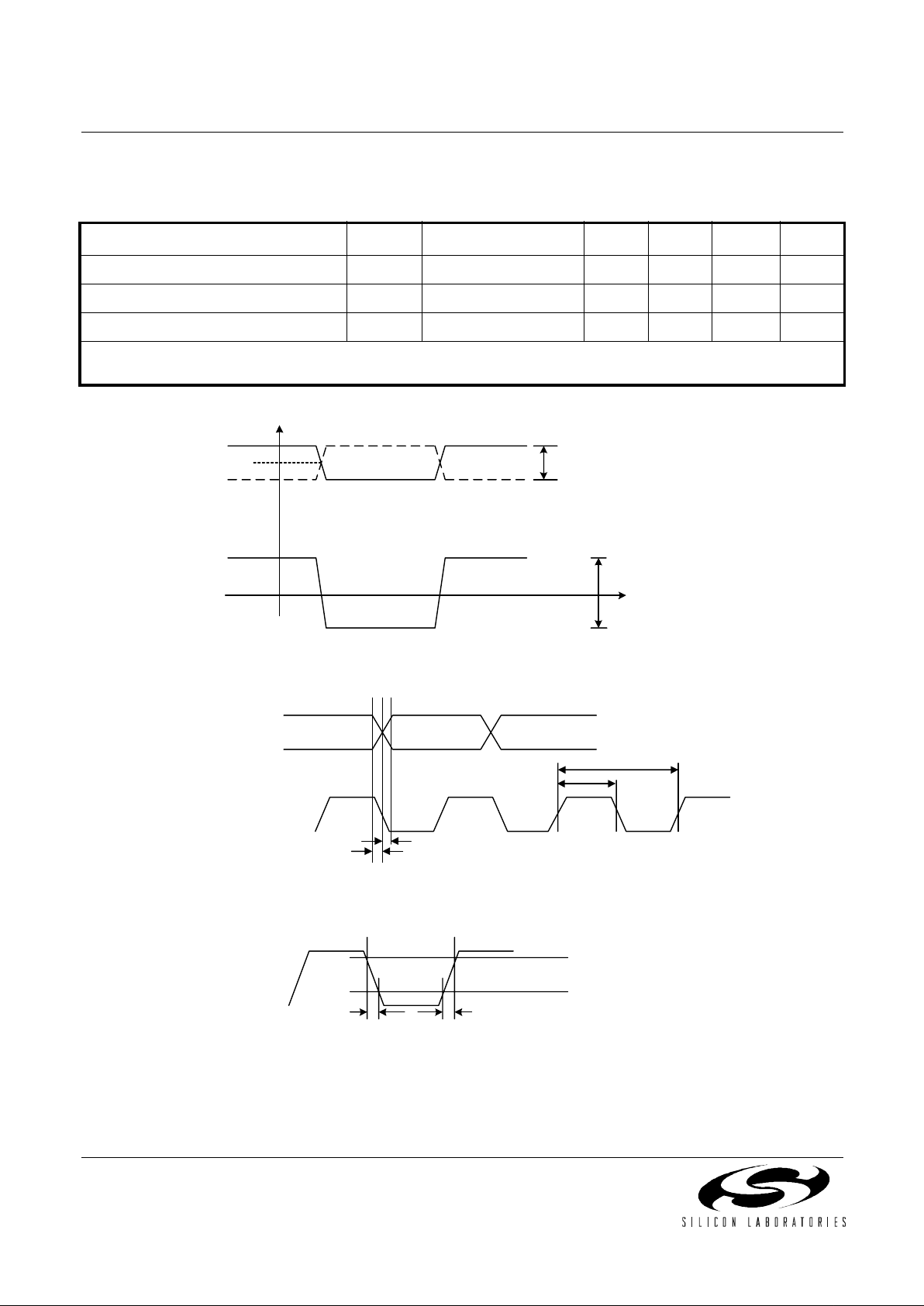

Figure 1. Differential Volta ge Measurement (RXDIN, RXDOUT, RXCLK1, RXCLK2)

Figure 2. Data to Clock Delay

Figure 3. Rise/Fall Time Measurement

Table 1. Recommended Operating Conditions

Parameter Symbol Test Condition

Min

*

Typ

Max

*

Unit

Ambient Temperature T

A

–40 25 85 °C

LVTTL Output Supply Voltage V

DD33

1.71 — 3.47 V

Si5530 Supply Voltage V

DD

1.71 1.8 1.89 V

*Note: All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

T ypical values apply at nominal supply voltages and an oper ating temperature of 25°C unless otherwise stated.

V

IS

VID,VOD (V

ID

= 2VIS)

Differential

I/Os

Differential

Voltage Swing

Single Ended Voltage

Differential Peak-to-Peak Voltage

SIGNAL +

SIGNAL –

(SIGNAL +) – (SIGNAL –)

V

ICM

, V

OCM

V

t

RXDOUT

RXCLK1

t

CP

t

CH

t

cq1

t

cq2

All Differential

IOs

t

F

t

R

80%

20%

Si5530

Preliminary Rev. 0.31 5

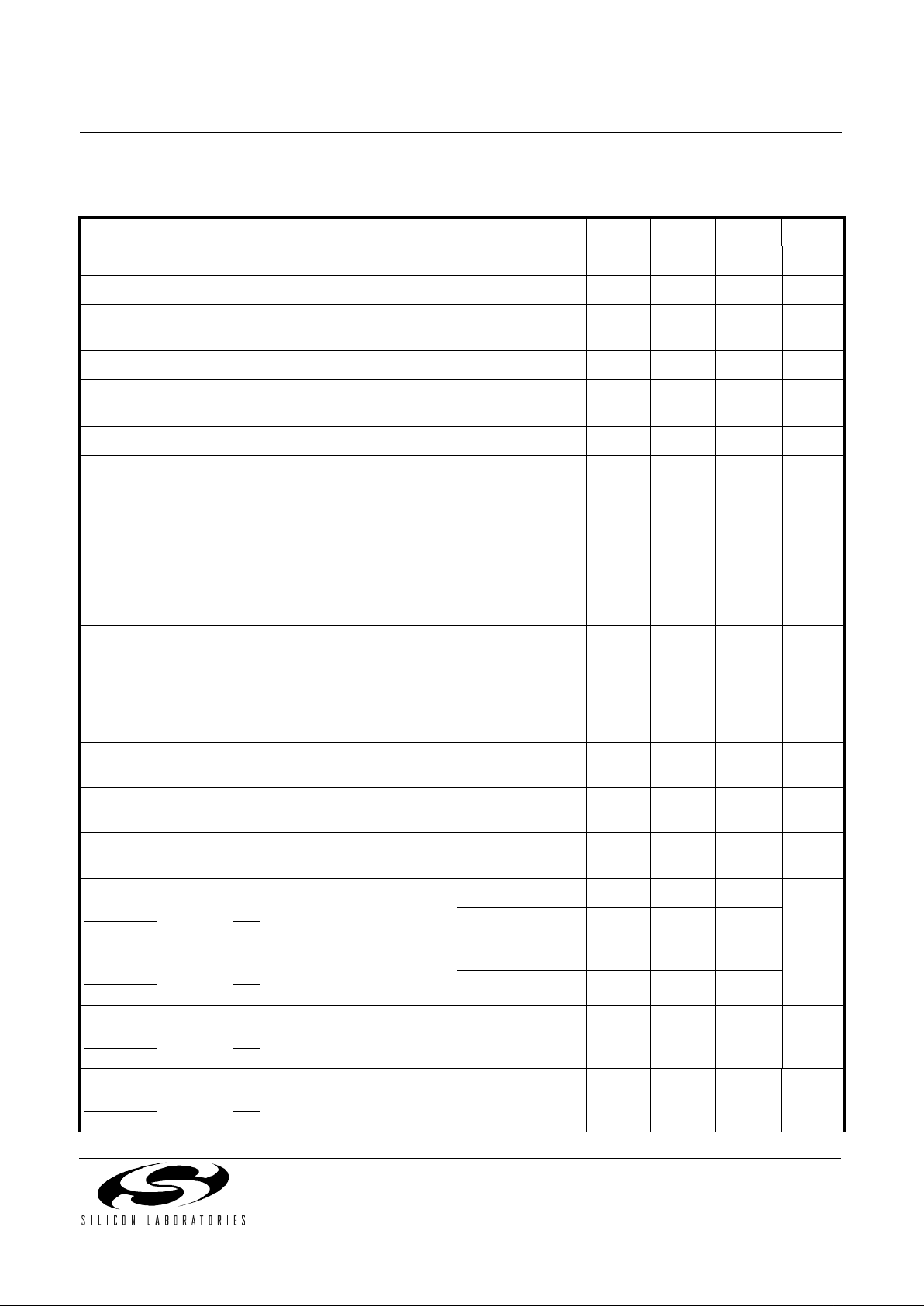

Table 2. D C Characteri sti cs

(VDD = 1.8 V ±5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Supply Current I

DD

— 278 TBD mA

Power Dissipation P

D

—0.5 TBDW

Voltage Reference (VREF) V

REF

VREF driving

10 k

Ω load

1.21 1.25 1.29 V

Common Mode Input Voltage (RXDIN) V

ICM

TBD 0.1 TBD V

Differential Input Voltage Swing (RXDIN) V

ID

See Figure 1 20 — 1.0 mV

(pk-pk)

L VPECL Input Voltage HIGH (REFCLK) V

IH

1.975 2.3 2.59 V

L VPECL Input Voltage LOW (REFCLK) V

IL

1.32 1.6 1.99 V

L VPECL Input Voltage Swing,

Differential pk-pk (REFCLK)

V

ID

Figure 1 250 — 2400 mV

(pk-pk)

L VPECL Internally Generated Input Bias

(REFCLK)

V

IB

1.65 1.95 2.3 V

L VDS Output High Voltage

(RXDOUT, RXCLK1, RXCLK2)

V

OH1

100 Ω Load

Line-to-Line

TBD — 1.475 mV

LVDS Output Low Voltage

(RXDOUT, RXCLK1, RXCLK2)

V

OL1

100 Ω Load

Line-to-Line

0.925 — TBD V

LVDS Output Voltage, Differential pk-pk

(RXDOUT, RXCLK1, RXCLK2)

V

OSE

100 Ω Load

Line-to-Line,

Figure 1

500 — 800 mV

(pk-pk)

LVDS Common Mode Voltage

(RXDOUT, RXCLK1, RXCLK2)

V

CM

1.125 — 1.275 V

Output Short to GND

(RXDOUT, RXCLK1, RXCLK2)

I

SC(–)

—25TBDmA

Output Short to V

DD

(RXDOUT, RXCLK1, RXCLK2)

I

SC(+)

TBD –100 — µA

LVTTL Input Voltage Low

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

, REFSE L , LTR, RESET)

V

IL2

VDD33 = 3.3 V — — 0.8 V

VDD33 = 1.8 V — — 0.7

LVTTL Input Voltage High

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

, REFSE L , LTR, RESET)

V

IH2

VDD33 = 3.3 V 2.0 — — V

VDD33 = 1.8 V 1.7 — —

LVTTL Input Low Current

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

, REFSE L , LTR, RESET)

I

IL

——10µA

LVTTL Input High Current

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

, REFSE L , LTR, RESET)

I

IH

——10µA

Si5530

6 Preliminary Rev. 0.31

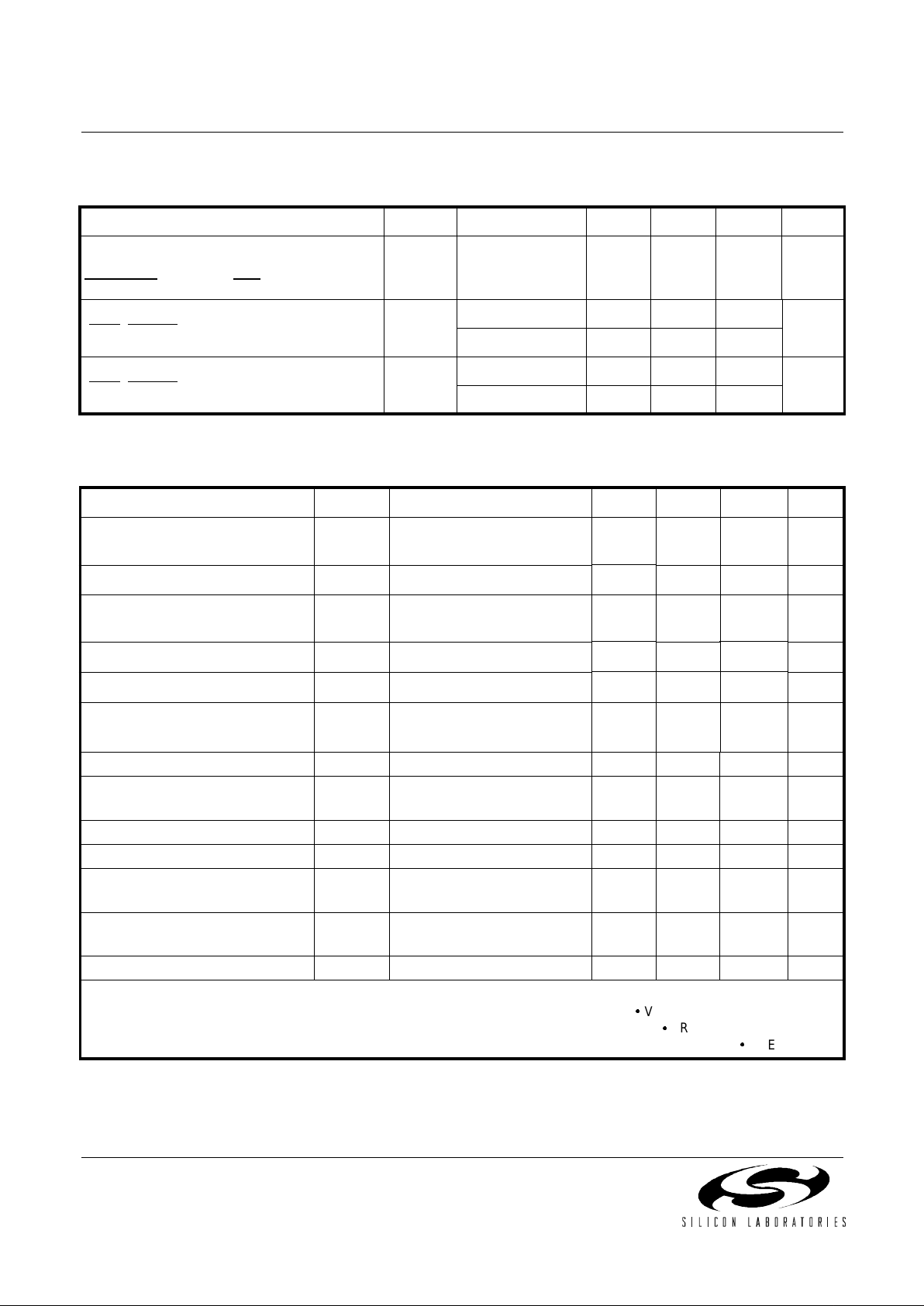

LVTTL Input Impedanc e

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

, REFSE L , LTR, RESET)

R

IN

10 — — kΩ

L VTTL Output Voltage Low

(LOS

, RXLOL)

V

OL2

VDD33 = 1.8 V — — 0.4 V

VDD33 = 3.3 V — — 0.4

L VTTL Output Voltage High

(LOS

, RXLOL)

V

OH2

VDD33 = 1.8 V 1.4 — — V

VDD33 = 3.3 V 2.4 — —

Table 3. AC Characteristics (RXDIN, RXDOUT, RXCLK1, RXCLK2)

(VDD = 1.8 V ±5%, TA = –40°C to 85°C)

Parameter Symbol T est Condition Min Typ Max Unit

Output Clock Frequency

(RXCLK1)

f

clkout

See Figure 2 — 622.08 667 MHz

Duty Cycle (RXCLK1, RXCLK2) tch/tcp, Figure 2 45 — 55 %

Output Rise and Fall Times

(RXCLK1, RXCLK2,RXD O U T)

t

R,tF

Figure 3 — 50 — ps

Data Invalid Prior to RXCLK1 t

cq1

Figure 2 — — 200 ps

Data In v a l i d After RXC L K1 t

cq2

Figure 2 — — 200 ps

Input Return Loss (RXIN) 400 kHz–10.0 GHz

10.0 GHz–16.0 GHz

18.7

TBD

—

—

—

—

dB

dB

Slicing Adjust Dynam ic Ran ge SLICELVL = 200–800 mV –20 — 20 m V

Slicing Level Offset

1

(referred to RXDIN)

SLICELVL = 200–800 mV –500 — 500

µV

Slicing Level Accuracy VSLICE –5 — 5 %

Sampling Phase Adjustment

2

PHASEADJ = 200–800 mV -45

o

—45

o

LOS Threshold Dynamic Range LOSLVL = 200–800 mV 10 — 50 mV

pk-pk

LOS Threshold Offset

3

(referred to RXDIN)

LOSLVL = 200–800 mV –500 — 500

µV

LOS Threshold Accuracy VLOS –5 — 5 %

Note:

1. Slice level (referred to RXDIN) is calculated as follows: VSLICE = (SLICE_LVL – 0.4

VREF)/15.

2. Sample Phase Offset is calcul ated as follows: PHASE OFFSET = 45° (PHASEADJ – 0.4

VREF)/0.3

3. LOS Threshold voltage (r eferred to RXDIN) is calculated as follows: VLOS = 30mV + (LOS_LVL – 0.4

VREF)/15.

Table 2. DC Characteristics (Continued)

(VDD = 1.8 V ±5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Loading...

Loading...