Page 1

ANY-FREQUENCY PRECISION CLOCKS

Si5316, Si5319, Si5322, Si5323, Si5324, Si5325,

Si5326, Si5327, Si5328, Si5365, Si5366, Si5367,

Si5368, Si5369, Si5374, Si5375, Si5376

F

AMILY REFERENCE MANUAL

Rev. 1.2 6/13 Copyright © 2013 by Silicon Laboratories Si53xx-RM

Page 2

Si53xx-RM

2 Rev. 1.2

Page 3

Si53xx-RM

TABLE OF CONTENTS

Section Page

1. Any-Frequency Precision Clock Product Family Overview . . . . . . . . . . . . . . . . . . . . . .12

2. Wideband Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

2.1. Narrowband vs. Wideband Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3. Any-Frequency Clock Family Members . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3.1. Si5316 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3.2. Si5319 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.3. Si5322 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.4. Si5323 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3.5. Si5324 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.6. Si5325 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.7. Si5326 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.8. Si5327 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.9. Si5328 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.10. Si5365 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.11. Si5366 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.12. Si5367 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

3.13. Si5368 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

3.14. Si5369 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.15. Si5374/75/76 Compared to Si5324/19/26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.16. Si5374 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.17. Si5375 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

3.18. Si5376 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

4. DSPLL (All Devices) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

4.1. Clock Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .34

4.2. PLL Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

4.2.1. Jitter Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.2.2. Jitter Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

4.2.3. Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

5. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . .37

5.1. Clock Multiplication (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . .37

5.1.1. Clock Multiplication (Si5316) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.1.2. Clock Multiplication (Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1.3. CKOUT3 and CKOUT4 (Si5365 and Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.4. Loop bandwidth (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.5. Jitter Tolerance (Si5316, Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.6. Narrowband Performance (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.7. Input-to-Output Skew (Si5316, Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.8. Wideband Performance (Si5322 and Si5365). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.9. Lock Detect (Si5322 and Si5365) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.1.10. Input-to-Output Skew (Si5322 and Si5365). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.2. PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52

5.2.1. Input Clock Stability during Internal Self-Calibration

(Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

5.2.2. Self-Calibration caused by Changes in Input Frequency

(Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Rev. 1.2 3

Page 4

Si53xx-RM

5.2.3. Recommended Reset Guidelines (Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . 52

5.3. Pin Control Input Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

5.3.1. Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.3.2. Automatic Clock Selection (Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . 55

5.3.3. Hitless Switching with Phase Build-Out (Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

5.4. Digital Hold/VCO Freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

5.4.1. Narrowband Digital Hold (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.4.2. Recovery from Digital Hold (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.4.3. Wideband VCO Freeze (Si5322, Si5365) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

5.5. Frame Synchronization (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57

5.6. Output Phase Adjust (Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

5.6.1. FSYNC Realignment (Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.6.2. Including FSYNC Inputs in Clock Selection (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.6.3. FS_OUT Polarity and Pulse Width Control (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.6.4. Using FS_OUT as a Fifth Output Clock (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.6.5. Disabling FS_OUT (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

5.7. Output Clock Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

5.7.1. LVPECL and CMOS TQFP Output Signal Format Restrictions at 3.3 V (Si5365, Si5366) . . . . 59

5.8. PLL Bypass Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

5.9. Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

5.9.1. Loss-of-Signal Alarms (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . 60

5.9.2. FOS Alarms (Si5365 and Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.9.3. FSYNC Align Alarm (Si5366 and CK_CONF = 1 and FRQTBL = L) . . . . . . . . . . . . . . . . . . . . . 61

5.9.4. C1B and C2B Alarm Outputs (Si5316, Si5322, Si5323) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.9.5. C1B, C2B, C3B, and ALRMOUT Outputs (Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.10. Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

5.11. DSPLLsim Configuration Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .62

6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328,

Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . .63

6.1. Clock Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

6.1.1. Jitter Tolerance (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328,

Si5368, Si5369, Si5374, Si5375, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.1.2. Wideband Parts (Si5325, Si5367) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

6.1.3. Narrowband Parts (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368,

Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.4. Loop Bandwidth (Si5319, Si5326, Si5368, Si5375, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . 66

6.1.5. Lock Detect (Si5319, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374,

Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

6.2. PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .66

6.2.1. Initiating Internal Self-Calibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.2.2. Input Clock Stability during Internal Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.2.3. Self-Calibration Caused by Changes in Input Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.2.4. Narrowband Input-to-Output Skew (Si5319, Si5324, Si5326, Si5327,

Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.2.5. Clock Output Behavior Before and During ICAL (Si5319, Si5324, Si5326,

Si5327, Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . 68

6.3. Input Clock Configurations (Si5367 and Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . .69

6.4. Input Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .69

6.4.1. Manual Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5367, Si5368,

Si5369, Si5374, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4.2. Automatic Clock Selection (Si5324, Si5325, Si5326, Si5328, Si5367, Si5368,

Si5369, Si5374, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4 Rev. 1.2

Page 5

Si53xx-RM

6.4.3. Hitless Switching with Phase Build-Out (Si5324, Si5326, Si5327, Si5328,

Si5368, Si5369, Si5374, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

6.5. Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374,

Si5375, and Si5376 Free Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

6.5.1. Free Run Mode Programming Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5.2. Clock Control Logic in Free Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.5.3. Free Run Reference Frequency Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.5.4. Free Run Reference Frequency Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.6. Digital Hold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

6.6.1. Narrowband Digital Hold (Si5316, Si5324, Si5326, Si5328, Si5368,

Si5369, Si5374, Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

6.6.2. History Settings for Low Bandwidth Devices (Si5324, Si5327, Si5328,

Si5369, Si5374). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.6.3. Recovery from Digital Hold (Si5319, Si5324, Si5326, Si5327, Si5328,

Si5368, Si5369, Si5374, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.6.4. VCO Freeze (Si5319, Si5325, Si5367, Si5375). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.6.5. Digital Hold versus VCO Freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

6.7. Output Phase Adjust (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78

6.7.1. Coarse Skew Control (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.7.2. Fine Skew Control (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

6.7.3. Independent Skew (Si5324, Si5326, Si5328, Si5368, Si5369, Si5374, and Si5376) . . . . . . . . 79

6.7.4. Output-to-output Skew (Si5324, Si5326, Si5327, Si5328, Si5368,

Si5369, Si5374, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.7.5. Input-to-Output Skew (All Devices) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

6.8. Frame Synchronization Realignment (Si5368 and CK_CONFIG_REG = 1) . . . . . . .79

6.8.1. FSYNC Realignment (Si5368). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.8.2. FSYNC Skew Control (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.8.3. Including FSYNC Inputs in Clock Selection (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.8.4. FS_OUT Polarity and Pulse Width Control (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.8.5. Using FS_OUT as a Fifth Output Clock (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.9. Output Clock Drivers (Si5319, Si5324, Si5325, Si5326, Si5327,

Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, Si5376) . . . . . . . . . . . . . . . . . . . .83

6.9.1. Disabling CKOUTn. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.9.2. LVPECL TQFP Output Signal Format Restrictions at 3.3 V (Si5367, Si5368, Si5369). . . . . . . 83

6.10. PLL Bypass Mode (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328,

Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . .84

6.11. Alarms (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367,

Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . .84

6.11.1. Loss-of-Signal Alarms (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328,

Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6.11.2. FOS Algorithm (Si5324, Si5325, Si5326, Si5328, Si5368, Si5369, Si5374, and Si5376 ). . . . 85

6.11.3. C1B, C2B (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5374,

Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

6.11.4. LOS (Si5319, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

6.11.5. C1B, C2B, C3B, ALRMOUT (Si5367, Si5368, Si5369 [CK_CONFIG_REG = 0]) . . . . . . . . . . 87

6.11.6. C1B, C2B, C3B, ALRMOUT (Si5368 [CK_CONFIG_REG = 1]) . . . . . . . . . . . . . . . . . . . . . . . 88

6.11.7. LOS Algorithm for Reference Clock Input (Si5319, Si5324, Si5326, Si5327,

Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

6.11.8. LOL (Si5319, Si5324, Si5326, Si5327, Si5328, Si5368, Si5369, Si5374,

Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

6.11.9. Device Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Rev. 1.2 5

Page 6

Si53xx-RM

6.12. Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

6.13. I2C Serial Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

6.14. Serial Microprocessor Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .91

6.14.1. Default Device Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

6.15. Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

6.16. DSPLLsim Configuration Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .93

7. High-Speed I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

7.1. Input Clock Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94

7.2. Output Clock Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

7.2.1. LVPECL TQFP Output Signal Format Restrictions at 3.3 V (Si5367, Si5368, Si5369). . . . . . . 96

7.2.2. Typical Output Circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.2.3. Typical Clock Output Scope Shots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.3. Typical Scope Shots for SFOUT Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .99

7.4. Crystal/Reference Clock Interfaces (Si5316, Si5319, Si5323, Si5324, Si5326,

Si5327, Si5328, Si5366, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . .102

7.5. Three-Level (3L) Input Pins (No External Resistors) . . . . . . . . . . . . . . . . . . . . . . .104

7.6. Three-Level (3L) Input Pins (With External Resistors) . . . . . . . . . . . . . . . . . . . . . .105

8. Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106

9. Packages and Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

Appendix A—Narrowband References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108

Appendix B—Frequency Plans and Typical Jitter Performance (Si5316,

Si5319, Si5323, Si5324, Si5326, Si5327, Si5366, Si5368, Si5369,

Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Appendix C—Typical Phase Noise Plots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Appendix D—Alarm Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

Appendix E—Internal Pullup, Pulldown by Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

Appendix F—Typical Performance: Bypass Mode, PSRR, Crosstalk,

Output Format Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

Appendix G—Near Integer Ratios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Appendix H—Jitter Attenuation and Loop BW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .157

Appendix I—Response to a Frequency Step Function . . . . . . . . . . . . . . . . . . . . . . . . . . .162

Appendix J—Si5374, Si5375, Si5376 PCB Layout Recommendations . . . . . . . . . . . . . .163

Appendix K—Si5374, Si5375, and Si5376 Crosstalk . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167

Appendix L—Jitter Transfer and Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .177

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 8

6 Rev. 1.2

Page 7

Si53xx-RM

LIST OF FIGURES

Figure 1. Si5316 Any-Frequency Jitter Attenuator Block Diagram . . . . . . . . . . . . . . . . . . . . . 16

Figure 2. Si5319 Any-Frequency Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . .17

Figure 3. Si5322 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 4. Si5323 Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . 19

Figure 5. Si5324 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 20

Figure 6. Si5325 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 7. Si5326 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 22

Figure 8. Si5327 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 23

Figure 9. Si5328 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 24

Figure 10. Si5365 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 11. Si5366 Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . 26

Figure 12. Si5367 Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 13. Si5368 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . 28

Figure 14. Si5369 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . 29

Figure 15. Si5374 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 16. Si5375 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 17. Si5376 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 18. Any-Frequency Precision Clock DSPLL Block Diagram . . . . . . . . . . . . . . . . . . . . 33

Figure 19. Clock Multiplication Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 20. PLL Jitter Transfer Mask/Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 21. Jitter Tolerance Mask/Template. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 22. Si5316 Divisor Ratios. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 23. Wideband PLL Divider Settings (Si5325, Si5367) . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 24. Narrowband PLL Divider Settings (Si5319, Si5324, Si5326, Si5327,

Si5328, Si5368, Si5369, Si5374, Si5375, and Si5376) . . . . . . . . . . . . . . . . . . . . . 65

Figure 25. Si5324, Si5325, Si5326, Si5327, Si5328, Si5374, and Si5376

Input Clock Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure

Figure 27. Free Run Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

Figure 28. Parameters in History Value of M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 29. Digital Hold vs. VCO Freeze Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Figure 30. Frame Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Figure 31. FOS Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 32. I

Figure 33. I2C Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Figure 34. SPI Write/Set Address Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 35. SPI Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 36. SPI Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Figure 37. Differential LVPECL Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 38. Single-Ended LVPECL Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 39. CML/LVDS Termination (1.8, 2.5, 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 40. Center Tap Bypassed Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Figure 41. CMOS Termination (1.8, 2.5, 3.3 V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

26. Si5367, Si5368, and Si5369 Input Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . 70

2

C Command Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Rev. 1.2 7

Page 8

Si53xx-RM

Figure 42. Typical Output Circuit (Differential) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Figure 43. Differential Output Example Requiring Attenuation . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 44. Typical CMOS Output Circuit (Tie CKOUTn+ and CKOUTn– Together). . . . . . . . 97

Figure 45. Differential CKOUT Structure (not for CMOS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 46. sfout_2, CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 47. sfout_3, lowSwingLVDS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Figure 48. sfout_5, LVPECL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 49. sfout_6, CML . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 50. sfout_7, LVDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Figure 51. CMOS External Reference Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 52. Sinewave External Clock Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 53. Differential External Reference Input Example

(Not for Si5374, Si5375, or Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

Figure 54. Differential OSC Reference Input Example for Si5374, Si5375 and Si5376 . . . . .103

Figure 55. Three Level Input Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 56. Three Level Input Pins. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 57. Typical Power Supply Bypass Network (TQFP Package) . . . . . . . . . . . . . . . . . . 106

Figure 58. Typical Power Supply Bypass Network (QFN Package) . . . . . . . . . . . . . . . . . . . 106

Figure 59. Typical Reference Jitter Transfer Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure 60. Phase Noise vs. f3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112

Figure 61. Jitter Integrated from 12 kHz to 20 MHz Jitter, fs RMS . . . . . . . . . . . . . . . . . . . . 113

Figure 62. Jitter Integrated from 100 Hz to 40 MHz Jitter, fs RMS . . . . . . . . . . . . . . . . . . . . 114

Figure 63. Jitter vs. f3 with FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 64. Reference vs. Output Frequency. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 65. 622.08 MHz Output with a 114.285 MHz Crystal. . . . . . . . . . . . . . . . . . . . . . . . . 117

Figure 66. 622.08 MHz Output with a 40 MHz Crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

Figure 67. 155.52 MHz In; 622.08 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Figure 68. 155.52 MHz In; 622.08 MHz Out; Loop BW = 7 Hz, Si5324 . . . . . . . . . . . . . . . . .120

Figure 69. 19.44 MHz In; 156.25 MHz Out; Loop BW = 80 Hz . . . . . . . . . . . . . . . . . . . . . . .121

Figure 70. 19.44 MHz In; 156.25 MHz Out; Loop BW = 5 Hz, Si5324 . . . . . . . . . . . . . . . . . .122

Figure 71. 27 MHz In; 148.35 MHz Out; Light Trace BW = 6 Hz;

Dark Trace BW = 110 Hz, Si5324 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

Figure 72. 61.44 MHz In; 491.52 MHz Out; Loop BW = 7 Hz, Si5324 . . . . . . . . . . . . . . . . . .124

Figure 73. 622.08 MHz In; 672.16 MHz Out; Loop BW = 6.9 kHz . . . . . . . . . . . . . . . . . . . . .125

Figure 74. 622.08 MHz In; 672.16 MHz Out; Loop BW = 100 Hz . . . . . . . . . . . . . . . . . . . . .126

Figure 75. 156.25 MHz In; 155.52 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127

Figure 76. 78.125 MHz In; 644.531 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128

Figure 77. 78.125 MHz In; 690.569 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129

Figure 78. 78.125 MHz In; 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Figure 79. 86.685 MHz In; 173.371 MHz and 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . 131

Figure 80. 86.685 MHz In; 173.371 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Figure 81. 86.685 MHz In; 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

Figure 82. 155.52 MHz and 156.25 MHz In; 622.08 MHz Out . . . . . . . . . . . . . . . . . . . . . . . 134

Figure 83. 10 MHz In; 1 GHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Figure 84. Si5324, Si5326, and Si5328 Alarm Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Figure 85. Si5368 and Si5369 Alarm Diagram (1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

8 Rev. 1.2

Page 9

Si53xx-RM

Figure 86. Si5368 and Si5369 Alarm Diagram (2 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Figure 87. ±50 ppm, 2 ppm Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155

Figure 88. ±200 ppm, 10 ppm Steps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Figure 89. ±2000 ppm, 50 ppm Steps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

Figure 90. RF Generator, Si5326, Si5324; No Jitter (For Reference) . . . . . . . . . . . . . . . . . .158

Figure 91. RF Generator, Si5326, Si5324 (50 Hz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Figure 92. RF Generator, Si5326, Si5324 (100 Hz Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 93. RF Generator, Si5326, Si5324 (500 Hz Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

Figure 94. RF Generator, Si5326, Si5324 (1 kHz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Figure 95. RF Generator, Si5326, Si5324 (5 kHz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Figure 96. RF Generator, Si5326, Si5324 (10 kHz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 97. Si5326 Frequency Step Function Response . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 98. Vdd Plane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163

Figure 99. Ground Plane and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

Figure 100. Output Clock Routing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 101. OSC_P, OSC_N Routing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Figure 102. Si5374, Si5375, and Si5376 DSPLL A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 103. Si5374, Si5375, and Si5376 DSPLL B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

Figure 104. Si5374, Si5375, and Si5376 DSPLL C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 105. Si5374, Si5375, and Si5376 DSPLL D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Figure 106. Example Frequency Plan Sources. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Figure 107. Run Time Frequency Plan Examples. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Figure 108. Wide View of Jitter Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .174

Figure 109. Zoomed View of Jitter Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Figure 110. Zoomed Again View of Jitter Transfer (Showing Peaking). . . . . . . . . . . . . . . . . 175

Figure 111. Maximum Zoomed View of Jitter Peaking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Rev. 1.2 9

Page 10

Si53xx-RM

LIST OF TABLES

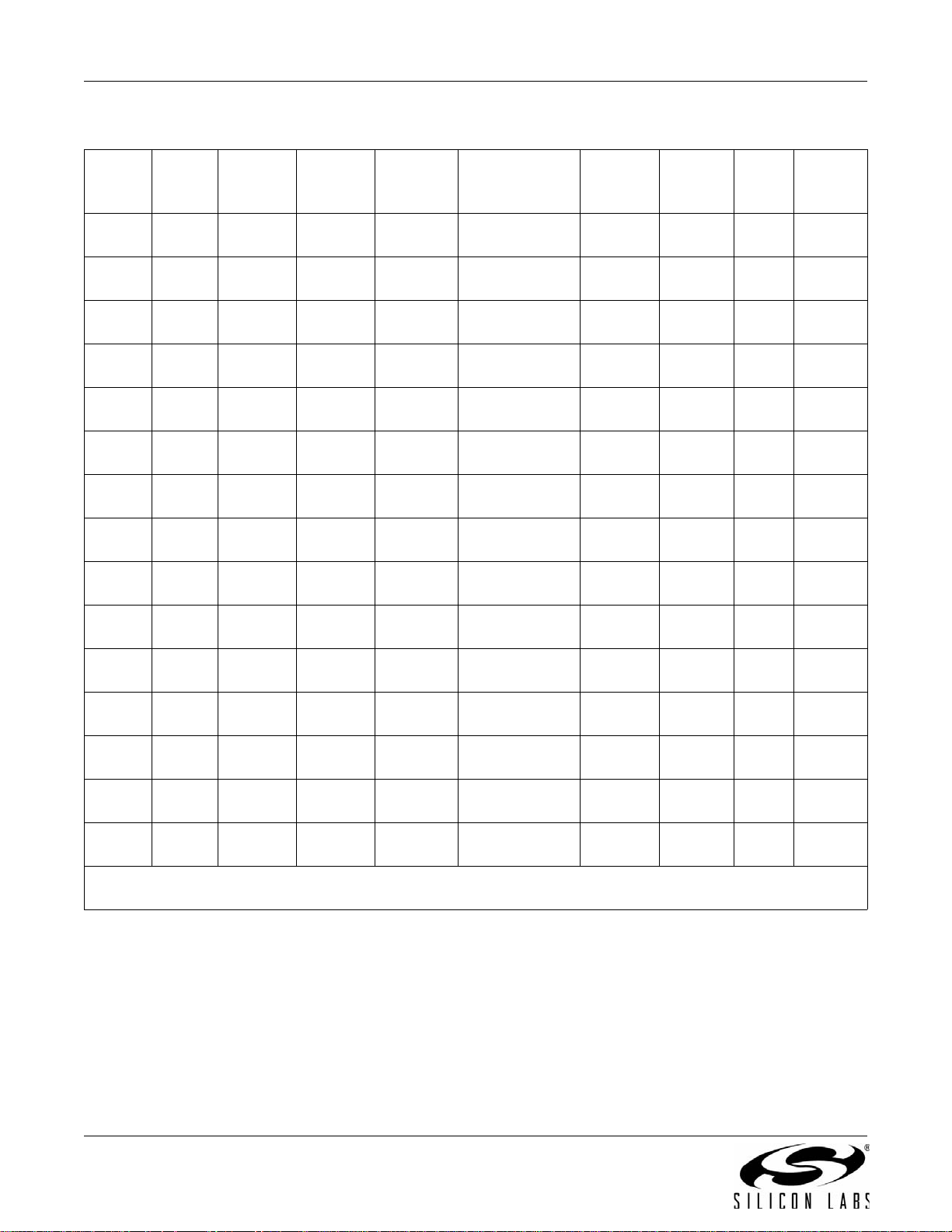

Table 1. Product Selection Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 2. Product Selection Guide (Si5322/25/65/67) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3. Si5316, Si5322, Si5323, Si5365 and Si5366 Key Features . . . . . . . . . . . . . . . . . . . 37

Table 4. Frequency Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 5. Input Divider Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 6. Si5316 Bandwidth Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 7. SONET Clock Multiplication Settings (FRQTBL=L) . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 8. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) . . . . . . . . . . 44

Table 9. SONET to Datacom Clock Multiplication Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 10. Clock Output Divider Control (DIV34) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 11. Si5316, Si5322, and Si5323 Pins and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 12. Si5365 and Si5366 Pins and Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 13. Manual Input Clock Selection (Si5316, Si5322, Si5323), AUTOSEL = L . . . . . . . . 54

Table 14. Manual Input Clock Selection (Si5365, Si5366), AUTOSEL = L. . . . . . . . . . . . . . . 54

Table 15. Automatic/Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 16. Clock Active Indicators (AUTOSEL = M or H) (Si5322 and Si5323). . . . . . . . . . . . 55

Table 17. Clock Active Indicators (AUTOSEL = M or H) (Si5365 and Si5367). . . . . . . . . . . . 55

Table 18. Input Clock Priority for Auto Switching (Si5322, Si5323) . . . . . . . . . . . . . . . . . . . . 55

Table 19. Input Clock Priority for Auto Switching (Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . 56

Table 20. FS_OUT Disable Control (DBLFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 21. Output Signal Format Selection (SFOUT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 22. DSBL2/BYPASS Pin Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 23. Frequency Offset Control (FOS_CTL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 24. Alarm Output Logic Equations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 25. Lock Detect Retrigger Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Table 26. Narrowband Frequency Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 27. Dividers and Limi

Table 28. CKOUT_ALWAYS_ON and SQ_ICAL Truth Table. . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 29. Manual Input Clock Selection (Si5367, Si5368, Si5369). . . . . . . . . . . . . . . . . . . . . 70

Table 30. Manual Input Clock Selection (Si5324, Si5325, Si5326, Si5328,

Si5374, and Si5376) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 31. Automatic/Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 32. Input Clock Priority for Auto Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 33. Digital Hold History Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 34. Digital Hold History Averaging Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Table 35. CKIN3/CKIN4 Frequency Selection (CK_CONF = 1) . . . . . . . . . . . . . . . . . . . . . . . 80

Table 36. Common NC5 Divider Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 37. Alignment Alarm Trigger Threshold. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 38. Output Signal Format Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 39. Loss-of-Signal Validation Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 40. Loss-of-Signal Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 41. FOS Reference Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

ts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10 Rev. 1.2

Page 11

Si53xx-RM

Table 42. CLKnRATE Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Table 43. Alarm Output Logic Equations (Si5367, Si5368, and Si5369

[CONFIG_REG = 0]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 44. Alarm Output Logic Equations [Si5368 and CKCONFIG_REG = 1] . . . . . . . . . . . . 88

Table 45. Lock Detect Retrigger Time (LOCKT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 46. SPI Command Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Table 47. Output Driver Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 48. Disabling Unused Output Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Table 49. Output Format Measurements1,2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 50. Approved 114.285 MHz Crystals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 51. XA/XB Reference Sources and Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 52. Jitter vs.f3 in fs, RMS1,2,3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 53. Jitter Values for Figure 63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Table 54. Jitter Values for Figure 64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Table 55. Jitter Values for Figure 74 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

Table 56. Jitter Values for Figure 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

Table 57. Jitter Values for Figure 76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Table 58. Jitter Values for Figure 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Table 59. Jitter Values for Figure 80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

Table 60. Si5316 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 61. Si5322 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Table 62. Si5323 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 63. Si5319, Si5324, Si5328 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 64. Si5325 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 65. Si5326 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Table 66. Si5327 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 67. Si5365 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

Table 68. Si5366 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Table 69. Si5367 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 70. Si5368 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Table 71. Si5369 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 72. Si5374/75/76 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Table 73. Output Format vs. Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 74. Jitter Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 75. Si5374/75/76 Crosstalk Jitter Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

167

Rev. 1.2 11

Page 12

Si53xx-RM

1. Any-Frequency Precision Clock Product Family Overview

Silicon Laboratories Any-Frequency Precision Clock products provide jitter attenuation and clock multiplication/

clock division for applications requiring sub 1 ps rms jitter performance. The device product family is based on

Silicon Laboratories' 3rd generation DSPLL technology, which provides any-frequency synthesis and jitter

attenuation in a highly integr ated PLL solution that eliminates the need for discrete VCXO/VCSOs and loop filter

components. These devices are ideally suited for applications which require low jitter reference clocks, including

OTN (OTU-1, OTU-2, OTU-3, OTU-4), OC-48/STM-16, OC-192/STM-64, OC-768/STM-256, GbE, 10GbE, Fibre

Channel, 10GFC, synchronous Ethernet, wireless backhaul, wireless point-point infrastructure, broadcast video/

HDTV (HD SDI, 3G SDI), test and measurement, data acquisition systems, and FPGA/ASIC reference clocking.

Table 1 provides a product selector guide for the Silicon Laboratories Any-Frequency Precision Clocks. Three

product families are available. The Si5316, Si5319, Si5323, Si5324, Si5326, Si5366, and Si5368 are jitterattenuating clock multipliers that provide ultra-low jitter generation as low as 0.30 ps RMS. The devices vary

according to the number of clock inputs, number of clock outputs, and control method. The Si5316 is a fixedfrequency, pin controlled jitter attenuator that can be used in clock smoothin g applications. The Si532 3 and Si536 6

are pin-controlled jitter-attenuating clock multipliers. The frequency plan for these pin-controlled devices is

selectable from frequency lookup tables and includes common frequency translations for SONET/SDH, ITU G.709

Forward Error Correction (FEC) applications (255/238, 255/237, 255/236, 238/255, 237/255, 236/255), Gigabit

Ethernet, 10G Ethernet, 1G/2G/4G/8G/10G Fibre Channel, ATM and broadcast video (Genlock). The Si5319,

Si5324, Si5326, Si5327, Si5328, Si5368, and Si5369 are microprocessor-controlled devices that can be controlled

via an I

710 MHz and generate multiple independent, synchronous clock outputs ranging from 2 kHz to 945 MHz and

select frequencies to 1.4 GHz. Virtually any frequency translation combination across this operating range is

supported. Independent dividers are available for every input clock and output clock, so the Si5324, Si5326,

Si5327, Si5328, and Si5368 can accept input clocks at different frequencies and generate output clocks at different

frequencies. The Si5316, Si5319, Si5323, Si5326, Si5366, Si5368, and Si5369 support a digitally programmable

loop bandwidth that can range from 60 Hz to 8.4 kHz. An external (37–41 MHz, 55–61 MHz, and 109–125.5 MHz)

reference clock or a low-cost 114.285 MHz 3rd overtone crystal is required for these devices to enable ultra-low

jitter generation and jitter attenuation. (See "Appendix A—Narrowband References" on page 108.) The Si5324,

Si5327, and Si5369 are much lower bandwidth devices, providing a user-programmable loop bandwidth from 4 to

525 Hz. The Si5328 is an ultra-low-loop BW device that is intended for SyncE timing card applications (G.8262)

with loop BW values of from 0.05 to 6 Hz.

The Si5323, Si5324, Si5326, Si5327, Si5328, Si5366, Si5368, and Si5369 support hitless switching between input

clocks in compliance with GR-253-CORE and GR-1244-CORE that greatly minimizes the propagation of phase

transients to the clock outputs during an input clock transition (<200 ps typ). Manual, automatic revertive and

automatic non-revertive input clock switching options are available. The devices monitor the input clocks for lossof-signal and provide a LOS alarm when missing pulses on any of the input clocks are detected. The devices

monitor the lock status of the PLL and provide a LOL alarm when the PLL is unlocked. The lock detect algorithm

works by continuously monitoring the phase of the selected input clock in relation to the phase of the feedback

clock. The Si5324, Si5326, Si5328, Si5366, Si5368, and Si5369 monitor the frequency of the input clocks with

respect to a reference frequency applied to an input clock or the XA/XB input, and generates a frequency offset

alarm (FOS) if the threshold is exceeded. This FOS feature is available for SONET/SDH applications. Both Stratum

3/3E and SONET Minimum Clock (SMC) FOS thresholds are supported.

The Si5319, Si5323, Si5324, Si5326, Si5328, Si5366, Si5368, and Si5369 provide a digital hold capability that

allows the device to continue gen eration of a s table output clock when the select ed input refe rence is los t. During

digital hold, the DSPLL generates an o utput frequency base d on a histor ical average tha t existed a fixed amount of

time before the error event occurred, eliminating the effects of phase and frequency transients that may occur

immediately preceding entry into digital hold.

The Si5322, Si5325, Si5365, and Si5367 are frequency flexible, low jitter clock multipliers that provide jitter

generation of 0.6 ps RMS without jitter attenuation. These devices provide low jitter integer clock multiplication or

fractional clock synthesis, but they are not as frequency-flexible as the Si5319/23/24/26/66/68/69. The devices

vary according to the number of clock inputs, number of clock ou tput s, and co ntrol method . The Si5322 and Si5365

are pin-controlled clock multipliers. The frequency plan for these devices is selectable from frequency lookup

2

C or SPI interface. These microprocessor-controlled devices accept clock inputs ranging from 2 kHz to

12 Rev. 1.2

Page 13

Si53xx-RM

tables.

A wide range of settings are available, but they are a subset of the frequency plans supported by the Si5323 and

Si5366 jitter-attenuating clock multipliers. The Si5325 and Si5367 are microprocessor-controlled clock multipliers

that can be controlled via an I

These devices accept clock inputs ranging from 10 MHz to 710 MHz and generate multiple independent,

synchronous clock outputs ranging from 10 MHz to 945 MHz and select frequencies to 1.4 GHz. The Si5325 and

Si5367 support a subset of the frequen cy translations available in the Si5319, Si5 324, Si5326, Si5327, Si5 368, and

Si5369 jitter-attenuating clock multipliers. The Si5325 and Si5367 can accept input clocks at different frequencies

and generate output clocks at different frequencies. The Si5322, Si5325, Si5365, and Si5367 support a digitally

programmable loop bandwidth that ranges from 150 kHz to 1.3 MHz. No external components are required for

these devices. LOS and FOS monitoring is available for these devices, as described above.

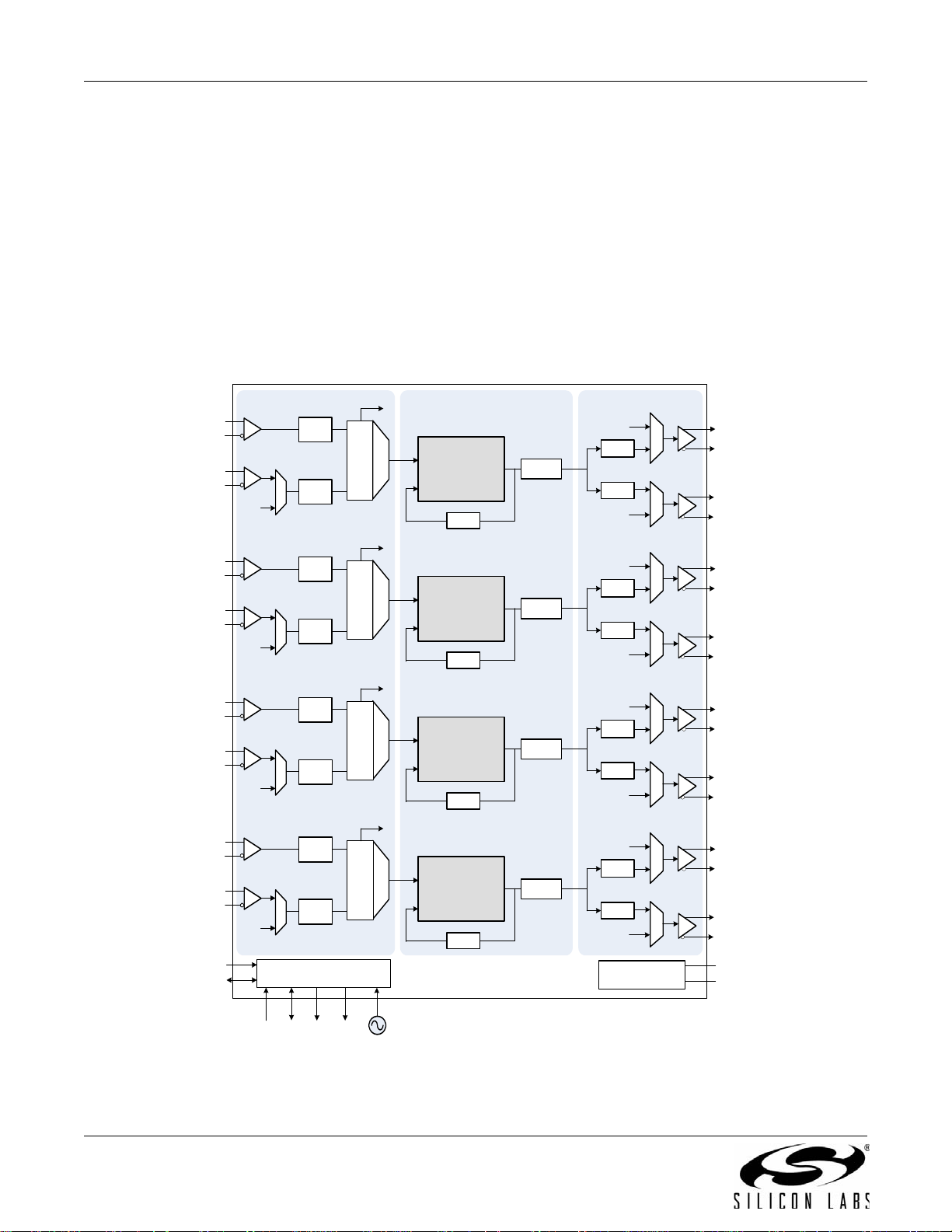

The Si5374, Si5375, and Si5376 are quad DSPLL versions of the Si5324, Si5319, and Si5326, respectively. Each

of the four DSPLLs can oper ate at comple tely independ ent frequencies. The only resources that they share are a

common I

reference source. Since they require a require a free standing reference oscillator, the XA/XB reference pins were

renamed to OSC_P and OSC_N. The Si5375 consists of four one-input and one-output DSPLLs. The Si5374

consists of four two-input and two-output DSPLLs with very low loop bandwid th. The Si5376 is similar to the Si5374

with the exception that it has higher loop BW values.

The Any-Frequency Precision Clocks have dif fere ntial clock ou tp ut(s) with pr ogr ammab le sign al for mats to support

LVPECL, LVDS, CML, and CMOS loads. If the CMOS signal format is selected, each differential output buffer

generates two in-phase CMOS clocks at the same frequency. For system-level debugging, a PLL bypass mode

drives the clock output directly from the selected input clock, bypassing the internal PLL.

Silicon Laboratories offers a PC-based software utility, DSPLLsim, that can be used to determine valid frequency

plans and loop bandwidth settings for the Any-Frequency Precision Clock product family. For the microprocessorcontrolled devices, DSPLLsim provides the optimum PLL divider settings for a given input frequency/clock

multiplication ratio combination that minimizes phase noise and power consumption. Two DSPLLsim configuration

software applications are available for the 1-PLL and 4-PLL devices, respectively. DSPLLsim can also be used to

simplify device selection and configuration. This utility can be downloaded from http://www.silabs.com/timing.

Other useful documentation, including device data sheets and programming files for the microprocessor-controlled

devices are available from this website.

2

C bus and a common XA/XB jitter reference oscillator. These quad devices cannot use a crystal as their

2

C or SPI interface.

Rev. 1.2 13

Page 14

Si53xx-RM

Table 1. Product Selection Guide

Part

Number

Si5315 Pin 1PLL, 2 | 2 0.008–644 0.008–644 0.45 ps

Si5316 Pin 1PLL, 2 | 1 19–710 19–710 0.3 ps

Si5317 Pin 1PLL, 1 | 2 1–710 1–710 0.3 ps

Si5319 I

Si5323 Pin 1PLL, 2 | 2 0.008–707 0.008–1050 0.3 ps

Si5324 I

Si5326 I2C/SPI 1PLL, 2 | 2 0.002–710 0.002–1417 0.3 ps

Si5327 I2C/SPI 1PLL, 2 | 2 0.002–710 0.002–808 0.5 ps

Si5328 I

Control Number of

Inputs and

Outputs

2

C/SPI 1PLL, 1 | 1 0.002–710 0.002–1417 0.3 ps

2

C/SPI 1PLL, 2 | 2 0.002–710 0.002–1417 0.3 ps

2

C/SPI 1PLL, 2 | 2 0.008–346 0.002–346 0.35 ps

Input

Frequency

(MHz)

*

Output

Frequency

(MHz)

*

RMS Phase Jitter

(12kHz–20MHz)

PLL

Bandwidth

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

4 Hz to

525 Hz

60 Hz to

8kHz

4 Hz to

525 Hz

0.05 Hz to

6Hz

Hitless

Switching

Free

Run

Mode

Package

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

Si5366 Pin 1PLL, 4 | 5 0.008–707 0.008–1050 0.3 ps

Si5368 I2C/SPI 1PLL, 4 | 5 0.002–710 0.002–1417 0.3 ps

2

Si5369 I

Si5374 I2C 4PLL, 8 | 8 0.002–710 0.002–808 0.4 ps

Si5375 I2C 4PLL, 4 | 4 0.002–710 0.002–808 0.4 ps

Si5376 I

*Note: Maximum input and output rates may be limited by speed rating of device. See each device’s data sheet for ordering

C/SPI 1PLL, 4 | 5 0.002–710 0.002–1417 0.3 ps

2

C 4PLL, 8 | 8 0.002–710 0.002–808 0.4 ps

information.

60 Hz to

8kHz

60 Hz to

8kHz

4 Hz to

525 Hz

4 Hz to

525 Hz

60 Hz to

8kHz

60 Hz to

8kHz

14x14 mm

100-TQFP

14x14 mm

100-TQFP

14x14 mm

100-TQFP

10x10 mm

80-BGA

10x10 mm

80-BGA

10x10 mm

80-BGA

14 Rev. 1.2

Page 15

Si53xx-RM

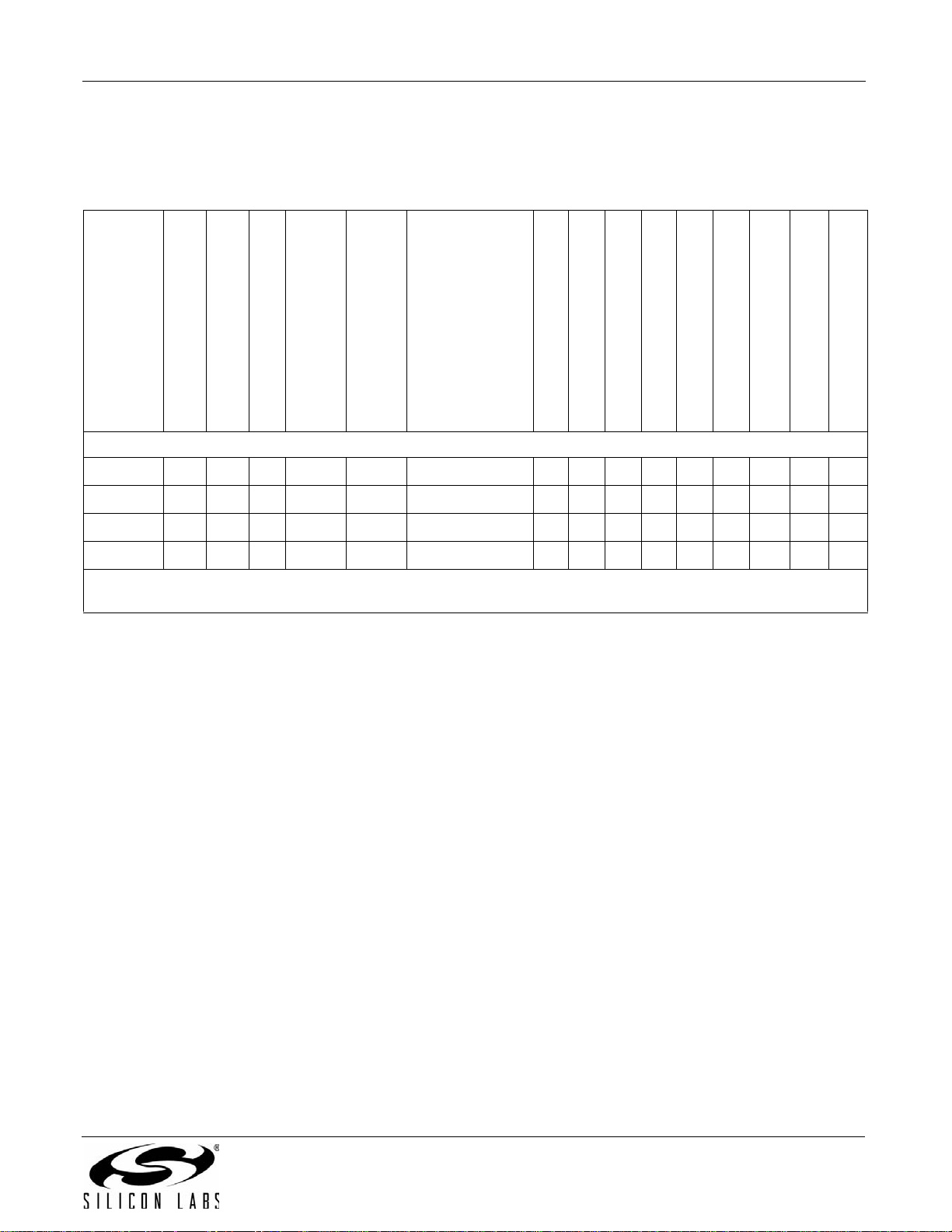

2. Wideband Devices

These are not recommended for new designs. For alternatives, see the Si533x family of products.

Table 2. Product Selection Guide (Si5322/25/65/67)

*

Device

Low Jitter Precision Clock Multipliers (Wideband)

Si5322 2 2 707 1050 0.6 ps rms typ

Si5325 2 2

Si5365 4 5 707 1050 0.6 ps rms typ

Si5367 4 5

*Note: Maxi mum input and output rates may be limited by speed rating of device. See each device’s data sheet for ordering

information.

Clock Inputs

Clock Outputs

P Control

Max Input Freq (MHz)

Max Output Frequency (MHz)

Jitter Generation

(12 kHz – 20 MHz)

LOS

Hitless Switching

FOS Alarm

LOL Alarm

FSYNC Realignment

36 Lead 6 mm x 6 mm QFN

100 Lead 14 x 14 mm TQFP

1.8, 2.5, 3.3 V Operation

1.8, 2.5 V Operation

710 1400 0.6 ps rms typ

710 1400 0.6 ps rms typ

2.1. Narrowband vs. Wideband Overview

The narrowband (NB) devices offer a number of features and capabilities that are not available with the wideband

(WB) devices, as outlined in the below list:

Broader set of frequency plans due to more divisor options

Hitless switching between input clocks

Lower minimum input clock frequency

Lower loop bandwidth

Digital Hold (reference-based holdover instead of VCO freeze)

FRAMESYNC realignment

CLAT and FLAT (input to output skew adjust)

INC and DEC pins

PLL Loss of Lock status indicator

FOS is not supported.

Rev. 1.2 15

Page 16

Si53xx-RM

2

DSPLL

®

C1B

CS

LOL

BWSEL[1:0]

DBL_BY

Xtal or Refclock

SFOUT[1:0]

CKOUT+

CKOUT–

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

Control

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

FRQSEL[1:0]

RST

0

1

RATE[1:0]

XA

XB

f

OSC

2

0

1

÷ N31

÷ N32

f

3_1

f

3_2

CK1DIV

CK2DIV

f

3

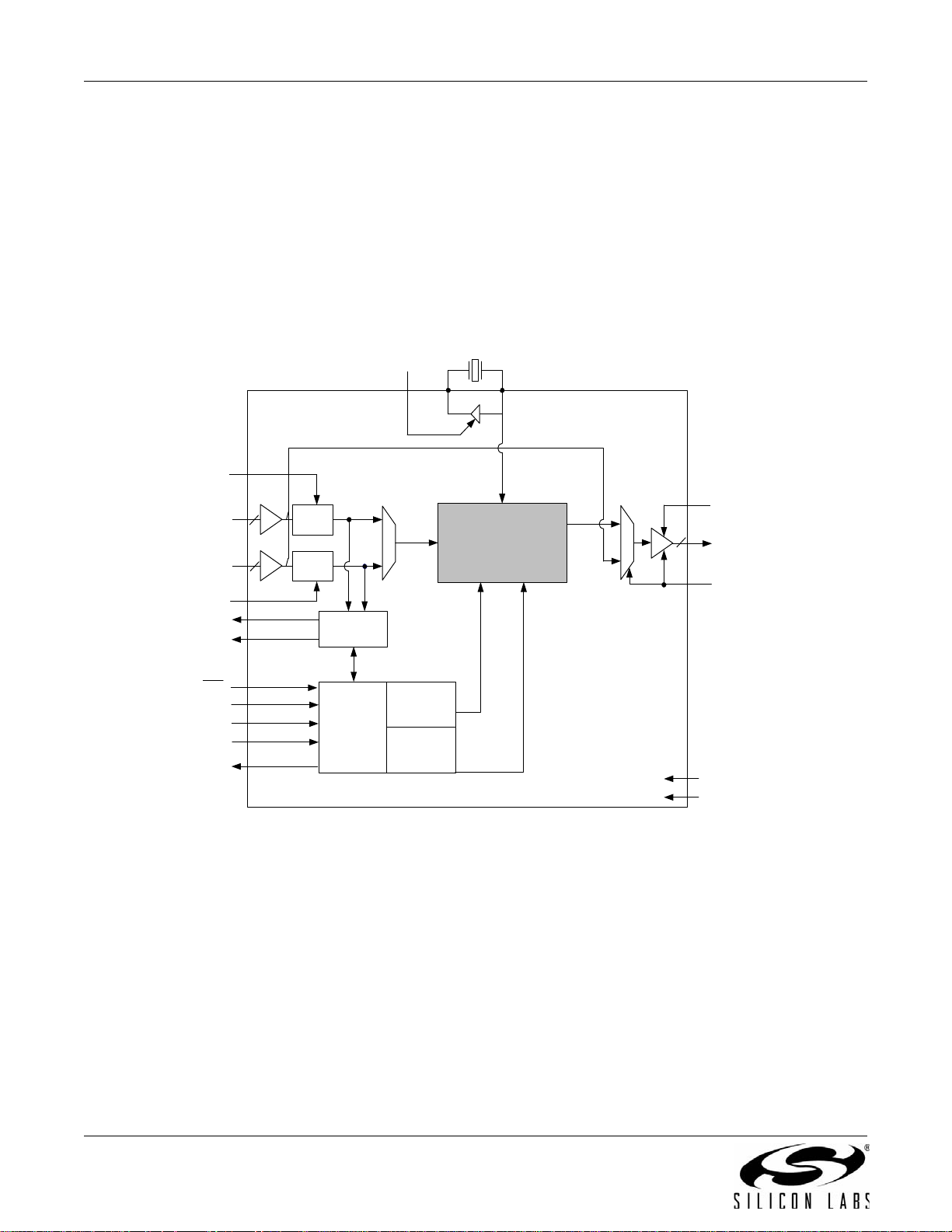

3. Any-Frequency Clock Family Members

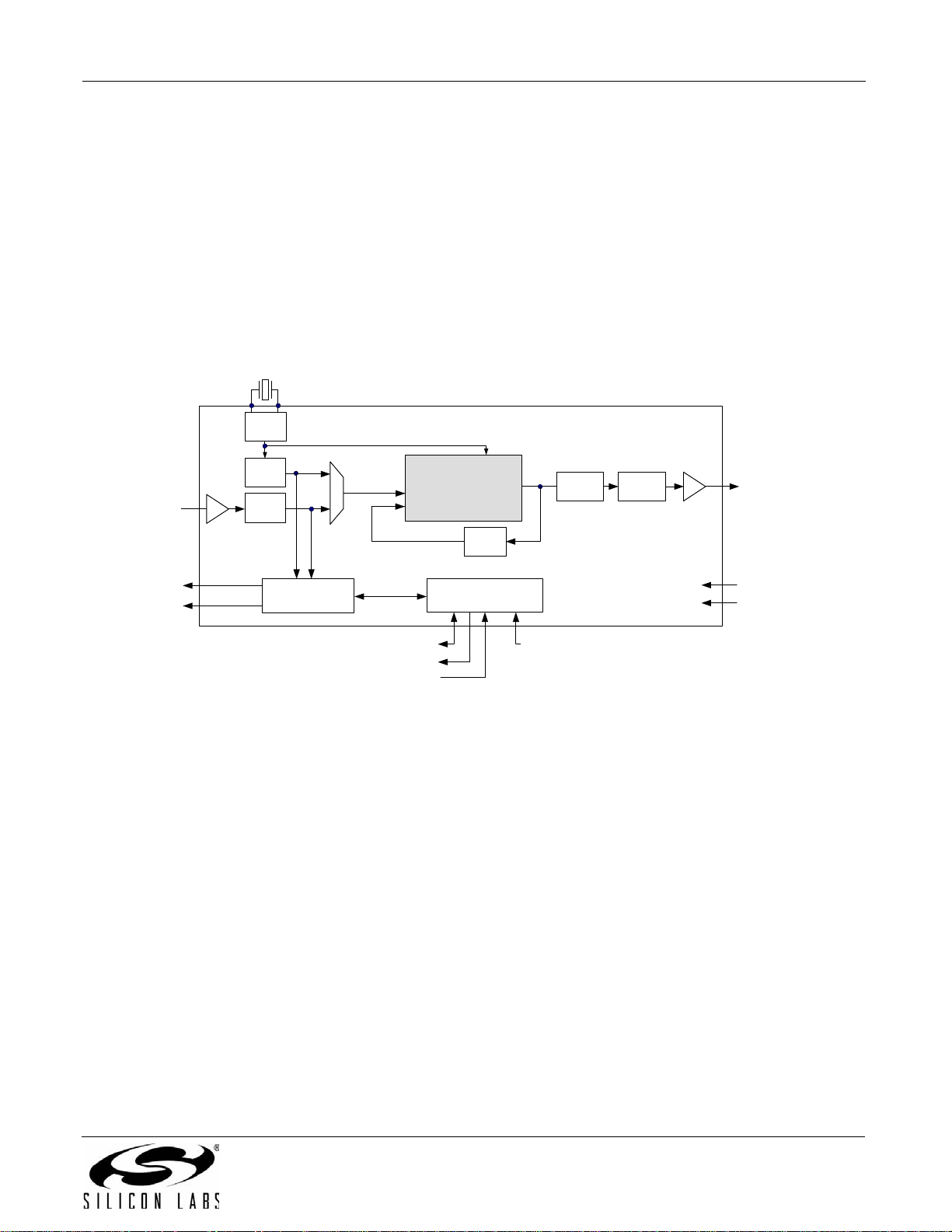

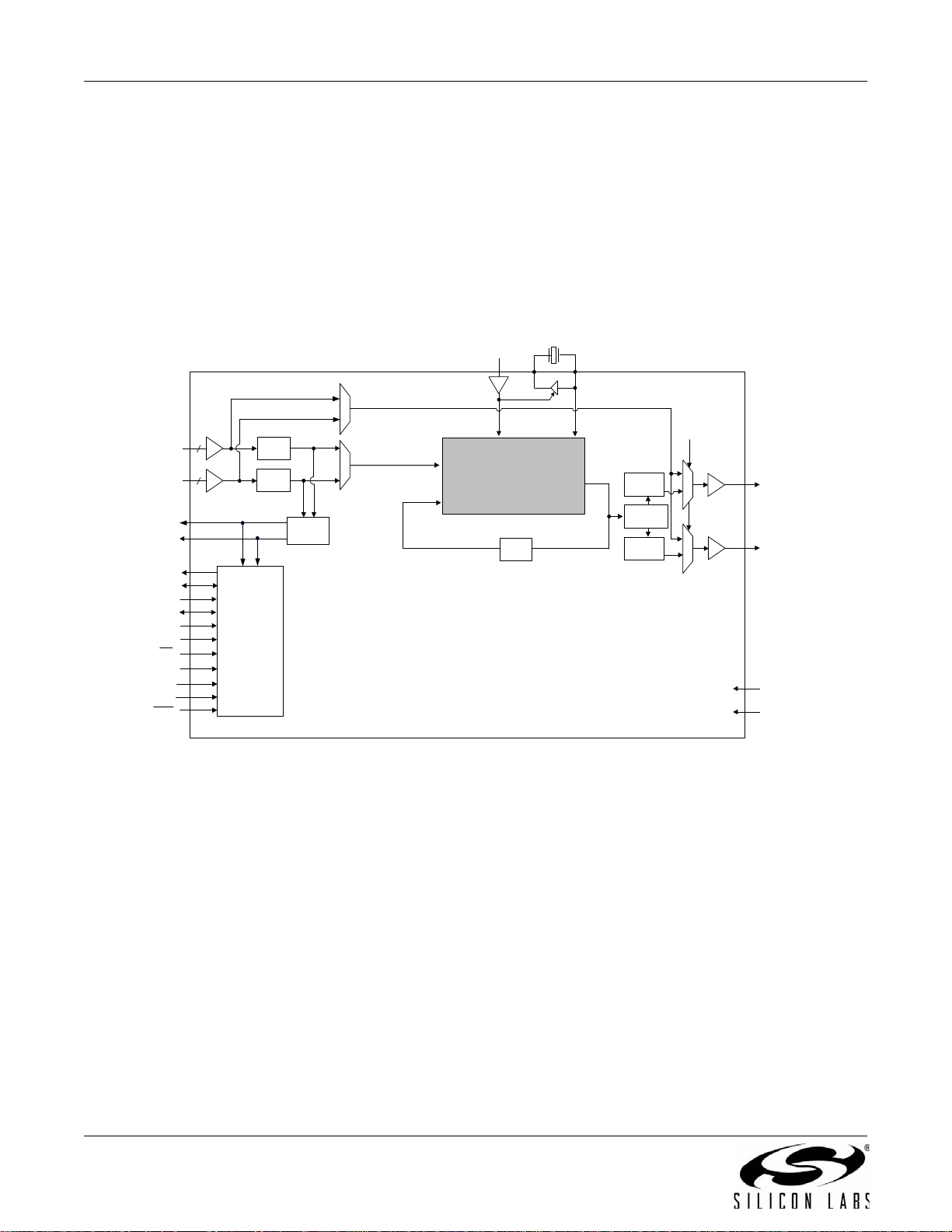

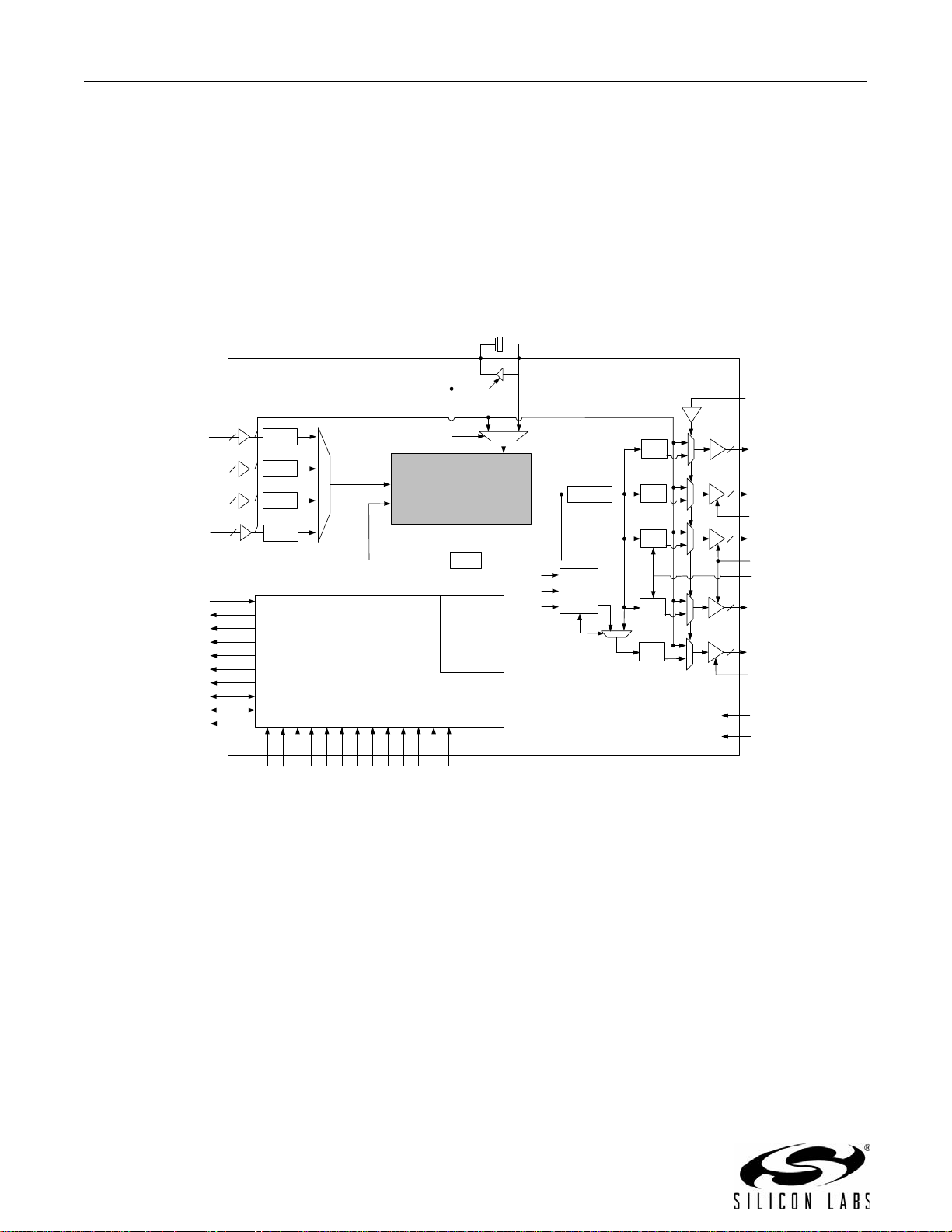

3.1. Si5316

The Si5316 is a low jitter, precision jitter attenuator for high-speed communication systems, including OC -48, OC192, 10G Ethernet, and 10G Fibre Channel. The Si5316 accepts dual clock inputs in the 19, 38, 77, 155, 311, or

622 MHz frequency range and generates a jitter-attenuated clock output at the same frequency. Within each of

these clock ranges, the device can be tuned approximately 14% higher tha n nomin al SONET/SDH fre quencies, up

to a maximum of 710 MHz in the 622 MHz range. The DSPLL loop bandwidth is digitally selec table, pr ov idin g jitte r

performance optimization at the application level. Operating fr om a single 1.8, 2.5, or 3.3 V supply, the Si5316 is

ideal for providing jitter attenuation in high performance timing applications. See "5. Pin Control Parts (Si5316,

Si5322, Si5323, Si5365, Si5366)" on page 37 for a complete description.

Figure 1. Si5316 Any-Frequency Jitter Attenuator Block Diagram

16 Rev. 1.2

Page 17

Si53xx-RM

DSPLL

®

Loss of Signal

Xtal or Refclock

CKIN

CKOUT

÷ N31

÷ N2

Signal Detect

Device Interrupt

VDD

GND

Loss of Lock

Xtal/Clock Select

I

2

C/SPI Port

Control

Rate Select

÷ N32

XO

f

3

÷ N1_HS ÷ NC1

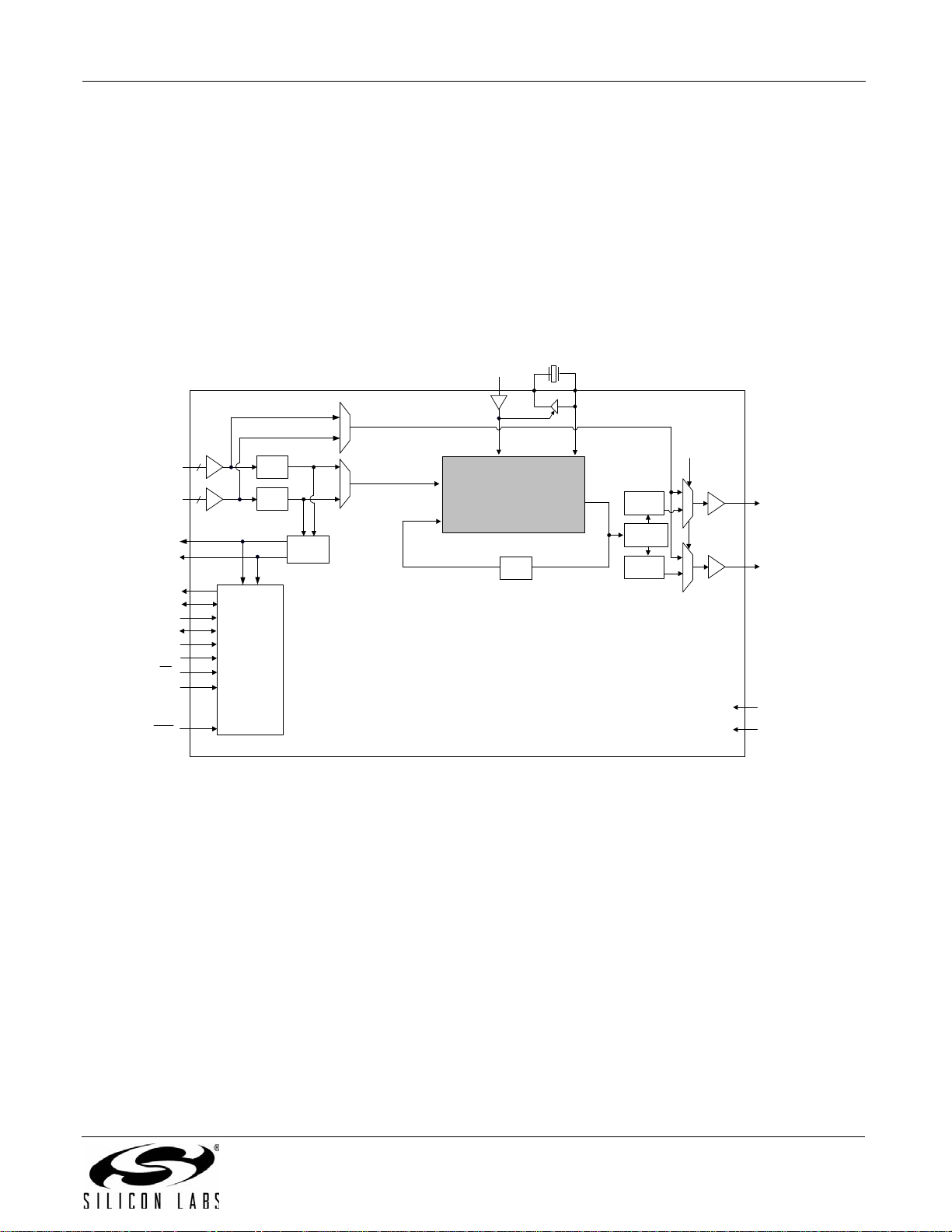

3.2. Si5319

The Si5319 is a jitter-attenuating precision M/N clock multiplier for applications requiring sub 1 ps jitter

performance. The Si5319 accepts one clock input ranging from 2 kHz to 710 MHz and generates one clock output

ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The Si5319 can also use its crystal oscillator as

a clock source for frequency synthesis. The device provides virtua lly any frequency translation combination across

this operating range. The Si5319 input clock frequency and clock multiplication r atio are programmable through an

I2C or SPI interface. The Si5319 is based on Silicon Laboratories' 3rd-generation DSPLL

provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need

for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing

jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5319

is ideal for providing clock multiplication and jitter attenuation in high performance timing applications. See "6.

Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369,

Si5374, Si5375, and Si5376)" on page 63 for a comp lete description.

®

technology, which

Figure 2. Si5319 Any-Frequency Jitter Attenuating Clock Multiplier Block Diagram

Rev. 1.2 17

Page 18

Si53xx-RM

DSPLL

®

C1B

CS_CA

BWSEL[1:0]

DBL2_BY

SFOUT[1:0]

CKOUT_2+

CKOUT_2–

CKIN_1+

CKIN_1–

CKOUT_1+

CKOUT_2–

CKIN_2+

CKIN_2–

Control

AUTOSEL

FRQTBL

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

2

FRQSEL[3:0]

RST

0

1

f

OSC

2

2

0

1

0

1

f

3

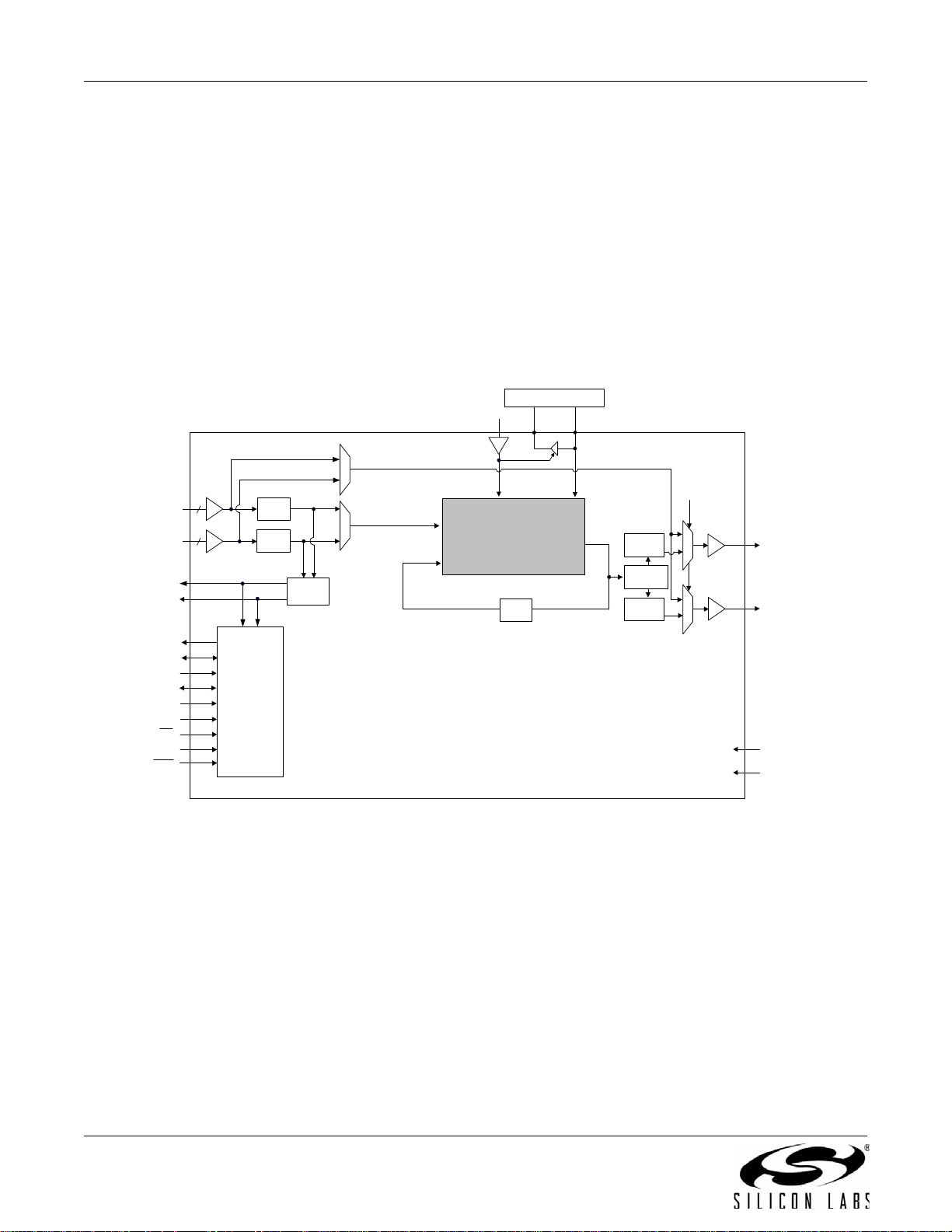

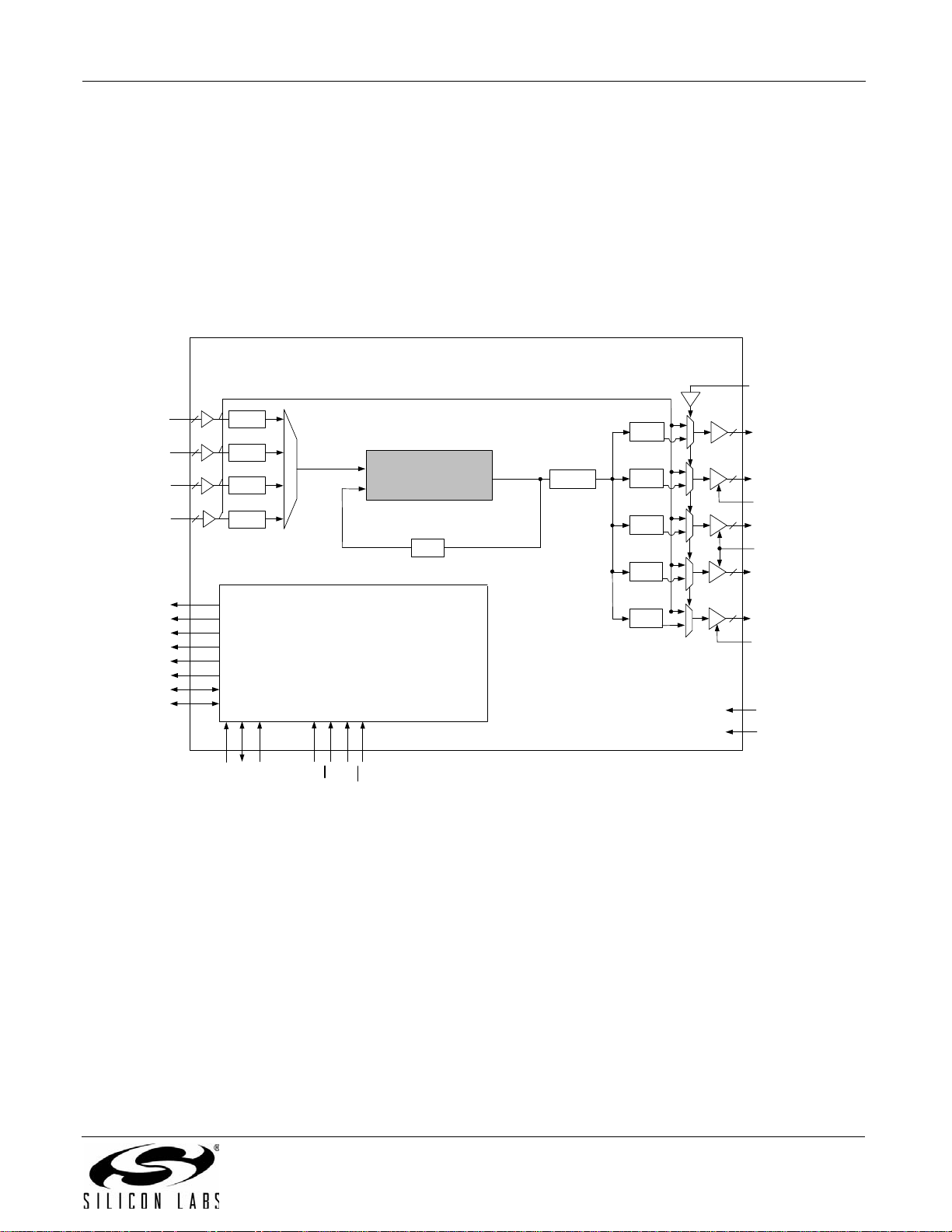

3.3. Si5322

The Si5322 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5322 acce pts dual clock inputs ranging from 19.44 to 707 MHz and generates two frequencymultiplied clock outputs ranging from 19.44 to 1050 MHz. The input clock frequency and clock multiplication ratio

are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI)

rates. The DSPLL loop bandwidth is digitally selectable from 150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5,

or 3.3 V supply, the Si5322 is ideal for providing low jitter clock multiplication in high performance timing

applications. See "5. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)" on page 37 for a complete

description.

Figure 3. Si5322 Low Jitter Clock Multiplier Block Diagram

Note: Not recommended for new designs. For alternatives, see the Si533x family of products.

18 Rev. 1.2

Page 19

Si53xx-RM

DSPLL

®

C1B

LOL

CS/CA

BWSEL[1:0]

DBL2/BY

Xtal or R e fc lo ck

SFOUT[1:0]

CKOUT_2+

CKOUT_2–

CKIN_1+

CKIN_1–

CKOUT_1+

CKOUT_1–

CKIN_2+

CKIN_2–

Control

AUTOSEL

FRQTBL

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

2

FRQSEL[3:0]

INC

DEC

RST

0

1

RATE[1:0]

XA

XB

f

OSC

2

2

0

1

0

1

f

3

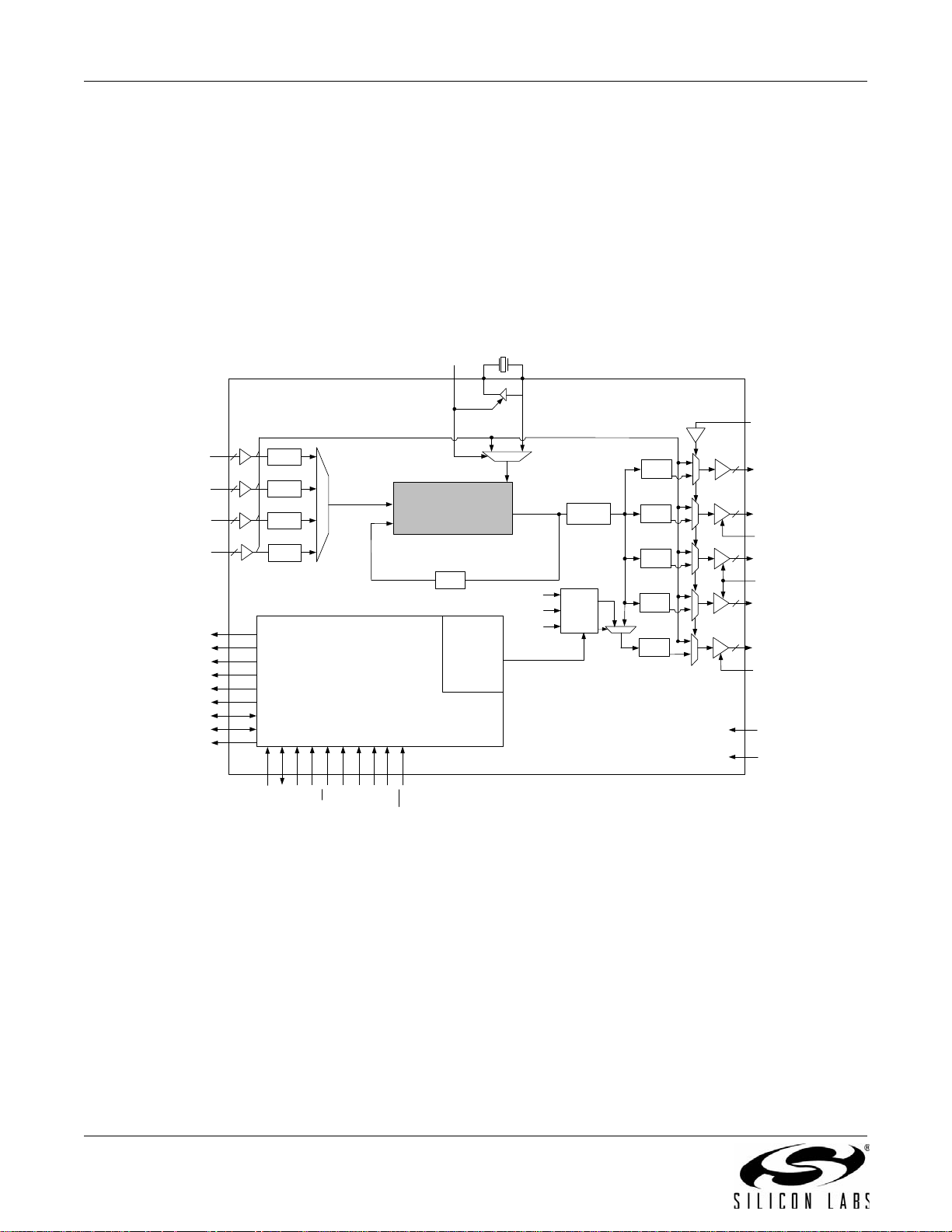

3.4. Si5323

The Si5323 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including

SONET OC-48/OC-192, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI). The Si5323 accepts

dual clock inputs ranging from 8 kHz to 707 MHz and generates two frequency-multiplied clock outputs ranging

from 8 kHz to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of

popular SONET, Ethernet, Fibre Channel, and broadcast video rates. The DSPLL loop bandwidth is digitally

selectable, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or

3.3 V supply, the Si5323 is ideal for providing clock multiplication and jitter attenuation in high-performance timing

applications. See "5. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)" on page 37 for a complete

description.

Rev. 1.2 19

Figure 4. Si5323 Jitter Attenuating Clock Multiplier Block Diagram

Page 20

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0 ]

LOL

CS_CA

SDA_SDO

INC

DEC

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

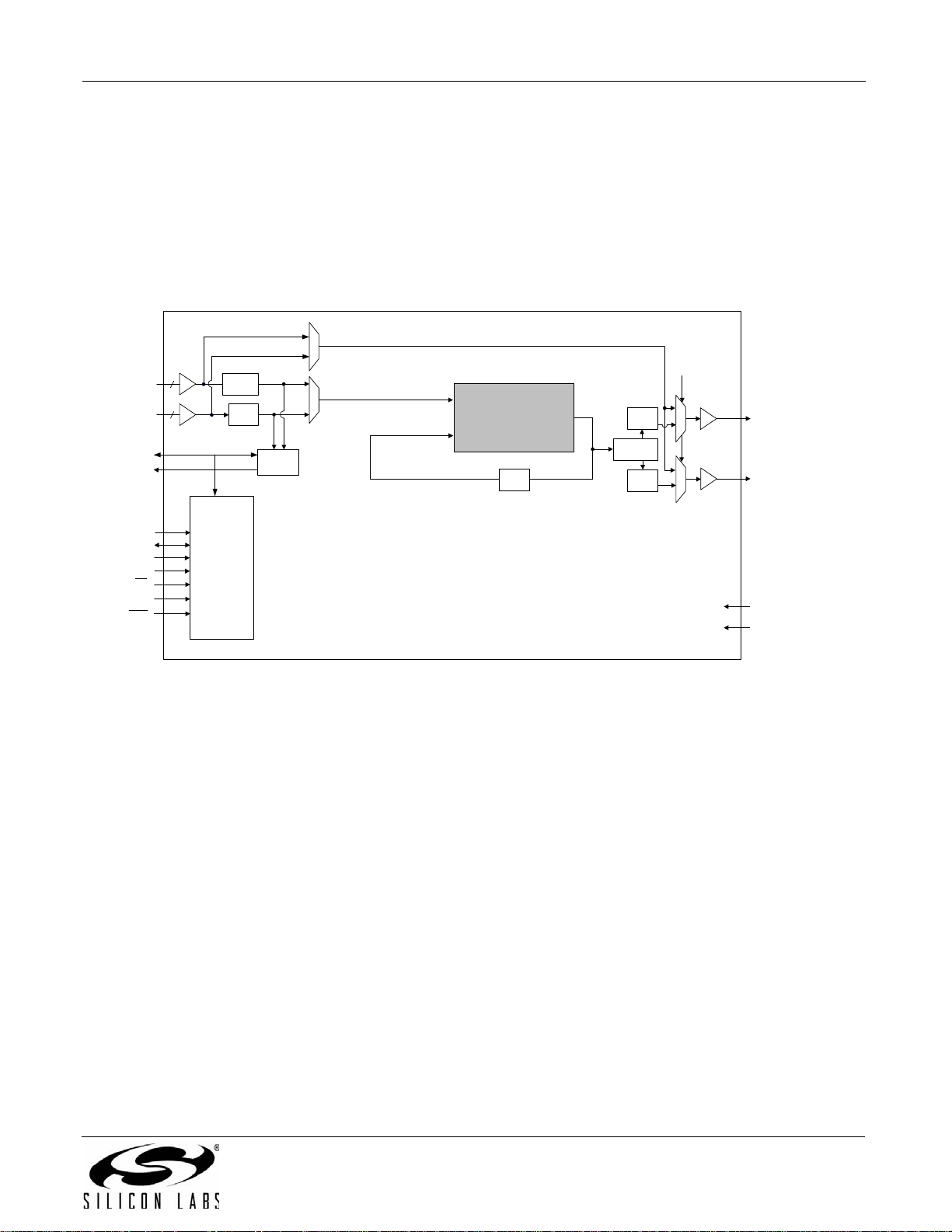

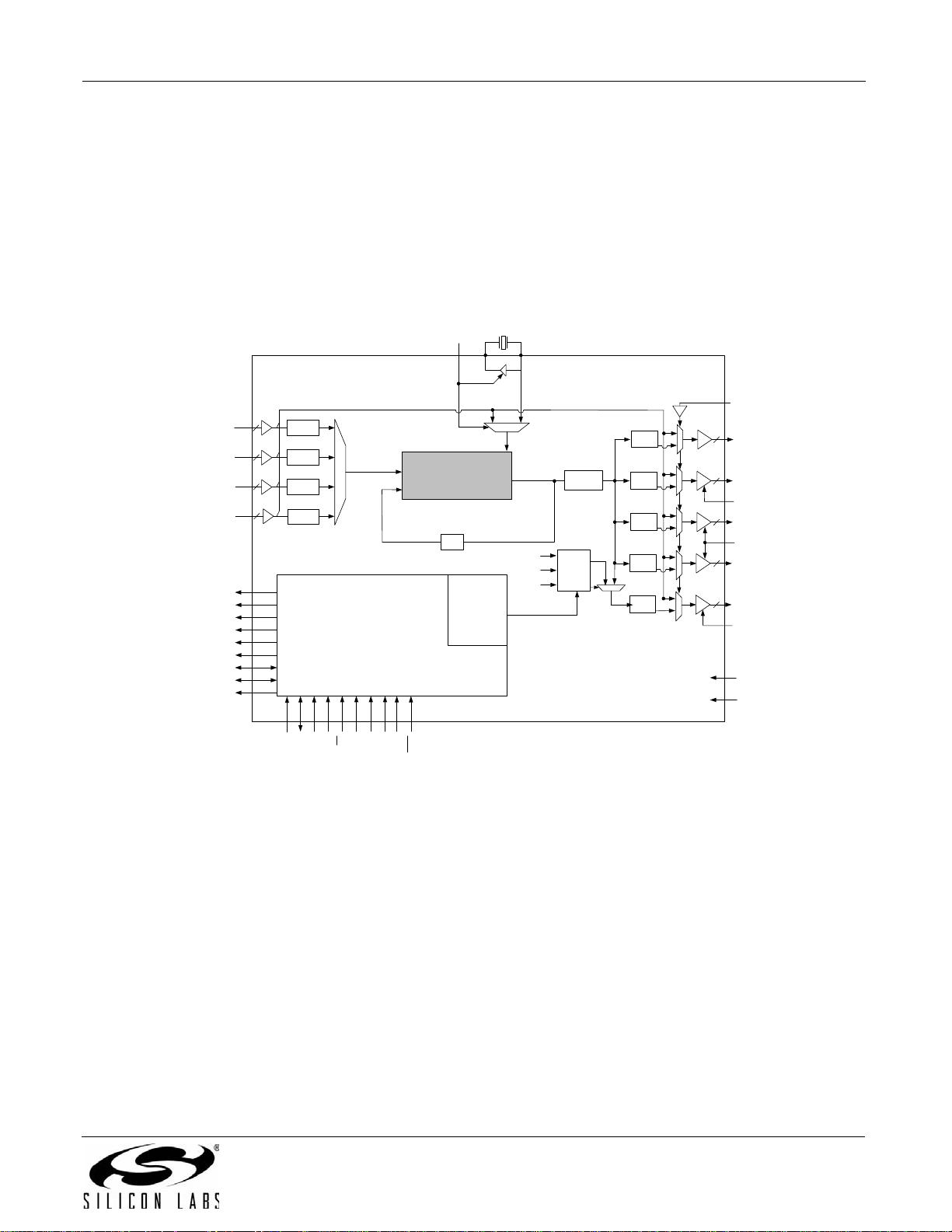

3.5. Si5324

The Si5324 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5324 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides

virtually any frequency translation combination across this operating range. The Si5324 input clock frequency and

clock multiplication ratios are programmable th rough an I

programmable, providing jitter performance optimization at the application level. The Si5324 features loop

bandwidth values as low as 4 Hz. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5324 is ideal for providing

clock multiplication and jitter attenuation in high-performance timing applications. See "6. Microprocessor

Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and

Si5376)" on page 63 for a complete description.

2

C or SPI interface. The DSPLL loop bandwid th is digit ally

Figure 5. Si5324 Clock Multiplier and Jitter Attenuator Block Diagram

20 Rev. 1.2

Page 21

Si53xx-RM

÷ N31

INT_C1B

÷ NC1

÷ NC2

Signal

Detect

C2B

0

1

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

SDA_SDO

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

CMODE

CKIN_1 +

CKIN_1 –

2

2

CKIN_2 +

CKIN_2 –

÷ N32

0

1

BYPASS

÷ N2

f

3

DSPLL

®

VDD

GND

÷ N1_HS

f

OSC

3.6. Si5325

The Si5325 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5325 accepts dual clock inputs ranging from 10 to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The Si5325 input

clock frequency and clock multiplication ratios are programmable through an I

bandwidth is digitally program mable from 150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5, or 3.3 V supply, the

Si5325 is ideal for providing clock multiplication in high performance timing applications. See "6. Microprocessor

Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and

Si5376)" on page 63 for a complete description.

2

C or SPI interface. The DSPLL loop

Figure 6. Si5325 Low Jitter Clock Multiplier Block Diagram

Note: Not recommended for new designs. For alternatives, see the Si533x family of products.

Rev. 1.2 21

Page 22

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0]

LOL

CS_CA

SDA_SDO

INC

DEC

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

3.7. Si5326

The Si5326 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5326 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides

virtually any frequency translation combination across this operating range. The Si5326 input clock frequency and

clock multiplication ratios are programmable th rough an I

programmable from 60 Hz to 8 kHz, providing jitter performance optimization at the application level. Operating

from a single 1.8, 2.5, or 3.3 V supply, the Si5326 is ideal for providing clock multiplication and jitter atte nuation in

high-performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326,

Si5327, Si5328, Si5367, Si5368, Si5369, Si5374, Si5375, and Si5376)" on page 63 for a complete description.

2

C or SPI interface. The DSPLL loop bandwid th is digit ally

Figure 7. Si5326 Clock Multiplier and Jitter Attenuator Block Diagram

22 Rev. 1.2

Page 23

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0 ]

LOL

CS

SDA_SDO

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

3.8. Si5327

The Si5327 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5327 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 808 MHz. The device provides virtually any frequency translation

combination across this operating range. The Si5327 input clock frequency and clock multiplication ratios are

programmable through an I

jitter performance optimization at the application level. The Si5327 features loop bandwidth values as low as 4 Hz.

Operating from a single 1.8, 2. 5, or 3.3 V supply, the Si5327 is ideal for providing clock multiplication and jitter

attenuation in high-performance timing applications. See "6. Microprocessor Controlled Parts (Si5319, Si5324,

Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si53 69, Si5374, Si5 375, a nd Si5376)" on page 63 for a complete

description.

2

C or SPI interface. The DSPLL loop bandwidth is digitally programmable, providing

Figure 8. Si5327 Clock Multiplier and Jitter Attenuator Block Diagram

Rev. 1.2 23

Page 24

Si53xx-RM

÷ N31

INT_C1B

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0]

CS_CA

RST

Control

XA

XB

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

TCXO or Refclock

A[1:0]

A[2]/SS

SDI

SCL

SDA_SDO

CMODE

LOL

3.9. Si5328

The Si5328 is a jitter-attenuating precision clock multiplier for applications requiring sub-1 ps jitter performance and

digitally-programmable ultra-low-loop BW ranging from 0.05 to 6 Hz. When combined with a low-wander, low-jitter

reference oscillator, the Si5328 meets all of the wander, MTIE, TDEV, and other requirements that are listed in ITUT G.8262. The Si5328 accepts two input clocks ranging from 8 kHz to 346 MHz and generates two output clocks

ranging from 2 kHz to 346 MHz. The device provides virtually any frequency translation combination across the

operating range. The Si5328 input clock frequency and clock multiplication ratio are programmable through and

2

C or SPI interface. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5328 is ideal for providing multiplication

I

and jitter/wander attenuation in high-performance timing applications like SyncE timing cards. See "6.

Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5328, Si5367, Si5368, Si5369,

Si5374, Si5375, and Si5376)" on page 63 for a complete description. Also see “AN775: Si5328 ITU-T G.8261

SyncE Compliance Test Report" and “AN776: Using the Si5328 in a G.8262 Compliant SyncE Application".

Figure 9. Si5328 Clock Multiplier and Jitter Attenuator Block Diagram

24 Rev. 1.2

Page 25

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

ALRMOUT

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

f

3

DBL2_BY

DBL34

DBL5

BWSEL[1:0]

FRQSEL[3:0]

DIV34[1:0]

FOS_CTL

SFOUT[1:0]

RST

CMODE

AUTOSEL

BYPASS/

DSBL2

Control

÷ N3_2

÷ N3_1

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

FRQTBL

DIV34[1:0]

÷ N1_HS

DSPLL

®

÷ N2

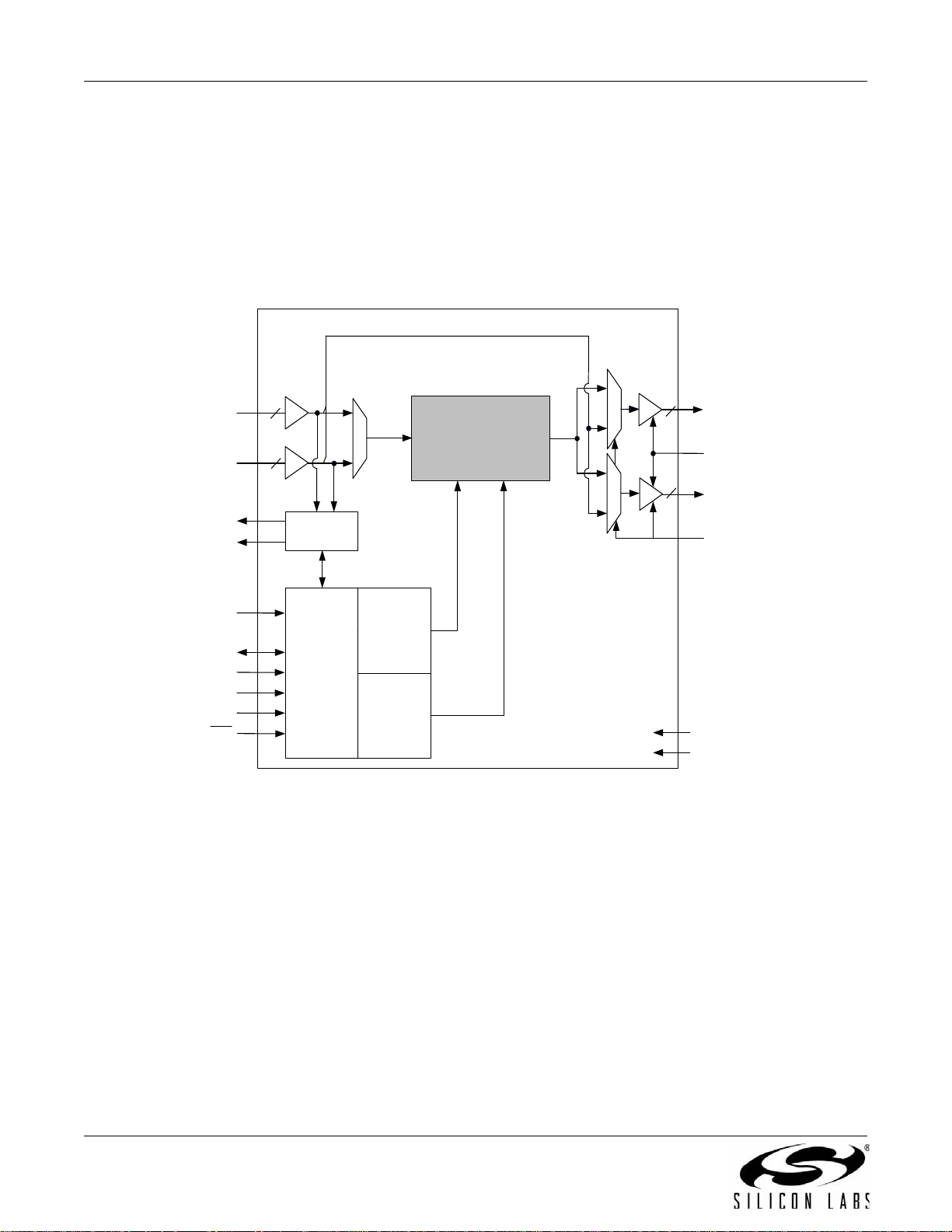

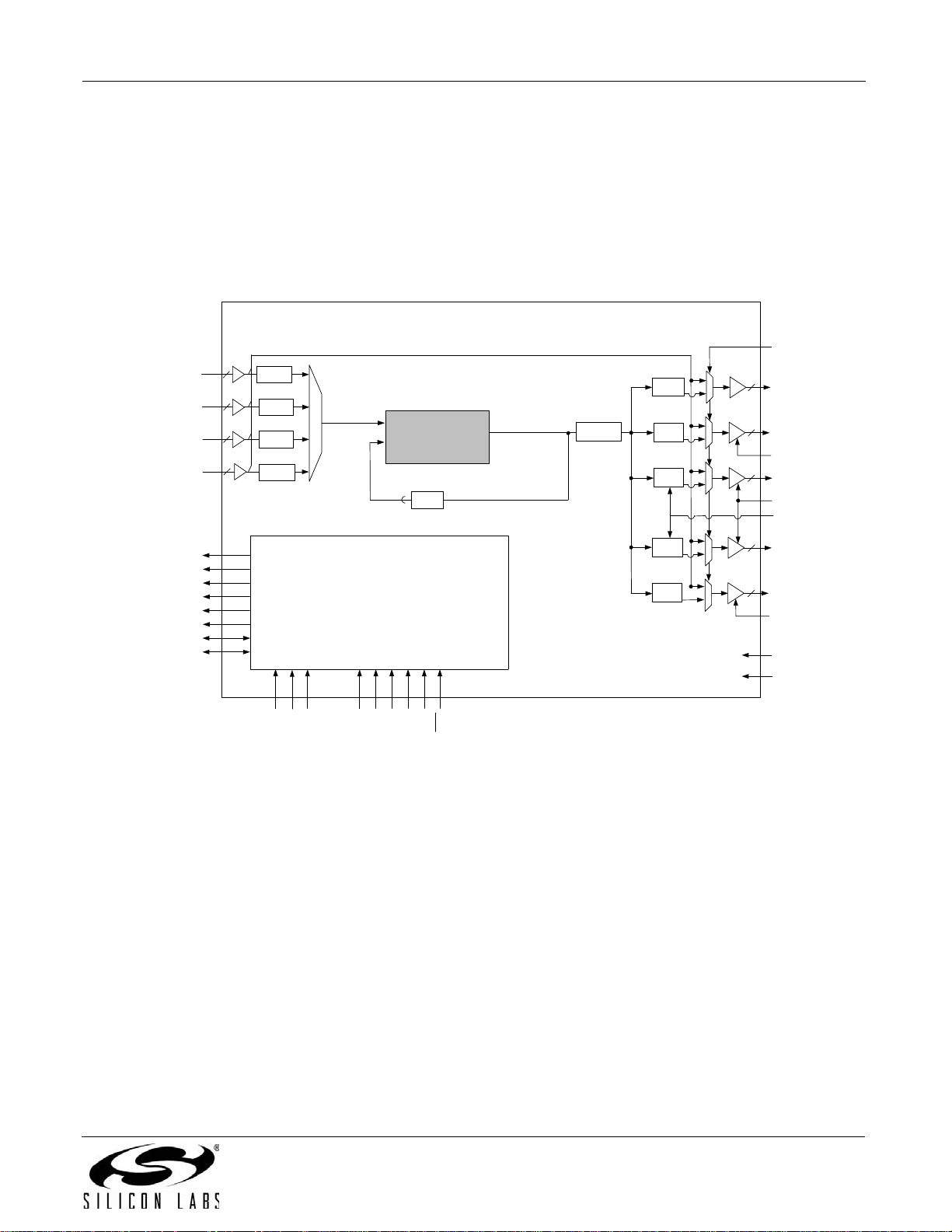

3.10. Si5365

The Si5365 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5365 accepts four clock inputs ranging from 19.44 MHz to 707 MHz and generates five

frequency-multiplied clock outputs ranging from 19.44 MHz to 1050 MHz. The input clock frequency and clock

multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video

rates. The DSPLL loop bandwidth is digitally selectable. Operating from a single 1.8, 2.5 V, or 3.3 V supply, the

Si5365 is ideal for providing clock multiplication in high performance timing applications. See "5. Pin Control Parts

(Si5316, Si5322, Si5323, Si5365, Si5366)" on page 37 for a complete descr iption.

Figure 10. Si5365 Low Jitter Clock Multiplier Block Diagram

Rev. 1.2 25

Note: Not recommended for new designs. For alternatives, see the Si533x family of products.

Page 26

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

ALRMOUT

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

CKIN_3

CKIN_4

CKOUT_2

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

Xtal or Refclock

RATE[1:0]

XA

XB

f

x

f

3

DBL2_BY

DBL34

DBL5

FSYNC

LOGIC/

ALIGN

CK_CONF

BWSEL[1:0]

FRQSEL[3:0]

DIV34[1:0]

FOS_CTL

SFOUT[1:0]

INC

DEC

FS_SW

FS_ALIGN

RST

CMODE

AUTOSEL

BYPASS/DSBL2

LOL

Control

÷ N3_2

÷ N3_1

FSYNC

3

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

1

0

FRQTBL

DIV34[1:0]

÷ N1_HS

DSPLL

®

÷ N2

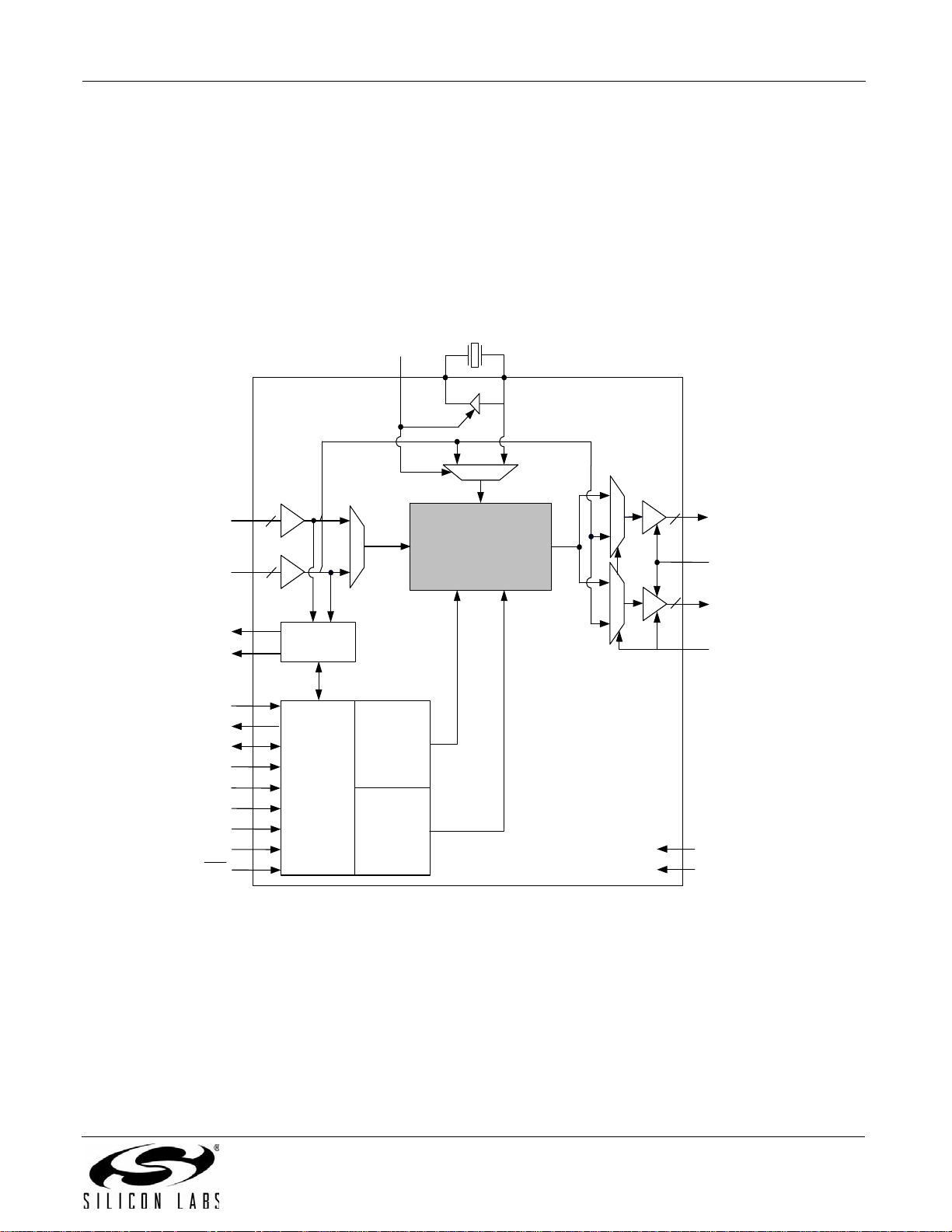

3.11. Si5366

The Si5366 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including

SONET OC-48/OC-192, Etherne t, and Fibr e Chan nel. T he S i53 66 acce pts four clo ck inp uts ranging fr om 8 kHz to