Silicon Laboratories SI5316, SI5319, SI5325, SI5375, SI5366 User Manual

...

ANY-FREQUENCY PRECISION CLOCKS

Si5316, Si5319, Si5322, Si5323, Si5324, Si5325,

Si5326, Si5327, Si5365, Si5366, Si5367,

Si5368, Si5369, Si5374, Si5375

F

AMILY REFERENCE MANUAL

Rev. 0.5 6/11 Copyright © 2011 by Silicon Laboratories Si53xx-RM

Si53xx-RM

2 Rev. 0.5

Si53xx-RM

TABLE OF CONTENTS

Section Page

1. Any-Frequency Precision Clock Product Family Overview . . . . . . . . . . . . . . . . . . . . . .12

2. Narrowband vs. Wideband Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3. Any-Frequency Clock Family Members . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.1. Si5316 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.2. Si5319 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

3.3. Si5322 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

3.4. Si5323 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3.5. Si5324 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.6. Si5325 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.7. Si5326 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.8. Si5327 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.9. Si5365 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.10. Si5366 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.11. Si5367 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

3.12. Si5368 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

3.13. Si5369 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.14. Si5374/75 Compared to Si5324/19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.15. Si5374 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.16. Si5375 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

4. Device Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

5. DSPLL (All Devices) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

5.1. Clock Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

5.2. PLL Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

5.2.1. Jitter Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

5.2.2. Jitter Transfer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

5.2.3. Jitter Tolerance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . .50

6.1. Clock Multiplication (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . .50

6.1.1. Clock Multiplication (Si5316) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

6.1.2. Clock Multiplication (Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

6.1.3. CKOUT3 and CKOUT4 (Si5365 and Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.4. Loop bandwidth (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.5. Jitter Tolerance (Si5316, Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.6. Narrowband Performance (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.7. Input-to-Output Skew (Si5316, Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.8. Wideband Performance (Si5322 and Si5365). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.9. Lock Detect (Si5322 and Si5365) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.1.10. Input-to-Output Skew (Si5322 and Si5365). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

6.2. PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65

6.2.1. Input Clock Stability during Internal Self-Calibration

(Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.2.2. Self-Calibration caused by Changes in Input Frequency

(Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

6.2.3. Recommended Reset Guidelines (Si5316, Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . 65

6.3. Pin Control Input Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

Rev. 0.5 3

Si53xx-RM

6.3.1. Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

6.3.2. Automatic Clock Selection (Si5322, Si5323, Si5365, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . 68

6.3.3. Hitless Switching with Phase Build-Out (Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

6.4. Digital Hold/VCO Freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

6.4.1. Narrowband Digital Hold (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4.2. Recovery from Digital Hold (Si5316, Si5323, Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.4.3. Wideband VCO Freeze (Si5322, Si5365) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

6.5. Frame Synchronization (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

6.6. Output Phase Adjust (Si5323, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71

6.6.1. FSYNC Realignment (Si5366). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.6.2. Including FSYNC Inputs in Clock Selection (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.6.3. FS_OUT Polarity and Pulse Width Control (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.6.4. Using FS_OUT as a Fifth Output Clock (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

6.6.5. Disabling FS_OUT (Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

6.7. Output Clock Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72

6.7.1. LVPECL and CMOS TQFP Output Signal Format Restrictions at 3.3 V (Si5365, Si5366) . . . . 72

6.8. PLL Bypass Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

6.9. Alarms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

6.9.1. Loss-of-Signal Alarms (Si5316, Si5322, Si5323, Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . 73

6.9.2. FOS Alarms (Si5365 and Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

6.9.3. FSYNC Align Alarm (Si5366 and CK_CONF = 1 and FRQTBL = L) . . . . . . . . . . . . . . . . . . . . . 74

6.9.4. C1B and C2B Alarm Outputs (Si5316, Si5322, Si5323) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.9.5. C1B, C2B, C3B, and ALRMOUT Outputs (Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

6.10. Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

6.11. DSPLLsim Configuration Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75

7. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326,

Si5327, Si5367, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

7.1. Clock Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76

7.1.1. Jitter Tolerance (Si5319, Si5324, Si5325, Si5326, Si5327, Si5368,

Si5369, Si5374 and Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.1.2. Wideband Parts (Si5325, Si5367) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

7.1.3. Narrowband Parts (Si5319, Si5324, Si5326, Si5327,

Si5368, Si5369, Si5374, Si5375). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

7.1.4. Loop Bandwidth (Si5319, Si5326, Si5368, Si5375). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.1.5. Lock Detect (Si5319, Si5326, Si5327, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . 79

7.2. PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79

7.2.1. Initiating Internal Self-Calibration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

7.2.2. Input Clock Stability during Internal Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.2.3. Self-Calibration Caused by Changes in Input Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.2.4. Narrowband Input-to-Output Skew (Si5319, Si5324, Si5326, Si5327,

Si5368, Si5369, Si5374, Si5375). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.2.5. Clock Output Behavior Before and During ICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

7.3. Input Clock Configurations (Si5367 and Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . .81

7.4. Input Clock Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81

7.4.1. Manual Clock Selection (Si5324, Si5325, Si5326, Si5367,

Si5368, Si5369, Si5374) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

7.4.2. Automatic Clock Selection (Si5324, Si5325, Si5326, Si5367,

Si5368, Si5369, Si5374) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

7.4.3. Hitless Switching with Phase Build-Out (Si5324, Si5326, Si5327,

Si5368, Si5369, Si5374) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

7.5. Si5319, Si5324, Si5326, Si5327, Si5368, Si5369, Si5374

4 Rev. 0.5

Si53xx-RM

and Si5375 Free Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

7.5.1. Free Run Mode Programming Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.5.2. Clock Control Logic in Free Run Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7.5.3. Free Run Reference Frequency Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.5.4. Free Run Reference Frequency Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

7.6. Digital Hold . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87

7.6.1. Narrowband Digital Hold (Si5316, Si5324, Si5326, Si5368, Si5369, Si5374) . . . . . . . . . . . . . . 87

7.6.2. History Settings for Low Bandwidth Devices (Si5324, Si5327, Si5369, Si5374). . . . . . . . . . . . 89

7.6.3. Recovery from Digital Hold (Si5319, Si5324, Si5326, Si5327, Si5368, Si5369, Si5374) . . . . . 89

7.6.4. VCO Freeze (Si5319, Si5325, Si5367, Si5375). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.6.5. Digital Hold versus VCO Freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

7.7. Output Phase Adjust (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .90

7.7.1. Coarse Skew Control (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.7.2. Fine Skew Control (Si5326, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.7.3. Independent Skew (Si5324, Si5326, Si5368, Si5369, Si5374) . . . . . . . . . . . . . . . . . . . . . . . . . 91

7.7.4. Output-to-output Skew (Si5324, Si5326, Si5327, Si5368, Si5369, Si5374) . . . . . . . . . . . . . . . 91

7.7.5. Input-to-Output Skew (All Devices) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

7.8. Frame Synchronization Realignment (Si5368 and CK_CONFIG_REG = 1) . . . . . . .91

7.8.1. FSYNC Realignment (Si5368). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

7.8.2. FSYNC Skew Control (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.8.3. Including FSYNC Inputs in Clock Selection (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.8.4. FS_OUT Polarity and Pulse Width Control (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.8.5. Using FS_OUT as a Fifth Output Clock (Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.9. Output Clock Drivers (Si5319, Si5324, Si5325, Si5326,

Si5327, Si5367, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . .95

7.9.1. Disabling CKOUTn. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.9.2. LVPECL TQFP Output Signal Format Restrictions at 3.3 V (Si5367, Si5368, Si5369). . . . . . . 95

7.10. PLL Bypass Mode (Si5319, Si5324, Si5325, Si5326, Si5327,

Si5367, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

7.11. Alarms (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367,

Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96

7.11.1. Loss-of-Signal Alarms (Si5319, Si5324, Si5325, Si5326, Si5327,

Si5367, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.11.2. FOS Algorithm (Si5324, Si5325, Si5326, Si5368, Si5369, Si5374). . . . . . . . . . . . . . . . . . . . . 97

7.11.3. C1B, C2B (Si5319, Si5324, Si5325, Si5326, Si5327, Si5374, Si5375). . . . . . . . . . . . . . . . . . 99

7.11.4. LOS (Si5319, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.11.5. C1B, C2B, C3B, ALRMOUT (Si5367, Si5368, Si5369 [CK_CONFIG_REG = 0]) . . . . . . . . . . 99

7.11.6. C1B, C2B, C3B, ALRMOUT (Si5368 [CK_CONFIG_REG = 1]) . . . . . . . . . . . . . . . . . . . . . . 100

7.11.7. LOS Algorithm for Reference Clock Input (Si5319, Si5324, Si5326,

Si5327, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

7.11.8. LOL (Si5319, Si5324, Si5326, Si5327, Si5368, Si5369, Si5374, Si5375). . . . . . . . . . . . . . . 100

7.11.9. Device Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

7.12. Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101

7.13. I

7.14. Serial Microprocessor Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103

7.15. Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

7.16. DSPLLsim Configuration Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .104

8. High-Speed I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

8.1. Input Clock Buffers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105

8.2. Output Clock Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107

2

C Serial Microprocessor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102

7.14.1. Default Device Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Rev. 0.5 5

Si53xx-RM

8.2.1. LVPECL TQFP Output Signal Format Restrictions at 3.3 V (Si5367, Si5368, Si5369). . . . . . 107

8.2.2. Typical Output Circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

8.2.3. Typical Clock Output Scope Shots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

8.3. Typical Scope Shots for SFOUT Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110

8.4. Crystal/Reference Clock Interfaces (Si5316, Si5319, Si5323,

Si5324, Si5326, Si5327, Si5366, Si5368, Si5369, Si5374, and Si5375) . . . . . . . .113

8.5. Three-Level (3L) Input Pins (No External Resistors) . . . . . . . . . . . . . . . . . . . . . . .115

8.6. Three-Level (3L) Input Pins (With External Resistors) . . . . . . . . . . . . . . . . . . . . . .116

9. Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117

10. Packages and Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118

Appendix A—Narrowband References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119

Appendix B—Frequency Plans and Jitter Performance (Si5316, Si5319,

Si5323, Si5324, Si5326, Si5327, Si5366, Si5368, Si5369,

Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .121

Appendix C—Typical Phase Noise Plots . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Appendix D—Alarm Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144

Appendix E—Internal Pullup, Pulldown by Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .147

Appendix F—Typical Performance: Bypass Mode, PSRR, Crosstalk,

Output Format Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

Appendix G—Near Integer Ratios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

Appendix H—Jitter Attenuation and Loop BW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164

Appendix I—Si5374 and Si5375 PCB Layout Recommendations . . . . . . . . . . . . . . . . . .169

Appendix J—Si5374 and Si5375 Crosstalk . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173

Document Change List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180

6 Rev. 0.5

Si53xx-RM

LIST OF FIGURES

Figure 1. Si5316 Any-Frequency Jitter Attenuator Block Diagram . . . . . . . . . . . . . . . . . . . . . 17

Figure 2. Si5319 Any-Frequency Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . .18

Figure 3. Si5322 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 4. Si5323 Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . 20

Figure 5. Si5324 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 21

Figure 6. Si5325 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 7. Si5326 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 23

Figure 8. Si5327 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . . 24

Figure 9. Si5365 Low Jitter Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Figure 10. Si5366 Jitter Attenuating Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . 26

Figure 11. Si5367 Clock Multiplier Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 12. Si5368 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . 28

Figure 13. Si5369 Clock Multiplier and Jitter Attenuator Block Diagram. . . . . . . . . . . . . . . . . 29

Figure 14. Si5374 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 15. Si5375 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 16. Differential Voltage Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 17. Rise/Fall Time Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 18. SPI Timing Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 19. Frame Synchronization Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 20. Any-Frequency Precision Clock DSPLL Block Diagram . . . . . . . . . . . . . . . . . . . . 46

Figure 21. Clock Multiplication Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 22. PLL Jitter Transfer Mask/Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 23. Jitter Tolerance Mask/Template. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 24. Si5316 Divisor Ratios. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 25. Wideband PLL Divider Settings (Si5325, Si5367) . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 26. Narrowband PLL Divider Settings (Si5319, Si5324, Si5326,

Si5327, Si5368, Si5369, Si5374, Si5375) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Figure

Figure 28. Si5367, Si5368, and Si5369 Input Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . 82

Figure 29. Free Run Mode Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

Figure 30. Parameters in History Value of M . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Figure 31. Digital Hold vs. VCO Freeze Exampl e . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 32. Frame Sync Frequencies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Figure 33. FOS Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 34. I2C Command Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 35. I2C Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Figure 36. SPI Write/Set Address Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 37. SPI Read Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 38. Differential LVPECL Termination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 39. Single-Ended LVPECL Termination. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Figure 40. CML/LVDS Termination (1.8, 2.5, 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 41. CMOS Termination (1.8, 2.5, 3.3 V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Figure 42. Typical Output Circuit (Differential) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

27. Si5324, Si5325, Si5326, Si5327, and Si5374 Input Clock Selection . . . . . . . . . . . 81

Rev. 0.5 7

Si53xx-RM

Figure 43. Differential Output Example Requiring Attenuation . . . . . . . . . . . . . . . . . . . . . . . 108

Figure 44. Typical CMOS Output Circuit (Tie CKOUTn+ and CKOUTn– Together). . . . . . . 108

Figure 45. CKOUT Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Figure 46. sfout_2, CMOS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 47. sfout_3, lowSwingLVDS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 48. sfout_5, LVPECL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure 49. sfout_6, CML . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure 50. sfout_7, LVDS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

Figure 51. CMOS External Reference Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 52. Sinewave External Clock Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

Figure 53. Differential External Reference Input Example (Not for Si5374 or Si5375) . . . . .114

Figure 54. Differential OSC Reference Input Example for Si5374 and Si 5375 . . . . . . . . . . .114

Figure 55. Three Level Input Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

Figure 56. Three Level Input Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

Figure 57. Typical Power Supply Bypass Network (TQFP Package) . . . . . . . . . . . . . . . . . . 117

Figure 58. Typical Power Supply Bypass Network (QFN Package) . . . . . . . . . . . . . . . . . . . 117

Figure 59. Typical Reference Jitter Transfer Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

Figure 60. Jitter vs. f3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

Figure 61. Jitter vs. f3 with FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Figure 62. Reference vs. Output Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Figure 63. Jitter vs. Reference Frequency (1 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

Figure 64. Jitter vs. Reference Frequency (2 of 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

Figure 65. 155.52 MHz In; 622.08 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .126

Figure 66. 155.52 MHz In; 622.08 MHz Out; Loop BW = 7 Hz, Si5324 . . . . . . . . . . . . . . . . .127

Figure 67. 19.44 MHz In; 156.25 MHz Out; Loop BW = 80 Hz . . . . . . . . . . . . . . . . . . . . . . .128

Figure 68. 19.44 MHz In; 156.25 MHz Out; Loop BW = 5 Hz, Si5324 . . . . . . . . . . . . . . . . . .129

Figure 69. 27 MHz In; 148.35 MHz Out; Light Trace BW = 6 Hz;

Dark Trace BW = 110 Hz, Si5324 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .130

Figure 70. 61.44 MHz In; 491.52 MHz Out; Loop BW = 7 Hz, Si5324 . . . . . . . . . . . . . . . . . .131

Figure 71. 622.08 MHz In; 672.16 MHz Out; Loop BW = 6.9 kHz . . . . . . . . . . . . . . . . . . . . .132

Figure 72. 622.08 MHz In; 672.16 MHz Out; Loop BW = 100 Hz . . . . . . . . . . . . . . . . . . . . .133

Figure 73. 156.25 MHz In; 155.52 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .134

Figure 74. 78.125 MHz In; 644.531 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135

Figure 75. 78.125 MHz In; 690.569 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .136

Figure 76. 78.125 MHz In; 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Figure 77. 86.685 MHz In; 173.371 MHz and 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . 138

Figure 78. 86.685 MHz In; 173.371 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

Figure 79. 86.685 MHz In; 693.493 MHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Figure 80. 155.52 MHz and 156.25 MHz In; 622.08 MHz Out . . . . . . . . . . . . . . . . . . . . . . . 141

Figure 81. 10 MHz In; 1 GHz Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

Figure 82. Si5324 and Si5326 Alarm Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

Figure 83. Si5368 Alarm Diagram (1 of 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

Figure 84. Si5368 Alarm Diagram (2 of 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

Figure 85. ±50 ppm, 2 ppm Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162

Figure 86. ±200 ppm, 10 ppm Steps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 87. ±2000 ppm, 50 ppm Steps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

8 Rev. 0.5

Si53xx-RM

Figure 88. RF Generator, Si5326, Si5324; No Jitter (For Reference) . . . . . . . . . . . . . . . . . .165

Figure 89. RF Generator, Si5326, Si5324 (50 Hz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

Figure 90. RF Generator, Si5326, Si5324 (100 Hz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Figure 91. RF Generator, Si5326, Si5324 (500 Hz Jitter). . . . . . . . . . . . . . . . . . . . . . . . . . . 166

Figure 92. RF Generator, Si5326, Si5324 (1 kHz Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 93. RF Generator, Si5326, Si5324 (5 kHz Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Figure 94. RF Generator, Si5326, Si5324 (10 kHz Jitter) . . . . . . . . . . . . . . . . . . . . . . . . . . . 168

Figure 95. Vdd Plane . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .169

Figure 96. Ground Plane and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

Figure 97. Output Clock Routing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

Figure 98. OSC_P, OSC_N Routing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

Figure 99. Si5374, Si5375 DSPLL A. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

Figure 100. Si5374, Si5375 DSPLL B. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Figure 101. Si5374, Si5375 DSPLL C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

Figure 102. Si5374, Si5375 DSPLL D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

Rev. 0.5 9

Si53xx-RM

LIST OF TABLES

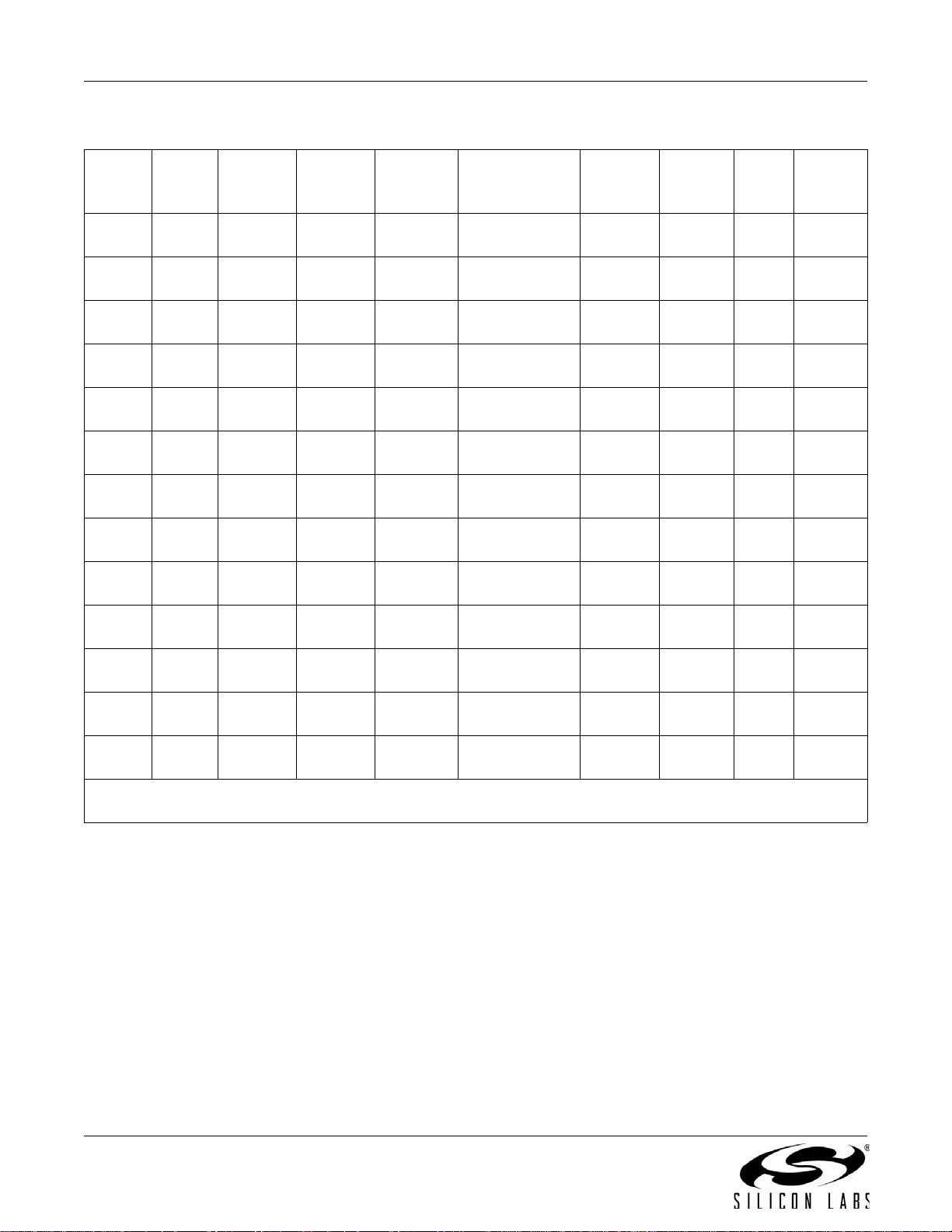

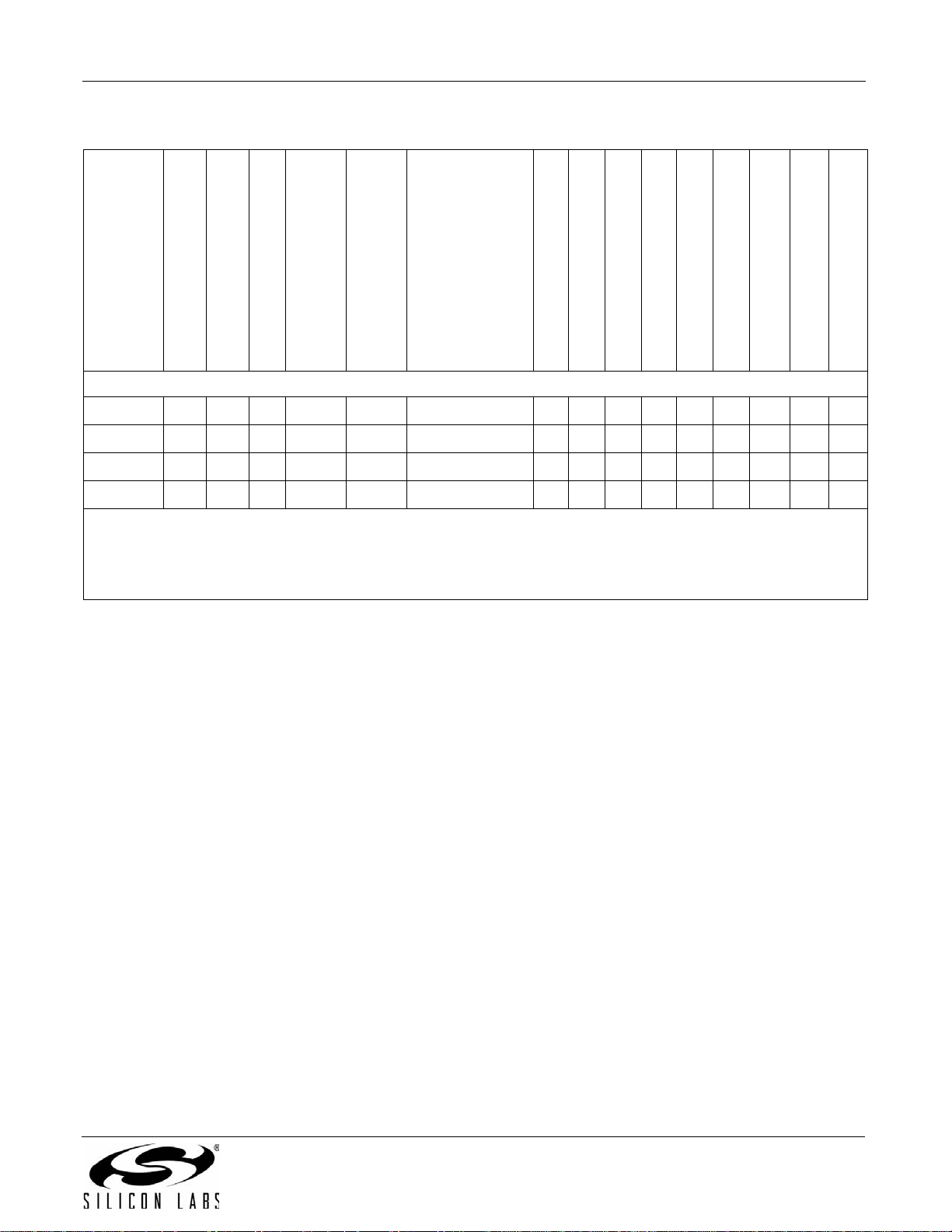

Table 1. Product Selection Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 2. Product Selection Guide (Si5322/25/65/67) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 3. Recommended Operating Conditions

Table 4. DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 5. DC Characteristics—Microprocessor Devices (Si5324, Si5325,

Si5367, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 6. SPI Specifications (Si5324, Si5325, Si5367, and Si5368) . . . . . . . . . . . . . . . . . . . . 37

Table 7. DC Characteristics—Narrowband Devices (Si5316, Si5319,

Si5323, Si5366, Si5368). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Table 8. AC Characteristics—All Devices. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 9. Jitter Generation (Si5316, Si5324, Si5366, Si5368) . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 10. Jitter Generation (Si5322, Si5325, Si5365, Si5367) . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 11. Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Table 12. Si5316, Si5322, Si5323, Si5365 and Si5366 Key Features . . . . . . . . . . . . . . . . . . 50

Table 13. Frequency Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 14. Input Divider Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 15. Si5316 Bandwidth Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 16. SONET Clock Multiplication Settings (FRQTBL=L) . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 17. Datacom Clock Multiplication Settings (FRQTBL = M, CK_CONF = 0) . . . . . . . . . 57

Table 18. SONET to Datacom Clock Multiplication Settings. . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 19. Clock Output Divider Control (DIV34) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 20. Si5316, Si5322, and Si5323 Pins and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 21. Si5365 and Si5366 Pins and Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 22. Manual Input Clock Selection (Si5316, Si5322, Si5323), AUTOSEL = L . . . . . . . . 67

Table 23. Manual Input Clock Selection (Si5365, Si5366), AUTOSEL = L. . . . . . . . . . . . . . . 67

Table 24. Automatic/Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 25. Clock Active Indicators (AUTOSEL = M or H) (Si5322 and Si5323). . . . . . . . . . . . 68

Table 26. Clock Active Indicators (AUTOSEL = M or H) (Si5365 and Si5367). . . . . . . . . . . . 68

Table 27. Input Clock Priority for Auto Switching (Si5322, Si5323) . . . . . . . . . . . . . . . . . . . . 68

Table 28. Input Clock Priority for Auto Switching (Si5365, Si5366) . . . . . . . . . . . . . . . . . . . . 69

Table 29. FS_OUT Disable Control (DBLFS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 30. Output Signal Format Selection (SFOUT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 31. DSBL2/BYPASS Pin Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Table 32. Frequency Offset Control (FOS_CTL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 33. Alarm Output Logic Equations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

Table 34. Lock Detect Retrigger Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Table 35. Narrowband Frequency Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 36. Dividers and Limits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

Table 37. CKOUT_ALWAYS_ON and SQ_ICAL Truth Table. . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 38. Manual Input Clock Selection (Si5367, Si5368, Si5369). . . . . . . . . . . . . . . . . . . . . 82

Table 39. Manual Input Clock Selection (Si5324, Si5325, Si5326, Si5374) . . . . . . . . . . . . . . 83

Table 40. Automatic/Manual Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 41. Input Clock Priority for Auto Switching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

1

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

10 Rev. 0.5

Si53xx-RM

Table 42. Digital Hold History Delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 43. Digital Hold History Averaging Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 44. CKIN3/CKIN4 Frequency Selection (CK_CONF = 1) . . . . . . . . . . . . . . . . . . . . . . . 92

Table 45. Common NC5 Divider Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 46. Alignment Alarm Trigger Threshold. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 47. Output Signal Format Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Table 48. Loss-of-Signal Validation Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 49. Loss-of-Signal Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 50. FOS Reference Clock Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 51. CLKnRATE Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Table 52. Alarm Output Logic Equations

(Si5367, Si5368, and Si5369 [CONFIG_REG = 0]) . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 53. Alarm Output Logic Equations [Si5368 and CKCONFIG_REG = 1] . . . . . . . . . . . 100

Table 54. Lock Detect Retrigger Time (LOCKT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 55. SPI Command Format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 56. Output Driver Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Table 57. Disabling Unused Output Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 58. Output Format Measurements1,2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

Table 59. Approved Crystals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 60. XA/XB Reference Sources and Frequencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

Table 61. Jitter Values for Figure 61 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

Table 62. Jitter Values for Figure 62 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

Table 63. Jitter Values for Figure 74 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

Table 64. Jitter Values for Figure 75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

Table 65. Jitter Values for Figure 76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Table 66. Jitter Values for Figure 77. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

Table 67. Jitter Values for Figure 80. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

Table 68. Si5316 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 69. Si5322 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 147

Table 70. Si5323 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 71. Si5319, Si5324, Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

Table 72. Si5325 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 73. Si5326 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

Table 74. Si5327 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 75. Si5365 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 150

Table 76. Si5366 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 77. Si5367 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 78. Si5368 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

Table 79. Si5369 Pullup/Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 80. Si5374/75 Pullup/Down. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

Table 81. Output Format vs. Jitter

Table 82. Jitter Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 83. Si5374/75 Crosstalk Jitter Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Rev. 0.5 11

Si53xx-RM

1. Any-Frequency Precision Clock Product Family Overview

Silicon Laboratories Any-Frequency Precision Clock products provide jitter attenuation and clock multiplication/

clock division for applications requiring sub 1 ps rms jitter performance. The device product family is based on

Silicon Laboratories' 3rd generation DSPLL technology, which provides any-frequency synthesis and jitter

attenuation in a highly integr ated PLL solution that eliminates the need for discrete VCXO/VCSOs and loop filter

components. These devices are ideally suited for applications which require low jitter reference clocks, including

OTN (OTU-1, OTU-2, OTU-3, OTU-4), OC-48/STM-16, OC-192/STM-64, OC-768/STM-256, GbE, 10GbE, Fibre

Channel, 10GFC, synchronous Ethernet, wireless backhaul, wireless point-point infrastructure, broadcast video/

HDTV (HD SDI, 3G SDI), test and measurement, data acquisition systems, and FPGA/ASIC reference clocking.

Table 1 provides a product selector guide for the Silicon Laboratories Any-Frequency Precision Clocks. Three

product families are available. The Si5316, Si5319, Si5323, Si5324, Si5326, Si5366, and Si5368 are jitterattenuating clock multipliers that provide ultra-low jitter generation as low as 0.30 ps RMS. The devices vary

according to the number of clock inputs, number of clock outputs, and control method. The Si5316 is a fixedfrequency, pin controlled jitter attenuator that can be used in clock smoothing applications. The Si5323 and Si5366

are pin-controlled jitter-attenuating clock multipliers. The frequency plan for these pin-controlled devices is

selectable from frequency lookup tables and includes common frequency translations for SONET/SDH, ITU G.709

Forward Error Correction (FEC) applications (255/238, 255/237, 255/236, 238/255, 237/255, 236/255), Gigabit

Ethernet, 10G Ethernet, 1G/2G/4G/8G/10G Fibre Channel, ATM and broadcast video (Genlock). The Si5319,

Si5324, Si5326, Si5327, Si5368, and Si5369 are microprocessor-controlled devices that can be controlled via an

2

C or SPI interface. These microprocessor-controlled devices accept clock inputs ranging from 2 kHz to 710 MHz

I

and generate multiple independent, synchronous clock outputs ranging from 2 kHz to 945 MHz and select

frequencies to 1.4 GHz. Virtually any frequency translation combination across this operating range is supported.

Independent dividers are available for every input clock and output clock, so the Si5324, Si5326, Si5327, and

Si5368 can accept input clocks at different frequencies and generate output clocks at different frequencies. The

Si5316, Si5319, Si5323, Si5326, Si5327, Si5366, Si5368, and Si5369 support a digitally programmable loop

bandwidth that can range from 60 Hz to 8.4 kHz. An exter nal (37–41 MHz, 55–61 MHz, 109–125.5 MHz, or 163–

180 MHz) reference clock or a low-cost 114.285 MHz 3rd overtone crystal is required for these devices to enable

ultra-low jitter generation and jitter attenuation. (See "Appendix A—Narrowband References" on page 119.) The

Si5324 and Si5369 are much lower bandwidth devices, providing a user-programmable loop bandwidth from 4 to

525 Hz.

The Si5323, Si5324, Si5326, Si5327, Si5366, Si5368, and Si5369 support hitless switching between input clocks in

compliance with GR-253-CORE and GR-1244-CORE that greatly minimizes the prop ag ation of phase transie nt s to

the clock outputs during an input clock transition (<200 ps typ). Manual, automatic revertive and automatic nonrevertive input clock switching options are available. The devices monitor the input clocks for loss-of-signal and

provide a LOS alarm when missing pulses on any of the input clocks are detected. The devices monitor the lock

status of the PLL and provide a LOL alarm when the PLL is unlocked. The lock detect algorithm works by

continuously monitoring the phase of the selected input clock in relation to the phase of the feedback clock. The

Si5326, Si5366, Si5368, and Si5369 monitor the frequency of the input clocks with respect to a reference

frequency applied to an input clock or the XA/XB input, and generates a frequency offset alarm (FOS) if the

threshold is exceeded. This FOS feature is available for SONET/SDH applications. Both Stratum 3/3E and SONET

Minimum Clock (SMC) FOS thresholds are supported.

The Si5319, Si5323, Si5324, Si5326, Si5366, Si5368, and Si5369 provide a digital hold capability that allows the

device to continue generation of a stable output clock when the selected input reference is lost. During digita l hold,

the DSPLL generates an output frequency based on a historical average that existed a fixed amount of time before

the error event occurred, eliminating the effects of phase and frequency transients that may occur immediately

preceding entry into digital hold.

The Si5322, Si5325, Si5365, and Si5367 are frequency flexible, low jitter clock multipliers that provide jitter

generation of 0.6 ps RMS without jitter attenuation. These devices provide low jitter integer clock multiplication or

fractional clock synthesis, but they are not as frequency-flexible as the Si5319/23/24/26/66/68/69. The devices

vary according to the number of clock inputs, number of clock ou tput s, and co ntrol method . The Si5322 and Si5365

are pin-controlled clock multipliers. The frequency plan for these devices is selectable from frequency lookup

tables.

12 Rev. 0.5

Si53xx-RM

A wide range of settings are available, but they are a subset of the frequency plans supported by the Si5323 and

Si5366 jitter-attenuating clock multipliers. The Si5325 and Si5367 are microprocessor-controlled clock multipliers

that can be controlled via an I

These devices accept clock inputs ranging from 10 MHz to 710 MHz and generate multiple independent,

synchronous clock outputs ranging from 10 MHz to 945 MHz and select frequencies to 1.4 GHz. The Si5325 and

Si5367 support a subset of the frequen cy translations available in the Si5319, Si5 324, Si5326, Si5327, Si5 368, and

Si5369 jitter-attenuating clock multipliers. The Si5325 and Si5367 can accept input clocks at different frequencies

and generate output clocks at different frequencies. The Si5322, Si5325, Si5365, and Si5367 support a digitally

programmable loop bandwidth that ranges from 150 kHz to 1.3 MHz. No external components are required for

these devices. LOS and FOS monitoring is available for these devices, as described above.

The Si5374 and Si5375 are quad DSPLL versions of the Si5324 and Si5319, respectively. Each of the four

DSPLLs can operate at completely independent frequencies. The only resources that they share are a common

2

C bus and a common XA/XB jitter reference oscillator. The Si5375 consists of four one-input and one-output

I

DSPLLs. The Si5374 consists of four two-input and two-output DSPLLs with very low loop bandwidth.

The Any-Frequency Precision Clocks have dif fere ntial clock ou tp ut(s) with pr ogr ammab le sign al for mats to support

LVPECL, LVDS, CML, and CMOS loads. If the CMOS signal format is selected, each differential output buffer

generates two in-phase CMOS clocks at the same frequency. For system-level debugging, a PLL bypass mode

drives the clock output directly from the selected input clock, bypassing the internal PLL.

Silicon Laboratories offers a PC-based software utility, DSPLLsim, tha t can be used to determine valid fre quency

plans and loop bandwidth settings for the Any-Frequency Precision Clock product family. For the microprocessorcontrolled devices, DSPLLsim provides the optimum PLL divider settings for a given input frequency/clock

multiplication ratio combination that minimizes phase noise and power consumption. Two DSPLLsim configuration

software applications are available for the 1-PLL and 4-PLL devices, respectively. DSPLLsim can also be used to

simplify device selection and configuration. This utility can be downloaded from http://www.silabs.com/timing.

Other useful documentation, including device data sheets and programming files for the microprocessor-controlled

devices are available from this website.

2

C or SPI interface.

Rev. 0.5 13

Si53xx-RM

Table 1. Product Selection Guide

Part

Number

Si5315 Pin 1PLL, 2 | 2 0.008–644 0.008–644 0.45 ps

Si5316 Pin 1PLL, 2 | 1 19–710 19–710 0.3 ps

Si5317 Pin 1PLL, 1 | 2 1–710 1–710 0.3 ps

Si5319 I

Si5323 Pin 1PLL, 2 | 2 0.008–707 0.008–1050 0.3 ps

Si5324 I

Si5326 I2C/SPI 1PLL, 2 | 2 0.002–710 0.002–1417 0.3 ps

Si5327 I2C/SPI 1PLL, 2 | 2 0.002–710 0.002–808 0.5 ps

Si5366 Pin 1PLL, 4 | 5 0.008–707 0.008–1050 0.3 ps

Control Number of

Inputs and

Outputs

2

C/SPI 1PLL, 1 | 1 0.002–710 0.002–1417 0.3 ps

2

C/SPI 1PLL, 2 | 2 0.002–710 0.002–1417 0.3 ps

Input

Frequency

(MHz)

*

Output

Frequency

(MHz)

*

RMS Phase Jitter

(12kHz–20MHz)

PLL

Bandwidth

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

4 Hz to

525 Hz

60 Hz to

8kHz

60 Hz to

8kHz

60 Hz to

8kHz

Hitless

Switching

Free

Run

Mode

Package

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

6x6 mm

36-QFN

14x14 mm

100-TQFP

Si5368 I2C/SPI 1PLL, 4 | 5 0.002–710 0.002–1417 0.3 ps

Si5369 I2C/SPI 1PLL, 4 | 5 0.002–710 0.002–1417 0.3 ps

2

Si5374 I

Si5375 I2C 4PLL, 4 | 4 0.002–710 0.002–808 0.4 ps

*Note: Maximum input and output rates may be limited by speed rating of device. See each device’s data sheet for ordering

information.

C 4PLL, 8 | 8 0.002–710 0.002–808 0.4 ps

60 Hz to

8kHz

4 Hz to

525 Hz

4 Hz to

525 Hz

60 Hz to

8kHz

14x14 mm

100-TQFP

14x14 mm

100-TQFP

10x10 mm

80-BGA

10x10 mm

80-BGA

14 Rev. 0.5

Table 2. Product Selection Guide (Si5322/25/65/67)

1

Si53xx-RM

Device

Low Jitter Precision Clock Multipliers (Wideband)

Si5322 2 2 707 1050 0.6 ps rms typ

Si5325 2 2

Si5365 4 5 707 1050 0.6 ps rms typ

Si5367 4 5

Notes:

1. Maximum input and output rates may be limited by speed rating of device. See each device’s data sheet for ordering

information.

2. Requires external low-cost, fixed frequency 3rd overtone 114.285 MHz crystal or reference clock. See "T able 60.X A/XB

Reference Sources and Frequencies" on page 119.

Clock Inputs

Clock Outputs

P Control

Max Input Freq (MHz)

Max Output Frequency (MHz)

Jitter Generation

(12 kHz – 20 MHz)

LOS

Hitless Switching

FOS Alarm

LOL Alarm

FSYNC Realignment

36 Lead 6 mm x 6 mm QFN

100 Lead 14 x 14 mm TQFP

710 1400 0.6 ps rms typ

710 1400 0.6 ps rms typ

1.8, 2.5, 3.3 V Operation

1.8, 2.5 V Operation

Rev. 0.5 15

Si53xx-RM

2. Narrowband vs. Wideband Overview

The narrowband (NB) devices offer a number of features and capabilities that are not available with the wideband

(WB) devices, as outlined in the below list:

Broader set of frequency plans due to more divisor options

Hitless switching between input clocks

Lower minimum input clock frequency

Lower loop bandwidth

Digital Hold (reference-based holdover instead of VCO freeze)

FRAMESYNC realignment

CLAT and FLAT (input to output skew adjust)

INC and DEC pins

PLL Loss of Lock status indicator

FOS is not supported.

16 Rev. 0.5

Si53xx-RM

2

DSPLL

®

C1B

CS

LOL

BWSEL[1:0]

DBL_BY

Xtal or Refclock

SFOUT[1:0]

CKOUT+

CKOUT–

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

Control

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

FRQSEL[1:0]

RST

0

1

RATE[1:0]

XA

XB

f

OSC

2

0

1

÷ N31

÷ N32

f

3_1

f

3_2

CK1DIV

CK2DIV

f

3

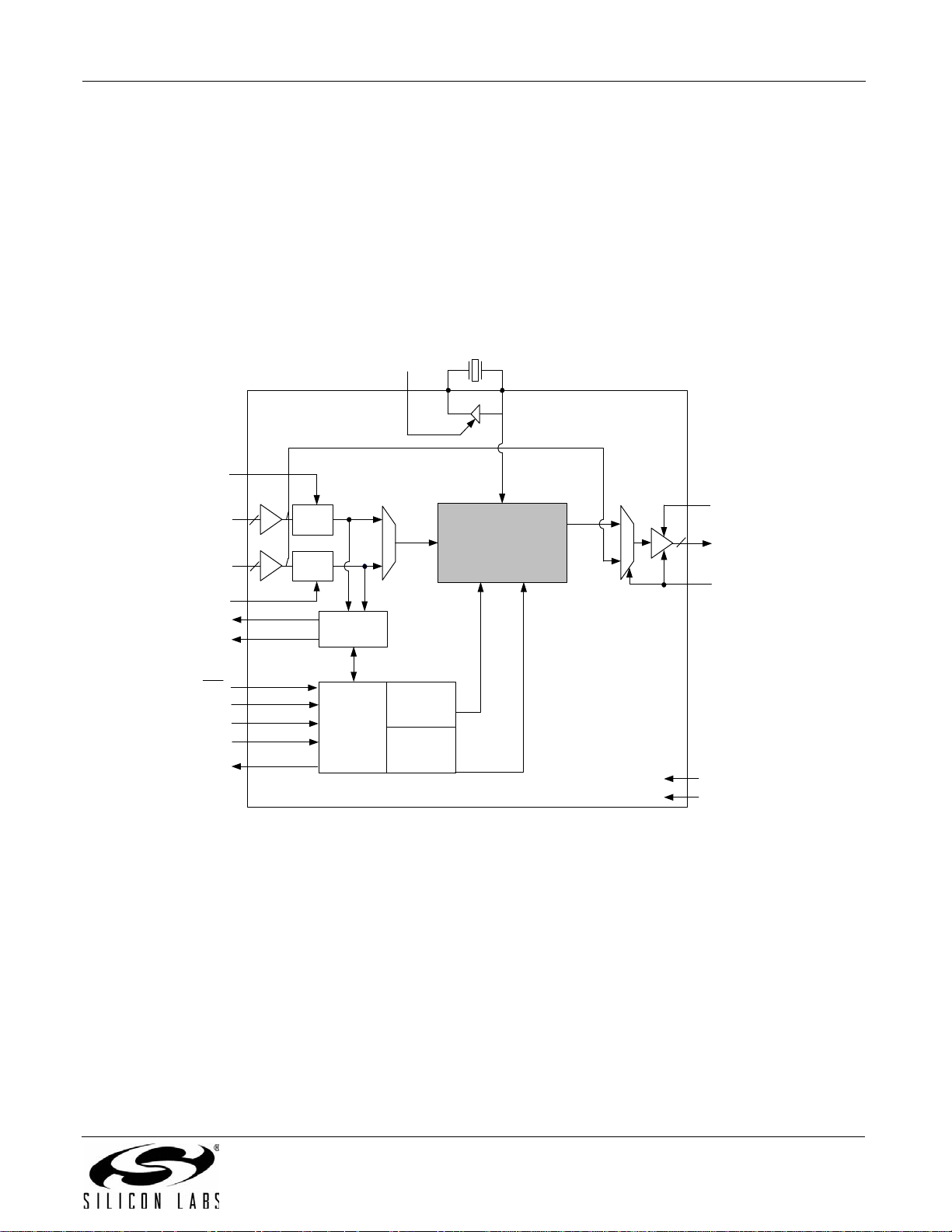

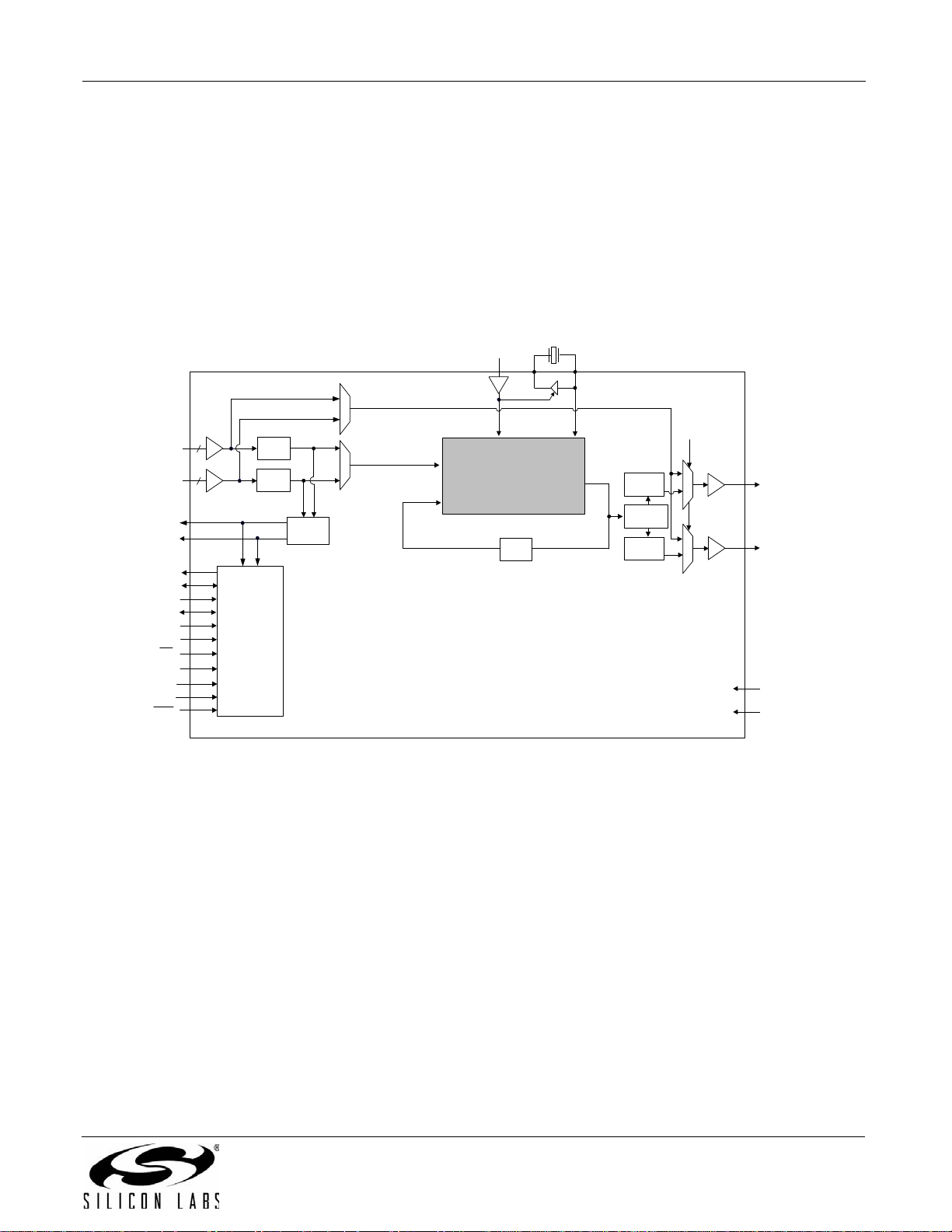

3. Any-Frequency Clock Family Members

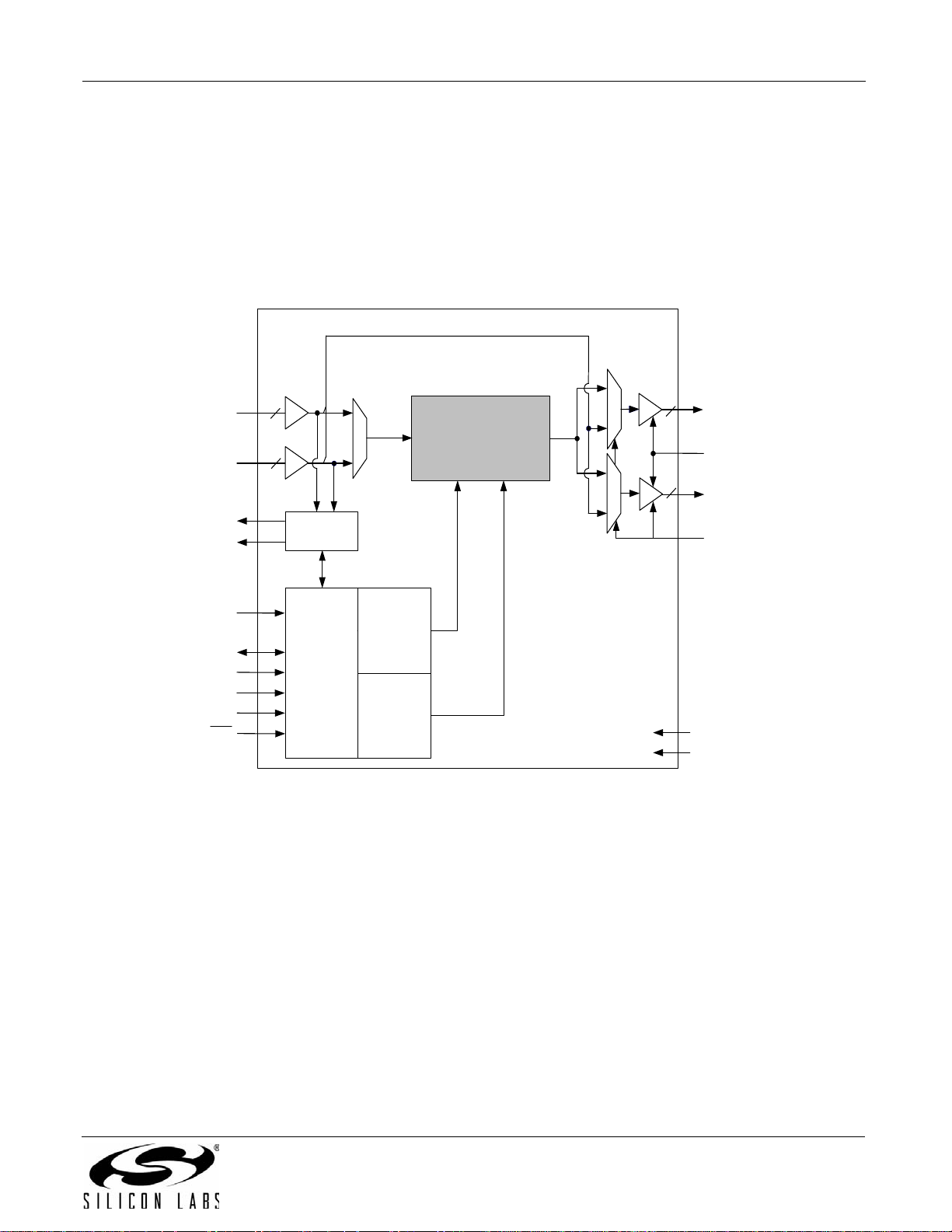

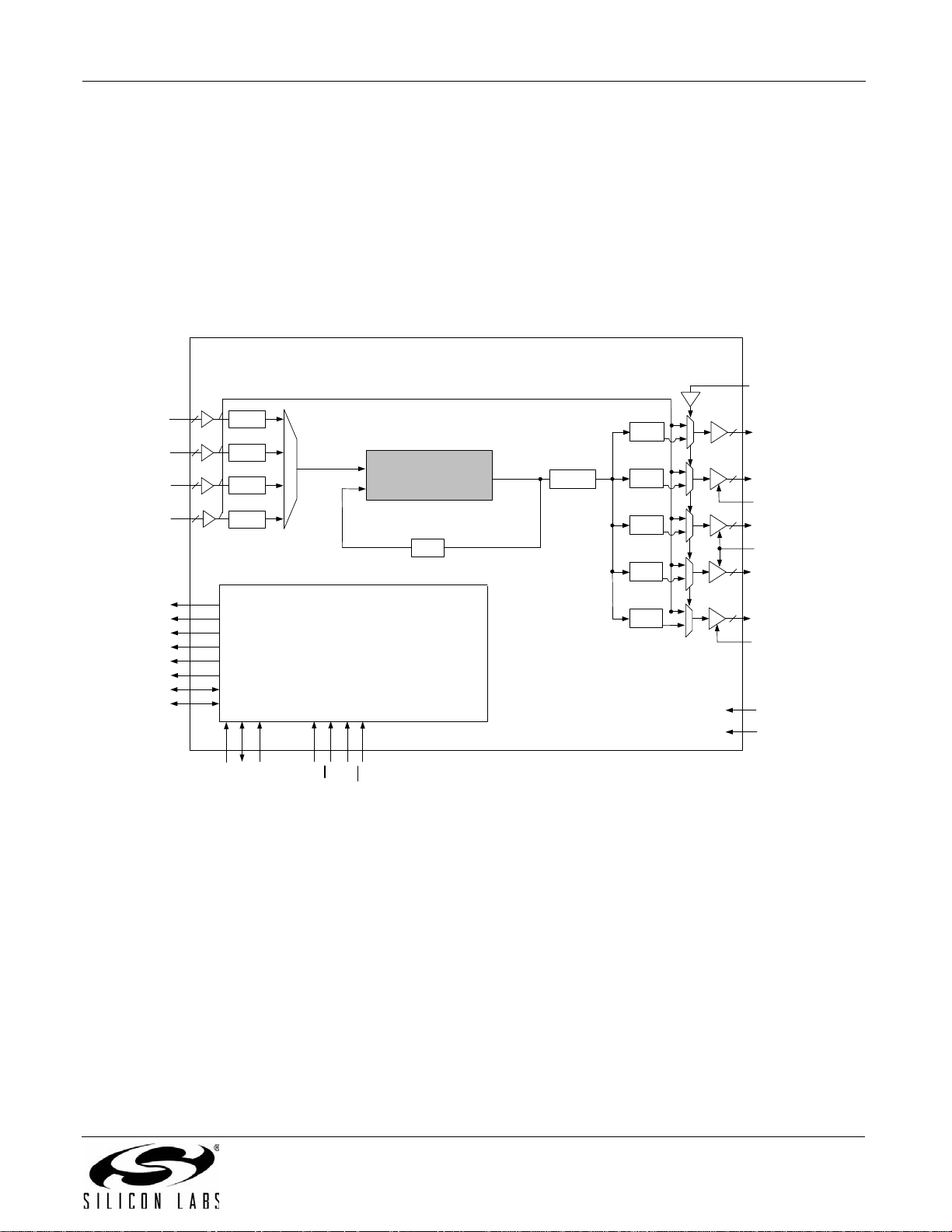

3.1. Si5316

The Si5316 is a low jitter, precision jitter attenuator for high-speed communication systems, including OC -48, OC192, 10G Ethernet, and 10G Fibre Channel. The Si5316 accepts dual clock inputs in the 19, 38, 77, 155, 311, or

622 MHz frequency range and generates a jitter-attenuated clock output at the same frequency. Within each of

these clock ranges, the device can be tuned approximately 14% higher tha n nomin al SONET/SDH fre quencies, up

to a maximum of 710 MHz in the 622 MHz range. Th e DSPL L lo op b an dw idth is digitally selec table, providing jitter

performance optimization at the application level. Operating fr om a single 1.8, 2.5, or 3.3 V supp ly, the Si5316 is

ideal for providing jitter attenuation in high performance timing applications. See "6. Pin Control Parts (Si5316,

Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete description.

Figure 1. Si5316 Any-Frequency Jitter Attenuator Block Diagram

Rev. 0.5 17

Si53xx-RM

DSPLL

®

Loss of Signal

Xtal or Refclock

CKIN

CKOUT

÷ N31

÷ N2

Signal Detect

Device Interrupt

VDD

GND

Loss of Lock

Xtal/Clock Select

I

2

C/SPI Port

Control

Rate Select

÷ N32

XO

f

3

÷ N1_HS ÷ NC1

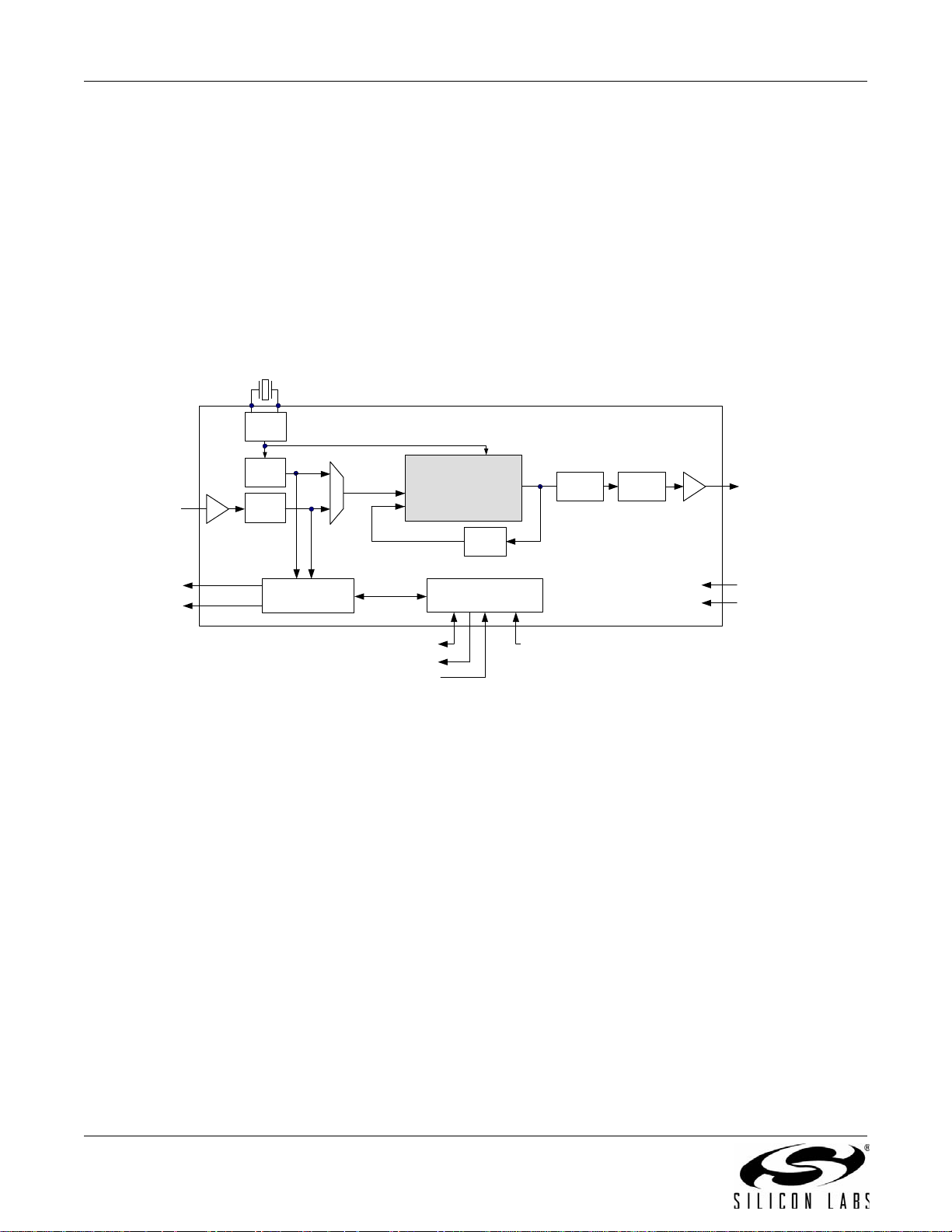

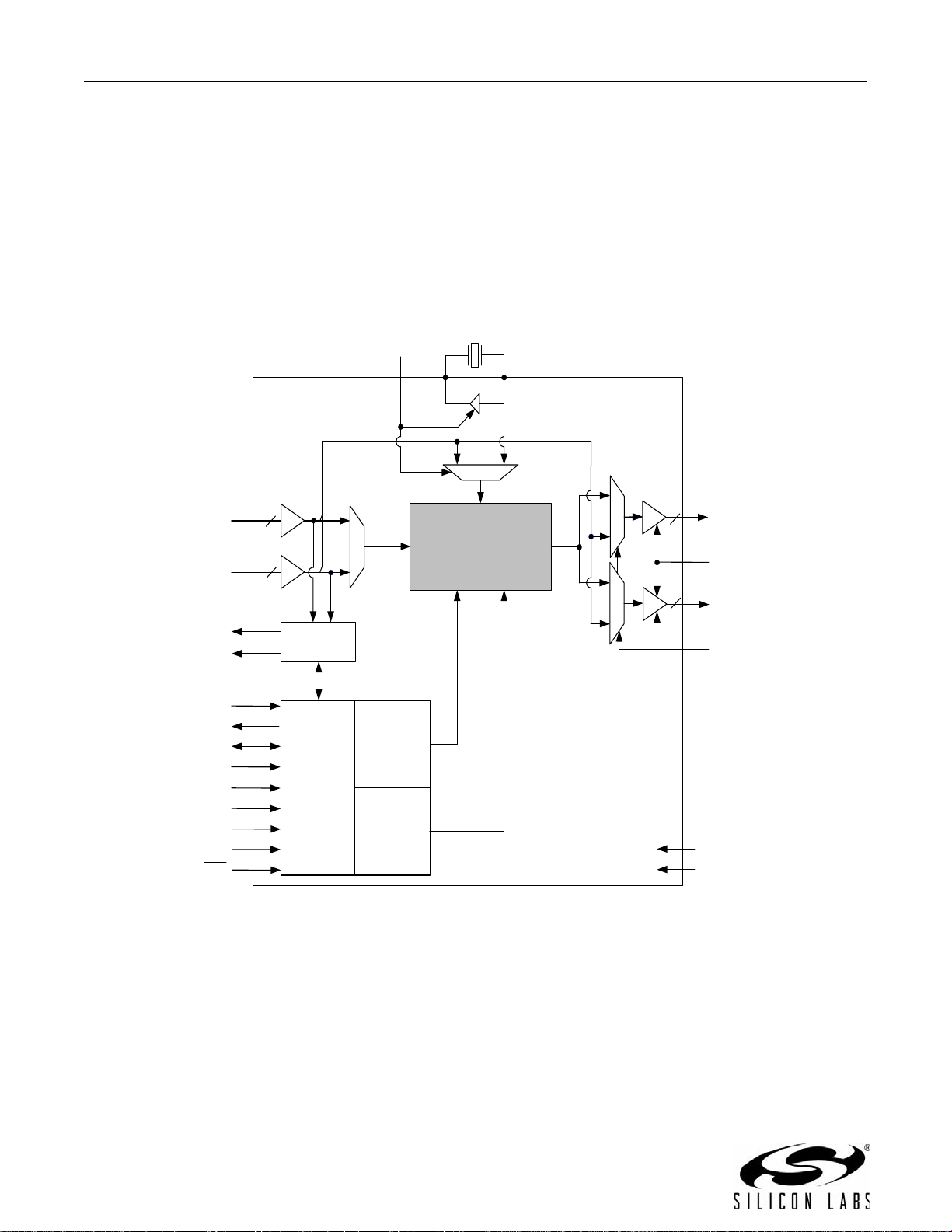

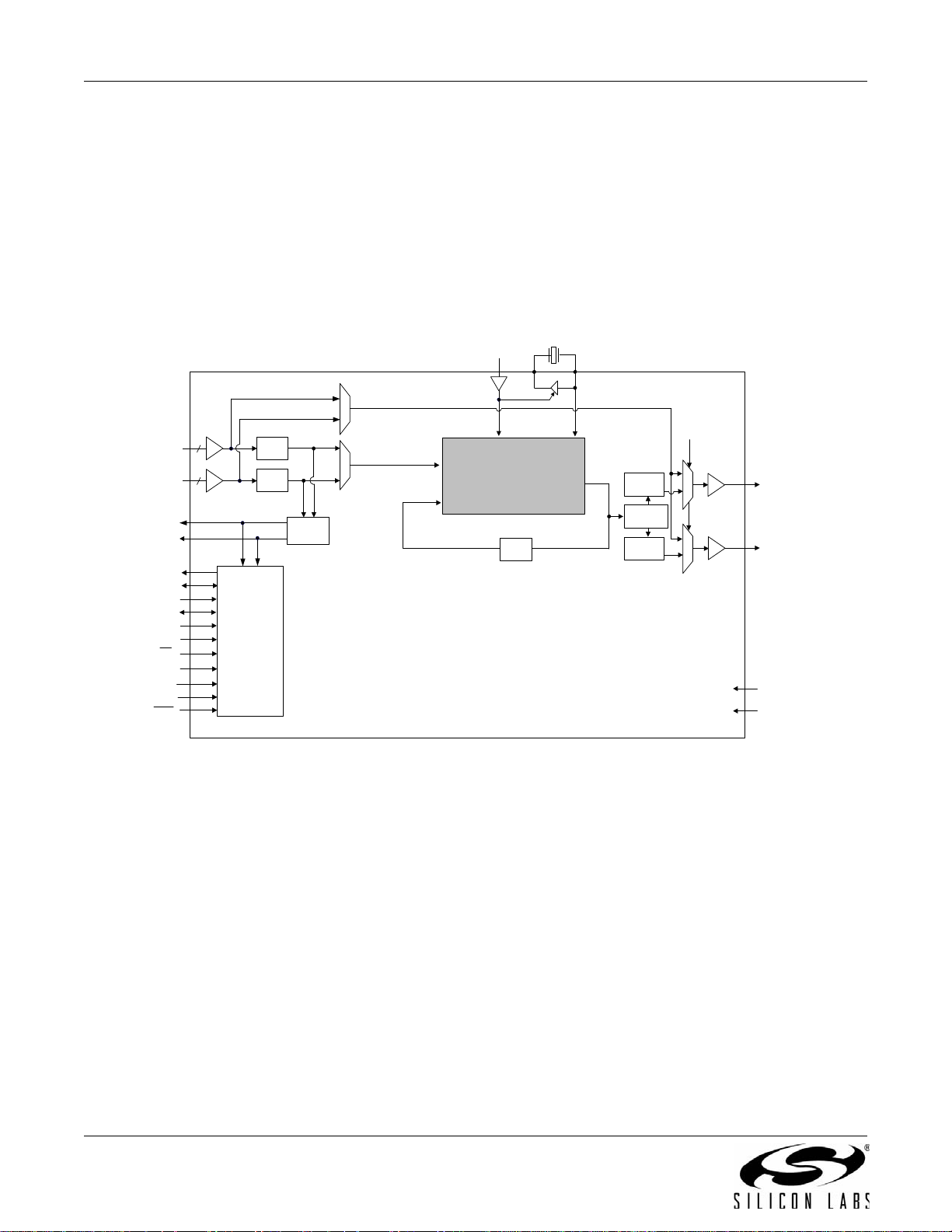

3.2. Si5319

The Si5319 is a jitter-attenuating precision M/N clock multiplier for applications requiring sub 1 ps jitter

performance. The Si5319 accepts one clock input ranging from 2 kHz to 710 MHz and generates one clock output

ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The Si5319 can also use its crystal oscillator as

a clock source for frequency synthesis. The device provides virtua lly any frequency translation combination across

this operating range. The Si5319 input clock frequency and clock multiplication r atio are programmable through an

I2C or SPI interface. The Si5319 is based on Silicon Laboratories' 3rd-generation DSPLL

provides any-frequency synthesis and jitter attenuation in a highly integrated PLL solution that eliminates the need

for external VCXO and loop filter components. The DSPLL loop bandwidth is digitally programmable, providing

jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5319

is ideal for providing clock multiplication and jitter attenuation in high performance timing applications. See "7.

Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374,

Si5375)" on page 76 for a complete description.

®

technology, which

Figure 2. Si5319 Any-Frequency Jitter Attenuating Clock Multiplier Block Diagram

18 Rev. 0.5

Si53xx-RM

DSPLL

®

C1B

CS_CA

BWSEL[1:0]

DBL2_BY

SFOUT[1:0]

CKOUT_2+

CKOUT_2–

CKIN_1+

CKIN_1–

CKOUT_1+

CKOUT_2–

CKIN_2+

CKIN_2–

Control

AUTOSEL

FRQTBL

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

2

FRQSEL[3:0]

RST

0

1

f

OSC

2

2

0

1

0

1

f

3

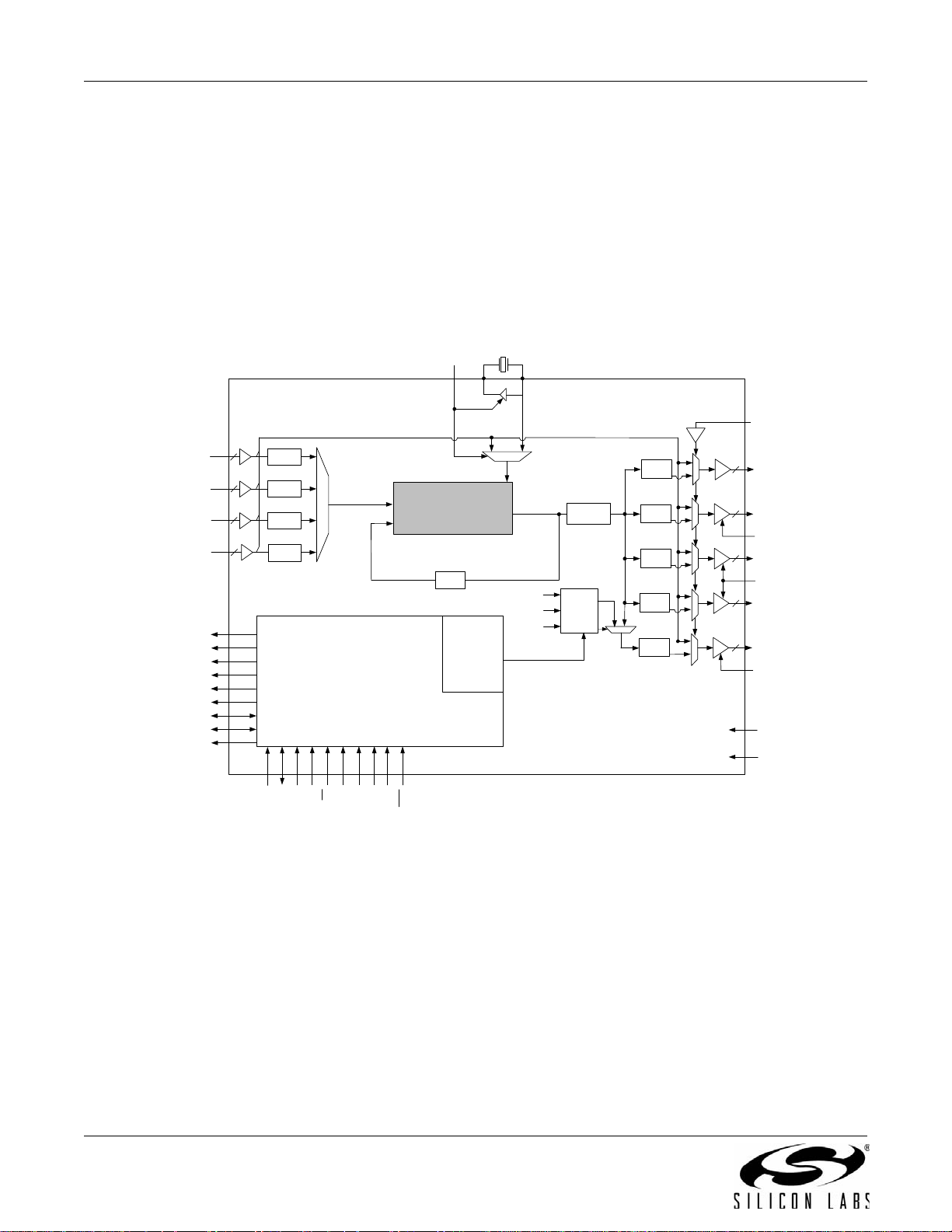

3.3. Si5322

The Si5322 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5322 acce pts dual clock inputs ranging from 19.44 to 707 MHz and generates two frequencymultiplied clock outputs ranging from 19.44 to 1050 MHz. The input clock frequency and clock multiplication ratio

are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI)

rates. The DSPLL loop bandwidth is digitally selectable from 150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5,

or 3.3 V supply, the Si5322 is ideal for providing low jitter clock multiplication in high performance timing

applications. See "6. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete

description.

Figure 3. Si5322 Low Jitter Clock Multiplier Block Diagram

Rev. 0.5 19

Si53xx-RM

DSPLL

®

C1B

LOL

CS/CA

BWSEL[1:0]

DBL2/BY

Xtal or R e fc lo ck

SFOUT[1:0]

CKOUT_2+

CKOUT_2–

CKIN_1+

CKIN_1–

CKOUT_1+

CKOUT_1–

CKIN_2+

CKIN_2–

Control

AUTOSEL

FRQTBL

Signal

Detect

VDD

GND

Frequency

Control

Bandwidth

Control

C2B

2

2

FRQSEL[3:0]

INC

DEC

RST

0

1

RATE[1:0]

XA

XB

f

OSC

2

2

0

1

0

1

f

3

3.4. Si5323

The Si5323 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including

SONET OC-48/OC-192, Ethernet, Fibre Channel, and broadcast video (HD SDI, 3G SDI). The Si5323 accepts

dual clock inputs ranging from 8 kHz to 707 MHz and generates two frequency-multiplied clock outputs ranging

from 8 kHz to 1050 MHz. The input clock frequency and clock multiplication ratio are selectable from a table of

popular SONET, Ethernet, Fibre Channel, and broadcast video rates. The DSPLL loop bandwidth is digitally

selectable, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or

3.3 V supply, the Si5323 is ideal for providing clock multiplication and jitter attenuation in high-performance timing

applications. See "6. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete

description.

20 Rev. 0.5

Figure 4. Si5323 Jitter Attenuating Clock Multiplier Block Diagram

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0 ]

LOL

CS_CA

SDA_SDO

INC

DEC

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

3.5. Si5324

The Si5324 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5324 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides

virtually any frequency translation combination across this operating range. The Si5324 input clock frequency and

clock multiplication ratios are programmable th rough an I

programmable, providing jitter performance optimization at the application level. The Si5324 features loop

bandwidth values as low as 4 Hz. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5324 is ideal for providing

clock multiplication and jitter attenuation in high-performance timing applications. See "7. Microprocessor

Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76

for a complete description.

2

C or SPI interface. The DSPLL loop bandwid th is digit ally

Figure 5. Si5324 Clock Multiplier and Jitter Attenuator Block Diagram

Rev. 0.5 21

Si53xx-RM

÷ N31

INT_C1B

÷ NC1

÷ NC2

Signal

Detect

C2B

0

1

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

SDA_SDO

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

CMODE

CKIN_1 +

CKIN_1 –

2

2

CKIN_2 +

CKIN_2 –

÷ N32

0

1

BYPASS

÷ N2

f

3

DSPLL

®

VDD

GND

÷ N1_HS

f

OSC

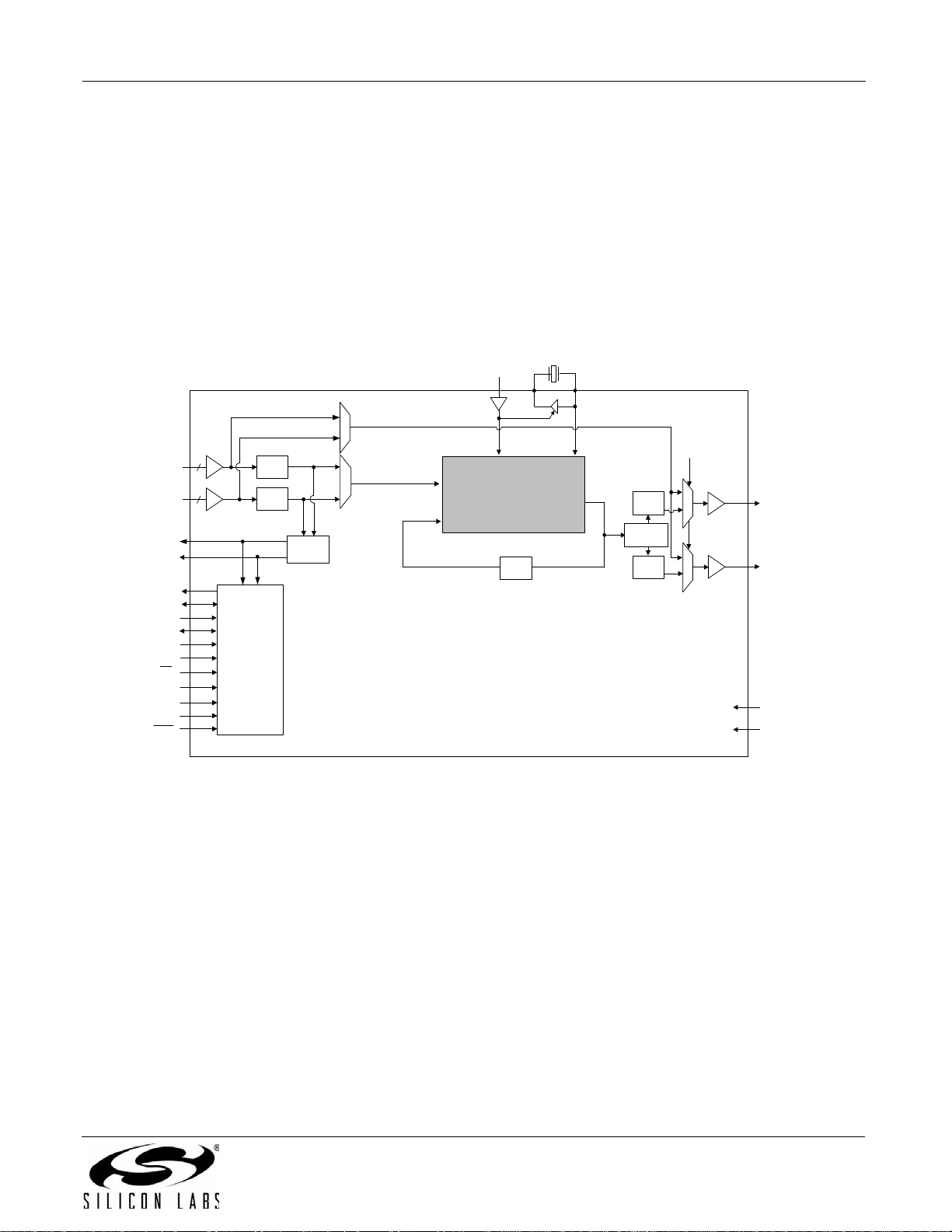

3.6. Si5325

The Si5325 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5325 accepts dual clock inputs ranging from 10 to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The Si5325 input

clock frequency and clock multiplication ratios are programmable through an I

bandwidth is digitally program mable from 150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5, or 3.3 V supply, the

Si5325 is ideal for providing clock multiplication in high performance timing applications. See "7. Microprocessor

Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76

for a complete description.

2

C or SPI interface. The DSPLL loop

Figure 6. Si5325 Low Jitter Clock Multiplier Block Diagram

22 Rev. 0.5

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0]

LOL

CS_CA

SDA_SDO

INC

DEC

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

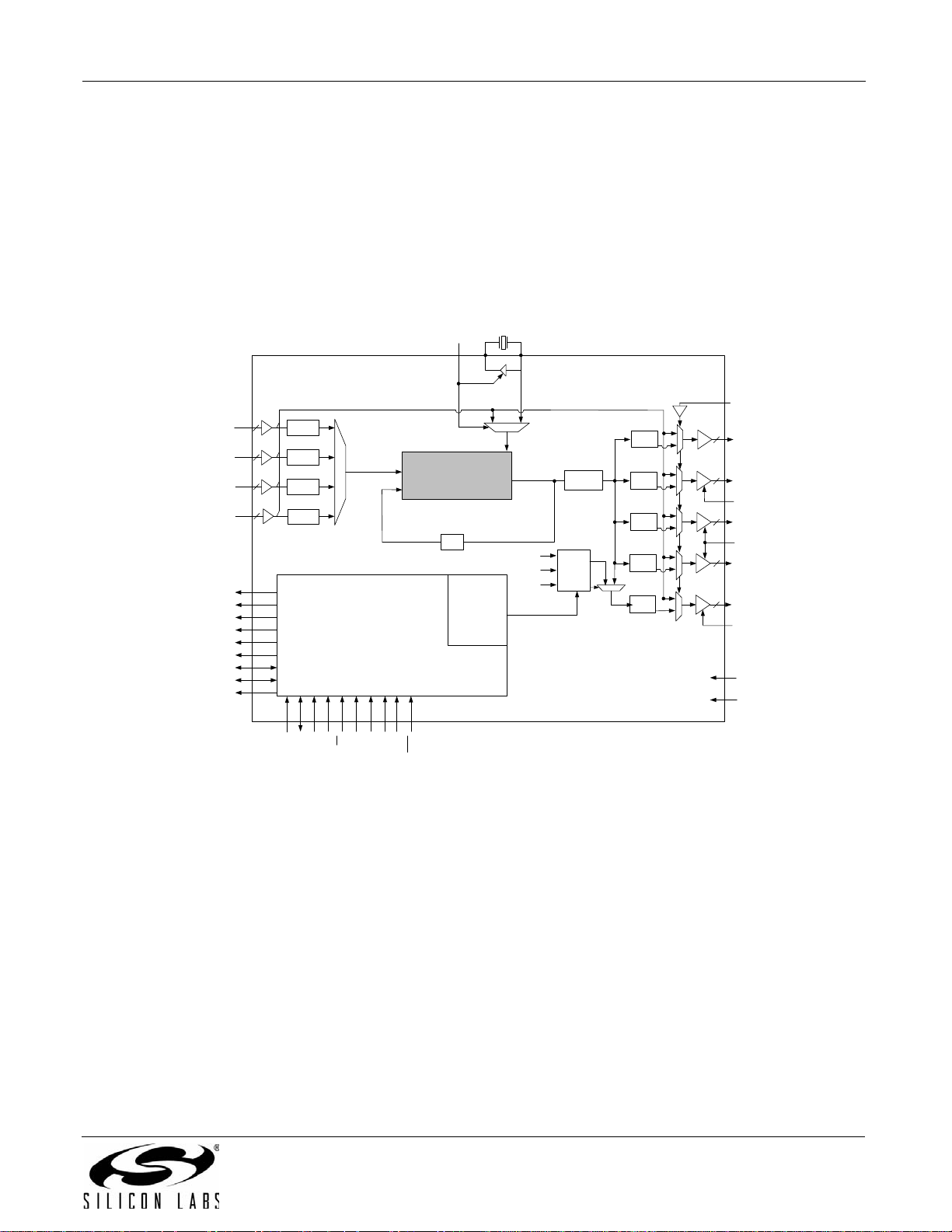

3.7. Si5326

The Si5326 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5326 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The device provides

virtually any frequency translation combination across this operating range. The Si5326 input clock frequency and

clock multiplication ratios are programmable th rough an I

programmable from 60 Hz to 8 kHz, providing jitter performance optimization at the application level. Operating

from a single 1.8, 2.5, or 3.3 V suppl y, the Si5326 is ideal for providing clock multiplication and jitter atte nuation in

high-performance timing applications. See "7. Microprocessor Controlled Parts (Si5319, Si5324, Si5325, Si5326,

Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76 for a complete description.

2

C or SPI interface. The DSPLL loop bandwid th is digit ally

Figure 7. Si5326 Clock Multiplier and Jitter Attenuator Block Diagram

Rev. 0.5 23

Si53xx-RM

÷ N31

INT_C1B

Xtal or Re fc lo c k

÷ NC1

÷ NC2

Signal

Detect

VDD

GND

C2B

0

1

f

3

CKOUT_2 +

CKOUT_2 –

CKOUT_1 +

CKOUT_1 –

/

/

2

2

1

0

1

0

f

OSC

RATE[1:0 ]

LOL

CS_CA

SDA_SDO

INC

DEC

RST

SCL

Control

SDI

A[2]/SS

A[1:0]

XAXB

CMODE

CKIN_ 1 +

CKIN_ 1 –

2

2

CKIN_ 2 +

CKIN_ 2 –

÷ N32

0

1

3

BYPASS

÷ N2

DSPLL

÷ N1_HS

DSPLL

®

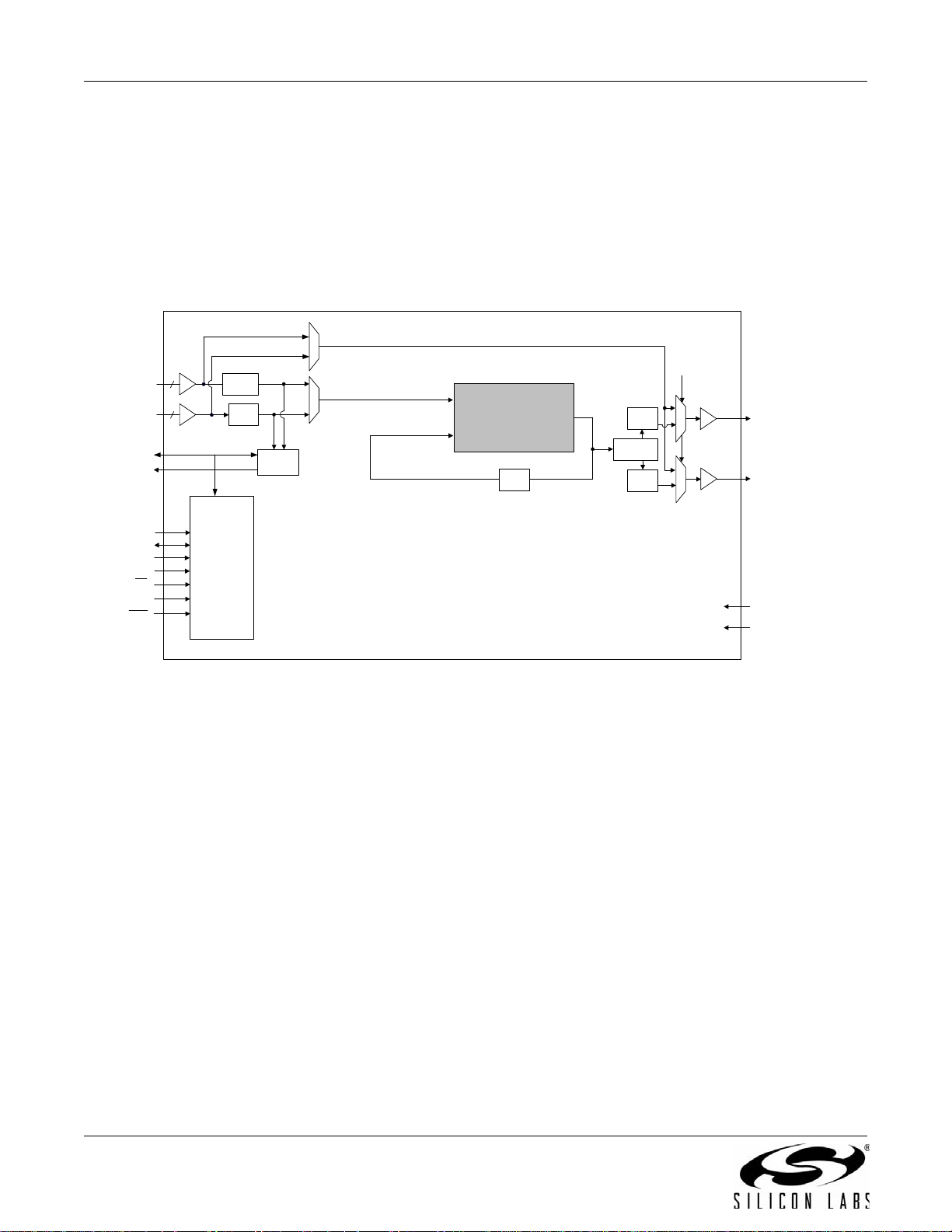

3.8. Si5327

The Si5327 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps jitter performance.

The Si5327 accepts dual clock inputs ranging from 2 kHz to 710 MHz and generates two independent,

synchronous clock outputs ranging from 2 kHz to 808 MHz. The device provides virtually any frequency translation

combination across this operating range. The Si5327 input clock frequency and clock multiplication ratios are

programmable through an I

jitter performance optimization at the application level. The Si5327 features loop bandwidth values as low as 4 Hz.

Operating from a single 1.8, 2. 5, or 3.3 V supply, the Si5327 is ideal for providing clock multiplication and jitter

attenuation in high-performance timing applications. See "7. Microprocessor Controlled Parts (Si5319, Si5324,

Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76 for a complete description.

2

C or SPI interface. The DSPLL loop bandwidth is digitally programmable, providing

Figure 8. Si5327 Clock Multiplier and Jitter Attenuator Block Diagram

24 Rev. 0.5

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

ALRMOUT

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

f

3

DBL2_BY

DBL34

DBL5

BWSEL[1:0]

FRQSEL[3:0]

DIV34[1:0]

FOS_CTL

SFOUT[1:0]

RST

CMODE

AUTOSEL

BYPASS/

DSBL2

Control

÷ N3_2

÷ N3_1

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

FRQTBL

DIV34[1:0]

÷ N1_HS

DSPLL

®

÷ N2

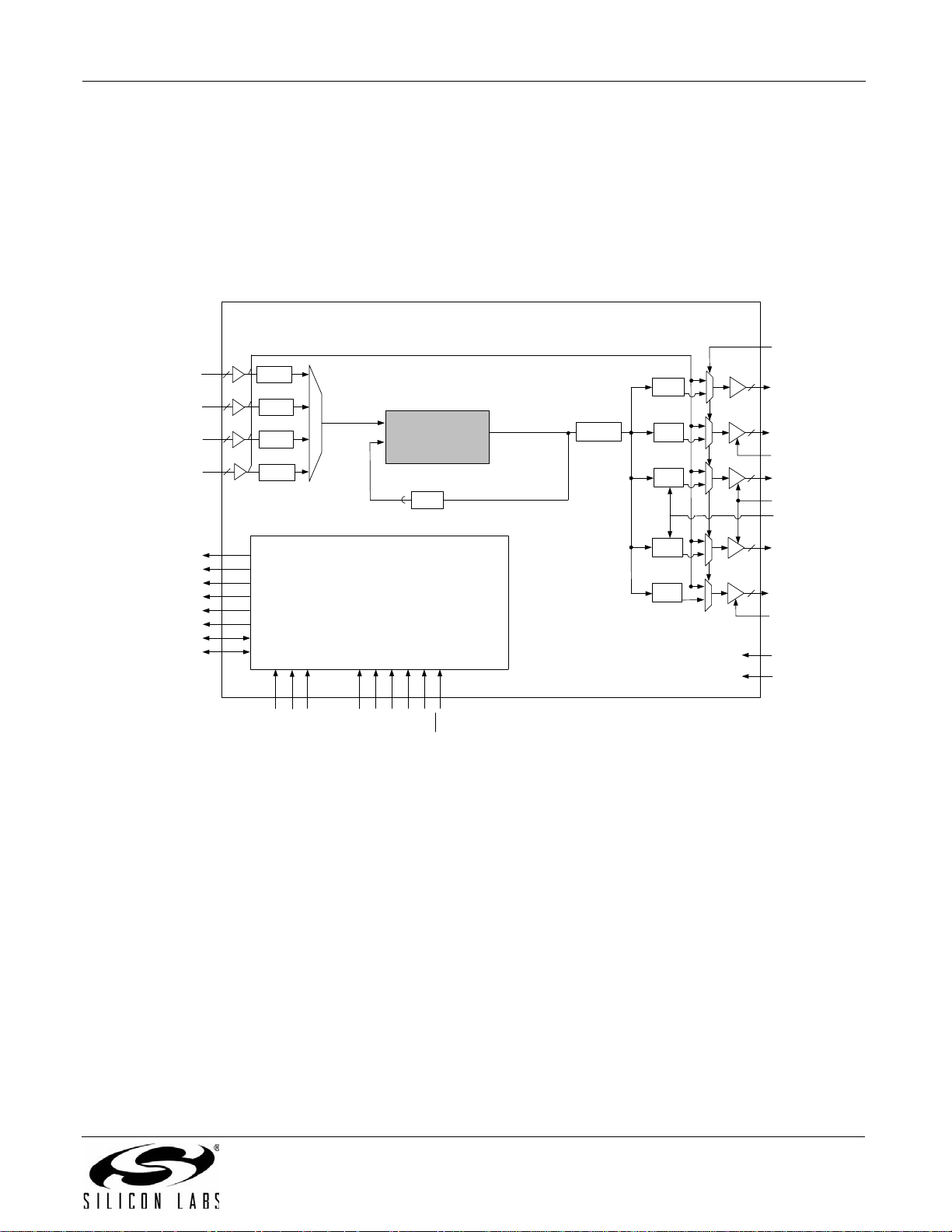

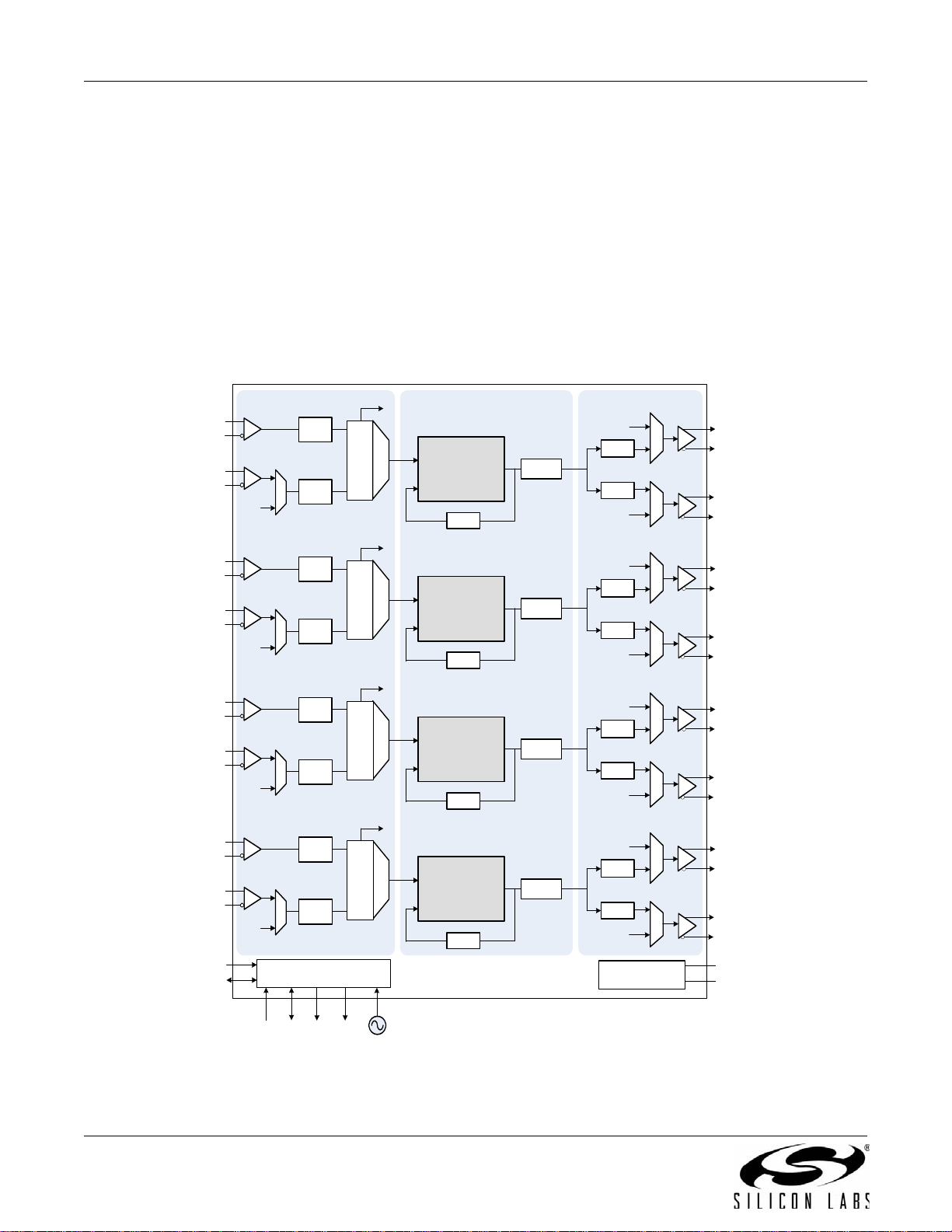

3.9. Si5365

The Si5365 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5365 accepts four clock inputs ranging from 19.44 MHz to 707 MHz and generates five

frequency-multiplied clock outputs ranging from 19.44 MHz to 1050 MHz. The input clock frequency and clock

multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel, and broadcast video

rates. The DSPLL loop bandwidth is digitally selectable. Operating from a single 1.8, 2.5 V, or 3.3 V supply, the

Si5365 is ideal for providing clock multiplication in high performance timing applications. See "6. Pin Control Parts

(Si5316, Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete descr iption.

Figure 9. Si5365 Low Jitter Clock Multiplier Block Diagram

Rev. 0.5 25

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

ALRMOUT

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

CKIN_3

CKIN_4

CKOUT_2

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

Xtal or Refclock

RATE[1:0]

XA

XB

f

x

f

3

DBL2_BY

DBL34

DBL5

FSYNC

LOGIC/

ALIGN

CK_CONF

BWSEL[1:0]

FRQSEL[3:0]

DIV34[1:0]

FOS_CTL

SFOUT[1:0]

INC

DEC

FS_SW

FS_ALIGN

RST

CMODE

AUTOSEL

BYPASS/DSBL2

LOL

Control

÷ N3_2

÷ N3_1

FSYNC

3

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

1

0

FRQTBL

DIV34[1:0]

÷ N1_HS

DSPLL

®

÷ N2

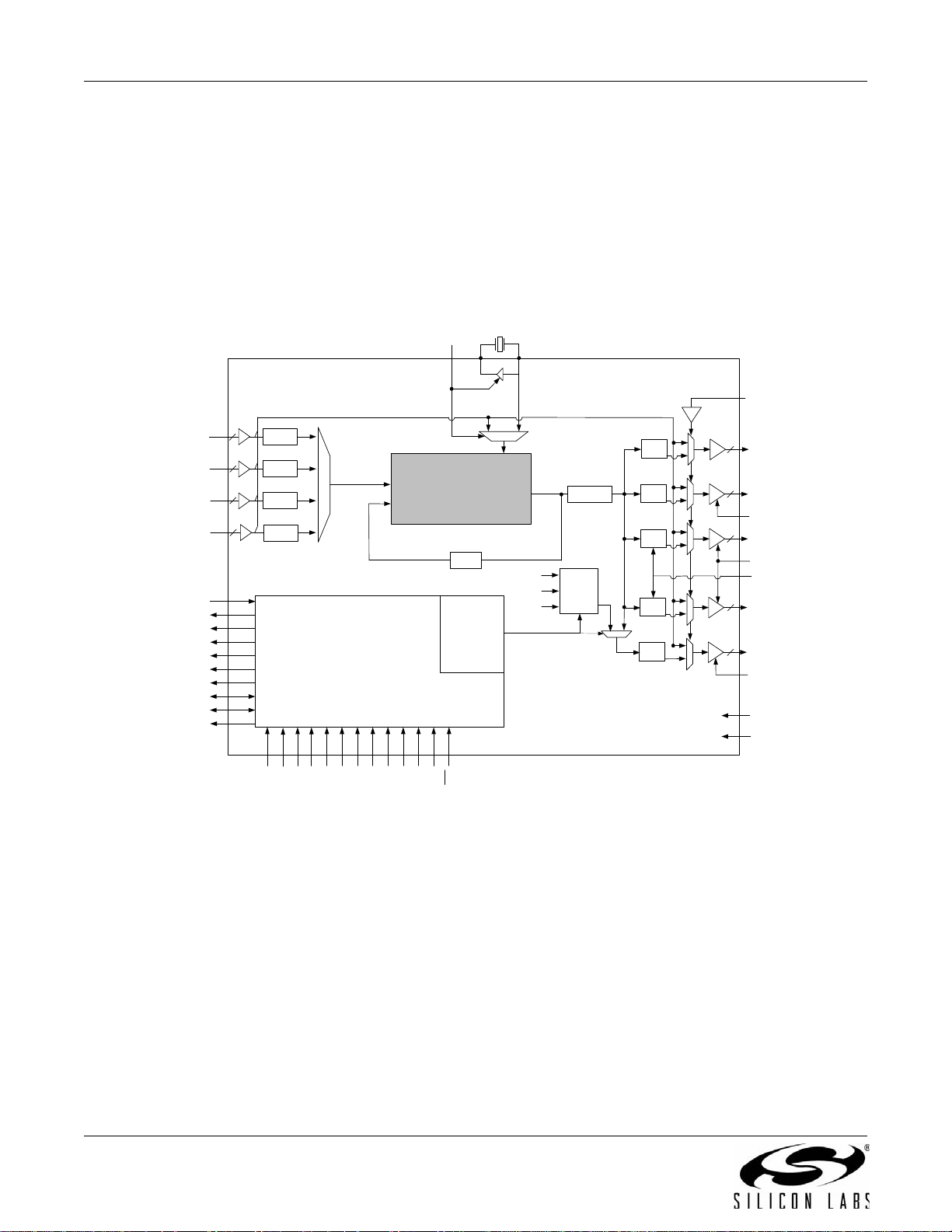

3.10. Si5366

The Si5366 is a jitter-attenuating precision clock multiplier for high-speed communication systems, including

SONET OC-48/OC-192, Etherne t, and Fibr e Chan nel. T he S i53 66 acce pts four clo ck inp uts ranging fr om 8 kHz to

707 MHz and generates five frequency-multiplied clock outputs ranging from 8 kHz to 1050 MHz. The input clock

frequency and clock multiplication ratio are selectable from a table of popular SONET, Ethernet, Fibre Channel,

and broadcast video (HD SDI, 3G SDI) rates. The DSPLL loop bandwidth is digitally selectable from 60 Hz to

8 kHz, providing jitter performance optimization at the application level. Operating from a single 1.8, 2.5, or 3.3 V

supply, the Si5366 is ideal for providing clock multiplication and jitter attenuation in high performance timing

applications. See "6. Pin Control Parts (Si5316, Si5322, Si5323, Si5365, Si5366)" on page 50 for a complete

description.

26 Rev. 0.5

Figure 10. Si5366 Jitter Attenuating Clock Multiplier Block Diagram

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

INT_ALM

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

f

3

DSBL2/BYPASS

DSBL34

DSBL5

SDA_SDO

SCL

SDI

A[1:0]

RST

CMODE

BYPASS/DSBL2

Control

÷ N3_2

÷ N3_1

÷ N2

3

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

A[2]/SS

÷ N1_HS

DSPLL

®

3.11. Si5367

The Si5367 is a low jitter, precision clock multiplier for applications requiring clock multiplication without jitter

attenuation. The Si5367 accepts four clock inputs ranging from 10 to 707 MHz and generates five frequencymultiplied clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The Si5367 input clock

frequency and clock multiplication ratio are programmable through an I

bandwidth is digitally program mable from 150 kHz to 1.3 MHz. Operating from a single 1.8, 2.5, or 3.3 V supply, the

Si5367 is ideal for providing clock multiplication in high performance timing applications. See "7. Microprocessor

Controlled Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76

for a complete description.

2

C or SPI interface. The DSPLL loop

Figure 11. Si5367 Clock Multiplier Block Diagram

Rev. 0.5 27

Si53xx-RM

C2A

CS0_C3A

C2B

CS1_C4A

INT_ALM

C1A

CKIN_1+

CKIN_1–

CKIN_2+

CKIN_2–

C3B

CKIN_3+

CKIN_3–

CKIN_4+

CKIN_4–

C1B

CKIN_3

CKIN_4

CKOUT_2

VDD

GND

CKOUT_1+

CKOUT_1–

÷ NC1

1

0

CKOUT_2+

CKOUT_2–

÷ NC2

1

0

CKOUT_3+

CKOUT_3–

÷ NC3

1

0

CKOUT_4+

CKOUT_4–

÷ NC4

1

0

2

2

2

2

2

2

2

2

f

OSC

Xtal or Refc lock

RATE[1:0]

XA

XB

f

x

DSBL2/BYPASS

DSBL34

DSBL5

FSYNC

LOGIC/

ALIGN

SDA_SDO

SCL

SDI

A[1:0]

INC

DEC

FS_ALIGN

RST

CMODE

BYPASS/DSBL2

LOL

Control

÷ N3_2

÷ N3_1

FSYNC

÷ N2

÷ N3_3

÷ N3_4

CKOUT_5+

CKOUT_5–

÷ NC5

1

0

2

1

0

A[2]/SS

÷ N1_HS

DSPLL

®

f

3

3

3.12. Si5368

The Si5368 is a jitter-attenuating precision clock multiplier for applications requiring sub 1 ps rms jitter

performance. The Si5368 accepts four clock inputs ranging from 2 kHz to 710 MHz and generates five

independent, synchronous clock outputs ranging from 2 kHz to 945 MHz and select frequencies to 1.4 GHz. The

device provides virtually any frequency translation combination across this operating range. The Si5368 input clock

frequency and clock multiplication ratio are programmable through an I

bandwidth is digitally programmable from 60 Hz to 8 kHz, providing jitter performance optimization at the

application level. Operating from a single 1.8, 2.5, or 3.3 V supply, the Si5368 is ideal for providing clock

multiplication and jitter attenuation in high performance timing applications. See "7. Microprocessor Controlled

Parts (Si5319, Si5324, Si5325, Si5326, Si5327, Si5367, Si5368, Si5369, Si5374, Si5375)" on page 76 for a

complete description.