RECISION CLOCK MULTIPLIER/REGENERATOR

P

Features

Complete precision clock multiplier and clock regenerator device:

Si5310

P

RELIMINARY DATA SHEET

IC

!

Performs Clock Multiplication to

One of Two Frequency Ranges:

150–167 MHz or 600–668 MHz

!

Jitter Generation as low as

0.5 ps

!

Accepts Input Clock from

for 622 MHz Output

RMS

9.4–668 MHz

!

Regenerates a “Clean”, JitterAttenuated Version of Input

Clock

!

DSPLL™ Technology Provides

Superior Jitter Performance

!

Small Footprint: 4 mm x 4 mm

!

Low Power: 310 mW typical

Applications

!

SONET/SDH Systems

!

Terabit Routers

!

Digital Cross Connects

!

Optical Transceiver Modules

!

Gigabit Ethernet Systems

!

Fibre Channel

Description

The Si5310 is a fully integrated low-power clock multiplier and clock

regenerator IC. The clock multiplier generates an output clock that is an

integer multiple of the input clock. The clock regenerator operates

simultaneously, creating a “clean” version of the input clock by using the

clock synthesis phase-locked loop (PLL) to remove unwanted jitter and

square up the input clock’s rising and falling edges. The Si5310 uses

Silicon Laboratories patented DSPLL

jitter performance while eliminating the analog loop filter found in

traditional PLL designs with a digital signal-processing algorithm.

The Si5310 represents a new standard in low jitter, small size, low power,

and ease-of-use for clock devices. It operates from a single 2.5 V supply

over the industrial temperature range (–40°C to 85°C).

™

architecture to achieve superior

Ordering Information:

See page 20.

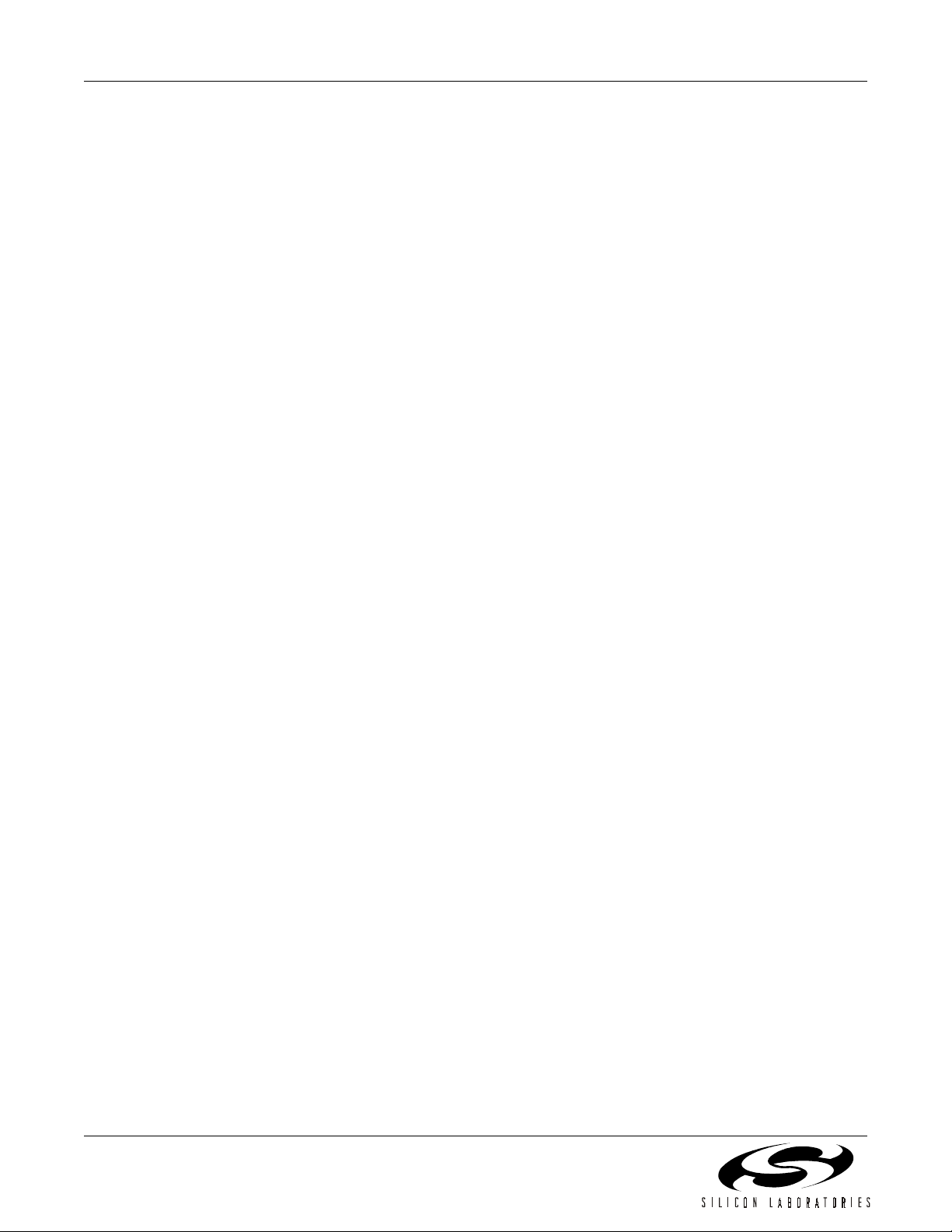

Pin Assignments

Si5310-BM

NC

20 19 18 17 16

REXT

1

VDD

2

GND

3

REFCLK+

REFCLK–

4

5

6 7 8 9 10

LOL

M ULTSEL

GND

Pa d

VDD

MULTOUT–

MULTOUT+

GND

15

PW RD N

VDD

14

CLKOUT+

13

12

CLKOUT–

11

VDD

GND

CLKIN–

CLKIN+

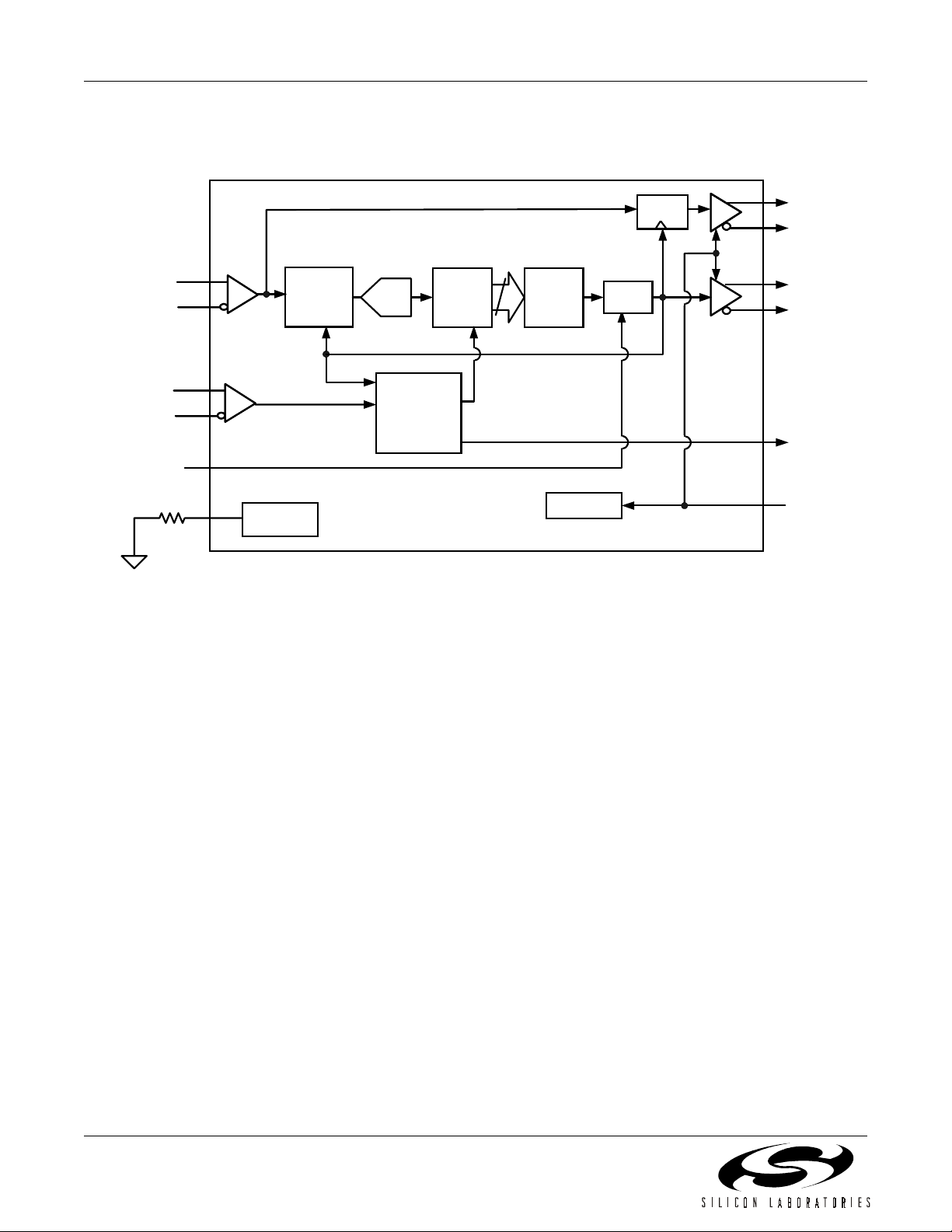

Functional Block Diagram

2

CLKIN+

CLKIN–

Regeneration

TM

2

BUF

DSPLL

Phase-Locked

Calibra tion

Loop

2

REFCLK+

REFCLK–

MULTSE L

Bias Gen

BUF

BUF

REXT

Preliminary Rev. 0.6 6/01 Copyright © 2001 by Silicon Laboratories Si5310-DS06

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

2

CLKOUT+

CLKOUT–

PWRD N/CAL

MULTOUT+

MULTOUT–

LOL

Si5310

2 Preliminary Rev. 0.6

Si5310

T

ABLE OF

C

ONTENTS

Section Page

Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

DSPLL™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clock Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

1x Multiplication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clock Regeneration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Reference Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

DSPLL Lock Detection (Loss-of-Lock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

PLL Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Device Power-Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Device Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Differential Input Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Pin Descriptions: Si5310-BM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

BM Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Preliminary Rev. 0.6 3

Si5310

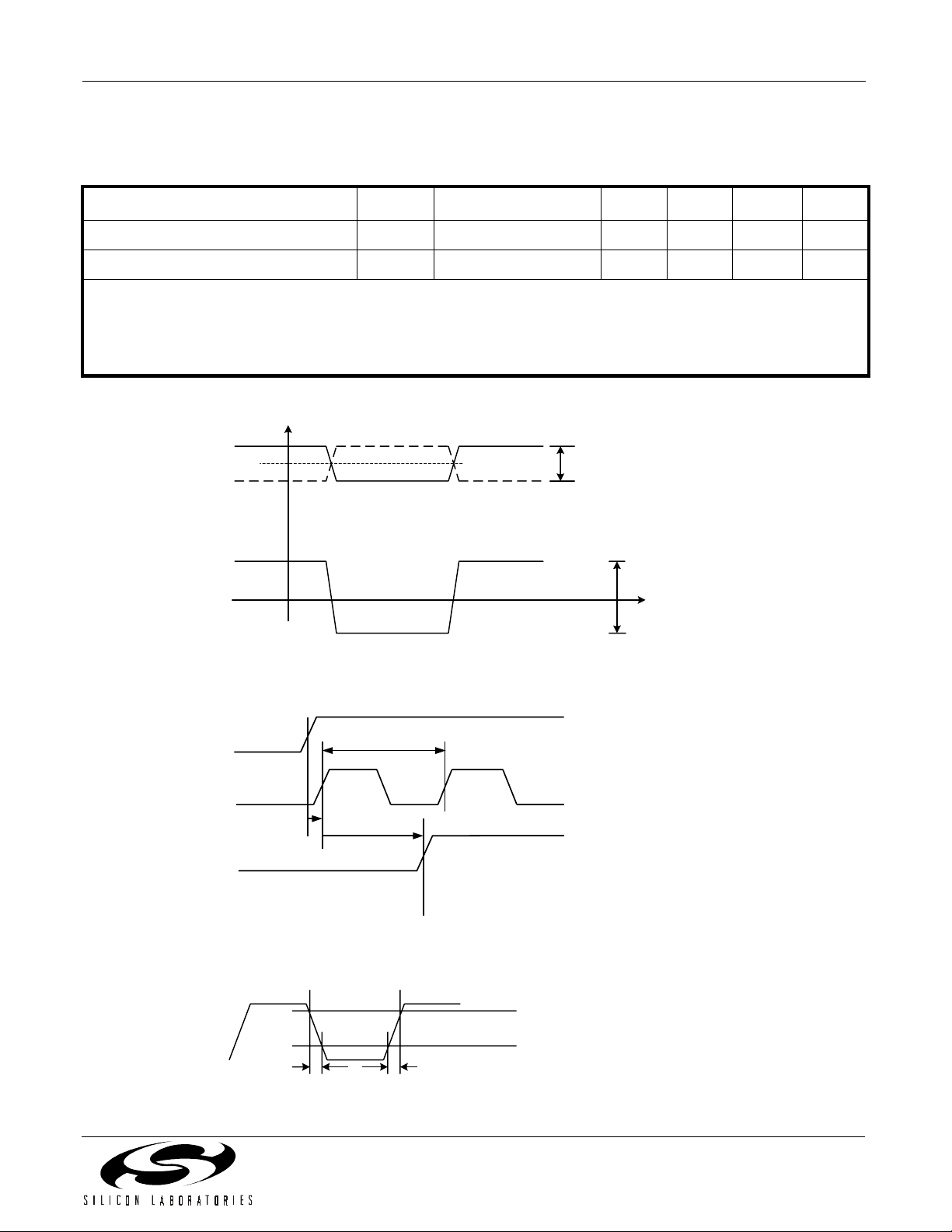

Detailed Block Diagram

CLKIN+

CLKIN–

REFCLK+

REFCLK+

REFCLK–

MULTSEL

REXT

Detector

Detector

Detector

Bias

Bias

Bias

Generation

Generation

Generation

Phase

Phase

Phase

A/D

DSP

n

Lock

Detector

Figure 1. Detailed Block Diagram

VCO

Calibration

CLK

Divider

Regen

Retime

Retime

c

CLKOUT+

CLKOUT–

c

MULTOUT+

MULTOUT–

LOL

PWRDN/CAL

4 Preliminary Rev. 0.6

Electrical Specifications

Table 1. Recommended Operating Conditions

Si5310

Parameter Symbol Test Condition

Ambient Temperature T

Si5310 Supply Voltage

2

A

V

DD

1

Min

Typ

–40 25 85 °C

2.375 2.5 2.625 V

Max

1

Notes:

1. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25°C unless otherwise stated.

2. The Si5310 specifications are guaranteed when using the recommended application circuit (including component

tolerance) of Figure 5 on page 11.

V

SIGNAL +

Differential

I/Os

V

ICM

SIGNAL –

, V

OCM

V

IS

(SIGNAL +) – (SIGNAL –)

Differential

Voltage Swing

VID,V

OD

Differential Peak-to-Peak Voltage

t

Unit

Figure 2. Differential Voltage Measurement (CLKIN, REFCLK, CLKOUT, MULTOUT)

CLKIN

MULTOUT

CLKOUT

t

CI-M

1/f

t

M-CO

MULT

Figure 3. CLKIN to CLKOUT, MULTOUT Phase Relationship

CLKIN,

REFCLK,

CLKOUT,

MULTOUT

t

F

t

R

80%

20%

Figure 4. Clock Input and Output Rise/Fall Times

Preliminary Rev. 0.6 5

Si5310

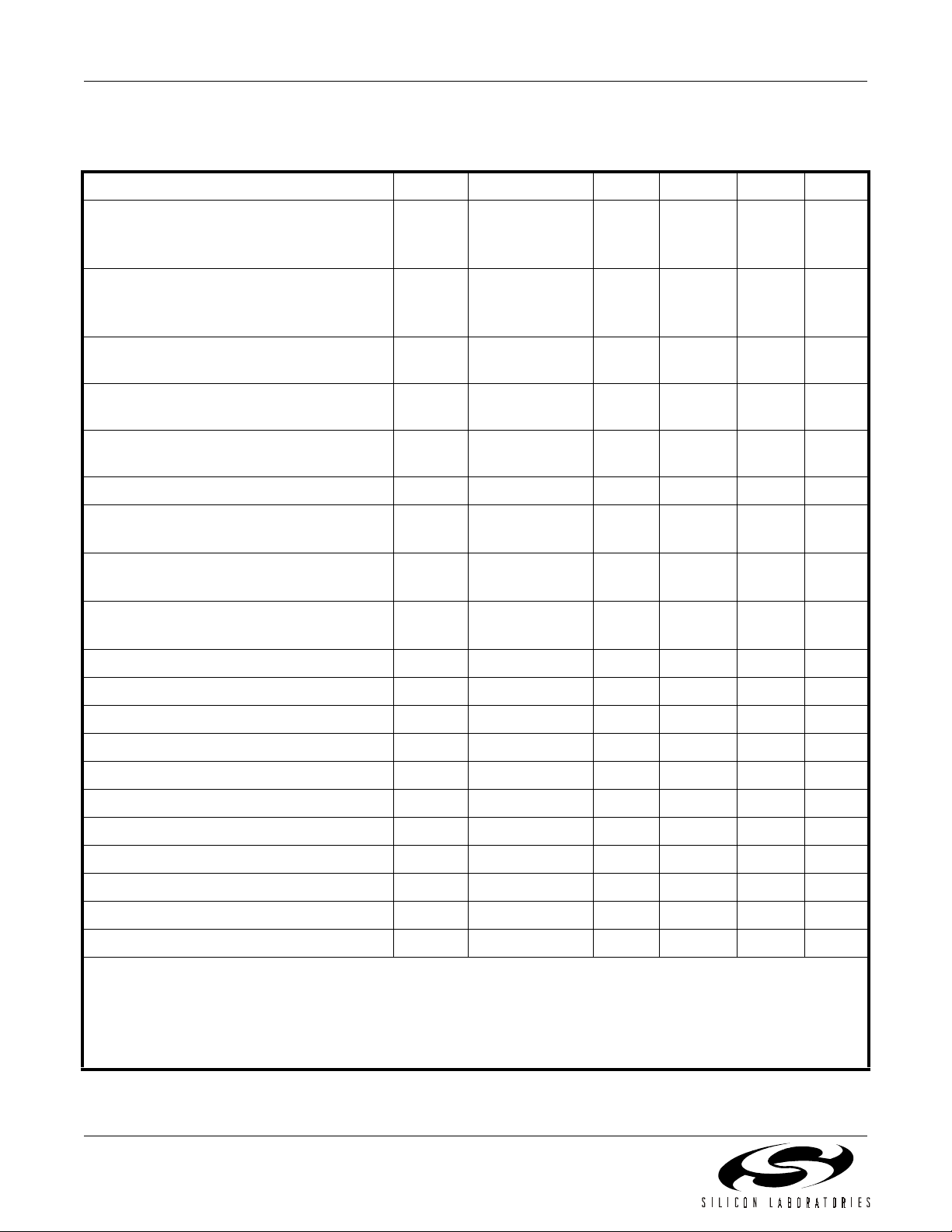

Table 2. DC Characteristics, VDD = 2.5 V, 622 Mbps (MULTSEL = 0)

(VDD = 2.5 V ± 5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Supply Current

MULTSEL = 0

MULTSEL = 1

Power Dissipation

MULTSEL = 0

MULTSEL = 1

Common Mode Input Voltage

V

I

DD

P

ICM

—

—

D

—

—

See Figure 2 — .80"V

117

124

293

310

DD

127

mA

134

333

mW

352

—V

(CLKIN, REFCLK)

Input Voltage Range*

V

IS

See Figure 2 — — 750 mV

(CLKIN+, CLKIN–, REFCLK+, REFCLK–)

Differential Input Voltage Swing*

V

ID

(CLKIN, REFCLK)

Input Impedance (CLKIN, REFCLK) R

Differential Output Voltage Swing

IN

V

OD

(CLKOUT)

Differential Output Voltage Swing

V

OD

(MULTOUT)

Output Common Mode Voltage

V

OCM

(CLKOUT, MULTOUT)

Output Impedance (CLKOUT, MULTOUT) R

Output Short to GND (CLKOUT, MULTOUT) I

Output Short to V

(CLKOUT, MULTOUT) I

DD

Input Voltage Low (LVTTL Inputs) V

Input Voltage High (LVTTL Inputs) V

Input Low Current (LVTTL Inputs) I

Input High Current (LVTTL Inputs) I

Output Voltage Low (LVTTL Outputs) V

Output Voltage High (LVTTL Outputs) V

Input Impedance (LVTTL Inputs) R

PWRDN/CAL Internal Pulldown Current I

*Note: The CLKIN and REFCLK inputs may be driven differentially or single-endedly. When driving single-endedly, the voltage

swing of the signal applied to the active input must exceed the specified minimum Differential Input Voltage Swing (V

min) and the unused input must be ac-coupled to ground. When driving differentially, the difference between the

positive and negative input signals must exceed VID min. (Each individual input signal needs to swing only half of this

range.) In either case, the voltage applied to any individual pin (CLKIN+, CLKIN–, REFCLK+, or REFCLK–) must not

exceed the specified maximum Input Voltage Range (V

OUT

SC(–)

SC(+)

IL

IH

IL

IH

OL

OH

IN

PWRDNVPWRDN

See Figure 2 200 — 1500 mV

Line-to-Line 84 100 116 Ω

100 Ω Load

TBD 940 TBD mV

Line-to-Line

100 Ω Load

TBD 900 TBD mV

Line-to-Line

100 Ω Load

—VDD–0.7 — V

Line-to-Line

Single-ended 84 100 116 Ω

—25TBDmA

TBD –15 — mA

—— .8V

2.0 — — V

—25TBDµA

—25TBDµA

IO = 2 mA — — 0.4 V

IO = 2 mA 2.0 — — V

100 — — kΩ

≥ 0.8 V TBD 25 TBD µA

max).

IS

(pk-pk)

(pk-pk)

(pk-pk)

ID

6 Preliminary Rev. 0.6

Si5310

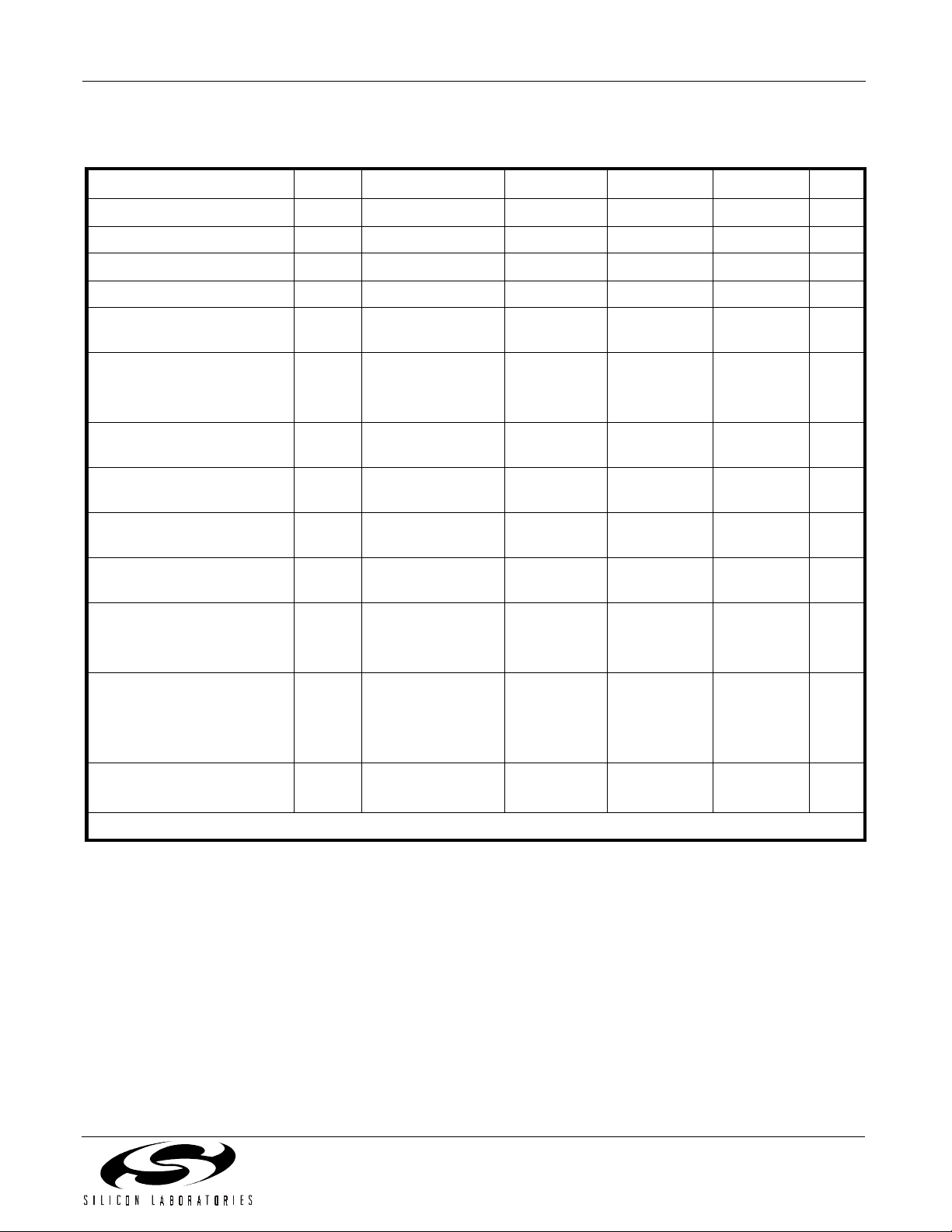

Table 3. AC Characteristics

(VDD = 2.5 V ± 5%, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

CLKIN Frequency Range

*

CLKIN Duty Cycle TBD — TBD %

REFCLK Range

*

9.375 — 668 MHz

9.375 — 167 MHz

REFCLK Duty Cycle C

REFCLK Frequency

Tol era nc e

MULTOUT Clock Rate

MULTOUT = 0

MULTOUT = 1

Output Rise Time

(CLKOUT, MULTOUT)

Output Fall Time

(CLKOUT, MULTOUT)

Input Rise Time

(CLKIN, REFCLK)

Input Fall Time

(CLKIN, REFCLK)

CLKIN to MULTOUT Delay

MULTSEL = 0

MULTSEL = 1

MULTOUT to CLKOUT

Delay

MULTSEL = 0

MULTSEL = 1

DUTY

C

TOL

f

MULT

t

t

t

t

t

CI-M

t

M-CO

40 50 60 %

–100 — 100 ppm

600

150

R

F

R

F

Figure 4 — 100 TBD ps

Figure 4 — 100 TBD ps

Figure 4 — — TBD ps

Figure 4 — — TBD ps

—

—

668

167

MHz

Figure 3

TBD

TBD

150

3.4

TBD

TBD

ps

ns

Figure 3

TBD

TBD

1/f

MULT

960

+160

TBD

TBD

ps

ps

Input Return Loss 100 kHz–2.5 GHz

2.5 GHz–4.0 GHz

*Note: See Table 9.

Preliminary Rev. 0.6 7

18.7

TBD

—

—

—

—

dB

Loading...

Loading...