Silicon Laboratories Si5110-BC Datasheet

Si5110

:0

T

B

Bottom View

PRELIMINA RY DATA SHEET

SiPHY™ OC-48/STM-16 SONET/SDH TRANSCEIVER

Features

Complete low power, high speed, SONET/SDH transceiver with

integrated limiting amp, CDR, CMU, and MUX/DEMUX

Data Rates Supported:

OC-48/STM-16 and 2.7 Gbps FEC

Low Power Operation 1.0 W (typ)

DSPLL™ Based Clock Multiplier Unit

w/ Selectable Loop Filter Bandwidths

Integrated Limiting Amplifier

Diagnostic and Line Loopbacks

SONET Compliant Loop Timed

Operation

Programmable Slicing Level and

Sample Phase Adjustment

LVDS Parallel Interfa ce

Single Supply 1.8 V Ope ratio n

11 x 11 mm B GA Package

Applications

Sonet/SDH Transmission

Systems

Optical Transc eiv e r Mo dules

Sonet/SDH Test Equipment

Si5110

Ordering Information:

See pa ge2 3.

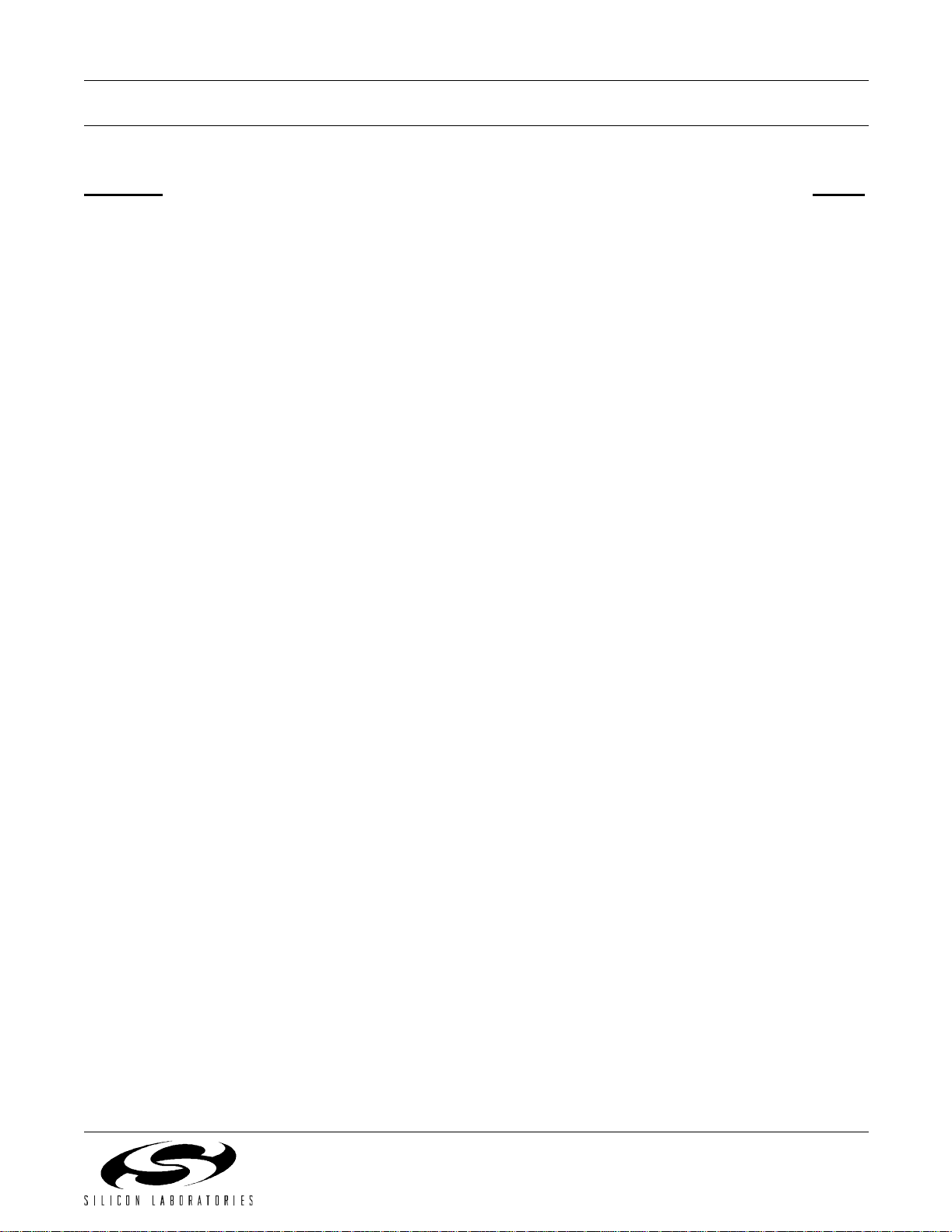

Description

The Si5110 is a complete low-power transceiver for high-speed serial

communication systems operating between 2.5 Gbps and 2.7 Gbps. The receive

path consists of a fully integrated lim iting amplifier, clock and data recover y unit

(CDR), and 1:4 deserializer. The transmit path combines a low jitter clock

multiplier unit (CMU) with a 4:1 serializer. The CMU uses Silicon Laboratories’

™

DSPLL

technology to provide superior jitter performance while reducing design

complexity by eliminating external loop filter components. To simplify BER

optimization in long haul applications, programmable slicing, and sample phase

adjustment are supported.

The Si5110 operates from a single 1.8 V supply over the industrial temperature

range (–40°C to 85°C).

Functional Block Diagram

LOS

LOSLVL

RXDIN

REFSEL

REFCLK

LPTM

REFRATE

TXLO L

BWSEL

TXCLKDSBL

TXCLKOUT

TXSQLCH

TXDOUT

RESET

SLICELVL

2

Limiting

AMP

2

TXCLK4IN

2

2

PHASEADJ

RESET

Control

LTR

CDR

DSPLL

TX CMU

RXLOL

tm

Loopback Control

DLBKLLBK

RXSQLCH

1:4

÷

÷

4:1

TXMSBSEL

DEMUX

MUX

8

2

2

FIFO

FIFOERR

2

2

8

RXMSBSEL

RXDOUT[3

RXCLK1

RXCLK2

RXCLK2DIV

RXCLK2DS

TXCLK4OU

TXCLK4IN

TXD IN[3:0]

FIFORST

Preliminary Rev. 0.41 8/ 01 Copyright © 2001 by Silicon Labora tories Si5110-DS041

This in formation applies to a product under devel opment. I ts characteristics and specifications are subject to change without notice.

Si5110

2 Preliminary Rev. 0.41

Si5110

TABLE OF CONTENTS

Section Page

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Limiting Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Clock and Data Recovery (CDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Deserialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Auxiliary Clock Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Data Squelch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

DSPLL™ Clock Multiplier Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Serialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Loop Timed Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Diagnostic Loopback . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Voltage Reference Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Transmit Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Si5110 Pinout: 99-Pin BGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Pin Descriptions: Si5110 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Preliminary Rev. 0.41 3

Si5110

t

t

Electrical Specifications

Table 1. Recommended Operating Condit ions

Parameter Symbol Test Condition

Ambient Temperatur e T

LVTTL Output Supply Voltage V

Si5110 Supply Voltage V

*Note: All minimum and maximum specifications are guaranteed and apply across the rec om me nded operating conditions.

T ypical values apply at nominal supply voltages and an operating temper ature of 25°C unless otherwise st ated.

A

DD33

DD

*

Min

Typ

–40 25 85 °C

1.71 — 3.47 V

1.71 1.8 1.89 V

Max

*

Unit

V

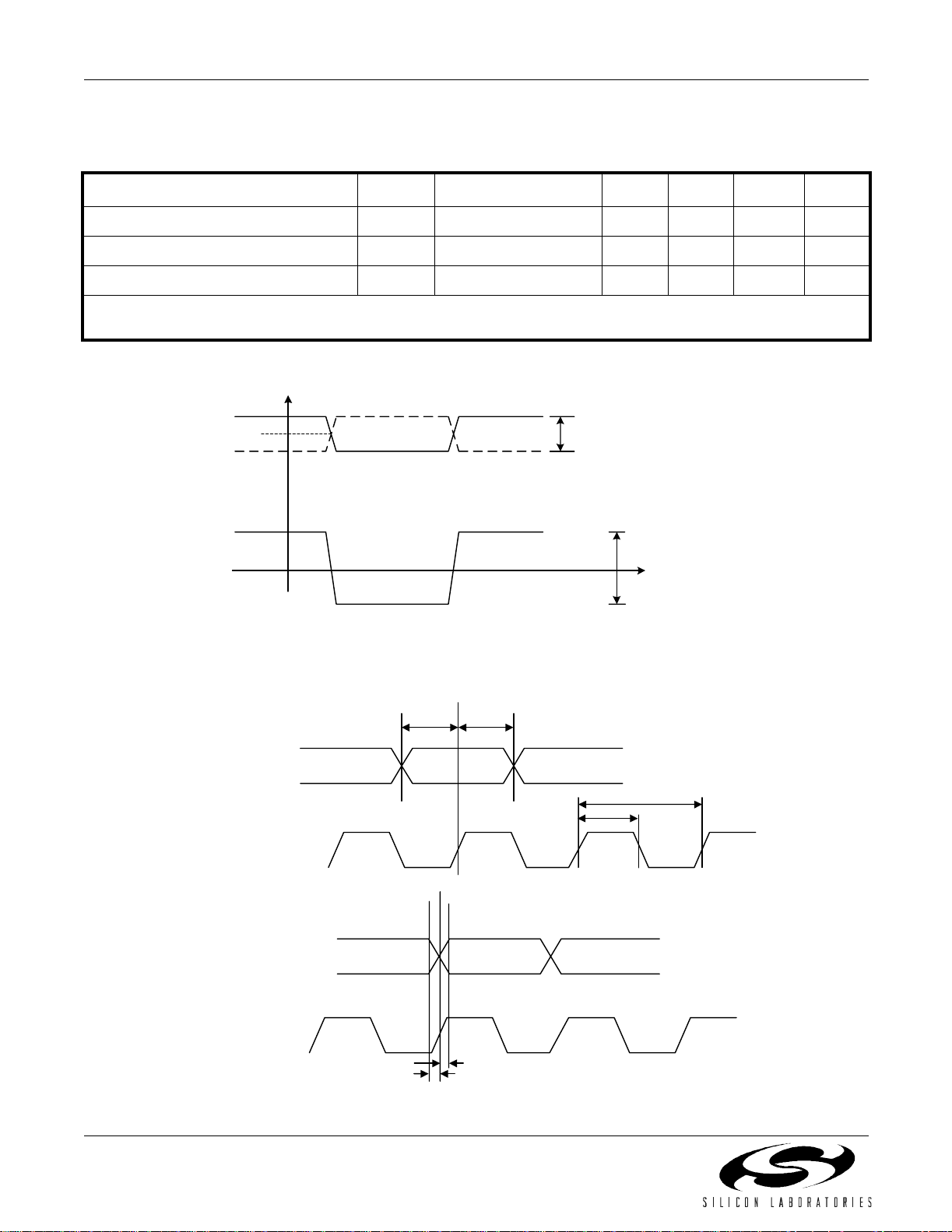

SIGNAL +

Differential

I/Os

V

ICM

SIGNAL –

, V

OCM

V

IS

Single Ended Voltage

(SIGNAL +) – (SIGNAL –)

Differential

Voltage Swing

VID,VOD (V

= 2VIS)

ID

Differential Peak-to-Peak Voltage

t

Figure 1. Differential Voltage Measurement

(RXDIN, RXDOUT, RXCLK1, RXCLK2, TXDIN, TXDOUT, TXCLKOUT, TXCLK4OUT, TXCLK4IN)

TXDOUT,

TXDIN

TXCLKOUT,

TXCLK4IN

RXDOUT

RXCLK1

su

hd

t

t

CH

CP

t

t

cq1

cq2

Figure 2. Data to Clock Delay

4 Preliminary Rev. 0.41

Si5110

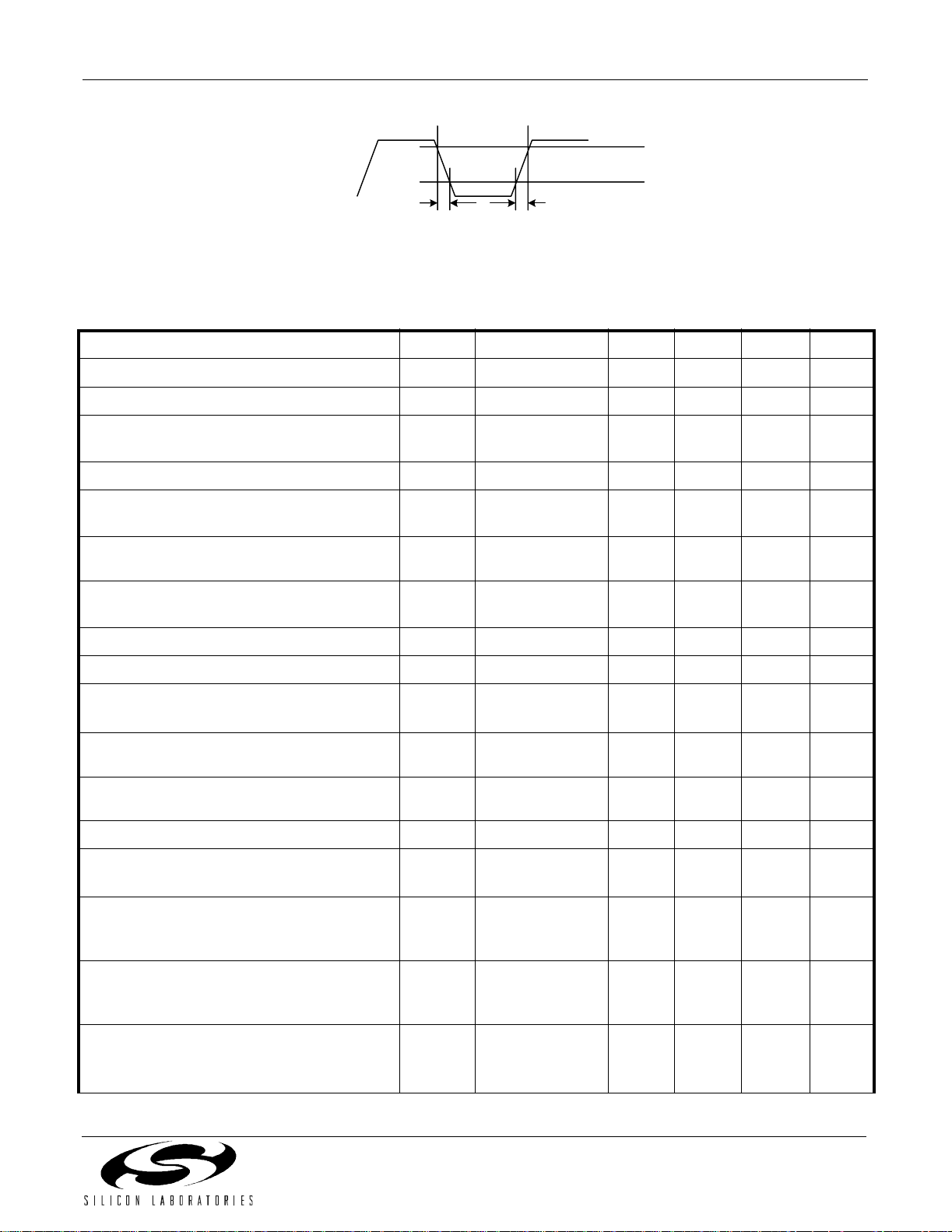

All

80%

Differential

IOs

t

F

t

R

20%

Figure 3. I/O Rise/Fall Times

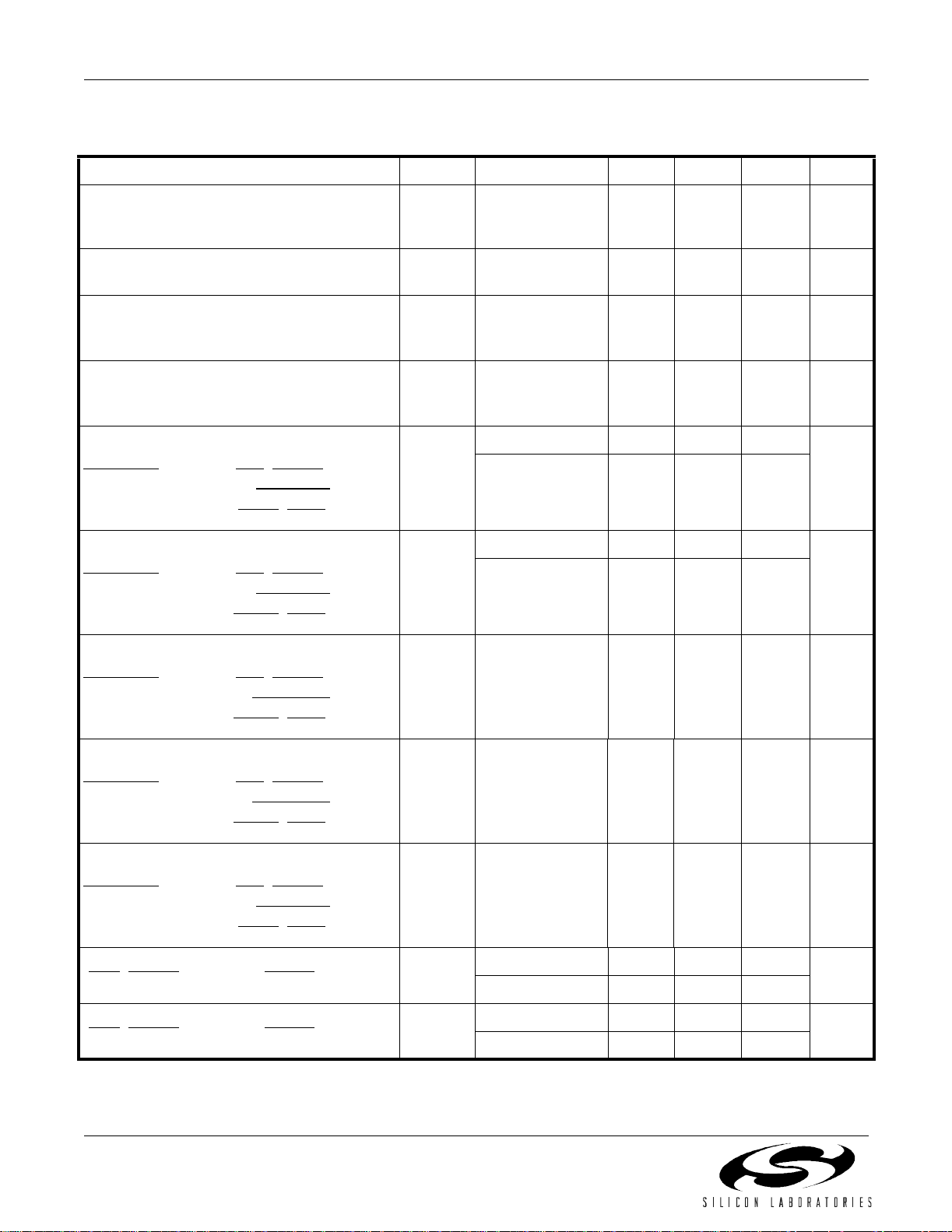

Table 2. DC Characteristic s

(VDD = 1.8 V ±5% , TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Supply Current I

Power Dissipation P

Voltage Reference (VREF) V

Common Mode Input Voltage (RXDIN) V

Differential Input Voltage Swing (RXDIN) V

Common Mode Output Voltage

V

(TXDOUT, TXCLKOUT)

Differential Output Voltage Swing

V

(TXDOUT, TXCLKOUT), Differential pk-pk

DD

D

REF

ICM

ID

OCM

OD

VREF driving

Ω load

10 k

See Figure 1 10 — 1.0 mV

See Figure 1 800 1000 1200 mV

—611TBDmA

—1.0TBDW

1.21 1.25 1.29 V

TBD 0.1 TBD V

(pk-pk)

.8 0.9 1.0 V

(pk-pk)

L VPECL Input Voltage HIGH (REFCLK) V

L VPECL Input Voltage LOW (REFCLK) V

L VPECL Input Voltage Swing,

Differential pk-pk (REFCLK)

LVPECL Internally Gene rated Input Bias

(REFCLK)

L VDS Input High Voltage (TXDIN,

TXCLK4IN)

L VDS Input Low Voltage (TXDIN, TXCLK4IN) V

L VDS Input Voltage, Single Ended pk-pk

V

(TXDIN, TXCLK4IN)

LVDS Output High Voltage

V

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT)

LVDS Output Low Voltage

V

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT)

L VDS Output Voltage, Differential pk-pk

V

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT)

V

V

V

ISE

OH1

OL1

OSE

IH

IL

ID

IB

IH

IL

1.975 2.3 2.59 V

1.32 1.6 1.99 V

Figure 1 250 — 2400 mV

1.6 1.95 2.3 V

——2.4V

0.0 — — V

100 — 600 mV

100 Ω Load

TBD — 1.475 mV

Line-to-Line

100 Ω Load

0.925 — TBD V

Line-to-Line

100 Ω Load

500 — 800 mV

Line-to-Line,

Figure 1

(pk-pk)

(pk-pk)

(pk-pk)

Preliminary Rev. 0.41 5

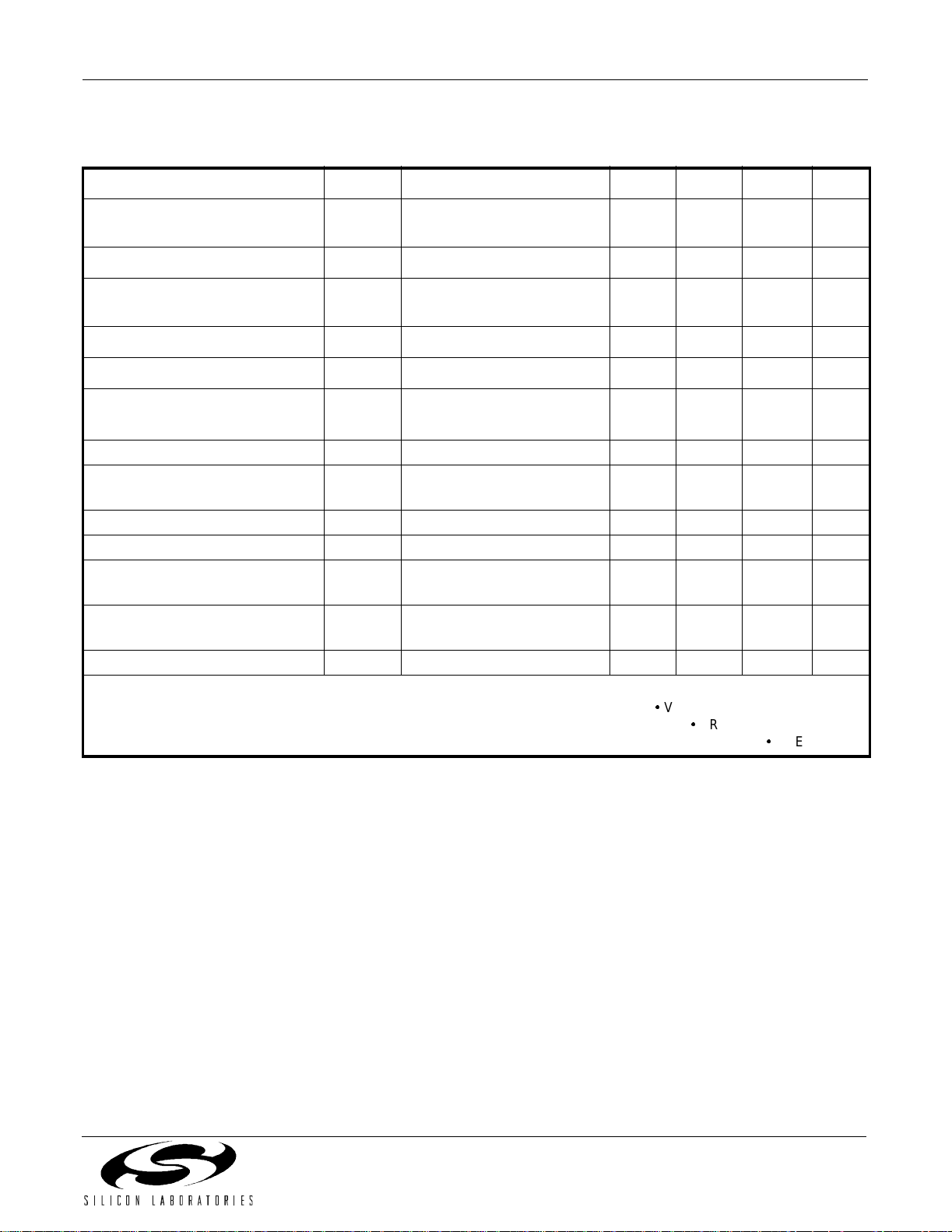

Si5110

Table 2. DC Characteristic s (Con tinued)

(VDD = 1.8 V ±5% , TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

L VDS Common Mode Voltage

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT)

Input Impedance (TXDIN, TXCLK4I N,

REFCLK, RXDIN)

Output Short to GND

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT, TXDOUT, TXCLKOUT)

Output Short to V

DD

(RXDOUT, RXCLK1, RXCLK2,

TXCLK4OUT, TXDOUT, TXCLKOUT)

LVTTL Input Voltage Low

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

TXCLKDSBL, FI FOR ST, TXSQL CH

BWSEL, TXMSBSEL, DLBK

, REFSEL, LTR, RESET, MODE16

,

, LLBK, LPTM)

LVTTL Input Voltage High

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

TXCLKDSBL, FI FOR ST, TXSQL CH

BWSEL, TXMSBSEL, DLBK

, REFSEL, LTR, RESET, MODE16

,

, LLBK, LPTM)

LVTTL Input Low Current

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

TXCLKDSBL, FI FOR ST, TXSQL CH

BWSEL, TXMSBSEL, DLBK

, REFSEL, LTR, RESET, MODE16

,

, LLBK, LPTM)

LVTTL Input High Current

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

TXCLKDSBL, FI FOR ST, TXSQL CH

BWSEL, TXMSBSEL, DLBK

, REFSEL, LTR, RESET, MODE16

,

, LLBK, LPTM)

L VTTL Input Impedance

(RXMSBSEL, RXCLK2DIV, RXCLK2DSBL,

RXSQLCH

TXCLKDSBL, FI FOR ST, TXSQL CH

BWSEL, TXMSBSEL, DLBK

, REFSEL, LTR, RESET, MODE16

,

, LLBK, LPTM)

LVTTL Output Voltage Low

(LOS

, RXLOL, FIFOERR, TXL OL)

V

CM

R

I

SC(–)

I

SC(+)

V

IL2

V

IH2

I

IL

I

IH

R

V

OL2

1.125 — 1.275 V

IN

Each input to

42 50 58 Ω

common mode

—25TBDmA

TBD –100 — µA

VDD33 = 3.3 V — — 0.8 V

VDD33 = 1.8 V — — 0.7

VDD33 = 3.3 V 2.0 — — V

VDD33 = 1.8 V 1.7

——10µA

——10µA

IN

10 — — kΩ

VDD33 = 1.8 V — — 0.4 V

VDD33 = 3.3 V — — 0.4

LVTTL Output Voltage High

(LOS

, RXLOL, FIFOERR, TXL OL)

6 Preliminary Rev. 0.41

V

OH2

VDD33 = 1.8 V 1.4 — — V

VDD33 = 3.3 V 2.4 — —

Si5110

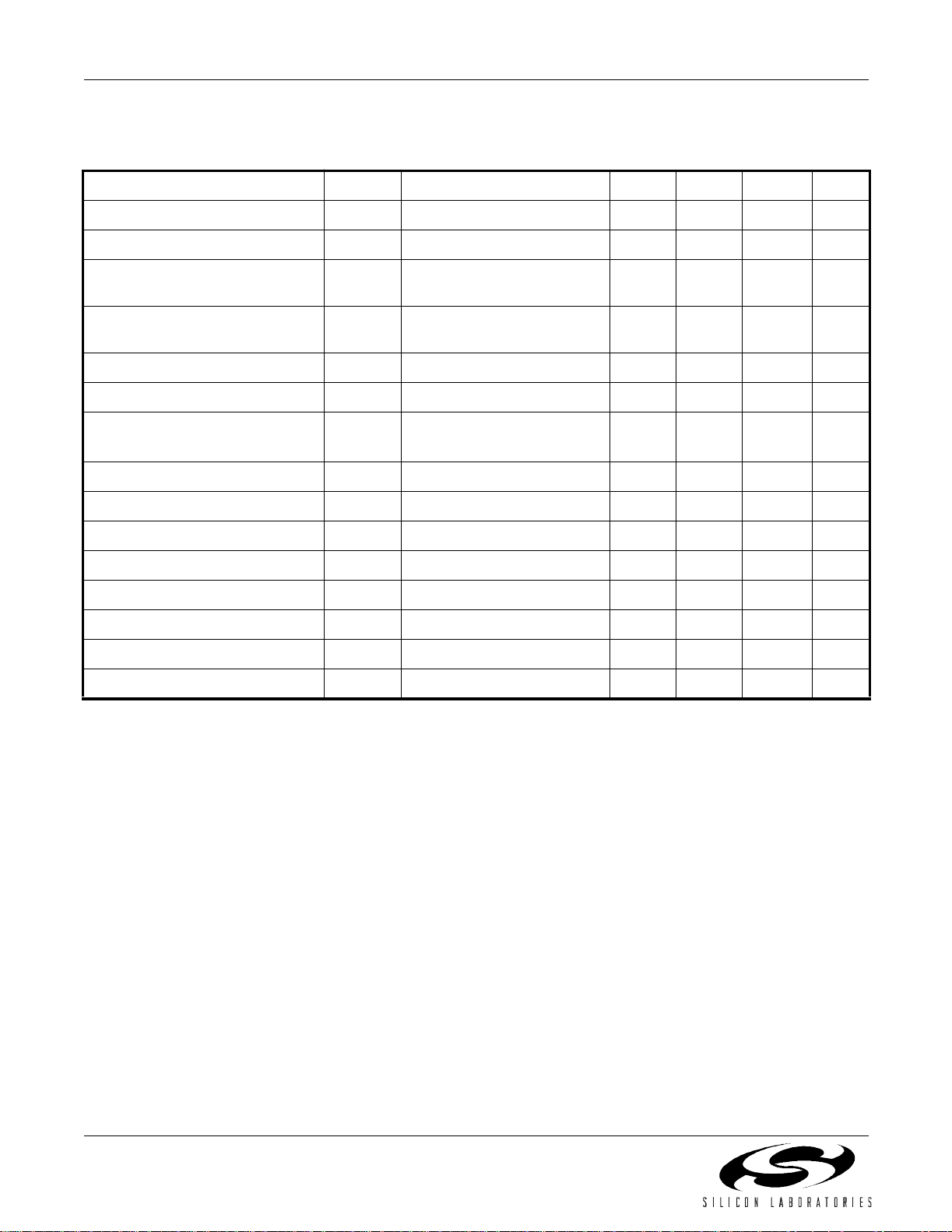

Table 3. AC Characteristics (RXDIN, RXDOUT, RXCLK1, RXCLK2)

(VDD = 1.8 V ±5% , TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Output Clock Frequency

f

clkout

See Figure 2 — 622 667 MHz

(RXCLK1)

Duty Cycle (RXCLK1, RXCLK2) tch/tcp, Figure 2 45 — 5 5 %

Output Rise and Fall Times

t

R,tF

Figure 3 — 50 — ps

(RXCLK1, RXCLK2, RXDOUT)

Data Invalid Prior to RXCLK1 t

Data In valid A fter RXCL K1 t

cq1

cq2

Input Return Loss (RXIN) 100 kHz–2.5 GHz

Figure 2 — — 200 ps

Figure 2 — — 200 ps

2.5 GHz–4.0 GHz

18.7

TBD

—

—

—

—

dB

dB

Slicing Adjust Dynam ic Range SLICELVL = 200–800 mV –20 — 20 mV

Slicing Level Offset

1

SLICELVL = 200–800 mV –500 — 500

µV

(referred to RXDIN)

Slicing Level Accuracy VSLICE –5 — 5 %

Sampling Phase Adjustment

2

PHASEADJ = 200–800 mV –22.5° — 22.5°

LOS Threshold Dynamic Range LOSLVL = 200–800 m V 10 — 50 mV

pk-pk

LOS Threshold Offset

3

LOSLVL = 200–800 mV –500 — 500

µV

(referred to RXDIN)

LOS Threshold Accuracy VLOS –5 — 5 %

Note:

1. Slice level (referred to RXDIN) is calculated as follows: VSLICE = (SLICE_LVL – 0.4

2. Sample Phase Offset is calcul ated as follows: PHASE OFFSET = 22.5

3. LOS Threshold voltage (referred to RXDIN) is calculated as follows: VLOS = 30 mV + (LOS_LVL – 0.4

°(PHASEADJ – 0.4

VREF)/15.

VREF)/0.3

VREF)/15.

Preliminary Rev. 0.41 7

Si5110

Table 4. AC Characteristics (TXCLK4OUT, TXCLK4IN, TXCLKOUT, TXDIN, TXDOUT)

(V

1.8 V ±5%, TA = –40°C to 85°C)

DD =

Parameter Symbol Test Condition Min Typ Max Unit

TXCLKOUT Frequency f

clkout

Figure 2 — 2.5 2.7 GHz

TXCLKOUT Duty Cycle tch/tcp, Figure 2 45 — 55 %

Output Rise Time

t

R

Figure 3 — 25 — ps

(TXCLKOUT, TXDOUT)

Output Fall Time

t

F

Figure 3 — 25 — ps

(TXCLKOUT, TXDOUT)

TXCLKOUT Setup to TXDOUT t

TXCLKOUT Hold From TXDOUT t

su

hd

Output Return Loss 100 kHz–2. 5 GHz

TXCLK4OUT Frequency f

CLKIN

Figure 2 25 — — ps

Figure 2 25 — — ps

2.5 GHz–4.0 GHz

TBD

TBD

—

—

—

—

— 622 667 MHz

dB

dB

TXCLK4OUT Duty Cycle tch/tcp, Figure 2 40 — 60 %

TXCLK4OUT Rise & Fall Times t

TXDIN Setup to TXCLK4IN t

TXDIN Hold from TXCLK4IN t

TXCLK4IN Frequency f

R,tF

DSIN

DHIN

CLKIN

100 — 300 ps

— — 300 ps

— — 300 ps

— 622 667 MHz

TXCLK4IN Duty Cycle tch/tcp, Figure 2 40 — 60 %

TXCLK4IN Rise & Fall Times t

R,tF

100 — 300 ps

8 Preliminary Rev. 0.41

Loading...

Loading...