Si5022/Si5023

L

P

RELIMINARY DATA SHEET

ULTI-RATE

M

SONET/SDH CDR IC

WITH LIMITING AMP

Features

igh Speed Clock and Data Recovery device with Integrated Limiting Amp:

H

! Supports OC-48/12/3, STM-16/4/1,

Gigabit Ethernet, and 2.7 Gbps FEC

! DSPLL™ Technology

Low Power—370 mW (TYP)

!

! Small Footprint: 5 mm x 5 mm

! Bit-Error-Rate Alarm

! External Reference Not Required

!

Jitter Generation 3.0 mUI

RMS

(TYP)

! Loss-of-signal Level Alarm

! Data Slicing Level Control

! 10 mV

Differential Sensitivity

PP

! 2.5 V (Si5022) or 3.3 V (Si5023) Supply

Applications

! SONET/SDH/ATM Routers

! Add/Drop Multiplexers

! Digital Cross Connects

! Gigabit Ethernet Interfaces

! SONET/SDH Test Equipment

! Optical Transceiver Modules

! SONET/SDH Regenerators

! Board Level Serial Links

Description

The Si5022/23 is a fully integrated, high performance limiting amp and clock and

data recovery (CDR) IC for high-speed serial communication systems. It extracts

timing information and data from a serial input at OC-48/12/3, STM-16/4/1, or

Gigabit Ethernet (GbE) rates. Support for 2.7 Gbps data streams is also provided

for OC-48/STM-16 applications that employ forward error correction (FEC). An

external reference clock is not required; applications with or without an external

reference clock are supported. Silicon Laboratories’ DSPLL

™

technology

eliminates sensitive noise entry points thus making the PLL less susceptible to

board-level interaction and helping to ensure optimal jitter performance.

The Si5022/23 represents a new standard in low jitter, low power, small size, and

integration for high speed LA/CDRs. It operates from either a 3.3 V (Si5023) or

2.5 V (Si5022) supply over the industrial temperature range (–40°C to 85°C).

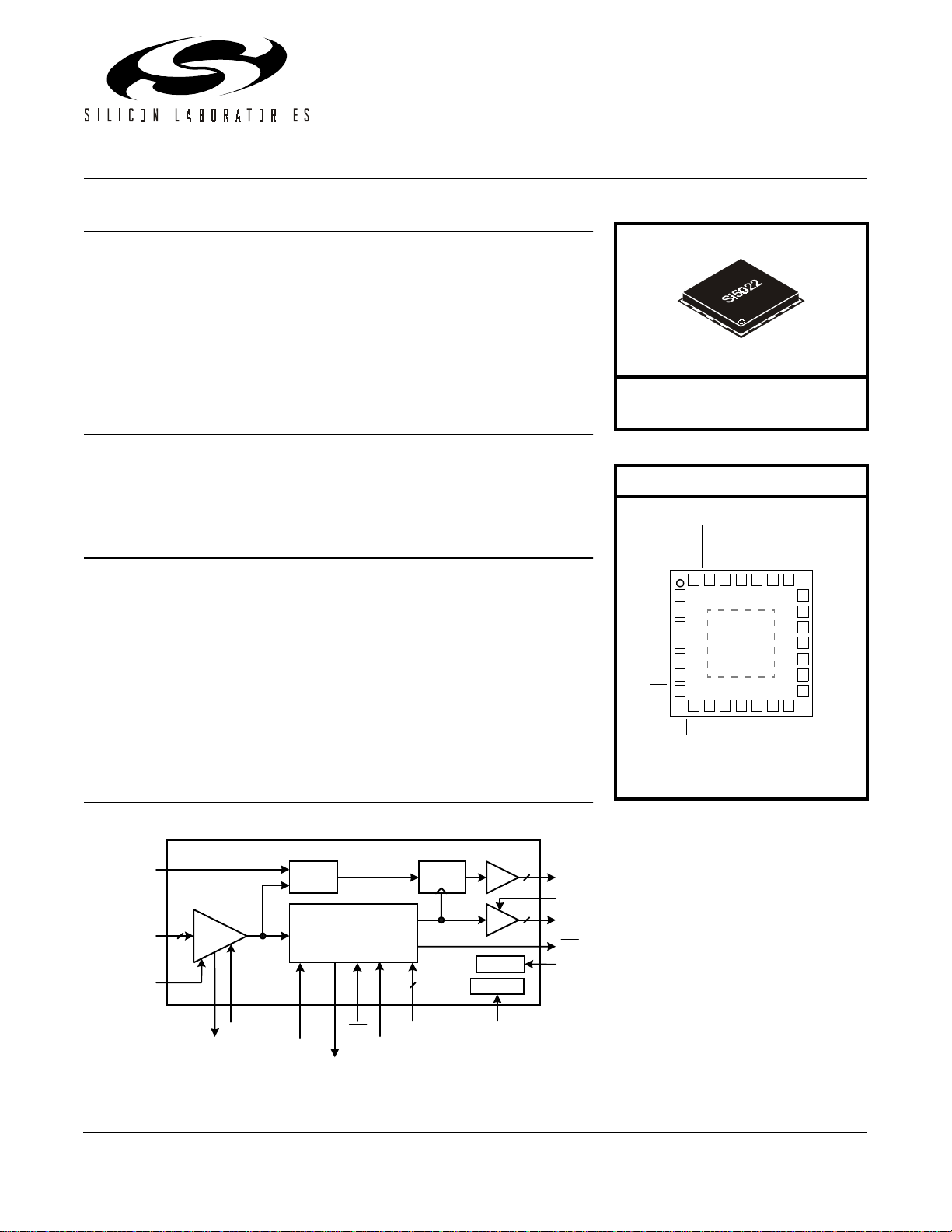

Functional Block Diagram

Ordering Information:

See page 14.

Pin Assignments

Si5022/23

NC

BER_ALM

RATESEL0

RATESEL1

LOS_LVL

SLICE_LVL

REFCLK+

REFCLK–

LOL

1

2

3

4

5

6

7

LTR

LOS

Top View

BER_LVL

GND

Pad

DSQLCH

VDD

VDD

CLKDSBL

DIN+

CLKOUT+

DIN–

22232425262728

141312111098

CLKOUT–

21

20

19

18

17

16

15

VDD

VDD

REXT

RESET/CA

VDD

DOUT+

DOUT–

TDI

DSQLCH

DIN+

DIN–

LOS_LVL

2

Limiting

AMP

LOS

SLICE_LVL

Squelch

Control

BER_LVL

DSPLL

Phase-Locked

Loop

BER_ALM

TM

LTR

REFCLK+

REFCLK–

(Optional)

Retimer

2

RATSEL[1:0]

BUF

BUF

Control

Bias Gen

REXT

2

2

DOUT+

DOUT–

CLKDSBL

CLKOUT+

CLKOUT–

LOL

RESET/CAL

Preliminary Rev. 0.46 5/01 Copyright © 2001 by Silicon Laboratories Si5022/23-DS046

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Silicon Laboratories Confidential. Information contained herein is covered under non-disclosure agreement (NDA).

Si5022/Si5023

2 Preliminary Rev. 0.46

Si5022/Si5023

T

ABLE OF

C

ONTENTS

Section Page

Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Limiting Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

DSPLL™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Multi-Rate Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Operation Without an External Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Operation With an External Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Lock Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Lock-to-Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Loss-of-Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Bit-Error-Rate (BER) Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Data Slicing Level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

PLL Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

RESET/DSPLL Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Clock Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Data Squelch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Device Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Voltage Regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Differential Input Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Pin Descriptions: Si5022/23 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Preliminary Rev. 0.46 3

Si5022/Si5023

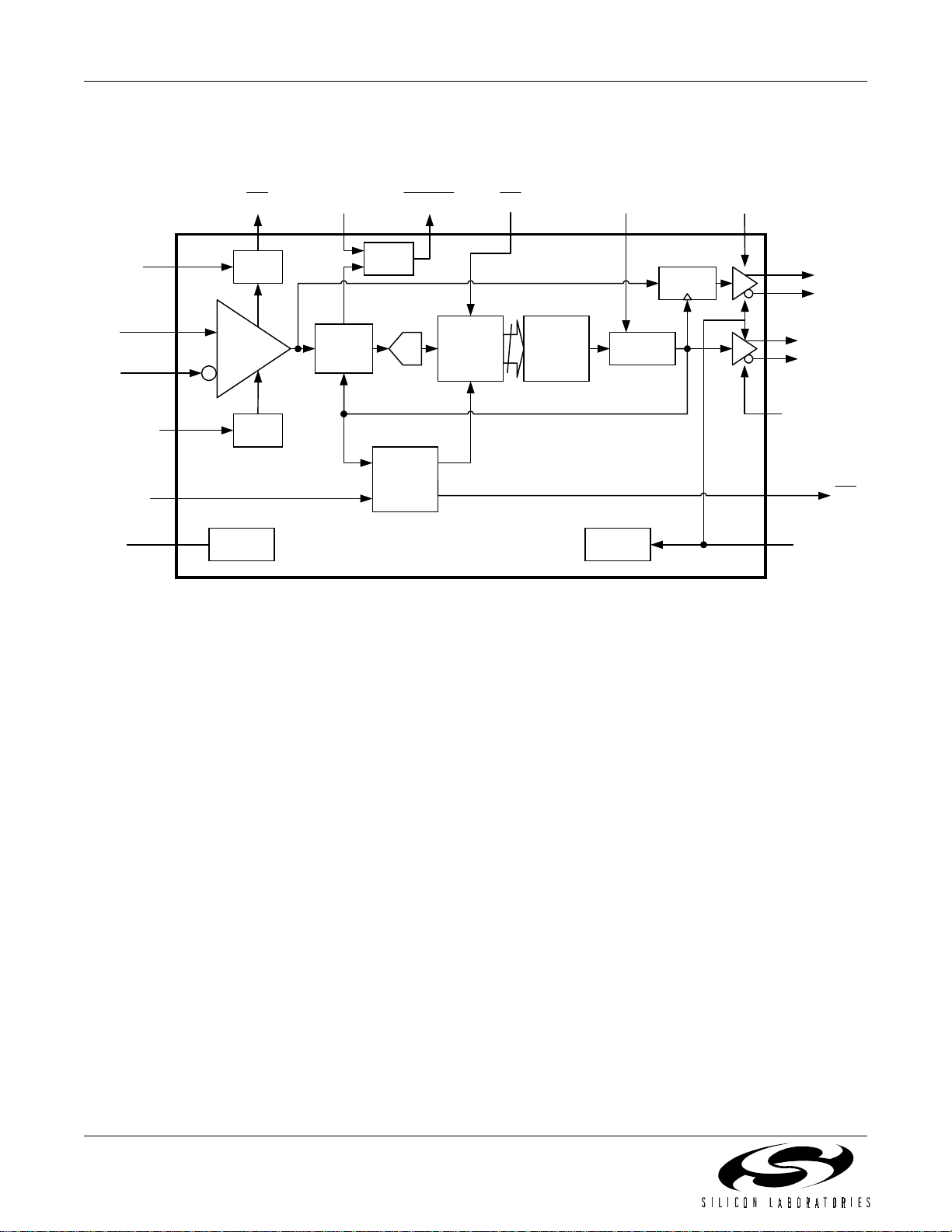

Detailed Block Diagram

LOS_LVL

DIN+

DIN+

SLICE_LVL

REFCLK±

(optional)

REXT

Signal

Detect

Limiting

Amp

Slicing

Control

Bias

Generation

LTR

DSP VCO

n

Phase

Detector

BER_ALMBER_LVLLOS

BER

Monitor

A/D

Lock

Detection

Figure 1. Detailed Block Diagram

RATESEL[0:1]

Retime

CLK

Dividers

Calibration RESET/CAL

DSQLCH

DOUT+

DOUT–

CLKOUT+

CLKOUT–

CLK_DSBL

LOL

4 Preliminary Rev. 0.46

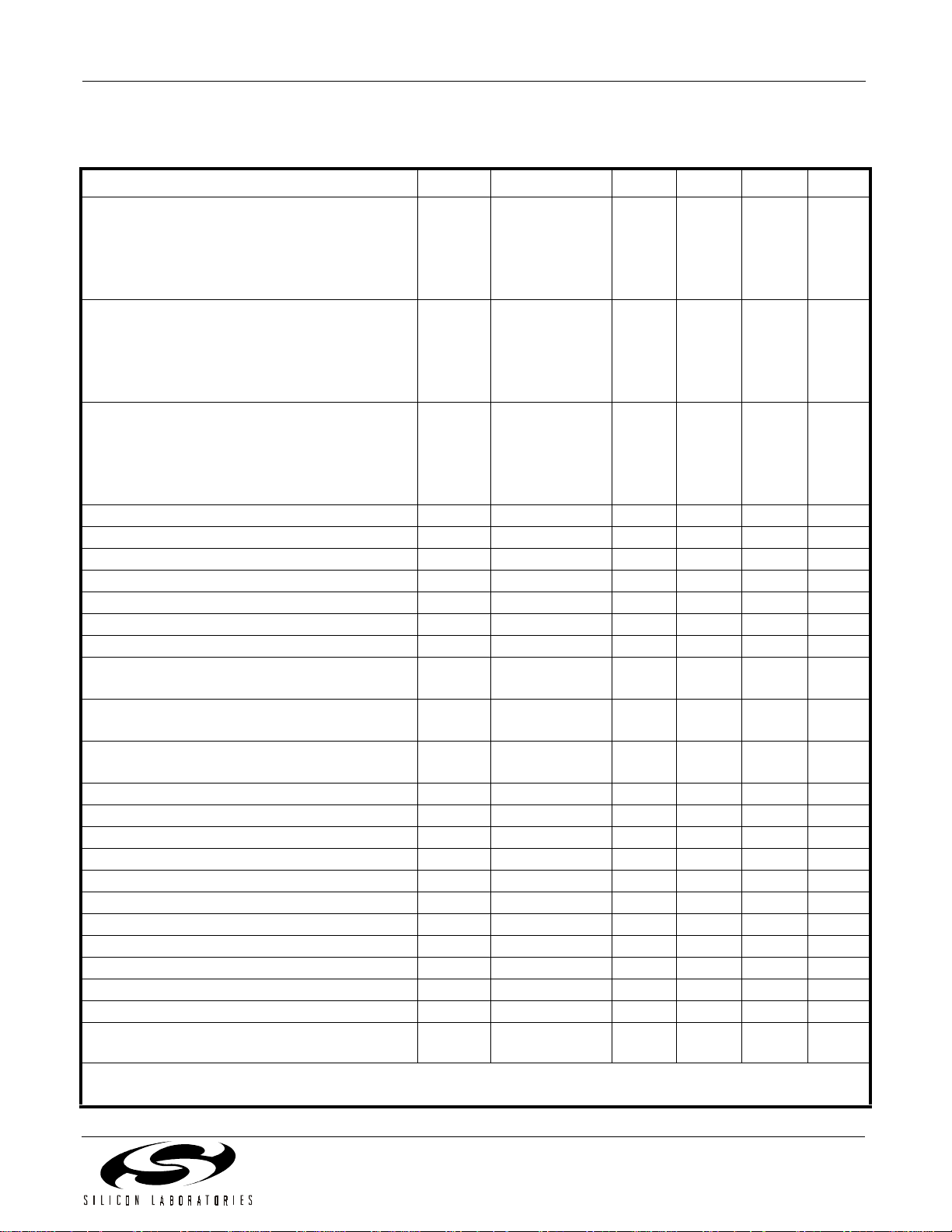

Electrical Specifications

Table 1. Recommended Operating Conditions

Si5022/Si5023

Parameter

Symbol Test Condition

Ambient Temperature T

Si5022 Supply Voltage

Si5023 Supply Voltage

2

2

V

V

A

DD

DD

1

Min

Typ

–40 25 85 °C

2.375 2.5 2.625 V

3.135 3.3 3.465 V

Max

1

Notes:

1. All minimum and maximum specifications are guaranteed and apply across the recommended operating

conditions. Typical values apply at nominal supply voltages and an operating temperature of 25°C unless

otherwise stated.

2. The Si5022/23 specifications are guaranteed when using the recommended application circuit (including

component tolerance) of Figure 5 on page 10.

V

SIGNAL+

SIGNAL–

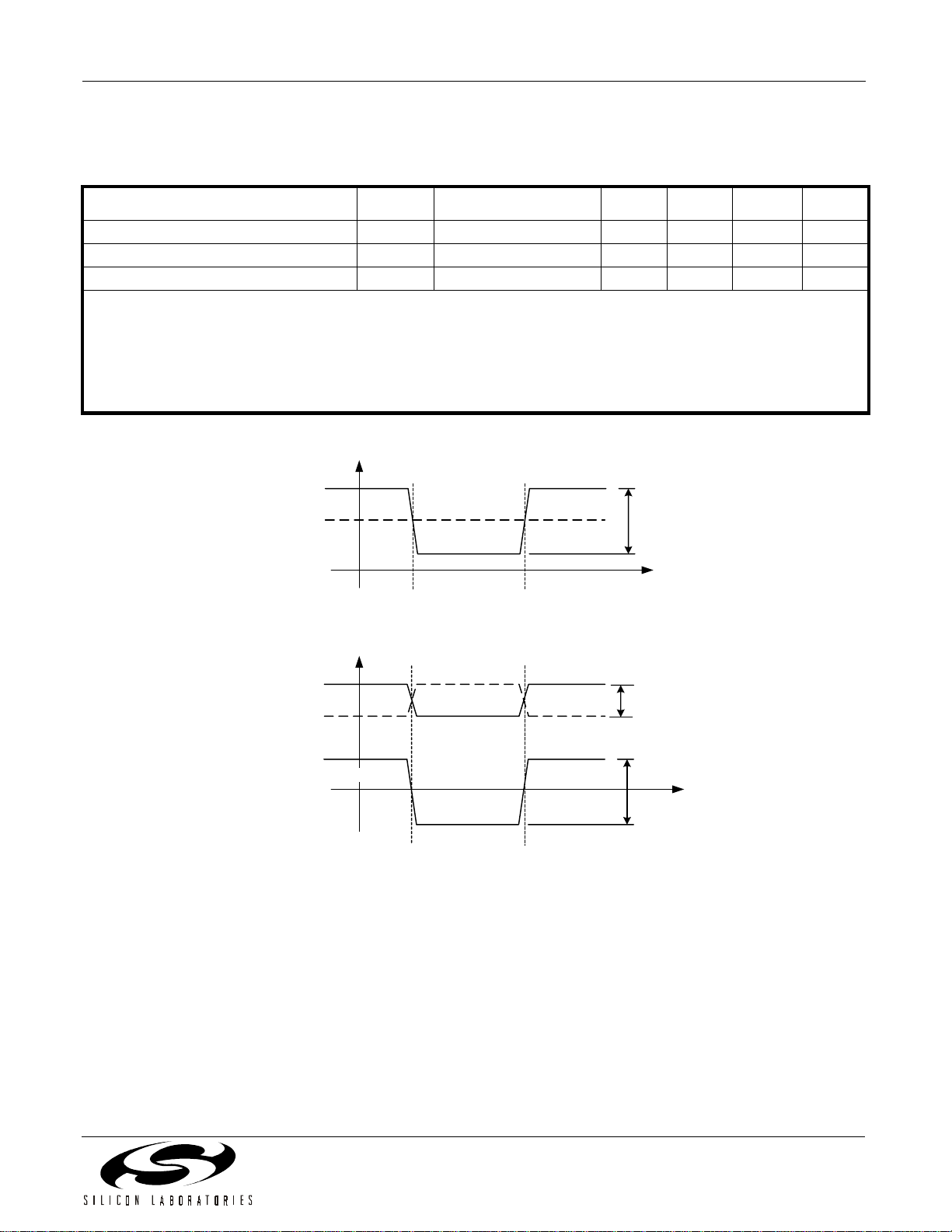

A. Operation with Single-Ended Inputs

V

IS

t

Unit

V

SIGNAL+

0.5 V

SIGNAL–

(SIGN A L +) – (SIG N A L –)

B. Operation with Differential Inputs and Outputs

ID

V

ID

t

Figure 2. Differential Voltage Measurement (DI N , REFCLK, DOUT, CLKOUT)

Preliminary Rev. 0.46 5

Si5022/Si5023

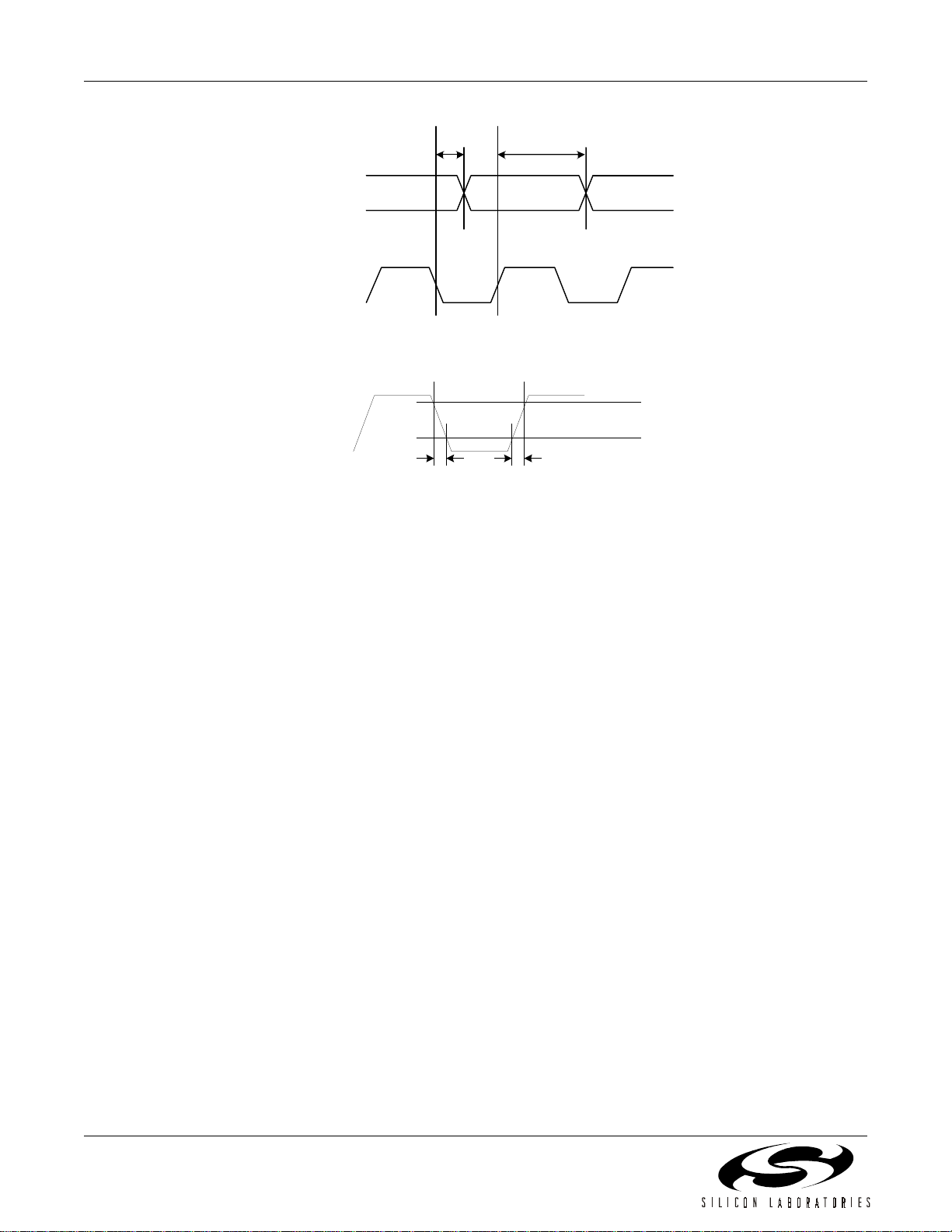

t

Cr-D

DOUT

CLKO UT

t

Cf-D

Figure 3. Clock to Data Timing

DOUT,

CLKOUT

t

F

t

R

Figure 4. DOUT and CLKOUT Rise/Fall Times

80%

20%

6 Preliminary Rev. 0.46

Si5022/Si5023

Table 2. DC Characteristics

(VDD=2.5 V ± 5% for Si5022 or 3.3V ± 5% for Si5023, TA = –40°C to 85°C)

Parameter Symbol Test Condition Min Typ Max Unit

Supply Current

OC-48 and FEC (2.7 G Hz)

GigE

OC-12

OC-3

Power Dissipation

OC-48 and FEC (2.7 G Hz)

GigE

OC-12

OC-3

Power Dissipation

OC-48 and FEC (2.7 G Hz)

GigE

OC-12

OC-3

Common Mode Input Voltage (DIN)* V

Common Mode Input Voltage (REFCLK)* V

DIN Single-ended Input Voltage Swing* V

DIN Differential Input Voltage Swing* V

REFCLK Single-ended Input Voltage Swing* V

REFCLK Differential Input Voltage Swing* V

Input Impedance (DIN, REFCLK) R

Differential Output Voltage Swing

(DOUT)

Differential Output Voltage Swing

(CLKOUT)

Output Common Mode Voltage

(DOUT,CLKOUT)

Output Impedance (DOUT,CLKOUT) R

Output Current Short to GND (DOUT,CLKOUT) I

Output Current Short to V

(DOUT,CLKOUT) I

DD

Input Voltage Low (LVTTL Inputs) V

Input Voltage High (LVTTL Inputs) V

Input Low Current (LVTTL Inputs) I

Input High Current (LVTTL Inputs) I

Output Voltage Low (LVTTL Outputs) V

Output Voltage High (LVTTL Outputs) V

Input Impedance (LVTTL Inputs) R

PWRDN/CAL Leakage Current I

LOS_LVL, BER_LVL, SLICE_LVL Input Imped-

ance

*Note: These inputs may be driven differentially or single-endedly. When driven single-endedly, the unused input must be ac

coupled to ground.

I

DD

P

D

VDD =

2.5 V (

P

D

VDD =

3.3 V (

See Figure 11 1.42 1.50 1.58 V

See Figure10 1.90 2.00 2.10 V

See Figure 2A 10 — 500 mV

See Figure 2B 10 — 1000 mV

See Figure 2A 200 — 750 mV

See Figure 2B 200 — 1500 mV

Line-to-Line 84 100 116 Ω

100 Ω Load

V

ICM

ICM

IS

ID

IS

ID

IN

OD

Line-to-Line

V

OD

100 Ω Load

Line-to-Line

V

OCM

100 Ω Load

Line-to-Line

OUT

SC(–)

SC(+)

IL

IH

IL

IH

OL

OH

IN

PWRDNVPWRDN

R

IN

Single-ended 84 100 116 Ω

IO = 2 mA — — 0.4 V

IO = 2 mA 2.0 — — V

± 5%)

± 5%)

—

—

—

—

—

—

—

—

—

—

—

—

148

150

152

154

370

375

380

385

488

495

502

508

160

162

164

165

400

405

410

414

554

561

568

572

mA

mW

mW

TBD 940 TBD mV

(pk-pk)

TBD 900 TBD mV

(pk-pk)

TBD 1.825 TBD V

—25TBDmA

TBD –15 — mA

——.8V

2.0 — — V

——10µA

——10µA

10 — — kΩ

≥ 0.8 V TBD 25 TBD µA

TBD 100 TBD kΩ

Preliminary Rev. 0.46 7

Loading...

Loading...