Silicon Laboratories Si5010-BM Datasheet

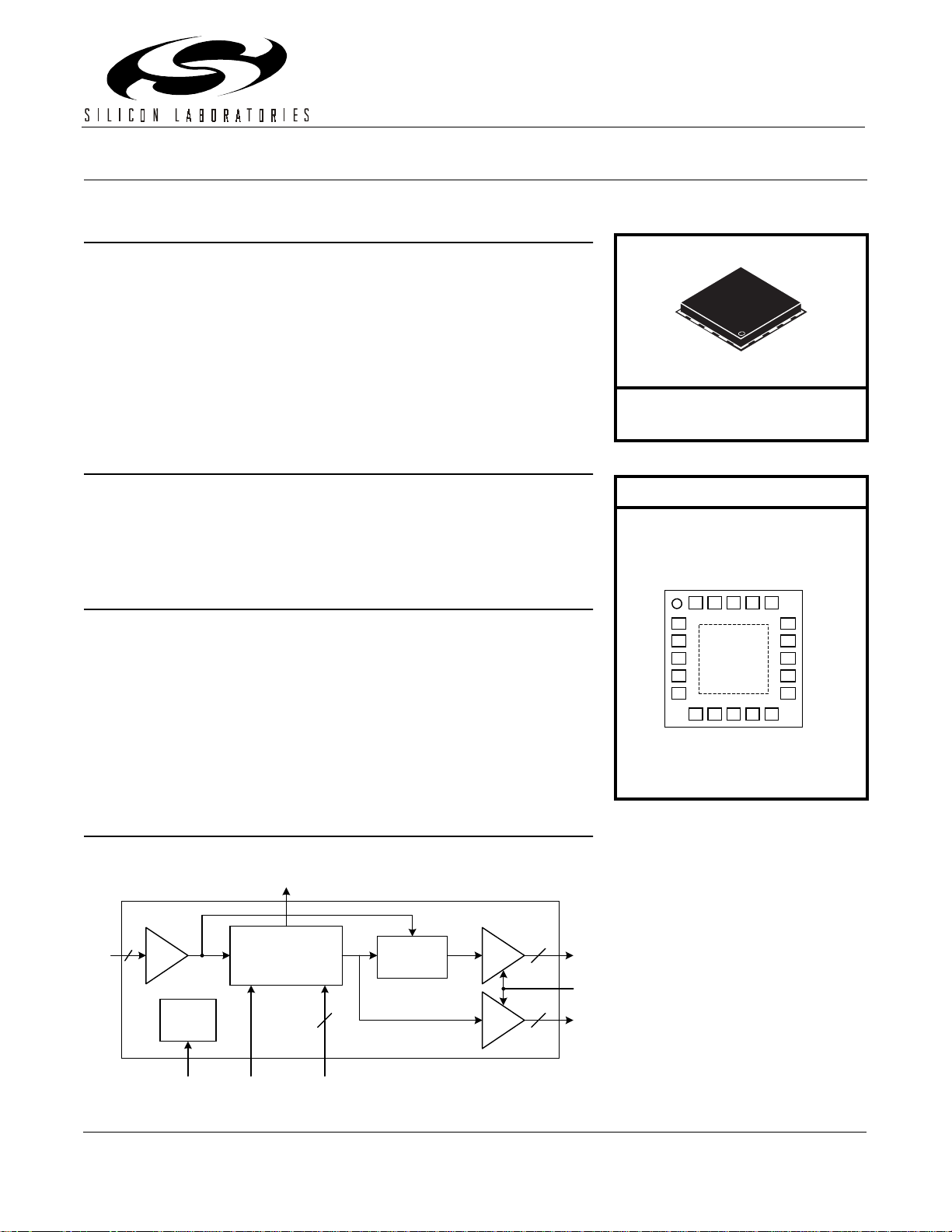

Si5010

OC-12/3, STM-4/1 SONET/SDH C

LOCK AND DATA RECOVERY

Features

Complete CDR solution includes the following:

!

Supports OC-12/3, STM-4/1

!

Low Power, 293 mW (TYP OC-12)

!

Small Footprint: 4 mm x 4 mm

!

DSPLL™ Eliminates External Loop

Filter Components

!

3.3 V Tolerant Control Inputs

!

Exceeds All SONET/SDH

Jitter Specifications

!

Jitter Generation

1.6 mUI

!

Device Power Down

!

Loss-of-Lock Indicator

!

Single 2.5 V Supply

RMS

(TYP)

Applications

!

SONET/SDH/ATM Routers

!

Add/Drop Multiplexers

!

Digital Cross Connects

!

Board Level Serial Links

!

SONET/SDH Test Equipment

!

Optical Transceiver Modules

!

SONET/SDH Regenerators

Description

The Si5010 is a fully integrated low-p ower clock and d ata recovery (CDR)

IC designed for high-speed serial communication systems. It extracts

timing information and data from a serial input at OC-12/3 or STM-4/1 data

rates. DSPLL™ technology eliminates sensitive noise entry points thus

making the PLL less susc eptible to board-level interaction and helpi ng to

ensure optimal jitter performance in the application.

The Si5010 represe nts an industry-leading combinati on of low jitter, low

power, and small size for high speed CDRs. It operates from a single 2.5 V

supply over the industrial temperature range (–40°C to 85°C).

REXT

REFCLK+

REFCLK–

Si5010

Ordering Information:

See page 14.

Pin Assignments

Si5010

NC

RATESEL

CLKOUT+

GND

20 19 18 17 16

1

VDD

2

GND

GND

3

Pad

4

5

6 7 8 9 10

LOL

VDD

T op V i e w

GND

DIN+

CLKOUT–

15

14

13

12

11

DIN–

IC

PWRDN/CAL

VDD

DOUT+

DOUT–

VDD

Functional Block Diagram

LOL

TM

DIN+

DIN–

2

BUF

Bias

REXT

Preliminary Rev. 0.31 4/01 Copyright © 2001 by Silicon Laboratories Si5010-DS031

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

DSPLL

Phase-Locked

Loop

RATESEL

2

REFCLK+

REFCLK–

Retimer

BUF

BUF

2

2

DOUT+

DOUT–

PWRDN/CAL

CLKOUT+

CLKOUT–

Si5010

2 Preliminary Rev. 0.31

Si5010

T

ABLE OF

C

ONTENTS

Section Page

Detailed Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

DSPLL™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

PLL Self-Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Multi-Rate Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Reference Clock Detect . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Lock Detect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Device Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Bias Generation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Differential Input Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Differential Output Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Pin Descriptions: Si5010 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Ordering Guide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Contact Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Preliminary Rev. 0.31 3

Si5010

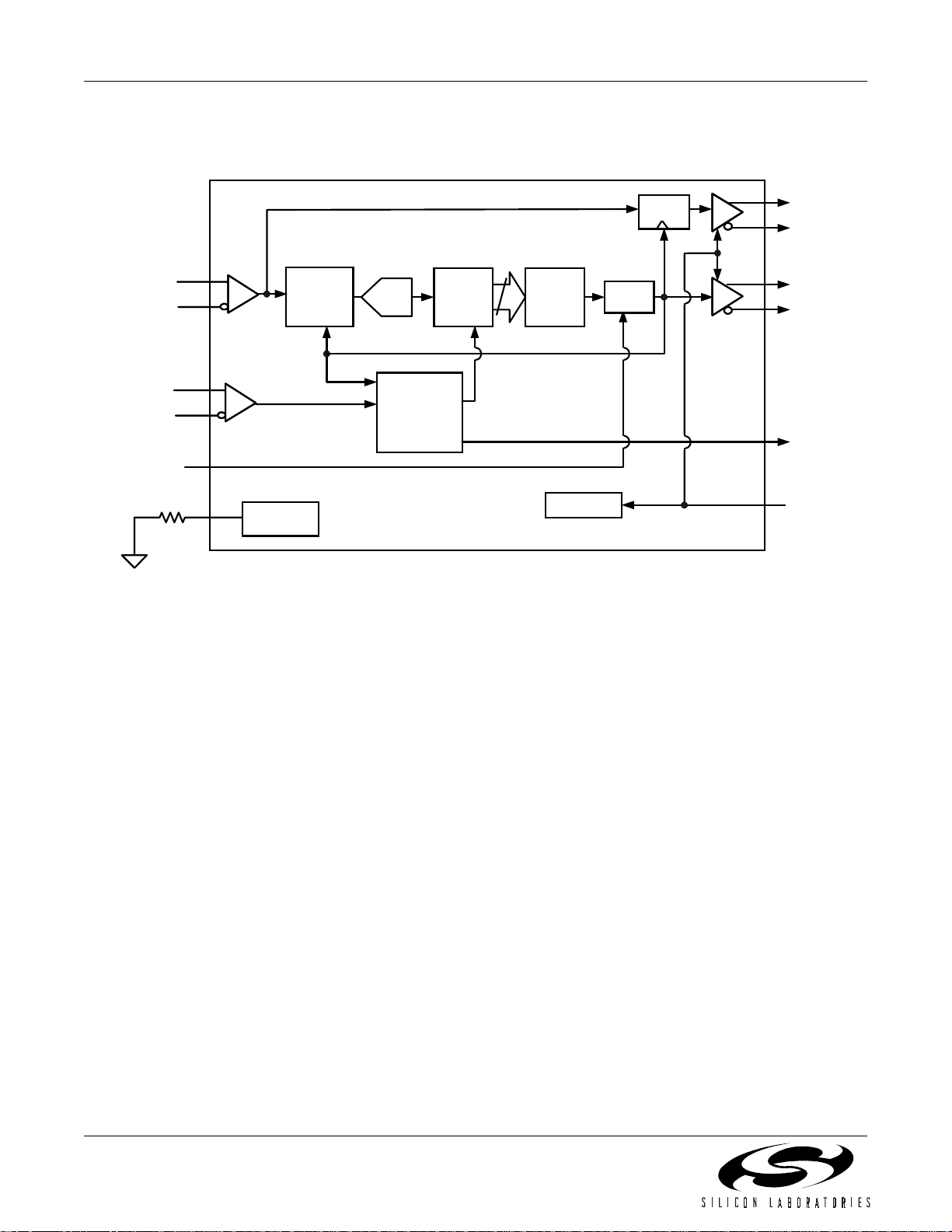

Detailed Block Diagram

DIN+

DIN+

DIN–

REFCLK+

REFCLK+

REFCLK–

RATESEL

REXT

Detector

Detector

Detector

Bias

Bias

Bias

Generation

Generation

Generation

Phase

Phase

Phase

A/D

DSP

n

Lock

Detector

Figure 1. Detailed Block Diagram

VCO

Ca libra t io n

CLK

Divider

Retime

RetimeRetime

c

DOUT+

DOUT–

c

CLKOUT+

CLKOUT–

LOL

PWRDN/CAL

4 Preliminary Rev. 0.31

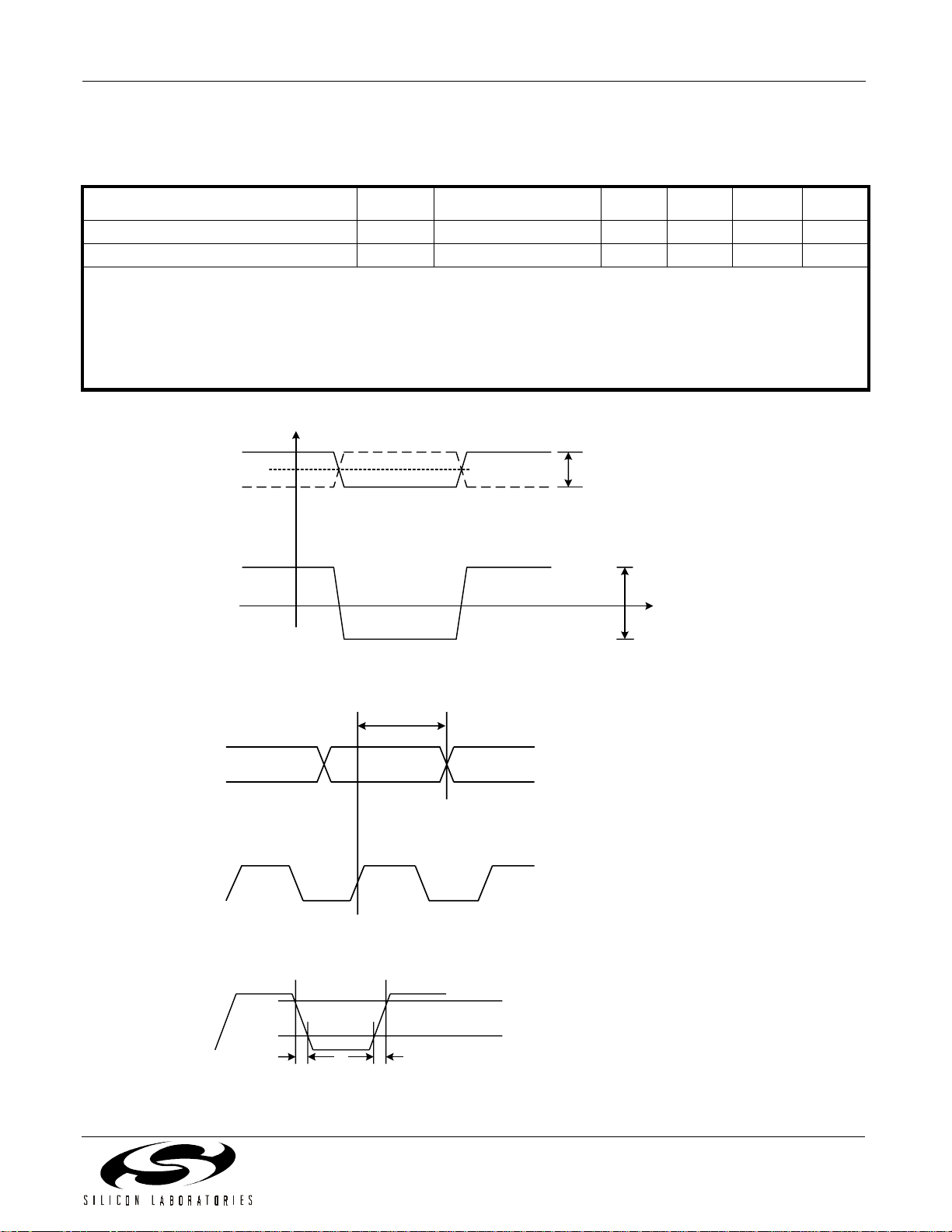

Electrical Specifications

t

Table 1. Recommended Operating Conditions

Si5010

Parameter

Symbol Test Condition

Ambient Temperature T

Si5010 Supply Voltage

2

V

A

DD

1

Min

Typ

–40 25 85 °C

2.375 2.5 2.625 V

Max

1

Notes:

1. All minimum and maximum specifications are guaranteed and apply across the recommended operating

conditions. Typical values apply at nominal supply voltages and an operating temperature of 25°C unless

otherwise stated.

2. The Si5010 specifications are guaranteed when using the recommended application circuit (including

component tolerance) of Figure 5 on page 8.

V

SIGNAL +

Differential

I/Os

(SIGNAL +) – (SIGNAL –)

Differential

Voltage Swing

SIGNAL –

, V

V

ICM

OCM

VID,V

OD

V

IS

Differential Peak-to-Peak Voltage

t

Unit

DOUT

CLKOUT

DOUT,

CLKOUT

Figure 2. Differential Voltage Measurement

C-D

Figure 3. Clock to Data Timing

80%

t

F

t

R

20%

Figure 4. DOUT and CLKOUT Rise/Fall Times

Preliminary Rev. 0.31 5

Loading...

Loading...