Page 1

EFR32xG21 Wireless Gecko

Reference Manual

The EFR32xG21 Wireless Gecko SoC is the first device in the Series 2 Wireless Gecko

Portfolio, and includes the EFR32MG21 Mighty Gecko and EFR32BG21 Blue Gecko.

The EFR32xG21 improves processing capability with a Cortex M33 core and has best in

class link budget while providing for lower active current for both the MCU and radio. The

dedicated security core (Secure Element) provides improved cryptography and hardware

security that is isolated from the main application CPU. This high performance and secure multi-protocol device supports Zigbee, Thread, and Bluetooth 5.0.

The single-die solution provides industry-leading energy efficiency, processing capability,

and RF performance in a small form factor for IoT connected applications.

Core / Memory

ARM Cortex

TM

M33 processor

with DSP extensions,

FPU and Trust Zone

ETM Debug Interface RAM Memory

Flash Program

Memory

Radio Transceiver

RF Frontend

LNA

PA

PA

I

Q

PGA

Frequency

Synth

DEMOD

IFADC

AGC

MOD

LDMA

Controller

FRC

CRC

HF Crystal

EM23 HF RC

Oscillator

LF Crystal

Peripheral Reflex System

Serial

Interfaces

BUFC

RAC

Clock Management

Oscillator

Oscillator

32-bit bus

USART

2

I

C

HF

RC Oscillator

Ultra LF RC

Oscillator

Fast Startup

RC Oscillator

RC Oscillator

I/O Ports Analog I/F

External

Interrupts

General

Purpose I/O

Pin Reset

Pin Wakeup

KEY FEATURES

• 32-bit ARM® Cortex M33 core with 80

MHz maximum operating frequency

• Scalable Memory and Radio configuration

options available in QFN packaging

• Peripheral Reflex System enabling

autonomous interaction of MCU

peripherals

• Autonomous Hardware Crypto Accelerator

and True Random Number Generator

• Multiple Integrated 2.4 GHz PAs with up to

20 dBm transmit power

Management

LF

Power-On Reset

Timers and Triggers

Timer/Counter

Low Energy Timer

Energy

Voltage

Regulator

Brown-Out

Detector

Protocol Timer

Watchdog Timer

Real Time

Capture Counter

Back-Up Real

Time Counter

Security

Crypto Acceleration

True Random

Number Generator

Secure Debug

Authentication

Secure Element

Comparator

iADC

Analog

Lowest power mode with peripheral operational:

EM3—StopEM2—Deep SleepEM1—SleepEM0—Active

EM4—Shutoff

silabs.com | Building a more connected world. Rev. 0.4

Page 2

Table of Contents

1. About This Document ...........................22

1.1 Introduction ...............................22

1.2 Conventions ...............................23

1.3 Related Documentation ...........................24

2. System Overview .............................25

2.1 Introduction ...............................26

2.2 Block Diagrams..............................26

2.3 MCU Features overview ...........................27

2.4 Oscillators and Clocks ...........................29

2.5 RF Frequency Synthesizer ..........................29

2.6 Modulation Modes .............................29

2.7 Transmit Mode ..............................30

2.8 Receive Mode ..............................30

2.9 Data Buffering ..............................30

2.10 Unbuffered Data Transfer ..........................30

2.11 Frame Format Support ...........................30

2.12 Hardware CRC Support ..........................31

2.13 Convolutional Encoding / Decoding ......................31

2.14 Binary Block Encoding / Decoding .......................31

2.15 Data Encryption and Authentication ......................32

2.16 Timers ................................33

2.17 RF Test Modes .............................33

3. System Processor ............................34

3.1 Introduction ...............................34

3.2 Features ................................35

3.3 Functional Description ...........................35

3.3.1 Interrupt Operation ...........................36

3.3.2 TrustZone ..............................36

3.3.3 Interrupt Request lines (IRQ) ........................37

4. Memory and Bus System ..........................39

4.1 Introduction ...............................39

4.2 Functional Description ...........................40

4.2.1 Bus Matrix ..............................41

4.2.2 Flash ................................42

4.2.3 SRAM ...............................42

4.2.4 Peripherals ..............................42

5. Radio Transceiver ............................48

silabs.com

| Building a more connected world. Rev. 0.4 | 2

Page 3

5.1 Introduction ...............................49

6. MSC - Memory System Controller ......................50

6.1 Introduction ...............................50

6.2 Features ................................51

6.3 Functional Description ...........................51

6.3.1 Ram Configuration ...........................51

6.3.2 Instruction Cache............................52

6.3.3 Device Information (DI) Page .......................52

6.3.4 User Data (UD) Page Description ......................52

6.3.5 Bootloader ..............................52

6.3.6 Post-reset Behavior ...........................52

6.3.7 Flash Startup .............................52

6.3.8 Wait-states ..............................53

6.3.9 Cortex-M33 If-Then Block Folding ......................53

6.3.10 Line Buffering (Prefetch) .........................53

6.3.11 Erase and Write Operations........................54

6.4 DEVINFO - Device Info Page .........................55

6.4.1 Register Map .............................56

6.4.2 Register Description...........................57

6.5 ICACHE - Instruction Cache .........................84

6.5.1 Cache Operation ............................84

6.5.2 Performance Measurement ........................85

6.5.3 Register Map .............................86

6.5.4 Register Description...........................87

6.6 SYSCFG - System Configuration ........................93

6.6.1 Ram Retention ............................93

6.6.2 ECC ................................94

6.6.3 RAM Wait-states ............................94

6.6.4 RAM Prefetch .............................94

6.6.5 RAM Cache .............................94

6.6.6 Software Interrupts ...........................94

6.6.7 Bus faults ..............................94

6.6.8 Register Map .............................95

6.6.9 Register Description...........................98

6.7 Register Map .............................110

6.8 Register Description ...........................112

6.8.1 MSC_IPVERSION - IP version ID .....................112

6.8.2 MSC_READCTRL - Read Control Register ..................113

6.8.3 MSC_WRITECTRL - Write Control Register..................114

6.8.4 MSC_WRITECMD - Write Command Register .................115

6.8.5 MSC_ADDRB - Page Erase/Write Address Buffer ................116

6.8.6 MSC_WDATA - Write Data Register ....................116

6.8.7 MSC_STATUS - Status Register .....................117

6.8.8 MSC_IF - Interrupt Flag Register .....................118

6.8.9 MSC_IEN - Interrupt Enable Register ....................119

silabs.com

| Building a more connected world. Rev. 0.4 | 3

Page 4

6.8.10 MSC_USERDATASIZE - user data regsion size ................119

6.8.11 MSC_CMD - Command Register .....................120

6.8.12 MSC_LOCK - Configuration Lock Register ..................120

6.8.13 MSC_MISCLOCKWORD - Mass erase and User data page lock word ........121

6.8.14 MSC_PAGELOCK0 - Main space page 0-31 lock word .............121

6.8.15 MSC_PAGELOCK1 - Main space page 32-63 lock word .............122

6.8.16 MSC_PAGELOCK2 - Main space page 64-95 lock word .............122

6.8.17 MSC_PAGELOCK3 - Main space page 96-127 lock word.............123

6.8.18 MSC_TESTCTRL - Flash test control register.................123

7. DBG - Debug Interface ...........................124

7.1 Introduction ..............................124

7.2 Features ...............................124

7.3 Functional Description ..........................125

7.3.1 Debug Pins.............................125

7.3.2 Embedded Trace Macrocell V3.5 (ETM) ...................125

7.3.3 Debug and EM2/EM3 .........................125

7.4 Register Map .............................126

7.5 Register Description ...........................126

7.5.1 DBG_DCIWDATA - Write Data ......................126

7.5.2 DBG_DCIRDATA - Read Data ......................126

7.5.3 DBG_DCISTATUS - Status .......................127

7.5.4 DBG_DCIID - Identification .......................127

7.5.5 DBG_SYSCOM0 - Communication Status ..................128

7.5.6 DBG_SYSCOM1 - Communication Status ..................129

7.5.7 DBG_SYSPWR0 - Power Status .....................130

7.5.8 DBG_SYSCLK0 - Clocking Status .....................132

7.5.9 DBG_SYSID - Identification .......................134

8. CMU - Clock Management Unit ........................135

8.1 Introduction ..............................135

8.2 Features ...............................135

8.3 Functional Description ..........................136

8.3.1 System Clocks ...........................138

8.3.2 Switching Clock Source ........................140

8.3.3 RC Oscillator Calibration ........................142

8.3.4 Energy Modes............................145

8.3.5 Clock Output on a Pin .........................145

8.3.6 Clock Input from a Pin .........................146

8.3.7 Clock Output on PRS .........................146

8.3.8 Interrupts .............................146

8.3.9 Protection .............................146

8.4 Register Map .............................147

8.5 Register Description ...........................149

8.5.1 CMU_IPVERSION - IP version ID .....................149

8.5.2 CMU_STATUS - Status Register .....................150

silabs.com

| Building a more connected world. Rev. 0.4 | 4

Page 5

8.5.3 CMU_LOCK - Configuration Lock Register ..................151

8.5.4 CMU_WDOGLOCK - WDOG Configuration Lock Register .............151

8.5.5 CMU_IF - Interrupt Flag Register .....................152

8.5.6 CMU_IEN - Interrupt Enable Register ....................152

8.5.7 CMU_CALCMD - Calibration Command Register ................153

8.5.8 CMU_CALCTRL - Calibration Control Register .................154

8.5.9 CMU_CALCNT - Calibration Result Counter Register ..............155

8.5.10 CMU_SYSCLKCTRL - System Clock Control .................156

8.5.11 CMU_TRACECLKCTRL - Debug Trace Clock Control ..............157

8.5.12 CMU_EXPORTCLKCTRL - Export Clock Control ...............158

8.5.13 CMU_DPLLREFCLKCTRL - Digital PLL Reference Clock Control ..........160

8.5.14 CMU_EM01GRPACLKCTRL - EM01 Peripheral Group A Clock Control ........161

8.5.15 CMU_EM23GRPACLKCTRL - EM23 Peripheral Group A Clock Control ........161

8.5.16 CMU_EM4GRPACLKCTRL - EM4 Peripheral Group A Clock Control .........162

8.5.17 CMU_IADCCLKCTRL - IADC Clock Control .................162

8.5.18 CMU_WDOG0CLKCTRL - Watchdog0 Clock Control ..............163

8.5.19 CMU_WDOG1CLKCTRL - Watchdog1 Clock Control ..............164

8.5.20 CMU_RTCCCLKCTRL - RTCC Clock Control.................164

8.5.21 CMU_RADIOCLKCTRL - Radio Clock Control ................165

9. Oscillators ...............................166

9.1 Introduction ..............................166

9.2 HFXO - High Frequency Crystal Oscillator ....................166

9.2.1 Introduction ............................166

9.2.2 Features .............................166

9.2.3 Functional Description .........................167

9.2.4 Register Map ............................170

9.2.5 Register Description ..........................171

9.3 HFRCO - High-Frequency RC Oscillator ....................181

9.3.1 Introduction ............................181

9.3.2 Features .............................181

9.3.3 Functional Description .........................181

9.3.4 Register Map ............................184

9.3.5 Register Description ..........................185

9.4 DPLL - Digital Phased Locked Loop ......................189

9.4.1 Introduction ............................189

9.4.2 Features .............................189

9.4.3 Functional Description .........................189

9.4.4 Register Map ............................191

9.4.5 Register Description ..........................192

9.5 LFXO - Low-Frequency Crystal Oscillator ....................197

9.5.1 Introduction ............................197

9.5.2 Features .............................197

9.5.3 Functional Description .........................197

9.5.4 Register Map ............................199

9.5.5 Register Description ..........................200

9.6 LFRCO - Low-Frequency RC Oscillator ....................207

silabs.com

| Building a more connected world. Rev. 0.4 | 5

Page 6

9.6.1 Introduction ............................207

9.6.2 Features .............................207

9.6.3 Functional Description .........................207

9.6.4 Register Map ............................209

9.6.5 Register Description ..........................210

9.7 FSRCO - Fast Start RCO .........................213

9.7.1 Introduction ............................213

9.7.2 Features .............................213

9.7.3 Functional Description .........................213

9.7.4 Register Map ............................213

9.7.5 Register Description ..........................214

9.8 ULFRCO - Ultra Low Frequency RC Oscillator ..................214

9.8.1 Introduction ............................214

9.8.2 Features .............................214

9.8.3 Functional Description .........................214

10. SMU - Security Management Unit ......................215

10.1 Introduction .............................215

10.2 Features ..............................215

10.3 Functional Description ..........................216

10.3.1 Bus Level Security ..........................216

10.3.2 Privileged Access Control .......................217

10.3.3 Secure Access Control ........................217

10.3.4 ARM Trust Zone ..........................218

10.3.5 Configuring Masters .........................218

10.3.6 Configuring Peripherals ........................218

10.3.7 Configuring Memory .........................219

10.3.8 Cortex-M33 Integration ........................219

10.3.9 Exception Handling .........................220

10.3.10 SMU Lock ............................220

10.4 Register Map .............................221

10.5 Register Description ...........................223

10.5.1 SMU_IPVERSION - IP Version .....................223

10.5.2 SMU_STATUS - Status Register .....................224

10.5.3 SMU_LOCK - Lock Register ......................224

10.5.4 SMU_IF - Interrupt Flag Register .....................225

10.5.5 SMU_IEN - Interrupt Enable Register ...................226

10.5.6 SMU_M33CTRL - M33 Control Settings ..................227

10.5.7 SMU_PPUPATD0 - Privileged Access ...................228

10.5.8 SMU_PPUPATD1 - Privileged Access ...................230

10.5.9 SMU_PPUSATD0 - Secure Access ....................232

10.5.10 SMU_PPUSATD1 - Secure Access ....................234

10.5.11 SMU_PPUFS - Fault Status ......................235

10.5.12 SMU_BMPUPATD0 - Privileged Attribute ..................236

10.5.13 SMU_BMPUSATD0 - Secure Attribute...................237

10.5.14 SMU_BMPUFS - Fault Status .....................238

10.5.15 SMU_BMPUFSADDR - Fault Status Address ................238

silabs.com

| Building a more connected world. Rev. 0.4 | 6

Page 7

10.5.16 SMU_ESAURTYPES0 - Region Types 0 ..................239

10.5.17 SMU_ESAURTYPES1 - Region Types 1 ..................239

10.5.18 SMU_ESAUMRB01 - Movable Region Boundary ...............240

10.5.19 SMU_ESAUMRB12 - Movable Region Boundary ...............240

10.5.20 SMU_ESAUMRB45 - Movable Region Boundary ...............241

10.5.21 SMU_ESAUMRB56 - Movable Region Boundary ...............241

11. SE - Secure Element Subsystem ......................242

11.1 Introduction .............................242

11.2 Features ..............................242

11.2.1 Basic Security Features ........................242

11.3 Security Features ...........................242

11.3.1 Secure Debug ...........................243

11.3.2 Cryptographic Acceleration .......................243

11.3.3 True Random Number Generation ....................243

11.4 SE Mailbox .............................243

11.4.1 Sending Commands .........................243

11.4.2 Receiving Responses ........................243

11.4.3 Register Map ...........................244

11.4.4 Register Description .........................244

12. EMU - Energy Management Unit ......................251

12.1 Introduction..............................251

12.2 Features ..............................252

12.3 Functional Description ..........................253

12.3.1 Energy Modes ...........................254

12.3.2 Entering Low Energy Modes ......................258

12.3.3 Exiting a Low Energy Mode ......................259

12.3.4 Brown Out Detector (BOD) .......................260

12.3.5 Reset Management Unit ........................261

12.3.6 Temperature Sensor .........................262

12.3.7 Register Resets ...........................263

12.3.8 Register Locks ...........................263

12.4 Register Map .............................264

12.5 Register Description ...........................266

12.5.1 EMU_DECBOD - DECOUPLE LVBOD Control register .............266

12.5.2 EMU_BOD3SENSE - BOD3SENSE Control register ..............267

12.5.3 EMU_LOCK - EMU Configuration lock register ................267

12.5.4 EMU_IF - Interrupt Flags ........................268

12.5.5 EMU_IEN - Interrupt Enables ......................269

12.5.6 EMU_EM4CTRL - EM4 Control .....................270

12.5.7 EMU_CMD - EMU Command register ...................271

12.5.8 EMU_CTRL - EMU Control register ....................272

12.5.9 EMU_TEMPLIMITS - EMU Temperature thresholds ..............273

12.5.10 EMU_STATUS - EMU Status register ...................274

12.5.11 EMU_TEMP - Temperature ......................275

12.5.12 EMU_RSTCTRL - Reset Management Control register .............276

silabs.com

| Building a more connected world. Rev. 0.4 | 7

Page 8

12.5.13 EMU_RSTCAUSE - Reset cause ....................278

12.5.14 EMU_DGIF - Interrupt Flags Debug ...................279

12.5.15 EMU_DGIEN - Interrupt Enables Debug ..................280

12.5.16 EMU_SEIF - Interrupt Flags Secure Element ................281

12.5.17 EMU_SEIEN - Interrupt Enables Secure Elements ..............281

13. PRS - Peripheral Reflex System .......................282

13.1 Introduction..............................282

13.2 Features ..............................282

13.3 Functional Description ..........................283

13.3.1 Asynchronous Channel Functions.....................283

13.3.2 Configurable Logic ..........................284

13.3.3 Producers .............................285

13.3.4 Consumers ............................290

13.4 Register Map .............................291

13.5 Register Description ...........................304

13.5.1 PRS_IPVERSION - IP version ID .....................304

13.5.2 PRS_ASYNC_SWPULSE - Software Pulse Register ..............305

13.5.3 PRS_ASYNC_SWLEVEL - Software Level Register ..............306

13.5.4 PRS_ASYNC_PEEK - Async Channel Values ................307

13.5.5 PRS_SYNC_PEEK - Sync Channel Values .................308

13.5.6 PRS_ASYNC_CHx_CTRL - Async Channel Control Register ...........309

13.5.7 PRS_SYNC_CHx_CTRL - Sync Channel Control Register ............310

13.5.8 PRS_CONSUMER_CMU_CALDN - CMU CALDN Consumer Selection ........311

13.5.9 PRS_CONSUMER_CMU_CALUP - CMU CALUP Consumer Selection ........311

13.5.10 PRS_CONSUMER_IADC0_SCANTRIGGER - IADC0 SCANTRIGGER Consumer Selection 312

13.5.11 PRS_CONSUMER_IADC0_SINGLETRIGGER - IADC0 SINGLETRIGGER Consumer

Selection .............................312

13.5.12 PRS_CONSUMER_LDMAXBAR_DMAREQ0 - DMAREQ0 Consumer Selection ....313

13.5.13 PRS_CONSUMER_LDMAXBAR_DMAREQ1 - DMAREQ1 Consumer Selection ....313

13.5.14 PRS_CONSUMER_LETIMER0_CLEAR - LETIMER CLEAR Consumer Selection ....314

13.5.15 PRS_CONSUMER_LETIMER0_START - LETIMER START Consumer Selection ....314

13.5.16 PRS_CONSUMER_LETIMER0_STOP - LETIMER STOP Consumer Selection .....315

13.5.17 PRS_CONSUMER_MODEM_DIN - MODEM DIN Consumer Selection........315

13.5.18 PRS_CONSUMER_RAC_CLR - RAC CLR Consumer Selection ..........316

13.5.19 PRS_CONSUMER_RAC_FORCETX - RAC FORCETX Consumer Selection .....316

13.5.20 PRS_CONSUMER_RAC_RXDIS - RAC RXDIS Consumer Selection ........317

13.5.21 PRS_CONSUMER_RAC_RXEN - RAC RXEN Consumer Selection .........317

13.5.22 PRS_CONSUMER_RAC_SEQ - RAC SEQ Consumer Selection ..........318

13.5.23 PRS_CONSUMER_RAC_TXEN - RAC TXEN Consumer Selection .........318

13.5.24 PRS_CONSUMER_RTCC_CC0 - RTCC CC0 Consumer Selection .........319

13.5.25 PRS_CONSUMER_RTCC_CC1 - RTCC CC1 Consumer Selection .........319

13.5.26 PRS_CONSUMER_RTCC_CC2 - RTCC CC2 Consumer Selection .........320

13.5.27 PRS_CONSUMER_SE_TAMPERSRC0 - SE TAMPERSRC0 Consumer Selection ...320

13.5.28 PRS_CONSUMER_SE_TAMPERSRC1 - SE TAMPERSRC1 Consumer Selection ...321

13.5.29 PRS_CONSUMER_SE_TAMPERSRC2 - SE TAMPERSRC2 Consumer Selection ...321

13.5.30 PRS_CONSUMER_SE_TAMPERSRC3 - SE TAMPERSRC3 Consumer Selection ...322

silabs.com

| Building a more connected world. Rev. 0.4 | 8

Page 9

13.5.31 PRS_CONSUMER_SE_TAMPERSRC4 - SE TAMPERSRC4 Consumer Selection ...322

13.5.32 PRS_CONSUMER_SE_TAMPERSRC5 - SE TAMPERSRC5 Consumer Selection ...323

13.5.33 PRS_CONSUMER_SE_TAMPERSRC6 - SE TAMPERSRC6 Consumer Selection ...323

13.5.34 PRS_CONSUMER_SE_TAMPERSRC7 - SE TAMPERSRC7 Consumer Selection ...324

13.5.35 PRS_CONSUMER_CORE_CTIIN0 - CTI0 Consumer Selection ..........324

13.5.36 PRS_CONSUMER_CORE_CTIIN1 - CTI1 Consumer Selection ..........325

13.5.37 PRS_CONSUMER_CORE_CTIIN2 - CTI2 Consumer Selection ..........325

13.5.38 PRS_CONSUMER_CORE_CTIIN3 - CTI3 Consumer Selection ..........326

13.5.39 PRS_CONSUMER_CORE_M33RXEV - M33 Consumer Selection .........326

13.5.40 PRS_CONSUMER_TIMER0_CC0 - TIMER0 CC0 Consumer Selection .......327

13.5.41 PRS_CONSUMER_TIMER0_CC1 - TIMER0 CC1 Consumer Selection .......327

13.5.42 PRS_CONSUMER_TIMER0_CC2 - TIMER0 CC2 Consumer Selection .......328

13.5.43 PRS_CONSUMER_TIMER0_DTI - TIMER0 DTI Consumer Selection ........328

13.5.44 PRS_CONSUMER_TIMER0_DTIFS1 - TIMER0 DTIFS1 Consumer Selection .....329

13.5.45 PRS_CONSUMER_TIMER0_DTIFS2 - TIMER0 DTIFS2 Consumer Selection .....329

13.5.46 PRS_CONSUMER_TIMER1_CC0 - TIMER1 CC0 Consumer Selection .......330

13.5.47 PRS_CONSUMER_TIMER1_CC1 - TIMER1 CC1 Consumer Selection .......330

13.5.48 PRS_CONSUMER_TIMER1_CC2 - TIMER1 CC2 Consumer Selection .......331

13.5.49 PRS_CONSUMER_TIMER1_DTI - TIMER1 DTI Consumer Selection ........331

13.5.50 PRS_CONSUMER_TIMER1_DTIFS1 - TIMER1 DTIFS1 Consumer Selection .....332

13.5.51 PRS_CONSUMER_TIMER1_DTIFS2 - TIMER1 DTIFS2 Consumer Selection .....332

13.5.52 PRS_CONSUMER_TIMER2_CC0 - TIMER2 CC0 Consumer Selection .......333

13.5.53 PRS_CONSUMER_TIMER2_CC1 - TIMER2 CC1 Consumer Selection .......333

13.5.54 PRS_CONSUMER_TIMER2_CC2 - TIMER2 CC2 Consumer Selection .......334

13.5.55 PRS_CONSUMER_TIMER2_DTI - TIMER2 DTI Consumer Selection ........334

13.5.56 PRS_CONSUMER_TIMER2_DTIFS1 - TIMER2 DTIFS1 Consumer Selection .....335

13.5.57 PRS_CONSUMER_TIMER2_DTIFS2 - TIMER2 DTIFS2 Consumer Selection .....335

13.5.58 PRS_CONSUMER_TIMER3_CC0 - TIMER3 CC0 Consumer Selection .......336

13.5.59 PRS_CONSUMER_TIMER3_CC1 - TIMER3 CC1 Consumer Selection .......336

13.5.60 PRS_CONSUMER_TIMER3_CC2 - TIMER3 CC2 Consumer Selection .......337

13.5.61 PRS_CONSUMER_TIMER3_DTI - TIMER3 DTI Consumer Selection ........337

13.5.62 PRS_CONSUMER_TIMER3_DTIFS1 - TIMER3 DTIFS1 Consumer Selection .....338

13.5.63 PRS_CONSUMER_TIMER3_DTIFS2 - TIMER3 DTIFS2 Consumer Selection .....338

13.5.64 PRS_CONSUMER_USART0_CLK - USART0 CLK Consumer Selection .......339

13.5.65 PRS_CONSUMER_USART0_IR - USART0 IR Consumer Selection ........339

13.5.66 PRS_CONSUMER_USART0_RX - USART0 RX Consumer Selection ........340

13.5.67 PRS_CONSUMER_USART0_TRIGGER - USART0 TRIGGER Consumer Selection ...340

13.5.68 PRS_CONSUMER_USART1_CLK - USART1 CLK Consumer Selection .......341

13.5.69 PRS_CONSUMER_USART1_IR - USART1 IR Consumer Selection ........341

13.5.70 PRS_CONSUMER_USART1_RX - USART1 RX Consumer Selection ........342

13.5.71 PRS_CONSUMER_USART1_TRIGGER - USART1 TRIGGER Consumer Selection ...342

13.5.72 PRS_CONSUMER_USART2_CLK - USART2 CLK Consumer Selection .......343

13.5.73 PRS_CONSUMER_USART2_IR - USART2 IR Consumer Selection ........343

13.5.74 PRS_CONSUMER_USART2_RX - USART2 RX Consumer Selection ........344

13.5.75 PRS_CONSUMER_USART2_TRIGGER - USART2 TRIGGER Consumer Selection ...344

13.5.76 PRS_CONSUMER_WDOG0_SRC0 - WDOG0 SRC0 Consumer Selection ......345

13.5.77 PRS_CONSUMER_WDOG0_SRC1 - WDOG0 SRC1 Consumer Selection ......345

13.5.78 PRS_CONSUMER_WDOG1_SRC0 - WDOG1 SRC0 Consumer Selection ......346

silabs.com

| Building a more connected world. Rev. 0.4 | 9

Page 10

13.5.79 PRS_CONSUMER_WDOG1_SRC1 - WDOG1 SRC1 Consumer Selection ......346

14. GPCRC - General Purpose Cyclic Redundancy Check ..............347

14.1 Introduction..............................347

14.2 Features ..............................347

14.3 Functional Description ..........................348

14.3.1 Polynomial Specification ........................349

14.3.2 Input and Output Specification ......................349

14.3.3 Initialization ............................349

14.3.4 DMA Usage ............................349

14.3.5 Byte-Level Bit Reversal and Byte Reordering .................350

14.4 Register Map .............................353

14.5 Register Description ...........................354

14.5.1 GPCRC_IPVERSION - IP Version ID ...................354

14.5.2 GPCRC_EN - CRC Enable .......................355

14.5.3 GPCRC_CTRL - Control Register .....................356

14.5.4 GPCRC_CMD - Command Register ....................357

14.5.5 GPCRC_INIT - CRC Init Value ......................357

14.5.6 GPCRC_POLY - CRC Polynomial Value ..................358

14.5.7 GPCRC_INPUTDATA - Input 32-bit Data Register ...............358

14.5.8 GPCRC_INPUTDATAHWORD - Input 16-bit Data Register ............359

14.5.9 GPCRC_INPUTDATABYTE - Input 8-bit Data Register .............359

14.5.10 GPCRC_DATA - CRC Data Register ...................360

14.5.11 GPCRC_DATAREV - CRC Data Reverse Register ..............360

14.5.12 GPCRC_DATABYTEREV - CRC Data Byte Reverse Register ...........361

15. RTCC - Real Time Clock with Capture.....................362

15.1 Introduction..............................362

15.2 Features ..............................363

15.3 Functional Description ..........................363

15.3.1 RTCC Counter ...........................364

15.3.2 Capture/Compare Channels ......................366

15.3.3 Interrupts and PRS Output .......................367

15.3.4 Register Lock ...........................368

15.3.5 Programmer's Model .........................368

15.3.6 Debug Features and Description .....................368

15.3.7 Compatibility ............................368

15.4 Register Map .............................369

15.5 Register Description ...........................371

15.5.1 RTCC_IPVERSION - IP VERSION ....................371

15.5.2 RTCC_EN - Module Enable Register ...................371

15.5.3 RTCC_CFG - Configuration Register ...................372

15.5.4 RTCC_CMD - Command Register ....................373

15.5.5 RTCC_STATUS - Status register .....................374

15.5.6 RTCC_IF - RTCC Interrupt Flags .....................375

15.5.7 RTCC_IEN - Interrupt Enable Register ...................376

silabs.com

| Building a more connected world. Rev. 0.4 | 10

Page 11

15.5.8 RTCC_PRECNT - Pre-Counter Value Register ................376

15.5.9 RTCC_CNT - Counter Value Register ...................377

15.5.10 RTCC_COMBCNT - Combined Pre-Counter and Counter Valu... ..........377

15.5.11 RTCC_SYNCBUSY - Synchronization Busy Register ..............378

15.5.12 RTCC_LOCK - Configuration Lock Register .................378

15.5.13 RTCC_CCx_CTRL - CC Channel Control Register ..............379

15.5.14 RTCC_CCx_OCVALUE - Output Compare Value Register ............380

15.5.15 RTCC_CCx_ICVALUE - Input Capture Value Register .............380

16. BURTC - Back-Up Real Time Counter .....................381

16.1 Introduction..............................381

16.2 Features ..............................381

16.3 Functional Description ..........................382

16.3.1 Clock Selection ...........................382

16.3.2 Configuration ...........................382

16.3.3 Debug Features and Description .....................382

16.3.4 Counter .............................383

16.3.5 Compare Channel ..........................383

16.3.6 Interrupts .............................384

16.3.7 Register Lock ...........................384

16.4 Register Map .............................385

16.5 Register Description ...........................386

16.5.1 BURTC_IPVERSION - IP version ID ....................386

16.5.2 BURTC_EN - Module Enable Register ...................387

16.5.3 BURTC_CFG - Configuration Register ...................388

16.5.4 BURTC_CMD - Command Register ....................389

16.5.5 BURTC_STATUS - Status Register ....................390

16.5.6 BURTC_IF - Interrupt Flag Register ....................390

16.5.7 BURTC_IEN - Interrupt Enable Register ..................391

16.5.8 BURTC_PRECNT - Pre-Counter Value Register ................391

16.5.9 BURTC_CNT - Counter Value Register ...................392

16.5.10 BURTC_EM4WUEN - EM4 wakeup request Enable Register ...........392

16.5.11 BURTC_SYNCBUSY - Synchronization Busy Register .............393

16.5.12 BURTC_LOCK - Configuration Lock Register ................394

16.5.13 BURTC_COMP - Compare Value Register .................394

17. BURAM - Backup RAM ..........................395

17.1 Introduction..............................395

17.2 Functional Description ..........................395

17.3 Register Map .............................395

17.4 Register Description ...........................396

17.4.1 BURAM_RETx_REG - Retention Register ..................396

18. LETIMER - Low Energy Timer ........................397

18.1 Introduction..............................397

18.2 Features ..............................397

silabs.com

| Building a more connected world. Rev. 0.4 | 11

Page 12

18.3 Functional Description ..........................398

18.3.1 Internal Overview ..........................399

18.3.2 Free Running Mode .........................400

18.3.3 One-shot Mode ...........................401

18.3.4 Buffered Mode ...........................402

18.3.5 Double Mode ...........................403

18.4 Clock Frequency ............................404

18.5 PRS Input Triggers ...........................405

18.6 Debug ...............................405

18.7 Output Action .............................406

18.8 PRS Output .............................406

18.9 Interrupts ..............................406

18.10 Using the LETIMER in EM3 ........................406

18.11 Register access ............................406

18.12 Programmer's Model ..........................407

18.12.1 FREE Running Mode ........................408

18.12.2 One Shot Mode ..........................409

18.12.3 DOUBLE Mode ..........................409

18.12.4 BUFFERED Mode .........................410

18.12.5 Continuous Output Generation .....................411

18.12.6 PWM Output ...........................412

18.13 Register Map.............................413

18.14 Register Description ..........................415

18.14.1 LETIMER_IPVERSION - IP version....................415

18.14.2 LETIMER_EN - module en ......................415

18.14.3 LETIMER_CTRL - Control Register ....................416

18.14.4 LETIMER_CMD - Command Register ...................418

18.14.5 LETIMER_STATUS - Status Register ...................419

18.14.6 LETIMER_CNT - Counter Value Register..................419

18.14.7 LETIMER_COMP0 - Compare Value Register 0 ...............420

18.14.8 LETIMER_COMP1 - Compare Value Register 1 ...............420

18.14.9 LETIMER_TOP - Counter TOP Value Register ................421

18.14.10 LETIMER_TOPBUFF - Buffered Counter TOP Value .............421

18.14.11 LETIMER_REP0 - Repeat Counter Register 0................422

18.14.12 LETIMER_REP1 - Repeat Counter Register 1................422

18.14.13 LETIMER_IF - Interrupt Flag Register ..................423

18.14.14 LETIMER_IEN - Interrupt Enable Register .................424

18.14.15 LETIMER_SYNCBUSY - Synchronization Busy Register ............425

18.14.16 LETIMER_PRSMODE - PRS Input mode select Register ............426

19. TIMER - Timer/Counter ..........................428

19.1 Introduction..............................428

19.2 Features ..............................429

19.3 Functional Description ..........................430

19.3.1 Register Access...........................430

silabs.com

| Building a more connected world. Rev. 0.4 | 12

Page 13

19.3.2 Counter Modes ...........................431

19.3.3 Compare/Capture Channels ......................437

19.3.4 Dead-Time Insertion Unit .......................448

19.3.5 Debug Mode ............................452

19.3.6 Interrupts, DMA and PRS Output .....................452

19.3.7 GPIO Input/Output ..........................452

19.4 Register Map .............................453

19.5 Register Description ...........................456

19.5.1 TIMER_IPVERSION - IP version ID ....................456

19.5.2 TIMER_CFG - Configuration Register ...................457

19.5.3 TIMER_CTRL - Control Register .....................460

19.5.4 TIMER_CMD - Command Register ....................461

19.5.5 TIMER_STATUS - Status Register ....................462

19.5.6 TIMER_IF - Interrupt Flag Register ....................465

19.5.7 TIMER_IEN - Interrupt Enable Register ...................467

19.5.8 TIMER_TOP - Counter Top Value Register .................468

19.5.9 TIMER_TOPB - Counter Top Value Buffer Register ...............468

19.5.10 TIMER_CNT - Counter Value Register ..................469

19.5.11 TIMER_LOCK - TIMER Configuration Lock Register ..............469

19.5.12 TIMER_EN - module en .......................470

19.5.13 TIMER_CCx_CFG - CC Channel Configuration Register ............471

19.5.14 TIMER_CCx_CTRL - CC Channel Control Register ..............473

19.5.15 TIMER_CCx_OC - OC Channel Value Register ...............474

19.5.16 TIMER_CCx_OCB - OC Channel Value Buffer Register .............475

19.5.17 TIMER_CCx_ICF - IC Channel Value Register ................475

19.5.18 TIMER_CCx_ICOF - IC Channel Value Overflow Register ............475

19.5.19 TIMER_DTCFG - DTI Configuration Register ................476

19.5.20 TIMER_DTTIMECFG - DTI Time Configuration Register ............477

19.5.21 TIMER_DTFCFG - DTI Fault Configuration Register ..............478

19.5.22 TIMER_DTCTRL - DTI Control Register ..................479

19.5.23 TIMER_DTOGEN - DTI Output Generation Enable Register ...........480

19.5.24 TIMER_DTFAULT - DTI Fault Register ..................481

19.5.25 TIMER_DTFAULTC - DTI Fault Clear Register ................482

19.5.26 TIMER_DTLOCK - DTI Configuration Lock Register ..............483

20. USART - Universal Synchronous Asynchronous Receiver/Transmitter ........484

20.1 Introduction..............................484

20.2 Features ..............................485

20.3 Functional Description ..........................486

20.3.1 Modes of Operation .........................487

20.3.2 Asynchronous Operation ........................487

20.3.3 Synchronous Operation ........................503

20.3.4 Hardware Flow Control ........................509

20.3.5 Debug Halt ............................509

20.3.6 PRS-triggered Transmissions ......................509

20.3.7 PRS RX Input ...........................509

20.3.8 PRS CLK Input ...........................510

silabs.com

| Building a more connected world. Rev. 0.4 | 13

Page 14

20.3.9 DMA Support ...........................510

20.3.10 Timer ..............................511

20.3.11 Interrupts ............................516

20.3.12 IrDA Modulator/ Demodulator ......................517

20.4 Register Map .............................518

20.5 Register Description ...........................521

20.5.1 USART_IPVERSION - IPVERSION ....................521

20.5.2 USART_EN - USART Enable ......................521

20.5.3 USART_CTRL - Control Register .....................522

20.5.4 USART_FRAME - USART Frame Format Register ...............527

20.5.5 USART_TRIGCTRL - USART Trigger Control register ..............529

20.5.6 USART_CMD - Command Register ....................530

20.5.7 USART_STATUS - USART Status Register .................531

20.5.8 USART_CLKDIV - Clock Control Register ..................532

20.5.9 USART_RXDATAX - RX Buffer Data Extended Register .............533

20.5.10 USART_RXDATA - RX Buffer Data Register ................533

20.5.11 USART_RXDOUBLEX - RX Buffer Double Data Extended Register .........534

20.5.12 USART_RXDOUBLE - RX FIFO Double Data Register .............535

20.5.13 USART_RXDATAXP - RX Buffer Data Extended Peek Register ..........535

20.5.14 USART_RXDOUBLEXP - RX Buffer Double Data Extended Peek R... ........536

20.5.15 USART_TXDATAX - TX Buffer Data Extended Register .............537

20.5.16 USART_TXDATA - TX Buffer Data Register .................538

20.5.17 USART_TXDOUBLEX - TX Buffer Double Data Extended Register .........539

20.5.18 USART_TXDOUBLE - TX Buffer Double Data Register .............540

20.5.19 USART_IF - Interrupt Flag Register....................541

20.5.20 USART_IEN - Interrupt Enable Register ..................543

20.5.21 USART_IRCTRL - IrDA Control Register ..................545

20.5.22 USART_I2SCTRL - I2S Control Register ..................546

20.5.23 USART_TIMING - Timing Register ....................548

20.5.24 USART_CTRLX - Control Register Extended ................550

20.5.25 USART_TIMECMP0 - Used to generate interrupts and vario... ..........552

20.5.26 USART_TIMECMP1 - Used to generate interrupts and vario... ..........554

20.5.27 USART_TIMECMP2 - Used to generate interrupts and vario... ..........556

21. I2C - Inter-Integrated Circuit Interface .....................558

21.1 Introduction..............................558

21.2 Features ..............................558

21.3 Functional Description ..........................559

21.3.1 I2C-Bus Overview ..........................560

21.3.2 Enable and Reset ..........................564

21.3.3 Pin Configuration ..........................564

21.3.4 Safely Disabling and Changing Slave Configuration...............564

21.3.5 Clock Generation ..........................565

21.3.6 Arbitration .............................565

21.3.7 Buffers ..............................565

21.3.8 Master Operation ..........................568

21.3.9 Bus States ............................576

silabs.com

| Building a more connected world. Rev. 0.4 | 14

Page 15

21.3.10 Slave Operation ..........................576

21.3.11 Transfer Automation .........................580

21.3.12 Using 10-bit Addresses ........................581

21.3.13 Error Handling ...........................581

21.3.14 DMA Support ...........................583

21.3.15 Interrupts ............................583

21.3.16 Wake-up .............................583

21.4 Register Map .............................584

21.5 Register Description ...........................586

21.5.1 I2C_IPVERSION - IP VERSION Register ..................586

21.5.2 I2C_EN - Enable Register .......................586

21.5.3 I2C_CTRL - Control Register ......................587

21.5.4 I2C_CMD - Command Register .....................591

21.5.5 I2C_STATE - State Register ......................592

21.5.6 I2C_STATUS - Status Register .....................593

21.5.7 I2C_CLKDIV - Clock Division Register ...................594

21.5.8 I2C_SADDR - Slave Address Register ...................594

21.5.9 I2C_SADDRMASK - Slave Address Mask Register ...............595

21.5.10 I2C_RXDATA - Receive Buffer Data Register ................595

21.5.11 I2C_RXDOUBLE - Receive Buffer Double Data Register ............596

21.5.12 I2C_RXDATAP - Receive Buffer Data Peek Register ..............596

21.5.13 I2C_RXDOUBLEP - Receive Buffer Double Data Peek Register ..........597

21.5.14 I2C_TXDATA - Transmit Buffer Data Register ................597

21.5.15 I2C_TXDOUBLE - Transmit Buffer Double Data Register ............598

21.5.16 I2C_IF - Interrupt Flag Register .....................599

21.5.17 I2C_IEN - Interrupt Enable Register ...................601

22. ACMP - Analog Comparator ........................603

22.1 Introduction .............................603

22.2 Features ..............................603

22.3 Functional Description ..........................604

22.3.1 Configuration and Control .......................604

22.3.2 Warmup Time ...........................605

22.3.3 Response Time ...........................605

22.3.4 Hysteresis ............................605

22.3.5 VREFDIV Sources ..........................606

22.3.6 Supply Voltage Monitoring (VSENSE) ...................606

22.3.7 Input Range and Accuracy Settings ....................606

22.3.8 Capacitive Sense Mode ........................607

22.3.9 Interrupts and PRS Output .......................608

22.3.10 Output to GPIO ..........................608

22.4 Register Map .............................609

22.5 Register Description ...........................610

22.5.1 ACMP_IPVERSION - IP version ID ....................610

22.5.2 ACMP_EN - ACMP enable .......................610

22.5.3 ACMP_CFG - Configuration register ....................611

22.5.4 ACMP_CTRL - Control Register .....................612

silabs.com

| Building a more connected world. Rev. 0.4 | 15

Page 16

22.5.5 ACMP_INPUTCTRL - Input Control Register .................613

22.5.6 ACMP_STATUS - Status Register ....................618

22.5.7 ACMP_IF - Interrupt Flag Register ....................619

22.5.8 ACMP_IEN - Interrupt Enable Register ...................620

22.5.9 ACMP_SYNCBUSY - Syncbusy .....................620

23. IADC - Incremental Analog to Digital Converter .................621

23.1 Introduction..............................621

23.2 Features ..............................622

23.3 Functional Description ..........................623

23.3.1 Register Access...........................624

23.3.2 Clocking .............................625

23.3.3 Conversion Timing ..........................626

23.3.4 Reference Selection and Analog Gain ...................633

23.3.5 Input and Configuration Selection .....................633

23.3.6 Gain and Offset Correction .......................638

23.3.7 Output Data FIFOs ..........................642

23.3.8 Window Compare ..........................644

23.3.9 Interrupts .............................645

23.4 Register Map .............................646

23.5 Register Description ...........................649

23.5.1 IADC_IPVERSION - IPVERSION .....................649

23.5.2 IADC_EN - Enable ..........................649

23.5.3 IADC_CTRL - Control ........................650

23.5.4 IADC_CMD - Command ........................652

23.5.5 IADC_TIMER - Timer .........................653

23.5.6 IADC_STATUS - Status ........................654

23.5.7 IADC_MASKREQ - Mask Request ....................655

23.5.8 IADC_STMASK - Scan Table Mask ....................656

23.5.9 IADC_CMPTHR - Digital Window comparator Threshold .............656

23.5.10 IADC_IF - Interrupt Flags .......................657

23.5.11 IADC_IEN - Interrupt Enable ......................659

23.5.12 IADC_TRIGGER - Trigger .......................661

23.5.13 IADC_CFGx - Configuration ......................664

23.5.14 IADC_SCALEx - Scaling .......................666

23.5.15 IADC_SCHEDx - Scheduling ......................666

23.5.16 IADC_SINGLEFIFOCFG - Single FIFO Configuration .............667

23.5.17 IADC_SINGLEFIFODATA - Single FIFO Read Data ..............668

23.5.18 IADC_SINGLEFIFOSTAT - Single FIFO Status ................668

23.5.19 IADC_SINGLEDATA - Single Data ....................669

23.5.20 IADC_SCANFIFOCFG - Scan FIFO Configuration ...............670

23.5.21 IADC_SCANFIFODATA - Scan FIFO Read Data ...............671

23.5.22 IADC_SCANFIFOSTAT - Scan FIFO Status .................671

23.5.23 IADC_SCANDATA - Scan Data .....................672

23.5.24 IADC_SINGLE - Single Queue Port Selection ................673

23.5.25 IADC_SCANx - SCAN Entry ......................675

24. GPIO - General Purpose Input/Output .....................677

silabs.com

| Building a more connected world. Rev. 0.4 | 16

Page 17

24.1 Introduction .............................677

24.2 Features ..............................678

24.3 Functional Description ..........................679

24.3.1 Pin Configuration ..........................680

24.3.2 Alternate Port Control ........................682

24.3.3 Slew Rate .............................682

24.3.4 Input Disable ............................682

24.3.5 Configuration Lock ..........................682

24.3.6 EM2 Functionality ..........................682

24.3.7 EM4 Functionality ..........................682

24.3.8 EM4 Wakeup ...........................683

24.3.9 Debug Connections .........................683

24.3.10 Interrupt Generation .........................684

24.3.11 Output to PRS ...........................685

24.3.12 Peripheral Resource Routing ......................685

24.4 Synchronization ............................687

24.5 Register Map .............................688

24.6 Register Description ...........................705

24.6.1 GPIO_PORTA_CTRL - Port control ....................705

24.6.2 GPIO_PORTA_MODEL - mode low ....................706

24.6.3 GPIO_PORTA_DOUT - data out .....................710

24.6.4 GPIO_PORTA_DIN - data in ......................710

24.6.5 GPIO_PORTB_CTRL - Port control ....................711

24.6.6 GPIO_PORTB_MODEL - mode low ....................712

24.6.7 GPIO_PORTB_DOUT - data out .....................713

24.6.8 GPIO_PORTB_DIN - data in ......................714

24.6.9 GPIO_PORTC_CTRL - Port control ....................715

24.6.10 GPIO_PORTC_MODEL - mode low ...................716

24.6.11 GPIO_PORTC_DOUT - data out ....................719

24.6.12 GPIO_PORTC_DIN - data in ......................720

24.6.13 GPIO_PORTD_CTRL - Port control ...................721

24.6.14 GPIO_PORTD_MODEL - mode low ...................722

24.6.15 GPIO_PORTD_DOUT - data out ....................725

24.6.16 GPIO_PORTD_DIN - data in ......................725

24.6.17 GPIO_LOCK - main .........................726

24.6.18 GPIO_GPIOLOCKSTATUS - Lock Status .................726

24.6.19 GPIO_ABUSALLOC - A Bus allocation ..................727

24.6.20 GPIO_BBUSALLOC - B Bus allocation ..................729

24.6.21 GPIO_CDBUSALLOC - CD Bus allocation .................731

24.6.22 GPIO_EXTIPSELL - External Interrupt Port Select Low .............733

24.6.23 GPIO_EXTIPINSELL - External Interrupt Pin Select Low ............736

24.6.24 GPIO_EXTIRISE - External Interrupt Rising Edge Trigger ............738

24.6.25 GPIO_EXTIFALL - External Interrupt Falling Edge Trigger ............739

24.6.26 GPIO_IF - Interrupt Flag .......................739

24.6.27 GPIO_IEN - Interrupt Enable ......................740

24.6.28 GPIO_EM4WUEN - main .......................740

24.6.29 GPIO_EM4WUPOL - New Register....................741

silabs.com

| Building a more connected world. Rev. 0.4 | 17

Page 18

24.6.30 GPIO_DBGROUTEPEN - Debugger Route Pin enable .............742

24.6.31 GPIO_TRACEROUTEPEN - Trace Route Pin Enable .............743

24.6.32 GPIO_ACMP0_ROUTEEN - ACMP0 pin enable ...............743

24.6.33 GPIO_ACMP0_ACMPOUTROUTE - ACMPOUT port/pin select ..........744

24.6.34 GPIO_ACMP1_ROUTEEN - ACMP1 pin enable ...............744

24.6.35 GPIO_ACMP1_ACMPOUTROUTE - ACMPOUT port/pin select ..........745

24.6.36 GPIO_CMU_ROUTEEN - CMU pin enable .................745

24.6.37 GPIO_CMU_CLKIN0ROUTE - CLKIN0 port/pin select .............746

24.6.38 GPIO_CMU_CLKOUT0ROUTE - CLKOUT0 port/pin select ...........746

24.6.39 GPIO_CMU_CLKOUT1ROUTE - CLKOUT1 port/pin select ...........747

24.6.40 GPIO_CMU_CLKOUT2ROUTE - CLKOUT2 port/pin select ...........747

24.6.41 GPIO_FRC_ROUTEEN - FRC pin enable .................748

24.6.42 GPIO_FRC_DCLKROUTE - DCLK port/pin select ...............748

24.6.43 GPIO_FRC_DFRAMEROUTE - DFRAME port/pin select ............749

24.6.44 GPIO_FRC_DOUTROUTE - DOUT port/pin select ..............749

24.6.45 GPIO_I2C0_ROUTEEN - I2C0 pin enable .................750

24.6.46 GPIO_I2C0_SCLROUTE - SCL port/pin select ................750

24.6.47 GPIO_I2C0_SDAROUTE - SDA port/pin select ................751

24.6.48 GPIO_I2C1_ROUTEEN - I2C1 pin enable .................751

24.6.49 GPIO_I2C1_SCLROUTE - SCL port/pin select ................752

24.6.50 GPIO_I2C1_SDAROUTE - SDA port/pin select ................752

24.6.51 GPIO_LETIMER0_ROUTEEN - LETIMER pin enable .............753

24.6.52 GPIO_LETIMER0_OUT0ROUTE - OUT0 port/pin select ............753

24.6.53 GPIO_LETIMER0_OUT1ROUTE - OUT1 port/pin select ............754

24.6.54 GPIO_MODEM_ROUTEEN - MODEM pin enable ...............754

24.6.55 GPIO_MODEM_ANT0ROUTE - ANT0 port/pin select .............755

24.6.56 GPIO_MODEM_ANT1ROUTE - ANT1 port/pin select .............755

24.6.57 GPIO_MODEM_DCLKROUTE - DCLK port/pin select .............756

24.6.58 GPIO_MODEM_DINROUTE - DIN port/pin select ...............756

24.6.59 GPIO_MODEM_DOUTROUTE - DOUT port/pin select .............757

24.6.60 GPIO_PRS0_ROUTEEN - PRS0 pin enable.................758

24.6.61 GPIO_PRS0_ASYNCH0ROUTE - ASYNCH0 port/pin select ...........759

24.6.62 GPIO_PRS0_ASYNCH1ROUTE - ASYNCH1 port/pin select ...........760

24.6.63 GPIO_PRS0_ASYNCH2ROUTE - ASYNCH2 port/pin select ...........760

24.6.64 GPIO_PRS0_ASYNCH3ROUTE - ASYNCH3 port/pin select ...........761

24.6.65 GPIO_PRS0_ASYNCH4ROUTE - ASYNCH4 port/pin select ...........761

24.6.66 GPIO_PRS0_ASYNCH5ROUTE - ASYNCH5 port/pin select ...........762

24.6.67 GPIO_PRS0_ASYNCH6ROUTE - ASYNCH6 port/pin select ...........762

24.6.68 GPIO_PRS0_ASYNCH7ROUTE - ASYNCH7 port/pin select ...........763

24.6.69 GPIO_PRS0_ASYNCH8ROUTE - ASYNCH8 port/pin select ...........763

24.6.70 GPIO_PRS0_ASYNCH9ROUTE - ASYNCH9 port/pin select ...........764

24.6.71 GPIO_PRS0_ASYNCH10ROUTE - ASYNCH10 port/pin select ..........764

24.6.72 GPIO_PRS0_ASYNCH11ROUTE - ASYNCH11 port/pin select ..........765

24.6.73 GPIO_PRS0_SYNCH0ROUTE - SYNCH0 port/pin select ............765

24.6.74 GPIO_PRS0_SYNCH1ROUTE - SYNCH1 port/pin select ............766

24.6.75 GPIO_PRS0_SYNCH2ROUTE - SYNCH2 port/pin select ............766

24.6.76 GPIO_PRS0_SYNCH3ROUTE - SYNCH3 port/pin select ............767

24.6.77 GPIO_TIMER0_ROUTEEN - TIMER0 pin enable ...............768

silabs.com

| Building a more connected world. Rev. 0.4 | 18

Page 19

24.6.78 GPIO_TIMER0_CC0ROUTE - CC0 port/pin select ..............769

24.6.79 GPIO_TIMER0_CC1ROUTE - CC1 port/pin select ..............769

24.6.80 GPIO_TIMER0_CC2ROUTE - CC2 port/pin select ..............770

24.6.81 GPIO_TIMER0_CDTI0ROUTE - CDTI0 port/pin select .............770

24.6.82 GPIO_TIMER0_CDTI1ROUTE - CDTI1 port/pin select .............771

24.6.83 GPIO_TIMER0_CDTI2ROUTE - CDTI2 port/pin select .............771

24.6.84 GPIO_TIMER1_ROUTEEN - TIMER1 pin enable ...............772

24.6.85 GPIO_TIMER1_CC0ROUTE - CC0 port/pin select ..............773

24.6.86 GPIO_TIMER1_CC1ROUTE - CC1 port/pin select ..............773

24.6.87 GPIO_TIMER1_CC2ROUTE - CC2 port/pin select ..............774

24.6.88 GPIO_TIMER1_CDTI0ROUTE - CDTI0 port/pin select .............774

24.6.89 GPIO_TIMER1_CDTI1ROUTE - CDTI1 port/pin select .............775

24.6.90 GPIO_TIMER1_CDTI2ROUTE - CDTI2 port/pin select .............775

24.6.91 GPIO_TIMER2_ROUTEEN - TIMER2 pin enable ...............776

24.6.92 GPIO_TIMER2_CC0ROUTE - CC0 port/pin select ..............777

24.6.93 GPIO_TIMER2_CC1ROUTE - CC1 port/pin select ..............777

24.6.94 GPIO_TIMER2_CC2ROUTE - CC2 port/pin select ..............778

24.6.95 GPIO_TIMER2_CDTI0ROUTE - CDTI0 port/pin select .............778

24.6.96 GPIO_TIMER2_CDTI1ROUTE - CDTI1 port/pin select .............779

24.6.97 GPIO_TIMER2_CDTI2ROUTE - CDTI2 port/pin select .............779

24.6.98 GPIO_TIMER3_ROUTEEN - TIMER3 pin enable ...............780

24.6.99 GPIO_TIMER3_CC0ROUTE - CC0 port/pin select ..............781

24.6.100 GPIO_TIMER3_CC1ROUTE - CC1 port/pin select ..............781

24.6.101 GPIO_TIMER3_CC2ROUTE - CC2 port/pin select ..............782

24.6.102 GPIO_TIMER3_CDTI0ROUTE - CDTI0 port/pin select .............782

24.6.103 GPIO_TIMER3_CDTI1ROUTE - CDTI1 port/pin select .............783

24.6.104 GPIO_TIMER3_CDTI2ROUTE - CDTI2 port/pin select .............783

24.6.105 GPIO_USART0_ROUTEEN - USART0 pin enable ..............784

24.6.106 GPIO_USART0_CSROUTE - CS port/pin select ...............784

24.6.107 GPIO_USART0_CTSROUTE - CTS port/pin select ..............785

24.6.108 GPIO_USART0_RTSROUTE - RTS port/pin select ..............785

24.6.109 GPIO_USART0_RXROUTE - RX port/pin select ...............786

24.6.110 GPIO_USART0_CLKROUTE - CLK port/pin select ..............786

24.6.111 GPIO_USART0_TXROUTE - TX port/pin select ...............787

24.6.112 GPIO_USART1_ROUTEEN - USART1 pin enable ..............787

24.6.113 GPIO_USART1_CSROUTE - CS port/pin select ...............788

24.6.114 GPIO_USART1_CTSROUTE - CTS port/pin select ..............788

24.6.115 GPIO_USART1_RTSROUTE - RTS port/pin select ..............789

24.6.116 GPIO_USART1_RXROUTE - RX port/pin select ...............789

24.6.117 GPIO_USART1_CLKROUTE - CLK port/pin select ..............790

24.6.118 GPIO_USART1_TXROUTE - TX port/pin select ...............790

24.6.119 GPIO_USART2_ROUTEEN - USART2 pin enable ..............791

24.6.120 GPIO_USART2_CSROUTE - CS port/pin select ...............791

24.6.121 GPIO_USART2_CTSROUTE - CTS port/pin select ..............792

24.6.122 GPIO_USART2_RTSROUTE - RTS port/pin select ..............792

24.6.123 GPIO_USART2_RXROUTE - RX port/pin select ...............793

24.6.124 GPIO_USART2_CLKROUTE - CLK port/pin select ..............793

24.6.125 GPIO_USART2_TXROUTE - TX port/pin select ...............794

silabs.com

| Building a more connected world. Rev. 0.4 | 19

Page 20

25. LDMA - Linked DMA ...........................795

25.1 Introduction..............................795

25.1.1 Features .............................796

25.2 Block Diagram.............................797

25.3 Functional Description ..........................798

25.3.1 Channel Descriptor .........................798

25.3.2 Channel Configuration ........................803

25.3.3 Channel Select Configuration ......................803

25.3.4 Starting a transfer ..........................803

25.3.5 Managing Transfer Errors .......................804

25.3.6 Arbitration .............................804

25.3.7 Channel descriptor data structure .....................806

25.3.8 Interaction with the EMU ........................809

25.3.9 Interrupts .............................810

25.3.10 Debugging ............................810

25.4 Examples ..............................810

25.4.1 Single Direct Register DMA Transfer ....................810

25.4.2 Descriptor Linked List .........................811

25.4.3 Single Descriptor Looped Transfer ....................813

25.4.4 Descriptor List with Looping .......................814

25.4.5 Simple Inter-Channel Synchronization ...................815

25.4.6 2D Copy .............................817

25.4.7 Ping-Pong ............................819

25.4.8 Scatter-Gather ...........................820

25.5 LDMA Source Selection Details .......................820

25.5.1 LDMA Source Selection Details .....................821

25.6 Register Map .............................823

25.7 Register Description ...........................826

25.7.1 LDMA_IPVERSION - DMA Channel Request Clear Register ...........826

25.7.2 LDMA_EN - DMA module enable disable Register ...............826

25.7.3 LDMA_CTRL - DMA Control Register ...................827

25.7.4 LDMA_STATUS - DMA Status Register...................828

25.7.5 LDMA_SYNCSWSET - DMA Sync Trig Sw Set Register .............829

25.7.6 LDMA_SYNCSWCLR - DMA Sync Trig Sw Clear register ............829

25.7.7 LDMA_SYNCHWEN - DMA Sync HW trigger enable register ...........830

25.7.8 LDMA_SYNCHWSEL - DMA Sync HW trigger selection register ..........831

25.7.9 LDMA_SYNCSTATUS - DMA Sync Trigger Status Register ............832

25.7.10 LDMA_CHEN - DMA Channel Enable Register ................832

25.7.11 LDMA_CHDIS - DMA Channel Disable Register ...............833

25.7.12 LDMA_CHSTATUS - DMA Channel Status Register ..............833

25.7.13 LDMA_CHBUSY - DMA Channel Busy Register ...............834

25.7.14 LDMA_CHDONE - DMA Channel Linking Done Register (Si..............835

25.7.15 LDMA_DBGHALT - DMA Channel Debug Halt Register .............836

25.7.16 LDMA_SWREQ - DMA Channel Software Transfer Request..............836

25.7.17 LDMA_REQDIS - DMA Channel Request Disable Register ............837

25.7.18 LDMA_REQPEND - DMA Channel Requests Pending Register ..........837

silabs.com

| Building a more connected world. Rev. 0.4 | 20

Page 21

25.7.19 LDMA_LINKLOAD - DMA Channel Link Load Register .............838

25.7.20 LDMA_REQCLEAR - DMA Channel Request Clear Register ...........838

25.7.21 LDMA_IF - Interrupt Flag Register ....................839

25.7.22 LDMA_IEN - Interrupt Enable Register ..................840

25.7.23 LDMA_CHx_CFG - Channel Configuration Register ..............841

25.7.24 LDMA_CHx_LOOP - Channel Loop Counter Register .............842

25.7.25 LDMA_CHx_CTRL - Channel Descriptor Control Word Register ..........843

25.7.26 LDMA_CHx_SRC - Channel Descriptor Source Data Addres... ..........846

25.7.27 LDMA_CHx_DST - Channel Descriptor Destination Data A... ...........846

25.7.28 LDMA_CHx_LINK - Channel Descriptor Link Structure Add... ...........847

25.8 Register Map .............................847

25.9 Register Description ...........................848

25.9.1 LDMAXBAR_CHx_REQSEL - Channel Peripheral Request Select Reg... .......848

26. WDOG - Watch Dog Timer .........................849

26.1 Introduction .............................849

26.2 Features ..............................849

26.3 Functional Description ..........................849

26.3.1 Clock Source ...........................850

26.3.2 Debug Functionality .........................850

26.3.3 Energy Mode Handling ........................850

26.3.4 Warning Interrupt ..........................850

26.3.5 Window Interrupt ..........................851

26.3.6 PRS as Watchdog Clear ........................852

26.3.7 PRS Rising Edge Monitoring ......................852

26.4 Register Map .............................853

26.5 Register Description ...........................854

26.5.1 WDOG_IPVERSION - IP Version Register ..................854

26.5.2 WDOG_EN - Enable Register ......................854

26.5.3 WDOG_CFG - Configuration Register ...................855

26.5.4 WDOG_CMD - Command Register ....................858

26.5.5 WDOG_STATUS - Status Register ....................858

26.5.6 WDOG_IF - Interrupt Flag Register ....................859

26.5.7 WDOG_IEN - Interrupt Enable Register ...................860

26.5.8 WDOG_LOCK - Lock Register ......................861

26.5.9 WDOG_SYNCBUSY - Synchronization Busy Register ..............861

27. Revision History.............................862

Appendix 1. Abbreviations ..........................863

silabs.com

| Building a more connected world. Rev. 0.4 | 21

Page 22

Reference Manual

About This Document

1. About This Document

1.1 Introduction

This document contains reference material for the EFR32xG21 devices. All modules and peripherals in the EFR32xG21 devices are

described in general terms. Not all modules are present in all devices and the feature set for each device might vary. Such differences,

including pinout, are covered in the device data sheets.

silabs.com | Building a more connected world. Rev. 0.4 | 22

Page 23

Reference Manual

About This Document

1.2 Conventions

Register Names

Register names are given with a module name prefix followed by the short register name:

TIMERn_CTRL - Control Register

The "n" denotes the module number for modules which can exist in more than one instance.

Some registers are grouped which leads to a group name following the module prefix:

GPIO_Px_DOUT - Port Data Out Register

The "x" denotes the different ports.

Bit Fields

Registers contain one or more bit fields which can be 1 to 32 bits wide. Bit fields wider than 1 bit are given with start (x) and stop (y) bit

[y:x].

Bit fields containing more than one bit are unsigned integers unless otherwise is specified.

Unspecified bit field settings must not be used, as this may lead to unpredictable behaviour.

Address

The address for each register can be found by adding the base address of the module found in the Memory Map (see Figure 4.1 Sys-

tem Address Space with Core and Code Space Listing on page 40), and the offset address for the register (found in module Register

Map).

Access Type

The register access types used in the register descriptions are explained in Table 1.1 Register Access Types on page 23.

Table 1.1. Register Access Types

Access Type Description

R Read only. Writes are ignored

RW Readable and writable

RW1 Readable and writable. Only writes to 1 have effect

(R)W1 Sometimes readable. Only writes to 1 have effect. Currently only

used for IF_CLEAR registers (see 3.3.1 Interrupt Operation)

W1 Read value undefined. Only writes to 1 have effect

W Write only. Read value undefined.

RWH Readable, writable, and updated by hardware

RW(nB), RWH(nB), etc. "(nB)" suffix indicates that register explicitly does not support pe-

ripheral bit set or clear (see 4. Memory and Bus System)

RW(a), R(a), etc. "(a)" suffix indicates that reading the register cause an action and

ay alter the register value.

Number format

0x prefix is used for hexadecimal numbers

0b prefix is used for binary numbers

Numbers without prefix are in decimal representation.

Reserved

Registers and bit fields marked with reserved are reserved for future use. These should be written to 0 unless otherwise stated in the

Register Description. Reserved bits might be read as 1 in future devices.

silabs.com | Building a more connected world. Rev. 0.4 | 23

Page 24

Reference Manual

About This Document

Reset Value

The reset value denotes the value after reset.

Registers denoted with X have unknown value out of reset and need to be initialized before use. Note that read-modify-write operations

on these registers before they are initialized results in undefined register values.

Pin Connections

Pin connections are given with a module prefix followed by a short pin name:

CMU_CLKOUT1 (Clock management unit, clock output pin number 1)

The location for the pin names given in the module documentation can be found in the device-specific datasheet.

1.3 Related Documentation

Further documentation on the EFR32xG21 devices and the ARM Cortex-M33 can be found at the Silicon Labs and ARM web pages:

www.silabs.com

www.arm.com

silabs.com | Building a more connected world. Rev. 0.4 | 24

Page 25

2. System Overview

43210

Reference Manual

System Overview

Quick Facts

What?

The EFR32 Wireless Gecko is a highly integrated,

configurable and low power wireless System-onChip (SoC) with a robust set of MCU and radio peripherals.

Why?

The Radio enables support for Bluetooth Smart

(BLE), ZigBee, Thread and Proprietary Protocols in

2.4 GHz frequency bands while the MCU system allows customized protocols and applications to run

efficiently.

How?

Dynamic or fixed packet lengths, optional address

recognition, and flexible CRC and security schemes

makes the EFR32xG21 ideal for many wireless IoT

applications. High performance analog and digital

peripherals allows complete applications to run on

the EFR32xG21 SoC.

silabs.com | Building a more connected world. Rev. 0.4 | 25

Page 26

Reference Manual

System Overview

2.1 Introduction

The high level features of EFR32xG21 include:

• High performance radio transceiver

• Low power consumption in transmit, receive, and standby modes

• Excellent receiver performance, including sensitivity, selectivity, and blocking

• Excellent transmitter performance, including programmable output power, low phase noise, and power-amplifier (PA) ramping

• Wake on Radio

• Configurable protocol support, including standards and customer developed protocols

• Preamble and frame synchronization insertion in transmit, and recovery in receive

• Flexible CRC support, including configurable polynomial and multiple CRCs for single data frames

• Basic address filtering performed in hardware

• High performance, low power MCU system

• High Performance 32-bit ARM Cortex-M33 CPU

• Flexible and efficient energy management

• Complete set of digital peripherals

• Peripheral Reflex System (PRS)

• Precision analog interfaces

• Low external component count

• Fully integrated 2.4 GHz BALUN

• Integrated tunable crystal loading capacitors

A further introduction to the MCU and radio system is included in the following sections.

Note: Detailed performance numbers, current consumption, pinout etc. is available in the device datasheet.

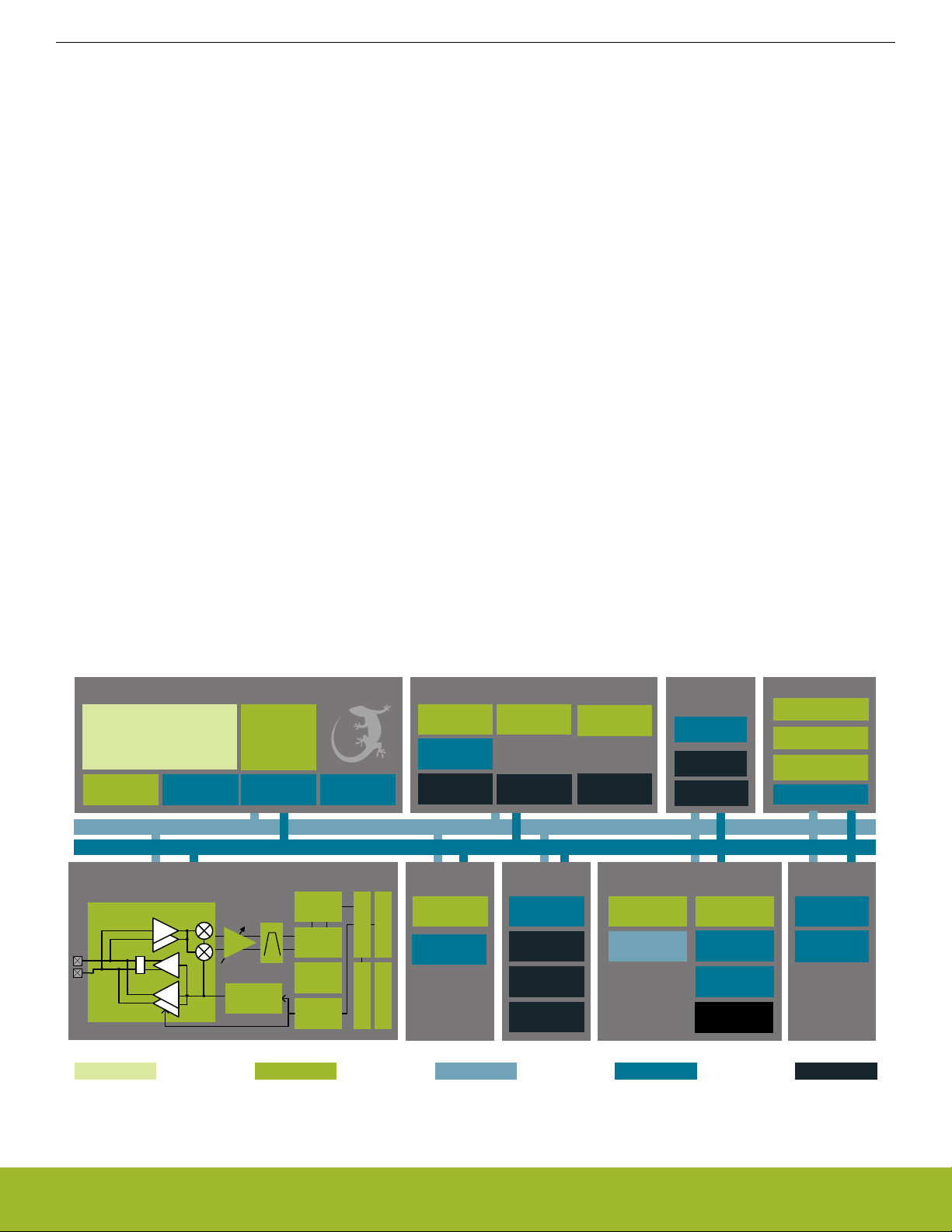

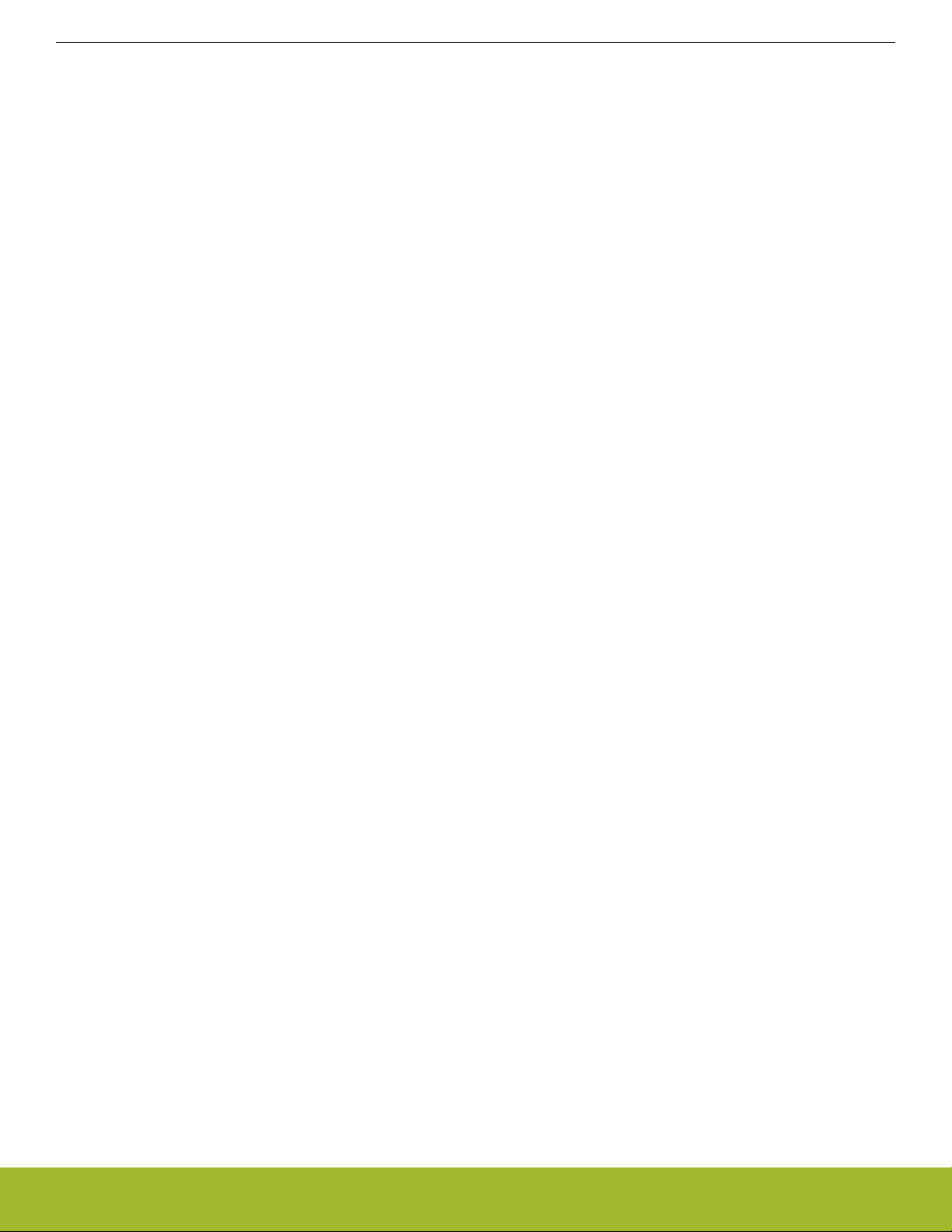

2.2 Block Diagrams

The block diagram for the EFR32xG21 System-On-Chip series is shown in (Figure 2.1 EFR32xG21 System-On-Chip Block Diagram on

page 26).

Core / Memory

ARM Cortex

TM

M33 processor

with DSP extensions,

FPU and Trust Zone

ETM Debug Interface RAM Memory

Flash Program

Memory

Radio Transceiver

RF Frontend

LNA

PA

PA

I

Q

PGA

Frequency

Synth

DEMOD

IFADC

AGC

MOD

LDMA

Controller

FRC

CRC

HF Crystal

Oscillator

EM23 HF RC

Oscillator

LF Crystal

Oscillator

32-bit bus

Peripheral Reflex System

Serial

Interfaces

USART

BUFC

RAC

2

I

C

Clock Management

HF

RC Oscillator

Ultra LF RC

Oscillator

I/O Ports Analog I/F

External

Interrupts

General

Purpose I/O

Pin Reset

Pin Wakeup

Fast Startup

RC Oscillator

LF

RC Oscillator

Timer/Counter

Low Energy Timer

Timers and Triggers

Energy

Management

Voltage

Regulator

Brown-Out

Detector

Power-On Reset

Protocol Timer

Watchdog Timer

Real Time

Capture Counter

Back-Up Real

Time Counter

Security

Crypto Acceleration

True Random

Number Generator

Secure Debug

Authentication

Secure Element

iADC

Analog

Comparator

Lowest power mode with peripheral operational:

EM3—StopEM2—Deep SleepEM1—SleepEM0—Active

EM4—Shutoff

Figure 2.1. EFR32xG21 System-On-Chip Block Diagram

silabs.com | Building a more connected world. Rev. 0.4 | 26

Page 27

Reference Manual

System Overview

2.3 MCU Features overview

• ARM Cortex-M33 CPU platform

• High Performance 32-bit processor @ up to 80 MHz

• DSP instruction support and floating-point unit

• Memory Protection Unit

• Wake-up Interrupt Controller

• Flexible Energy Management System

• 5 Energy Modes from EM0 to EM4 provide flexibility between higher performance and low power

• Power routing configurations including DCDC control

• Voltage Monitoring and Brown Out Detection

• State Retention

• Up to 1024 kB Flash

• Read-while-write support

• Up to 96 kB RAM

• Up to 20 General Purpose I/O pins

• Configurable push-pull, open-drain, pull-up/down, input filter, slew rate

• Configurable peripheral I/O locations

• 16 asynchronous external interrupts

• Output state retention and wake-up from Shutoff Mode

• 8 Channel DMA Controller

• Alternate/primary descriptors with scatter-gather/ping-pong operation

• 16 Channel Peripheral Reflex System (PRS)

• Autonomous inter-peripheral signaling enables smart operation in low energy modes

• 12 asynchronous channels with configurable logic functionality

• 4 synchronous channels for high-speed signalling between TIMER and IADC

• Advanced Encryption Standard Accelerator (AES)

• AES encryption / decryption, with 128 or 256 bit keys

• Multiple AES modes of operation, including Counter (CTR), Electronic CodeBook (ECB), Cipher Block Chaining (CBC), Counter

mode with CBC-MAC (CCM), and Cipher-based Message Authentication Code (CMAC).

• Accelerated SHA-1 and SHA-2 (SHA-224 / SHA-256)

• Accelerated Elliptic Curve Cryptography (ECC), with binary or prime fields

• Flexible 256-bit ALU and sequencer

• General Purpose Cyclic Redundancy Check (GPCRC)

• Programmable 16-bit polynomial, fixed 32-bit polynomial

• The GPCRC module is in addition to the radio CRC

• Communication interfaces

• 3 × Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

• UART/SPI/SmartCard (ISO 7816)/IrDA/I2S

• Triple buffered full/half-duplex operation

• Hardware flow control

• 4-16 data bits

•

2 × I2C Interface (I2C) with SMBus support

• Address recognition in EM3 Stop Mode

silabs.com | Building a more connected world. Rev. 0.4 | 27

Page 28

• Timers/Counters

• 2 × 16-bit Timer/Counter (TIMER)

• Up to 3 Compare/Capture/PWM channels

• Dead-Time Insertion

• 32-bit Timer/Counter (TIMER)

• Up to 3 Compare/Capture/PWM channels

• 24-bit Low Energy Timer (LETIMER)

• 32-bit Ultra Low Energy Backup Real Time Counter (BURTC) for periodic wake-up from any Energy Mode

• 32-bit Real-Time Capture Counter (RTCC)

• 32-bit Back-Up Real-Time Counter (BURTC)

• 2 × Watchdog Timers (WDOG)

• Ultra low power precision analog peripherals

• 12-bit 1 Msps Incremental Analog to Digital Converter (IADC)

• Single ended or differential operation

• Conversion tailgating for predictable latency

• 2 × Analog Comparator (ACMP)

• Programmable speed/current

• Capacitive sensing

• Analog Bus (ABUS)

• Ultra efficient Power-on Reset (POR) and Brown-Out Detector (BOD)

• Debug Interface

• 4-pin Joint Test Action Group (JTAG) interface

• 2-pin serial-wire debug (SWD) interface

Reference Manual

System Overview

silabs.com | Building a more connected world. Rev. 0.4 | 28

Page 29

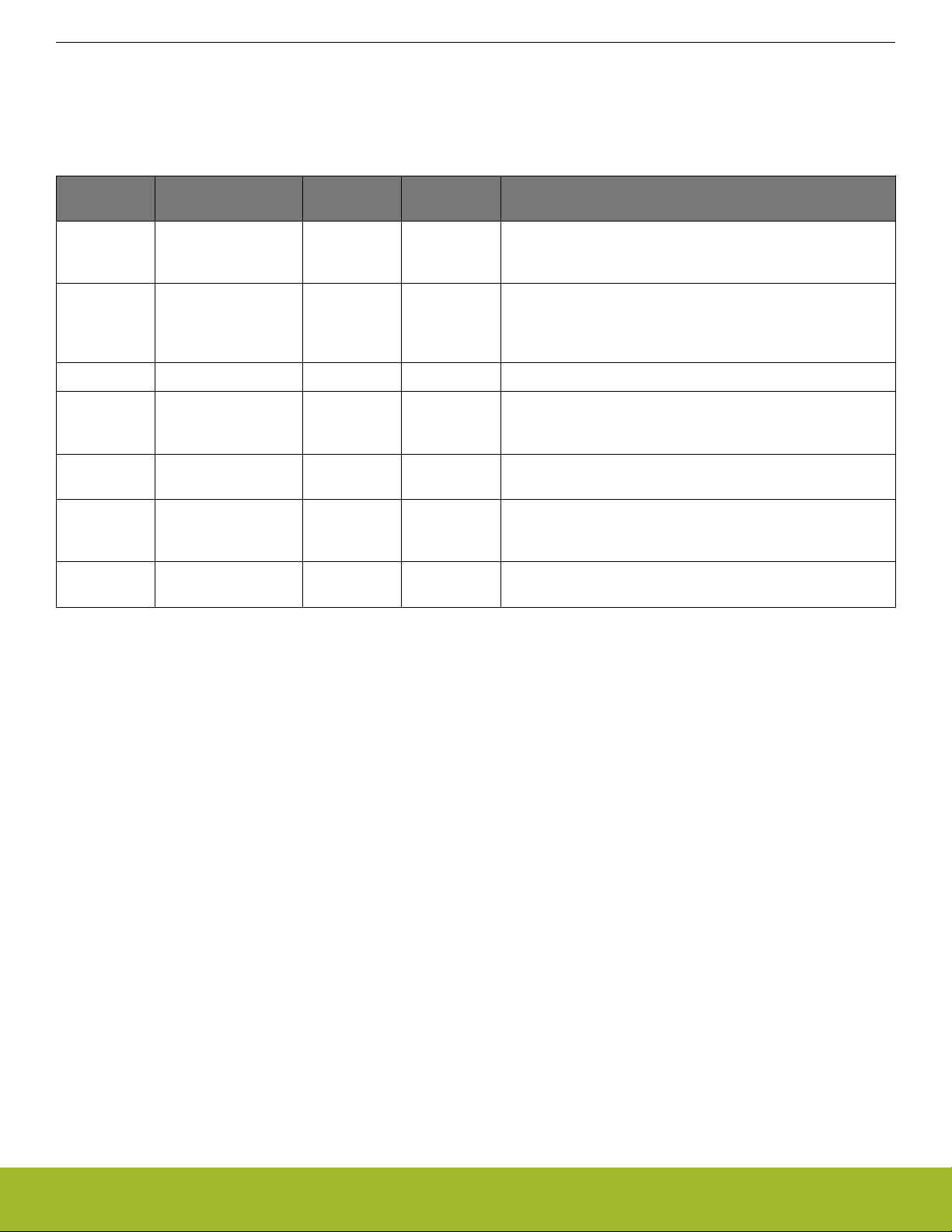

2.4 Oscillators and Clocks

EFR32xG21 has seven different oscillators integrated, as shown in Table 2.1 EFR32xG21 Oscillators on page 29.

Table 2.1. EFR32xG21 Oscillators

Reference Manual

System Overview

Oscillator Frequency Optional? External

Description

components

HFXO 38 MHz - 40 MHz No Crystal High accuracy, low jitter high frequency crystal oscillator. Tun-

able crystal loading capacitors are fully integrated. The HFXO

is required for all types of RF communication to be active.

HFRCO 1 MHz - 80 MHz Yes - Medium accuracy RC oscillator, typically used for timing dur-

ing startup of the HFXO and as a clock source as long as no

RF communication is active. In EM0/1 energy modes, the

HFRCO can be used in conjunction with the DPLL.

FSRCO 20 MHz No - Fast startup RC oscillator.

HFRCOEM23 1 MHz - 40 MHz Yes - Medium accuracy RC oscillator available in EM2 and EM3,

typically used as a clock source for the Analog to Digital Converter or Debug Trace.

LFRCO 32.768 kHz Yes - Medium accuracy frequency reference typically used for medi-

um accuracy RTCC timing.

LFXO 32.768 kHz Yes Crystal High accuracy frequency reference typically used for high ac-

curacy RTCC timing. Tunable crystal loading capacitors are

fully integrated.

ULFRCO 1000 Hz No - Ultra low frequency oscillator typically used for the watchdog

timer.

The RC oscillators can be calibrated against either of the crystal oscillators in order to compensate for temperature and voltage supply

variations. Hardware support is included to measure the frequency of various oscillators against each other.

Oscillator and clock management is available through the Clock Management Unit (CMU), see section 8. CMU - Clock Management

Unit for details.

2.5 RF Frequency Synthesizer