Page 1

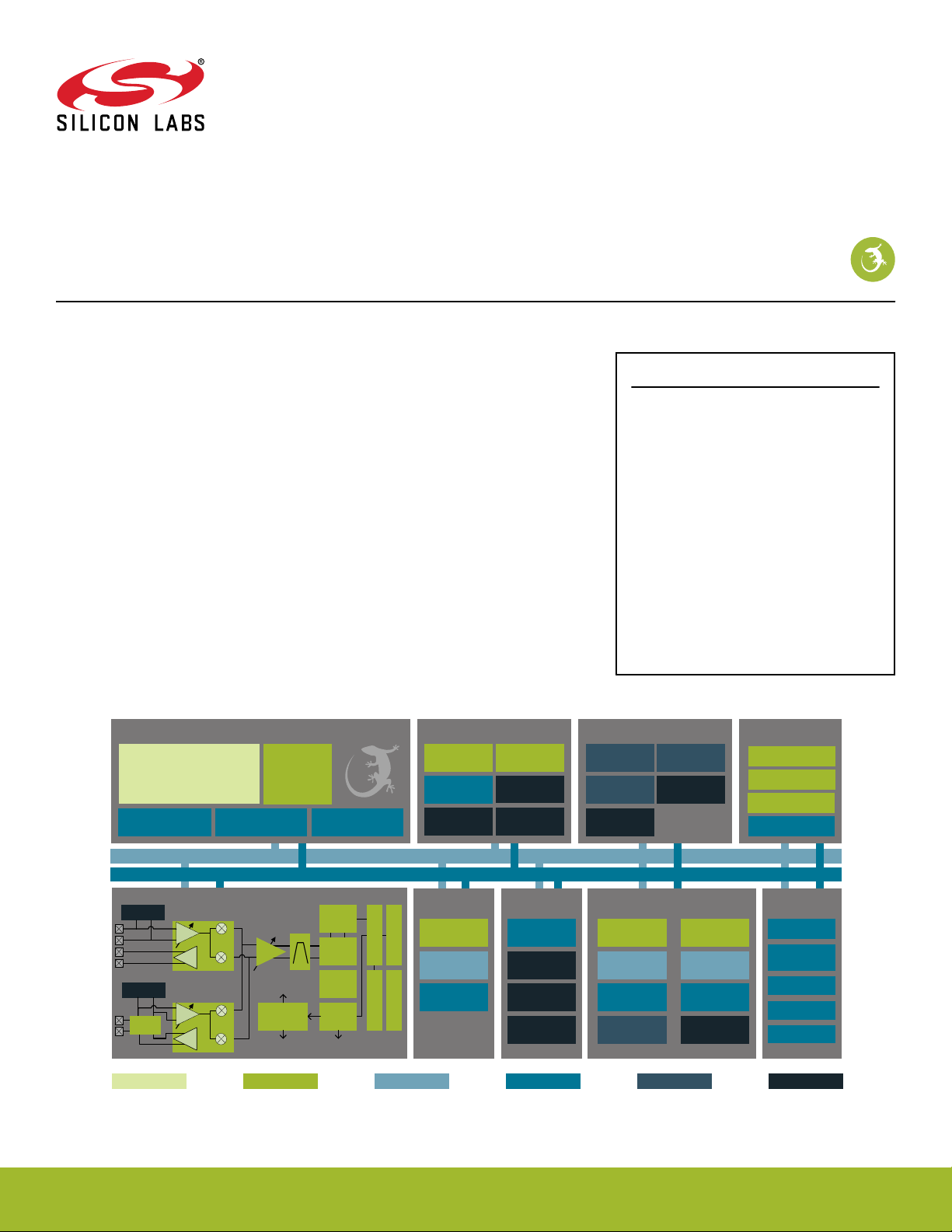

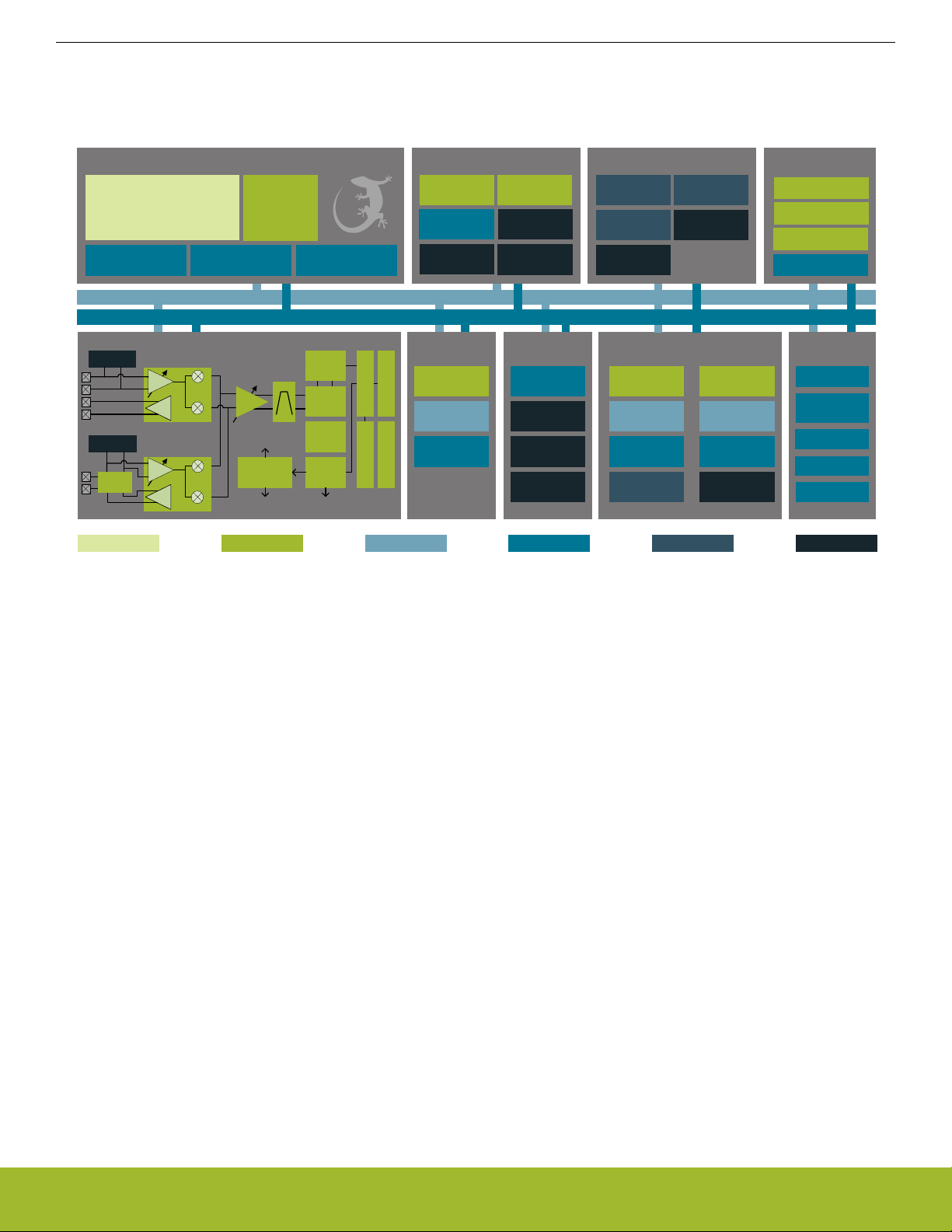

EFR32xG14 Wireless Gecko

Reference Manual

The Wireless Gecko portfolio of SoCs (EFR32) includes Mighty

Gecko (EFR32MG14), Blue Gecko (EFR32BG14), and Flex

Gecko (EFR32FG14) families. With support for Zigbee®, Thread,

Bluetooth Low Energy (BLE) and proprietary protocols, the Wireless Gecko portfolio is ideal for enabling energy-friendly wireless

networking for IoT devices.

The single-die solution provides industry-leading energy efficiency, ultra-fast wakeup

times, a scalable high-power amplifier, an integrated balun and no-compromise MCU

features.

Core / Memory

TM

ARM Cortex

with DSP extensions, FPU and MPU

Debug Interface RAM Memory LDMA Controller

M4 processor

Flash Program

Memory

Clock Management

H-F Crystal

Oscillator

Auxiliary H-F RC

Oscillator

L-F Crystal

Oscillator

H-F

RC Oscillator

L-F

RC Oscillator

Ultra L-F RC

Oscillator

KEY FEATURES

• 32-bit ARM® Cortex-M4 core with 40 MHz

maximum operating frequency

• Scalable Memory and Radio configuration

options available in several footprint

compatible QFN packages

• 12-channel Peripheral Reflex System

enabling autonomous interaction of MCU

peripherals

• Autonomous Hardware Crypto Accelerator

and True Random Number Generator

• Integrated balun for 2.4 GHz and

integrated PA with up to 19 dBm transmit

power for 2.4 GHz and 20 dBm transmit

power for Sub-GHz radios

• Integrated DC-DC with RF noise mitigation

Energy Management

Voltage

Regulator

DC-DC

Converter

Brown-Out

Detector

Voltage Monitor

Power-On Reset

Other

CRYPTO

CRC

True Random

Number Generator

SMU

32-bit bus

Peripheral Reflex System

RFSENSE

RFSENSE

Lowest power mode with peripheral operational:

BALUN

Sub GHz

LNA

RF Frontend

PA

2.4 GHz

LNA

RF Frontend

PA

I

Q

I

Q

PGA

To Sub GHz

receive I/Q

mixers and PA

Frequency

Synthesizer

To 2.4 GHz receive

I/Q mixers and PA

Radio Transceiver

DEMOD

IFADC

AGC

MOD

To Sub GHz

and 2.4 GHz PA

FRC

CRC

BUFC

RAC

Serial

Interfaces

USART

Low Energy

TM

UART

2

I

C

I/O Ports Analog I/F

External

Interrupts

General

Purpose I/O

Pin Reset

Pin Wakeup

EM3—StopEM2—Deep SleepEM1—Sleep EM4—Hibernate EM4—ShutoffEM0—Active

Timers and Triggers

Timer/Counter

Low Energy

Timer

Pulse Counter Watchdog Timer

Real Time

Counter and

Calendar

Protocol Timer

Low Energy

Sensor Interface

Cryotimer

ADC

Analog

Comparator

IDAC

VDAC

Op-Amp

silabs.com | Building a more connected world. Rev. 1.1

Page 2

Table of Contents

1. About This Document ........................... 26

1.1 Introduction...............................26

1.2 Conventions ..............................26

1.3 Related Documentation ..........................27

2. System Overview ............................. 28

2.1 Introduction...............................28

2.2 Block Diagrams .............................29

2.3 MCU Features Overview ..........................30

2.4 Oscillators and Clocks ...........................32

2.5 RF Frequency Synthesizer .........................32

2.6 Modulation Modes ............................32

2.7 Transmit Mode .............................33

2.8 Receive Mode ..............................33

2.9 Data Buffering ..............................33

2.10 Unbuffered Data Transfer .........................33

2.11 Frame Format Support ..........................33

2.12 Hardware CRC Support ..........................34

2.13 Convolutional Encoding / Decoding ......................34

2.14 Binary Block Encoding / Decoding ......................34

2.15 Data Encryption and Authentication ......................35

2.16 Timers ................................36

2.17 RF Test Modes .............................36

3. System Processor ............................ 37

3.1 Introduction...............................37

3.2 Features................................38

3.3 Functional Description ...........................38

3.3.1 Interrupt Operation ..........................39

3.3.2 Interrupt Request Lines (IRQ) ......................40

4. Memory and Bus System .......................... 41

4.1 Introduction...............................42

4.2 Functional Description ...........................43

4.2.1 Peripheral Non-Word Access Behavior ...................45

4.2.2 Bit-banding .............................45

4.2.3 Peripheral Bit Set and Clear .......................46

4.2.4 Peripherals .............................47

4.2.5 Bus Matrix .............................48

4.3 Access to Low Energy Peripherals (Asynchronous Registers) ..............51

silabs.com

| Building a more connected world. Rev. 1.1 | 2

Page 3

4.3.1 Writing ..............................52

4.3.2 Reading ..............................54

4.3.3 FREEZE Register ..........................54

4.4 Flash .................................54

4.5 SRAM ................................55

4.6 DI Page Entry Map ............................56

4.7 DI Page Entry Description ..........................58

4.7.1 CAL - CRC of DI-page and calibration temperature ...............58

4.7.2 EXTINFO - External Component description .................59

4.7.3 EUI48L - EUI48 OUI and Unique identifier ..................60

4.7.4 EUI48H - OUI ...........................60

4.7.5 CUSTOMINFO - Custom information ...................60

4.7.6 MEMINFO - Flash page size and misc. chip information .............61

4.7.7 UNIQUEL - Low 32 bits of device unique number ...............62

4.7.8 UNIQUEH - High 32 bits of device unique number ...............62

4.7.9 MSIZE - Flash and SRAM Memory size in kB .................62

4.7.10 PART - Part description ........................63

4.7.11 DEVINFOREV - Device information page revision ...............65

4.7.12 EMUTEMP - EMU Temperature Calibration Information .............65

4.7.13 ADC0CAL0 - ADC0 calibration register 0 ..................66

4.7.14 ADC0CAL1 - ADC0 calibration register 1 ..................67

4.7.15 ADC0CAL2 - ADC0 calibration register 2 ..................68

4.7.16 ADC0CAL3 - ADC0 calibration register 3 ..................68

4.7.17 HFRCOCAL0 - HFRCO Calibration Register (4 MHz) ..............69

4.7.18 HFRCOCAL3 - HFRCO Calibration Register (7 MHz) ..............70

4.7.19 HFRCOCAL6 - HFRCO Calibration Register (13 MHz) .............71

4.7.20 HFRCOCAL7 - HFRCO Calibration Register (16 MHz) .............72

4.7.21 HFRCOCAL8 - HFRCO Calibration Register (19 MHz) .............73

4.7.22 HFRCOCAL10 - HFRCO Calibration Register (26 MHz) .............74

4.7.23 HFRCOCAL11 - HFRCO Calibration Register (32 MHz) .............75

4.7.24 HFRCOCAL12 - HFRCO Calibration Register (38 MHz) .............76

4.7.25 AUXHFRCOCAL0 - AUXHFRCO Calibration Register (4 MHz) ..........77

4.7.26 AUXHFRCOCAL3 - AUXHFRCO Calibration Register (7 MHz) ..........78

4.7.27 AUXHFRCOCAL6 - AUXHFRCO Calibration Register (13 MHz) ..........79

4.7.28 AUXHFRCOCAL7 - AUXHFRCO Calibration Register (16 MHz) ..........80

4.7.29 AUXHFRCOCAL8 - AUXHFRCO Calibration Register (19 MHz) ..........81

4.7.30 AUXHFRCOCAL10 - AUXHFRCO Calibration Register (26 MHz) .........82

4.7.31 AUXHFRCOCAL11 - AUXHFRCO Calibration Register (32 MHz) ..........83

4.7.32 AUXHFRCOCAL12 - AUXHFRCO Calibration Register (38 MHz) .........84

4.7.33 VMONCAL0 - VMON Calibration Register 0 .................85

4.7.34 VMONCAL1 - VMON Calibration Register 1 .................86

4.7.35 VMONCAL2 - VMON Calibration Register 2 .................87

4.7.36 IDAC0CAL0 - IDAC0 Calibration Register 0 .................88

4.7.37 IDAC0CAL1 - IDAC0 Calibration Register 1 .................89

4.7.38 DCDCLNVCTRL0 - DCDC Low-noise VREF Trim Register 0 ...........89

4.7.39 DCDCLPVCTRL0 - DCDC Low-power VREF Trim Register 0 ...........90

4.7.40 DCDCLPVCTRL1 - DCDC Low-power VREF Trim Register 1 ...........91

silabs.com

| Building a more connected world. Rev. 1.1 | 3

Page 4

4.7.41 DCDCLPVCTRL2 - DCDC Low-power VREF Trim Register 2 ...........92

4.7.42 DCDCLPVCTRL3 - DCDC Low-power VREF Trim Register 3 ...........93

4.7.43 DCDCLPCMPHYSSEL0 - DCDC LPCMPHYSSEL Trim Register 0 .........93

4.7.44 DCDCLPCMPHYSSEL1 - DCDC LPCMPHYSSEL Trim Register 1 .........94

4.7.45 VDAC0MAINCAL - VDAC0 Cals for Main Path ................95

4.7.46 VDAC0ALTCAL - VDAC0 Cals for Alternate Path ...............96

4.7.47 VDAC0CH1CAL - VDAC0 CH1 Error Cal ..................97

4.7.48 OPA0CAL0 - OPA0 Calibration Register for DRIVESTRENGTH 0, INCBW=1 .....98

4.7.49 OPA0CAL1 - OPA0 Calibration Register for DRIVESTRENGTH 1, INCBW=1 .....99

4.7.50 OPA0CAL2 - OPA0 Calibration Register for DRIVESTRENGTH 2, INCBW=1 ....100

4.7.51 OPA0CAL3 - OPA0 Calibration Register for DRIVESTRENGTH 3, INCBW=1 ....101

4.7.52 OPA1CAL0 - OPA1 Calibration Register for DRIVESTRENGTH 0, INCBW=1 ....102

4.7.53 OPA1CAL1 - OPA1 Calibration Register for DRIVESTRENGTH 1, INCBW=1 ....103

4.7.54 OPA1CAL2 - OPA1 Calibration Register for DRIVESTRENGTH 2, INCBW=1 ....104

4.7.55 OPA1CAL3 - OPA1 Calibration Register for DRIVESTRENGTH 3, INCBW=1 ....105

4.7.56 OPA0CAL4 - OPA0 Calibration Register for DRIVESTRENGTH 0, INCBW=0 ....106

4.7.57 OPA0CAL5 - OPA0 Calibration Register for DRIVESTRENGTH 1, INCBW=0 ....107

4.7.58 OPA0CAL6 - OPA0 Calibration Register for DRIVESTRENGTH 2, INCBW=0 ....108

4.7.59 OPA0CAL7 - OPA0 Calibration Register for DRIVESTRENGTH 3, INCBW=0 ....109

4.7.60 OPA1CAL4 - OPA1 Calibration Register for DRIVESTRENGTH 0, INCBW=0 ....110

4.7.61 OPA1CAL5 - OPA1 Calibration Register for DRIVESTRENGTH 1, INCBW=0 ....111

4.7.62 OPA1CAL6 - OPA1 Calibration Register for DRIVESTRENGTH 2, INCBW=0 ....112

4.7.63 OPA1CAL7 - OPA1 Calibration Register for DRIVESTRENGTH 3, INCBW=0 ....113

5. Radio Transceiver ............................114

5.1 Introduction..............................115

6. DBG - Debug Interface ...........................116

6.1 Introduction..............................116

6.2 Features...............................116

6.3 Functional Description ..........................116

6.3.1 Debug Pins............................117

6.3.2 Debug and EM2 Deep Sleep/EM3 Stop ..................117

6.3.3 Authentication Access Point ......................117

6.3.4 Debug Lock ...........................118

6.3.5 AAP Lock ............................118

6.3.6 Debugger Reads of Actionable Registers .................119

6.3.7 Debug Recovery ..........................119

6.4 Register Map .............................119

6.5 Register Description ...........................120

6.5.1 AAP_CMD - Command Register ....................120

6.5.2 AAP_CMDKEY - Command Key Register .................120

6.5.3 AAP_STATUS - Status Register ....................121

6.5.4 AAP_CTRL - Control Register .....................121

6.5.5 AAP_CRCCMD - CRC Command Register ................122

6.5.6 AAP_CRCSTATUS - CRC Status Register .................122

6.5.7 AAP_CRCADDR - CRC Address Register .................123

6.5.8 AAP_CRCRESULT - CRC Result Register .................123

silabs.com

| Building a more connected world. Rev. 1.1 | 4

Page 5

6.5.9 AAP_IDR - AAP Identification Register ..................124

7. MSC - Memory System Controller ......................125

7.1 Introduction..............................125

7.2 Features...............................126

7.3 Functional Description ..........................127

7.3.1 User Data (UD) Page Description ....................127

7.3.2 Lock Bits (LB) Page Description.....................128

7.3.3 Device Information (DI) Page .....................128

7.3.4 Bootloader ............................129

7.3.5 Device Revision ..........................129

7.3.6 Post-reset Behavior .........................129

7.3.7 Flash Startup ...........................130

7.3.8 Wait-states ............................130

7.3.9 Suppressed Conditional Branch Target Prefetch (SCBTP) ............131

7.3.10 Cortex-M4 If-Then Block Folding ....................131

7.3.11 Instruction Cache .........................132

7.3.12 Low Voltage Flash Read .......................133

7.3.13 Erase and Write Operations......................133

7.4 Register Map .............................134

7.5 Register Description ...........................135

7.5.1 MSC_CTRL - Memory System Control Register ...............135

7.5.2 MSC_READCTRL - Read Control Register ................136

7.5.3 MSC_WRITECTRL - Write Control Register ................137

7.5.4 MSC_WRITECMD - Write Command Register ...............138

7.5.5 MSC_ADDRB - Page Erase/Write Address Buffer ..............139

7.5.6 MSC_WDATA - Write Data Register ...................139

7.5.7 MSC_STATUS - Status Register ....................140

7.5.8 MSC_IF - Interrupt Flag Register ....................141

7.5.9 MSC_IFS - Interrupt Flag Set Register ..................142

7.5.10 MSC_IFC - Interrupt Flag Clear Register .................143

7.5.11 MSC_IEN - Interrupt Enable Register ..................144

7.5.12 MSC_LOCK - Configuration Lock Register ................145

7.5.13 MSC_CACHECMD - Flash Cache Command Register ............146

7.5.14 MSC_CACHEHITS - Cache Hits Performance Counter ............146

7.5.15 MSC_CACHEMISSES - Cache Misses Performance Counter ..........147

7.5.16 MSC_MASSLOCK - Mass Erase Lock Register ..............148

7.5.17 MSC_STARTUP - Startup Control ...................149

7.5.18 MSC_CMD - Command Register ...................150

7.5.19 MSC_BOOTLOADERCTRL - Bootloader Read and Write Enable, Write Once Register . 150

7.5.20 MSC_AAPUNLOCKCMD - Software Unlock AAP Command Register .......151

7.5.21 MSC_CACHECONFIG0 - Cache Configuration Register 0 ...........152

8. LDMA - Linked DMA Controller........................153

8.1 Introduction..............................153

8.1.1 Features ............................154

8.2 Block Diagram.............................155

silabs.com

| Building a more connected world. Rev. 1.1 | 5

Page 6

8.3 Functional Description ..........................156

8.3.1 Channel Descriptor .........................156

8.3.2 Channel Configuration ........................161

8.3.3 Channel Select Configuration .....................161

8.3.4 Starting a Transfer .........................161

8.3.5 Managing Transfer Errors .......................162

8.3.6 Arbitration ............................162

8.3.7 Channel Descriptor Data Structure ....................165

8.3.8 Interaction With the EMU .......................167

8.3.9 Interrupts ............................168

8.3.10 Debugging ...........................168

8.4 Examples ..............................168

8.4.1 Single Direct Register DMA Transfer ...................168

8.4.2 Descriptor Linked List ........................169

8.4.3 Single Descriptor Looped Transfer ....................171

8.4.4 Descriptor List With Looping ......................172

8.4.5 Simple Inter-Channel Synchronization...................173

8.4.6 2D Copy.............................175

8.4.7 Ping-Pong ............................177

8.4.8 Scatter-Gather ..........................178

8.5 Register Map .............................179

8.6 Register Description ...........................180

8.6.1 LDMA_CTRL - DMA Control Register ..................180

8.6.2 LDMA_STATUS - DMA Status Register ..................181

8.6.3 LDMA_SYNC - DMA Synchronization Trigger Register (Single-Cycle RMW) .....182

8.6.4 LDMA_CHEN - DMA Channel Enable Register (Single-Cycle RMW) ........182

8.6.5 LDMA_CHBUSY - DMA Channel Busy Register ...............183

8.6.6 LDMA_CHDONE - DMA Channel Linking Done Register (Single-Cycle RMW) .....183

8.6.7 LDMA_DBGHALT - DMA Channel Debug Halt Register ............184

8.6.8 LDMA_SWREQ - DMA Channel Software Transfer Request Register ........184

8.6.9 LDMA_REQDIS - DMA Channel Request Disable Register ...........185

8.6.10 LDMA_REQPEND - DMA Channel Requests Pending Register .........185

8.6.11 LDMA_LINKLOAD - DMA Channel Link Load Register ............186

8.6.12 LDMA_REQCLEAR - DMA Channel Request Clear Register ..........186

8.6.13 LDMA_IF - Interrupt Flag Register ...................187

8.6.14 LDMA_IFS - Interrupt Flag Set Register .................187

8.6.15 LDMA_IFC - Interrupt Flag Clear Register ................188

8.6.16 LDMA_IEN - Interrupt Enable Register .................188

8.6.17 LDMA_CHx_REQSEL - Channel Peripheral Request Select Register .......189

8.6.18 LDMA_CHx_CFG - Channel Configuration Register .............192

8.6.19 LDMA_CHx_LOOP - Channel Loop Counter Register ............193

8.6.20 LDMA_CHx_CTRL - Channel Descriptor Control Word Register .........194

8.6.21 LDMA_CHx_SRC - Channel Descriptor Source Data Address Register ......197

8.6.22 LDMA_CHx_DST - Channel Descriptor Destination Data Address Register .....197

8.6.23 LDMA_CHx_LINK - Channel Descriptor Link Structure Address Register ......198

9. RMU - Reset Management Unit ........................199

9.1 Introduction..............................199

silabs.com

| Building a more connected world. Rev. 1.1 | 6

Page 7

9.2 Features...............................199

9.3 Functional Description ..........................200

9.3.1 Reset Levels ...........................201

9.3.2 RMU_RSTCAUSE Register ......................202

9.3.3 Power-On Reset (POR) .......................203

9.3.4 Brown-Out Detector (BOD) ......................203

9.3.5 RESETn Pin Reset .........................204

9.3.6 Watchdog Reset ..........................204

9.3.7 Lockup Reset ...........................204

9.3.8 System Reset Request ........................204

9.3.9 Reset State ...........................204

9.3.10 Register Reset Signals .......................204

9.4 Register Map .............................206

9.5 Register Description ...........................207

9.5.1 RMU_CTRL - Control Register .....................207

9.5.2 RMU_RSTCAUSE - Reset Cause Register ................209

9.5.3 RMU_CMD - Command Register ....................210

9.5.4 RMU_RST - Reset Control Register ...................210

9.5.5 RMU_LOCK - Configuration Lock Register .................211

10. EMU - Energy Management Unit .......................212

10.1 Introduction .............................212

10.2 Features ..............................213

10.3 Functional Description .........................214

10.3.1 Energy Modes ..........................215

10.3.2 Entering Low Energy Modes .....................219

10.3.3 Exiting a Low Energy Mode .....................221

10.3.4 Power Configurations ........................222

10.3.5 DC-to-DC Interface ........................226

10.3.6 Analog Peripheral Power Selection ...................228

10.3.7 Digital LDO Power Selection .....................229

10.3.8 IOVDD Connection.........................229

10.3.9 Voltage Scaling ..........................230

10.3.10 EM23 Peripheral Retention Disable...................232

10.3.11 Brown Out Detector (BOD)......................232

10.3.12 Voltage Monitor (VMON) ......................233

10.3.13 Powering Off SRAM Blocks .....................234

10.3.14 Temperature Sensor ........................234

10.3.15 Registers latched in EM4 ......................235

10.3.16 Register Resets .........................235

10.4 Register Map.............................236

10.5 Register Description ..........................238

10.5.1 EMU_CTRL - Control Register ....................238

10.5.2 EMU_STATUS - Status Register ....................240

10.5.3 EMU_LOCK - Configuration Lock Register ................242

10.5.4 EMU_RAM0CTRL - Memory Control Register ...............242

silabs.com

| Building a more connected world. Rev. 1.1 | 7

Page 8

10.5.5 EMU_CMD - Command Register ...................243

10.5.6 EMU_EM4CTRL - EM4 Control Register .................244

10.5.7 EMU_TEMPLIMITS - Temperature Limits for Interrupt Generation ........245

10.5.8 EMU_TEMP - Value of Last Temperature Measurement ............245

10.5.9 EMU_IF - Interrupt Flag Register ...................246

10.5.10 EMU_IFS - Interrupt Flag Set Register .................248

10.5.11 EMU_IFC - Interrupt Flag Clear Register ................250

10.5.12 EMU_IEN - Interrupt Enable Register .................252

10.5.13 EMU_PWRLOCK - Regulator and Supply Lock Register ...........254

10.5.14 EMU_PWRCTRL - Power Control Register ................255

10.5.15 EMU_DCDCCTRL - DCDC Control ..................256

10.5.16 EMU_DCDCMISCCTRL - DCDC Miscellaneous Control Register ........257

10.5.17 EMU_DCDCZDETCTRL - DCDC Power Train NFET Zero Current Detector Control Register

................................259

10.5.18 EMU_DCDCCLIMCTRL - DCDC Power Train PFET Current Limiter Control Register . 260

10.5.19 EMU_DCDCLNCOMPCTRL - DCDC Low Noise Compensator Control Register ...261

10.5.20 EMU_DCDCLNVCTRL - DCDC Low Noise Voltage Register ..........262

10.5.21 EMU_DCDCLPVCTRL - DCDC Low Power Voltage Register .........263

10.5.22 EMU_DCDCLPCTRL - DCDC Low Power Control Register ..........264

10.5.23 EMU_DCDCLNFREQCTRL - DCDC Low Noise Controller Frequency Control ....265

10.5.24 EMU_DCDCSYNC - DCDC Read Status Register .............265

10.5.25 EMU_VMONAVDDCTRL - VMON AVDD Channel Control ..........266

10.5.26 EMU_VMONALTAVDDCTRL - Alternate VMON AVDD Channel Control ......267

10.5.27 EMU_VMONDVDDCTRL - VMON DVDD Channel Control ..........268

10.5.28 EMU_VMONIO0CTRL - VMON IOVDD0 Channel Control ...........269

10.5.29 EMU_RAM1CTRL - Memory Control Register ...............270

10.5.30 EMU_RAM2CTRL - Memory Control Register ...............271

10.5.31 EMU_DCDCLPEM01CFG - Configuration Bits for Low Power Mode to Be Applied During

EM01, This Field is Only Relevant If LP Mode is Used in EM01 ...........272

10.5.32 EMU_EM23PERNORETAINCMD - Clears Corresponding Bits in EM23PERNORETAINSTA-

TUS Unlocking Access to Peripheral ....................273

10.5.33 EMU_EM23PERNORETAINSTATUS - Status Indicating If Peripherals Were Powered Down

in EM23, Subsequently Locking Access to It .................275

10.5.34 EMU_EM23PERNORETAINCTRL - When Set Corresponding Peripherals May Get Powered

Down in EM23 ...........................277

11. CMU - Clock Management Unit .......................279

11.1 Introduction .............................279

11.2 Features ..............................279

11.3 Functional Description..........................280

11.3.1 System Clocks ..........................281

11.3.2 Oscillators............................284

11.3.3 Configuration for Operating Frequencies .................302

11.3.4 Energy Modes ..........................303

11.3.5 Clock Output on a Pin ........................304

11.3.6 Clock Input From a Pin .......................304

11.3.7 Clock Output on PRS ........................304

11.3.8 Error Handling ..........................304

silabs.com

| Building a more connected world. Rev. 1.1 | 8

Page 9

11.3.9 Interrupts ............................304

11.3.10 Wake-up ............................305

11.3.11 Protection ...........................305

11.4 Register Map .............................306

11.5 Register Description ..........................308

11.5.1 CMU_CTRL - CMU Control Register ..................308

11.5.2 CMU_HFRCOCTRL - HFRCO Control Register ..............310

11.5.3 CMU_AUXHFRCOCTRL - AUXHFRCO Control Register ...........312

11.5.4 CMU_LFRCOCTRL - LFRCO Control Register ...............313

11.5.5 CMU_HFXOCTRL - HFXO Control Register ................315

11.5.6 CMU_HFXOSTARTUPCTRL - HFXO Startup Control .............317

11.5.7 CMU_HFXOSTEADYSTATECTRL - HFXO Steady State Control .........318

11.5.8 CMU_HFXOTIMEOUTCTRL - HFXO Timeout Control ............319

11.5.9 CMU_LFXOCTRL - LFXO Control Register ................322

11.5.10 CMU_CALCTRL - Calibration Control Register ..............324

11.5.11 CMU_CALCNT - Calibration Counter Register ...............326

11.5.12 CMU_OSCENCMD - Oscillator Enable/Disable Command Register .......327

11.5.13 CMU_CMD - Command Register ...................328

11.5.14 CMU_DBGCLKSEL - Debug Trace Clock Select ..............329

11.5.15 CMU_HFCLKSEL - High Frequency Clock Select Command Register ......329

11.5.16 CMU_LFACLKSEL - Low Frequency A Clock Select Register .........330

11.5.17 CMU_LFBCLKSEL - Low Frequency B Clock Select Register .........330

11.5.18 CMU_LFECLKSEL - Low Frequency E Clock Select Register .........331

11.5.19 CMU_STATUS - Status Register ...................332

11.5.20 CMU_HFCLKSTATUS - HFCLK Status Register ..............334

11.5.21 CMU_HFXOTRIMSTATUS - HFXO Trim Status ..............335

11.5.22 CMU_IF - Interrupt Flag Register ...................336

11.5.23 CMU_IFS - Interrupt Flag Set Register .................338

11.5.24 CMU_IFC - Interrupt Flag Clear Register ................340

11.5.25 CMU_IEN - Interrupt Enable Register .................342

11.5.26 CMU_HFBUSCLKEN0 - High Frequency Bus Clock Enable Register 0 ......344

11.5.27 CMU_HFPERCLKEN0 - High Frequency Peripheral Clock Enable Register 0 ....345

11.5.28 CMU_HFRADIOALTCLKEN0 - High Frequency Alternate Radio Peripheral Clock Enable

Register 0 .............................346

11.5.29 CMU_LFACLKEN0 - Low Frequency a Clock Enable Register 0 (Async Reg) ....346

11.5.30 CMU_LFBCLKEN0 - Low Frequency B Clock Enable Register 0 (Async Reg) ....347

11.5.31 CMU_LFECLKEN0 - Low Frequency E Clock Enable Register 0 (Async Reg) ....347

11.5.32 CMU_HFPRESC - High Frequency Clock Prescaler Register .........348

11.5.33 CMU_HFCOREPRESC - High Frequency Core Clock Prescaler Register .....349

11.5.34 CMU_HFPERPRESC - High Frequency Peripheral Clock Prescaler Register ....349

11.5.35 CMU_HFRADIOPRESC - High Frequency Radio Peripheral Clock Prescaler Register . 350

11.5.36 CMU_HFEXPPRESC - High Frequency Export Clock Prescaler Register .....350

11.5.37 CMU_LFAPRESC0 - Low Frequency a Prescaler Register 0 (Async Reg) .....351

11.5.38 CMU_LFBPRESC0 - Low Frequency B Prescaler Register 0 (Async Reg) .....352

11.5.39 CMU_LFEPRESC0 - Low Frequency E Prescaler Register 0 (Async Reg) .....353

11.5.40 CMU_HFRADIOALTPRESC - High Frequency Alternate Radio Peripheral Clock Prescaler

Register .............................353

11.5.41 CMU_SYNCBUSY - Synchronization Busy Register .............354

silabs.com

| Building a more connected world. Rev. 1.1 | 9

Page 10

11.5.42 CMU_FREEZE - Freeze Register ...................357

11.5.43 CMU_PCNTCTRL - PCNT Control Register ...............358

11.5.44 CMU_ADCCTRL - ADC Control Register ................359

11.5.45 CMU_ROUTEPEN - I/O Routing Pin Enable Register ............360

11.5.46 CMU_ROUTELOC0 - I/O Routing Location Register ............361

11.5.47 CMU_ROUTELOC1 - I/O Routing Location Register ............362

11.5.48 CMU_LOCK - Configuration Lock Register ................363

12. SMU - Security Management Unit ......................364

12.1 Introduction .............................364

12.2 Features ..............................364

12.3 Functional Description .........................365

12.3.1 PPU - Peripheral Protection Unit ....................365

12.3.2 Programming Model ........................366

12.4 Register Map.............................367

12.5 Register Description ..........................368

12.5.1 SMU_IF - Interrupt Flag Register ...................368

12.5.2 SMU_IFS - Interrupt Flag Set Register ..................368

12.5.3 SMU_IFC - Interrupt Flag Clear Register .................369

12.5.4 SMU_IEN - Interrupt Enable Register ..................369

12.5.5 SMU_PPUCTRL - PPU Control Register .................370

12.5.6 SMU_PPUPATD0 - PPU Privilege Access Type Descriptor 0 ..........371

12.5.7 SMU_PPUPATD1 - PPU Privilege Access Type Descriptor 1 ..........373

12.5.8 SMU_PPUFS - PPU Fault Status ...................374

13. RTCC - Real Time Counter and Calendar ...................376

13.1 Introduction .............................376

13.2 Features ..............................376

13.3 Functional Description .........................377

13.3.1 Counter ............................378

13.3.2 Capture/Compare Channels .....................382

13.3.3 Interrupts and PRS Output ......................384

13.3.4 Energy Mode Availability .......................385

13.3.5 Register Lock ..........................385

13.3.6 Oscillator Failure Detection ......................385

13.3.7 Retention Registers ........................385

13.3.8 Debug Session ..........................385

13.4 Register Map.............................386

13.5 Register Description ..........................387

13.5.1 RTCC_CTRL - Control Register (Async Reg) ...............387

13.5.2 RTCC_PRECNT - Pre-Counter Value Register (Async Reg) ..........389

13.5.3 RTCC_CNT - Counter Value Register (Async Reg) .............389

13.5.4 RTCC_COMBCNT - Combined Pre-Counter and Counter Value Register ......390

13.5.5 RTCC_TIME - Time of Day Register (Async Reg) ..............391

13.5.6 RTCC_DATE - Date Register (Async Reg) ................392

13.5.7 RTCC_IF - RTCC Interrupt Flags ...................393

silabs.com

| Building a more connected world. Rev. 1.1 | 10

Page 11

13.5.8 RTCC_IFS - Interrupt Flag Set Register .................394

13.5.9 RTCC_IFC - Interrupt Flag Clear Register ................395

13.5.10 RTCC_IEN - Interrupt Enable Register .................396

13.5.11 RTCC_STATUS - Status Register ...................397

13.5.12 RTCC_CMD - Command Register ...................397

13.5.13 RTCC_SYNCBUSY - Synchronization Busy Register ............397

13.5.14 RTCC_POWERDOWN - Retention RAM Power-down Register (Async Reg) ....398

13.5.15 RTCC_LOCK - Configuration Lock Register (Async Reg) ...........398

13.5.16 RTCC_EM4WUEN - Wake Up Enable .................399

13.5.17 RTCC_CCx_CTRL - CC Channel Control Register (Async Reg) ........400

13.5.18 RTCC_CCx_CCV - Capture/Compare Value Register (Async Reg) ........402

13.5.19 RTCC_CCx_TIME - Capture/Compare Time Register (Async Reg) ........403

13.5.20 RTCC_CCx_DATE - Capture/Compare Date Register (Async Reg) .......404

13.5.21 RTCC_RETx_REG - Retention Register .................404

14. WDOG - Watchdog Timer .........................405

14.1 Introduction .............................405

14.2 Features ..............................405

14.3 Functional Description .........................405

14.3.1 Clock Source ..........................406

14.3.2 Debug Functionality ........................406

14.3.3 Energy Mode Handling .......................406

14.3.4 Register Access..........................406

14.3.5 Warning Interrupt .........................406

14.3.6 Window Interrupt .........................407

14.3.7 PRS as Watchdog Clear .......................408

14.3.8 PRS Rising Edge Monitoring .....................408

14.4 Register Map.............................409

14.5 Register Description ..........................410

14.5.1 WDOG_CTRL - Control Register (Async Reg) ...............410

14.5.2 WDOG_CMD - Command Register (Async Reg) ..............413

14.5.3 WDOG_SYNCBUSY - Synchronization Busy Register ............414

14.5.4 WDOGn_PCHx_PRSCTRL - PRS Control Register (Async Reg) .........415

14.5.5 WDOG_IF - Watchdog Interrupt Flags ..................416

14.5.6 WDOG_IFS - Interrupt Flag Set Register .................417

14.5.7 WDOG_IFC - Interrupt Flag Clear Register ................418

14.5.8 WDOG_IEN - Interrupt Enable Register .................419

15. PRS - Peripheral Reflex System .......................420

15.1 Introduction .............................420

15.2 Features ..............................420

15.3 Functional Description .........................421

15.3.1 Channel Functions .........................421

15.3.2 Producers............................422

15.3.3 Consumers ...........................423

15.3.4 Event on PRS ..........................424

15.3.5 DMA Request on PRS .......................424

silabs.com

| Building a more connected world. Rev. 1.1 | 11

Page 12

15.3.6 Example ............................425

15.4 Register Map.............................425

15.5 Register Description ..........................426

15.5.1 PRS_SWPULSE - Software Pulse Register ................426

15.5.2 PRS_SWLEVEL - Software Level Register ................427

15.5.3 PRS_ROUTEPEN - I/O Routing Pin Enable Register .............428

15.5.4 PRS_ROUTELOC0 - I/O Routing Location Register .............429

15.5.5 PRS_ROUTELOC1 - I/O Routing Location Register .............432

15.5.6 PRS_ROUTELOC2 - I/O Routing Location Register .............434

15.5.7 PRS_CTRL - Control Register ....................436

15.5.8 PRS_DMAREQ0 - DMA Request 0 Register ................437

15.5.9 PRS_DMAREQ1 - DMA Request 1 Register ................438

15.5.10 PRS_PEEK - PRS Channel Values ..................439

15.5.11 PRS_CHx_CTRL - Channel Control Register ...............440

16. PCNT - Pulse Counter ..........................446

16.1 Introduction .............................446

16.2 Features ..............................446

16.3 Functional Description .........................447

16.3.1 Pulse Counter Modes ........................447

16.3.2 Hysteresis ...........................454

16.3.3 Auxiliary Counter .........................455

16.3.4 Triggered Compare and Clear .....................456

16.3.5 Register Access..........................457

16.3.6 Clock Sources ..........................457

16.3.7 Input Filter ...........................457

16.3.8 Edge Polarity ..........................458

16.3.9 PRS and PCNTn_S0IN,PCNTn_S1IN Inputs ................458

16.3.10 Interrupts ...........................458

16.3.11 Cascading Pulse Counters......................460

16.4 Register Map.............................461

16.5 Register Description ..........................462

16.5.1 PCNTn_CTRL - Control Register (Async Reg) ...............462

16.5.2 PCNTn_CMD - Command Register (Async Reg) ..............466

16.5.3 PCNTn_STATUS - Status Register ...................466

16.5.4 PCNTn_CNT - Counter Value Register .................467

16.5.5 PCNTn_TOP - Top Value Register ...................467

16.5.6 PCNTn_TOPB - Top Value Buffer Register (Async Reg) ............468

16.5.7 PCNTn_IF - Interrupt Flag Register ...................468

16.5.8 PCNTn_IFS - Interrupt Flag Set Register .................469

16.5.9 PCNTn_IFC - Interrupt Flag Clear Register ................470

16.5.10 PCNTn_IEN - Interrupt Enable Register .................471

16.5.11 PCNTn_ROUTELOC0 - I/O Routing Location Register ............472

16.5.12 PCNTn_FREEZE - Freeze Register ..................474

16.5.13 PCNTn_SYNCBUSY - Synchronization Busy Register ............475

16.5.14 PCNTn_AUXCNT - Auxiliary Counter Value Register ............475

16.5.15 PCNTn_INPUT - PCNT Input Register .................476

silabs.com

| Building a more connected world. Rev. 1.1 | 12

Page 13

16.5.16 PCNTn_OVSCFG - Oversampling Config Register (Async Reg) ........477

17. I2C - Inter-Integrated Circuit Interface.....................478

17.1 Introduction .............................478

17.2 Features ..............................478

17.3 Functional Description .........................479

17.3.1 I2C-Bus Overview .........................480

17.3.2 Enable and Reset .........................484

17.3.3 Safely Disabling and Changing Slave Configuration..............484

17.3.4 Clock Generation .........................484

17.3.5 Arbitration............................485

17.3.6 Buffers .............................485

17.3.7 Master Operation .........................487

17.3.8 Bus States ...........................495

17.3.9 Slave Operation .........................495

17.3.10 Transfer Automation ........................499

17.3.11 Using 10-bit Addresses .......................500

17.3.12 Error Handling ..........................500

17.3.13 DMA Support ..........................502

17.3.14 Interrupts ...........................502

17.3.15 Wake-up............................502

17.4 Register Map.............................503

17.5 Register Description ..........................504

17.5.1 I2Cn_CTRL - Control Register ....................504

17.5.2 I2Cn_CMD - Command Register ...................507

17.5.3 I2Cn_STATE - State Register .....................508

17.5.4 I2Cn_STATUS - Status Register ....................509

17.5.5 I2Cn_CLKDIV - Clock Division Register .................510

17.5.6 I2Cn_SADDR - Slave Address Register .................510

17.5.7 I2Cn_SADDRMASK - Slave Address Mask Register .............511

17.5.8 I2Cn_RXDATA - Receive Buffer Data Register (Actionable Reads) ........511

17.5.9 I2Cn_RXDOUBLE - Receive Buffer Double Data Register (Actionable Reads) ....512

17.5.10 I2Cn_RXDATAP - Receive Buffer Data Peek Register ............512

17.5.11 I2Cn_RXDOUBLEP - Receive Buffer Double Data Peek Register ........513

17.5.12 I2Cn_TXDATA - Transmit Buffer Data Register ..............513

17.5.13 I2Cn_TXDOUBLE - Transmit Buffer Double Data Register ..........514

17.5.14 I2Cn_IF - Interrupt Flag Register ...................515

17.5.15 I2Cn_IFS - Interrupt Flag Set Register .................517

17.5.16 I2Cn_IFC - Interrupt Flag Clear Register ................519

17.5.17 I2Cn_IEN - Interrupt Enable Register ..................521

17.5.18 I2Cn_ROUTEPEN - I/O Routing Pin Enable Register ............522

17.5.19 I2Cn_ROUTELOC0 - I/O Routing Location Register .............523

18. USART - Universal Synchronous Asynchronous Receiver/Transmitter ........526

18.1 Introduction .............................526

18.2 Features ..............................527

18.3 Functional Description .........................528

silabs.com

| Building a more connected world. Rev. 1.1 | 13

Page 14

18.3.1 Modes of Operation ........................529

18.3.2 Asynchronous Operation.......................529

18.3.3 Synchronous Operation .......................546

18.3.4 Hardware Flow Control .......................552

18.3.5 Debug Halt ...........................552

18.3.6 PRS-triggered Transmissions .....................552

18.3.7 PRS RX Input ..........................552

18.3.8 PRS CLK Input ..........................553

18.3.9 DMA Support ..........................553

18.3.10 Timer .............................554

18.3.11 Interrupts ...........................559

18.3.12 IrDA Modulator/ Demodulator.....................560

18.4 Register Map.............................561

18.5 Register Description ..........................562

18.5.1 USARTn_CTRL - Control Register ...................562

18.5.2 USARTn_FRAME - USART Frame Format Register .............567

18.5.3 USARTn_TRIGCTRL - USART Trigger Control Register ............569

18.5.4 USARTn_CMD - Command Register ..................571

18.5.5 USARTn_STATUS - USART Status Register ...............572

18.5.6 USARTn_CLKDIV - Clock Control Register ................573

18.5.7 USARTn_RXDATAX - RX Buffer Data Extended Register (Actionable Reads) ....574

18.5.8 USARTn_RXDATA - RX Buffer Data Register (Actionable Reads) ........574

18.5.9 USARTn_RXDOUBLEX - RX Buffer Double Data Extended Register (Actionable Reads) 575

18.5.10 USARTn_RXDOUBLE - RX FIFO Double Data Register (Actionable Reads) ....576

18.5.11 USARTn_RXDATAXP - RX Buffer Data Extended Peek Register ........576

18.5.12 USARTn_RXDOUBLEXP - RX Buffer Double Data Extended Peek Register ....577

18.5.13 USARTn_TXDATAX - TX Buffer Data Extended Register ...........578

18.5.14 USARTn_TXDATA - TX Buffer Data Register ...............579

18.5.15 USARTn_TXDOUBLEX - TX Buffer Double Data Extended Register .......580

18.5.16 USARTn_TXDOUBLE - TX Buffer Double Data Register ...........581

18.5.17 USARTn_IF - Interrupt Flag Register ..................582

18.5.18 USARTn_IFS - Interrupt Flag Set Register ................584

18.5.19 USARTn_IFC - Interrupt Flag Clear Register ...............586

18.5.20 USARTn_IEN - Interrupt Enable Register ................588

18.5.21 USARTn_IRCTRL - IrDA Control Register ................590

18.5.22 USARTn_INPUT - USART Input Register ................592

18.5.23 USARTn_I2SCTRL - I2S Control Register ................594

18.5.24 USARTn_TIMING - Timing Register ..................596

18.5.25 USARTn_CTRLX - Control Register Extended ..............598

18.5.26 USARTn_TIMECMP0 - Used to Generate Interrupts and Various Delays ......599

18.5.27 USARTn_TIMECMP1 - Used to Generate Interrupts and Various Delays ......601

18.5.28 USARTn_TIMECMP2 - Used to Generate Interrupts and Various Delays ......603

18.5.29 USARTn_ROUTEPEN - I/O Routing Pin Enable Register ...........605

18.5.30 USARTn_ROUTELOC0 - I/O Routing Location Register ...........607

18.5.31 USARTn_ROUTELOC1 - I/O Routing Location Register ...........612

19. LEUART - Low Energy Universal Asynchronous Receiver/Transmitter ........615

19.1 Introduction .............................615

silabs.com

| Building a more connected world. Rev. 1.1 | 14

Page 15

19.2 Features ..............................616

19.3 Functional Description .........................617

19.3.1 Frame Format ..........................618

19.3.2 Clock Source ..........................618

19.3.3 Clock Generation .........................619

19.3.4 Data Transmission .........................619

19.3.5 Data Reception ..........................621

19.3.6 Loopback ............................624

19.3.7 Half Duplex Communication .....................624

19.3.8 Transmission Delay ........................625

19.3.9 PRS RX Input ..........................626

19.3.10 DMA Support ..........................626

19.3.11 Pulse Generator/ Pulse Extender ...................627

19.3.12 Register Access .........................627

19.4 Register Map.............................628

19.5 Register Description ..........................629

19.5.1 LEUARTn_CTRL - Control Register (Async Reg) ..............629

19.5.2 LEUARTn_CMD - Command Register (Async Reg) .............632

19.5.3 LEUARTn_STATUS - Status Register ..................633

19.5.4 LEUARTn_CLKDIV - Clock Control Register (Async Reg) ...........634

19.5.5 LEUARTn_STARTFRAME - Start Frame Register (Async Reg) .........634

19.5.6 LEUARTn_SIGFRAME - Signal Frame Register (Async Reg) ..........635

19.5.7 LEUARTn_RXDATAX - Receive Buffer Data Extended Register (Actionable Reads) ..635

19.5.8 LEUARTn_RXDATA - Receive Buffer Data Register (Actionable Reads) ......636

19.5.9 LEUARTn_RXDATAXP - Receive Buffer Data Extended Peek Register ......636

19.5.10 LEUARTn_TXDATAX - Transmit Buffer Data Extended Register (Async Reg) ....637

19.5.11 LEUARTn_TXDATA - Transmit Buffer Data Register (Async Reg) ........638

19.5.12 LEUARTn_IF - Interrupt Flag Register .................639

19.5.13 LEUARTn_IFS - Interrupt Flag Set Register ...............640

19.5.14 LEUARTn_IFC - Interrupt Flag Clear Register ...............641

19.5.15 LEUARTn_IEN - Interrupt Enable Register ................642

19.5.16 LEUARTn_PULSECTRL - Pulse Control Register (Async Reg) .........643

19.5.17 LEUARTn_FREEZE - Freeze Register .................644

19.5.18 LEUARTn_SYNCBUSY - Synchronization Busy Register ...........645

19.5.19 LEUARTn_ROUTEPEN - I/O Routing Pin Enable Register ..........646

19.5.20 LEUARTn_ROUTELOC0 - I/O Routing Location Register ...........647

19.5.21 LEUARTn_INPUT - LEUART Input Register ...............650

20. TIMER/WTIMER - Timer/Counter .......................651

20.1 Introduction .............................651

20.2 Features ..............................652

20.3 Functional Description .........................653

20.3.1 Counter Modes ..........................653

20.3.2 Compare/Capture Channels .....................659

20.3.3 Dead-Time Insertion Unit.......................669

20.3.4 Debug Mode ...........................673

20.3.5 Interrupts, DMA and PRS Output ....................673

silabs.com

| Building a more connected world. Rev. 1.1 | 15

Page 16

20.3.6 GPIO Input/Output .........................673

20.4 Register Map.............................674

20.5 Register Description ..........................675

20.5.1 TIMERn_CTRL - Control Register ...................675

20.5.2 TIMERn_CMD - Command Register ..................678

20.5.3 TIMERn_STATUS - Status Register ..................679

20.5.4 TIMERn_IF - Interrupt Flag Register ..................682

20.5.5 TIMERn_IFS - Interrupt Flag Set Register ................683

20.5.6 TIMERn_IFC - Interrupt Flag Clear Register ................684

20.5.7 TIMERn_IEN - Interrupt Enable Register .................686

20.5.8 TIMERn_TOP - Counter Top Value Register ................687

20.5.9 TIMERn_TOPB - Counter Top Value Buffer Register .............687

20.5.10 TIMERn_CNT - Counter Value Register .................688

20.5.11 TIMERn_LOCK - TIMER Configuration Lock Register ............688

20.5.12 TIMERn_ROUTEPEN - I/O Routing Pin Enable Register ...........689

20.5.13 TIMERn_ROUTELOC0 - I/O Routing Location Register ...........690

20.5.14 TIMERn_ROUTELOC2 - I/O Routing Location Register ...........695

20.5.15 TIMERn_CCx_CTRL - CC Channel Control Register ............699

20.5.16 TIMERn_CCx_CCV - CC Channel Value Register (Actionable Reads) ......702

20.5.17 TIMERn_CCx_CCVP - CC Channel Value Peek Register ...........702

20.5.18 TIMERn_CCx_CCVB - CC Channel Buffer Register .............703

20.5.19 TIMERn_DTCTRL - DTI Control Register ................704

20.5.20 TIMERn_DTTIME - DTI Time Control Register ..............706

20.5.21 TIMERn_DTFC - DTI Fault Configuration Register .............708

20.5.22 TIMERn_DTOGEN - DTI Output Generation Enable Register .........710

20.5.23 TIMERn_DTFAULT - DTI Fault Register .................711

20.5.24 TIMERn_DTFAULTC - DTI Fault Clear Register ..............712

20.5.25 TIMERn_DTLOCK - DTI Configuration Lock Register ............713

21. LETIMER - Low Energy Timer ........................714

21.1 Introduction .............................714

21.2 Features ..............................714

21.3 Functional Description .........................715

21.3.1 Timer .............................715

21.3.2 Compare Registers ........................715

21.3.3 Top Value ............................716

21.3.4 Underflow Output Action .......................722

21.3.5 PRS Output ...........................724

21.3.6 Examples ............................724

21.3.7 Register Access..........................727

21.4 Register Map.............................728

21.5 Register Description ..........................729

21.5.1 LETIMERn_CTRL - Control Register (Async Reg) ..............729

21.5.2 LETIMERn_CMD - Command Register .................731

21.5.3 LETIMERn_STATUS - Status Register ..................731

21.5.4 LETIMERn_CNT - Counter Value Register ................732

21.5.5 LETIMERn_COMP0 - Compare Value Register 0 (Async Reg) .........732

silabs.com

| Building a more connected world. Rev. 1.1 | 16

Page 17

21.5.6 LETIMERn_COMP1 - Compare Value Register 1 (Async Reg) .........733

21.5.7 LETIMERn_REP0 - Repeat Counter Register 0 (Async Reg) ..........733

21.5.8 LETIMERn_REP1 - Repeat Counter Register 1 (Async Reg) ..........734

21.5.9 LETIMERn_IF - Interrupt Flag Register .................734

21.5.10 LETIMERn_IFS - Interrupt Flag Set Register ...............735

21.5.11 LETIMERn_IFC - Interrupt Flag Clear Register ..............736

21.5.12 LETIMERn_IEN - Interrupt Enable Register ...............737

21.5.13 LETIMERn_SYNCBUSY - Synchronization Busy Register ..........737

21.5.14 LETIMERn_ROUTEPEN - I/O Routing Pin Enable Register ..........738

21.5.15 LETIMERn_ROUTELOC0 - I/O Routing Location Register ..........739

21.5.16 LETIMERn_PRSSEL - PRS Input Select Register .............742

22. CRYOTIMER - Ultra Low Energy Timer/Counter .................745

22.1 Introduction .............................745

22.2 Features ..............................745

22.3 Functional Description .........................745

22.3.1 Block Diagram ..........................746

22.3.2 Operation ............................747

22.3.3 Debug Mode ...........................747

22.3.4 Energy Mode Availability .......................747

22.4 Register Map.............................748

22.5 Register Description ..........................749

22.5.1 CRYOTIMER_CTRL - Control Register .................749

22.5.2 CRYOTIMER_PERIODSEL - Interrupt Duration ..............750

22.5.3 CRYOTIMER_CNT - Counter Value ..................751

22.5.4 CRYOTIMER_EM4WUEN - Wake Up Enable ...............751

22.5.5 CRYOTIMER_IF - Interrupt Flag Register .................752

22.5.6 CRYOTIMER_IFS - Interrupt Flag Set Register ...............752

22.5.7 CRYOTIMER_IFC - Interrupt Flag Clear Register ..............753

22.5.8 CRYOTIMER_IEN - Interrupt Enable Register ...............753

23. VDAC - Digital to Analog Converter .....................754

23.1 Introduction .............................754

23.2 Features ..............................755

23.3 Functional Description .........................755

23.3.1 Power Supply ..........................756

23.3.2 I/O Pin Considerations .......................756

23.3.3 Enabling and Disabling a Channel ...................756

23.3.4 Conversions ...........................757

23.3.5 Reference Selection ........................757

23.3.6 Warmup Time and Initial Conversion ...................758

23.3.7 Analog Output ..........................758

23.3.8 Output Mode ...........................758

23.3.9 Async Mode ...........................759

23.3.10 Refresh Timer ..........................759

23.3.11 Clock Prescaling .........................759

23.3.12 High Speed ...........................759

silabs.com

| Building a more connected world. Rev. 1.1 | 17

Page 18

23.3.13 Sine Generation Mode .......................760

23.3.14 Interrupt Flags ..........................760

23.3.15 PRS Outputs ..........................761

23.3.16 DMA Request ..........................761

23.3.17 LESENSE Trigger Mode ......................761

23.3.18 Opamps ............................761

23.3.19 Calibration ...........................761

23.3.20 Warmup Mode..........................762

23.4 Register Map.............................763

23.5 Register Description ..........................764

23.5.1 VDACn_CTRL - Control Register ...................764

23.5.2 VDACn_STATUS - Status Register ...................767

23.5.3 VDACn_CH0CTRL - Channel 0 Control Register ..............769

23.5.4 VDACn_CH1CTRL - Channel 1 Control Register ..............771

23.5.5 VDACn_CMD - Command Register ...................773

23.5.6 VDACn_IF - Interrupt Flag Register ...................774

23.5.7 VDACn_IFS - Interrupt Flag Set Register .................776

23.5.8 VDACn_IFC - Interrupt Flag Clear Register ................778

23.5.9 VDACn_IEN - Interrupt Enable Register .................780

23.5.10 VDACn_CH0DATA - Channel 0 Data Register ...............781

23.5.11 VDACn_CH1DATA - Channel 1 Data Register ...............782

23.5.12 VDACn_COMBDATA - Combined Data Register ..............782

23.5.13 VDACn_CAL - Calibration Register ..................783

23.5.14 VDACn_OPAx_APORTREQ - Operational Amplifier APORT Request Status Register . 784

23.5.15 VDACn_OPAx_APORTCONFLICT - Operational Amplifier APORT Conflict Status Register

................................785

23.5.16 VDACn_OPAx_CTRL - Operational Amplifier Control Register .........786

23.5.17 VDACn_OPAx_TIMER - Operational Amplifier Timer Control Register ......789

23.5.18 VDACn_OPAx_MUX - Operational Amplifier Mux Configuration Register ......790

23.5.19 VDACn_OPAx_OUT - Operational Amplifier Output Configuration Register .....793

23.5.20 VDACn_OPAx_CAL - Operational Amplifier Calibration Register ........795

24. OPAMP - Operational Amplifier .......................797

24.1 Introduction .............................797

24.2 Features ..............................797

24.3 Functional Description .........................798

24.3.1 Opamp Configuration........................799

24.3.2 Interrupts and PRS Output ......................803

24.3.3 APORT Request and Conflict Status ...................803

24.3.4 Opamp Modes ..........................803

24.3.5 Opamp VDAC Combination ......................810

24.4 Register Map.............................811

24.5 Register Description ..........................811

25. ACMP - Analog Comparator ........................812

25.1 Introduction .............................812

25.2 Features ..............................813

silabs.com

| Building a more connected world. Rev. 1.1 | 18

Page 19

25.3 Functional Description .........................814

25.3.1 Power Supply ..........................814

25.3.2 Warm-up Time ..........................815

25.3.3 Response Time .........................815

25.3.4 Hysteresis ...........................816

25.3.5 Input Pin Considerations .......................817

25.3.6 Input Selection ..........................817

25.3.7 Capacitive Sense Mode ......................818

25.3.8 Interrupts and PRS Output ......................820

25.3.9 Output to GPIO .........................820

25.3.10 APORT Conflicts ........................820

25.3.11 Supply Voltage Monitoring .....................820

25.3.12 External Override Interface .....................821

25.4 Register Map.............................821

25.5 Register Description ..........................822

25.5.1 ACMPn_CTRL - Control Register ...................822

25.5.2 ACMPn_INPUTSEL - Input Selection Register ...............825

25.5.3 ACMPn_STATUS - Status Register ...................830

25.5.4 ACMPn_IF - Interrupt Flag Register ..................831

25.5.5 ACMPn_IFS - Interrupt Flag Set Register .................831

25.5.6 ACMPn_IFC - Interrupt Flag Clear Register ................832

25.5.7 ACMPn_IEN - Interrupt Enable Register .................833

25.5.8 ACMPn_APORTREQ - APORT Request Status Register ...........834

25.5.9 ACMPn_APORTCONFLICT - APORT Conflict Status Register .........835

25.5.10 ACMPn_HYSTERESIS0 - Hysteresis 0 Register ..............837

25.5.11 ACMPn_HYSTERESIS1 - Hysteresis 1 Register ..............838

25.5.12 ACMPn_ROUTEPEN - I/O Routing Pine Enable Register ...........839

25.5.13 ACMPn_ROUTELOC0 - I/O Routing Location Register ............840

25.5.14 ACMPn_EXTIFCTRL - External Override Interface Control ..........842

26. ADC - Analog to Digital Converter ......................844

26.1 Introduction .............................844

26.2 Features ..............................845

26.3 Functional Description .........................846

26.3.1 Clock Selection ..........................847

26.3.2 Conversions ...........................848

26.3.3 ADC Modes ...........................848

26.3.4 Warm-up Time ..........................850

26.3.5 Power Supply ..........................851

26.3.6 Input Pin Considerations .......................851

26.3.7 Input Selection ..........................852

26.3.8 Reference Selection and Input Range Definition ...............856

26.3.9 Programming of Bias Current .....................860

26.3.10 Feature Set ...........................860

26.3.11 Interrupts, PRS Output .......................867

26.3.12 DMA Request ..........................867

26.3.13 Calibration ...........................867

silabs.com

| Building a more connected world. Rev. 1.1 | 19

Page 20

26.3.14 EM2 Deep Sleep or EM3 Stop Operation .................868

26.3.15 ASYNC ADC_CLK Usage Restrictions and Benefits .............869

26.3.16 Window Compare Function .....................869

26.3.17 ADC Programming Model ......................870

26.4 Register Map.............................871

26.5 Register Description ..........................872

26.5.1 ADCn_CTRL - Control Register ....................872

26.5.2 ADCn_CMD - Command Register ...................875

26.5.3 ADCn_STATUS - Status Register ...................876

26.5.4 ADCn_SINGLECTRL - Single Channel Control Register ............878

26.5.5 ADCn_SINGLECTRLX - Single Channel Control Register Continued .......883

26.5.6 ADCn_SCANCTRL - Scan Control Register ................886

26.5.7 ADCn_SCANCTRLX - Scan Control Register Continued ...........889

26.5.8 ADCn_SCANMASK - Scan Sequence Input Mask Register ...........892

26.5.9 ADCn_SCANINPUTSEL - Input Selection Register for Scan Mode ........894

26.5.10 ADCn_SCANNEGSEL - Negative Input Select Register for Scan ........897

26.5.11 ADCn_CMPTHR - Compare Threshold Register ..............899

26.5.12 ADCn_BIASPROG - Bias Programming Register for Various Analog Blocks Used in ADC Op-

eration ..............................900

26.5.13 ADCn_CAL - Calibration Register ...................901

26.5.14 ADCn_IF - Interrupt Flag Register ...................903

26.5.15 ADCn_IFS - Interrupt Flag Set Register .................905

26.5.16 ADCn_IFC - Interrupt Flag Clear Register ................907

26.5.17 ADCn_IEN - Interrupt Enable Register .................909

26.5.18 ADCn_SINGLEDATA - Single Conversion Result Data (Actionable Reads) .....910

26.5.19 ADCn_SCANDATA - Scan Conversion Result Data (Actionable Reads) ......910

26.5.20 ADCn_SINGLEDATAP - Single Conversion Result Data Peek Register ......911

26.5.21 ADCn_SCANDATAP - Scan Sequence Result Data Peek Register ........911

26.5.22 ADCn_SCANDATAX - Scan Sequence Result Data + Data Source Register (Actionable

Reads) ..............................912

26.5.23 ADCn_SCANDATAXP - Scan Sequence Result Data + Data Source Peek Register ..912

26.5.24 ADCn_APORTREQ - APORT Request Status Register ...........913

26.5.25 ADCn_APORTCONFLICT - APORT Conflict Status Register ..........914

26.5.26 ADCn_SINGLEFIFOCOUNT - Single FIFO Count Register ..........915

26.5.27 ADCn_SCANFIFOCOUNT - Scan FIFO Count Register ...........915

26.5.28 ADCn_SINGLEFIFOCLEAR - Single FIFO Clear Register ...........916

26.5.29 ADCn_SCANFIFOCLEAR - Scan FIFO Clear Register ............916

26.5.30 ADCn_APORTMASTERDIS - APORT Bus Master Disable Register .......917

27. IDAC - Current Digital to Analog Converter...................920

27.1 Introduction .............................920

27.2 Features ..............................920

27.3 Functional Description .........................921

27.3.1 Current Programming .......................921

27.3.2 IDAC Enable and Warm-up ......................921

27.3.3 Output Control ..........................922

27.3.4 APORT Configuration ........................922

27.3.5 Interrupts ............................922

silabs.com

| Building a more connected world. Rev. 1.1 | 20

Page 21

27.3.6 Minimizing Output Transition .....................922

27.3.7 Duty Cycle Configuration.......................922

27.3.8 Calibration ...........................922

27.3.9 PRS Triggered Charge Injection ....................923

27.4 Register Map.............................923

27.5 Register Description ..........................924

27.5.1 IDAC_CTRL - Control Register ....................924

27.5.2 IDAC_CURPROG - Current Programming Register .............926

27.5.3 IDAC_DUTYCONFIG - Duty Cycle Configuration Register ...........927

27.5.4 IDAC_STATUS - Status Register ...................927

27.5.5 IDAC_IF - Interrupt Flag Register ...................928

27.5.6 IDAC_IFS - Interrupt Flag Set Register .................928

27.5.7 IDAC_IFC - Interrupt Flag Clear Register .................929

27.5.8 IDAC_IEN - Interrupt Enable Register ..................929

27.5.9 IDAC_APORTREQ - APORT Request Status Register ............930

27.5.10 IDAC_APORTCONFLICT - APORT Request Status Register .........930

28. LESENSE - Low Energy Sensor Interface ...................931

28.1 Introduction .............................931

28.2 Features ..............................932

28.3 Functional Description .........................932

28.3.1 Channel Configuration .......................933

28.3.2 Scan Sequence ..........................934

28.3.3 Sensor Timing ..........................935

28.3.4 Sensor Interaction .........................937

28.3.5 Sensor Sampling .........................938

28.3.6 Sensor Evaluation .........................939

28.3.7 Decoder ............................941

28.3.8 Measurement Results........................944

28.3.9 VDAC Interface ..........................945

28.3.10 ACMP Interface .........................945

28.3.11 ACMP and VDAC Duty Cycling ....................945

28.3.12 ADC Interface ..........................946

28.3.13 DMA Requests .........................946

28.3.14 PRS Output...........................946

28.3.15 RAM .............................946

28.3.16 Application Examples .......................946

28.4 Register Map.............................952

28.5 Register Description ..........................954

28.5.1 LESENSE_CTRL - Control Register (Async Reg) ..............954

28.5.2 LESENSE_TIMCTRL - Timing Control Register (Async Reg) ..........957

28.5.3 LESENSE_PERCTRL - Peripheral Control Register (Async Reg) .........959

28.5.4 LESENSE_DECCTRL - Decoder Control Register (Async Reg) .........962

28.5.5 LESENSE_BIASCTRL - Bias Control Register (Async Reg) ..........965

28.5.6 LESENSE_EVALCTRL - LESENSE Evaluation Control (Async Reg) .......965

28.5.7 LESENSE_PRSCTRL - PRS Control Register (Async Reg) ..........966

28.5.8 LESENSE_CMD - Command Register ..................967

silabs.com

| Building a more connected world. Rev. 1.1 | 21

Page 22

28.5.9 LESENSE_CHEN - Channel Enable Register (Async Reg) ...........967

28.5.10 LESENSE_SCANRES - Scan Result Register (Async Reg) ..........968

28.5.11 LESENSE_STATUS - Status Register (Async Reg) .............969

28.5.12 LESENSE_PTR - Result Buffer Pointers (Async Reg) ............970

28.5.13 LESENSE_BUFDATA - Result Buffer Data Register (Async Reg) (Actionable Reads) . 970

28.5.14 LESENSE_CURCH - Current Channel Index (Async Reg) ..........971

28.5.15 LESENSE_DECSTATE - Current Decoder State (Async Reg) .........971

28.5.16 LESENSE_SENSORSTATE - Decoder Input Register (Async Reg) .......972

28.5.17 LESENSE_IDLECONF - GPIO Idle Phase Configuration (Async Reg) ......973

28.5.18 LESENSE_ALTEXCONF - Alternative Excite Pin Configuration (Async Reg) ....977

28.5.19 LESENSE_IF - Interrupt Flag Register .................980

28.5.20 LESENSE_IFS - Interrupt Flag Set Register ...............982

28.5.21 LESENSE_IFC - Interrupt Flag Clear Register ...............984

28.5.22 LESENSE_IEN - Interrupt Enable Register ................986

28.5.23 LESENSE_SYNCBUSY - Synchronization Busy Register ...........987

28.5.24 LESENSE_ROUTEPEN - I/O Routing Register (Async Reg) ..........988

28.5.25 LESENSE_STx_TCONFA - State Transition Configuration a (Async Reg) .....990

28.5.26 LESENSE_STx_TCONFB - State Transition Configuration B (Async Reg) .....992

28.5.27 LESENSE_BUFx_DATA - Scan Results (Async Reg) ............993

28.5.28 LESENSE_CHx_TIMING - Scan Configuration (Async Reg) ..........994

28.5.29 LESENSE_CHx_INTERACT - Scan Configuration (Async Reg) .........995

28.5.30 LESENSE_CHx_EVAL - Scan Configuration (Async Reg) ...........997

29. GPCRC - General Purpose Cyclic Redundancy Check ..............999

29.1 Introduction .............................999

29.2 Features ..............................999

29.3 Functional Description .........................1000

29.3.1 Polynomial Specification .......................1001

29.3.2 Input and Output Specification .....................1001

29.3.3 Initialization ...........................1001

29.3.4 DMA Usage ...........................1001

29.3.5 Byte-Level Bit Reversal and Byte Reordering ................1002

29.4 Register Map.............................1004

29.5 Register Description ..........................1005

29.5.1 GPCRC_CTRL - Control Register ...................1005

29.5.2 GPCRC_CMD - Command Register ..................1006

29.5.3 GPCRC_INIT - CRC Init Value ....................1006

29.5.4 GPCRC_POLY - CRC Polynomial Value .................1007

29.5.5 GPCRC_INPUTDATA - Input 32-bit Data Register ..............1007

29.5.6 GPCRC_INPUTDATAHWORD - Input 16-bit Data Register ...........1008

29.5.7 GPCRC_INPUTDATABYTE - Input 8-bit Data Register ............1008

29.5.8 GPCRC_DATA - CRC Data Register ..................1009

29.5.9 GPCRC_DATAREV - CRC Data Reverse Register .............1009

29.5.10 GPCRC_DATABYTEREV - CRC Data Byte Reverse Register .........1010

30. TRNG - True Random Number Generator ...................1011

30.1 Introduction .............................1011

silabs.com

| Building a more connected world. Rev. 1.1 | 22

Page 23

30.2 Features ..............................1011

30.3 Functional Description .........................1012

30.3.1 Built-In Tests ...........................1012

30.3.2 FIFO Interface ..........................1012

30.3.3 Data Format - Byte Ordering .....................1013

30.3.4 TRNG Usage ..........................1013

30.4 Register Map.............................1015

30.5 Register Description ..........................1016

30.5.1 TRNGn_CONTROL - Main Control Register ................1016

30.5.2 TRNGn_FIFOLEVEL - FIFO Level Register (Actionable Reads) .........1018

30.5.3 TRNGn_FIFODEPTH - FIFO Depth Register ...............1018

30.5.4 TRNGn_KEY0 - Key Register 0 ....................1019

30.5.5 TRNGn_KEY1 - Key Register 1 ....................1019

30.5.6 TRNGn_KEY2 - Key Register 2 ....................1020

30.5.7 TRNGn_KEY3 - Key Register 3 ....................1020

30.5.8 TRNGn_TESTDATA - Test Data Register .................1021

30.5.9 TRNGn_STATUS - Status Register ...................1022

30.5.10 TRNGn_INITWAITVAL - Initial Wait Counter ...............1023

30.5.11 TRNGn_FIFO - FIFO Data (Actionable Reads) ..............1023

31. CRYPTO - Crypto Accelerator........................1024

31.1 Introduction .............................1024

31.2 Features ..............................1025

31.3 Usage and Programming Interface .....................1025

31.4 Functional Description .........................1026

31.4.1 Data and Key Registers .......................1027

31.4.2 Instructions and Execution ......................1029

31.4.3 Repeated Sequence ........................1034

31.4.4 AES..............................1035

31.4.5 SHA..............................1037

31.4.6 ECC .............................1037

31.4.7 GCM and GMAC .........................1038

31.4.8 DMA .............................1038

31.4.9 BUFC Data Transfer ........................1040

31.4.10 Debugging ...........................1041

31.4.11 Example: Cipher Block Chaining (CBC) .................1041

31.5 Register Map.............................1044

31.6 Register Description ..........................1046

31.6.1 CRYPTO_CTRL - Control Register ...................1046

31.6.2 CRYPTO_WAC - Wide Arithmetic Configuration ..............1049

31.6.3 CRYPTO_CMD - Command Register ..................1051

31.6.4 CRYPTO_STATUS - Status Register ..................1056

31.6.5 CRYPTO_DSTATUS - Data Status Register ................1057

31.6.6 CRYPTO_CSTATUS - Control Status Register ...............1058

31.6.7 CRYPTO_KEY - KEY Register Access (No Bit Access) (Actionable Reads) .....1059

31.6.8 CRYPTO_KEYBUF - KEY Buffer Register Access (No Bit Access) (Actionable Reads) . 1060

silabs.com

| Building a more connected world. Rev. 1.1 | 23

Page 24

31.6.9 CRYPTO_SEQCTRL - Sequence Control ................1061

31.6.10 CRYPTO_SEQCTRLB - Sequence Control B ...............1062

31.6.11 CRYPTO_IF - AES Interrupt Flags ...................1063

31.6.12 CRYPTO_IFS - Interrupt Flag Set Register ................1064

31.6.13 CRYPTO_IFC - Interrupt Flag Clear Register ...............1065

31.6.14 CRYPTO_IEN - Interrupt Enable Register ................1066

31.6.15 CRYPTO_SEQ0 - Sequence Register 0 .................1066

31.6.16 CRYPTO_SEQ1 - Sequence Register 1 .................1067

31.6.17 CRYPTO_SEQ2 - Sequence Register 2 .................1067

31.6.18 CRYPTO_SEQ3 - Sequence Register 3 .................1068

31.6.19 CRYPTO_SEQ4 - Sequence Register 4 .................1068

31.6.20 CRYPTO_DATA0 - DATA0 Register Access (No Bit Access) (Actionable Reads) ...1069

31.6.21 CRYPTO_DATA1 - DATA1 Register Access (No Bit Access) (Actionable Reads) ...1069

31.6.22 CRYPTO_DATA2 - DATA2 Register Access (No Bit Access) (Actionable Reads) ...1070

31.6.23 CRYPTO_DATA3 - DATA3 Register Access (No Bit Access) (Actionable Reads) ...1070

31.6.24 CRYPTO_DATA0XOR - DATA0XOR Register Access (No Bit Access) (Actionable Reads) .

................................1071

31.6.25 CRYPTO_DATA0BYTE - DATA0 Register Byte Access (No Bit Access) (Actionable Reads)

................................1071

31.6.26 CRYPTO_DATA1BYTE - DATA1 Register Byte Access (No Bit Access) (Actionable Reads)

................................1072

31.6.27 CRYPTO_DATA0XORBYTE - DATA0 Register Byte XOR Access (No Bit Access) (Actionable

Reads) ..............................1072

31.6.28 CRYPTO_DATA0BYTE12 - DATA0 Register Byte 12 Access (No Bit Access) ....1073

31.6.29 CRYPTO_DATA0BYTE13 - DATA0 Register Byte 13 Access (No Bit Access) ....1073

31.6.30 CRYPTO_DATA0BYTE14 - DATA0 Register Byte 14 Access (No Bit Access) ....1074

31.6.31 CRYPTO_DATA0BYTE15 - DATA0 Register Byte 15 Access (No Bit Access) ....1074

31.6.32 CRYPTO_DDATA0 - DDATA0 Register Access (No Bit Access) (Actionable Reads) ..1075

31.6.33 CRYPTO_DDATA1 - DDATA1 Register Access (No Bit Access) (Actionable Reads) ..1075

31.6.34 CRYPTO_DDATA2 - DDATA2 Register Access (No Bit Access) (Actionable Reads) ..1076

31.6.35 CRYPTO_DDATA3 - DDATA3 Register Access (No Bit Access) (Actionable Reads) ..1076

31.6.36 CRYPTO_DDATA4 - DDATA4 Register Access (No Bit Access) (Actionable Reads) ..1077

31.6.37 CRYPTO_DDATA0BIG - DDATA0 Register Big Endian Access (No Bit Access) (Actionable

Reads) ..............................1077

31.6.38 CRYPTO_DDATA0BYTE - DDATA0 Register Byte Access (No Bit Access) (Actionable

Reads) ..............................1078

31.6.39 CRYPTO_DDATA1BYTE - DDATA1 Register Byte Access (No Bit Access) (Actionable

Reads) ..............................1078

31.6.40 CRYPTO_DDATA0BYTE32 - DDATA0 Register Byte 32 Access (No Bit Access) ...1079

31.6.41 CRYPTO_QDATA0 - QDATA0 Register Access (No Bit Access) (Actionable Reads) ..1079

31.6.42 CRYPTO_QDATA1 - QDATA1 Register Access (No Bit Access) (Actionable Reads) ..1080

31.6.43 CRYPTO_QDATA1BIG - QDATA1 Register Big Endian Access (No Bit Access) (Actionable

Reads) ..............................1080

31.6.44 CRYPTO_QDATA0BYTE - QDATA0 Register Byte Access (No Bit Access) (Actionable

Reads) ..............................1081

31.6.45 CRYPTO_QDATA1BYTE - QDATA1 Register Byte Access (No Bit Access) (Actionable

Reads) ..............................1081

32. GPIO - General Purpose Input/Output.....................1082

silabs.com

| Building a more connected world. Rev. 1.1 | 24

Page 25

32.1 Introduction .............................1082

32.2 Features ..............................1083

32.3 Functional Description .........................1084

32.3.1 Pin Configuration .........................1085

32.3.2 EM4 Wake-up ..........................1088

32.3.3 EM4 Retention ..........................1088

32.3.4 Alternate Functions ........................1089

32.3.5 Interrupt Generation ........................1089

32.3.6 Output to PRS ..........................1091

32.3.7 Synchronization..........................1091

32.4 Register Map.............................1092

32.5 Register Description ..........................1094

32.5.1 GPIO_Px_CTRL - Port Control Register .................1094

32.5.2 GPIO_Px_MODEL - Port Pin Mode Low Register ..............1096

32.5.3 GPIO_Px_MODEH - Port Pin Mode High Register ..............1101

32.5.4 GPIO_Px_DOUT - Port Data Out Register ................1106

32.5.5 GPIO_Px_DOUTTGL - Port Data Out Toggle Register ............1106

32.5.6 GPIO_Px_DIN - Port Data in Register ..................1107

32.5.7 GPIO_Px_PINLOCKN - Port Unlocked Pins Register .............1107

32.5.8 GPIO_Px_OVTDIS - Over Voltage Disable for All Modes ...........1108

32.5.9 GPIO_EXTIPSELL - External Interrupt Port Select Low Register .........1109

32.5.10 GPIO_EXTIPSELH - External Interrupt Port Select High Register ........1112

32.5.11 GPIO_EXTIPINSELL - External Interrupt Pin Select Low Register ........1115

32.5.12 GPIO_EXTIPINSELH - External Interrupt Pin Select High Register ........1118

32.5.13 GPIO_EXTIRISE - External Interrupt Rising Edge Trigger Register ........1120

32.5.14 GPIO_EXTIFALL - External Interrupt Falling Edge Trigger Register .......1121

32.5.15 GPIO_EXTILEVEL - External Interrupt Level Register ............1122

32.5.16 GPIO_IF - Interrupt Flag Register ...................1123

32.5.17 GPIO_IFS - Interrupt Flag Set Register .................1123

32.5.18 GPIO_IFC - Interrupt Flag Clear Register ................1124

32.5.19 GPIO_IEN - Interrupt Enable Register .................1124

32.5.20 GPIO_EM4WUEN - EM4 Wake Up Enable Register .............1125

32.5.21 GPIO_ROUTEPEN - I/O Routing Pin Enable Register ............1126