Page 1

EFM32 Jade Gecko Family

EFM32JG1 Reference Manual

The EFM32 Jade Gecko MCUs are the world’s most energyfriendly microcontrollers.

EFM32JG1 features a powerful 32-bit ARM® Cortex-M3 and a wide selection of peripherals, including a unique cryptographic hardware engine supporting AES, ECC, and

SHA. These features, combined with ultra-low current active mode and short wake-up

time from energy-saving modes, make EFM32JG1 microcontrollers well suited for any

battery-powered application, as well as other systems requiring high performance and

low-energy consumption.

Example applications:

• IoT devices and sensors

• Health and fitness

• Smart accessories

Core / Memory

ARM Cortex

Flash Program

Memory

TM

M3 processor

RAM Memory

Memory

Protection Unit

Debug Interface DMA Controller

• Home automation and security

• Industrial and factory automation

Clock Management

High Frequency

Crystal

Oscillator

Low Frequency

RC Oscillator

Low Frequency

Crystal

Oscillator

High Frequency

Auxiliary High

Frequency RC

Frequency RC

ENERGY FRIENDLY FEATURES

• ARM Cortex-M3 at 40 MHz

• Ultra low energy operation:

• 2.1 μA EM3 Stop current (CRYOTIMER

running with state/RAM retention)

• 2.5 μA EM2 DeepSleep current (RTCC

running with state and RAM retention)

• 63 μA/MHz in Energy Mode 0 (EM0)

• Hardware cryptographic engine supports

AES, ECC, and SHA

• Integrated dc-dc converter

• CRYOTIMER operates down to EM4

• 5 V tolerant I/O

Energy Management

RC Oscillator

Oscillator

Ultra Low

Oscillator

Voltage

Regulator

DC-DC

Converter

Brown-Out

Detector

Voltage Monitor

Power-On Reset

32-bit bus

Peripheral Reflex System

Serial Interfaces

USART

Low Energy UART

I

Lowest power mode with peripheral operational:

EM0 - Active

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

TM

2

C

I/O Ports Timers and Triggers

External Interrupts

General Purpose I/O

Pin Reset

Pin Wakeup

EM1 - Sleep

Timer/Counter Low Energy Timer

Pulse Counter

Watchdog Timer

EM2 – Deep Sleep

Real Time Counter

and Calendar

CRYOTIMER

EM3 - Stop

Analog Interfaces

ADC

Analog Comparator

IDAC

EM4 - Hibernate

Other

CRYPTO

CRC

EM4 - Shutoff

Page 2

EFM32JG1 Reference Manual

About This Document

1. About This Document

1.1 Introduction

This document contains reference material for the EFM32 Jade Gecko devices. All modules and peripherals in the EFM32 Jade Gecko

devices are described in general terms. Not all modules are present in all devices and the feature set for each device might vary. Such

differences, including pinout, are covered in the device data sheets.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 1

Page 3

EFM32JG1 Reference Manual

About This Document

1.2 Conventions

Register Names

Register names are given with a module name prefix followed by the short register name:

TIMERn_CTRL - Control Register

The "n" denotes the module number for modules which can exist in more than one instance.

Some registers are grouped which leads to a group name following the module prefix:

GPIO_Px_DOUT - Port Data Out Register

The "x" denotes the different ports.

Bit Fields

Registers contain one or more bit fields which can be 1 to 32 bits wide. Bit fields wider than 1 bit are given with start (x) and stop (y) bit

[y:x].

Bit fields containing more than one bit are unsigned integers unless otherwise is specified.

Unspecified bit field settings must not be used, as this may lead to unpredictable behaviour.

Address

The address for each register can be found by adding the base address of the module found in the Memory Map (see Figure 4.2 Sys-

tem Address Space with Core and Code Space Listing on page 15), and the offset address for the register (found in module Register

Map).

Access Type

The register access types used in the register descriptions are explained in Table 1.1 Register Access Types on page 2.

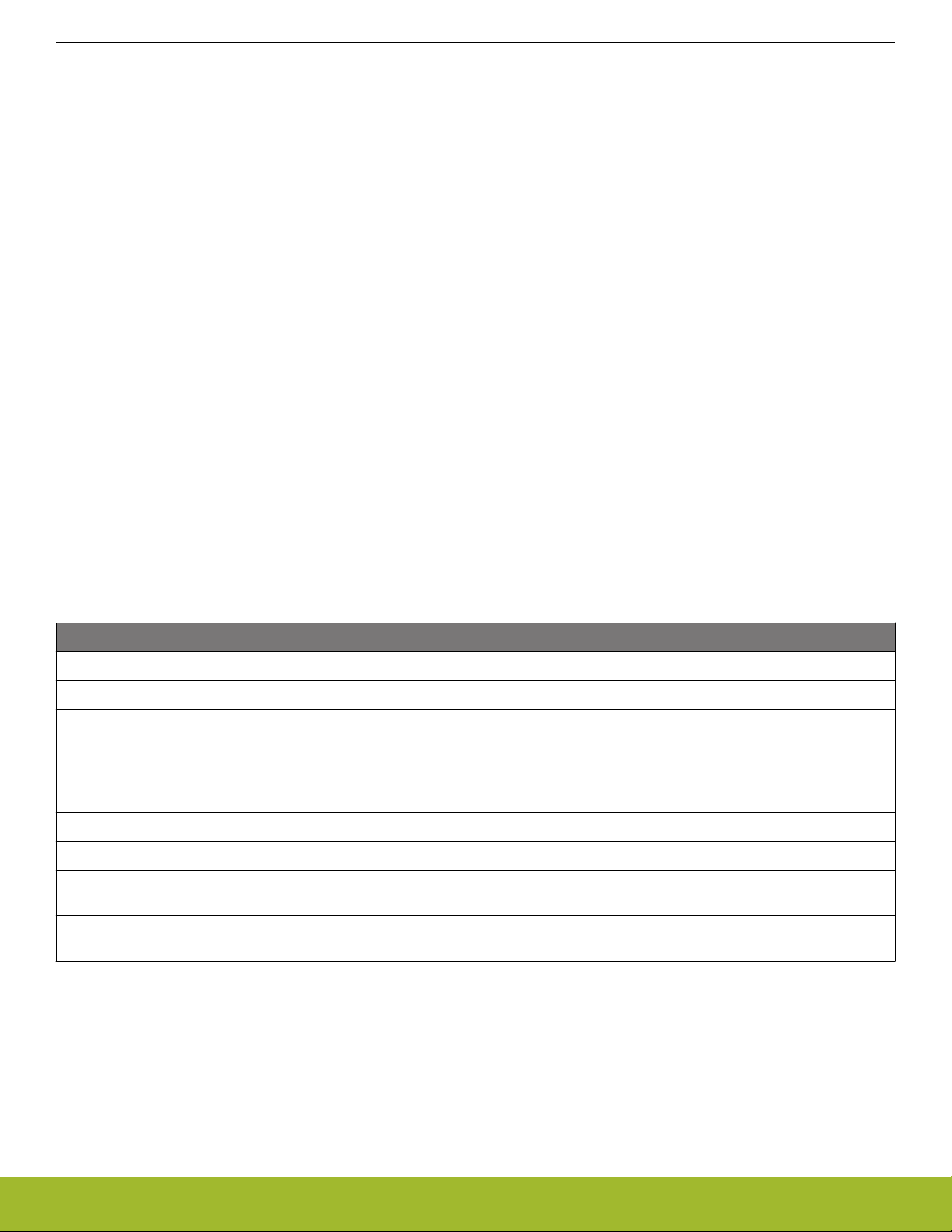

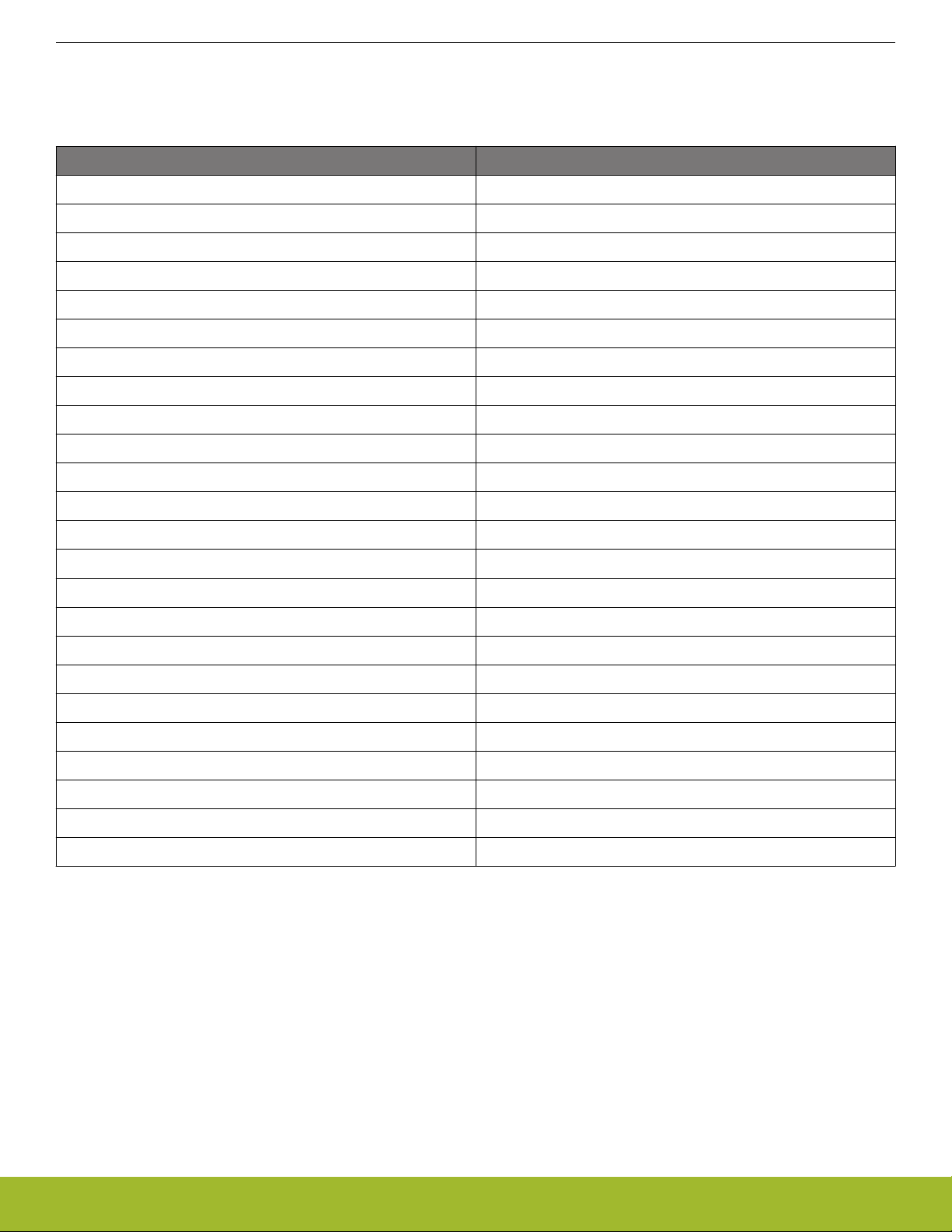

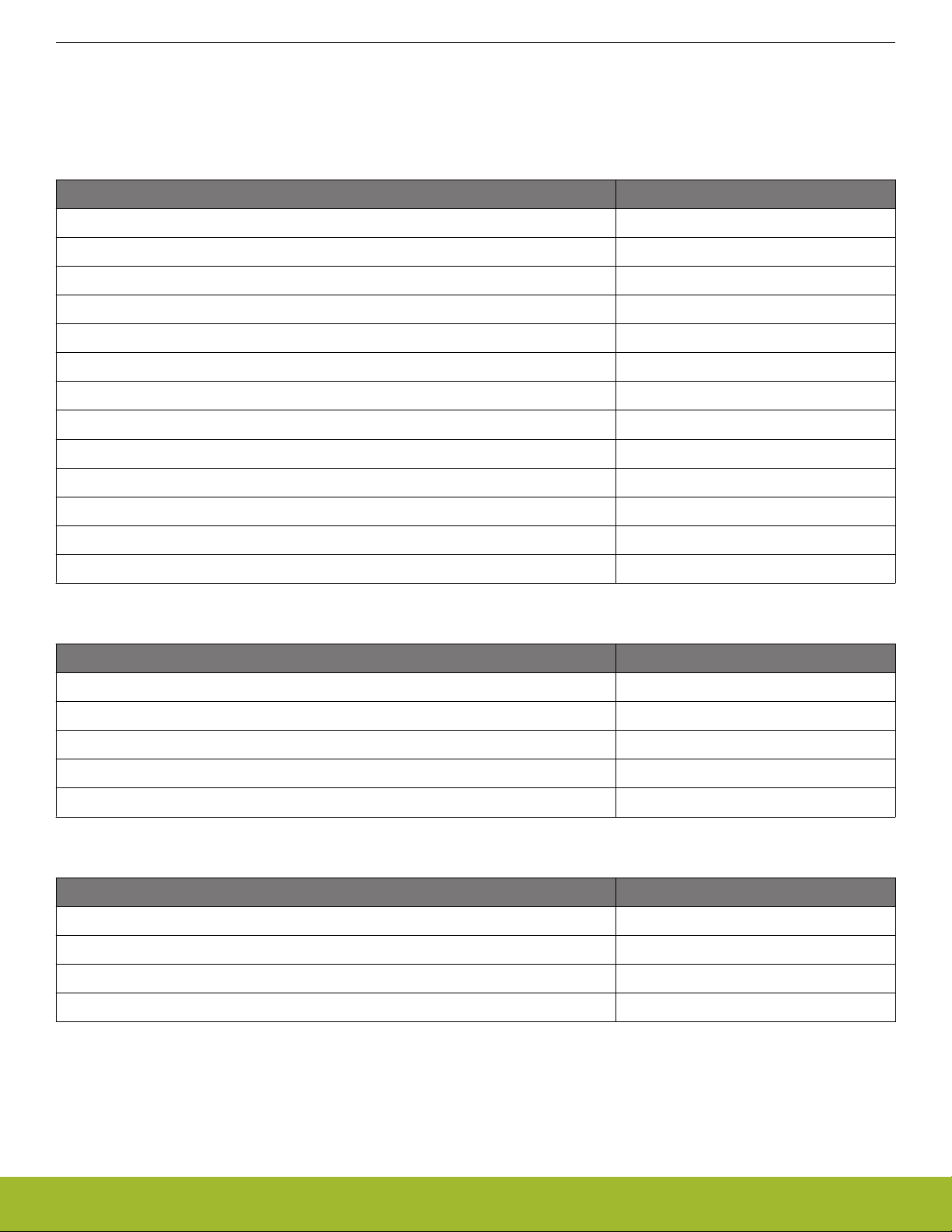

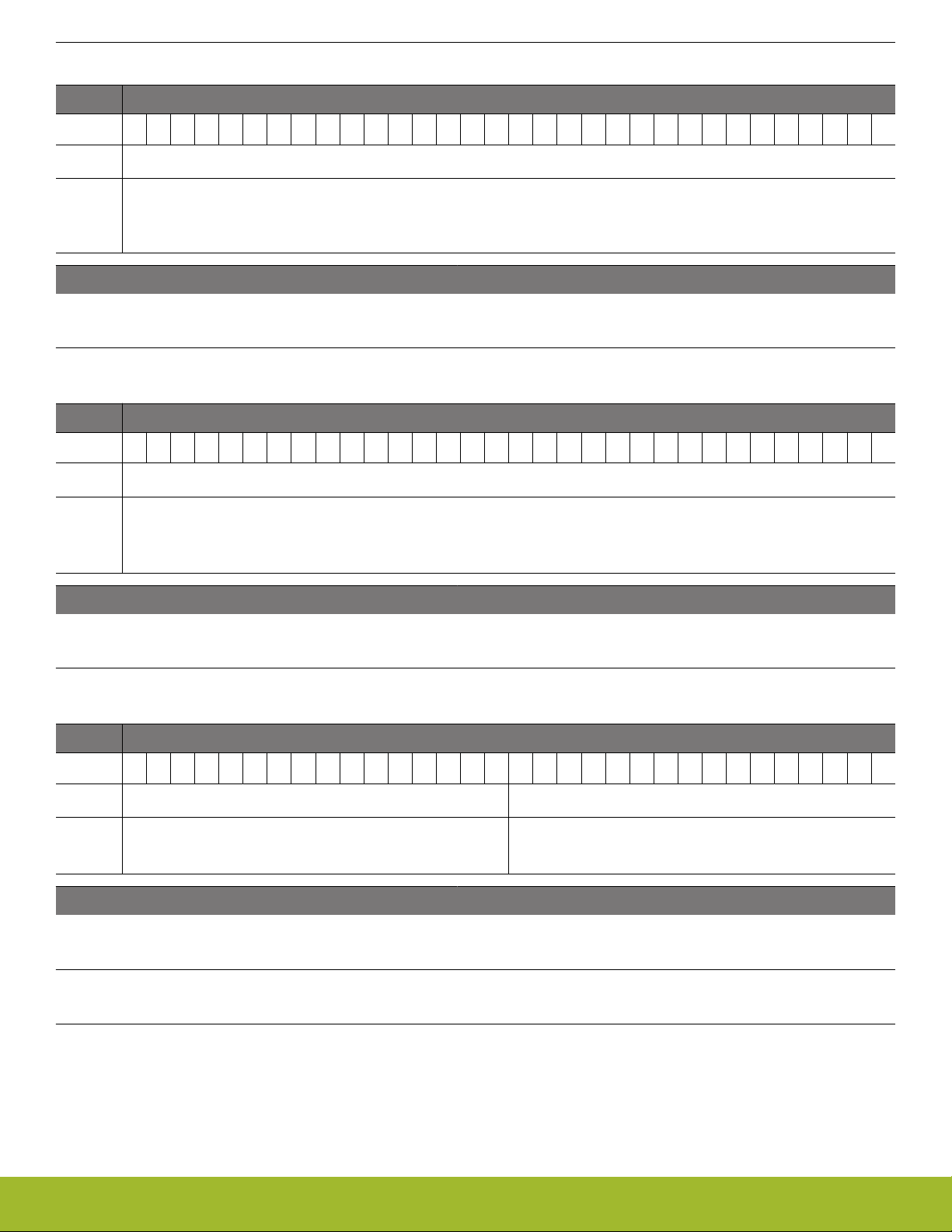

Table 1.1. Register Access Types

Access Type Description

R Read only. Writes are ignored

RW Readable and writable

RW1 Readable and writable. Only writes to 1 have effect

(R)W1 Sometimes readable. Only writes to 1 have effect. Currently only

used for IFC registers (see 3.3.1.2 IFC Read-clear Operation)

W1 Read value undefined. Only writes to 1 have effect

W Write only. Read value undefined.

RWH Readable, writable, and updated by hardware

RW(nB), RWH(nB), etc. "(nB)" suffix indicates that register explicitly does not support pe-

ripheral bit set or clear (see 4.2.2 Peripheral Bit Set and Clear)

RW(a), R(a), etc. "(a)" suffix indicates that register has actionable reads (see

5.3.6 Debugger reads of actionable registers)

Number format

0x prefix is used for hexadecimal numbers

0b prefix is used for binary numbers

Numbers without prefix are in decimal representation.

Reserved

Registers and bit fields marked with reserved are reserved for future use. These should be written to 0 unless otherwise stated in the

Register Description. Reserved bits might be read as 1 in future devices.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 2

Page 4

EFM32JG1 Reference Manual

About This Document

Reset Value

The reset value denotes the value after reset.

Registers denoted with X have unknown value out of reset and need to be initialized before use. Note that read-modify-write operations

on these registers before they are initialized results in undefined register values.

Pin Connections

Pin connections are given with a module prefix followed by a short pin name:

CMU_CLKOUT1 (Clock management unit, clock output pin number 1)

The location for the pin names given in the module documentation can be found in the device-specific datasheet.

1.3 Related Documentation

Further documentation on the EFM32 Jade Gecko devices and the ARM Cortex-M3 can be found at the Silicon Labs and ARM web

pages:

www.silabs.com

www.arm.com

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 3

Page 5

2. System Overview

0 1 2 3 4

EFM32JG1 Reference Manual

System Overview

Quick Facts

What?

The EFM32 Jade Gecko is a highly integrated, configurable and low power MCU with a complete set of

peripherals.

Why?

EFM32 Jade Gecko features an Cortex-M3 core, a

unique cryptographic hardware engine supporting

AES, ECC, and SHA, ultra-low current active mode,

and short wake-up time from energy-saving modes.

How?

EFM32 Jade Gecko microcontrollers are well suited

for any batter-powered application, as well as other

systems requiring high performance and low-energy

consumption

2.1 Introduction

The EFM32 MCUs are the world’s most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM CortexM3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32

Jade Gecko microcontroller is well suited for any battery operated application as well as other systems requiring high performance and

low-energy consumption.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 4

Page 6

EFM32JG1 Reference Manual

System Overview

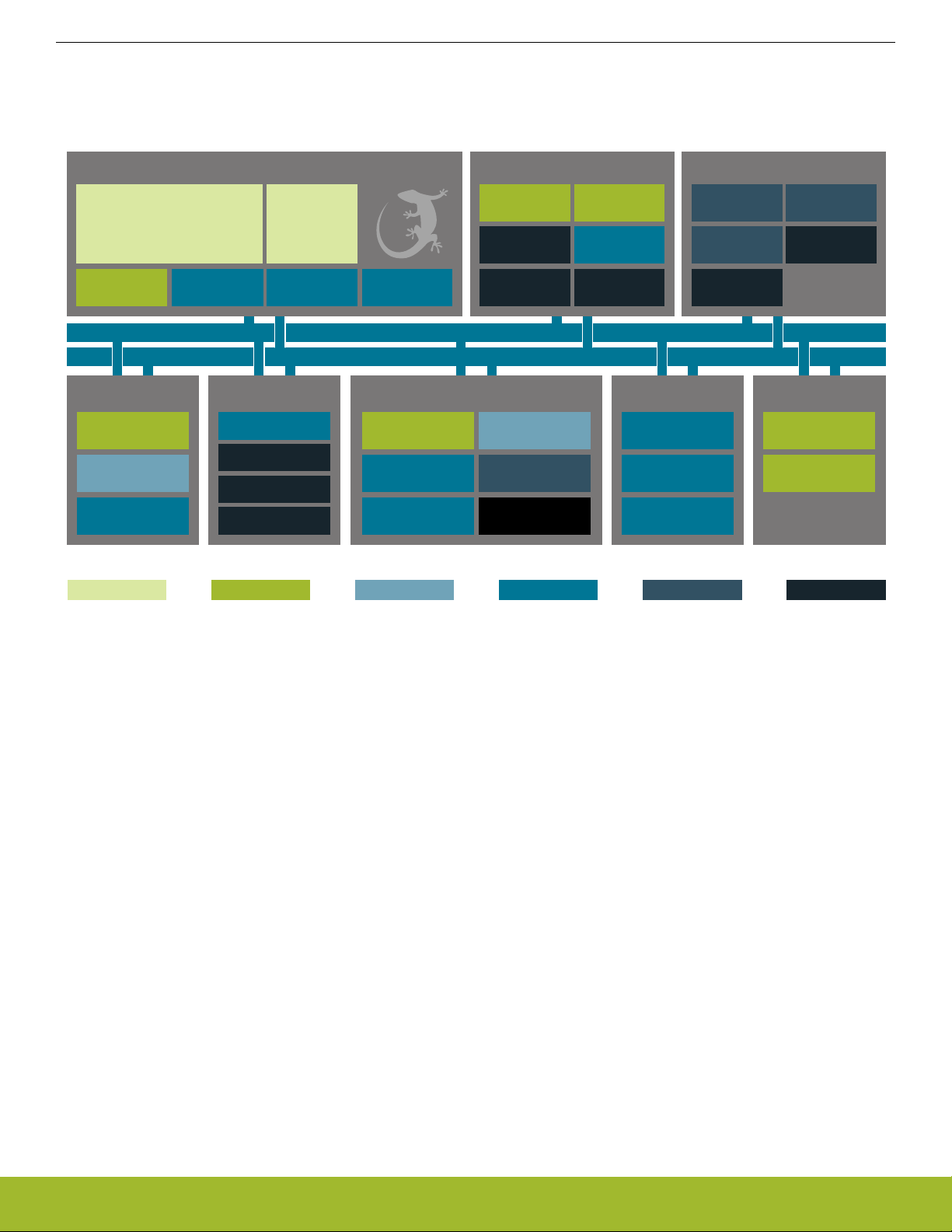

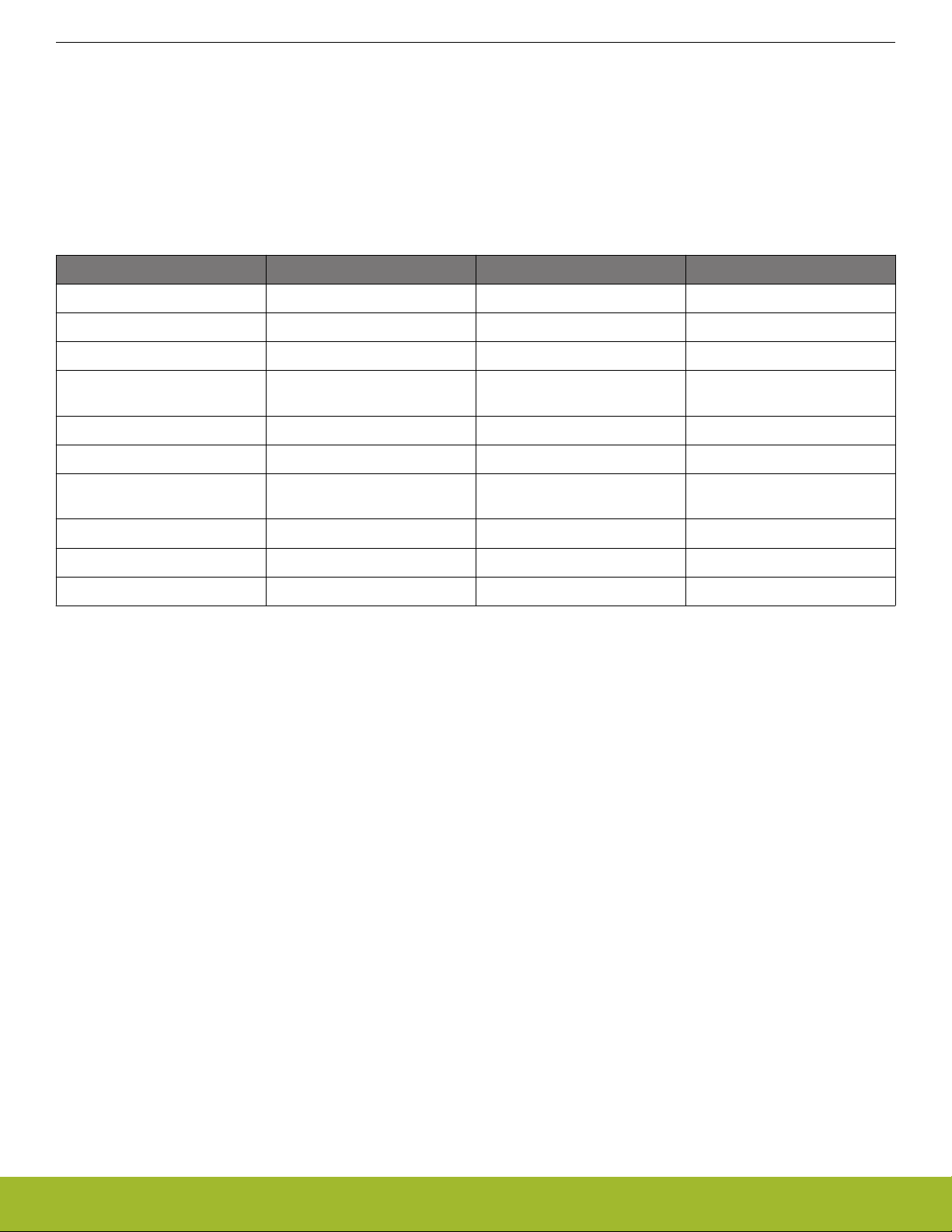

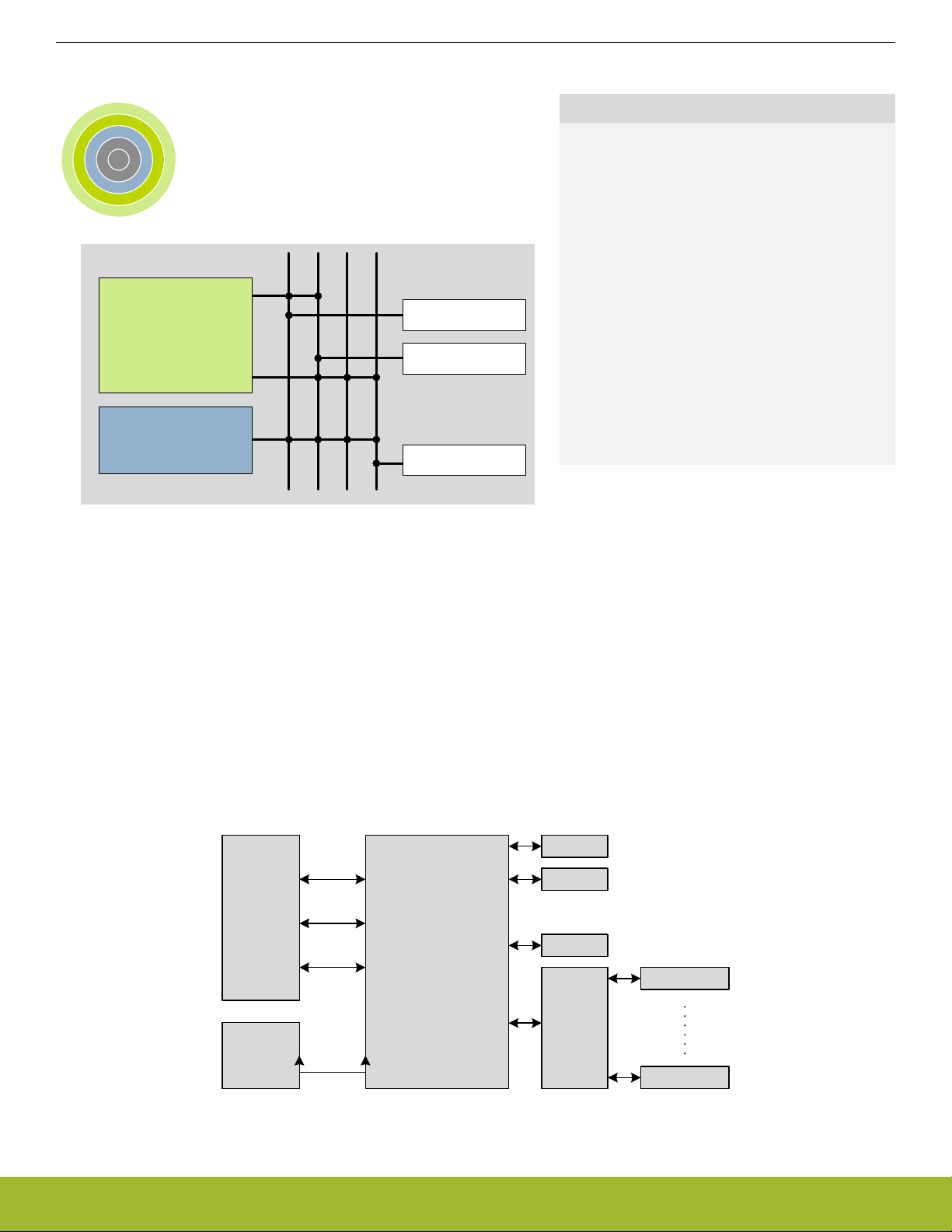

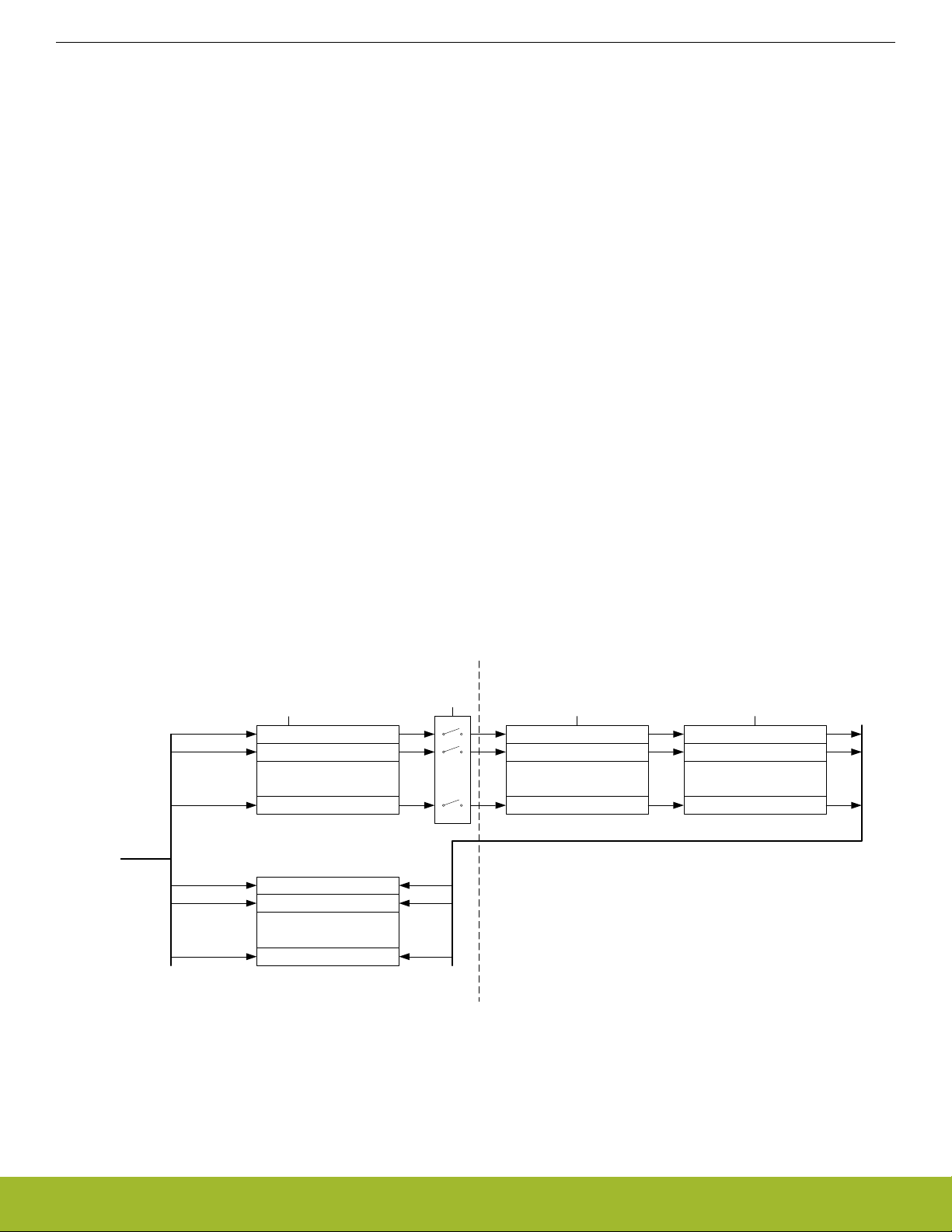

2.2 Block Diagrams

The block diagram for the EFM32 Jade Gecko MCU series is shown in (Figure 2.1 EFM32 Jade Gecko System-On-Chip Block Diagram

on page 5).

Core / Memory

ARM Cortex

Flash Program

Memory

TM

M3 processor

RAM Memory

Serial Interfaces

USART

Low Energy UART

I

TM

2

C

Lowest power mode with peripheral operational:

EM0 - Active

External Interrupts

General Purpose I/O

Pin Wakeup

EM1 - Sleep

Memory

Protection Unit

Debug Interface DMA Controller

I/O Ports Timers and Triggers

Pin Reset

Clock Management

High Frequency

Crystal

Oscillator

Low Frequency

RC Oscillator

Low Frequency

Crystal

Oscillator

32-bit bus

Peripheral Reflex System

Timer/Counter Low Energy Timer

Pulse Counter

Watchdog Timer

EM2 – Deep Sleep

Real Time Counter

and Calendar

CRYOTIMER

EM3 - Stop

High Frequency

RC Oscillator

Auxiliary High

Frequency RC

Oscillator

Ultra Low

Frequency RC

Oscillator

Analog Interfaces

Analog Comparator

Energy Management

Voltage

Regulator

Converter

Brown-Out

Detector

ADC

IDAC

EM4 - Hibernate

DC-DC

Voltage Monitor

Power-On Reset

Other

CRYPTO

CRC

EM4 - Shutoff

Figure 2.1. EFM32 Jade Gecko System-On-Chip Block Diagram

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 5

Page 7

EFM32JG1 Reference Manual

System Overview

2.3 MCU Features overview

• ARM Cortex-M3 CPU platform

• High Performance 32-bit processor @ up to 40 MHz

• Memory Protection Unit

• Wake-up Interrupt Controller

• Flexible Energy Management System

• Power routing configurations including DCDC control

• Voltage Monitoring and Brown Out Detection

• State Retention

• 256 KB Flash

• 32 KB RAM

• Up to 32 General Purpose I/O pins

• Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

• Configurable peripheral I/O locations

• 16 asynchronous external interrupts

• Output state retention and wake-up from Shutoff Mode

• 8 Channel DMA Controller

• Alternate/primary descriptors with scatter-gather/ping-pong operation

• 12 Channel Peripheral Reflex System

• Autonomous inter-peripheral signaling enables smart operation in low energy modes

• CRYPTO Advanced Encryption Standard Accelerator

• AES encryption / decryption, with 128 or 256 bit keys

• Multiple AES modes of operation, including Counter (CTR), Galois/Counter Mode (GCM), Cipher Block Chaining (CBC), Cipher

Feedback (CFB) and Output Feedback (OFB).

• Accelerated SHA-1 and SHA-2

• Accelerated Elliptic Curve Cryptography (ECC), with binary or prime fields

• Flexible 256-bit ALU and sequencer

• General Purpose Cyclic Redundancy Check

• Programmable 16-bit polynomial, fixed 32-bit polynomial

• Communication interfaces

• 2×Universal Synchronous/Asynchronous Receiver/Transmitter

• UART/SPI/SmartCard (ISO 7816)/IrDA/I2S

• Triple buffered full/half-duplex operation

• Hardware flow control

• 4-16 data bits

• 1× Low Energy UART

• Autonomous operation with DMA in Deep Sleep Mode

•

1×I2C Interface with SMBus support

• Address recognition in Stop Mode

• Timers/Counters

• 2× 16-bit Timer/Counter

• 3 or 4 Compare/Capture/PWM channels

• Dead-Time Insertion on TIMER0

• 16-bit Low Energy Timer

• 32-bit Ultra Low Energy Timer/Counter (CRYOTIMER) for periodic wake-up from any Energy Mode

• 32-bit Real-Time Counter and Calendar

• 16+16+32 bit Protocol Timer

• 16-bit Pulse Counter

• Asynchronous pulse counting/quadrature decoding

• Watchdog Timer with dedicated RC oscillator @ 50 nA

• Ultra low power precision analog peripherals

• 12-bit 1 Msamples/s Analog to Digital Converter

• 8 input channels and on-chip temperature sensor

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 6

Page 8

EFM32JG1 Reference Manual

System Overview

• Single ended or differential operation

• Conversion tailgating for predictable latency

• Current Digital to Analog Converter

• Source or sink a configurable constant current

• 2× Analog Comparator

• Programmable speed/current

• Capacitive sensing with up to 8 inputs

• Analog Port

• Ultra efficient Power-on Reset and Brown-Out Detector

• Debug Interface

• 4-pin Joint Test Action Group (JTAG) interface

• 2-pin serial-wire debug (SWD) interface

2.4 Oscillators and Clocks

EFM32 Jade Gecko has six different oscillators integrated, as shown in Table 2.1 EFM32 Jade Gecko Oscillators on page 7

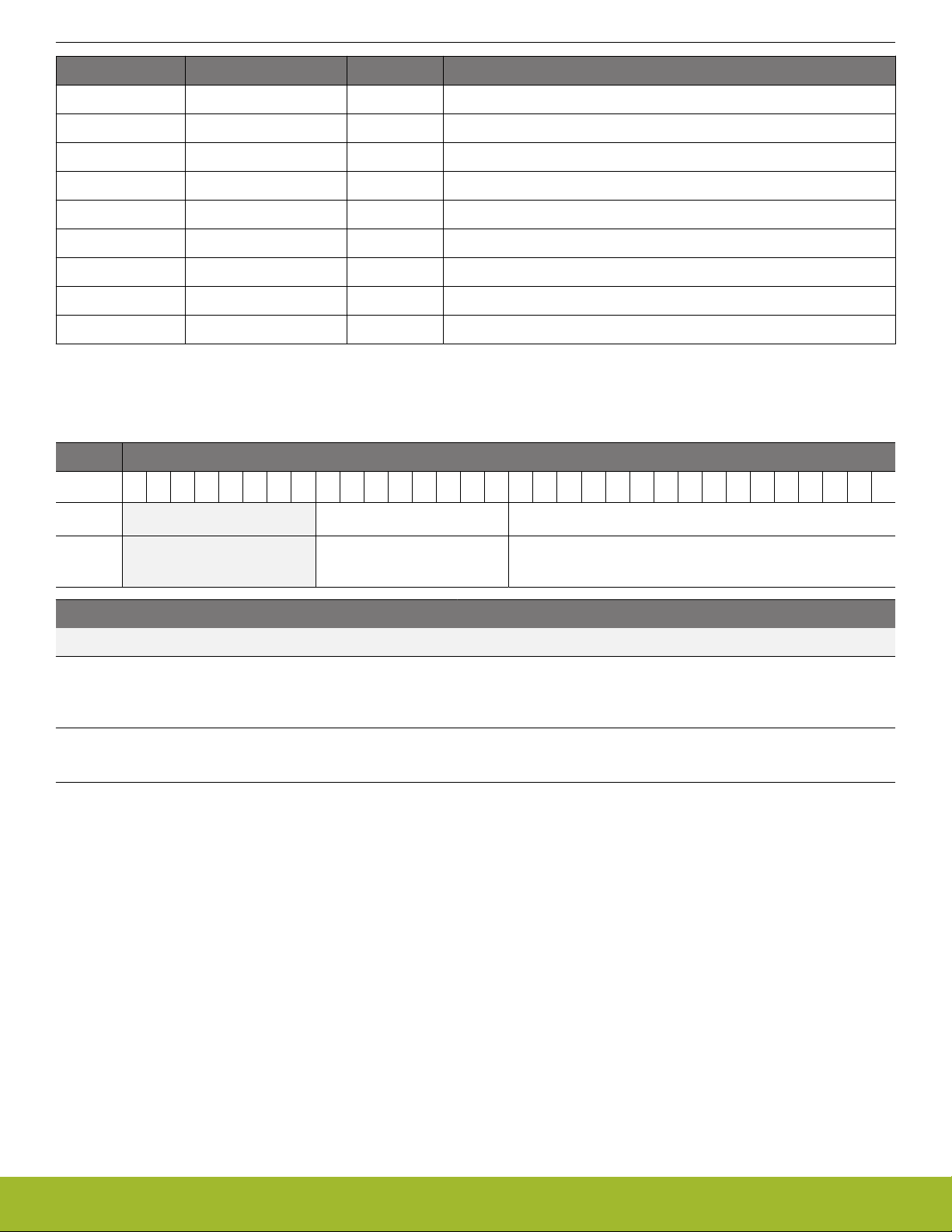

Table 2.1. EFM32 Jade Gecko Oscillators

Oscillator Frequency Optional? External

Description

components

HFXO 38 MHz - 40 MHz No Crystal High accuracy, low jitter high frequency crystal oscillator. Tun-

able crystal loading capacitors are fully integrated.

HFRCO 1 MHz - 38 MHz No - Medium accuracy RC oscillator, typically used for timing dur-

ing startup of the HFXO or if a precise oscillator is not required.

AUXHFRCO 1 MHz - 38 MHz No - Medium accuracy RC oscillator, typically used as alternative

clock source for Analog to Digital Converter or Debug Trace.

LFRCO 32768 Hz No - Medium accuracy frequency reference typically used for medi-

um accuracy RTCC timing.

LFXO 32768 Hz Yes Crystal High accuracy frequency reference typically used for high ac-

curacy RTCC timing. Tunable crystal loading capacitors are

fully integrated.

ULFRCO 1000 Hz No - Ultra low frequency oscillator typically used for the watchdog

timer.

The RC oscillators can be calibrated against either of the crystal oscillators in order to compensate for temperature and voltage supply

variations. Hardware support is included to measure the frequency of various oscillators against each other.

Oscillator and clock management is available through the Clock Management Unit (CMU), see section 10. CMU - Clock Management

Unit for details.

2.5 Hardware CRC Support

EFM32 Jade Gecko supports a configurable CRC generation:

• 8, 16, 24 or 32 bit CRC value

• Configurable polynomial and initialization value

• Optional inversion of CRC value over air

• Configurable CRC byte ordering

• Support for multiple CRC values calculated and verified per transmitted or received frame

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 7

Page 9

EFM32JG1 Reference Manual

System Overview

2.6 Data Encryption and Authentication

EFM32 Jade Gecko has hardware support for AES encryption, decryption and authentication modes. These security operations can be

performed on data in RAM or any data buffer, without further CPU intervention. The key size is 128 bits.

AES modes of operations directly supported by the EFM32 Jade Gecko hardware are listed in Table 2.2 AES modes of operation with

hardware support on page 8. In addition to these modes, other modes can also be implemented by using combinations of modes.

For example, the CCM mode can be implemented using the CTR and CBC-MAC modes in combination.

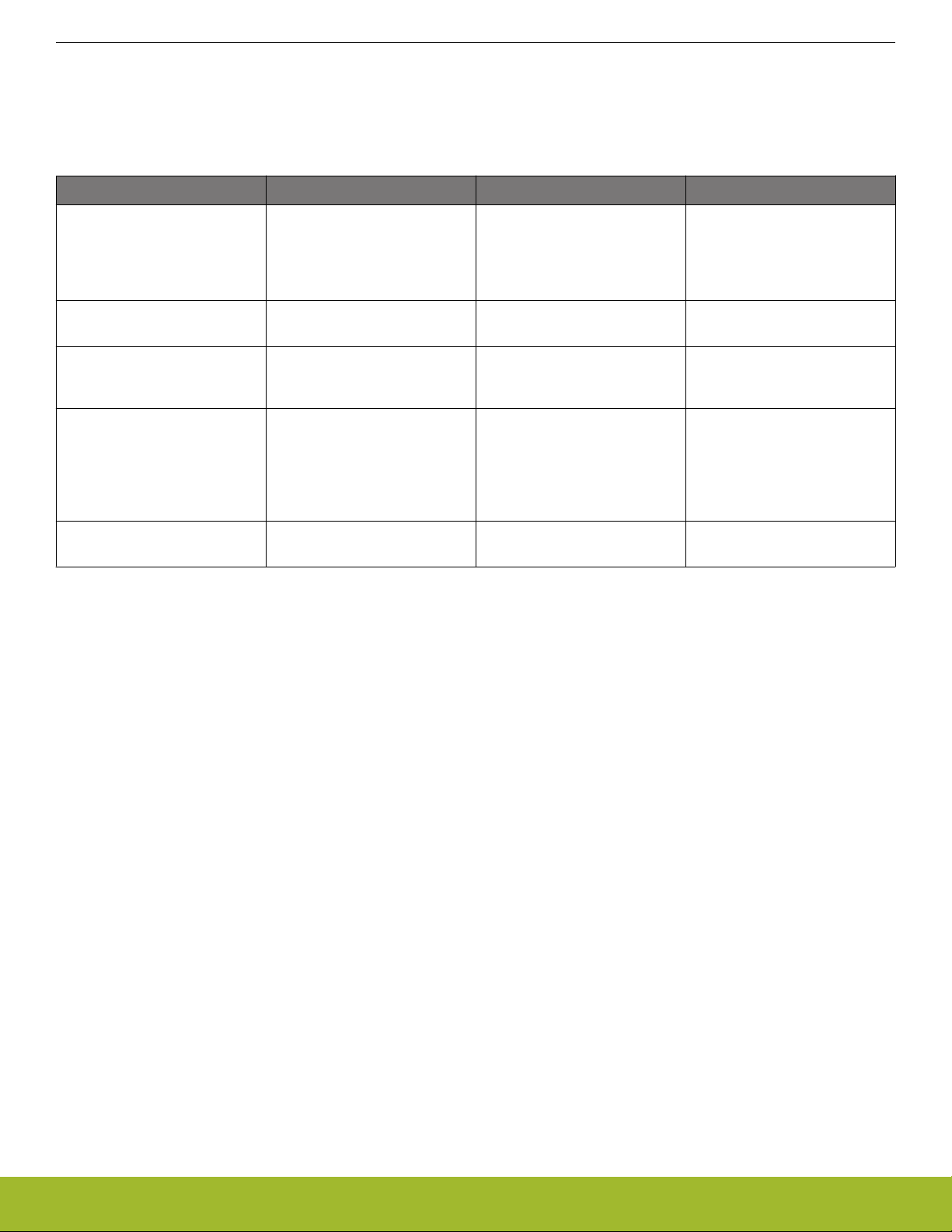

Table 2.2. AES modes of operation with hardware support

AES Mode Encryption / Decryption Authentication Comment

ECB Yes - Electronic Code Book

CTR Yes - Counter mode

CCM Yes Yes Counter with CBC-MAC

CCM* Yes Yes CCM with encryption-only and

integrity-only capabilities

GCM Yes Yes Galois Counter Mode

CBC Yes - Cipher Block Chaining

CBC-MAC - Yes Cipher Block Chaining, Mes-

sage Authentication Code

CMAC - Yes Cipher-basec MAC

CFB Yes - Cipher Feedback

OFB Yes - Output Feedback

The CRYPTO module can provide data directly from the embedded Cortex-M3 or via DMA.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 8

Page 10

EFM32JG1 Reference Manual

System Overview

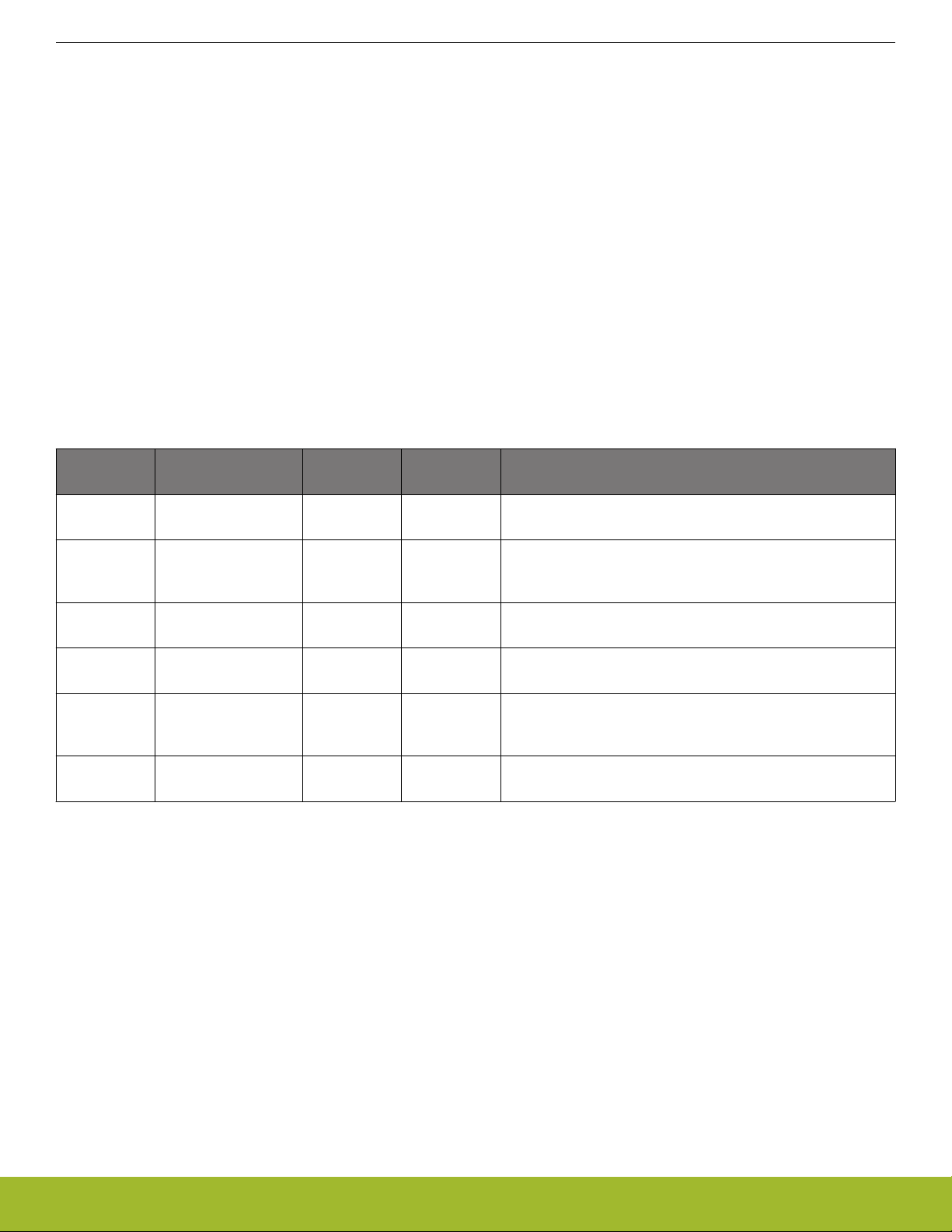

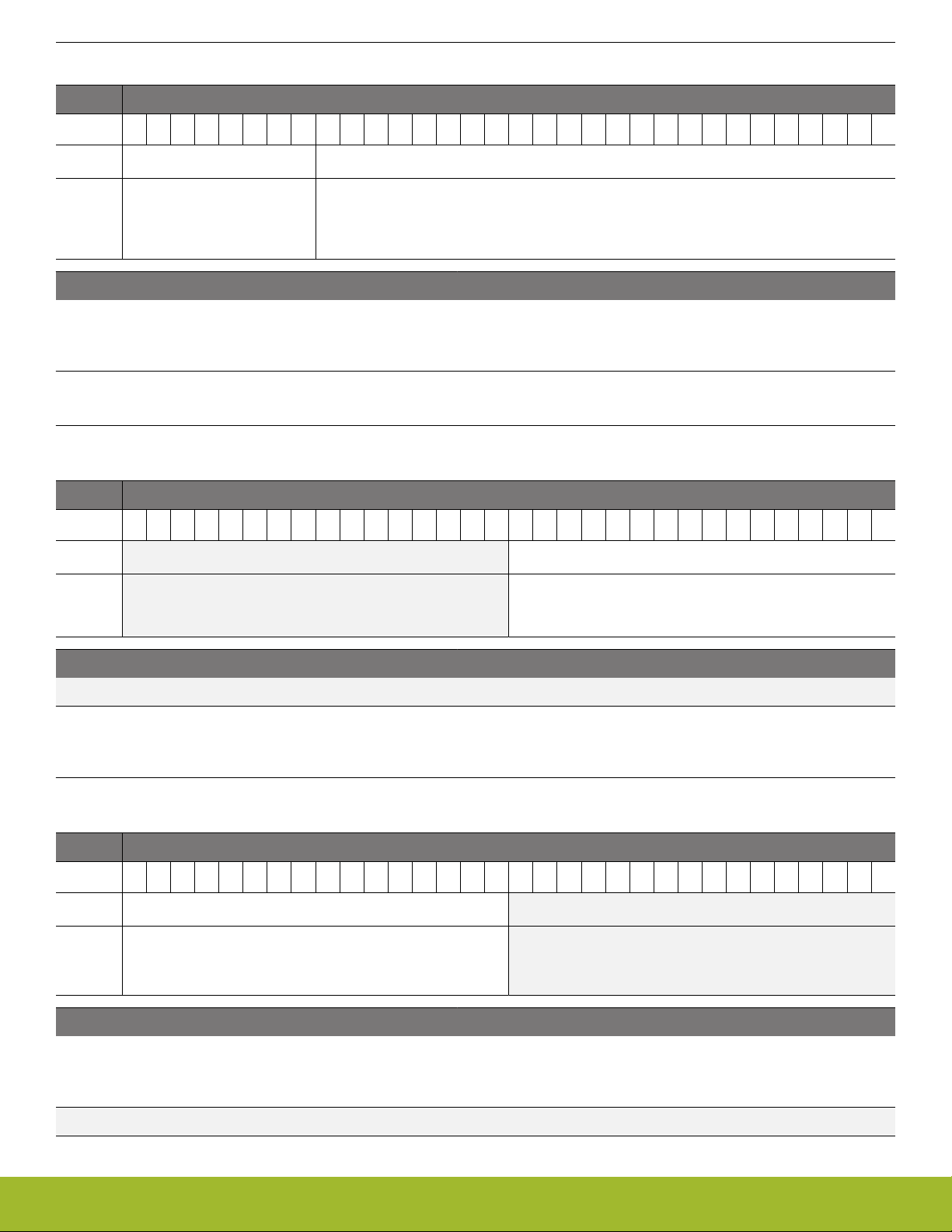

2.7 Timers

EFM32 Jade Gecko includes multiple timers, as can be seen from Table 2.3 EFM32 Jade Gecko Timers Overview on page 9.

Table 2.3. EFM32 Jade Gecko Timers Overview

Timer Number of instances Typical clock source Overview

RTCC 1 Low frequency (LFXO or

LFRCO)

32 bit Real Time Counter and

Calendar, typically used to accurately time inactive periods

and enable wakeup on compare

match.

TIMER 2 High frequency (HFXO or

16 bit general purpose timer.

HFRCO)

Systick timer 1 High frequency (HFXO or

HFRCO)

32 bit systick timer integrated in

the Cortex-M3. Typically used

as an Operating System timer.

WDOG 1 Low frequency (LFXO, LFRCO

or ULFRCO)

Watch dog timer. Once enabled,

this module must be periodically

accessed. If not, this is considered an error and the EFM32

Jade Gecko is reset in order to

recover the system.

LETIMER 1 Low frequency (LFXO, LFRCO

or ULFRCO)

Low energy general purpose

timer.

Advanced interconnect features allows synchronization between timers. This includes:

• Start / stop any high frequency timer synchronized with the RTCC

• Trigger RSM state transitions based on compare timer compare match, for instance to provide clock cycle accuracy on frame transmit timing

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 9

Page 11

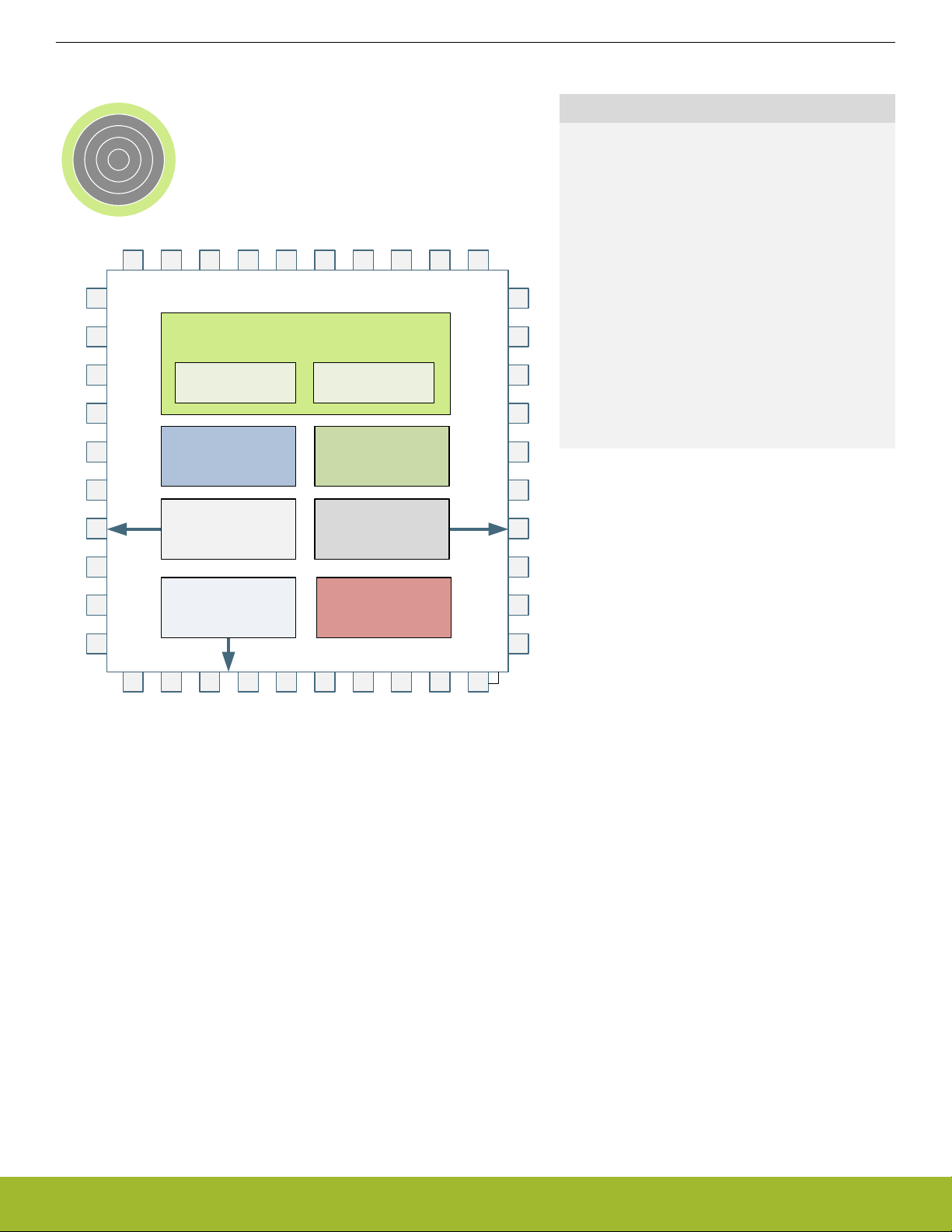

3. System Processor

0 1 2 3 4

CM3Core

Hardware divider

Control Logic

32-bit ALU

32-bit multiplier

Thumb & Thumb-2

Single cycle

Decode

EFM32JG1 Reference Manual

System Processor

Quick Facts

What?

The industry leading Cortex-M3 processor from

ARM is the CPU in the EFM32 Jade Gecko devices.

Why?

The ARM Cortex-M3 is designed for exceptionally

short response time, high code density, and high 32bit throughput while maintaining a strict cost and

power consumption budget.

How?

Combined with the ultra low energy peripherals

available in EFM32 Jade Gecko devices, the CortexM3 processor's Harvard architecture, 3 stage pipeline, single cycle instructions, Thumb-2 instruction

set support, and fast interrupt handling make it perfect for 8-bit, 16-bit, and 32-bit applications.

Instruction Interface Data Interface

NVIC Interface

Memory Protection Unit

3.1 Introduction

The ARM Cortex-M3 32-bit RISC processor provides outstanding computational performance and exceptional system response to interrupts while meeting low cost requirements and low power consumption.

The ARM Cortex-M3 implemented is revision r2p1.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 10

Page 12

EFM32JG1 Reference Manual

System Processor

3.2 Features

• Harvard architecture

• Separate data and program memory buses (No memory bottleneck as in a single bus system)

• 3-stage pipeline

• Thumb-2 instruction set

• Enhanced levels of performance, energy efficiency, and code density

• Single cycle multiply and hardware divide instructions

• 32-bit multiplication in a single cycle

• Signed and unsigned divide operations between 2 and 12 cycles

• Atomic bit manipulation with bit banding

• Direct access to single bits of data

• Two 1MB bit banding regions for memory and peripherals mapping to 32MB alias regions

• Atomic operation, cannot be interrupted by other bus activities

• 1.25 DMIPS/MHz

• Memory Protection Unit

• Up to 8 protected memory regions

• 24 bits System Tick Timer for Real Time OS

• Excellent 32-bit migration choice for 8/16 bit architecture based designs

• Simplified stack-based programmer's model is compatible with traditional ARM architecture and retains the programming simplicity of legacy 8-bit and 16-bit architectures

• Alligned or unaligned data storage and access

• Contiguous storage of data requiring different byte lengths

• Data access in a single core access cycle

• Integrated power modes

• Sleep Now mode for immediate transfer to low power state

• Sleep on Exit mode for entry into low power state after the servicing of an interrupt

• Ability to extend power savings to other system components

• Optimized for low latency, nested interrupts

3.3 Functional Description

For a full functional description of the ARM Cortex-M3 implementation in the EFM32 Jade Gecko family, the reader is referred to the

ARM Cortex-M3 documentation.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 11

Page 13

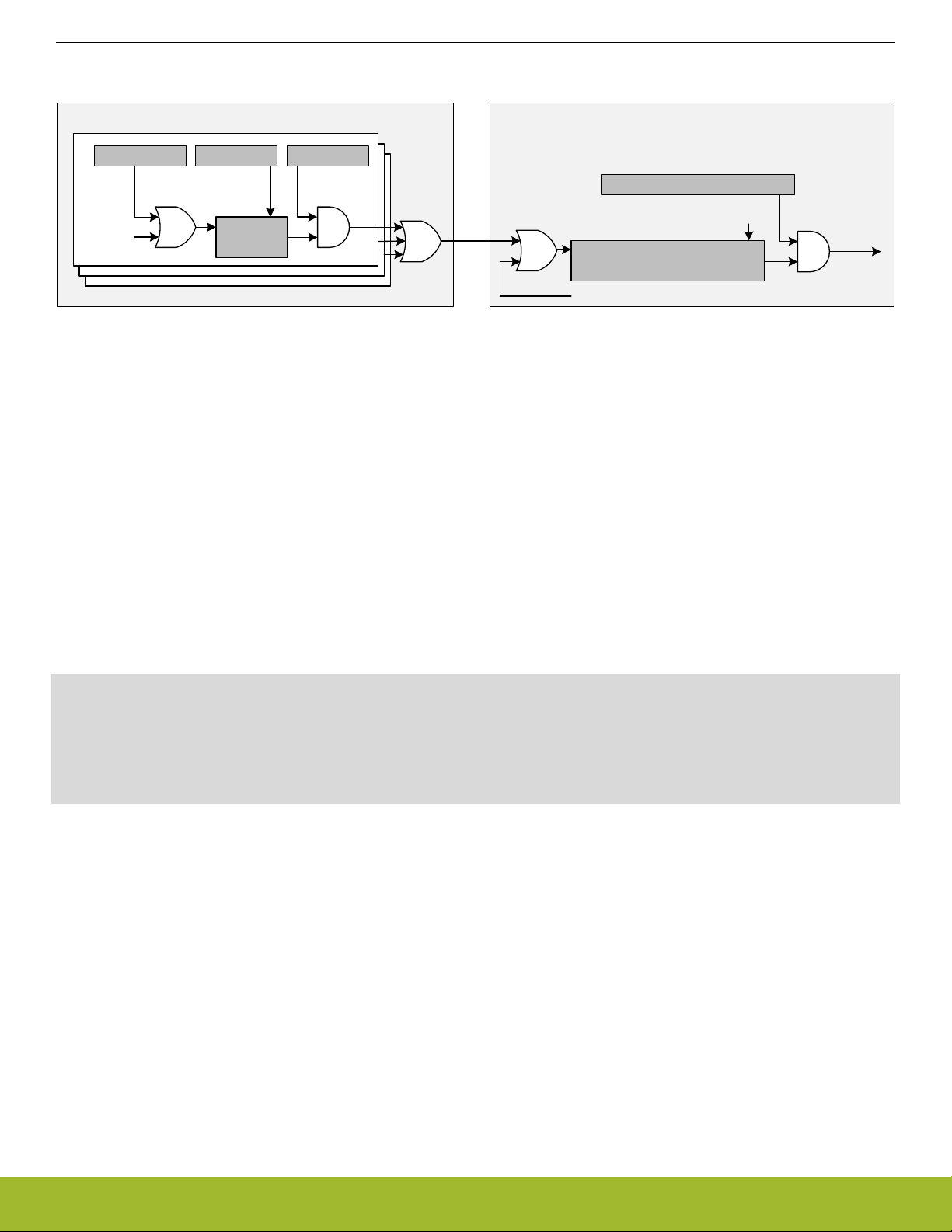

3.3.1 Interrupt Operation

Module Cortex-M4 NVIC

EFM32JG1 Reference Manual

System Processor

IFS[n] IFC[n]

IEN[n]

SETENA[n]/CLRENA[n]

Interrupt

condition

set clear

IF[n]

Active interrupt

IRQ

set clear

Interrupt

request

SETPEND[n]/CLRPEND[n]

Software generated interrupt

Figure 3.1. Interrupt Operation

The interrupt request (IRQ) lines are connected to the Cortex-M3. Each of these lines (shown in Table 3.1 Interrupt Request Lines (IRQ)

on page 13) is connected to one or more interrupt flags in one or more modules. The interrupt flags are set by hardware on an inter-

rupt condition. It is also possible to set/clear the interrupt flags through the IFS/IFC registers. Each interrupt flag is then qualified with its

own interrupt enable bit (IEN register), before being OR'ed with the other interrupt flags to generate the IRQ. A high IRQ line will set the

corresponding pending bit (can also be set/cleared with the SETPEND/CLRPEND bits in ISPR0/ICPR0) in the Cortex-M3 NVIC. The

pending bit is then qualified with an enable bit (set/cleared with SETENA/CLRENA bits in ISER0/ICER0) before generating an interrupt

request to the core. Figure 3.1 Interrupt Operation on page 12 illustrates the interrupt system. For more information on how the interrupts are handled inside the Cortex-M3, the reader is referred to the EFM32 Cortex-M3 Reference Manual.

3.3.1.1 Avoiding Extraneous Interrupts

There can be latencies in the system such that clearing an interrupt flag could take longer than leaving an Interrupt Service Routine

(ISR). This can lead to the ISR being re-entered as the interrupt flag has yet to clear immediately after leaving the ISR. To avoid this,

when clearing an interrupt flag at the end of an ISR, the user should execute ARM's Data Synchronization Barrier (DSB) instruction.

Another approach is to clear the interrupt flag immediately after identifying the interrupt source and then service the interrupt as shown

in the pseudo-code below. The ISR typically is sufficiently long to more than cover the few cycles it may take to clear the interrupt status, and also allows the status to be checked for further interrupts before exiting the ISR.

irqXServiceRoutine() {

do {

clearIrqXStatus();

serviceIrqX();

} while(irqXStatusIsActive());

}

3.3.1.2 IFC Read-clear Operation

In addition to the normal interrupt setting and clearing operations via the IFS/IFC registers, there is an additional atomic Read-clear

operation that can be enabled by setting IFCREADCLEAR=1 in the MSC_CTRL register. When enabled, reads of peripheral IFC registers will return the interrupt vector (mirroring the IF register), while at the same time clearing whichever interrupt flags are set. This operation is functionally equivalent to reading the IF register and then writing the result immediately back to the IFC register.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 12

Page 14

3.3.2 Interrupt Request Lines (IRQ)

Table 3.1. Interrupt Request Lines (IRQ)

IRQ # Source

0 EMU

2 WDOG0

8 LDMA

9 GPIO_EVEN

10 TIMER0

11 USART0_RX

12 USART0_TX

13 ACMP0

14 ADC0

15 IDAC0

EFM32JG1 Reference Manual

System Processor

16 I2C0

17 GPIO_ODD

18 TIMER1

19 USART1_RX

20 USART1_TX

21 LEUART0

22 PCNT0

23 CMU

24 MSC

25 CRYPTO

26 LETIMER0

29 RTCC

31 CRYOTIMER

33 FPUEH

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 13

Page 15

4. Memory and Bus System

0 1 2 3 4

ARM Cortex-M

DMA Controller

Flash

RAM

Peripherals

EFM32JG1 Reference Manual

Memory and Bus System

Quick Facts

What?

A low latency memory system including low energy

Flash and RAM with data retention which makes the

energy modes attractive.

Why?

RAM retention reduces the need for storing data in

Flash and enables frequent use of the ultra low energy modes EM2 DeepSleep and EM3 Stop.

How?

Low energy and non-volatile Flash memory stores

program and application data in all energy modes

and can easily be reprogrammed in system. Low

leakage RAM with data retention in EM0 Active to

EM3 Stop removes the data restore time penalty,

and the DMA ensures fast autonomous transfers

with predictable response time.

4.1 Introduction

The EFM32 Jade Gecko contains an AMBA AHB Bus system to allow bus masters to access the memory mapped address space. A

multilayer AHB bus matrix connects the 4 master bus interfaces to the AHB slaves (Figure 4.1 EFM32 Jade Gecko Bus System on

page 14). The bus matrix allows several AHB slaves to be accessed simultaneously. An AMBA APB interface is used for the peripher-

als, which are accessed through an AHB-to-APB bridge connected to the AHB bus matrix. The 4 AHB bus masters are:

• Cortex-M3 ICode: Used for instruction fetches from Code memory (valid address range: 0x00000000 - 0x1FFFFFFF)

• Cortex-M3 DCode: Used for debug and data access to Code memory (valid address range: 0x00000000 - 0x1FFFFFFF)

• Cortex-M3 System: Used for data and debug access to system space. It can access entire memory space except Code memory

(valid address range: 0x20000000 - 0xFFFFFFFF)

• DMA: Can access entire memory space except internal core memory region and Code memory (valid address range: 0x20000000 0xDFFFFFFF)

ARM

Cortex-M

DMA

ICode

DCode

System

AHB Multilayer

Bus Matrix

Flash

RAM

CRYPTO

AHB/

APB

Bridge

Peripheral 0

Peripheral n

Figure 4.1. EFM32 Jade Gecko Bus System

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 14

Page 16

EFM32JG1 Reference Manual

Memory and Bus System

4.2 Functional Description

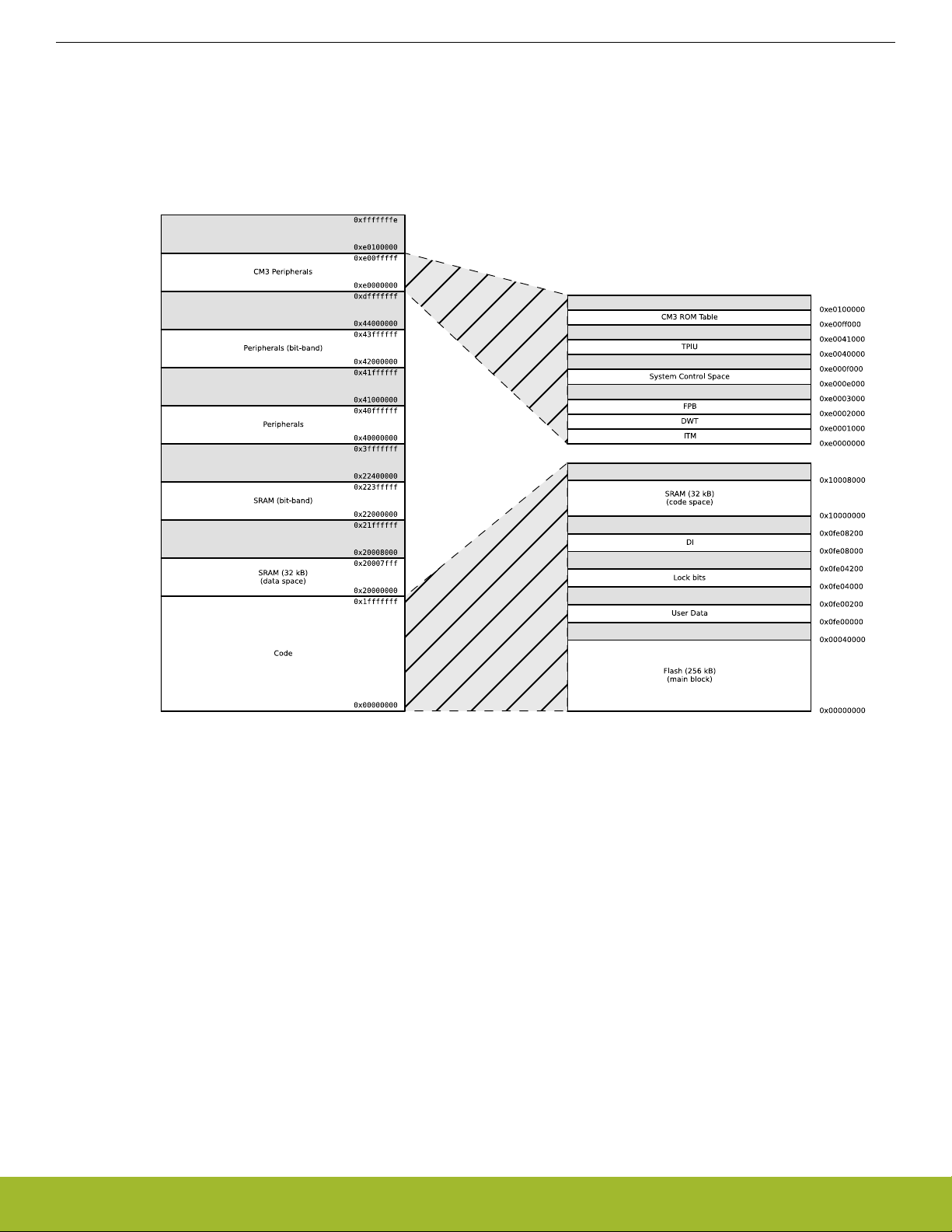

The memory segments are mapped together with the internal segments of the Cortex-M3 into the system memory map shown by Fig-

ure 4.2 System Address Space with Core and Code Space Listing on page 15.

Figure 4.2. System Address Space with Core and Code Space Listing

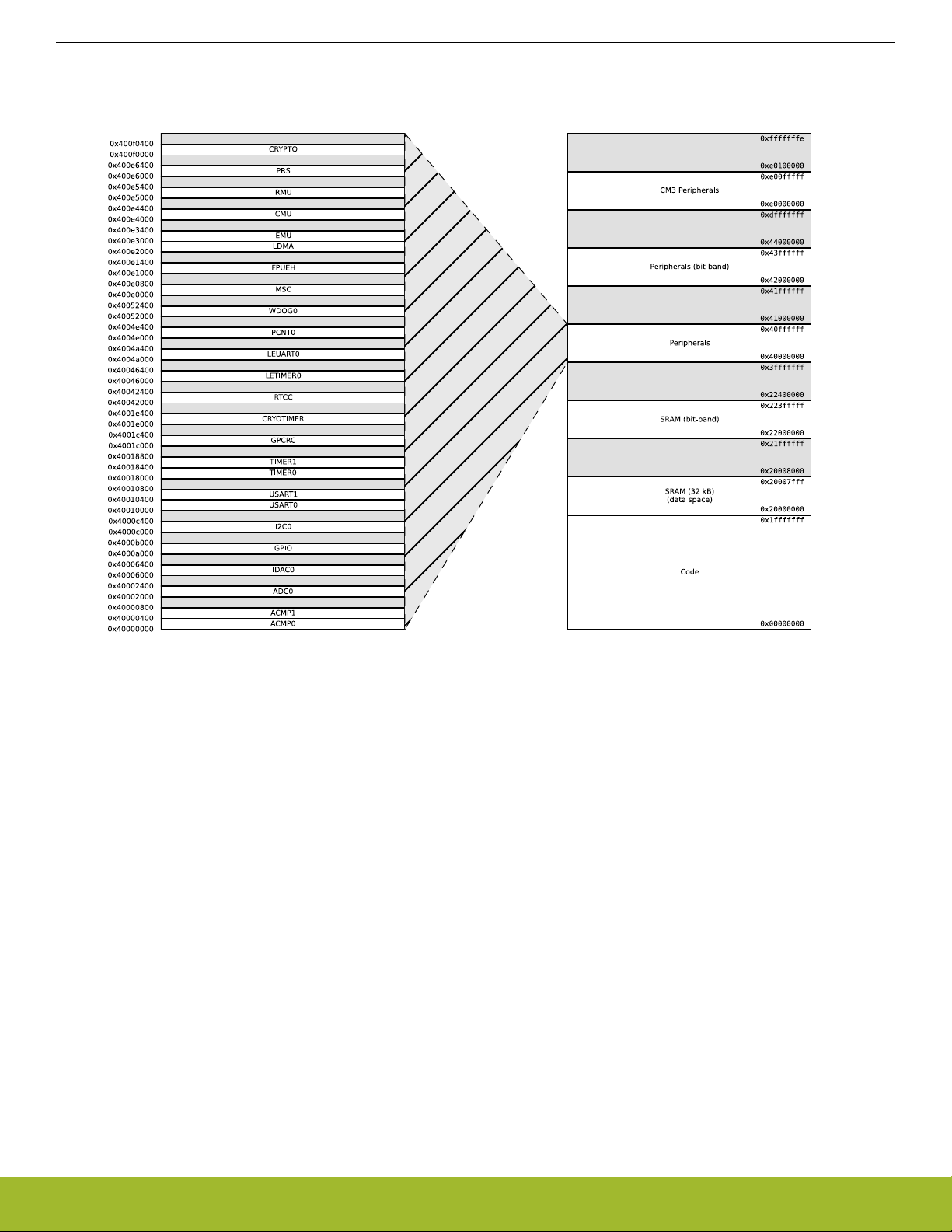

Additionally, the peripheral address map is detailed by Figure 4.3 System Address Space with Peripheral Listing on page 16.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 15

Page 17

EFM32JG1 Reference Manual

Memory and Bus System

Figure 4.3. System Address Space with Peripheral Listing

The embedded SRAM is located at address 0x20000000 in the memory map of the EFM32 Jade Gecko. When running code located in

SRAM starting at this address, the Cortex-M3 uses the System bus interface to fetch instructions. This results in reduced performance

as the Cortex-M3 accesses stack, other data in SRAM and peripherals using the System bus interface. To be able to run code from

SRAM efficiently, the SRAM is also mapped in the code space at address 0x10000000. When running code from this space, the CortexM3 fetches instructions through the I/D-Code bus interface, leaving the System bus interface for data access. The SRAM mapped into

the code space can however only be accessed by the CPU, i.e. not the DMA.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 16

Page 18

EFM32JG1 Reference Manual

Memory and Bus System

4.2.1 Bit-banding

The SRAM bit-band alias and peripheral bit-band alias regions are located at 0x22000000 and 0x42000000 respectively. Read and

write operations to these regions are converted into masked single-bit reads and atomic single-bit writes to the embedded SRAM and

peripherals of the EFM32 Jade Gecko.

Note: Bit-banding is only available through the CPU. No other AHB masters (e.g., DMA) can perform Bit-banding operations.

Using a standard approach to modify a single register or SRAM bit in the aliased regions, would require software to read the value of

the byte, half-word or word containing the bit, modify the bit, and then write the byte, half-word or word back to the register or SRAM

address. Using bit-banding, this can be done in a single operation, consuming only two bus cycles. As read-writeback, bit-masking and

bit-shift operations are not necessary in software, code size is reduced and execution speed improved.

The bit-band regions allow each bit in the SRAM and Peripheral areas of the memory map to be addressed. To set or clear a bit in the

embedded SRAM, write a 1 or a 0 to the following address:

bit_address = 0x22000000 + (address – 0x20000000) × 32 + bit × 4

where address is the address of the 32-bit word containing the bit to modify, and bit is the index of the bit in the 32-bit word.

To modify a bit in the Peripheral area, use the following address:

bit_address = 0x42000000 + (address – 0x40000000) × 32 + bit × 4

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 17

Page 19

EFM32JG1 Reference Manual

Memory and Bus System

4.2.2 Peripheral Bit Set and Clear

The EFM32 Jade Gecko supports bit set and bit clear access to all peripherals except those listed in Table 4.1 Peripherals that Do Not

Support Bit Set and Bit Clear on page 18. The bit set and bit clear functionality (also called Bit Access) enables modification of bit

fields (single bit or multiple bit wide) without the need to perform a read-modify-write (though it is functionally equivalent). Also, the operation is contained within a single bus access (for HF peripherals), unlike the Bit-banding operation described in section 4.2.1 Bit-

banding which consumes two bus accesses per operation. All AHB masters can utilize this feature.

The bit clear aliasing region starts at 0x44000000 and the bit set aliasing region starts at 0x46000000. Thus, to apply a bit set or clear

operation, write the bit set or clear mask to the following addresses:

bit_clear_address = address + 0x04000000

bit_set_address = address + 0x06000000

For bit set operations, bit locations that are 1 in the bit mask will be set in the destination register:

register = (register OR mask)

For bit clear operations, bit locations that are 1 in the bit mask will be cleared in the destination register:

register = (register AND (NOT mask))

Note: It is possible to combine bit clear and bit set operations in order to arbitrarily modify multi-bit register fields, without affecting other

fields in the same register. In this case, care should be taken to ensure that the field does not have intermediate values that can lead to

erroneous behavior. For example, if bit clear and bit set operations are used to change an analog tuning register field from 25 to 26, the

field would initially take on a value of zero. If the analog module is active at the time, this could lead to undesired behavior.

The peripherals listed in Table 4.1 Peripherals that Do Not Support Bit Set and Bit Clear on page 18 do not support Bit Access for any

registers. All other peripherals do support Bit Access, however, there may be cases of certain registers that do not support it. Such

registers have a note regarding this lack of support.

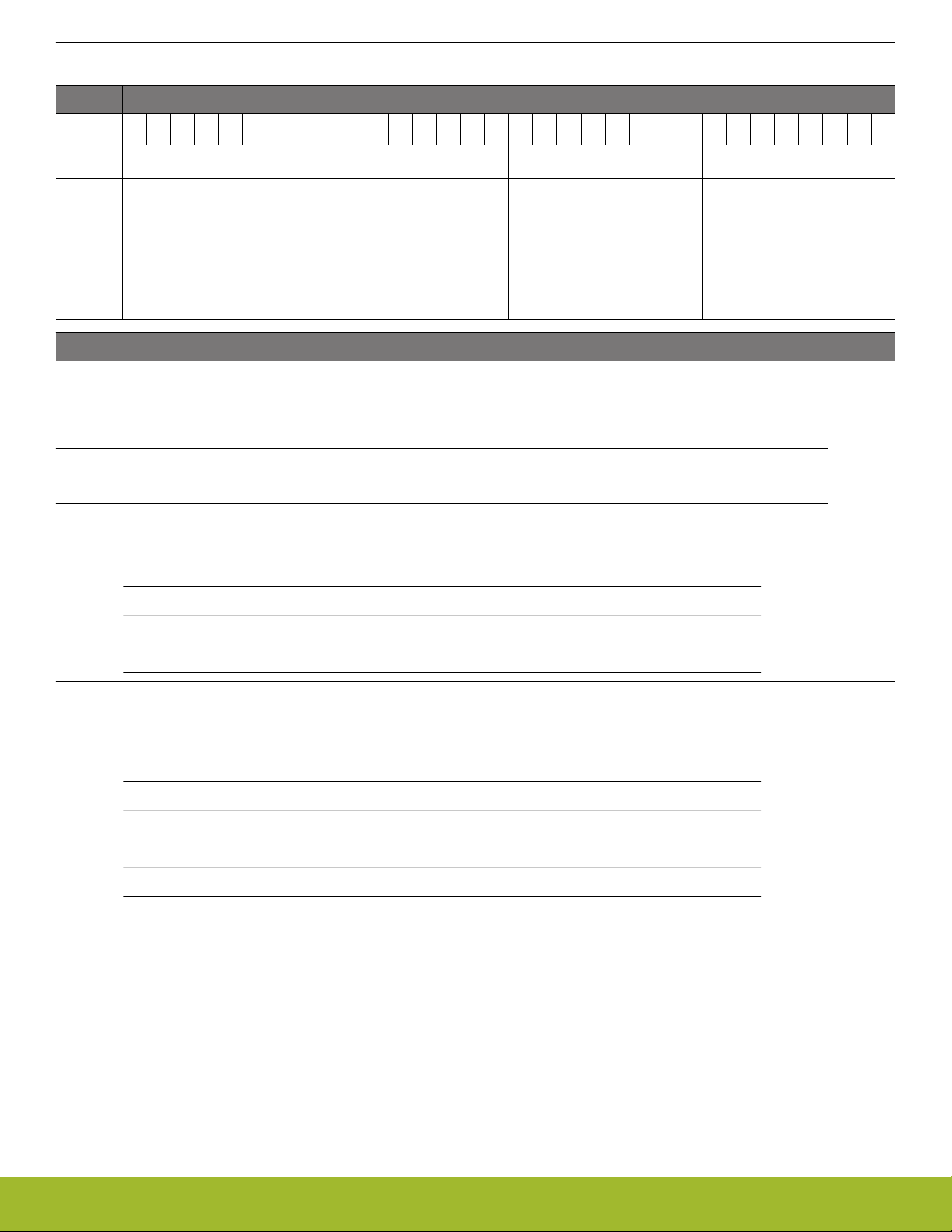

Table 4.1. Peripherals that Do Not Support Bit Set and Bit Clear

Module

EMU

RMU

CRYOTIMER

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 18

Page 20

EFM32JG1 Reference Manual

Memory and Bus System

4.2.3 Peripherals

The peripherals are mapped into the peripheral memory segment, each with a fixed size address range according to Table 4.2 Periph-

erals on page 19, Table 4.3 Low Energy Peripherals on page 19 , and Table 4.4 Core Peripherals on page 19.

Table 4.2. Peripherals

Address Range Module Name

0x400E6000 - 0x400E6400 PRS

0x4001E000 - 0x4001E400 CRYOTIMER

0x4001C000 - 0x4001C400 GPCRC

0x40018400 - 0x40018800 TIMER1

0x40018000 - 0x40018400 TIMER0

0x40010400 - 0x40010800 USART1

0x40010000 - 0x40010400 USART0

0x4000C000 - 0x4000C400 I2C0

0x4000A000 - 0x4000B000 GPIO

0x40006000 - 0x40006400 IDAC0

0x40002000 - 0x40002400 ADC0

0x40000400 - 0x40000800 ACMP1

0x40000000 - 0x40000400 ACMP0

Table 4.3. Low Energy Peripherals

Address Range Module Name

0x40052000 - 0x40052400 WDOG0

0x4004E000 - 0x4004E400 PCNT0

0x4004A000 - 0x4004A400 LEUART0

0x40046000 - 0x40046400 LETIMER0

0x40042000 - 0x40042400 RTCC

Table 4.4. Core Peripherals

Address Range Module Name

0x400F0000 - 0x400F0400 CRYPTO

0x400E2000 - 0x400E3000 LDMA

0x400E1000 - 0x400E1400 FPUEH

0x400E0000 - 0x400E0800 MSC

4.2.4 Bus Matrix

The Bus Matrix connects the memory segments to the bus masters as detailed in 4.1 Introduction.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 19

Page 21

EFM32JG1 Reference Manual

Memory and Bus System

4.2.4.1 Arbitration

The Bus Matrix uses a round-robin arbitration algorithm which enables high throughput and low latency, while starvation of simultaneous accesses to the same bus slave are eliminated. Round-robin does not assign a fixed priority to each bus master. The arbiter does

not insert any bus wait-states during peak interaction. However, one wait state is inserted for master accesses occurring after a prolonged inactive time. This wait state allows for increased power efficiency during master idle time.

4.2.4.2 Access Performance

The Bus Matrix is a multi-layer energy optimized AMBA AHB compliant bus with an internal bandwidth of 4x a single AHB interface.

The Bus Matrix accepts new transfers to be initiated by each master in each cycle without inserting any wait-states. However, the

slaves may insert wait-states depending on their internal throughput and the clock frequency.

The Cortex-M3, DMA Controller, and peripherals (not peripherals in the low frequency clock domain) run on clocks which can be prescaled separately. Clocks and prescaling are described in more detail in 10. CMU - Clock Management Unit .

In general, when accessing a peripheral, the latency in number of HFBUSCLK cycles, not including master arbitration, is given by:

where N

slave cycles

N

bus cycles

N

bus cycles

N

bus cycles

N

bus cycles

is the number of cycles required to access the particular slave, including any wait cycles introduced by the slave.

= (N

= (N

= N

= N

slave cycles

slave cycles

slave cycles

slave cycles

+ 1) × f

+ 1) × f

× f

HFBUSCLK/fHFPERCLK

× f

HFBUSCLK/fHFPERCLK

HFBUSCLK/fHFPERCLK

HFBUSCLK/fHFPERCLK

, best-case write accesses

+ 1, best-case read accesses

- 1, worst-case write accesses

, worst-case read accesses

Figure 4.4. Bus Access Latency (General Case)

Note that a latency of 1 cycle corresponds to 0 wait states.

Additionally, for back-to-back accesses to the same peripheral, the throughput in number of cycles per transfer is given by:

N

bus cycles

N

bus cycles

= N

= (N

slave cycles

slave cycles

× f

HFBUSCLK/fHFPERCLK

+ 1) × f

HFBUSCLK/fHFPERCLK

, write accesses

, read accesses

Figure 4.5. Bus Access Throughput (Back-to-Back Transfers)

Lastly, in the highest performing case, where HFPERCLK equals HFBUSCLK and the slave doesn't introduce any additional wait

states, the access latency in number of cycles is given by:

N

bus cycles

= 1, write accesses

N

bus cycles

= 2, read accesses

Figure 4.6. Bus Access Latency (Max Performance)

Note that the cycle counts in the equations above is in terms of the HFBUSCLK. When the core is prescaled from the bus clock, the

core will see a reduced number of latency cycles given by:

N

core cycles

= ceiling( N

bus cycles

× f

HFCORECLK/fHFBUSCLK

)

where master arbitration is not included.

Figure 4.7. Core Access Latency

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 20

Page 22

EFM32JG1 Reference Manual

Memory and Bus System

4.2.4.3 Bus Faults

System accesses from the core can receive a bus fault in the following condition(s):

• The core attempts to access an address that is not assigned to any peripheral or other system device. These faults can be enabled

or disabled by setting the ADDRFAULTEN bit appropriately in MSC_CTRL.

• The core attempts to access a peripheral or system device that has its clock disabled. These faults can be enabled or disabled by

setting the CLKDISFAULTEN bit appropriately in MSC_CTRL.

In addition to any condition-specific bus fault control bits, the bus fault interrupt itself can be enabled or disabled in the same way as all

other internal core interrupts.

4.3 Access to Low Energy Peripherals (Asynchronous Registers)

The Low Energy Peripherals are capable of running when the high frequency oscillator and core system is powered off, i.e. in energy

mode EM2 DeepSleep and in some cases also EM3 Stop. This enables the peripherals to perform tasks while the system energy consumption is minimal.

The Low Energy Peripherals are listed in Table 4.3 Low Energy Peripherals on page 19.

All Low Energy Peripherals are memory mapped, with automatic data synchronization. Because the Low Energy Peripherals are running on clocks asynchronous to the high frequency system clock, there are some constraints on how register accesses are performed,

as described in the following sections.

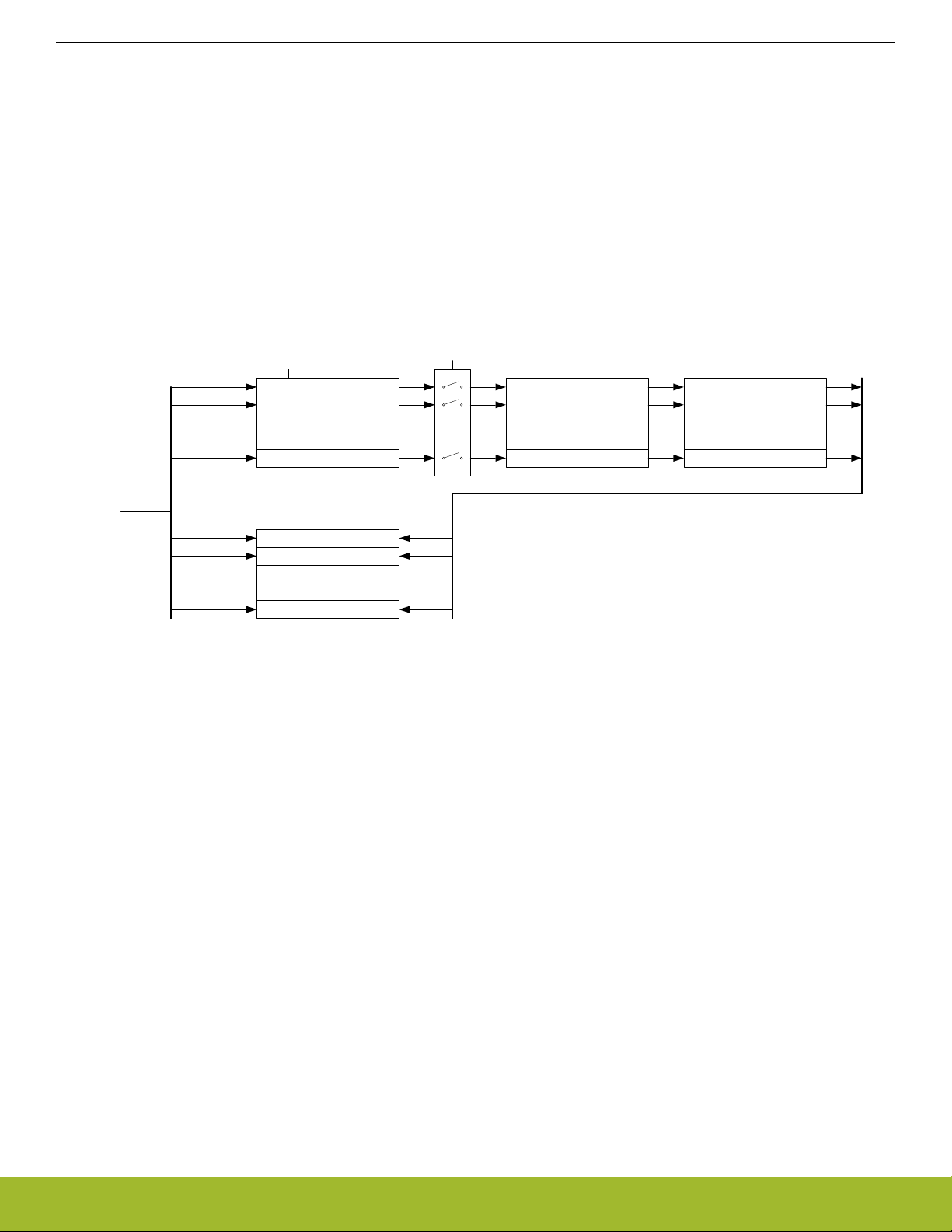

4.3.1 Writing

Every Low Energy Peripheral has one or more registers with data that needs to be synchronized into the Low Energy clock domain to

maintain data consistency and predictable operation. There are two different synchronization mechanisms on the EFM32JG1, immediate synchronization, and delayed synchronization. Immediate synchronization is available for the RTCC and LETIMER, and results in

an immediate update of the target registers. Delayed synchronization is used for the remaining Low Energy Peripherals, and for these

peripherals, a write operation requires 3 positive edges of the clock on the Low Energy Peripheral being accessed. Registers requiring

synchronization are marked "Async Reg" in their description header.

Note: On the Gecko series of devices, all LE peripherals are subject to delayed synchronization.

Write request [0:n]

High Frequency Clock Domain

High Frequency Clock

Write request 0

Write request 1

Write request n

Set 0

Set 1

Set n

Register 0

Register 1

.

.

.

Register n

Syncbusy Register 0

Syncbusy Register 1

.

.

.

Syncbusy Register n

Freeze

Clear 0

Clear 1

Clear n

Low Frequency Clock Domain

Low Frequency Clock Low Frequency Clock

Synchronizer 0

Synchronizer 1

.

.

.

Synchronizer n

Synchronization Done

Register 0 Sync

Register 1 Sync

Register n Sync

.

.

.

Figure 4.8. Write operation to Low Energy Peripherals

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 21

Page 23

EFM32JG1 Reference Manual

Memory and Bus System

4.3.1.1 Delayed Synchronization

After writing data to a register which value is to be synchronized into the Low Energy Peripheral using delayed synchronization, a corresponding busy flag in the <module_name>_SYNCBUSY register (e.g. LETIMER_SYNCBUSY) is set. This flag is set as long as synchronization is in progress and is cleared upon completion.

Note: Subsequent writes to the same register before the corresponding busy flag is cleared is not supported. Write before the busy flag

is cleared may result in undefined behavior. In general the SYNCBUSY register only needs to be observed if there is a risk of multiple

write access to a register (which must be prevented). It is not required to wait until the relevant flag in the SYNCBUSY register is

cleared after writing a register. E.g., EM2 DeepSleep can be entered directly after writing a register.

See Figure 4.9 Write operation to Low Energy Peripherals on page 22 for an overview of the writing mechanism operation.

Write request [0:n]

High Frequency Clock Domain

High Frequency Clock

Write request 0

Write request 1

Write request n

Set 0

Set 1

Set n

Register 0

Register 1

.

.

.

Register n

Syncbusy Register 0

Syncbusy Register 1

.

.

.

Syncbusy Register n

Freeze

Clear 0

Clear 1

Clear n

Low Frequency Clock Domain

Low Frequency Clock Low Frequency Clock

Synchronizer 0

Synchronizer 1

.

.

.

Synchronizer n

Synchronization Done

Register 0 Sync

Register 1 Sync

Register n Sync

.

.

.

Figure 4.9. Write operation to Low Energy Peripherals

4.3.1.2 Immediate Synchronization

In contrast to the peripherals with delayed synchronization, peripherals with immediate synchronization don't experience a delay from a

value is written to it takes effect in the peripheral. They are updated immediately on the peripheral write access. If such a write is done

close to an edge on the clock of the peripheral, the write is delayed to after the clock edge. This will introduce wait-states on the peripheral access.

Peripherals with immediate synchronization each have a SYNCBUSY register. Commands written to a peripheral with immediate synchronization are not executed before the first peripheral clock after the write. In this period, the SYNCBUSY flag for the command register is set, indicating that the command has not yet been performed. Secondly, to maintain compatibility with the Gecko series, the rest

of the SYNCBUSY registers are also present, but these are always 0, indicating that register writes are always safe.

Note: If compatibility with the Gecko series is a requirement for a given application, the rules that apply to delayed synchronization with

respect to SYNCBUSY should also be followed for the peripherals that support immediate synchronization.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 22

Page 24

EFM32JG1 Reference Manual

Memory and Bus System

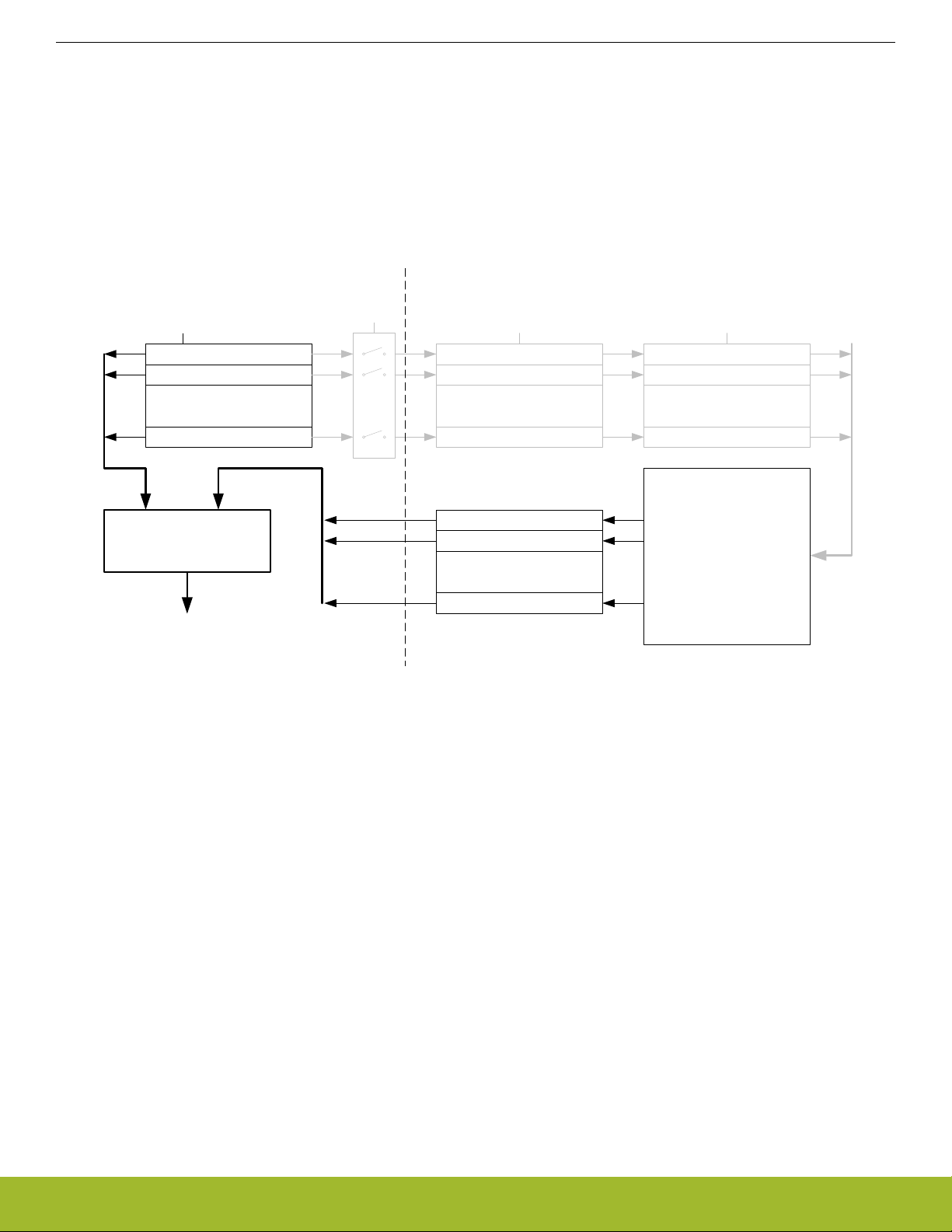

4.3.2 Reading

When reading from a Low Energy Peripheral, the data read is synchronized regardless if it originates in the Low Energy clock domain

or High Frequency clock domain. See Figure 4.10 Read operation from Low Energy Peripherals on page 23 for an overview of the

reading operation.

Note: Writing a register and then immediately reading the new value of the register may give the impression that the write operation is

complete. This may not be the case. Please refer to the SYNCBUSY register for correct status of the write operation to the Low Energy

Peripheral.

High Frequency Clock Domain Low Frequency Clock Domain

High Frequency Clock

Freeze

Low Frequency Clock Low Frequency Clock

Register 0

Register 1

.

.

.

Register n

Read

Synchronizer

Read Data

Synchronizer 0

Synchronizer 1

.

.

.

Synchronizer n

HW Status Register 0

HW Status Register 1

.

.

.

HW Status Register m

Register 0 Sync

Register 1 Sync

.

.

.

Register n Sync

Low Energy

Peripheral

Main

Function

Figure 4.10. Read operation from Low Energy Peripherals

4.3.3 FREEZE Register

In all Low Energy Peripheral with delayed synchronization there is a <module_name>_FREEZE register (e.g. RTCC_FREEZE). The

register contains a bit named REGFREEZE. If precise control of the synchronization process is required, this bit may be utilized. When

REGFREEZE is set, the synchronization process is halted allowing the software to write multiple Low Energy registers before starting

the synchronization process, thus providing precise control of the module update process. The synchronization process is started by

clearing the REGFREEZE bit.

Note: The FREEZE register is also present on peripherals with immediate synchronization, but there it has no effect

4.4 Flash

The Flash retains data in any state and typically stores the application code, special user data and security information. The Flash

memory is typically programmed through the debug interface, but can also be erased and written to from software.

• Up to 256 KB of memory

• Page size of 2048 bytes (minimum erase unit)

• Minimum 10K erase cycles endurance

• Greater than 10 years data retention at 85°C

• Lock-bits for memory protection

• Data retention in any state

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 23

Page 25

EFM32JG1 Reference Manual

Memory and Bus System

4.5 SRAM

The primary task of the SRAM memory is to store application data. Additionally, it is possible to execute instructions from SRAM, and

the DMA may be set up to transfer data between the SRAM, Flash and peripherals.

• Up to 32 KB of memory

• Bit-band access support

• Set of RAM blocks may be powered down when not in use

• Data retention of the entire memory in EM0 Active to EM3 Stop

The SRAM memory may be split among two or more different AHB slaves (e.g., RAM0, RAM1, ...) in order to allow simultaneous access to different sections of the memory from two different AHB masters. For example, the Cortex-M3 can access RAM0 while the DMA

controller accesses RAM1 in parallel. See Figure 4.1 EFM32 Jade Gecko Bus System on page 14 for AHB slave connectivity details.

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 24

Page 26

EFM32JG1 Reference Manual

Memory and Bus System

4.6 DI Page Entry Map

The DI page contains production calibration data as well as device identification information. See the peripheral chapters for how each

calibration value is to be used with the associated peripheral.

The offset address is relative to the start address of the DI page.(see 6.3 Functional Description)

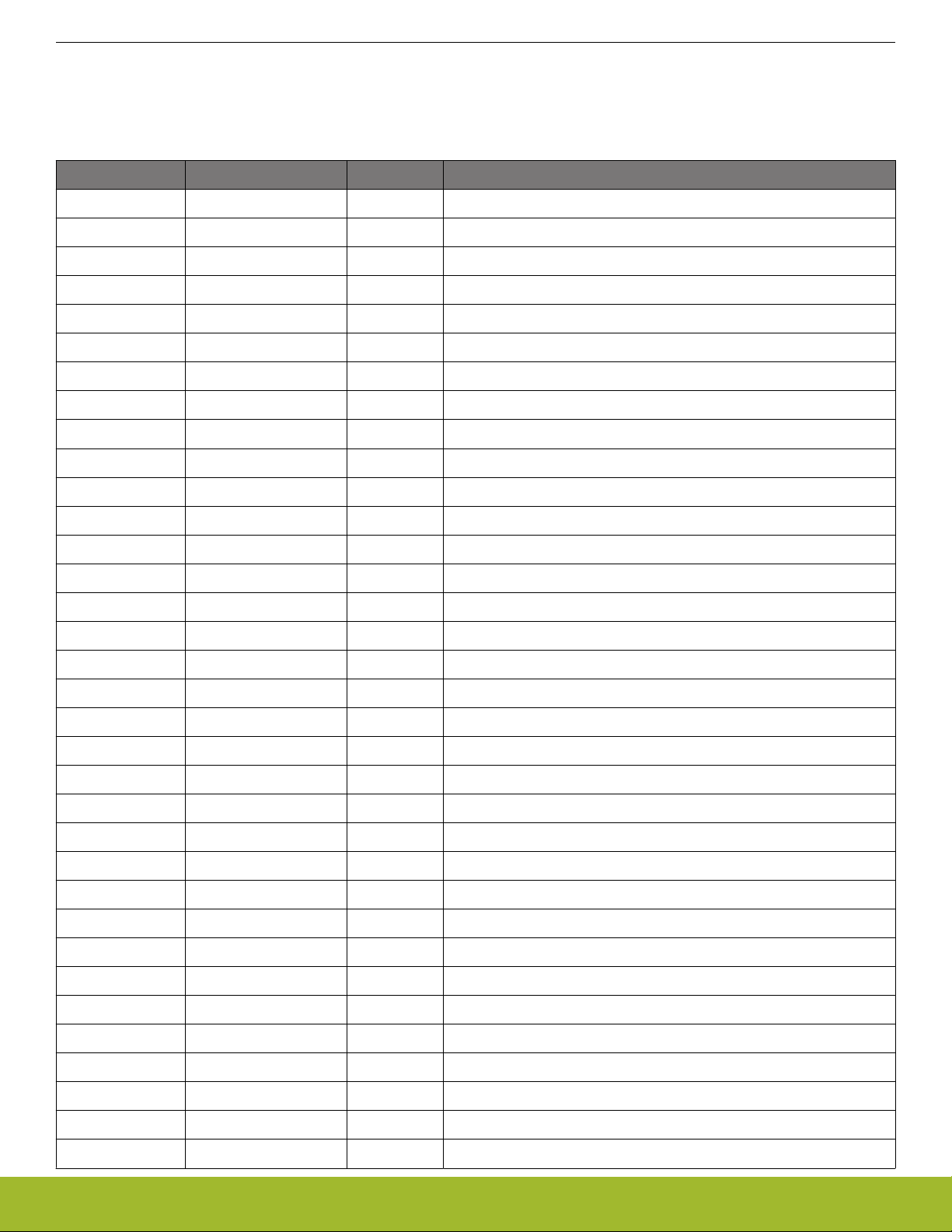

Offset Name Type Description

0x000 CAL RO CRC of DI-page and calibration temperature

0x028 EUI48L RO EUI48 OUI and Unique identifier

0x02C EUI48H RO OUI

0x030 CUSTOMINFO RO Custom information

0x034 MEMINFO RO Flash page size and misc. chip information

0x040 UNIQUEL RO Low 32 bits of device unique number

0x044 UNIQUEH RO High 32 bits of device unique number

0x048 MSIZE RO Flash and SRAM Memory size in kB

0x04C PART RO Part description

0x050 DEVINFOREV RO Device information page revision

0x054 EMUTEMP RO EMU Temperature Calibration Information

0x060 ADC0CAL0 RO ADC0 calibration register 0

0x064 ADC0CAL1 RO ADC0 calibration register 1

0x068 ADC0CAL2 RO ADC0 calibration register 2

0x06C ADC0CAL3 RO ADC0 calibration register 3

0x080 HFRCOCAL0 RO HFRCO Calibration Register (4 MHz)

0x08C HFRCOCAL3 RO HFRCO Calibration Register (7 MHz)

0x098 HFRCOCAL6 RO HFRCO Calibration Register (13 MHz)

0x09C HFRCOCAL7 RO HFRCO Calibration Register (16 MHz)

0x0A0 HFRCOCAL8 RO HFRCO Calibration Register (19 MHz)

0x0A8 HFRCOCAL10 RO HFRCO Calibration Register (26 MHz)

0x0AC HFRCOCAL11 RO HFRCO Calibration Register (32 MHz)

0x0B0 HFRCOCAL12 RO HFRCO Calibration Register (38 MHz)

0x0E0 AUXHFRCOCAL0 RO AUXHFRCO Calibration Register (4 MHz)

0x0EC AUXHFRCOCAL3 RO AUXHFRCO Calibration Register (7 MHz)

0x0F8 AUXHFRCOCAL6 RO AUXHFRCO Calibration Register (13 MHz)

0x0FC AUXHFRCOCAL7 RO AUXHFRCO Calibration Register (16 MHz)

0x100 AUXHFRCOCAL8 RO AUXHFRCO Calibration Register (19 MHz)

0x108 AUXHFRCOCAL10 RO AUXHFRCO Calibration Register (26 MHz)

0x10C AUXHFRCOCAL11 RO AUXHFRCO Calibration Register (32 MHz)

0x110 AUXHFRCOCAL12 RO AUXHFRCO Calibration Register (38 MHz)

0x140 VMONCAL0 RO VMON Calibration Register 0

0x144 VMONCAL1 RO VMON Calibration Register 1

0x148 VMONCAL2 RO VMON Calibration Register 2

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 25

Page 27

Offset Name Type Description

0x158 IDAC0CAL0 RO IDAC0 Calibration Register 0

0x15C IDAC0CAL1 RO IDAC0 Calibration Register 1

0x168 DCDCLNVCTRL0 RO DCDC Low-noise VREF Trim Register 0

0x16C DCDCLPVCTRL0 RO DCDC Low-power VREF Trim Register 0

0x170 DCDCLPVCTRL1 RO DCDC Low-power VREF Trim Register 1

0x174 DCDCLPVCTRL2 RO DCDC Low-power VREF Trim Register 2

0x178 DCDCLPVCTRL3 RO DCDC Low-power VREF Trim Register 3

0x17C DCDCLPCMPHYSSEL0 RO DCDC LPCMPHYSSEL Trim Register 0

0x180 DCDCLPCMPHYSSEL1 RO DCDC LPCMPHYSSEL Trim Register 1

4.7 DI Page Entry Description

4.7.1 CAL - CRC of DI-page and calibration temperature

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x000

Access

31

30

29

28

27

26

25

24

23

22

21

20

RO

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

RO

Name

TEMP

CRC

Bit Name Access Description

31:24 Reserved Reserved for future use

23:16 TEMP RO Calibration temperature as an usigned int in DegC

(25 = 25DegC)

15:0 CRC RO CRC of DI-page (CRC-16-CCITT)

4

3

2

1

0

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 26

Page 28

4.7.2 EUI48L - EUI48 OUI and Unique identifier

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x028

Access

31

30

29

28

RO

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

OUI48L

UNIQUEID

Bit Name Access Description

31:24 OUI48L RO Lower Octet of EUI48 Organizationally Unique Identi-

fier

23:0 UNIQUEID RO Unique identifier

4.7.3 EUI48H - OUI

Offset Bit Position

0x02C

Access

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

RO

3

2

1

0

3

2

1

0

Name

OUI48H

Bit Name Access Description

31:16 Reserved Reserved for future use

15:0 OUI48H RO Upper two Octets of EUI48 Organizationally Unique

Identifier

4.7.4 CUSTOMINFO - Custom information

Offset Bit Position

0x030

Access

31

30

29

28

27

26

25

24

RO

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

Name

PARTNO

Bit Name Access Description

31:16 PARTNO RO Custom part identifier as unsigned integer (e.g. 903)

65535 for standard product

4

3

2

1

0

15:0 Reserved Reserved for future use

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 27

Page 29

4.7.5 MEMINFO - Flash page size and misc. chip information

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x034

Access

31

30

29

28

RO

27

26

25

24

23

22

21

20

RO

19

18

17

16

15

14

13

12

11

RO

10

9

8

7

Name

FLASH_PAGE_SIZE

PINCOUNT

PKGTYPE

Bit Name Access Description

31:24 FLASH_PAGE_SIZE RO Flash page size in bytes coded as 2 ^ ((MEM_IN-

FO_PAGE_SIZE + 10) & 0xFF). Ie. the value 0xFF

= 512 bytes.

23:16 PINCOUNT RO Device pin count as unsigned integer (eg. 48)

15:8 PKGTYPE RO Package Identifier as character

Value Mode Description

6

5

4

3

2

1

0

RO

TEMPGRADE

74 WLCSP WLCSP package

77 QFN QFN package

81 QFP QFP package

7:0 TEMPGRADE RO Temperature Grade of product as unsigned inte-

ger enumeration

Value Mode Description

0 N40TO85 -40 to 85degC

1 N40TO125 -40 to 125degC

2 N40TO105 -40 to 105degC

3 N0TO70 0 to 70degC

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 28

Page 30

4.7.6 UNIQUEL - Low 32 bits of device unique number

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x040

Access

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RO

15

14

13

12

11

10

9

Name

UNIQUEL

Bit Name Access Description

31:0 UNIQUEL RO Low 32 bits of device unique number

4.7.7 UNIQUEH - High 32 bits of device unique number

Offset Bit Position

0x044

Access

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RO

15

14

13

12

11

10

9

Name

UNIQUEH

8

7

6

5

4

3

2

1

0

8

7

6

5

4

3

2

1

0

Bit Name Access Description

31:0 UNIQUEH RO High 32 bits of device unique number

4.7.8 MSIZE - Flash and SRAM Memory size in kB

Offset Bit Position

0x048

Access

31

30

29

28

27

26

25

24

RO

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

RO

Name

SRAM

FLASH

Bit Name Access Description

31:16 SRAM RO Ram size, kbyte count as unsigned integer (eg. 16)

15:0 FLASH RO Flash size, kbyte count as unsigned integer (eg. 128)

4

3

2

1

0

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 29

Page 31

4.7.9 PART - Part description

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x04C

Access

31

30

29

28

RO

27

26

25

24

23

22

21

20

RO

19

18

17

16

15

14

13

12

11

10

9

Name

PROD_REV

DEVICE_FAMILY

Bit Name Access Description

31:24 PROD_REV RO Production revision as unsigned integer

23:16 DEVICE_FAMILY RO Device Family

Value Mode Description

16 EFR32MG1P EFR32 Mighty Gecko Gen1 Device Family

17 EFR32MG1B EFR32 Mighty Gecko Gen1 Device Family

18 EFR32MG1V EFR32 Mighty Gecko Gen1 Device Family

8

7

6

5

RO

DEVICE_NUMBER

4

3

2

1

0

19 EFR32BG1P EFR32 Blue Gecko Gen1 Device Family

20 EFR32BG1B EFR32 Blue Gecko Gen1 Device Family

21 EFR32BG1V EFR32 Blue Gecko Gen1 Device Family

25 EFR32FG1P EFR32 Flex Gecko Gen1 Device Family

26 EFR32FG1B EFR32 Flex Gecko Gen1 Device Family

27 EFR32FG1V EFR32 Flex Gecko Gen1 Device Family

71 EFM32G EFM32 Gecko Device Family

71 G EFM32 Gecko Device Family

72 EFM32GG EFM32 Giant Gecko Device Family

72 GG EFM32 Giant Gecko Device Family

73 TG EFM32 Tiny Gecko Device Family

73 EFM32TG EFM32 Tiny Gecko Device Family

74 EFM32LG EFM32 Leopard Gecko Device Family

74 LG EFM32 Leopard Gecko Device Family

75 EFM32WG EFM32 Wonder Gecko Device Family

75 WG EFM32 Wonder Gecko Device Family

76 ZG EFM32 Zero Gecko Device Family

76 EFM32ZG EFM32 Zero Gecko Device Family

77 HG EFM32 Happy Gecko Device Family

77 EFM32HG EFM32 Happy Gecko Device Family

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 30

Page 32

Bit Name Access Description

81 EFM32PG1B EFM32 Pearl Gecko Gen1 Device Family

83 EFM32JG1B EFM32 Jade Gecko Gen1 Device Family

120 EZR32LG EZR32 Leopard Gecko Device Family

121 EZR32WG EZR32 Wonder Gecko Device Family

122 EZR32HG EZR32 Happy Gecko Device Family

15:0 DEVICE_NUMBER RO Part number as unsigned integer (e.g. 233 for

EFR32BG1P233F256GM48-B0)

4.7.10 DEVINFOREV - Device information page revision

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x050

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

Access

Name

Bit Name Access Description

31:8 Reserved Reserved for future use

7:0 DEVINFOREV RO DEVINFO layout revision as unsigned integer (initial-

ly 1)

4.7.11 EMUTEMP - EMU Temperature Calibration Information

Offset Bit Position

0x054

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

Access

3

2

1

RO

DEVINFOREV

3

2

1

RO

0

0

Name

EMUTEMPROOM

Bit Name Access Description

31:8 Reserved Reserved for future use

7:0 EMUTEMPROOM RO EMU_TEMP temperature reading at room

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 31

Page 33

4.7.12 ADC0CAL0 - ADC0 calibration register 0

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x060

Access

31

30

29

28

27

RO

26

25

24

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

RO

Name

GAIN2V5

NEGSEOFFSET2V5

OFFSET2V5

GAIN1V25

NEGSEOFFSET1V25

Bit Name Access Description

31 Reserved Reserved for future use

30:24 GAIN2V5 RO Gain for 2.5V reference

23:20 NEGSEOFFSET2V5 RO Negative single ended offset for 2.5V reference

19:16 OFFSET2V5 RO Offset for 2.5V reference

15 Reserved Reserved for future use

5

4

3

2

1

0

RO

OFFSET1V25

14:8 GAIN1V25 RO Gain for 1.25V reference

7:4 NEGSEOFFSET1V25 RO Negative single ended offset for 1.25V reference

3:0 OFFSET1V25 RO Offset for 1.25V reference

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 32

Page 34

4.7.13 ADC0CAL1 - ADC0 calibration register 1

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x064

Access

31

30

29

28

27

RO

26

25

24

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

RO

Name

GAIN5VDIFF

NEGSEOFFSET5VDIFF

OFFSET5VDIFF

GAINVDD

NEGSEOFFSETVDD

Bit Name Access Description

31 Reserved Reserved for future use

30:24 GAIN5VDIFF RO Gain for for 5V differential reference

23:20 NEGSEOFFSET5VDIFF RO Negative single ended offset with for 5V differential

reference

19:16 OFFSET5VDIFF RO Offset for 5V differential reference

4

3

2

1

0

RO

OFFSETVDD

15 Reserved Reserved for future use

14:8 GAINVDD RO Gain for VDD reference

7:4 NEGSEOFFSETVDD RO Negative single ended offset for VDD reference

3:0 OFFSETVDD RO Offset for VDD reference

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 33

Page 35

4.7.14 ADC0CAL2 - ADC0 calibration register 2

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x068

Access

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

RO

Name

NEGSEOFFSET2XVDD

Bit Name Access Description

31 Reserved Reserved for future use

30:24 Reserved Reserved for future use

23:20 Reserved Reserved for future use

19:16 Reserved Reserved for future use

15:8 Reserved Reserved for future use

7:4 NEGSEOFFSET2XVDD RO Negative single ended offset for 2XVDD reference

4

3

2

1

0

RO

OFFSET2XVDD

3:0 OFFSET2XVDD RO Offset for 2XVDD reference

4.7.15 ADC0CAL3 - ADC0 calibration register 3

Offset Bit Position

0x06C

Access

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

RO

9

8

Name

TEMPREAD1V25

Bit Name Access Description

31:16 Reserved Reserved for future use

15:4 TEMPREAD1V25 RO Temperature reading at 1V25 reference

3:0 Reserved Reserved for future use

7

6

5

4

3

2

1

0

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 34

Page 36

4.7.16 HFRCOCAL0 - HFRCO Calibration Register (4 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x080

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 35

Page 37

4.7.17 HFRCOCAL3 - HFRCO Calibration Register (7 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x08C

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 36

Page 38

4.7.18 HFRCOCAL6 - HFRCO Calibration Register (13 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x098

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 37

Page 39

4.7.19 HFRCOCAL7 - HFRCO Calibration Register (16 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x09C

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 38

Page 40

4.7.20 HFRCOCAL8 - HFRCO Calibration Register (19 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0A0

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 39

Page 41

4.7.21 HFRCOCAL10 - HFRCO Calibration Register (26 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0A8

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 40

Page 42

4.7.22 HFRCOCAL11 - HFRCO Calibration Register (32 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0AC

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 41

Page 43

4.7.23 HFRCOCAL12 - HFRCO Calibration Register (38 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0B0

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO HFRCO Temperature Coefficient Trim on Comparator

Reference

27 FINETUNINGEN RO HFRCO enable reference for fine tuning

26:25 CLKDIV RO HFRCO Clock Output Divide

24 LDOHP RO HFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO HFRCO Comparator Bias Current

20:16 FREQRANGE RO HFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO HFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO HFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 42

Page 44

4.7.24 AUXHFRCOCAL0 - AUXHFRCO Calibration Register (4 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0E0

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO AUXHFRCO Temperature Coefficient Trim on Compa-

rator Reference

27 FINETUNINGEN RO AUXHFRCO enable reference for fine tuning

26:25 CLKDIV RO AUXHFRCO Clock Output Divide

24 LDOHP RO AUXHFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO AUXHFRCO Comparator Bias Current

20:16 FREQRANGE RO AUXHFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO AUXHFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO AUXHFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 43

Page 45

4.7.25 AUXHFRCOCAL3 - AUXHFRCO Calibration Register (7 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0EC

Access

31

30

RO

29

28

27

RO

26

RO

25

24

RO

23

22

RO

21

20

19

18

RO

17

16

15

14

13

12

11

RO

10

9

8

7

6

5

4

Name

VREFTC

FINETUNINGEN

CLKDIV

LDOHP

CMPBIAS

FREQRANGE

FINETUNING

Bit Name Access Description

31:28 VREFTC RO AUXHFRCO Temperature Coefficient Trim on Compa-

rator Reference

27 FINETUNINGEN RO AUXHFRCO enable reference for fine tuning

26:25 CLKDIV RO AUXHFRCO Clock Output Divide

24 LDOHP RO AUXHFRCO LDO High Power Mode

3

2

RO

TUNING

1

0

23:21 CMPBIAS RO AUXHFRCO Comparator Bias Current

20:16 FREQRANGE RO AUXHFRCO Frequency Range

15:14 Reserved Reserved for future use

13:8 FINETUNING RO AUXHFRCO Fine Tuning Value

7 Reserved Reserved for future use

6:0 TUNING RO AUXHFRCO Tuning Value

silabs.com | Smart. Connected. Energy-friendly. Preliminary Rev. 0.6 | 44

Page 46

4.7.26 AUXHFRCOCAL6 - AUXHFRCO Calibration Register (13 MHz)

Offset Bit Position

EFM32JG1 Reference Manual

Memory and Bus System

0x0F8

Access

31

30

RO

29