Page 1

...the world's most energy friendly microcontrollers

EFM32G Reference Manual

Gecko Series

• 32-bit ARM Cortex-M3 processor running at up to 32 MHz

• Up to 128 kB Flash and 16 kB RAM memory

• Energy efficient and autonomous peripherals

• Ultra low power Energy Modes with sub-µA operation

• Fast wake-up time of only 2 µs

The EFM32G microcontroller series revolutionizes the 8- to 32-bit market with a

combination of unmatched performance and ultra low power consumption in both

active- and sleep modes. EFM32G devices consume as little as 180 µA/MHz in run

mode, and as little as 900 nA with a Real Time Counter running, Brown-out and full

RAM and register retention.

EFM32G's low energy consumption outperforms any other available 8-, 16-, and 32bit solution. The EFM32G includes autonomous and energy efficient peripherals,

high overall chip- and analog integration, and the performance of the industry

standard 32-bit ARM Cortex-M3 processor.

Page 2

...the world's most energy friendly microcontrollers

1 Energy Friendly Microcontrollers

1.1 Typical Applications

The EFM32G Gecko is the ideal choice for demanding 8-, 16-, and 32-bit energy sensitive applications.

These devices are developed to minimize the energy consumption by lowering both the power and the

active time, over all phases of MCU operation. This unique combination of ultra low energy consumption

and the performance of the 32-bit ARM Cortex-M3 processor, help designers get more out of the

available energy in a variety of applications.

Ultra low energy EFM32G microcontrollers are perfect for:

• Gas metering

• Energy metering

• Water metering

• Smart metering

• Alarm and security systems

• Health and fitness applications

• Industrial and home automation

1 2 3 4

0

1.2 EFM32G Development

Because EFM32G use the Cortex-M3 CPU, embedded designers benefit from the largest development

ecosystem in the industry, the ARM ecosystem. The development suite spans the whole design

process and includes powerful debug tools, and some of the world’s top brand compilers. Libraries with

documentation and user examples shorten time from idea to market.

The range of EFM32G devices ensure easy migration and feature upgrade possibilities.

2014-07-02 - Gecko Family - d0001_Rev1.30 2

www.silabs.com

Page 3

...the world's most energy friendly microcontrollers

2 About This Document

This document contains reference material for the EFM32G series of microcontrollers. All modules and

peripherals in the EFM32G series devices are described in general terms. Not all modules are present

in all devices, and the feature set for each device might vary. Such differences, including pin-out, are

covered in the device-specific datasheets.

2.1 Conventions

Register Names

Register names are given as a module name prefix followed by the short register name:

TIMERn_CTRL - Control Register

The "n" denotes the numeric instance for modules that might have more than one instance.

Some registers are grouped which leads to a group name following the module prefix:

GPIO_Px_DOUT - Port Data Out Register,

where x denotes the port instance (A,B,...).

Bit Fields

Registers contain one or more bit fields which can be 1 to 32 bits wide. Multi-bit fields are denoted with

(x:y), where x is the start bit and y is the end bit.

Address

The address for each register can be found by adding the base address of the module (found in the

Memory Map), and the offset address for the register (found in module Register Map).

Access Type

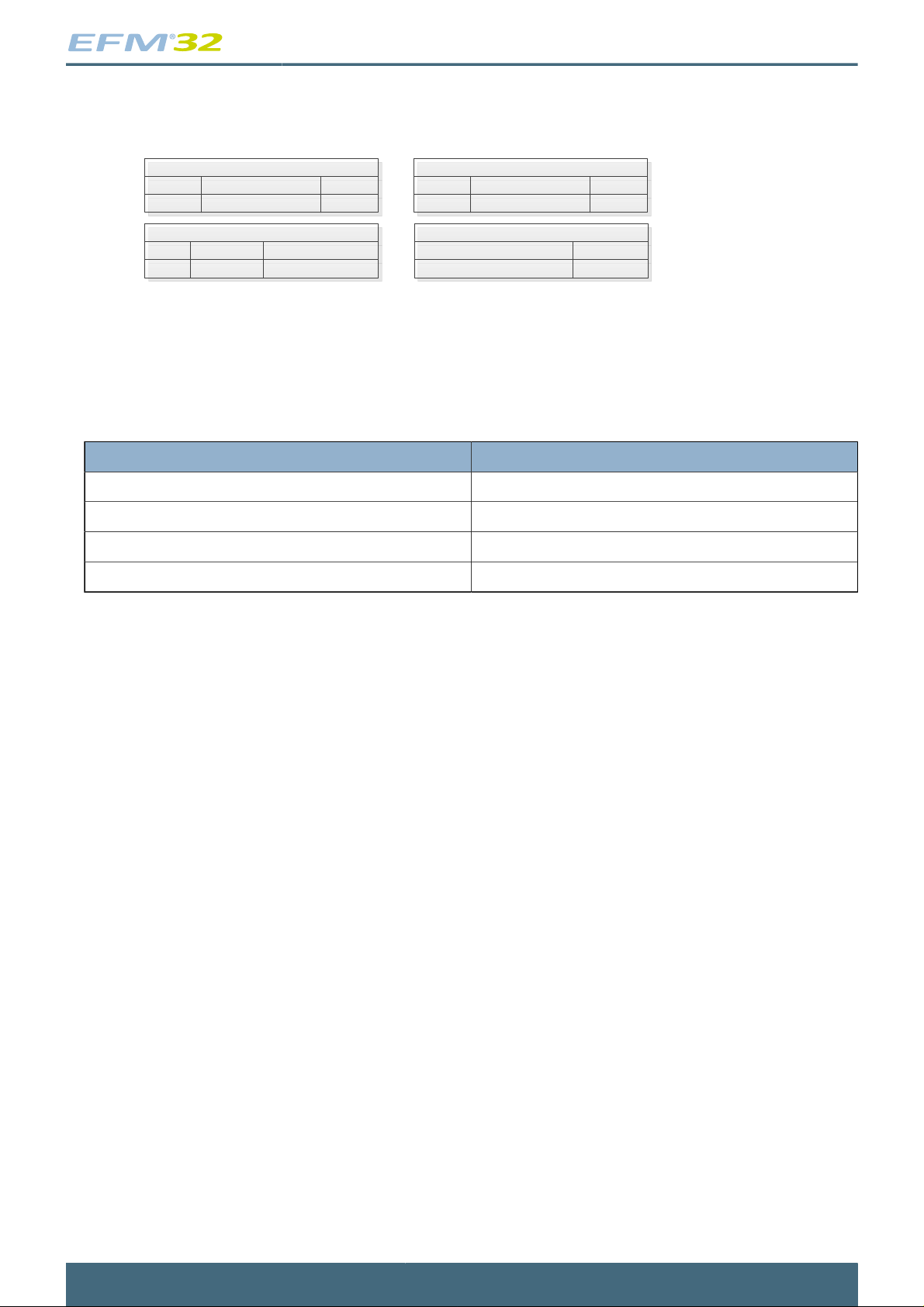

The register access types used in the register descriptions are explained in Table 2.1 (p. 3) .

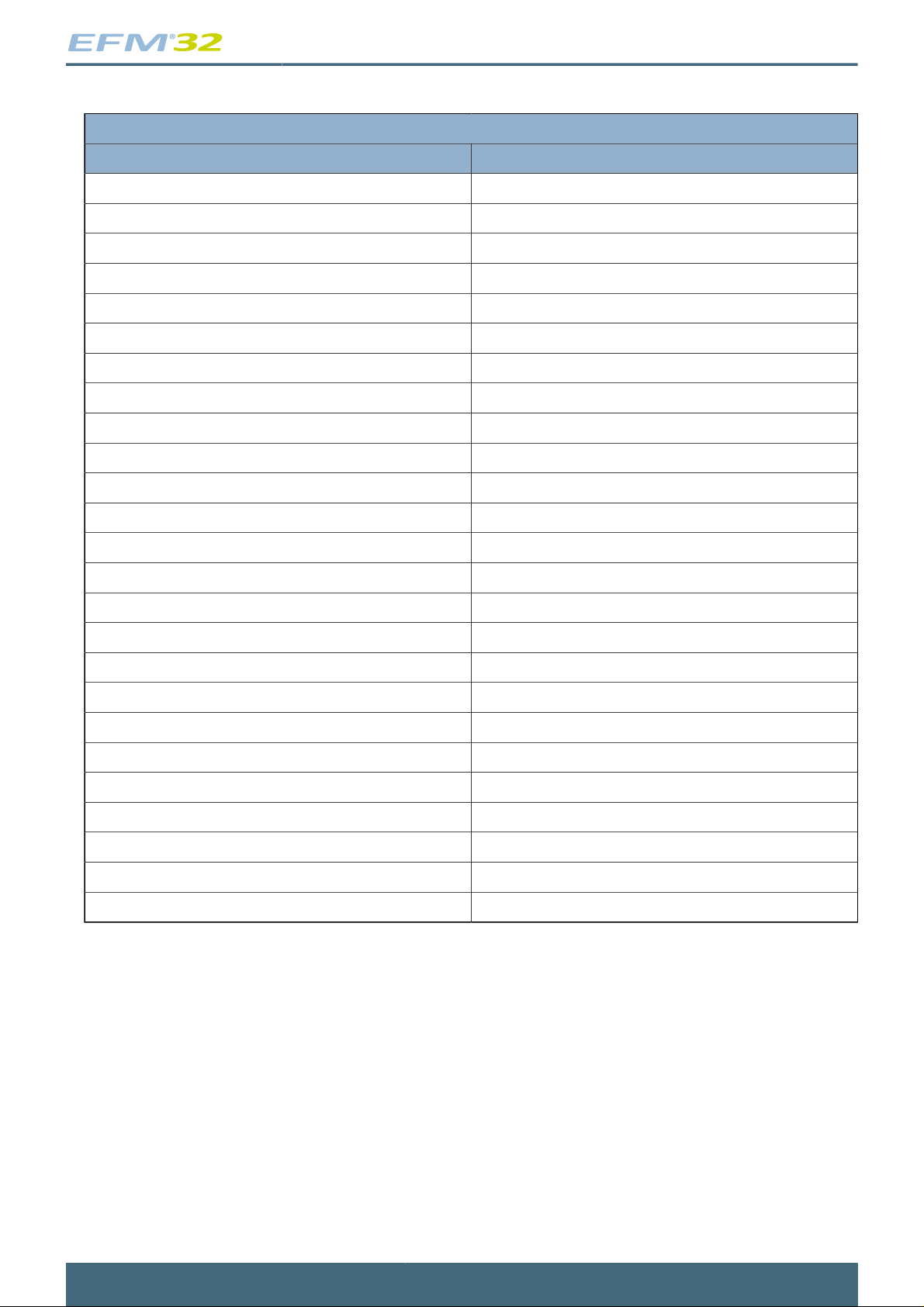

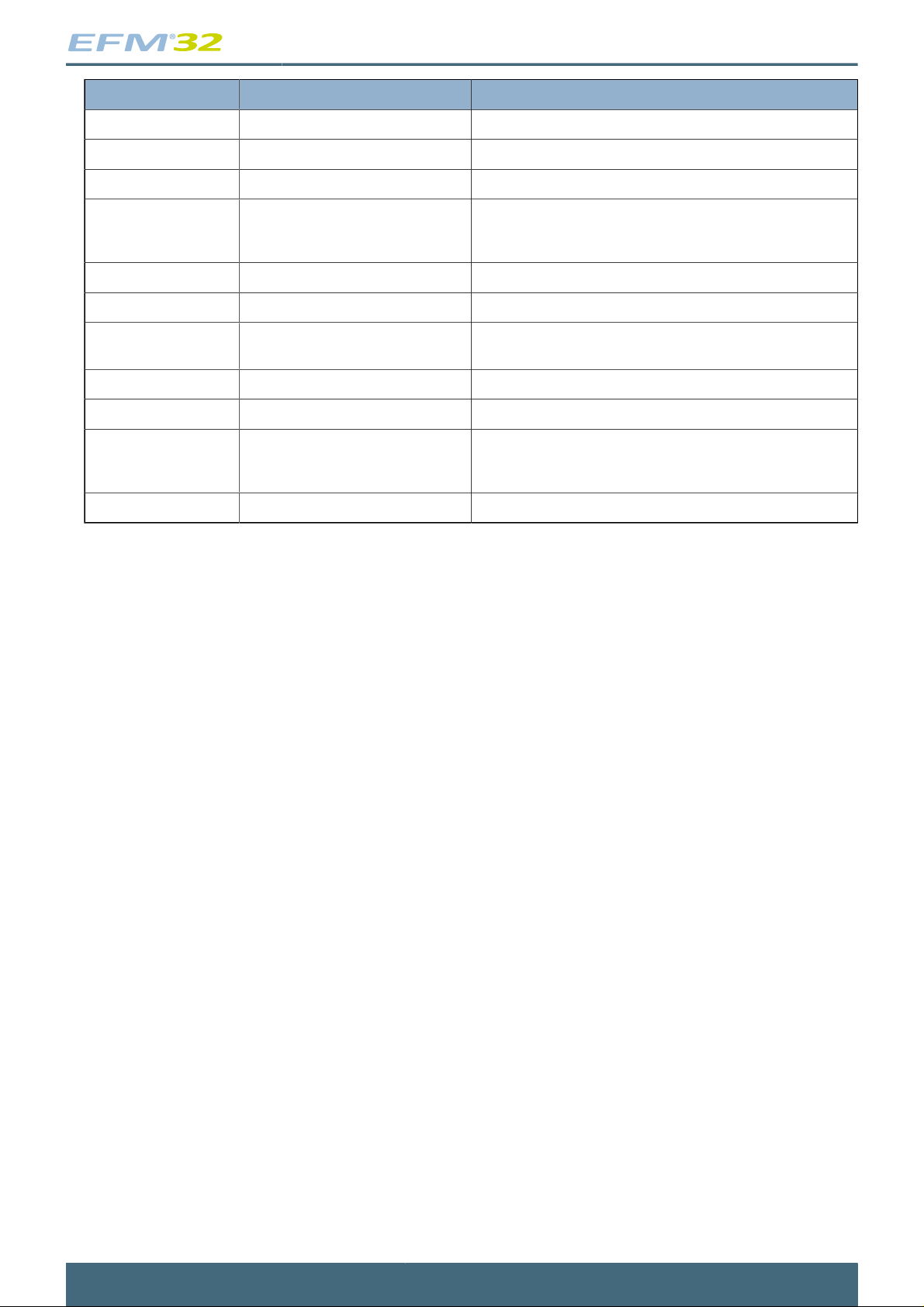

Table 2.1. Register Access Types

Access Type Description

R Read only. Writes are ignored.

RW Readable and writable.

RW1 Readable and writable. Only writes to 1 have effect.

RW1H Readable, writable and updated by hardware. Only writes to

1 have effect.

W1 Read value undefined. Only writes to 1 have effect.

W Write only. Read value undefined.

RWH Readable, writable and updated by hardware.

Number format

0x prefix is used for hexadecimal numbers.

0b prefix is used for binary numbers.

Numbers without prefix are in decimal representation.

2014-07-02 - Gecko Family - d0001_Rev1.30 3

www.silabs.com

Page 4

...the world's most energy friendly microcontrollers

Reserved

Registers and bit fields marked with reserved are reserved for future use. These should be written to 0

unless otherwise stated in the Register Description. Reserved bits might be read as 1 in future devices.

Reset Value

The reset value denotes the value after reset.

Registers denoted with X have an unknown reset value and need to be initialized before use. Note

that, before these registers are initialized, read-modify-write operations might result in undefined register

values.

Pin Connections

Pin connections are given as a module prefix followed by a short pin name:

USn_TX (USARTn TX pin)

The pin locations referenced in this document are given in the device-specific datasheet.

2.2 Related Documentation

Further documentation on the EFM32G family and the ARM Cortex-M3 can be found at the Silicon

Laboratories and ARM web pages:

www.silabs.com

www.arm.com

2014-07-02 - Gecko Family - d0001_Rev1.30 4

www.silabs.com

Page 5

...the world's most energy friendly microcontrollers

3 System Overview

3.1 Introduction

The EFM32 MCUs are the world’s most energy friendly microcontrollers. With a unique combination

of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from

energy saving modes, and a wide selection of peripherals, the EFM32G microcontroller is well suited for

any battery operated application, as well as other systems requiring high performance and low-energy

consumption, see Figure 3.1 (p. 7) .

3.2 Features

• ARM Cortex-M3 CPU platform

• High Performance 32-bit processor @ up to 32 MHz

• Memory Protection Unit

• Wake-up Interrupt Controller

• Flexible Energy Management System

• 20 nA @ 3 V Shutoff Mode

• 0.6 µA @ 3 V Stop Mode, including Power-on Reset, Brown-out Detector, RAM and CPU

retention

• 0.9 µA @ 3 V Deep Sleep Mode, including RTC with 32.768 kHz oscillator, Power-on

Reset, Brown-out Detector, RAM and CPU retention

• 45 µA/MHz @ 3 V Sleep Mode

• 180 µA/MHz @ 3 V Run Mode, with code executed from flash

• 128/64/32/16 KB Flash

• 16/8 KB RAM

• Up to 90 General Purpose I/O pins

• Configurable push-pull, open-drain, pull-up/down, input filter, drive strength

• Configurable peripheral I/O locations

• 16 asynchronous external interrupts

• 8 Channel DMA Controller

• Alternate/primary descriptors with scatter-gather/ping-pong operation

• 8 Channel Peripheral Reflex System

• Autonomous inter-peripheral signaling enables smart operation in low energy modes

• External Bus Interface (EBI)

• Up to 4x64 MB of external memory mapped space

• Integrated LCD Controller for up to 4×40 Segments

• Voltage boost, adjustable contrast adjustment and autonomous animation feature

• Hardware AES with 128/256-bit Keys in 54/75 cycles

• Communication interfaces

• 3× Universal Synchronous/Asynchronous Receiver/Transmitter

• UART/SPI/SmartCard (ISO 7816)/IrDA

• Triple buffered full/half-duplex operation

• 4-16 data bits

• 1× Universal Asynchronous Receiver/Transmitter

• Triple buffered full/half-duplex operation

• 8-9 data bits

• 2× Low Energy UART

• Autonomous operation with DMA in Deep Sleep Mode

• 1× I2C Interface with SMBus support

• Address recognition in Stop Mode

• Timers/Counters

2014-07-02 - Gecko Family - d0001_Rev1.30 5

www.silabs.com

Page 6

...the world's most energy friendly microcontrollers

• 3× 16-bit Timer/Counter

• 3 Compare/Capture/PWM channels

• Dead-Time Insertion on TIMER0

• 16-bit Low Energy Timer

• 24-bit Real-Time Counter

• 3× 8-bit Pulse Counter

• Asynchronous pulse counting/quadrature decoding

• Watchdog Timer with dedicated RC oscillator @ 50 nA

• Ultra low power precision analog peripherals

• 12-bit 1 Msamples/s Analog to Digital Converter

• 8 input channels and on-chip temperature sensor

• Single ended or differential operation

• Conversion tailgating for predictable latency

• 12-bit 500 ksamples/s Digital to Analog Converter

• 2 single ended channels/1 differential channel

• 2× Analog Comparator

• Programmable speed/current

• Capacitive sensing with up to 8 inputs

• Supply Voltage Comparator

• Ultra efficient Power-on Reset and Brown-Out Detector

• 2-pin Serial Wire Debug interface

• 1-pin Serial Wire Viewer

• Temperature range -40 - 85°C

• Single power supply 1.98 - 3.8 V

• Packages

• QFN32

• QFN64

• TQFP48

• TQFP64

• LQFP100

• LFBGA112

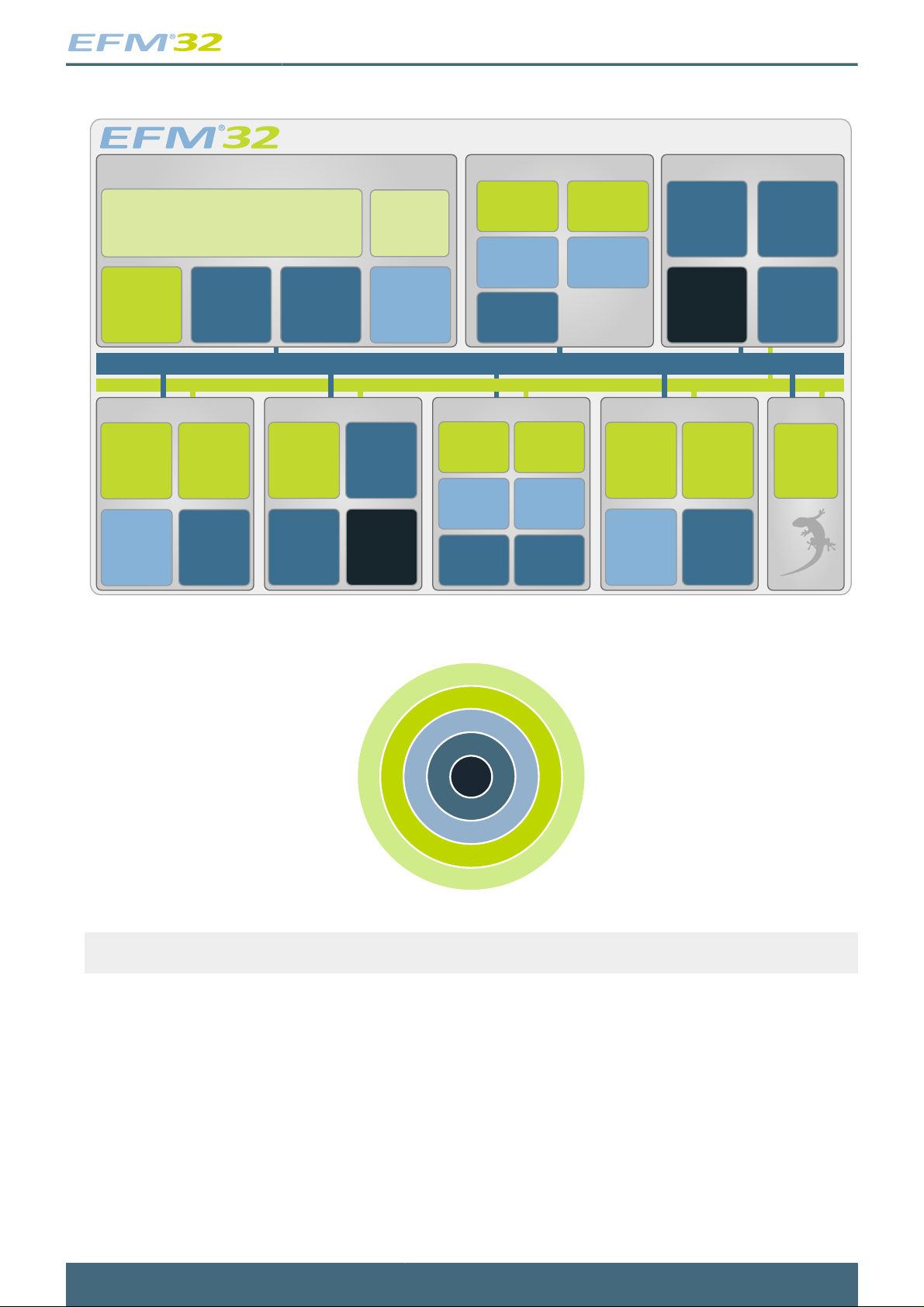

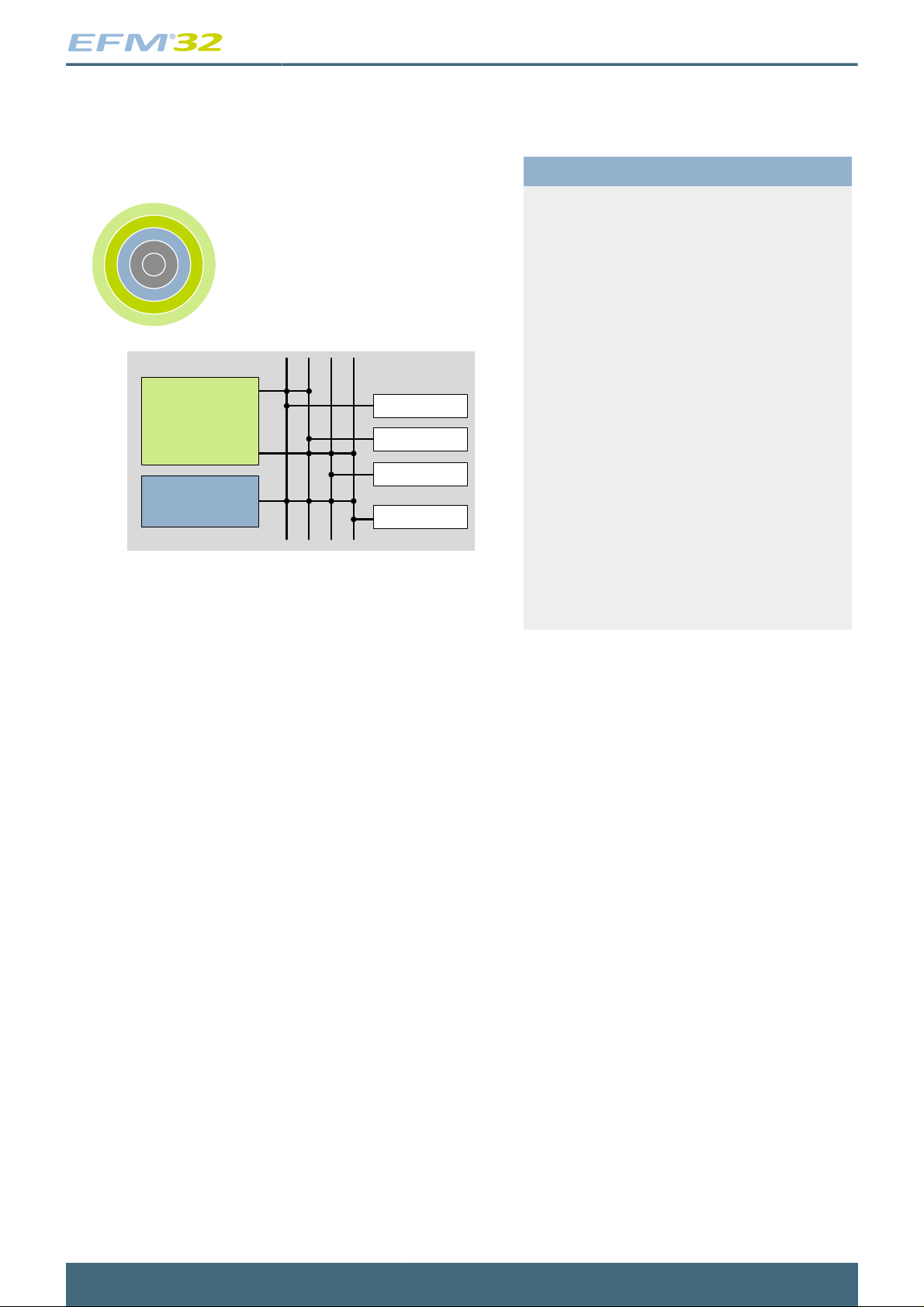

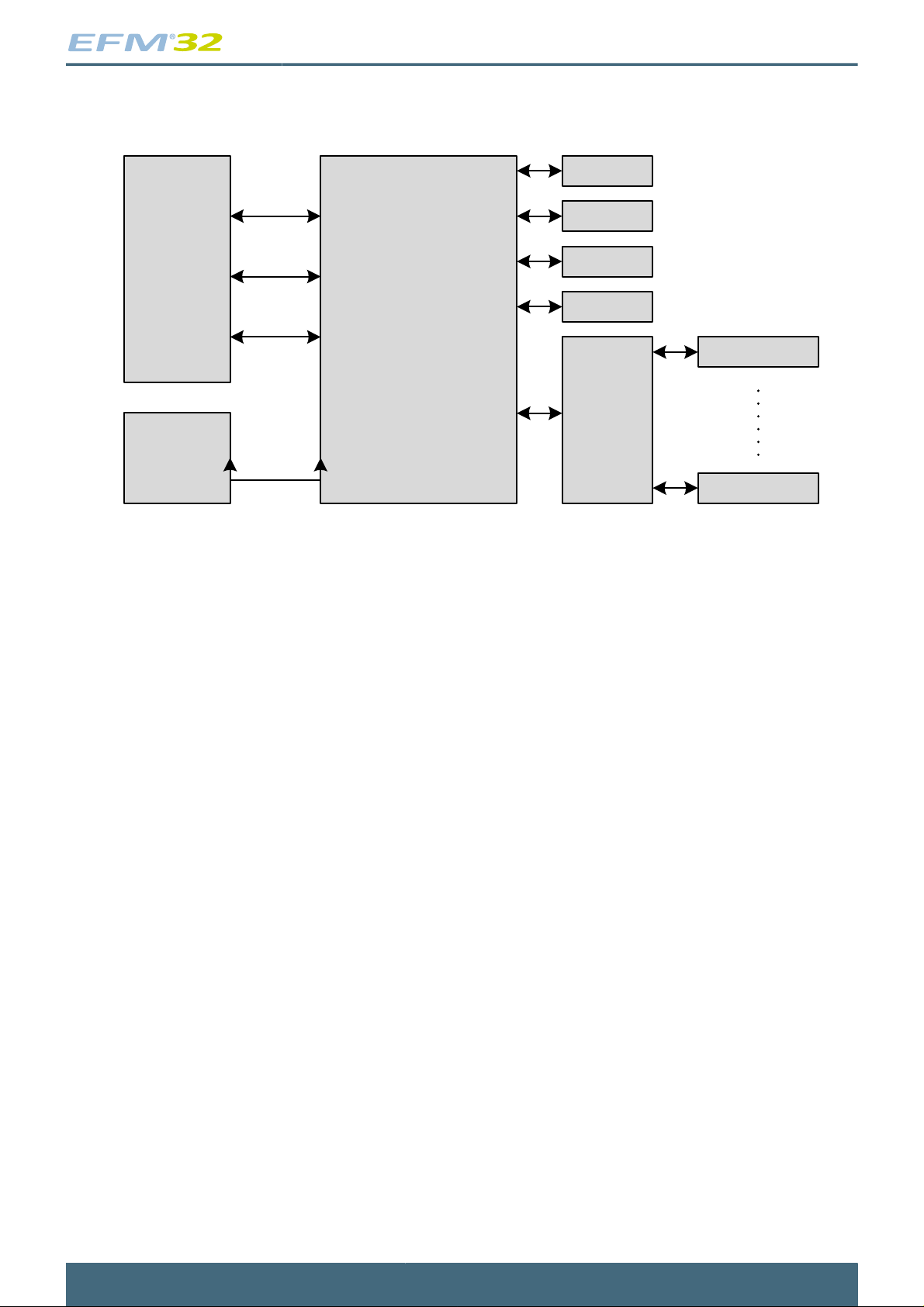

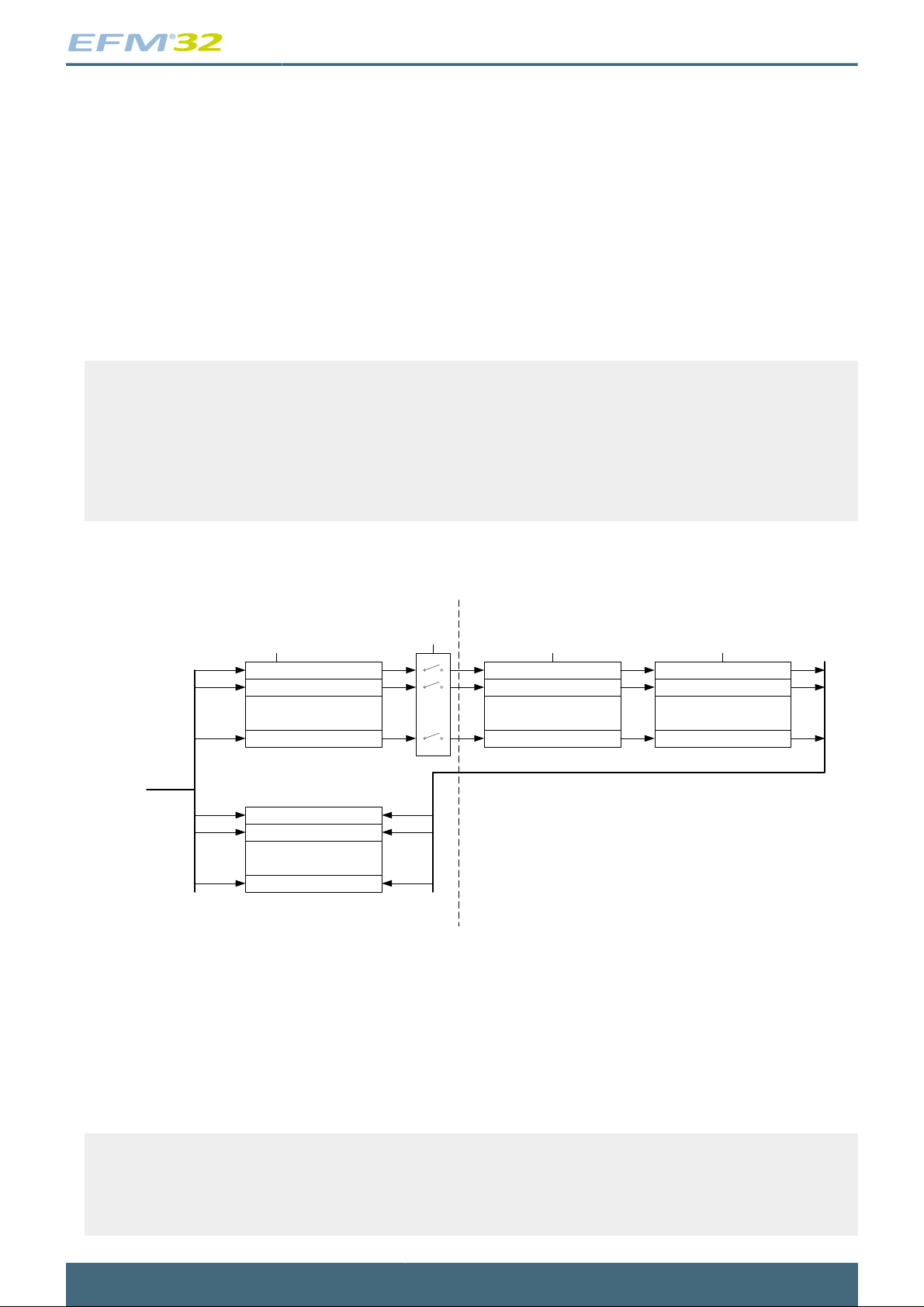

3.3 Block Diagram

Figure 3.1 (p. 7) shows the block diagram of EFM32G. The color indicates peripheral availability in

the different energy modes, described in Section 3.4 (p. 7) .

2014-07-02 - Gecko Family - d0001_Rev1.30 6

www.silabs.com

Page 7

Figure 3.1. Block Diagram of EFM32G

Clock Management Energy Management

Serial Interfaces

I/O Ports

Core and Memory

Timers and Triggers Analog Interfaces Security

ARM Cortex™- M3 processor

Flash

Program

Memory

Peripheral

Reflex

System

High Frequency

RC

Oscillator

High Frequency

Crystal

Oscillator

Timer/

Counter

Low Energy

Timer™

Pulse

Counter

Real Time

Counter

Low Frequency

Crystal

Oscillator

Low Frequency

RC

Oscillator

LCD

Controller

Voltage

Regulator

Watchdog

Timer

RAM

Memory

Voltage

Comparator

Power-on

Reset

Brown-out

Detector

Analog

Comparator

External

Bus

Interface

General

Purpose

I/ O

Low

Energy

UART™

Watchdog

Oscillator

Memory

Protection

Unit

ADC DAC

DMA

Controller

Debug

Interface

External

Interrupts

Pin

Reset

USART

I2C

UART AES

Gecko

32-bit bus

Peripheral Reflex System

...the world's most energy friendly microcontrollers

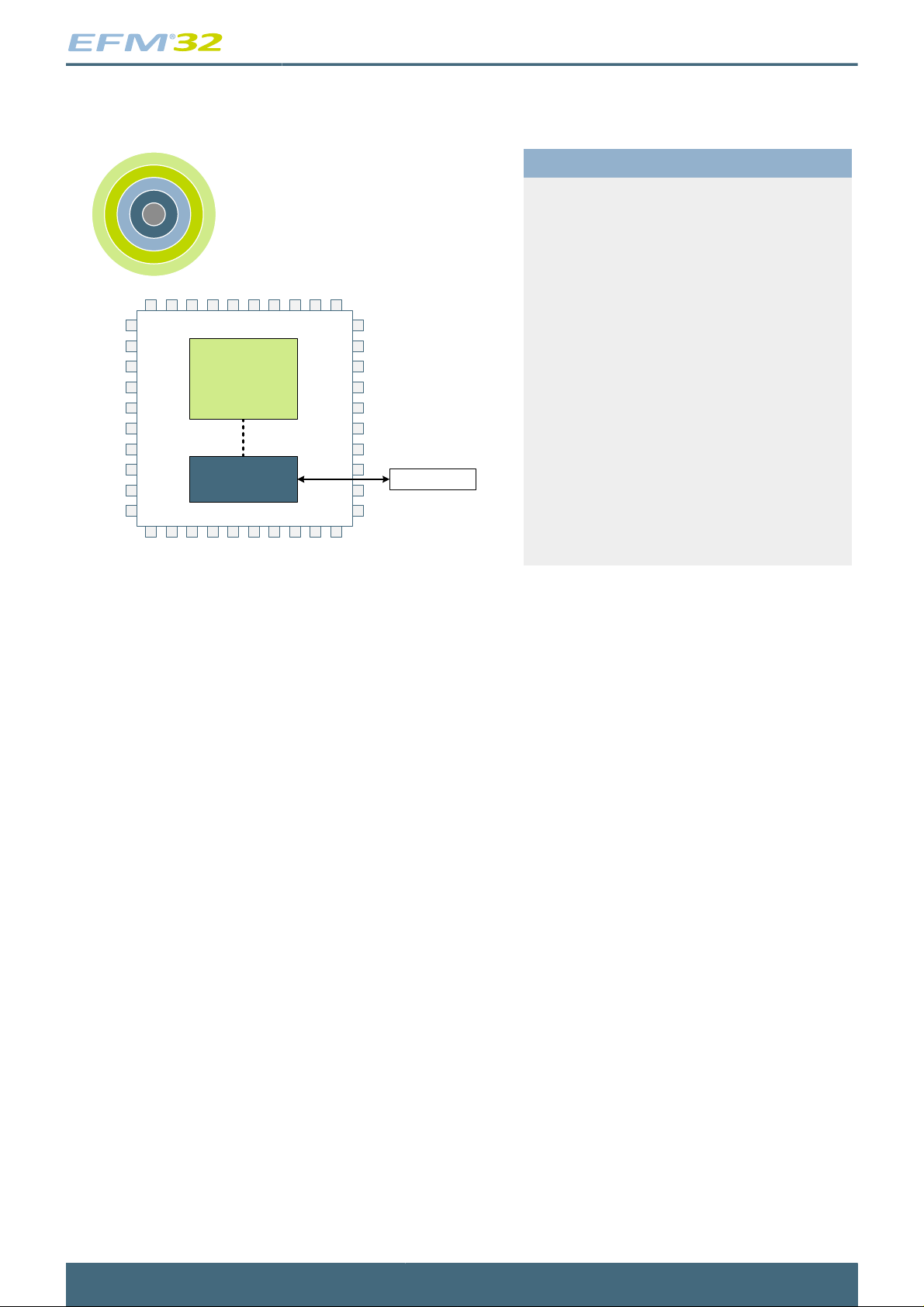

Figure 3.2. Energy Mode Indicator

Note

In the energy mode indicator, the numbers indicates Energy Mode, i.e EM0-EM4.

3.4 Energy Modes

There are five different Energy Modes (EM0-EM4) in the EFM32G, see Table 3.1 (p. 8) . The

EFM32G is designed to achieve a high degree of autonomous operation in low energy modes. The

intelligent combination of peripherals, RAM with data retention, DMA, low-power oscillators, and short

wake-up time, makes it attractive to remain in low energy modes for long periods and thus saving energy

consumption.

Tip

Throughout this document, the first figure in every module description contains an Energy Mode

Indicator showing which energy mode(s) the module can operate (see Table 3.1 (p. 8) ).

2014-07-02 - Gecko Family - d0001_Rev1.30 7

1 2 3 4

0

www.silabs.com

Page 8

Table 3.1. Energy Mode Description

Energy Mode Name Description

...the world's most energy friendly microcontrollers

1 2 3 4

0

1 2 3 4

0

1 2 3 4

0

1 2 3 4

0

EM0 – Energy Mode 0

(Run mode)

EM1 – Energy Mode 1

(Sleep Mode)

EM2 – Energy Mode 2

(Deep Sleep Mode)

EM3 - Energy Mode 3

(Stop Mode)

In EM0, the CPU is running and consuming as little as 180 µA/MHz, when

running code from flash. All peripherals can be active.

In EM1, the CPU is sleeping and the power consumption is only 45 µA/MHz.

All peripherals, including DMA, PRS and memory system, are still available.

In EM2 the high frequency oscillator is turned off, but with the 32.768 kHz

oscillator running, selected low energy peripherals (LCD, RTC, LETIMER,

PCNT, LEUART, I2C, WDOG and ACMP) are still available. This gives a high

degree of autonomous operation with a current consumption as low as 0.9 µA

with RTC enabled. Power-on Reset, Brown-out Detection and full RAM and

CPU retention is also included.

In EM3, the low-frequency oscillator is disabled, but there is still full CPU

and RAM retention, as well as Power-on Reset, Pin reset and Brownout Detection, with a consumption of only 0.6 µA. The low-power ACMP,

asynchronous external interrupt, PCNT, and I2C can wake-up the device.

Even in this mode, the wake-up time is a few microseconds.

1 2 3 4

0

EM4 – Energy Mode 4

(Shutoff Mode)

In EM4, the current is down to 20 nA and all chip functionality is turned off

except the pin reset and the Power-On Reset. All pins are put into their reset

state.

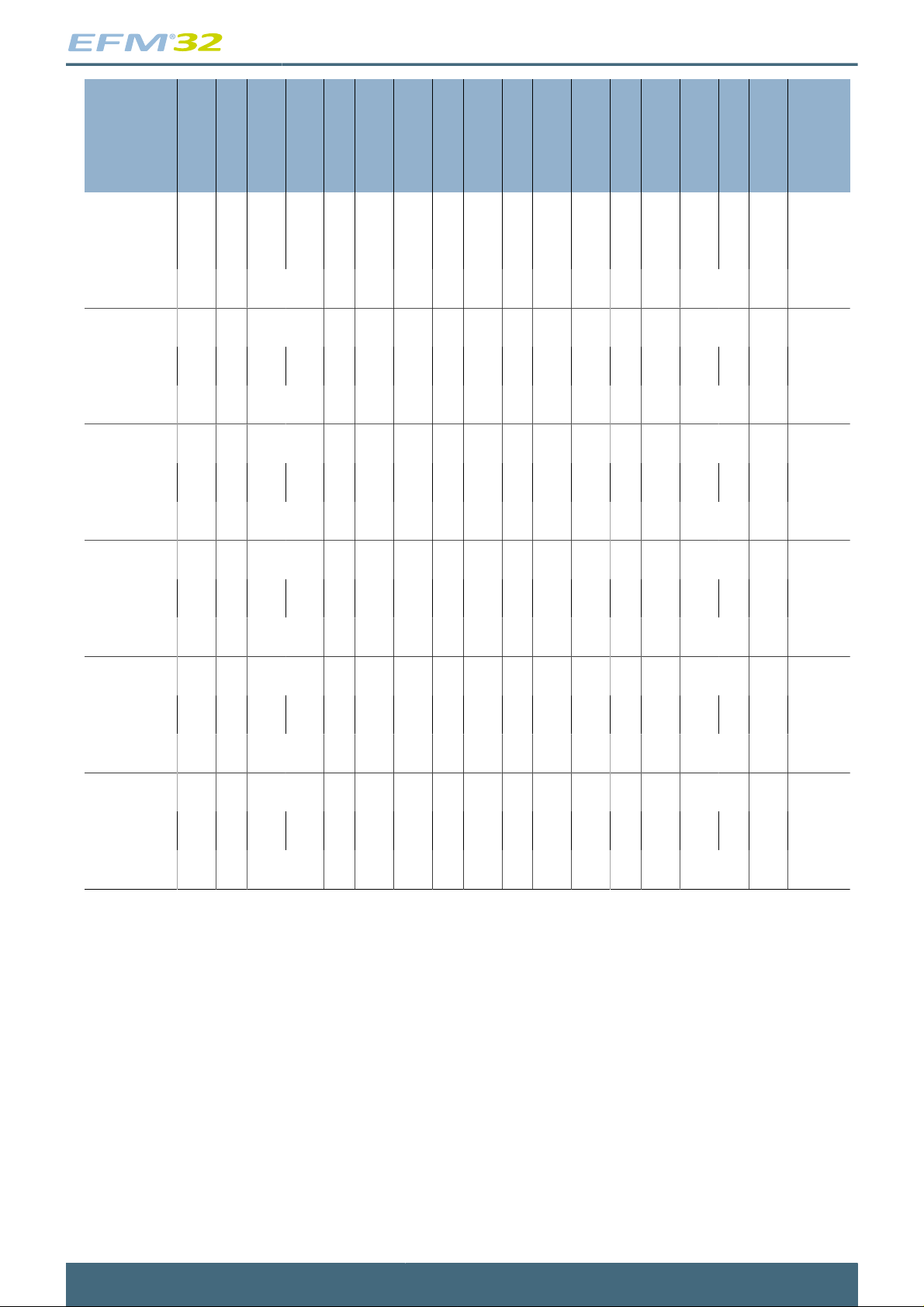

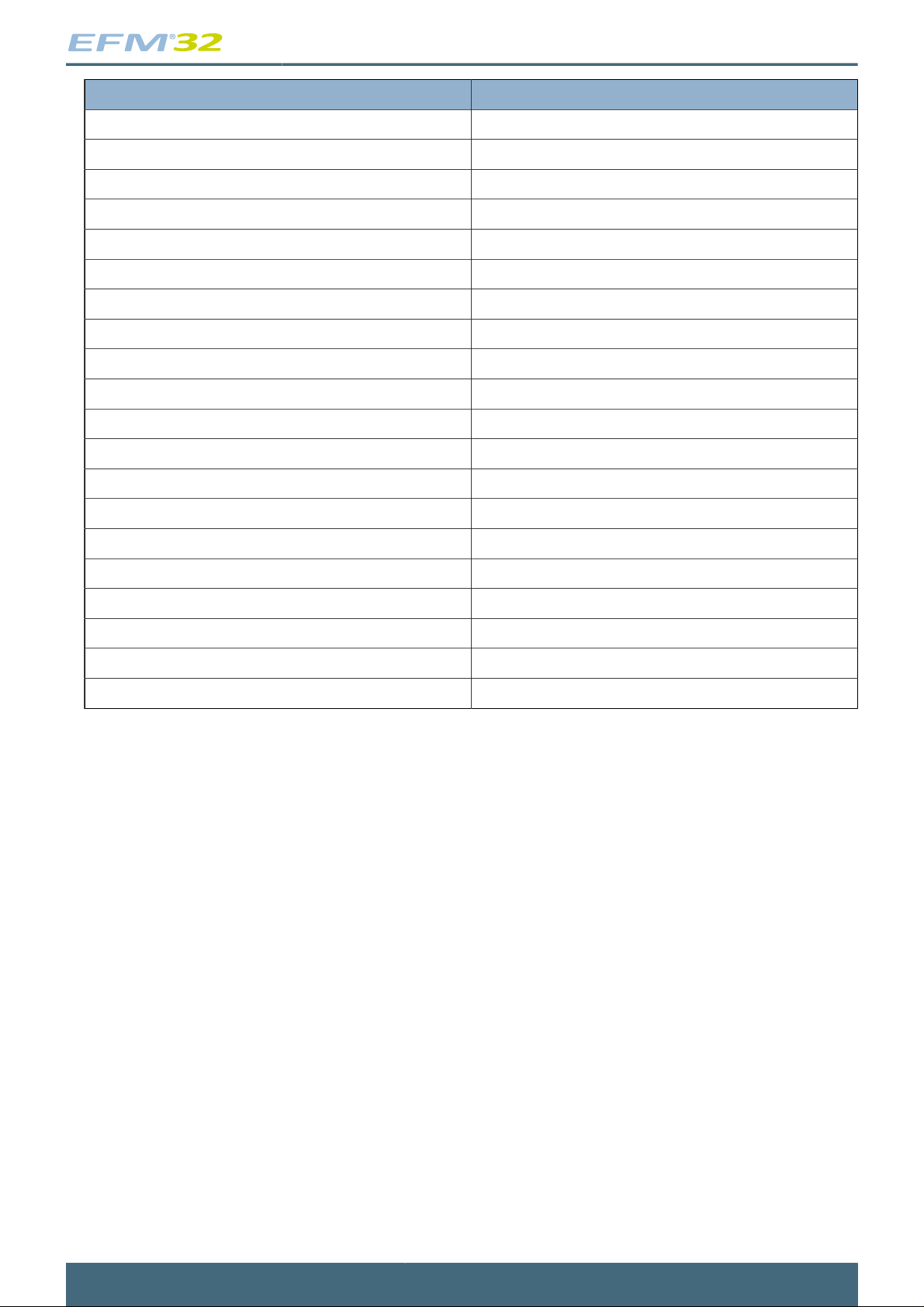

3.5 Product Overview

Table 3.2 (p. 8) shows a device overview of the EFM32G Microcontroller Series, including peripheral

functionality. For more information, the reader is referred to the device specific datasheets.

Table 3.2. EFM32G Microcontroller Series

C

EFM32G Part #

200F16 16 8 24 - 2 1 1

200F32 32 8 24 - 2 1 1

200F64 64 16 24 - 2 1 1

210F128 128 16 24 - 2 1 1

Flash

RAM

GPIO(pins)

LCD

USART+UART

2

LEUART

I

Timer(PWM)

LETIMER

2

1 1 1 1

(6)

2

1 1 1 1

(6)

2

1 1 1 1

(6)

2

1 1 1 1

(6)

RTC

PCNT

Watchdog

ADC(pins)

1

1 (1) 2 (5) - - QFN32

(4)

1

1 (1) 2 (5) - - QFN32

(4)

1

1 (1) 2 (5) - - QFN32

(4)

1

1 (1) 2 (5) Y - QFN32

(4)

DAC(pins)

ACMP(pins)

AES

EBI

Package

2014-07-02 - Gecko Family - d0001_Rev1.30 8

www.silabs.com

Page 9

...the world's most energy friendly microcontrollers

C

EFM32G Part #

230F32 32 8 56 - 3 2 1

230F64 64 16 56 - 3 2 1

230F128 128 16 56 - 3 2 1

280F32 32 8 85 - 3+1 2 1

280F64 64 16 85 - 3+1 2 1

280F128 128 16 85 - 3+1 2 1

290F32 32 8 90 - 3+1 2 1

290F64 64 16 90 - 3+1 2 1

290F128 128 16 90 - 3+1 2 1

840F32 32 8 56 4x24 3 2 1

840F64 64 16 56 4x24 3 2 1

840F128 128 16 56 4x24 3 2 1

880F32 32 8 85 4x40 3+1 2 1

880F64 64 16 85 4x40 3+1 2 1

880F128 128 16 85 4x40 3+1 2 1

890F32 32 8 90 4x40 3+1 2 1

890F64 64 16 90 4x40 3+1 2 1

890F128 128 16 90 4x40 3+1 2 1

1

EBI and LCD share pins in the part. Only a reduced pin count LCD driver can be used simultaneously with the EBI.

Flash

RAM

GPIO(pins)

LCD

USART+UART

2

LEUART

I

Timer(PWM)

LETIMER

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

3

1 1 3 1

(9)

RTC

PCNT

Watchdog

ADC(pins)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2) 2 (8) Y - QFN64

(8)

1

2 (2) 2 (8) Y - QFN64

(8)

1

2 (2) 2 (8) Y - QFN64

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

1

2 (2)

(8)

DAC(pins)

ACMP(pins)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

2

(16)

AES

Y - QFN64

Y - QFN64

Y - QFN64

Y Y LQFP100

Y Y LQFP100

Y Y LQFP100

Y Y LFBGA112

Y Y LFBGA112

Y Y LFBGA112

Y Y 1LQFP100

Y Y1LQFP100

Y Y1LQFP100

Y Y1LFBGA112

Y Y1LFBGA112

Y Y1LFBGA112

EBI

Package

3.6 Device Revision

The device revision number is read from the ROM Table. The major revision number and the chip family

number is read from PID0 and PID1 registers. The minor revision number is extracted from the PID2 and

PID3 registers, as illustrated in Figure 3.3 (p. 10) . The Fam[5:2] and Fam[1:0] must be combined

to complete the chip family number, while the Minor Rev[7:4] and Minor Rev[3:0] must be combined to

form the complete revision number.

2014-07-02 - Gecko Family - d0001_Rev1.30 9

www.silabs.com

Page 10

Figure 3.3. Revision Number Extraction

...the world's most energy friendly microcontrollers

PID2 (0xE00FFFE8)

31:8 7:4

Minor Rev[7:4]

PID0 (0xE00FFFE0)

31:7 6:5

Fam[1:0] Fam[5:2]

Major Rev[5:0]

3:0

5:0

PID3 (0xE00FFFEC)

31:8 7:4

Minor Rev[3:0]

PID1 (0xE00FFFE4)

31:4

3:0

3:0

For the latest revision of the Gecko family, the chip family number is 0x00 and the major revision number

is 0x01. The minor revision number is to be interpreted according to Table 3.3 (p. 10) .

Table 3.3. Minor Revision Number Interpretation

Minor Rev[7:0] Revision

0x00 A

0x01 B

0x02 C

0x03 D

2014-07-02 - Gecko Family - d0001_Rev1.30 10

www.silabs.com

Page 11

4 System Processor

1 2 3 4

0

...the world's most energy friendly microcontrollers

Quick Facts

What?

The industry leading Cortex-M3 processor

from ARM is the CPU in the EFM32G

microcontrollers.

Why?

CM3 Core

Hardware divider

32- bit ALU

Single cycle

32- bit multiplier

The ARM Cortex-M3 is designed for

exceptional short response time, high

code density, and high 32-bit throughput

while maintaining a strict cost and power

consumption budget.

Control Logic

Instruction Interface Data Interface

Thumb & Thumb- 2

Decode

How?

Combined with the ultra low energy

peripherals available, the Cortex-M3 makes

the EFM32G devices perfect for 8- to 32-bit

NVIC Interface

Memory Protection Unit

applications. The processor is featuring a

Harvard architecture, 3 stage pipeline, single

cycle instructions, Thumb-2 instruction set

support, and fast interrupt handling.

4.1 Introduction

The ARM Cortex-M3 32-bit RISC processor provides outstanding computational performance and

exceptional system response to interrupts while meeting low cost requirements and low power

consumption.

The ARM Cortex-M3 implemented is revision r2p0.

4.2 Features

• Harvard Architecture

• Separate data and program memory buses (No memory bottleneck as for a single-bus system)

• 3-stage pipeline

• Thumb-2 instruction set

• Enhanced levels of performance, energy efficiency, and code density

• Single-cycle multiply and efficient divide instructions

• 32-bit multiplication in a single cycle

• Signed and unsigned divide operations between 2 and 12 cycles

• Atomic bit manipulation with bit banding

• Direct access to single bits of data

• Two 1MB bit banding regions for memory and peripherals mapping to 32MB alias regions

• Atomic operation which cannot be interrupted by other bus activities

• 1.25 DMIPS/MHz

• Memory Protection Unit

• Up to 8 protected memory regions

• 24-bit System Tick Timer for Real-Time Operating System (RTOS)

• Excellent 32-bit migration choice for 8/16 bit architecture based designs

• Simplified stack-based programmer's model is compatible with traditional ARM architecture and

retains the programming simplicity of legacy 8- and 16-bit architectures

2014-07-02 - Gecko Family - d0001_Rev1.30 11

www.silabs.com

Page 12

...the world's most energy friendly microcontrollers

• Unaligned data storage and access

• Continuous storage of data requiring different byte lengths

• Data access in a single core clock cycle

• Integrated power modes

• Sleep Now mode for immediate transfer to low power state

• Sleep on Exit mode for entry into low power state after the servicing of an interrupt

• Ability to extend power savings to other system components

• Optimized for low latency, nested interrupts

4.3 Functional Description

For a full functional description of the ARM Cortex-M3 (r2p0) implementation in the EFM32G family, the

reader is referred to the EFM32G Cortex-M3 Reference Manual.

4.3.1 Interrupt Operation

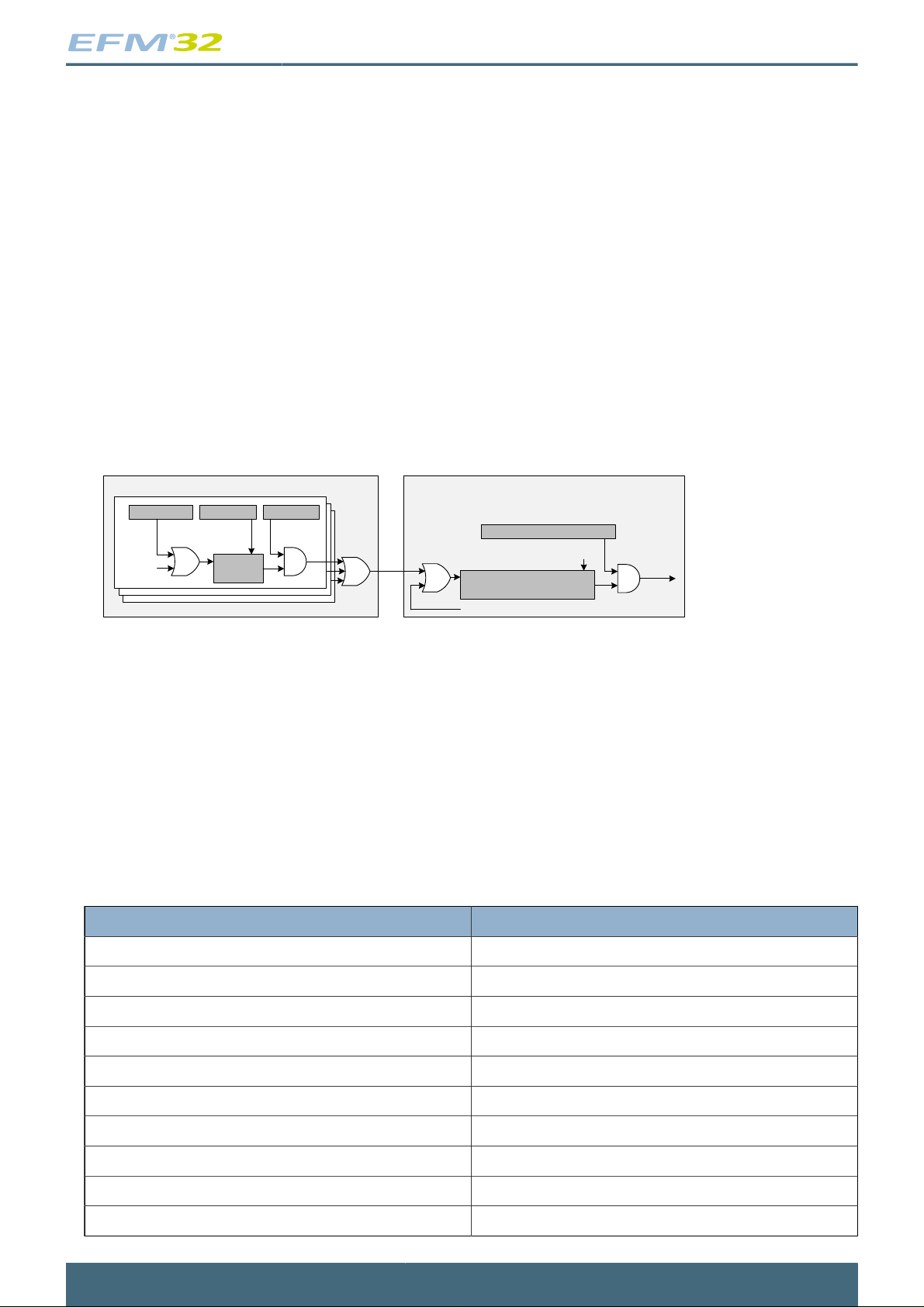

Figure 4.1. Interrupt Operation

Module Cortex- M3 NVIC

IFS[n] IFC[n]

Interrupt

condition

set clear

IF[n]

IEN[n]

IRQ

SETENA[n]/ CLRENA[n]

Active int errupt

set clear

SETPEND[n]/ CLRPEND[n]

Software generated interrupt

Interrupt

request

The EFM32G devices have up to 30 interrupt request lines (IRQ) which are connected to the Cortex-M3.

Each of these lines (shown in Table 4.1 (p. 12) ) are connected to one or more interrupt flags in one

or more modules. The interrupt flags are set by hardware on an interrupt condition. It is also possible

to set/clear the interrupt flags through the IFS/IFC registers. Each interrupt flag is then qualified with its

own interrupt enable bit (IEN register), before being OR'ed with the other interrupt flags to generate the

IRQ. A high IRQ line will set the corresponding pending bit (can also be set/cleared with the SETPEND/

CLRPEND bits in ISPR0/ICPR0) in the Cortex-M3 NVIC. The pending bit is then qualified with an enable

bit (set/cleared with SETENA/CLRENA bits in ISER0/ICER0) before generating an interrupt request to

the core. Figure 4.1 (p. 12) illustrates the interrupt system. For more information on how the interrupts

are handled inside the Cortex-M3, the reader is referred to the EFM32G Cortex-M3 Reference Manual.

Table 4.1. Interrupt Request Lines (IRQ)

IRQ # Source

0 DMA

1 GPIO_EVEN

2 TIMER0

3 USART0_RX

4 USART0_TX

5 ACMP0/ACMP1

6 ADC0

7 DAC0

8 I2C0

9 GPIO_ODD

2014-07-02 - Gecko Family - d0001_Rev1.30 12

www.silabs.com

Page 13

...the world's most energy friendly microcontrollers

IRQ # Source

10 TIMER1

11 TIMER2

12 USART1_RX

13 USART1_TX

14 USART2_RX

15 USART2_TX

16 UART0_RX

17 UART0_TX

18 LEUART0

19 LEUART1

20 LETIMER0

21 PCNT0

22 PCNT1

23 PCNT2

24 RTC

25 CMU

26 VCMP

27 LCD

28 MSC

29 AES

2014-07-02 - Gecko Family - d0001_Rev1.30 13

www.silabs.com

Page 14

...the world's most energy friendly microcontrollers

5 Memory and Bus System

1 2 3 4

0

ARM Cortex- M3

DMA Controller

Flash

RAM

EBI

Peripherals

Quick Facts

What?

A low latency memory system, including low

energy flash and RAM with data retention,

makes extended use of low-power energymodes possible.

Why?

RAM retention reduces the need for storing

data in flash and enables frequent use of the

ultra low energy modes EM2 and EM3 with

as little as 0.6 µA current consumption.

How?

Low energy and non-volatile flash memory

stores program and application data

in all energy modes and can easily be

reprogrammed in system. Low leakage RAM,

with data retention in EM0 to EM3, removes

the data restore time penalty, and the DMA

ensures fast autonomous transfers with

predictable response time.

5.1 Introduction

The EFM32G contains an AMBA AHB Bus system allowing bus masters to access the memory mapped

address space. A multilayer AHB bus matrix, using a Round-robin arbitration scheme, connects the

master bus interfaces to the AHB slaves (Figure 5.1 (p. 15) ). The bus matrix allows several AHB

slaves to be accessed simultaneously. An AMBA APB interface is used for the peripherals, which are

accessed through an AHB-to-APB bridge connected to the AHB bus matrix. The AHB bus masters are:

• Cortex-M3 ICode: Used for instruction fetches from Code memory (0x00000000 - 0x1FFFFFFF).

• Cortex-M3 DCode: Used for debug and data access to Code memory (0x00000000 - 0x1FFFFFFF).

• Cortex-M3 System: Used for instruction fetches, data and debug access to system space

(0x20000000 - 0xDFFFFFFF).

• DMA: Can access EBI, SRAM, Flash and peripherals (0x00000000 - 0xDFFFFFFF).

2014-07-02 - Gecko Family - d0001_Rev1.30 14

www.silabs.com

Page 15

Figure 5.1. EFM32G Bus System

...the world's most energy friendly microcontrollers

Cortex

ICode

DCode

System

DMA

AHB Multilayer

Bus Matrix

5.2 Functional Description

Flash

RAM

EBI

AES

AHB/APB

Bridge

Peripheral 0

Peripheral n

The memory segments are mapped together with the internal segments of the Cortex-M3 into the system

memory map shown by Figure 5.2 (p. 16)

2014-07-02 - Gecko Family - d0001_Rev1.30 15

www.silabs.com

Page 16

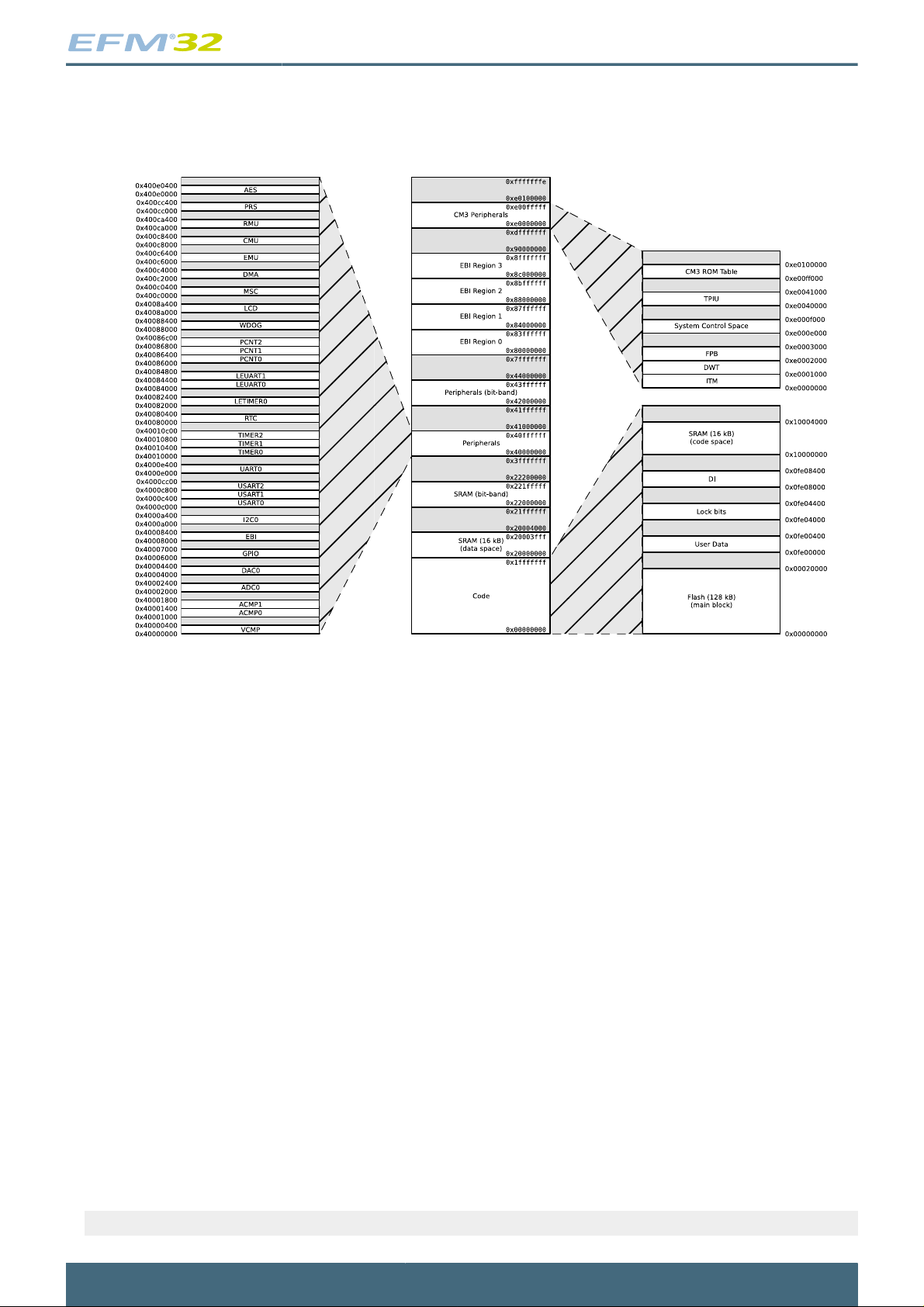

Figure 5.2. System Address Space

...the world's most energy friendly microcontrollers

The embedded SRAM is located at address 0x20000000 in the memory map of the EFM32G. When

running code located in SRAM starting at this address, the Cortex-M3 uses the System bus to fetch

instructions. This results in reduced performance as the Cortex-M3 accesses stack, other data in SRAM

and peripherals using the System bus. To be able to run code from SRAM efficiently, the SRAM is also

mapped in the code space at address 0x10000000. When running code from this space, the Cortex-M3

fetches instructions through the I/D-Code bus interface, leaving the System bus for data access. The

SRAM mapped into the code space can however only be accessed by the CPU, i.e. not the DMA.

5.2.1 Bit-banding

The SRAM bit-band alias and peripheral bit-band alias regions are located at 0x22000000 and

0x42000000 respectively. Read and write operations to these regions are converted into masked singlebit reads and atomic single-bit writes to the embedded SRAM and peripherals of the EFM32G.

The standard approach to modify a single register or SRAM bit in the aliased regions, requires software

to read the value of the byte, half-word or word containing the bit, modify the bit, and then write the byte,

half-word or word back to the register or SRAM address. Using bit-banding, this read-modify-write can

be done in a single atomic operation. As read-writeback, bit-masking and bit-shift operations are not

necessary in software, code size is reduced and execution speed improved.

The bit-band regions allows addressing each individual bit in the SRAM and peripheral areas of the

memory map. To set or clear a bit in the embedded SRAM, write a 1 or a 0 to the following address:

Memory SRAM Area Set/Clear Bit

2014-07-02 - Gecko Family - d0001_Rev1.30 16

www.silabs.com

Page 17

...the world's most energy friendly microcontrollers

bit_address = 0x22000000 + (address – 0x20000000) × 32 + bit × 4, (5.1)

where address is the address of the 32-bit word containing the bit to modify, and bit is the index of the

bit in the 32-bit word.

To modify a bit in the Peripheral area, use the following address:

Memory Peripheral Area Bit Modification

bit_address = 0x42000000 + (address – 0x40000000) × 32 + bit × 4, (5.2)

where address and bit are defined as above.

Note that the AHB-peripheral AES does not support bit-banding.

5.2.2 Peripherals

The peripherals are mapped into the peripheral memory segment, each with a fixed size address range

according to Table 5.1 (p. 17) , Table 5.2 (p. 18) and Table 5.3 (p. 19) .

Table 5.1. Memory System Core Peripherals

Core peripherals

Address range Peripheral

0x400E0400 – 0x41FFFFFF Reserved

0x400E0000 – 0x400E03FF AES

0x400CC400 – 0x400FFFFF Reserved

0x400CC000 – 0x400CC3FF PRS

0x400CA400 – 0x400CBFFF Reserved

0x400CA000 – 0x400CA3FF RMU

0x400C8400 – 0x400C9FFF Reserved

0x400C8000 – 0x400C83FF CMU

0x400C6400 – 0x400C7FFF Reserved

0x400C6000 – 0x400C63FF EMU

0x400C4000 – 0x400C5FFF Reserved

0x400C2000 – 0x400C3FFF DMA

0x400C0400 – 0x400C1FFF Reserved

0x400C0000 – 0x400C03FF MSC

2014-07-02 - Gecko Family - d0001_Rev1.30 17

www.silabs.com

Page 18

...the world's most energy friendly microcontrollers

Table 5.2. Memory System Low Energy Peripherals

Low energy peripherals

Address range Peripheral

0x4008A400 – 0x400BFFFF Reserved

0x4008A000 – 0x4008A3FF LCD

0x40088400 – 0x40089FFF Reserved

0x40088000 – 0x400883FF WDOG

0x40086C00 – 0x40087FFF Reserved

0x40086800 – 0x40086BFF PCNT2

0x40086400 – 0x400867FF PCNT1

0x40086000 – 0x400863FF PCNT0

0x40084800 – 0x40085FFF Reserved

0x40084400 – 0x400847FF LEUART1

0x40084000 – 0x400843FF LEUART0

0x40082400 – 0x40083FFF Reserved

0x40082000 – 0x400823FF LETIMER0

0x40080400 – 0x40081FFF Reserved

0x40080000 – 0x400803FF RTC

2014-07-02 - Gecko Family - d0001_Rev1.30 18

www.silabs.com

Page 19

...the world's most energy friendly microcontrollers

Table 5.3. Memory System Peripherals

Peripherals

Address range Peripheral

0x40010C00 – 0x4007FFFF Reserved

0x40010800 – 0x40010BFF TIMER2

0x40010400 – 0x400107FF TIMER1

0x40010000 – 0x400103FF TIMER0

0x4000E400 – 0x4000FFFF Reserved

0x4000E000 – 0x4000E3FF UART0

0x4000CC00 – 0x4000DFFF Reserved

0x4000C800 – 0x4000CBFF USART2

0x4000C400 – 0x4000C7FF USART1

0x4000C000 – 0x4000C3FF USART0

0x4000A400 – 0x4000BFFF Reserved

0x4000A000 – 0x4000A3FF I2C0

0x40008400 – 0x40009FFF Reserved

0x40008000 – 0x400083FF EBI

0x40007000 – 0x40007FFF Reserved

0x40006000 – 0x40006FFF GPIO

0x40004400 – 0x40005FFF Reserved

0x40004000 – 0x400043FF DAC0

0x40002400 – 0x40003FFF Reserved

0x40002000 – 0x400023FF ADC0

0x40001800 – 0x40001FFF Reserved

0x40001400 – 0x400017FF ACMP1

0x40001000 – 0x400013FF ACMP0

0x40000400 – 0x40000FFF Reserved

0x40000000 - 0x400003FF VCMP

5.2.3 Bus Matrix

The Bus Matrix connects the memory segments to the bus masters:

• Code: CPU instruction or data fetches from the code space

• System: CPU read and write to the SRAM, EBI and peripherals

• DMA: Access to EBI, SRAM, Flash and peripherals

5.2.3.1 Arbitration

The Bus Matrix uses a round-robin arbitration algorithm which enables high throughput and low latency

while starvation of simultaneous accesses to the same bus slave are eliminated. Round-robin does not

assign a fixed priority to each bus master. The arbiter does not insert any bus wait-states.

2014-07-02 - Gecko Family - d0001_Rev1.30 19

www.silabs.com

Page 20

...the world's most energy friendly microcontrollers

5.2.3.2 Access Performance

The Bus Matrix is a multi-layer energy optimized AMBA AHB compliant bus with an internal bandwidth

equal to 4 times a single AHB-bus.

The Bus Matrix accepts new transfers initiated by each master in every clock cycle without inserting

any wait-states. The slaves, however, may insert wait-states depending on their internal throughput and

the clock frequency.

The Cortex-M3, the DMA Controller, and the peripherals run on clocks that can be prescaled separately.

When accessing a peripheral which runs on a frequency equal to or faster than the HFCORECLK, the

number of wait cycles per access, in addition to master arbitration, is given by:

Memory Wait Cycles with Clock Equal or Faster than HFCORECLK

where N

slave cycles

N

is the wait cycles introduced by the slave.

cycles

= 2 + N

slave cycles

, (5.3)

When accessing a peripheral running on a clock slower than the HFCORECLK, wait-cycles are

introduced to allow the transfer to complete on the peripheral clock. The number of wait cycles per

access, in addition to master arbitration, is given by:

Memory Wait Cycles with Clock Slower than CPU

N

where N

slave cycles

is the number of wait cycles introduced by the slave.

For general register access, N

cycles

= (2 + N

slave cycles

slave cycles

= 1.

) x f

HFCORECLK/fHFPERCLK

, (5.4)

More details on clocks and prescaling can be found in Chapter 11 (p. 95) .

5.3 Access to Low Energy Peripherals (Asynchronous Registers)

5.3.1 Introduction

The Low Energy Peripherals are capable of running when the high frequency oscillator and core system

is powered off, i.e. in energy mode EM2 and in some cases also EM3. This enables the peripherals to

perform tasks while the system energy consumption is minimal.

The Low Energy Peripherals are:

• Liquid Crystal Display driver - LCD

• Low Energy Timer - LETIMER

• Low Energy UART - LEUART

• Pulse Counter - PCNT

• Real Time Counter - RTC

• Watchdog - WDOG

All Low Energy Peripherals are memory mapped, with automatic data synchronization. Because the Low

Energy Peripherals are running on clocks asynchronous to the core clock, there are some constraints

on how register accesses can be done, as described in the following sections.

2014-07-02 - Gecko Family - d0001_Rev1.30 20

www.silabs.com

Page 21

...the world's most energy friendly microcontrollers

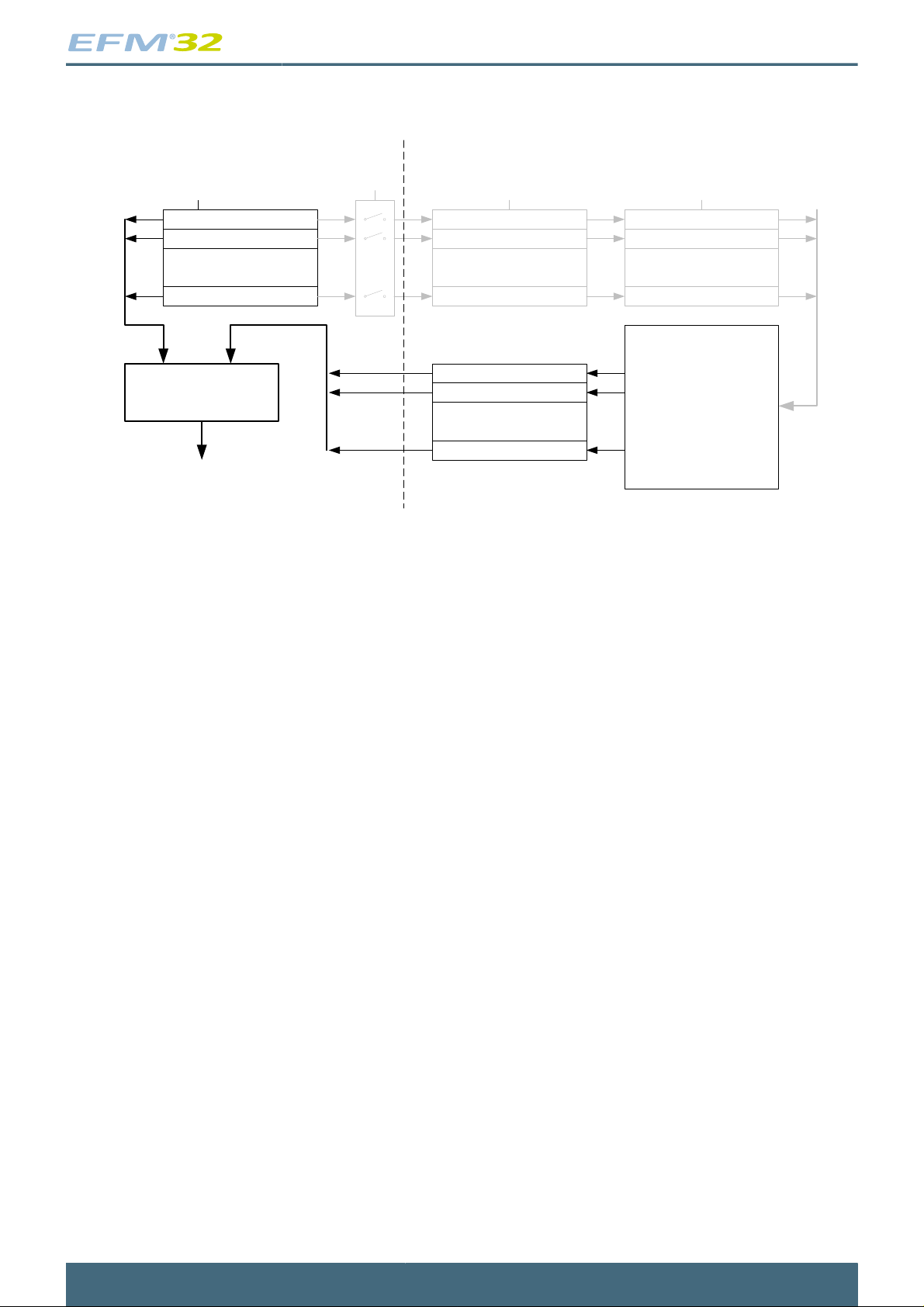

5.3.1.1 Writing

Every Low Energy Peripheral has one or more registers with data that needs to be synchronized

into the Low Energy clock domain to maintain data consistency and predictable operation. Due to

synchronization, the write operation requires 3 positive edges of the clock of the Low Energy Peripheral

being accessed. Such registers are marked "Asynchronous" in their description header.

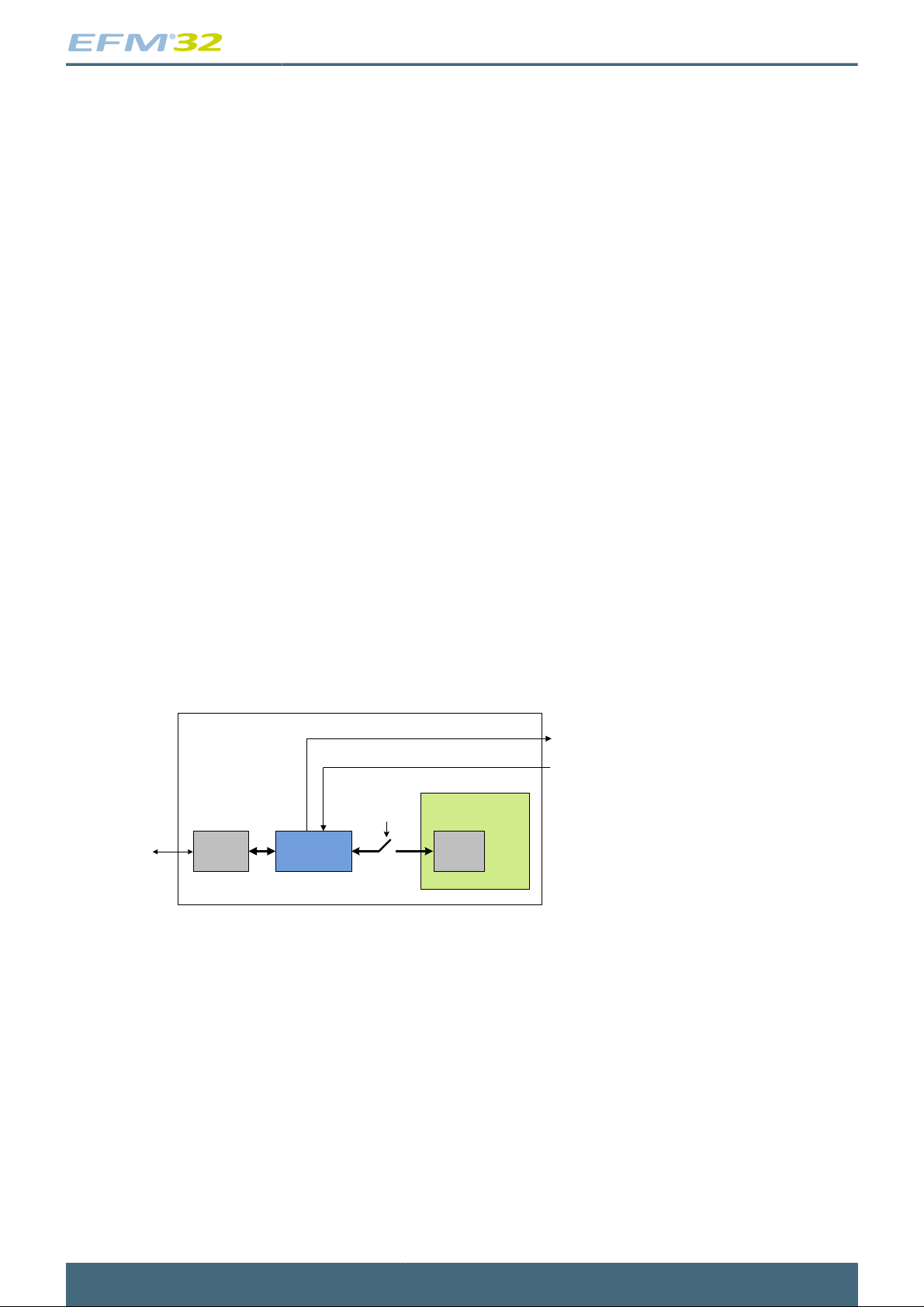

See Figure 5.3 (p. 21) for a more detailed overview of the writing operation.

After writing data to a register which value is to be synchronized into the Low Energy clock domain, a

corresponding busy flag in the <module_name>_SYNCBUSY register (e.g. RTC_SYNCBUSY) is set.

This flag is set as long as synchronization is in progress and is cleared upon completion.

Note

Subsequent writes to the same register before the corresponding busy flag is cleared is not

supported. Write before the busy flag is cleared may result in undefined behavior.

In general, the SYNCBUSY register only needs to be observed if there is a risk of multiple

write access to a register (which must be prevented). It is not required to wait until the

relevant flag in the SYNCBUSY register is cleared after writing a register. E.g EM2 can be

entered immediately after writing a register.

Figure 5.3. Write operation to Low Energy Peripherals

Core Clock Domain Low Frequency Clock Domain

Freeze

Clear 0

Clear 1

Clear n

Write[0:n]

Set 0

Set 1

Set n

Core Clock

Register 0

Register 1

.

.

.

Register n

Syncbusy Register 0

Syncbusy Register 1

.

.

.

Syncbusy Register n

5.3.1.2 Reading

Low Frequency Clock Low Frequency Clock

Synchronizer 0

Synchronizer 1

.

.

.

Synchronizer n

Synchronization Done

Register 0 Sync

Register 1 Sync

Register n Sync

.

.

.

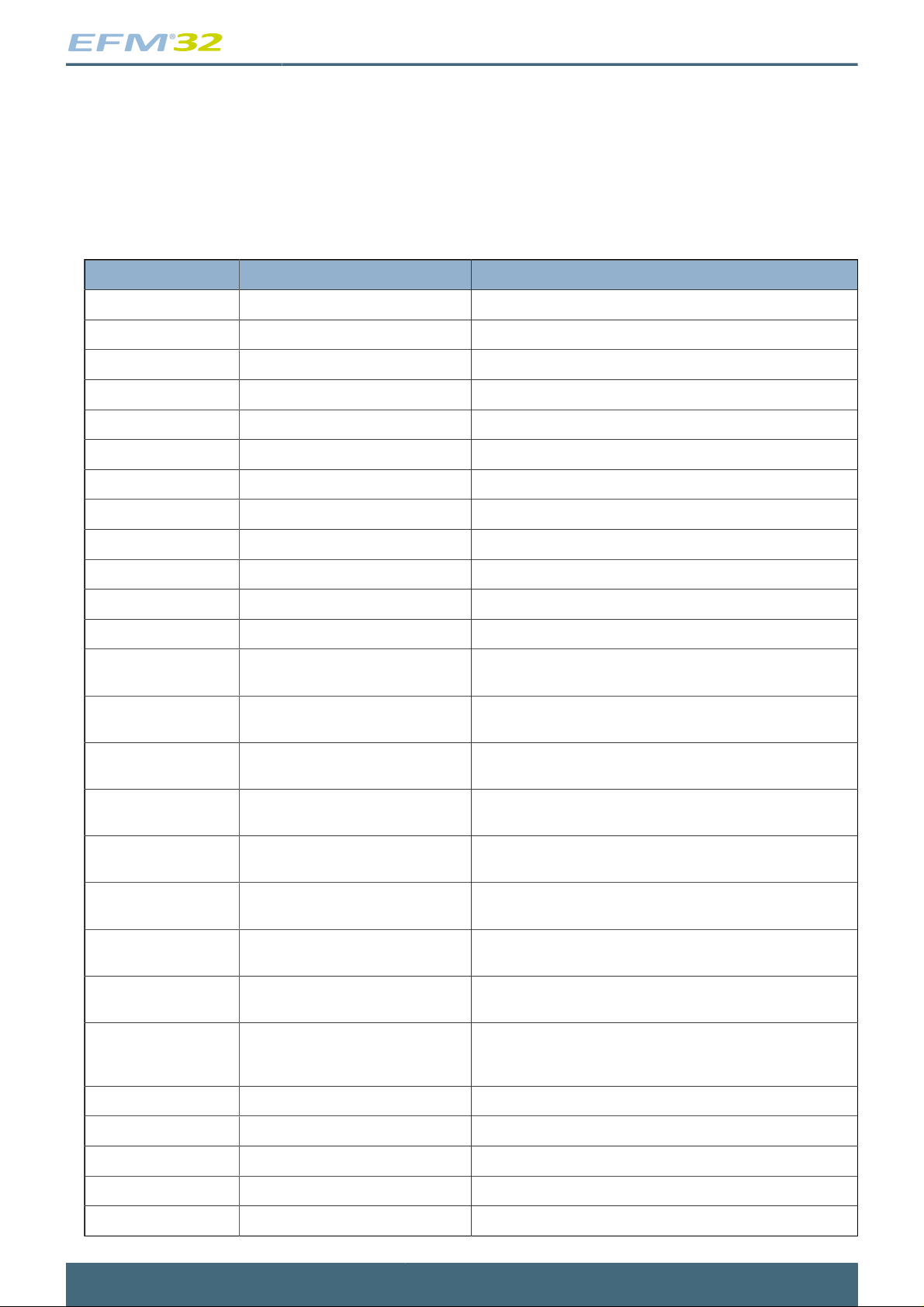

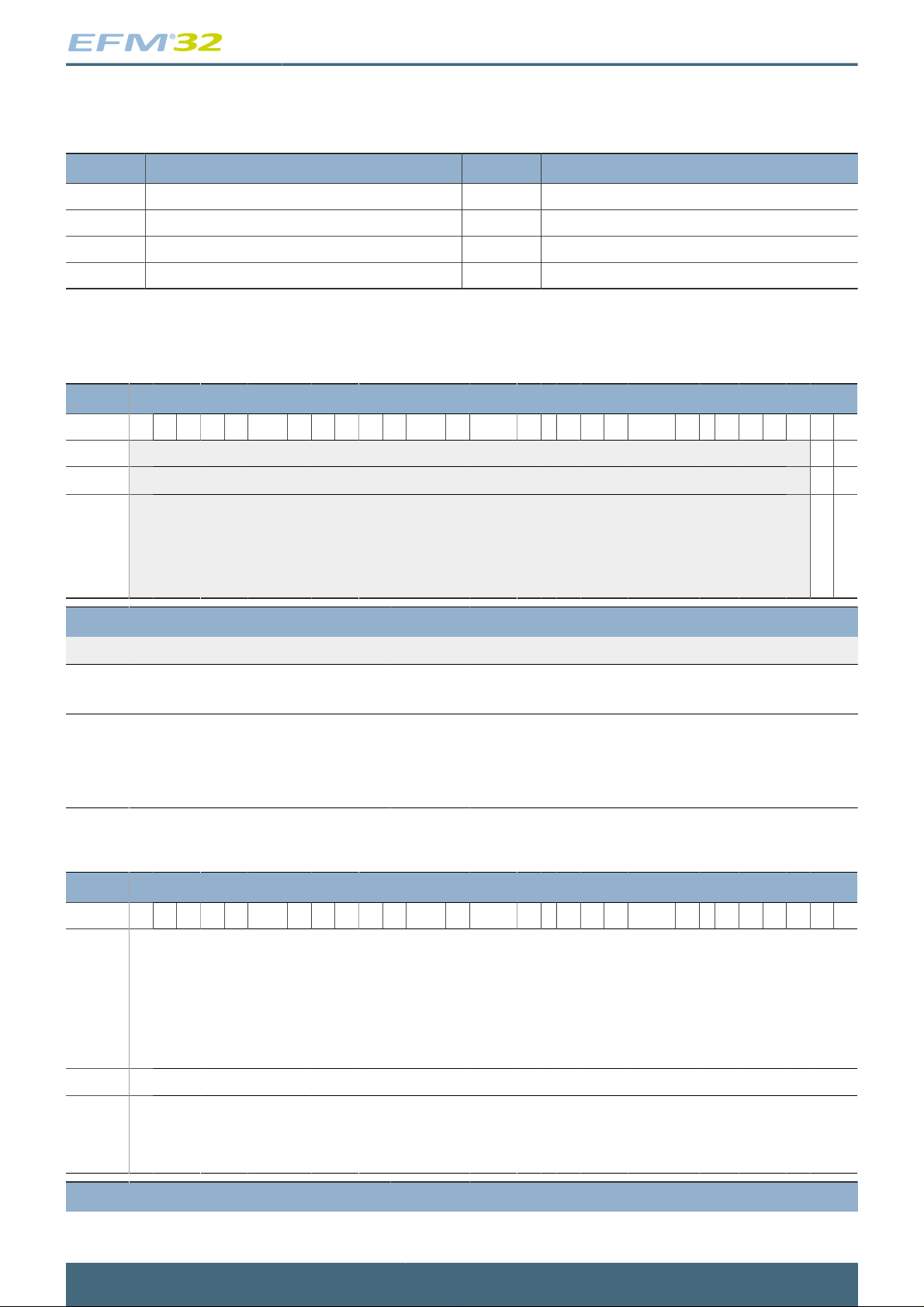

When reading from Low Energy Peripherals, the data is synchronized regardless of the originating clock

domain. Registers updated/maintained by the Low Energy Peripheral are read directly from the Low

Energy clock domain. Registers residing in the core clock domain, are read from the core clock domain.

See Figure 5.4 (p. 22) for a more detailed overview of the read operation.

Note

Writing a register and then immediately reading back the value of the register may give the

impression that the write operation is complete. This is not necessarily the case. Please

refer to the SYNCBUSY register for correct status of the write operation to the Low Energy

Peripheral.

2014-07-02 - Gecko Family - d0001_Rev1.30 21

www.silabs.com

Page 22

...the world's most energy friendly microcontrollers

Figure 5.4. Read operation from Low Energy Peripherals

Core Clock Domain Low Frequency Clock Domain

Core Clock

Freeze

Register 0

Register 1

.

.

.

Register n

Low Frequency Clock Low Frequency Clock

Synchronizer 0

Synchronizer 1

.

.

.

Synchronizer n

Register 0 Sync

Register 1 Sync

.

.

.

Register n Sync

Read

Synchronizer

Read Data

HW Status Register 0

HW Status Register 1

.

.

.

HW Status Register m

Low Energy

Peripheral

Main

Function

5.3.2 FREEZE register

For Low Energy Peripherals there is a <module_name>_FREEZE register (e.g. RTC_FREEZE),

containing a bit named REGFREEZE. If precise control of the synchronization process is required,

this bit may be utilized. When REGFREEZE is set, the synchronization process is halted, allowing

the software to write multiple Low Energy registers before starting the synchronization process, thus

providing precise control of the module update process. The synchronization process is started by

clearing the REGFREEZE bit.

5.4 Flash

The Flash retains data in any state and typically stores the application code, special user data and

security information. The Flash memory is typically programmed through the debug interface, but can

also be erased and written to from software.

• Up to 128 kB of memory

• Page size of 512 bytes (minimum erase unit)

• Minimum 20 000 erase cycles

• More than 10 years data retention at 85°C

• Lock-bits for memory protection

• Data retention in any state

5.5 SRAM

The primary task of the SRAM memory is to store application data. Additionally, it is possible to execute

instructions from SRAM, and the DMA may used to transfer data between the SRAM, Flash and

peripherals.

• Up to 16 kB memory

• Bit-band access support

• 4 kB blocks may be individually powered down when not in use

2014-07-02 - Gecko Family - d0001_Rev1.30 22

www.silabs.com

Page 23

...the world's most energy friendly microcontrollers

• Data retention of the entire memory in EM0 to EM3

5.6 Device Information (DI) Page

The DI page contains calibration values, a unique identification number and other useful data. See the

table below for a complete overview.

Table 5.4. Device Information Page Contents

DI Address Register Description

0x0FE08020 CMU_LFRCOCTRL Register reset value.

0x0FE08028 CMU_HFRCOCTRL Register reset value.

0x0FE08030 CMU_AUXHFRCOCTRL Register reset value.

0x0FE08040 ADC0_CAL Register reset value.

0x0FE08048 ADC0_BIASPROG Register reset value.

0x0FE08050 DAC0_CAL Register reset value.

0x0FE08058 DAC0_BIASPROG Register reset value.

0x0FE08060 ACMP0_CTRL Register reset value.

0x0FE08068 ACMP1_CTRL Register reset value.

0x0FE08078 CMU_LCDCTRL Register reset value.

0x0FE081B0 DI_CRC [15:0]: DI data CRC-16.

0x0FE081B2 CAL_TEMP_0 [7:0] Calibration temperature (°C).

0x0FE081B4 ADC0_CAL_1V25 [14:8]: Gain for 1V25 reference, [6:0]: Offset for 1V25

reference.

0x0FE081B6 ADC0_CAL_2V5 [14:8]: Gain for 2V5 reference, [6:0]: Offset for 2V5

reference.

0x0FE081B8 ADC0_CAL_VDD [14:8]: Gain for VDD reference, [6:0]: Offset for VDD

reference.

0x0FE081BA ADC0_CAL_5VDIFF [14:8]: Gain for 5VDIFF reference, [6:0]: Offset for 5VDIFF

reference.

0x0FE081BC ADC0_CAL_2XVDD [14:8]: Reserved (gain for this reference cannot be

calibrated), [6:0]: Offset for 2XVDD reference.

0x0FE081BE ADC0_TEMP_0_READ_1V25 [15:4] Temperature reading at 1V25 reference, [3:0]

Reserved.

0x0FE081C8 DAC0_CAL_1V25 [22:16]: Gain for 1V25 reference, [13:8]: Channel 1 offset for

1V25 reference, [5:0]: Channel 0 offset for 1V25 reference.

0x0FE081CC DAC0_CAL_2V5 [22:16]: Gain for 2V5 reference, [13:8]: Channel 1 offset for

2V5 reference, [5:0]: Channel 0 offset for 2V5 reference.

0x0FE081D0 DAC0_CAL_VDD [22:16]: Reserved (gain for this reference cannot be

calibrated), [13:8]: Channel 1 offset for VDD reference, [5:0]:

Channel 0 offset for VDD reference.

0x0FE081D4 RESERVED [31:0] Reserved

0x0FE081D8 RESERVED [31:0] Reserved

0x0FE081DC HFRCO_CALIB_BAND_1 [7:0]: Tuning for the 1.2 MHZ HFRCO band.

0x0FE081DD HFRCO_CALIB_BAND_7 [7:0]: Tuning for the 6.6 MHZ HFRCO band.

0x0FE081DE HFRCO_CALIB_BAND_11 [7:0]: Tuning for the 11 MHZ HFRCO band.

2014-07-02 - Gecko Family - d0001_Rev1.30 23

www.silabs.com

Page 24

...the world's most energy friendly microcontrollers

DI Address Register Description

0x0FE081DF HFRCO_CALIB_BAND_14 [7:0]: Tuning for the 14 MHZ HFRCO band.

0x0FE081E0 HFRCO_CALIB_BAND_21 [7:0]: Tuning for the 21 MHZ HFRCO band.

0x0FE081E1 HFRCO_CALIB_BAND_28 [7:0]: Tuning for the 28 MHZ HFRCO band.

0x0FE081E7 MEM_INFO_PAGE_SIZE [7:0] Flash page size in bytes coded as 2 ^

((MEM_INFO_PAGE_SIZE + 10) & 0xFF). Ie. the value

0xFF = 512 bytes.

0x0FE081F0 UNIQUE_0 [31:0] Unique number.

0x0FE081F4 UNIQUE_1 [63:32] Unique number.

0x0FE081F8 MEM_INFO_FLASH [15:0]: Flash size, kbyte count as unsigned integer (eg.

128).

0x0FE081FA MEM_INFO_RAM [15:0]: Ram size, kbyte count as unsigned integer (eg. 16).

0x0FE081FC PART_NUMBER [15:0]: EFM32 part number as unsigned integer (eg. 230).

0x0FE081FE PART_FAMILY [7:0]: EFM32 part family number (Gecko = 71, Giant Gecko

= 72, Tiny Gecko = 73, Leopard Gecko=74, Wonder

Gecko=75).

0x0FE081FF PROD_REV [7:0]: EFM32 Production ID.

2014-07-02 - Gecko Family - d0001_Rev1.30 24

www.silabs.com

Page 25

6 DBG - Debug Interface

1 2 3 4

0

ARM Cortex- M3

DBG

Debug Data

...the world's most energy friendly microcontrollers

Quick Facts

What?

The DBG (Debug Interface) is used to

program and debug EFM32G devices.

Why?

The Debug Interface makes it easy to reprogram and update the system in the field,

and allows debugging with minimal I/O pin

usage.

How?

The Cortex-M3 supports advanced

debugging features. EFM32G devices

only use two port pins for debugging or

programming. The internal and external state

of the system can be examined with debug

extensions supporting instruction or data

access break- and watch points.

6.1 Introduction

The EFM32G devices include hardware debug support through a 2-pin serial-wire debug (SWD)

interface. In addition, there is also a Serial Wire Viewer pin which can be used to output profiling

information, data trace and software-generated messages.

For more technical information about the debug interface the reader is referred to:

• ARM Cortex-M3 Technical Reference Manual

• ARM CoreSight Components Technical Reference Manual

• ARM Debug Interface v5 Architecture Specification

6.2 Features

• Flash Patch and Breakpoint (FPB) unit

• Implement breakpoints and code patches

• Data Watch point and Trace (DWT) unit

• Implement watch points, trigger resources and system profiling

• Instrumentation Trace Macrocell (ITM)

• Application-driven trace source that supports printf style debugging

6.3 Functional Description

There are three debug pins and four trace pins available on the device. Operation of these pins are

described in the following section.

6.3.1 Debug Pins

The following pins are the debug connections for the device:

2014-07-02 - Gecko Family - d0001_Rev1.30 25

www.silabs.com

Page 26

...the world's most energy friendly microcontrollers

• Serial Wire Clock input (SWCLK): This pin is enabled after reset and has a built-in pull down.

• Serial Wire Data Input/Output (SWDIO): This pin is enabled after reset and has a built-in pull-up.

• Serial Wire Viewer (SWV): This pin is disabled after reset.

The debug pins can be enabled and disabled through GPIO_ROUTE, see Section 28.3.2.1 (p. 429)

. Please remeberer that upon disabling, debug contact with the device is lost. Also note that, because

the debug pins have pull-down and pull-up enabled by default, leaving them enabled might increase the

current consumption with up to 200 µA if left connected to supply or ground.

6.3.2 Debug and EM2/EM3

Leaving the debugger connected when issuing a WFI or WFE to enter EM2 or EM3 will make the system

enter a special EM2. This mode differs from regular EM2 and EM3 in that the high frequency clocks

are still enabled, and certain core functionality is still powered in order to maintain debug-functionality.

Because of this, the current consumption in this mode is closer to EM1 and it is therefore important to

disconnect the debugger before doing current consumption measurements.

6.4 Debug Lock and Device Erase

The debug access to the Cortex-M3 is locked by clearing the Debug Lock Word (DLW) and resetting

the device, see Section 7.3.2 (p. 32) .

When debug access is locked, the debug interface remains accessible but the connection to the CortexM3 core and the whole bus-system is blocked as shown in Figure 6.2 (p. 27) . This mechanism is

controlled by the Authentication Access Port (AAP) as illustrated by Figure 6.1 (p. 26) . The AAP is

only accessible from a debugger and not from the core.

Figure 6.1. AAP - Authentication Access Port

DEVICEERASE

ERASEBUSY

Cortex

SerialWire

debug

interface

DLW[3:0] = = 0xF

SW-DP AHB-AP

Authentication

Access Port

(AAP)

The debugger can access the AAP-registers, and only these registers just after reset, for the time of the

AAP-window outlined in Figure 6.2 (p. 27) . If the device is locked, access to the core and bus-system

is blocked even after code execution starts, and the debugger can only access the AAP-registers. If the

device is not locked, the AAP is no longer accessible after code execution starts, and the debugger can

access the core and bus-system normally.

2014-07-02 - Gecko Family - d0001_Rev1.30 26

www.silabs.com

Page 27

Figure 6.2. Device Unlock

Reset

Locked

No access

150 us

...the world's most energy friendly microcontrollers

Program

execution

AAP

Program

execution

Unlocked

No access

AAP

47 us

Cortex

If the device is locked, it can be unlocked by writing a valid key to the AAP_CMDKEY register and then

setting the DEVICEERASE bit of the AAP_CMD register via the debug interface. The commands are not

executed before AAP_CMDKEY is invalidated, so this register should be cleared to to start the erase

operation. This operation erases the main block of flash, all lock bits are reset and debug access through

the AHB-AP is enabled. The operation takes 40 ms to complete. Note that the SRAM contents will also

be deleted during a device erase, while the UD-page is not erased.

Even if the device is not locked, the can device can be erased through the AAP, using the above

procedure during the AAP window. This can be useful if the device has been programmed with code that,

e.g., disables the debug interface pins on start-up, or does something else that prevents communication

with a debugger.

If the device is locked, the debugger may read the status from the AAP_STATUS register. When the

ERASEBUSY bit is set low after DEVICEERASE of the AAP_CMD register is set, the debugger may

set the SYSRESETREQ bit in the AAP_CMD register. After reset, the debugger may resume a normal

debug session through the AHB-AP. If the device is not locked, the device erase starts when the AAP

window closes, so it is not possible to poll the status.

2014-07-02 - Gecko Family - d0001_Rev1.30 27

www.silabs.com

Page 28

...the world's most energy friendly microcontrollers

6.5 Register Map

The offset register address is relative to the registers base address.

Offset Name Type Description

0x000 AAP_CMD W1 Command Register

0x004 AAP_CMDKEY W1 Command Key Register

0x008 AAP_STATUS R Status Register

0x0FC AAP_IDR R AAP Identification Register

6.6 Register Description

6.6.1 AAP_CMD - Command Register

Offset Bit Position

0x000

Reset

Access

Name

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

11

9

8

7

6

10

5

Bit Name Reset Access Description

31:2 Reserved

1 SYSRESETREQ 0 W1 System Reset Request

A system reset request is generated when set to 1. This register is write enabled from the AAP_CMDKEY register.

0 DEVICEERASE 0 W1 Erase the Flash Main Block, SRAM and Lock Bits

When set, all data and program code in the main block is erased, the SRAM is cleared and then the Lock Bit (LB) page is erased.

This also includes the Debug Lock Word (DLW), causing debug access to be enabled after the next reset. The information block

User Data page (UD) is left unchanged, but the User data page Lock Word (ULW) is erased. This register is write enabled from

the AAP_CMDKEY register.

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

6.6.2 AAP_CMDKEY - Command Key Register

4

3

2

1

0

0

0

W1

W1

SYSRESETREQ

DEVICEERASE

Offset Bit Position

0x004

Reset

Access

Name

31

30

29

28

272625

24

23

22

21

201918

17

16

15

0x00000000

W1

WRITEKEY

141312

Bit Name Reset Access Description

31:0 WRITEKEY 0x00000000 W1 CMD Key Register

2014-07-02 - Gecko Family - d0001_Rev1.30 28

9

8

7

6

5

4

3

2

1

11

10

0

www.silabs.com

Page 29

...the world's most energy friendly microcontrollers

Bit Name Reset Access Description

The key value must be written to this register to write enable the AAP_CMD register. After AAP_CMD is written, this register should

be cleared to excecute the command.

Value Mode Description

0xCFACC118 WRITEEN Enable write to AAP_CMD

6.6.3 AAP_STATUS - Status Register

Offset Bit Position

0x008

Reset

Access

Name

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

11

10

Bit Name Reset Access Description

31:1 Reserved

0 ERASEBUSY 0 R Device Erase Command Status

This bit is set when a device erase is executing.

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

6.6.4 AAP_IDR - AAP Identification Register

Offset Bit Position

0x0FC

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

11

10

9

8

7

6

5

4

3

2

1

0

0

R

ERASEBUSY

9

8

7

6

5

4

3

2

1

0

Reset

0x16E60001

Access

Name

R

ID

Bit Name Reset Access Description

31:0 ID 0x16E60001 R AAP Identification Register

Access port identification register in compliance with the ARM ADI v5 specification (JEDEC Manufacturer ID) .

2014-07-02 - Gecko Family - d0001_Rev1.30 29

www.silabs.com

Page 30

...the world's most energy friendly microcontrollers

7 MSC - Memory System Controller

What?

The user can perform Flash memory read,

read configuration and write operations

through the Memory System Controller

(MSC) .

Why?

1 2 3 4

0

01000101011011100110010101110010

01100111011110010010000001001101

01101001011000110111001001101111

00100000011100100111010101101100

01100101011100110010000001110100

01101000011001010010000001110111

01101111011100100110110001100100

00100000011011110110011000100000

01101100011011110111011100101101

01100101011011100110010101110010

01100111011110010010000001101101

01101001011000110111001001101111

01100011011011110110111001110100

01110010011011110110110001101100

01100101011100100010000001100100

01100101011100110110100101100111

01101110001000010100010101101110

The MSC allows the application code, user

data and flash lock bits to be stored in nonvolatile Flash memory. Certain memory

system functions, such as program memory

wait-states and bus faults are also configured

from the MSC peripheral register interface,

giving the developer the ability to dynamically

customize the memory system performance,

security level, energy consumption and error

handling capabilities to the requirements at

hand.

How?

The MSC integrates a low-energy Flash

IP with a charge pump, enabling minimum

energy consumption while eliminating the

need for external programming voltage to

erase the memory. An easy to use write and

erase interface is supported by an internal,

fixed-frequency oscillator and autonomous

flash timing and control reduces software

complexity while not using other timer

resources.

Quick Facts

Application code may dynamically scale

between high energy optimization and

high code execution performance through

advanced read modes.

7.1 Introduction

The Memory System Controller (MSC) is the program memory unit of the EFM32G microcontroller. The

flash memory is readable and writable from both the Cortex-M3 and DMA. The flash memory is divided

into two blocks; the main block and the information block. Program code is normally written to the main

block. Additionally, the information block is available for special user data and flash lock bits. There is

also a read-only page in the information block containing system and device calibration data. Read and

write operations are supported in the energy modes EM0 and EM1.

7.2 Features

• AHB read interface

• Scalable access performance to optimize the Cortex-M3 code interface

• Zero wait-state access up to 16 MHz and one wait-state for 16 MHz and above

• Advanced energy optimization functionality

2014-07-02 - Gecko Family - d0001_Rev1.30 30

www.silabs.com

Page 31

...the world's most energy friendly microcontrollers

• Conditional branch target prefetch suppression

• Cortex-M3 disfolding of if-then (IT) blocks

• DMA read support in EM0 and EM1

• Command and status interface

• Flash write and erase

• Accessible from Cortex-M3 in EM0

• DMA write support in EM0 and EM1

• Core clock independent Flash timing

• Internal oscillator and internal timers for precise and autonomous Flash timing

• General purpose timers are not occupied during Flash erase and write operations

• Need for special time scaling registers eliminated

• Configurable interrupt erase abort

• Improved interrupt predictability

• Memory and bus fault control

• Security features

• Lockable debug access

• Page lock bits

• User data lock bits

• End-of-write and end-of-erase interrupts

7.3 Functional Description

The size of the main block is device dependent. The largest size available is 128 kB (256 pages).

The information block has 512 bytes available for user data. The information block also contains chip

configuration data located in a reserved area. The main block is mapped to address 0x00000000 and

the information block is mapped to address 0x0FE00000. Table 7.1 (p. 31) outlines how the Flash

is mapped in the memory space. All Flash memory is organized into 512 byte pages.

Table 7.1. MSC Flash Memory Mapping

Block Page Base address Write/Erase by Software

readable

1

Main

Reserved - 0x00020000 - - Reserved for flash

Information

0 0x00000000 Software, debug Yes

. Software, debug Yes

255 0x0001FE00 Software, debug Yes

0 0x0FE00000 Software, debug Yes User Data (UD) 512 B

- 0x0FE00200 - - Reserved

1 0x0FE04000 Debug only Yes Lock Bits (LB) 512 B

Purpose/Name Size

User code and data 16 KB - 128 kB

~24 MB

expansion

- 0x0FE04200 - - Reserved

2 0x0FE08000 - Yes Device Information

(DI)

- 0x0FE08200 - - Reserved

Reserved - 0x0FE10000 - - Reserved for flash

expansion

1

Block/page erased by a device erase

2014-07-02 - Gecko Family - d0001_Rev1.30 31

512 B

Rest of code

space

www.silabs.com

Page 32

...the world's most energy friendly microcontrollers

7.3.1 User Data (UD) Page Description

This is the user data page in the information block. The page can be erased and written by software. The

page is erased by the ERASEPAGE command of the MSC_WRITECMD register. Note that the page is

not erased by a device erase operation. The device erase operation is described in Section 6.4 (p. 26) .

7.3.2 Lock Bits (LB) Page Description

This page contains the following information:

• Debug Lock Word (DLW)

• User data page Lock Word (ULW)

• Main block Page Lock Words (PLWs)

The words in this page are organized as shown in Table 7.2 (p. 32) :

Table 7.2. Lock Bits Page Structure

127 DLW

126 ULW

N PLW[N]

… …

1 PLW[1]

0 PLW[0]

Word 127 is the debug lock word (DLW). Bit 0 of this word is the debug lock bit. If this bit is 1, then

debug access is enabled. Debug access to the core is disabled from power-on reset until the DLW is

evaluated immediately before the Cortex-M3 starts execution of the user application code. If the bit is

0, then debug access to the core remains blocked.

Word 126 is the user page lock word (ULW). Bit 0 of this word is the page lock bit. The lock bits can

be reset by a device erase operation initiated from the Authentication Access Port (AAP) registers. The

AAP is described in more detail in Section 6.4 (p. 26) . Note that the AAP is only accessible from the

debug interface, and cannot be accessed from the Cortex-M3 core.

There are 32 page lock bits per page lock word (PLW). Bit 0 refers to the first page and bit 31 refers to

the last page within a PLW. Thus, PLW[0] contains lock bits for page 0-31 in the main block. Similarly,

PLW[1] contains lock bits for page 32-63 and so on. A page is locked when the bit is 0. A locked page

cannot be erased or written.

The lock bits can be reset by a device erase operation initiated from the Authentication Access Port

(AAP) registers. The AAP is described in more detail in Section 6.4 (p. 26) . Note that the AAP is only

accessible from the debug interface, and cannot be accessed from the Cortex-M3 core.

7.3.3 Device Information (DI) Page

This read-only page holds the calibration data for the oscillator and other analog peripherals from the

production test as well as a unique device ID. The page is further described in Section 5.6 (p. 23) .

7.3.4 Post-reset Behavior

Calibration values are automatically written to registers by the MSC before application code startup. The

values are also available to read from the DI page for later reference by software. Other information

such as the device ID and production date is also stored in the DI page and is readable from software.

2014-07-02 - Gecko Family - d0001_Rev1.30 32

www.silabs.com

Page 33

...the world's most energy friendly microcontrollers

7.3.4.1 One Wait-state Access

After reset, the HFCORECLK is normally 14 MHz from the HFRCO and the MODE field of the

MSC_READCTRL register is set to WS1 (one wait-state). The reset value must be WS1 as an

uncalibrated HFRCO may produce a frequency higher than 16 MHz. Software must not select a zero

wait-state mode unless the clock is guaranteed to be 16 MHz or below, otherwise the resulting behavior

is undefined. If a HFCORECLK frequency above 16 MHz is to be set by software, the MODE field of

the MSC_READCTRL register must be set to WS1 or WS1SCBTP before the core clock is switched to

the higher frequency clock source.

When changing to a lower frequency, the MODE field of the MSC_READCTRL register can be set to

WS0 or WS0SCBTP, but only after the frequency transition is completed. If the HFRCO is used, wait

until the oscillator is stable on the new frequency. Otherwise, the behavior is unpredictable.

7.3.4.2 Zero Wait-state Access

At 16 MHz and below, read operations from flash may be performed without any wait-states. Zero waitstate access greatly improves code execution performance at frequencies from 16 MHz and below.

By default, the Cortex-M3 uses speculative prefetching and If-Then block folding to maximize code

execution performance at the cost of additional flash accesses and energy consumption.

7.3.4.3 Suppressed Conditional Branch Target Prefetch (SCBTP)

MSC offers a special instruction fetch mode which optimizes energy consumption by cancelling CortexM3 conditional branch target prefetches. Normally, the Cortex-M3 core prefetches both the next

sequential instruction and the instruction at the branch target address when a conditional branch

instruction reaches the pipeline decode stage. This prefetch scheme improves performance while one

extra instruction is fetched from memory at each conditional branch, regardless of whether the branch is

taken or not. To optimize for low energy, the MSC can be configured to cancel these speculative branch

target prefetches. With this configuration, energy consumption is more optimal, as the branch target

instruction fetch is delayed until the branch condition is evaluated.

The performance penalty with this mode enabled is source code dependent, but is normally less than

1% for core frequencies from 16 MHz and below. To enable the mode at frequencies from 16 MHz and

below write WS0SCBTP to the MODE field of the MSC_READCTRL register. For frequencies above 16

MHz, use the WS1SCBTP mode. An increased performance penalty per clock cycle must be expected

compared to WS0SCBTP mode. The performance penalty in WS1SCBTP mode depends greatly on the

density and organization of conditional branch instructions in the code.

7.3.4.4 Cortex-M3 If-Then Block Folding

The Cortex-M3 offers a mechanism known as if-then block folding. This is a form of speculative

prefetching where small if-then blocks are collapsed in the prefetch buffer if the condition evaluates to

false. The instructions in the block then appear to execute in zero cycles. With this scheme, performance

is optimized at the cost of higher energy consumption as the processor fetches more instructions from

memory than it actually executes. To disable the mode, write a 1 to the DISFOLD bit in the NVIC Auxiliary

Control Register; see the Cortex-M3 Technical Reference Manual for details. Normally, it is expected

that this feature is most efficient at core frequencies above 16 MHz. Folding is enabled by default.

7.3.5 Erase and Write Operations

Both page erase and write operations require that the address is written into the MSC_ADDRB register.

For erase operations, the address may be any within the page to be erased. Load the address by

writing 1 to the LADDRIM bit in the MSC_WRITECMD register. The LADDRIM bit only has to be written

once when loading the first address. After each word is written the internal address register ADDR

will be incremented automatically by 4. The INVADDR bit of the MSC_STATUS register is set if the

loaded address is outside the flash and the LOCKED bit of the MSC_STATUS register is set if the page

2014-07-02 - Gecko Family - d0001_Rev1.30 33

www.silabs.com

Page 34

...the world's most energy friendly microcontrollers

addressed is locked. Any attempts to command erase of or write to the page are ignored if INVADDR

or the LOCKED bits of the MSC_STATUS register are set.

When a word is written to the MSC_WDATA register, the WDATAREADY bit of the MSC_STATUS

register is cleared. When this status bit is set, software or DMA may write the next word.

A single word write is commanded by setting the WRITEONCE bit of the MSC_WRITECMD register.

The operation is complete when the BUSY bit of the MSC_STATUS register is cleared and control of

the flash is handed back to the AHB interface, allowing application code to resume execution.

For a DMA write the software must write the first word to the MSC_WDATA register and then set the

WRITETRIG bit of the MSC_WRITECMD register. DMA triggers when the WDATAREADY bit of the

MSC_STATUS register is set.

It is possible to write words twice between each erase by keeping at 1 the bits that are not to be changed.

Let us take as an example writing two 16 bit values, 0xAAAA and 0x5555. To safely write them in the

same flash word this method can be used:

• Write 0xFFFFAAAA (word in flash becomes 0xFFFFAAAA)

• Write 0x5555FFFF (word in flash becomes 0x5555AAAA)

Note

Note

The WRITEONCE, WRITETRIG and ERASEPAGE bits in the MSC_WRITECMD register

cannot safely be written from code in Flash. It is recommended to place a small code

section in RAM to set these bits and wait for the operation to complete. Also note that

DMA transfers to or from any other address in Flash while a write or erase operation is in

progress will produce unpredictable results.

The MSC_WDATA and MSC_ADDRB registers are not retained when entering EM2 or

lower energy modes.

2014-07-02 - Gecko Family - d0001_Rev1.30 34

www.silabs.com

Page 35

...the world's most energy friendly microcontrollers

7.4 Register Map

The offset register address is relative to the registers base address.

Offset Name Type Description

0x000 MSC_CTRL RW Memory System Control Register

0x004 MSC_READCTRL RW Read Control Register

0x008 MSC_WRITECTRL RW Write Control Register

0x00C MSC_WRITECMD W1 Write Command Register

0x010 MSC_ADDRB RW Page Erase/Write Address Buffer

0x018 MSC_WDATA RW Write Data Register

0x01C MSC_STATUS R Status Register

0x02C MSC_IF R Interrupt Flag Register

0x030 MSC_IFS W1 Interrupt Flag Set Register

0x034 MSC_IFC W1 Interrupt Flag Clear Register

0x038 MSC_IEN RW Interrupt Enable Register

0x03C MSC_LOCK RW Configuration Lock Register

7.5 Register Description

7.5.1 MSC_CTRL - Memory System Control Register

Offset Bit Position

0x000

Reset

Access

Name

Bit Name Reset Access Description

31:1 Reserved

0 BUSFAULT 1 RW Bus Fault Response Enable

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

11

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

When this bit is set, the memory system generates bus error response.

Value Mode Description

0 GENERATE A bus fault is generated on access to unmapped code and system space.

1 IGNORE Accesses to unmapped address space is ignored.

9

8

7

6

5

4

3

2

1

10

0

1

RW

BUSFAULT

7.5.2 MSC_READCTRL - Read Control Register

Offset Bit Position

0x004

Reset

Access

Name

2014-07-02 - Gecko Family - d0001_Rev1.30 35

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

9

8

7

6

5

4

3

2

1

11

10

0

0x1

RW

MODE

www.silabs.com

Page 36

...the world's most energy friendly microcontrollers

Bit Name Reset Access Description

31:3 Reserved

2:0 MODE 0x1 RW Read Mode

If software wants to set a core clock frequency above 16 MHz, this register must be set to WS1 or WS1SCBTP before the core

clock is switched to the higher frequency. When changing to a lower frequency, this register can be set to WS0 or WS0SCBTP

after the frequency transition has been completed. After reset, the core clock is 14 MHz from the HFRCO but the MODE field of

MSC_READCTRL register is set to WS1. This is because the HFRCO may produce a frequency above 16 MHz before it is calibrated.

If the HFRCO is used as clock source, wait until the oscillator is stable on the new frequency to avoid unpredictable behavior.

Value Mode Description

0 WS0 Zero wait-states inserted in fetch or read transfers.

1 WS1 One wait-state inserted for each fetch or read transfer. This mode is required for a core

2 WS0SCBTP Zero wait-states inserted with the Suppressed Conditional Branch Target Prefetch

3 WS1SCBTP One wait-state access with SCBTP enabled.

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

frequency above 16 MHz.

(SCBTP) function enabled. SCBTP saves energy by delaying the Cortex' conditional

branch target prefetches until the conditional branch instruction is in the execute stage.

When the instruction reaches this stage, the evaluation of the branch condition is

completed and the core does not perform a speculative prefetch of both the branch

target address and the next sequential address. With the SCBTP function enabled,

one instruction fetch is saved for each branch not taken, with a negligible performance

penalty.

7.5.3 MSC_WRITECTRL - Write Control Register

Offset Bit Position

0x008

Reset

Access

Name

Bit Name Reset Access Description

31:2 Reserved

1 IRQERASEABORT 0 RW Abort Page Erase on Interrupt

0 WREN 0 RW Enable Write/Erase Controller

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

11

10

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

When this bit is set to 1, any Cortex interrupt aborts any current page erase operation. Executing that interrupt vector from Flash

will halt the CPU.

When this bit is set, the MSC write and erase functionality is enabled.

9

8

7

6

5

4

3

2

1

0

0

0

RW

RW

WREN

IRQERASEABORT

7.5.4 MSC_WRITECMD - Write Command Register

Offset Bit Position

0x00C

Reset

Access

Name

2014-07-02 - Gecko Family - d0001_Rev1.30 36

31

30

29

28

272625

24

23

22

21

201918

17

16

15

141312

9

8

7

6

5

4

3

2

1

11

10

0

0

0

W1

W1

W1

WRITETRIG

WRITEEND

WRITEONCE

0

0

0

W1

W1

LADDRIM

ERASEPAGE

www.silabs.com

Page 37

...the world's most energy friendly microcontrollers

Bit Name Reset Access Description

31:5 Reserved

4 WRITETRIG 0 W1 Word Write Sequence Trigger

Functions like MSC_CMD_WRITEONCE, but will set MSC_STATUS_WORDTIMEOUT if no new data is written to MSC_WDATA

within the 30 µs timeout.

3 WRITEONCE 0 W1 Word Write-Once Trigger

Start write of the first word written to MSC_WDATA, then add 4 to ADDR and write the next word if available within a 30 µs timeout.

When ADDR is incremented past the page boundary, ADDR is set to the base of the page.

2 WRITEEND 0 W1 End Write Mode

Write 1 to end write mode when using the WRITETRIG command.

1 ERASEPAGE 0 W1 Erase Page

Erase any user defined page selected by the MSC_ADDRB register. The WREN bit in the MSC_WRITECTRL register must be set

in order to use this command.

0 LADDRIM 0 W1 Load MSC_ADDRB into ADDR

Load the internal write address register ADDR from the MSC_ADDRB register. The internal address register ADDR is incremented

automatically by 4 after each word is written. When ADDR is incremented past the page boundary, ADDR is set to the base of the page.

To ensure compatibility with future devices, always write bits to 0. More information in Section 2.1 (p. 3)

7.5.5 MSC_ADDRB - Page Erase/Write Address Buffer

Offset Bit Position

0x010

Reset

Access

Name

31

30

29

28

272625

24

23

22

21

201918

17

16

15

0x00000000

RW

ADDRB

141312

11

9

10

Bit Name Reset Access Description

31:0 ADDRB 0x00000000 RW Page Erase or Write Address Buffer

This register holds the page address for the erase or write operation. This register is loaded into the internal MSC_ADDR register

when the LADDRIM field in MSC_WRITECMD is set. The MSC_ADDR register is not readable. This register is not retained when

entering EM2 or lower energy modes.

7.5.6 MSC_WDATA - Write Data Register

8

7

6

5

4

3

2

1

0

Offset Bit Position

0x018

Reset

Access

Name

2014-07-02 - Gecko Family - d0001_Rev1.30 37

31

30

29

28

272625

24

23

22

21

201918

17

16

15

0x00000000

RW

WDATA

141312

9

8

7

6

5

4

3

2

1

11

10

0

www.silabs.com

Page 38

...the world's most energy friendly microcontrollers

Bit Name Reset Access Description

31:0 WDATA 0x00000000 RW Write Data

The data to be written to the address in MSC_ADDR. This register must be written when the WDATAREADY bit of MSC_STATUS

is set, otherwise the data is ignored. This register is not retained when entering EM2 or lower energy modes.

7.5.7 MSC_STATUS - Status Register

Offset Bit Position

0x01C

Reset

Access

Name

31

30

29

28

272625

24

23

22

21

201918

17