Page 1

C8051F120/1/2/3/4/5/6/7

High-Speed Mixed-Signal ISP FLASH MCU Family

ANALOG PERIPHERALS

-

SAR ADC

• 12-Bit (C8051F120/1/4/5)

• 10-Bit (C8051F122/3/6/7)

• ±1 LSB INL

• Programmable Throughput up to 100 ksps

• Up to 8 External Inputs; Programmable as Single-Ended or

Differential

• Programmable Amplifier Gain: 16, 8, 4, 2, 1, 0.5

• Data-Dependent Windowed Interrupt Generator

• Built-in Temperature Sensor

- 8-bit ADC

• Programmable Throughput up to 500 ksps

• 8 External Inputs (Single-Ended or Differential)

• Programmable Amplifier Gain: 4, 2, 1, 0.5

- Two 12-bit DACs

• Can Synchronize Outputs to Timers for Jitter-Free Wave-

- Two Analog Comparators

form Generation

- Voltage Reference

- VDD Monitor/Brown-Out Detector

ON-CHIP JTAG DEBUG & BOUNDARY SCAN

-

On-Chip Debug Circuitry Facilitates Full- Speed, NonIntrusive In-Circuit/In-System Debugging

- Provides Breakpoints, Single-Stepping, Watchpoints,

Stack Monitor; Inspect/Modify Memory and Registers

- Superior Performance to Emulation Systems Using ICE-

Chips, Target Pods, and Sockets

- IEEE1149.1 Compliant Boundary Scan

- Complete Development Kit

HIGH SPEED 8051 µC CORE

-

Pipelined Instruction Architecture; Executes 70% of

Instruction Set in 1 or 2 System Clocks

- Up to 100 MIPS (C8051F120/1/2/3) or 50 MIPS

(C8051F124/5/6/7) Throughput using Integrated PLL

- 2-cycle 16 x 16 MAC Engine (C8051F120/1/2/3)

- Flexible Interrupt Sources

MEMORY

-

8448 Bytes Internal Data RAM (8k + 256)

- 128k Bytes Banked FLASH; In-System programmable in

1024-byte Sectors

- External 64k Byte Data Memory Interface (programma-

ble multiplexed or non-multiplexed modes)

DIGITAL PERIPHERALS

-

8 Byte-Wide Port I/O (C8051F120/2/4/6); 5V tolerant

- 4 Byte-Wide Port I/O (C8051F121/3/5/7); 5V tolerant

- Hardware SMBus™ (I

Two UART Serial Ports Available Concurrently

2

C™ Compatible), SPI™, and

- Programmable 16-bit Counter/Timer Array with

6 Capture/Compare Modules

- 5 General Purpose 16-bit Counter/Timers

- Dedicated Watch-Dog Timer; Bi-directional Reset Pin

CLOCK SOURCES

- Internal Precision Oscillator: 24.5 MHz

- Flexible PLL technology

- External Oscillator: Crystal, RC, C, or Clock

POWER SUPPLIES

-

Supply Range: 2.7-3.6V (50 MIPS) 3.0-3.6V (100 MIPS)

- Power Saving Sleep and Shutdown Modes

100-PIN TQFP OR 64-PIN TQFP PACKAGING

-

Temperature Range: -40°C to +85°C

ANALOG PERIPHERALS

TEMP

AMUX

12-Bit

DAC

12-Bit

DAC

SENSOR

PGA

VREF

AMUX

10/12-bit

100ksps

ADC

PGA

500ksps

+

+

-

-

VOLTAGE

COMPARATORS

8-bit

ADC

DIGITAL I/O

UART0

UART1

SMBus

SPI Bus

PCA

Timer 0

Timer 1

Timer 2

Timer 3

Timer 4

CROSSBAR

64 pin

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

External Memory Interface

Port 6

Port 7

100 pin

HIGH-SPEED CONTROLLER CORE

8051 CPU

(50 or 100MIPS)

20

INTERRUPTS

128KB

ISP FLASH

DEBUG

CIRCUITRY

8448 B

SRAM

CLOCK / PLL

CIRCUIT

16 x 16 MAC

('F120/1/2/3)

JTAG

Preliminary Rev. 1.2 12/03 Copyright © 2003 by Silicon Laboratories C8051F120/1/2/3/4/5/6/7-DS12

This information applies to a product under development. Its characteristics and specifications are subject to change without notice.

Page 2

C8051F120/1/2/3/4/5/6/7

Notes

2 Rev. 1.2

Page 3

C8051F120/1/2/3/4/5/6/7

TABLE OF CONTENTS

1. SYSTEM OVERVIEW .........................................................................................................19

1.1. CIP-51™ Microcontroller Core ......................................................................................25

1.1.1. Fully 8051 Compatible ..........................................................................................25

1.1.2. Improved Throughput ............................................................................................25

1.1.3. Additional Features................................................................................................26

1.2. On-Chip Memory ............................................................................................................27

1.3. JTAG Debug and Boundary Scan ...................................................................................28

1.4. 16 x 16 MAC (Multiply and Accumulate) Engine..........................................................29

1.5. Programmable Digital I/O and Crossbar .........................................................................30

1.6. Programmable Counter Array .........................................................................................31

1.7. Serial Ports.......................................................................................................................32

1.8. 12-Bit Analog to Digital Converter.................................................................................33

1.9. 8-Bit Analog to Digital Converter...................................................................................34

1.10.Comparators and DACs...................................................................................................35

2. ABSOLUTE MAXIMUM RATINGS..................................................................................36

3. GLOBAL DC ELECTRICAL CHARACTERISTICS ......................................................37

4. PINOUT AND PACKAGE DEFINITIONS........................................................................39

5. ADC0 (12-BIT ADC, C8051F120/1/4/5 ONLY) ..................................................................49

5.1. Analog Multiplexer and PGA..........................................................................................49

5.2. ADC Modes of Operation ...............................................................................................51

5.2.1. Starting a Conversion.............................................................................................51

5.2.2. Tracking Modes .....................................................................................................52

5.2.3. Settling Time Requirements ..................................................................................53

5.3. ADC0 Programmable Window Detector.........................................................................60

6. ADC0 (10-BIT ADC, C8051F122/3/6/7 ONLY) ..................................................................67

6.1. Analog Multiplexer and PGA..........................................................................................67

6.2. ADC Modes of Operation ...............................................................................................69

6.2.1. Starting a Conversion.............................................................................................69

6.2.2. Tracking Modes .....................................................................................................70

6.2.3. Settling Time Requirements ..................................................................................71

6.3. ADC0 Programmable Window Detector.........................................................................78

7. ADC2 (8-BIT ADC) ...............................................................................................................85

7.1. Analog Multiplexer and PGA..........................................................................................85

7.2. ADC2 Modes of Operation .............................................................................................86

7.2.1. Starting a Conversion.............................................................................................86

7.2.2. Tracking Modes .....................................................................................................86

7.2.3. Settling Time Requirements ..................................................................................88

7.3. ADC2 Programmable Window Detector.........................................................................94

7.3.1. Window Detector In Single-Ended Mode .............................................................94

7.3.2. Window Detector In Differential Mode.................................................................95

8. DACS, 12-BIT VOLTAGE MODE......................................................................................99

8.1. DAC Output Scheduling..................................................................................................99

Rev. 1.2 3

Page 4

C8051F120/1/2/3/4/5/6/7

8.1.1. Update Output On-Demand ...................................................................................99

8.1.2. Update Output Based on Timer Overflow...........................................................100

8.2. DAC Output Scaling/Justification.................................................................................100

9. VOLTAGE REFERENCE (C8051F120/2/4/6) .................................................................107

10. VOLTAGE REFERENCE (C8051F121/3/5/7) .................................................................109

11. COMPARATORS................................................................................................................111

12. CIP-51 MICROCONTROLLER........................................................................................119

12.1.Instruction Set................................................................................................................120

12.1.1. Instruction and CPU Timing................................................................................120

12.1.2. MOVX Instruction and Program Memory...........................................................120

12.2.Memory Organization ...................................................................................................125

12.2.1. Program Memory.................................................................................................125

12.2.2. Data Memory .......................................................................................................127

12.2.3. General Purpose Registers ...................................................................................127

12.2.4. Bit Addressable Locations ...................................................................................127

12.2.5. Stack .................................................................................................................127

12.2.6. Special Function Registers...................................................................................128

12.2.6.1.SFR Paging ..................................................................................................128

12.2.6.2.Interrupts and SFR Paging...........................................................................128

12.2.6.3.SFR Page Stack Example ............................................................................130

12.2.7. Register Descriptions...........................................................................................143

12.3.Interrupt Handler ...........................................................................................................146

12.3.1. MCU Interrupt Sources and Vectors ...................................................................146

12.3.2. External Interrupts ...............................................................................................146

12.3.3. Interrupt Priorities................................................................................................148

12.3.4. Interrupt Latency..................................................................................................148

12.3.5. Interrupt Register Descriptions............................................................................149

12.4.Power Management Modes ...........................................................................................155

12.4.1. Idle Mode.............................................................................................................155

12.4.2. Stop Mode............................................................................................................155

13. MULTIPLY AND ACCUMULATE (MAC0) ...................................................................157

13.1.Special Function Registers ............................................................................................157

13.2.Integer and Fractional Math ..........................................................................................158

13.3.Operating in Multiply and Accumulate Mode...............................................................159

13.4.Operating in Multiply Only Mode.................................................................................159

13.5.Accumulator Shift Operations .......................................................................................159

13.6.Rounding and Saturation ...............................................................................................160

13.7.Usage Examples ............................................................................................................160

14. RESET SOURCES ..............................................................................................................167

14.1.Power-on Reset..............................................................................................................168

14.2.Power-fail Reset ............................................................................................................168

14.3.External Reset................................................................................................................168

14.4.Missing Clock Detector Reset .......................................................................................169

14.5.Comparator0 Reset ........................................................................................................169

14.6.External CNVSTR0 Pin Reset.......................................................................................169

4 Rev. 1.2

Page 5

C8051F120/1/2/3/4/5/6/7

14.7.Watchdog Timer Reset ..................................................................................................169

14.7.1. Enable/Reset WDT ..............................................................................................169

14.7.2. Disable WDT .......................................................................................................170

14.7.3. Disable WDT Lockout.........................................................................................170

14.7.4. Setting WDT Interval...........................................................................................170

15. OSCILLATORS...................................................................................................................173

15.1.Programmable Internal Oscillator .................................................................................173

15.2.External Oscillator Drive Circuit...................................................................................175

15.3.System Clock Selection .................................................................................................175

15.4.External Crystal Example..............................................................................................177

15.5.External RC Example ....................................................................................................177

15.6.External Capacitor Example..........................................................................................177

15.7.Phase-Locked Loop (PLL) ............................................................................................178

15.7.1. PLL Input Clock and Pre-divider.........................................................................178

15.7.2. PLL Multiplication and Output Clock .................................................................178

15.7.3. Powering on and Initializing the PLL..................................................................179

16. FLASH MEMORY ..............................................................................................................185

16.1.Programming The Flash Memory .................................................................................185

16.1.1. Non-volatile Data Storage ...................................................................................185

16.1.2. Erasing FLASH Pages From Software ................................................................186

16.1.3. Writing FLASH Memory From Software ...........................................................187

16.2.Security Options ............................................................................................................188

17. BRANCH TARGET CACHE.............................................................................................193

17.1.Cache and Prefetch Operation .......................................................................................193

17.2.Cache and Prefetch Optimization ..................................................................................194

18. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM.......................199

18.1.Accessing XRAM..........................................................................................................199

18.1.1. 16-Bit MOVX Example.......................................................................................199

18.1.2. 8-Bit MOVX Example.........................................................................................199

18.2.Configuring the External Memory Interface .................................................................199

18.3.Port Selection and Configuration ..................................................................................200

18.4.Multiplexed and Non-multiplexed Selection.................................................................202

18.4.1. Multiplexed Configuration ..................................................................................202

18.4.2. Non-multiplexed Configuration...........................................................................203

18.5.Memory Mode Selection ...............................................................................................204

18.5.1. Internal XRAM Only ...........................................................................................204

18.5.2. Split Mode without Bank Select ..........................................................................204

18.5.3. Split Mode with Bank Select ...............................................................................205

18.5.4. External Only.......................................................................................................205

18.6.Timing .......................................................................................................................206

18.6.1. Non-multiplexed Mode........................................................................................207

18.6.1.1.16-bit MOVX: EMI0CF[4:2] = ‘101’, ‘110’, or ‘111’................................207

18.6.1.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = ‘101’ or ‘111’. ...........208

18.6.1.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = ‘110’. ..............................209

18.6.2. Multiplexed Mode................................................................................................210

Rev. 1.2 5

Page 6

C8051F120/1/2/3/4/5/6/7

18.6.2.1.16-bit MOVX: EMI0CF[4:2] = ‘001’, ‘010’, or ‘011’................................210

18.6.2.2.8-bit MOVX without Bank Select: EMI0CF[4:2] = ‘001’ or ‘011’. ...........211

18.6.2.3.8-bit MOVX with Bank Select: EMI0CF[4:2] = ‘010’. ..............................212

19. PORT INPUT/OUTPUT .....................................................................................................215

19.1.Ports 0 through 3 and the Priority Crossbar Decoder ....................................................217

19.1.1. Crossbar Pin Assignment and Allocation ............................................................217

19.1.2. Configuring the Output Modes of the Port Pins ..................................................218

19.1.3. Configuring Port Pins as Digital Inputs...............................................................219

19.1.4. Weak Pull-ups......................................................................................................219

19.1.5. Configuring Port 1 Pins as Analog Inputs ...........................................................219

19.1.6. External Memory Interface Pin Assignments......................................................220

19.1.7. Crossbar Pin Assignment Example......................................................................222

19.2.Ports 4 through 7 (C8051F120/2/4/6 only) ...................................................................231

19.2.1. Configuring Ports which are not Pinned Out.......................................................231

19.2.2. Configuring the Output Modes of the Port Pins ..................................................231

19.2.3. Configuring Port Pins as Digital Inputs...............................................................232

19.2.4. Weak Pull-ups......................................................................................................232

19.2.5. External Memory Interface..................................................................................232

20. SYSTEM MANAGEMENT BUS / I2C BUS (SMBUS0) .................................................237

20.1.Supporting Documents ..................................................................................................238

20.2.SMBus Protocol.............................................................................................................238

20.2.1. Arbitration............................................................................................................239

20.2.2. Clock Low Extension...........................................................................................239

20.2.3. SCL Low Timeout ...............................................................................................239

20.2.4. SCL High (SMBus Free) Timeout.......................................................................239

20.3.SMBus Transfer Modes.................................................................................................240

20.3.1. Master Transmitter Mode ....................................................................................240

20.3.2. Master Receiver Mode.........................................................................................240

20.3.3. Slave Transmitter Mode.......................................................................................241

20.3.4. Slave Receiver Mode ...........................................................................................241

20.4.SMBus Special Function Registers ...............................................................................242

20.4.1. Control Register...................................................................................................242

20.4.2. Clock Rate Register .............................................................................................244

20.4.3. Data Register........................................................................................................245

20.4.4. Address Register ..................................................................................................245

20.4.5. Status Register .....................................................................................................246

21. ENHANCED SERIAL PERIPHERAL INTERFACE (SPI0) .........................................249

21.1.Signal Descriptions........................................................................................................250

21.1.1. Master Out, Slave In (MOSI) ..............................................................................250

21.1.2. Master In, Slave Out (MISO) ..............................................................................250

21.1.3. Serial Clock (SCK) ..............................................................................................250

21.1.4. Slave Select (NSS)...............................................................................................250

21.2.SPI0 Master Mode Operation ........................................................................................251

21.3.SPI0 Slave Mode Operation ..........................................................................................253

21.4.SPI0 Interrupt Sources...................................................................................................253

6 Rev. 1.2

Page 7

C8051F120/1/2/3/4/5/6/7

21.5.Serial Clock Timing ......................................................................................................254

21.6.SPI Special Function Registers .....................................................................................256

22. UART0 ..................................................................................................................................263

22.1.UART0 Operational Modes ..........................................................................................264

22.1.1. Mode 0: Synchronous Mode................................................................................264

22.1.2. Mode 1: 8-Bit UART, Variable Baud Rate .........................................................265

22.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate ..............................................................266

22.1.4. Mode 3: 9-Bit UART, Variable Baud Rate .........................................................267

22.2.Multiprocessor Communications...................................................................................268

22.2.1. Configuration of a Masked Address ....................................................................268

22.2.2. Broadcast Addressing ..........................................................................................268

22.3.Frame and Transmission Error Detection......................................................................269

23. UART1 ..................................................................................................................................275

23.1.Enhanced Baud Rate Generation...................................................................................276

23.2.Operational Modes ........................................................................................................277

23.2.1. 8-Bit UART .........................................................................................................277

23.2.2. 9-Bit UART .........................................................................................................278

23.3.Multiprocessor Communications...................................................................................279

24. TIMERS................................................................................................................................285

24.1.Timer 0 and Timer 1......................................................................................................285

24.1.1. Mode 0: 13-bit Counter/Timer.............................................................................285

24.1.2. Mode 1: 16-bit Counter/Timer.............................................................................286

24.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload.................................................287

24.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) ...........................................288

24.2.Timer 2, Timer 3, and Timer 4 ......................................................................................293

24.2.1. Configuring Timer 2, 3, and 4 to Count Down....................................................293

24.2.2. Capture Mode ......................................................................................................294

24.2.3. Auto-Reload Mode ..............................................................................................295

24.2.4. Toggle Output Mode (Timer 2 and Timer 4 Only)..............................................295

25. PROGRAMMABLE COUNTER ARRAY .......................................................................301

25.1.PCA Counter/Timer.......................................................................................................302

25.2.Capture/Compare Modules............................................................................................303

25.2.1. Edge-triggered Capture Mode .............................................................................304

25.2.2. Software Timer (Compare) Mode........................................................................305

25.2.3. High Speed Output Mode ....................................................................................306

25.2.4. Frequency Output Mode ......................................................................................307

25.2.5. 8-Bit Pulse Width Modulator Mode ....................................................................308

25.2.6. 16-Bit Pulse Width Modulator Mode ..................................................................309

25.3.Register Descriptions for PCA0 ....................................................................................310

26. JTAG (IEEE 1149.1)............................................................................................................315

26.1.Boundary Scan...............................................................................................................316

26.1.1. EXTEST Instruction ............................................................................................317

26.1.2. SAMPLE Instruction ...........................................................................................317

26.1.3. BYPASS Instruction ............................................................................................317

26.1.4. IDCODE Instruction ............................................................................................317

Rev. 1.2 7

Page 8

C8051F120/1/2/3/4/5/6/7

26.2.Flash Programming Commands ....................................................................................318

26.3.Debug Support...............................................................................................................321

8 Rev. 1.2

Page 9

C8051F120/1/2/3/4/5/6/7

LIST OF FIGURES

1. SYSTEM OVERVIEW .........................................................................................................19

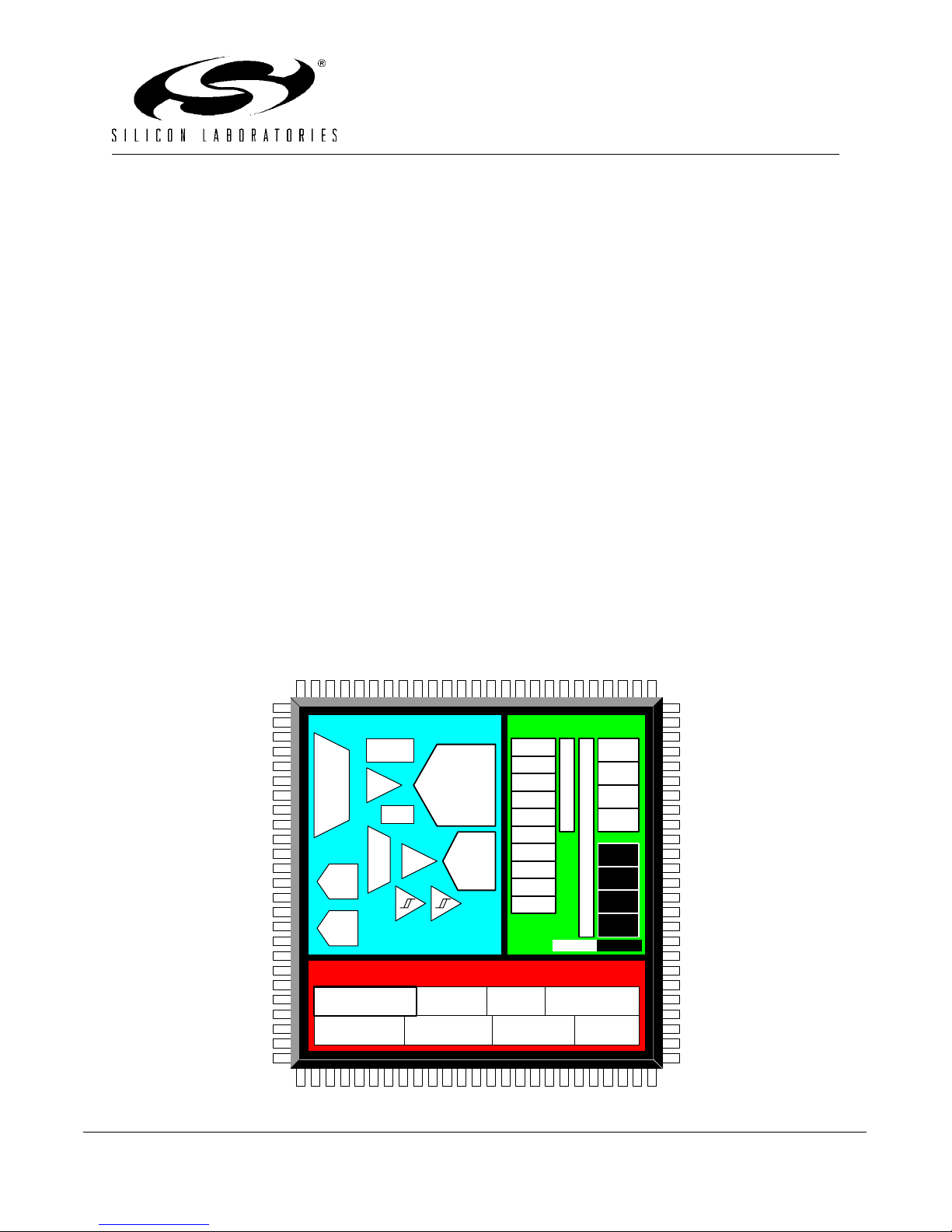

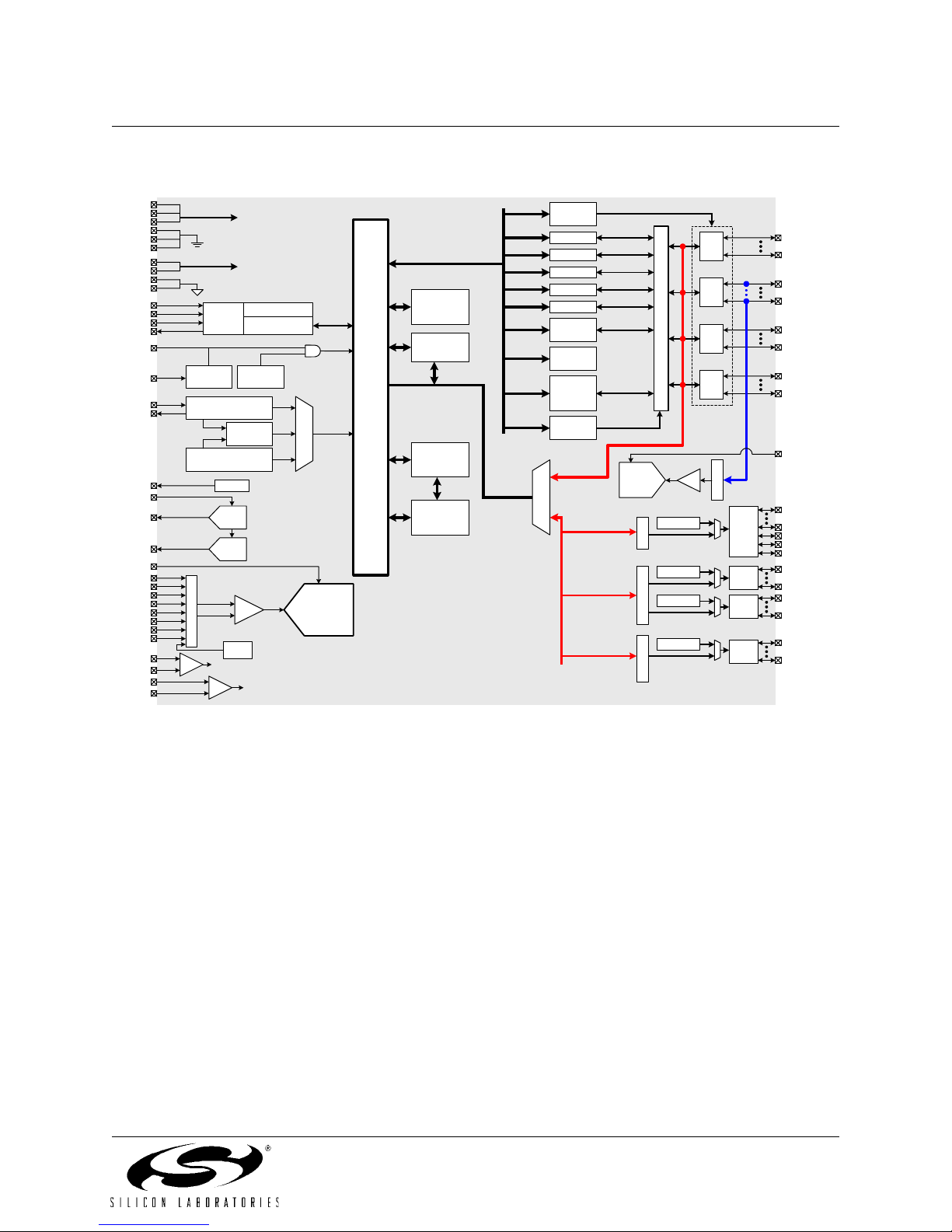

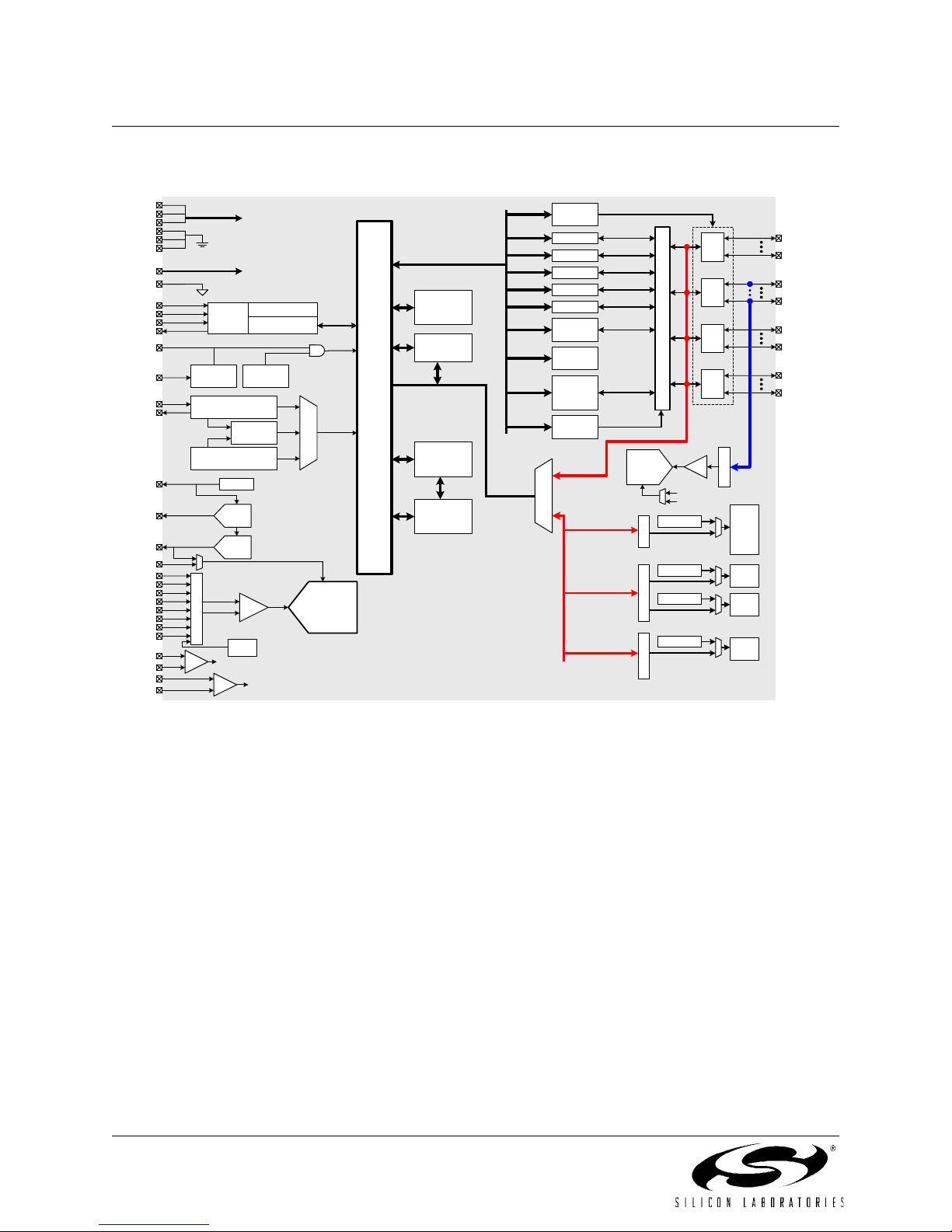

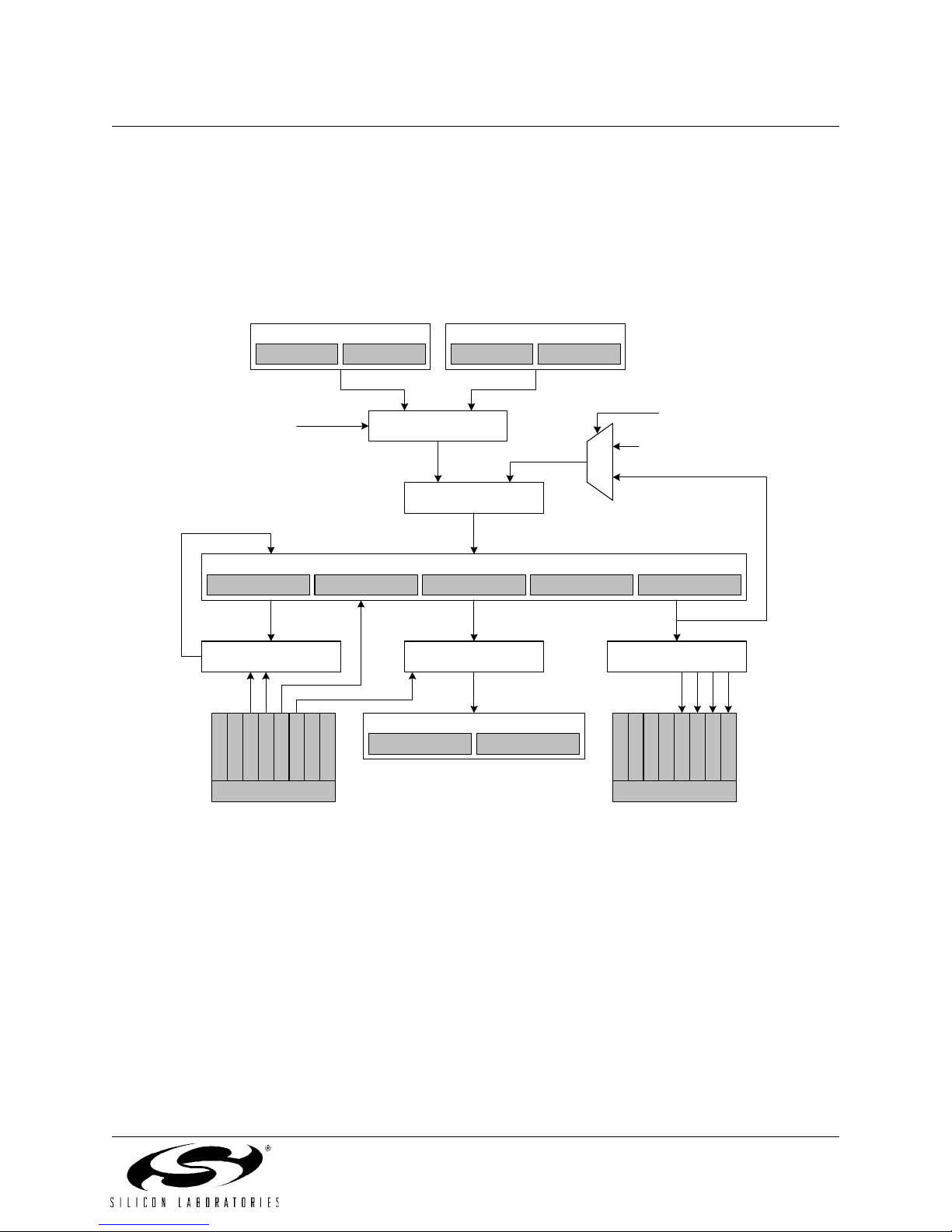

Figure 1.1. C8051F120/124 Block Diagram..........................................................................21

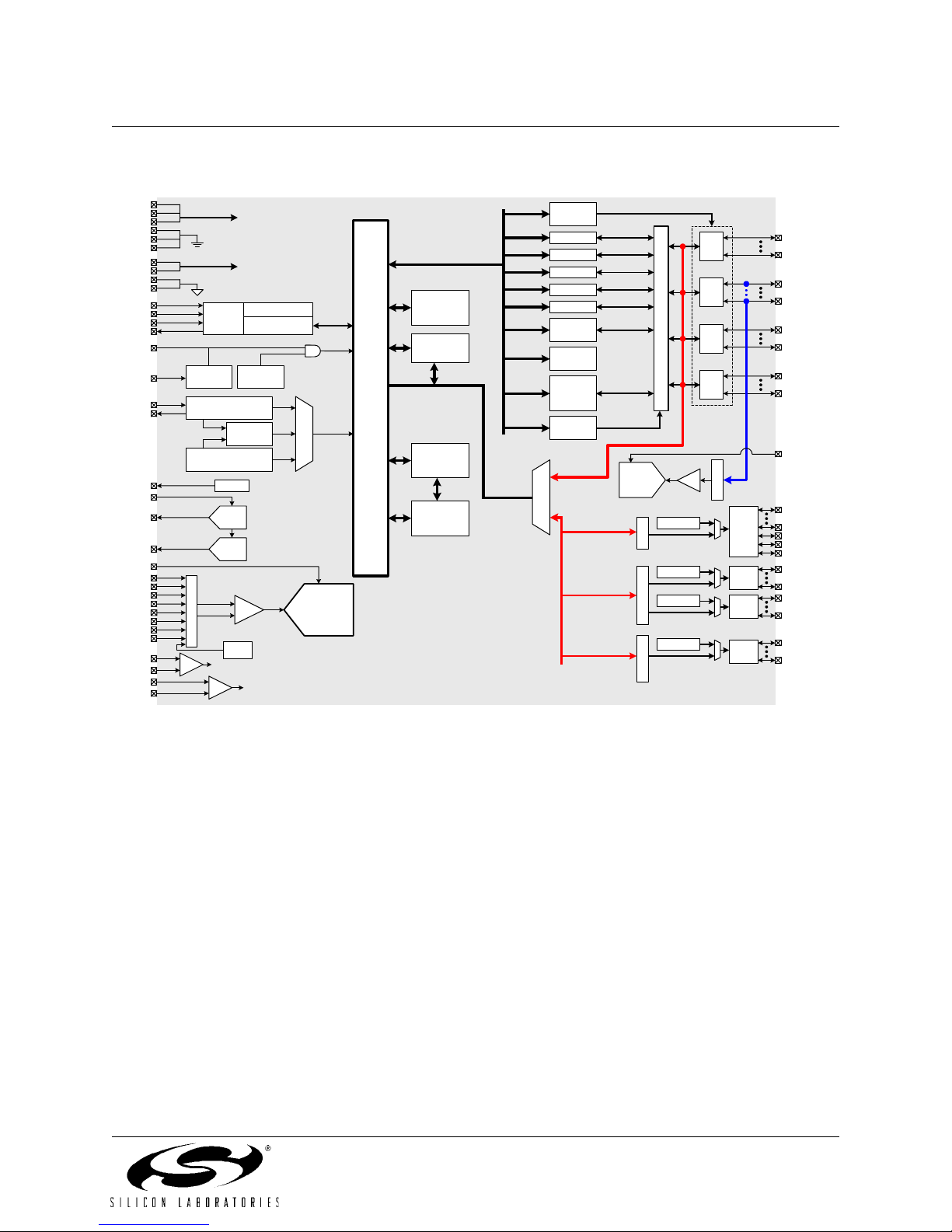

Figure 1.2. C8051F121/125 Block Diagram..........................................................................22

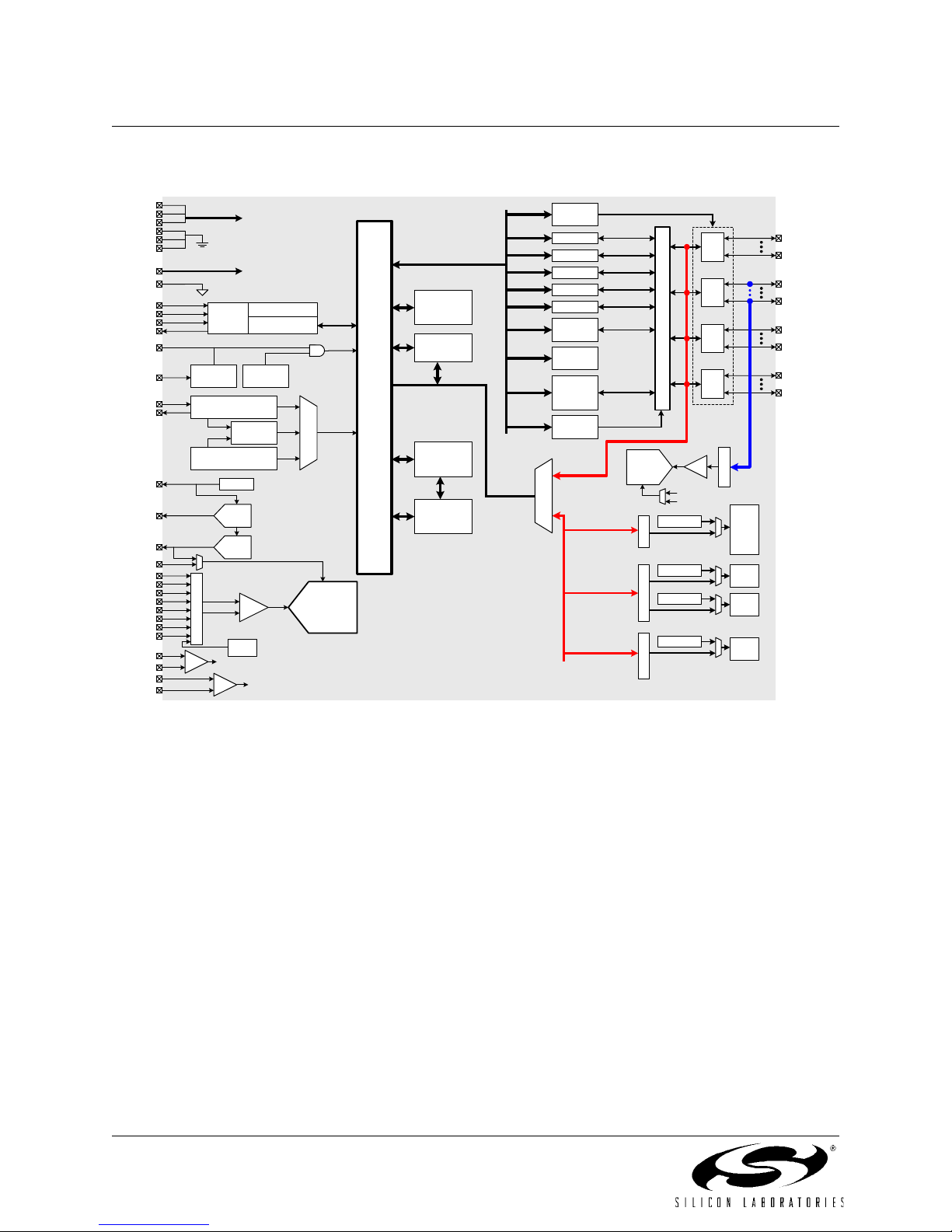

Figure 1.3. C8051F122/126 Block Diagram..........................................................................23

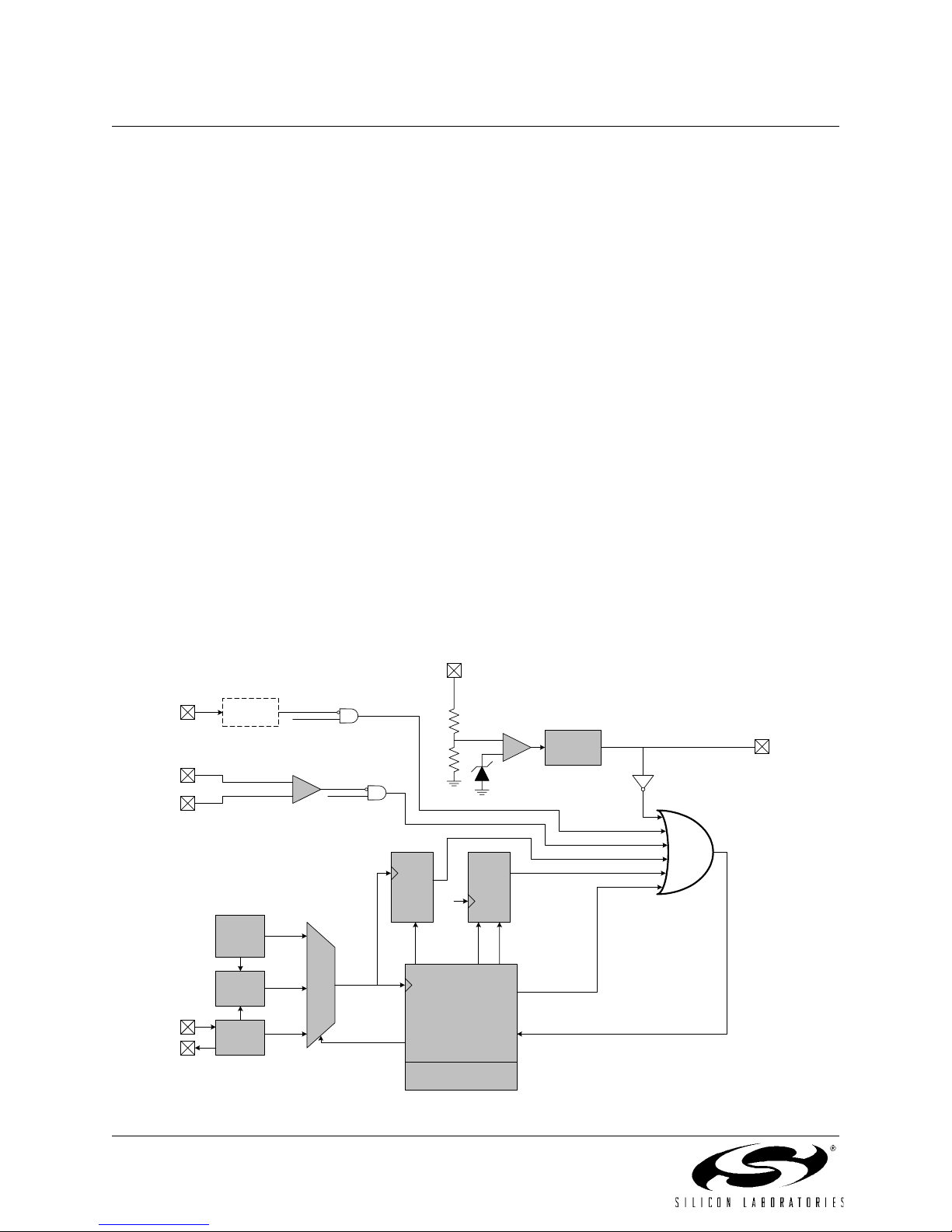

Figure 1.4. C8051F123/127 Block Diagram..........................................................................24

Figure 1.5. On-Board Clock and Reset..................................................................................26

Figure 1.6. On-Chip Memory Map........................................................................................27

Figure 1.7. Development/In-System Debug Diagram ...........................................................28

Figure 1.8. MAC0 Block Diagram ........................................................................................29

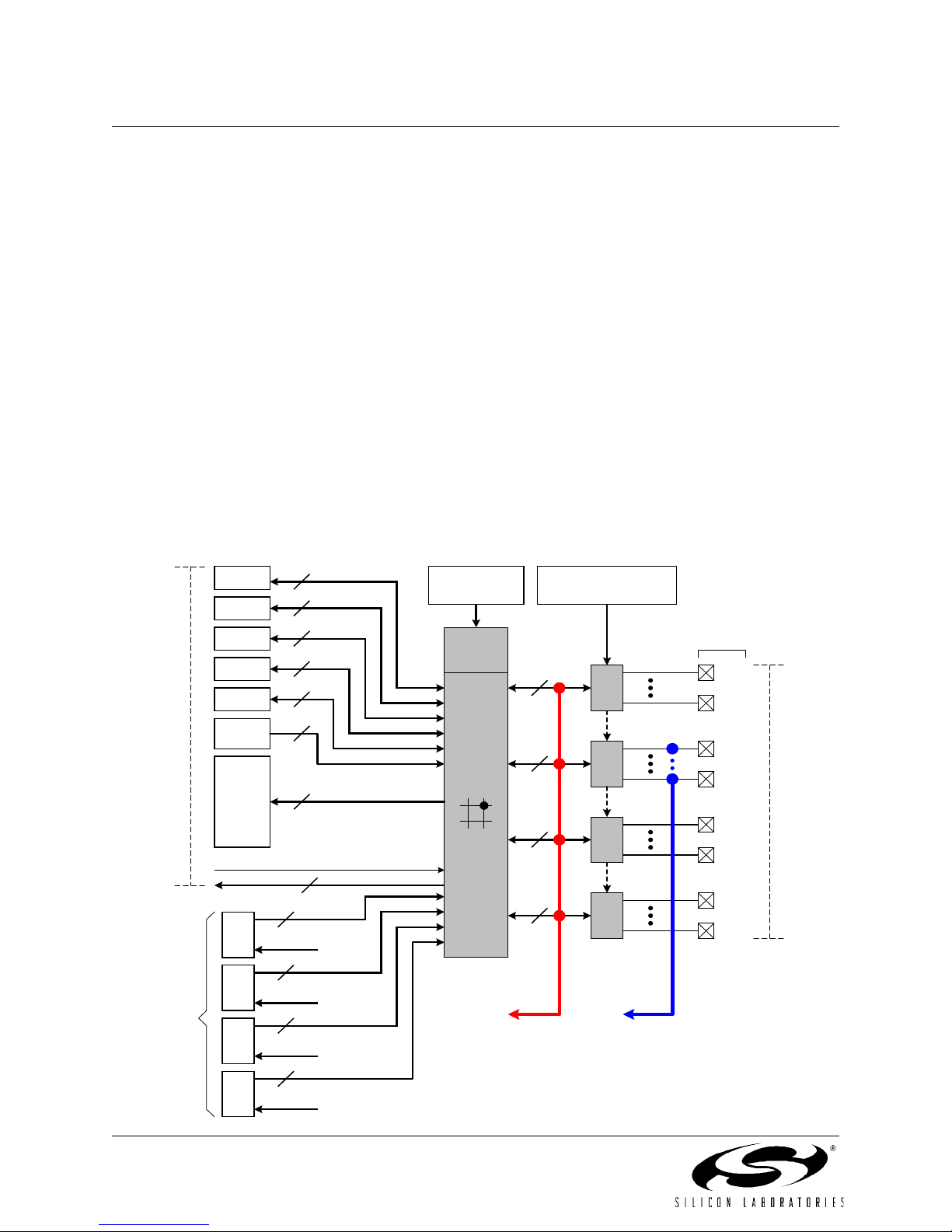

Figure 1.9. Digital Crossbar Diagram....................................................................................30

Figure 1.10. PCA Block Diagram............................................................................................31

Figure 1.11. 12-Bit ADC Block Diagram................................................................................33

Figure 1.12. 8-Bit ADC Diagram ............................................................................................34

Figure 1.13. Comparator and DAC Diagram...........................................................................35

2. ABSOLUTE MAXIMUM RATINGS..................................................................................36

3. GLOBAL DC ELECTRICAL CHARACTERISTICS ......................................................37

4. PINOUT AND PACKAGE DEFINITIONS........................................................................39

Figure 4.1. TQFP-100 Pinout Diagram..................................................................................44

Figure 4.2. TQFP-100 Package Drawing...............................................................................45

Figure 4.3. TQFP-64 Pinout Diagram....................................................................................46

Figure 4.4. TQFP-64 Package Drawing.................................................................................47

5. ADC0 (12-BIT ADC, C8051F120/1/4/5 ONLY) ..................................................................49

Figure 5.1. 12-Bit ADC0 Functional Block Diagram............................................................49

Figure 5.2. Typical Temperature Sensor Transfer Function..................................................50

Figure 5.3. ADC0 Track and Conversion Example Timing ..................................................52

Figure 5.4. ADC0 Equivalent Input Circuits .........................................................................53

Figure 5.5. AMX0CF: AMUX0 Configuration Register.......................................................54

Figure 5.6. AMX0SL: AMUX0 Channel Select Register .....................................................55

Figure 5.7. ADC0CF: ADC0 Configuration Register ...........................................................56

Figure 5.8. ADC0CN: ADC0 Control Register.....................................................................57

Figure 5.9. ADC0H: ADC0 Data Word MSB Register.........................................................58

Figure 5.10. ADC0L: ADC0 Data Word LSB Register ..........................................................58

Figure 5.11. ADC0 Data Word Example.................................................................................59

Figure 5.12. ADC0GTH: ADC0 Greater-Than Data High Byte Register...............................60

Figure 5.13. ADC0GTL: ADC0 Greater-Than Data Low Byte Register................................60

Figure 5.14. ADC0LTH: ADC0 Less-Than Data High Byte Register....................................61

Figure 5.15. ADC0LTL: ADC0 Less-Than Data Low Byte Register .....................................61

Figure 5.16. 12-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data .62

Figure 5.17. 12-Bit ADC0 Window Interrupt Example: Right Justified Differential Data.....63

Figure 5.18. 12-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data....64

Figure 5.19. 12-Bit ADC0 Window Interrupt Example: Left Justified Differential Data.......65

6. ADC0 (10-BIT ADC, C8051F122/3/6/7 ONLY) ..................................................................67

Rev. 1.2 9

Page 10

C8051F120/1/2/3/4/5/6/7

Figure 6.1. 10-Bit ADC0 Functional Block Diagram............................................................67

Figure 6.2. Typical Temperature Sensor Transfer Function..................................................68

Figure 6.3. ADC0 Track and Conversion Example Timing ..................................................70

Figure 6.4. ADC0 Equivalent Input Circuits .........................................................................71

Figure 6.5. AMX0CF: AMUX0 Configuration Register.......................................................72

Figure 6.6. AMX0SL: AMUX0 Channel Select Register .....................................................73

Figure 6.7. ADC0CF: ADC0 Configuration Register ...........................................................74

Figure 6.8. ADC0CN: ADC0 Control Register.....................................................................75

Figure 6.9. ADC0H: ADC0 Data Word MSB Register.........................................................76

Figure 6.10. ADC0L: ADC0 Data Word LSB Register ..........................................................76

Figure 6.11. ADC0 Data Word Example.................................................................................77

Figure 6.12. ADC0GTH: ADC0 Greater-Than Data High Byte Register...............................78

Figure 6.13. ADC0GTL: ADC0 Greater-Than Data Low Byte Register................................78

Figure 6.14. ADC0LTH: ADC0 Less-Than Data High Byte Register....................................79

Figure 6.15. ADC0LTL: ADC0 Less-Than Data Low Byte Register .....................................79

Figure 6.16. 10-Bit ADC0 Window Interrupt Example: Right Justified Single-Ended Data .80

Figure 6.17. 10-Bit ADC0 Window Interrupt Example: Right Justified Differential Data.....81

Figure 6.18. 10-Bit ADC0 Window Interrupt Example: Left Justified Single-Ended Data....82

Figure 6.19. 10-Bit ADC0 Window Interrupt Example: Left Justified Differential Data.......83

7. ADC2 (8-BIT ADC) ...............................................................................................................85

Figure 7.1. ADC2 Functional Block Diagram.......................................................................85

Figure 7.2. ADC2 Track and Conversion Example Timing ..................................................87

Figure 7.3. ADC2 Equivalent Input Circuit...........................................................................88

Figure 7.4. AMX2CF: AMUX2 Configuration Register.......................................................89

Figure 7.5. AMX2SL: AMUX2 Channel Select Register .....................................................90

Figure 7.6. ADC2CF: ADC2 Configuration Register ...........................................................91

Figure 7.7. ADC2CN: ADC2 Control Register.....................................................................92

Figure 7.8. ADC2: ADC2 Data Word Register .....................................................................93

Figure 7.9. ADC2 Data Word Example.................................................................................93

Figure 7.10. ADC2 Window Compare Examples, Single-Ended Mode .................................94

Figure 7.11. ADC2 Window Compare Examples, Differential Mode ....................................95

Figure 7.12. ADC2GT: ADC2 Greater-Than Data Byte Register...........................................96

Figure 7.13. ADC2LT: ADC2 Less-Than Data Byte Register................................................96

8. DACS, 12-BIT VOLTAGE MODE......................................................................................99

Figure 8.1. DAC Functional Block Diagram.........................................................................99

Figure 8.2. DAC0H: DAC0 High Byte Register .................................................................101

Figure 8.3. DAC0L: DAC0 Low Byte Register ..................................................................101

Figure 8.4. DAC0CN: DAC0 Control Register...................................................................102

Figure 8.5. DAC1H: DAC1 High Byte Register .................................................................103

Figure 8.6. DAC1L: DAC1 Low Byte Register ..................................................................103

Figure 8.7. DAC1CN: DAC1 Control Register...................................................................104

9. VOLTAGE REFERENCE (C8051F120/2/4/6) .................................................................107

Figure 9.1. Voltage Reference Functional Block Diagram..................................................107

Figure 9.2. REF0CN: Reference Control Register ..............................................................108

10. VOLTAGE REFERENCE (C8051F121/3/5/7) .................................................................109

10 Rev. 1.2

Page 11

C8051F120/1/2/3/4/5/6/7

Figure 10.1. Voltage Reference Functional Block Diagram .................................................109

Figure 10.2. REF0CN: Reference Control Register ..............................................................110

11. COMPARATORS................................................................................................................111

Figure 11.1. Comparator Functional Block Diagram ............................................................111

Figure 11.2. Comparator Hysteresis Plot...............................................................................113

Figure 11.3. CPT0CN: Comparator0 Control Register .........................................................114

Figure 11.4. CPT0MD: Comparator0 Mode Selection Register ...........................................115

Figure 11.5. CPT1CN: Comparator1 Control Register .........................................................116

Figure 11.6. CPT1MD: Comparator1 Mode Selection Register ...........................................117

12. CIP-51 MICROCONTROLLER........................................................................................119

Figure 12.1. CIP-51 Block Diagram.....................................................................................119

Figure 12.2. Memory Map.....................................................................................................125

Figure 12.3. PSBANK: Program Space Bank Select Register ..............................................126

Figure 12.4. Address Memory Map for Instruction Fetches..................................................126

Figure 12.5. SFR Page Stack .................................................................................................129

Figure 12.6. SFR Page Stack While Using SFR Page 0x0F To Access Port 5 .....................130

Figure 12.7. SFR Page Stack After ADC2 Window Comparator Interrupt Occurs ..............131

Figure 12.8. SFR Page Stack Upon PCA Interrupt Occurring During an ADC2 ISR...........132

Figure 12.9. SFR Page Stack Upon Return From PCA Interrupt ..........................................133

Figure 12.10. SFR Page Stack Upon Return From ADC2 Window Interrupt.......................134

Figure 12.11. SFRPGCN: SFR Page Control Register..........................................................135

Figure 12.12. SFRPAGE: SFR Page Register .......................................................................135

Figure 12.13. SFRNEXT: SFR Next Register.......................................................................136

Figure 12.14. SFRLAST: SFR Last Register ........................................................................136

Figure 12.15. SP: Stack Pointer .............................................................................................143

Figure 12.16. DPL: Data Pointer Low Byte ..........................................................................143

Figure 12.17. DPH: Data Pointer High Byte .........................................................................143

Figure 12.18. PSW: Program Status Word ............................................................................144

Figure 12.19. ACC: Accumulator..........................................................................................145

Figure 12.20. B: B Register ...................................................................................................145

Figure 12.21. IE: Interrupt Enable .........................................................................................149

Figure 12.22. IP: Interrupt Priority ........................................................................................150

Figure 12.23. EIE1: Extended Interrupt Enable 1 .................................................................151

Figure 12.24. EIE2: Extended Interrupt Enable 2 .................................................................152

Figure 12.25. EIP1: Extended Interrupt Priority 1.................................................................153

Figure 12.26. EIP2: Extended Interrupt Priority 2.................................................................154

Figure 12.27. PCON: Power Control.....................................................................................156

13. MULTIPLY AND ACCUMULATE (MAC0) ...................................................................157

Figure 13.1. MAC0 Block Diagram ......................................................................................157

Figure 13.2. Integer Mode Data Representation....................................................................158

Figure 13.3. Fractional Mode Data Representation...............................................................158

Figure 13.4. MAC0 Pipeline..................................................................................................159

Figure 13.5. Multiply and Accumulate Example...................................................................160

Figure 13.6. Multiply Only Example.....................................................................................161

Figure 13.7. MAC0 Accumulator Shift Example ..................................................................161

Rev. 1.2 11

Page 12

C8051F120/1/2/3/4/5/6/7

Figure 13.8. MAC0CF: MAC0 Configuration Register ........................................................162

Figure 13.9. MAC0STA: MAC0 Status Register ..................................................................163

Figure 13.10. MAC0AH: MAC0 A High Byte Register .......................................................163

Figure 13.11. MAC0AL: MAC0 A Low Byte Register ........................................................164

Figure 13.12. MAC0BH: MAC0 B High Byte Register........................................................164

Figure 13.13. MAC0BL: MAC0 B Low Byte Register.........................................................164

Figure 13.14. MAC0ACC3: MAC0 Accumulator Byte 3 Register.......................................164

Figure 13.15. MAC0ACC2: MAC0 Accumulator Byte 2 Register.......................................165

Figure 13.16. MAC0ACC1: MAC0 Accumulator Byte 1 Register.......................................165

Figure 13.17. MAC0ACC0: MAC0 Accumulator Byte 0 Register.......................................165

Figure 13.18. MAC0OVR: MAC0 Accumulator Overflow Register....................................165

Figure 13.19. MAC0RNDH: MAC0 Rounding Register High Byte.....................................166

Figure 13.20. MAC0RNDL: MAC0 Rounding Register Low Byte......................................166

14. RESET SOURCES ..............................................................................................................167

Figure 14.1. Reset Sources ....................................................................................................167

Figure 14.2. Reset Timing .....................................................................................................168

Figure 14.3. WDTCN: Watchdog Timer Control Register ...................................................170

Figure 14.4. RSTSRC: Reset Source Register.......................................................................171

15. OSCILLATORS...................................................................................................................173

Figure 15.1. Oscillator Diagram ............................................................................................173

Figure 15.2. OSCICL: Internal Oscillator Calibration Register ............................................174

Figure 15.3. OSCICN: Internal Oscillator Control Register .................................................174

Figure 15.4. CLKSEL: System Clock Selection Register .....................................................175

Figure 15.5. OSCXCN: External Oscillator Control Register...............................................176

Figure 15.6. PLL Block Diagram ..........................................................................................178

Figure 15.7. PLL0CN: PLL Control Register........................................................................180

Figure 15.8. PLL0DIV: PLL Pre-divider Register ................................................................180

Figure 15.9. PLL0MUL: PLL Clock Scaler Register............................................................181

Figure 15.10. PLL0FLT: PLL Filter Register........................................................................181

16. FLASH MEMORY ..............................................................................................................185

Figure 16.1. FLASH Memory Map for MOVC Read and MOVX Write Operations...........186

Figure 16.2. FLASH Program Memory Map and Security Bytes .........................................189

Figure 16.3. FLACL: FLASH Access Limit .........................................................................190

Figure 16.4. FLSCL: FLASH Memory Control ....................................................................191

Figure 16.5. PSCTL: Program Store Read/Write Control .....................................................192

17. BRANCH TARGET CACHE.............................................................................................193

Figure 17.1. Branch Target Cache Data Flow .......................................................................193

Figure 17.2. Branch Target Cache Organiztion.....................................................................194

Figure 17.3. Cache Lock Operation.......................................................................................195

Figure 17.4. CCH0CN: Cache Control Register....................................................................196

Figure 17.5. CCH0TN: Cache Tuning Register ....................................................................197

Figure 17.6. CCH0LC: Cache Lock Control Register...........................................................197

Figure 17.7. CCH0MA: Cache Miss Accumulator................................................................198

Figure 17.8. FLSTAT: FLASH Status...................................................................................198

18. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM.......................199

12 Rev. 1.2

Page 13

C8051F120/1/2/3/4/5/6/7

Figure 18.1. EMI0CN: External Memory Interface Control .................................................201

Figure 18.2. EMI0CF: External Memory Configuration.......................................................201

Figure 18.3. Multiplexed Configuration Example.................................................................202

Figure 18.4. Non-multiplexed Configuration Example .........................................................203

Figure 18.5. EMIF Operating Modes.....................................................................................204

Figure 18.6. EMI0TC: External Memory Timing Control ....................................................206

Figure 18.7. Non-multiplexed 16-bit MOVX Timing ...........................................................207

Figure 18.8. Non-multiplexed 8-bit MOVX without Bank Select Timing............................208

Figure 18.9. Non-multiplexed 8-bit MOVX with Bank Select Timing.................................209

Figure 18.10. Multiplexed 16-bit MOVX Timing.................................................................210

Figure 18.11. Multiplexed 8-bit MOVX without Bank Select Timing .................................211

Figure 18.12. Multiplexed 8-bit MOVX with Bank Select Timing.......................................212

19. PORT INPUT/OUTPUT .....................................................................................................215

Figure 19.1. Port I/O Cell Block Diagram.............................................................................215

Figure 19.2. Port I/O Functional Block Diagram ..................................................................216

Figure 19.3. Priority Crossbar Decode Table ........................................................................217

Figure 19.4. Priority Crossbar Decode Table ........................................................................220

Figure 19.5. Priority Crossbar Decode Table ........................................................................221

Figure 19.6. Crossbar Example: ............................................................................................223

Figure 19.7. XBR0: Port I/O Crossbar Register 0 .................................................................224

Figure 19.8. XBR1: Port I/O Crossbar Register 1 .................................................................225

Figure 19.9. XBR2: Port I/O Crossbar Register 2 .................................................................226

Figure 19.10. P0: Port0 Data Register ...................................................................................227

Figure 19.11. P0MDOUT: Port0 Output Mode Register.......................................................227

Figure 19.12. P1: Port1 Data Register ...................................................................................228

Figure 19.13. P1MDIN: Port1 Input Mode Register .............................................................228

Figure 19.14. P1MDOUT: Port1 Output Mode Register.......................................................229

Figure 19.15. P2: Port2 Data Register ...................................................................................229

Figure 19.16. P2MDOUT: Port2 Output Mode Register.......................................................230

Figure 19.17. P3: Port3 Data Register ...................................................................................230

Figure 19.18. P3MDOUT: Port3 Output Mode Register.......................................................231

Figure 19.19. P4: Port4 Data Register ...................................................................................233

Figure 19.20. P4MDOUT: Port4 Output Mode Register.......................................................233

Figure 19.21. P5: Port5 Data Register ...................................................................................234

Figure 19.22. P5MDOUT: Port5 Output Mode Register.......................................................234

Figure 19.23. P6: Port6 Data Register ...................................................................................235

Figure 19.24. P6MDOUT: Port6 Output Mode Register.......................................................235

Figure 19.25. P7: Port7 Data Register ...................................................................................236

Figure 19.26. P7MDOUT: Port7 Output Mode Register.......................................................236

20. SYSTEM MANAGEMENT BUS / I2C BUS (SMBUS0) .................................................237

Figure 20.1. SMBus0 Block Diagram ...................................................................................237

Figure 20.2. Typical SMBus Configuration ..........................................................................238

Figure 20.3. SMBus Transaction ...........................................................................................239

Figure 20.4. Typical Master Transmitter Sequence...............................................................240

Figure 20.5. Typical Master Receiver Sequence ...................................................................240

Rev. 1.2 13

Page 14

C8051F120/1/2/3/4/5/6/7

Figure 20.6. Typical Slave Transmitter Sequence.................................................................241

Figure 20.7. Typical Slave Receiver Sequence .....................................................................241

Figure 20.8. SMB0CN: SMBus0 Control Register ...............................................................243

Figure 20.9. SMB0CR: SMBus0 Clock Rate Register..........................................................244

Figure 20.10. SMB0DAT: SMBus0 Data Register ...............................................................245

Figure 20.11. SMB0ADR: SMBus0 Address Register..........................................................245

Figure 20.12. SMB0STA: SMBus0 Status Register..............................................................246

21. ENHANCED SERIAL PERIPHERAL INTERFACE (SPI0) .........................................249

Figure 21.1. SPI Block Diagram............................................................................................249

Figure 21.2. Multiple-Master Mode Connection Diagram ....................................................252

Figure 21.3. 3-Wire Single Master and 3-Wire Single Slave Mode Connection Diagram ...252

Figure 21.4. 4-Wire Single Master Mode and 4-Wire Slave Mode Connection Diagram ....252

Figure 21.5. Master Mode Data/Clock Timing......................................................................254

Figure 21.6. Slave Mode Data/Clock Timing (CKPHA = 0) ................................................255

Figure 21.7. Slave Mode Data/Clock Timing (CKPHA = 1) ................................................255

Figure 21.8. SPI0CFG: SPI0 Configuration Register............................................................256

Figure 21.9. SPI0CN: SPI0 Control Register ........................................................................257

Figure 21.10. SPI0CKR: SPI0 Clock Rate Register..............................................................258

Figure 21.11. SPI0DAT: SPI0 Data Register ........................................................................259

Figure 21.12. SPI Master Timing (CKPHA = 0)...................................................................260

Figure 21.13. SPI Master Timing (CKPHA = 1)...................................................................260

Figure 21.14. SPI Slave Timing (CKPHA = 0) .....................................................................261

Figure 21.15. SPI Slave Timing (CKPHA = 1) .....................................................................261

22. UART0 ..................................................................................................................................263

Figure 22.1. UART0 Block Diagram.....................................................................................263

Figure 22.2. UART0 Mode 0 Timing Diagram .....................................................................264

Figure 22.3. UART0 Mode 0 Interconnect............................................................................264

Figure 22.4. UART0 Mode 1 Timing Diagram .....................................................................265

Figure 22.5. UART0 Modes 2 and 3 Timing Diagram..........................................................266

Figure 22.6. UART0 Modes 1, 2, and 3 Interconnect Diagram ............................................267

Figure 22.7. UART Multi-Processor Mode Interconnect Diagram .......................................269

Figure 22.8. SCON0: UART0 Control Register....................................................................271

Figure 22.9. SSTA0: UART0 Status and Clock Selection Register......................................272

Figure 22.10. SBUF0: UART0 Data Buffer Register............................................................273

Figure 22.11. SADDR0: UART0 Slave Address Register ....................................................273

Figure 22.12. SADEN0: UART0 Slave Address Enable Register ........................................273

23. UART1 ..................................................................................................................................275

Figure 23.1. UART1 Block Diagram.....................................................................................275

Figure 23.2. UART1 Baud Rate Logic ..................................................................................276

Figure 23.3. UART Interconnect Diagram ............................................................................277

Figure 23.4. 8-Bit UART Timing Diagram ...........................................................................277

Figure 23.5. 9-Bit UART Timing Diagram ...........................................................................278

Figure 23.6. UART Multi-Processor Mode Interconnect Diagram .......................................279

Figure 23.7. SCON1: Serial Port 1 Control Register.............................................................280

Figure 23.8. SBUF1: Serial (UART1) Port Data Buffer Register .........................................281

14 Rev. 1.2

Page 15

C8051F120/1/2/3/4/5/6/7

24. TIMERS................................................................................................................................285

Figure 24.1. T0 Mode 0 Block Diagram................................................................................286

Figure 24.2. T0 Mode 2 Block Diagram................................................................................287

Figure 24.3. T0 Mode 3 Block Diagram................................................................................288

Figure 24.4. TCON: Timer Control Register.........................................................................289

Figure 24.5. TMOD: Timer Mode Register...........................................................................290

Figure 24.6. CKCON: Clock Control Register......................................................................291

Figure 24.7. TL0: Timer 0 Low Byte ....................................................................................292

Figure 24.8. TL1: Timer 1 Low Byte ....................................................................................292

Figure 24.9. TH0: Timer 0 High Byte ...................................................................................292

Figure 24.10. TH1: Timer 1 High Byte .................................................................................292

Figure 24.11. T2, 3, and 4 Capture Mode Block Diagram ....................................................294

Figure 24.12. T2, 3, and 4 Auto-reload Mode Block Diagram..............................................295

Figure 24.13. TMRnCN: Timer 2, 3, and 4 Control Registers ..............................................297

Figure 24.14. TMRnCF: Timer 2, 3, and 4 Configuration Registers ....................................298

Figure 24.15. RCAPnL: Timer 2, 3, and 4 Capture Register Low Byte................................299

Figure 24.16. RCAPnH: Timer 2, 3, and 4 Capture Register High Byte ..............................299

Figure 24.17. TMRnL: Timer 2, 3, and 4 Low Byte .............................................................299

Figure 24.18. TMRnH Timer 2, 3, and 4 High Byte .............................................................300

25. PROGRAMMABLE COUNTER ARRAY .......................................................................301

Figure 25.1. PCA Block Diagram..........................................................................................301

Figure 25.2. PCA Counter/Timer Block Diagram.................................................................302

Figure 25.3. PCA Interrupt Block Diagram...........................................................................303

Figure 25.4. PCA Capture Mode Diagram ............................................................................304

Figure 25.5. PCA Software Timer Mode Diagram................................................................305

Figure 25.6. PCA High Speed Output Mode Diagram ..........................................................306

Figure 25.7. PCA Frequency Output Mode...........................................................................307

Figure 25.8. PCA 8-Bit PWM Mode Diagram ......................................................................308

Figure 25.9. PCA 16-Bit PWM Mode ...................................................................................309

Figure 25.10. PCA0CN: PCA Control Register ....................................................................310

Figure 25.11. PCA0MD: PCA0 Mode Register ....................................................................311

Figure 25.12. PCA0CPMn: PCA0 Capture/Compare Mode Registers .................................312

Figure 25.13. PCA0L: PCA0 Counter/Timer Low Byte .......................................................313

Figure 25.14. PCA0H: PCA0 Counter/Timer High Byte ......................................................313

Figure 25.15. PCA0CPLn: PCA0 Capture Module Low Byte ..............................................314

Figure 25.16. PCA0CPHn: PCA0 Capture Module High Byte .............................................314

26. JTAG (IEEE 1149.1)............................................................................................................315

Figure 26.1. IR: JTAG Instruction Register ..........................................................................315

Figure 26.2. DEVICEID: JTAG Device ID Register ............................................................317

Figure 26.3. FLASHCON: JTAG Flash Control Register.....................................................319

Figure 26.4. FLASHDAT: JTAG Flash Data Register..........................................................320

Figure 26.5. FLASHADR: JTAG Flash Address Register....................................................320

Rev. 1.2 15

Page 16

C8051F120/1/2/3/4/5/6/7

Notes

16 Rev. 1.2

Page 17

C8051F120/1/2/3/4/5/6/7

LIST OF TABLES

1. SYSTEM OVERVIEW ........................................................................................................19

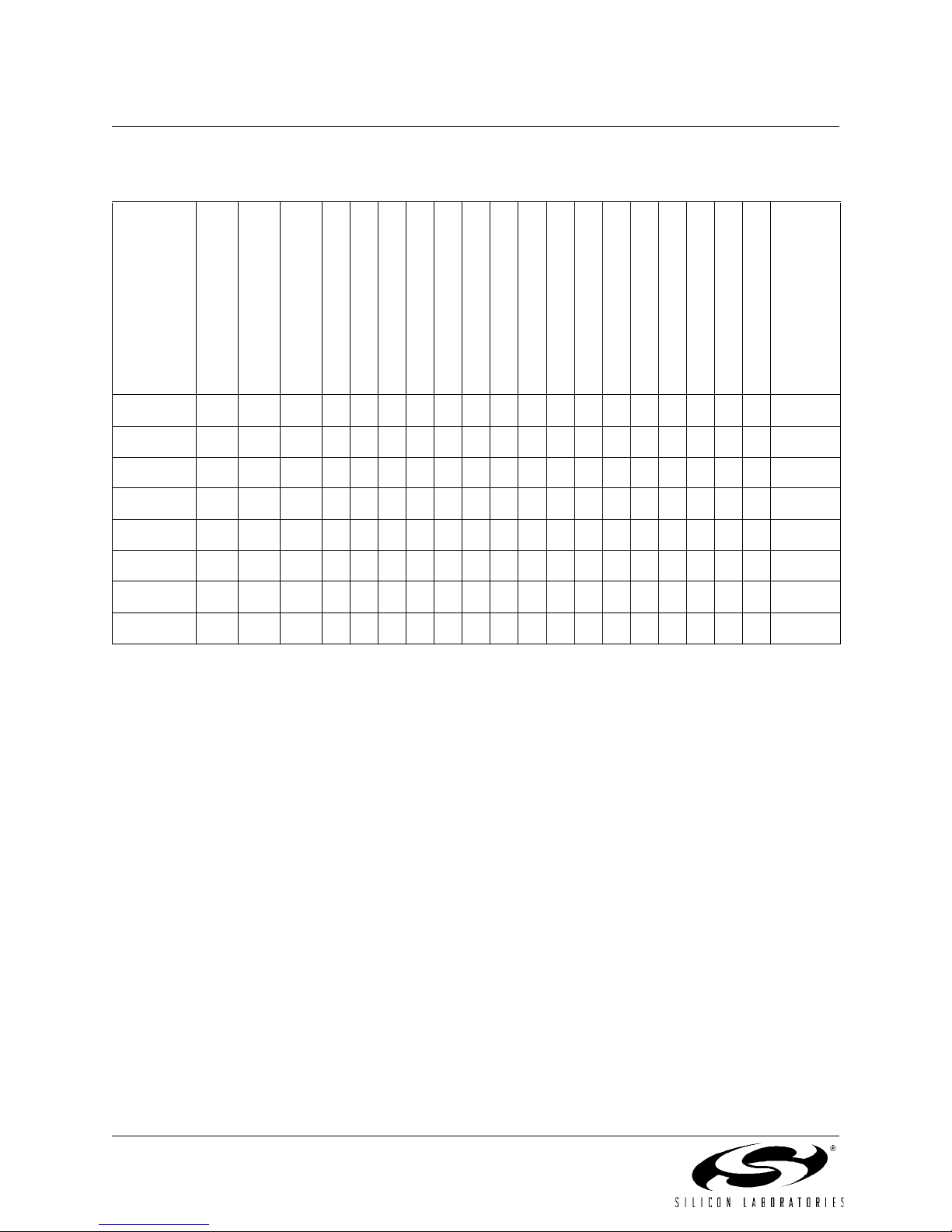

Table 1.1. Product Selection Guide .......................................................................................20

2. ABSOLUTE MAXIMUM RATINGS .................................................................................36

Table 2.1. Absolute Maximum Ratings* ...............................................................................36

3. GLOBAL DC ELECTRICAL CHARACTERISTICS .....................................................37

Table 3.1. Global DC Electrical Characteristics (C8051F120/1/2/3) ....................................37

Table 3.2. Global DC Electrical Characteristics (C8051F124/5/6/7) ....................................38

4. PINOUT AND PACKAGE DEFINITIONS .......................................................................39

Table 4.1. Pin Definitions ......................................................................................................39

5. ADC0 (12-BIT ADC, C8051F120/1/4/5 ONLY) .................................................................49

Table 5.1. 12-Bit ADC0 Electrical Characteristics (C8051F120/1/4/5) ................................66

6. ADC0 (10-BIT ADC, C8051F122/3/6/7 ONLY) .................................................................67

Table 6.1. 10-Bit ADC0 Electrical Characteristics (C8051F122/3/6/7) ................................84

7. ADC2 (8-BIT ADC) ..............................................................................................................85

Table 7.1. ADC2 Electrical Characteristics ...........................................................................97

8. DACS, 12-BIT VOLTAGE MODE .....................................................................................99

Table 8.1. DAC Electrical Characteristics ...........................................................................105

9. VOLTAGE REFERENCE (C8051F120/2/4/6) ................................................................107

Table 9.1. Voltage Reference Electrical Characteristics .....................................................108

10. VOLTAGE REFERENCE (C8051F121/3/5/7) ................................................................109

Table 10.1.Voltage Reference Electrical Characteristics .....................................................110

11. COMPARATORS ...............................................................................................................111

Table 11.1.Comparator Electrical Characteristics ................................................................118

12. CIP-51 MICROCONTROLLER .......................................................................................119

Table 12.1.CIP-51 Instruction Set Summary ........................................................................121

Table 12.2.Special Function Register (SFR) Memory Map .................................................137

Table 12.3.Special Function Registers .................................................................................138

Table 12.4.Interrupt Summary ..............................................................................................147

13. MULTIPLY AND ACCUMULATE (MAC0) ..................................................................157

Table 13.1.MAC0 Rounding (MAC0SAT = 0) ....................................................................160

14. RESET SOURCES .............................................................................................................167

Table 14.1.Reset Electrical Characteristics ..........................................................................172

15. OSCILLATORS ..................................................................................................................173

Table 15.1.Oscillator Electrical Characteristics ...................................................................173

Table 15.2.PLL Frequency Characteristics ...........................................................................182

Table 15.3.PLL Lock Timing Characteristics ......................................................................182

16. FLASH MEMORY .............................................................................................................185

Table 16.1.FLASH Electrical Characteristics .......................................................................188

17. BRANCH TARGET CACHE ............................................................................................193

18. EXTERNAL DATA MEMORY INTERFACE AND ON-CHIP XRAM ......................199

Table 18.1.AC Parameters for External Memory Interface† ................................................213

19. PORT INPUT/OUTPUT ....................................................................................................215

Rev. 1.2 17

Page 18

C8051F120/1/2/3/4/5/6/7

Table 19.1.Port I/O DC Electrical Characteristics ................................................................215

20. SYSTEM MANAGEMENT BUS / I2C BUS (SMBUS0) ................................................237

Table 20.1.SMB0STA Status Codes and States ...................................................................247

21. ENHANCED SERIAL PERIPHERAL INTERFACE (SPI0) ........................................249

Table 21.1.SPI Slave Timing Parameters .............................................................................262

22. UART0 .................................................................................................................................263

Table 22.1.UART0 Modes ....................................................................................................264

Table 22.2.Oscillator Frequencies for Standard Baud Rates ................................................270

23. UART1 .................................................................................................................................275

Table 23.1.Timer Settings for Standard Baud Rates Using The Internal Oscillator ............282

Table 23.2.Timer Settings for Standard Baud Rates Using an External Oscillator ..............282

Table 23.3.Timer Settings for Standard Baud Rates Using an External Oscillator ..............283

Table 23.4.Timer Settings for Standard Baud Rates Using the PLL ....................................283

Table 23.5.Timer Settings for Standard Baud Rates Using the PLL ....................................284

24. TIMERS ...............................................................................................................................285

25. PROGRAMMABLE COUNTER ARRAY ......................................................................301

Table 25.1.PCA Timebase Input Options .............................................................................302

Table 25.2.PCA0CPM Register Settings for PCA Capture/Compare Modules ...................303

26. JTAG (IEEE 1149.1) ...........................................................................................................315

Table 26.1.Boundary Data Register Bit Definitions .............................................................316

18 Rev. 1.2

Page 19

C8051F120/1/2/3/4/5/6/7

1. SYSTEM OVERVIEW

The C8051F12x devices are fully integrated mixed-signal System-on-a-Chip MCUs with 64 digital I/O pins

(C8051F120/2/4/6) or 32 digital I/O pins (C8051F121/3/5/7). Highlighted features are listed below; refer to Table 1.1

for specific product feature selection.

• High-Speed pipelined 8051-compatible CIP-51 microcontroller core (up to 100 MIPS for C8051F120/1/2/3 and

50 MIPS for C8051F124/5/6/7)

• In-system, full-speed, non-intrusive debug interface (on-chip)

• True 12-bit (C8051F120/1/4/5) or 10-bit (C8051F122/3/6/7) 100 ksps ADC with PGA and 8-channel analog

multiplexer

• True 8-bit 500 ksps ADC with PGA and 8-channel analog multiplexer

• Two 12-bit DACs with programmable update scheduling

• 2-cycle 16 by 16 Multiply and Accumulate Engine (C8051F120/1/2/3)

• 128k bytes of in-system programmable FLASH memory

• 8448 (8k + 256) bytes of on-chip RAM

• External Data Memory Interface with 64k byte address space

•SPI, SMBus/I

• Five general purpose 16-bit Timers

• Programmable Counter/Timer Array with 6 capture/compare modules

• On-chip Watchdog Timer, VDD Monitor, and Temperature Sensor

2

C, and (2) UART serial interfaces implemented in hardware

With on-chip VDD monitor, Watchdog Timer, and clock oscillator, the C8051F12x devices are truly stand-alone System-on-a-Chip solutions. All analog and digital peripherals are enabled/disabled and configured by user firmware.

The FLASH memory can be reprogrammed even in-circuit, providing non-volatile data storage, and also allowing

field upgrades of the 8051 firmware.

On-board JTAG debug circuitry allows non-intrusive (uses no on-chip resources), full speed, in-circuit debugging

using the production MCU installed in the final application. This debug system supports inspection and modification

of memory and registers, setting breakpoints, watchpoints, single stepping, run and halt commands. All analog and

digital peripherals are fully functional while debugging using JTAG.

Each MCU is specified for operation over the industrial temperature range (-45° C to +85° C). The Port I/Os, /RST,

and JTAG pins are tolerant for input signals up to 5 V. The C8051F120/2/4/6 are available in a 100-pin TQFP package (see block diagrams in Figure 1.1 and Figure 1.3). The C8051F121/3/5/7 are available in a 64-pin TQFP package

(see block diagrams in Figure 1.2 and Figure 1.4).

Rev. 1.2 19

Page 20