)

0

(

RED

YELLOW

HIGH EFFICIENCY RED

GREEN

HIGH EFFICIENCY GREEN

PLCD5580

PLCD5581

PLCD5582

PLCD5583

PLCD5584

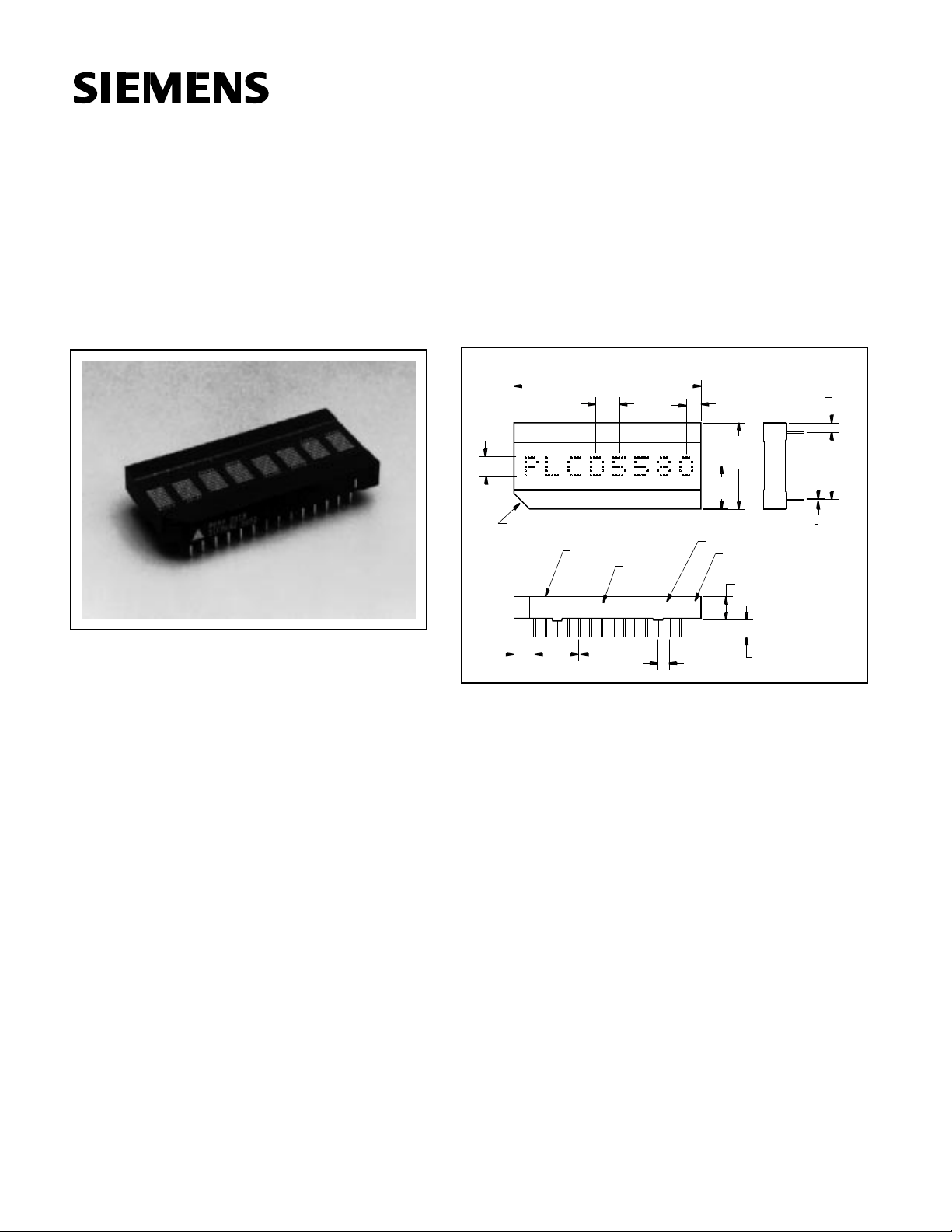

Low Power 0.145” 8-Character, 5x5 Dot Matrix

Parallel Input Alphanumeric Intelligent Display

Package Dimensions in inches (mm)

.145

3.68)

1.680 (42.67) max.

0.210

(5.34)

Pin 1 Indicator

Part Number

PLCD558X

SIEMENS

WW

EIA Date

Code

Z

0.105

(2.67)

0.771

(19.58)

0.386

(9.8)

0.012 (0.30) typ.

Intensity Code

Color Bin

(For Yellow Only)

1

0.209 (5.31)

0.086

(2.19)

0.600

(15.24

FEATURES

•

Eight 0.145” (3.68 mm) High 5 x 5 Dot Matrix Characters in Red, Yellow, High Efficiency Red, Green,

or High Efficiency Green

Built-in 2 Page, 256 Character ROM. Both Pages

•

Mask Programmable for Custom Fonts

•

Built-in Decoders, Multiplexers and Drivers

Wide Viewing Angle, X Axis ± 50 ° , Y Axis ± 65 °

•

•

Programmable Features:

– Individual Flashing Character

– Full Display Blinking

– Multi-Level Dimming and Blanking

– Clear Function

– Lamp Test

•

Internal or External Clock

•

End Stackable Dual-In-Line Plastic Package

Low Power: 20% Less Power Consumption Than

•

5 X 7 Format

0.189

(4.79)

DESCRIPTION

The PLCD5580 (Red), PLCD5581 (Yellow), PLCD5582 (High Efficiency Red), PLCD5583 (Green), and PLCD5584 (High Efficiency

Green) are eight digit, 5x5 dot matrix, alphanumeric Programmable Displays. The 0.145 inch high digits are packaged in a rugged, high quality, optically transparent, standard 0.6 inch 28 pin

plastic DIP.

The on-board CMOS has a built-in two page, 256 character ROM.

Both pages are mask programmable for 256 custom characters.

The first page of ROM of the standard product contains 128 characters including ASCII, selected European and Scientific symbols. The second page contains Katakana Japanese characters,

more European characters, Avionics, and other graphic symbols.

The PLCD558X is designed for standard microprocessor interface techniques and is fully TTL compatible. The Clock I/O and

Clock Select pins allow the user to synchronize multiple display

modules.

0.018 typ.

(.46)

0.100

(2.54) typ.

0.160±.020

(4.06±.50)

2–131

)

.

Maximum Rating

DC Supply Voltage ........................................–0.5 to +7.0 Vdc

Input Voltage Levels Relative

to Ground...............................................–0.5 to V

Operating Temperature .................................–40 °

Storage Temperature....................................–40 °

+0.5 Vdc

CC

C to +85 ° C

C to +100 ° C

Maximum Solder Temperature 0.063"

below Seating Plane, t<5 sec...................................... 260 °

Relative Humidity at 85 °

Note: Maximum voltage is with no LEDs illuminated.

C.................................................85%

C

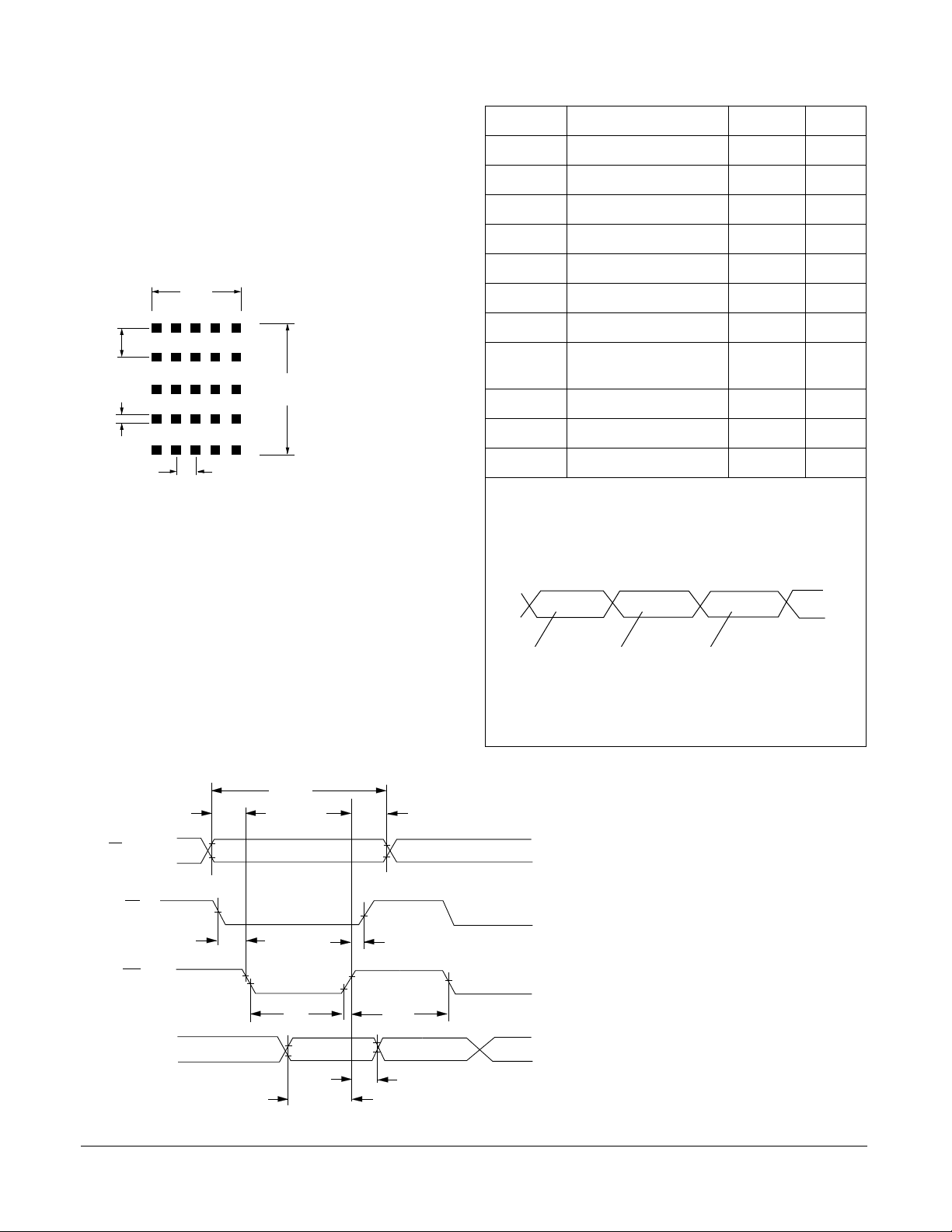

Enlarged Character Font

0.033

(0.84)

typ.

0.011

(0.28)

typ.

0.100

(2.54)

C0 C1 C2 C3 C4

0.022

(0.56) typ.

R0

R1

R2

R3

R4

0.145

(3.68)

Dimensions in inches (mm)

Tolerance: .XXX= ±

.010 (.25)

Switching Specifications

(over operating temperature range and V

=4.5 V).

CC

Symbol Description Min. Units

Tbw Time Between Writes 30 ns

(2)

Tacc

Display Access Time 130 ns

Tas Address Setup Time 10 ns

Tces Chip Enable Hold Time 0 ns

Tah Address Hold Time 20 ns

Tceh Chip Enable Hold Time 0 ns

Tw Write Active Time 100 ns

Tds Data Valid Prior to

50 ns

Rising Edge of Write

Tdh Data Hold Time 20 ns

(1)

Trc

Tclr

(3)

Reset Active Time 300 ns

Clear Cycle Time 3

µ s

1. Wait 300 ns min. after the reset function is turned off.

2. Tacc=Tas + Tw + Tah

3. The Clear Cycle Time may be shortened by writing a

second Control Word with the Clear Bit disabled, 160 ns

after the first control word that enabled the Clear Bit.

Write Cycle Timing Diagram

Tas

FL, A3-A0

CE

Tces

WR

D7-D0

Tacc

Tw

Tds

Tah

Tdh

Tceh

Tbw

data wait data

write control

word-clear bit

enabled

wait 130 ns write control

word-clear bit

enabled

The Flash RAM and Character RAM may not be accessed

until the Clear Cycle is complete.

see Notes

see Notes

see Notes

Notes

see Notes

1. All input voltages are (VIL=0.8 V, VIH=2.0 V

2. These wave forms are not edge triggered

3. Tbw=Tas + Tah

2–132

PLCD5580/1/2/3/4

Optical Characteristics at 25 ° C

V

=5.0 V at Full Brightness

CC

Red PLCD5580

Description Symbol Min. Typ. Units

Peak Luminous Intensity

Peak Wavelength

Dominant Wavelength

(1)

I

V

peak

λ

(peak) 660 nm

λ

(d) 639 nm

70 90

Yellow PLCD5581

Description Symbol Min. Typ. Units

Peak Luminous Intensity

Peak Wavelength

Dominant Wavelength

(1)

I

V

peak

λ

(peak) 583 nm

λ

(d) 585 nm

130 210

High Efficiency Red PLCD5582

Description Symbol Min. Typ. Units

Peak Luminous Intensity

Peak Wavelength

Dominant Wavelength

(1)

I

V

peak

λ

(peak) 630 nm

λ

(d) 626 nm

150 330

Green PLCD5583

Description Symbol Min. Typ. Units

µ cd/dot

µ cd/dot

µ cd/dot

Peak Luminous Intensity

Peak Wavelength

Dominant Wavelength

(1)

I

V

peak

λ

(peak) 565 nm

λ

(d) 570 nm

150 260

High Efficiency Green PLCD5584

Description Symbol Min. Typ. Units

Peak Luminous Intensity

Peak Wavelength

Dominant Wavelength

Note

1. Peak luminous intensity is meaaured at T

(1)

I

V

peak

λ

(peak) 568 nm

λ

(d) 574 nm

=T

=25 ° C. No time is allowed for the device to warm up prior to measurement.

A

J

200 510

µ cd/dot

µ cd/dot

2–133

PLCD5580/1/2/3/4

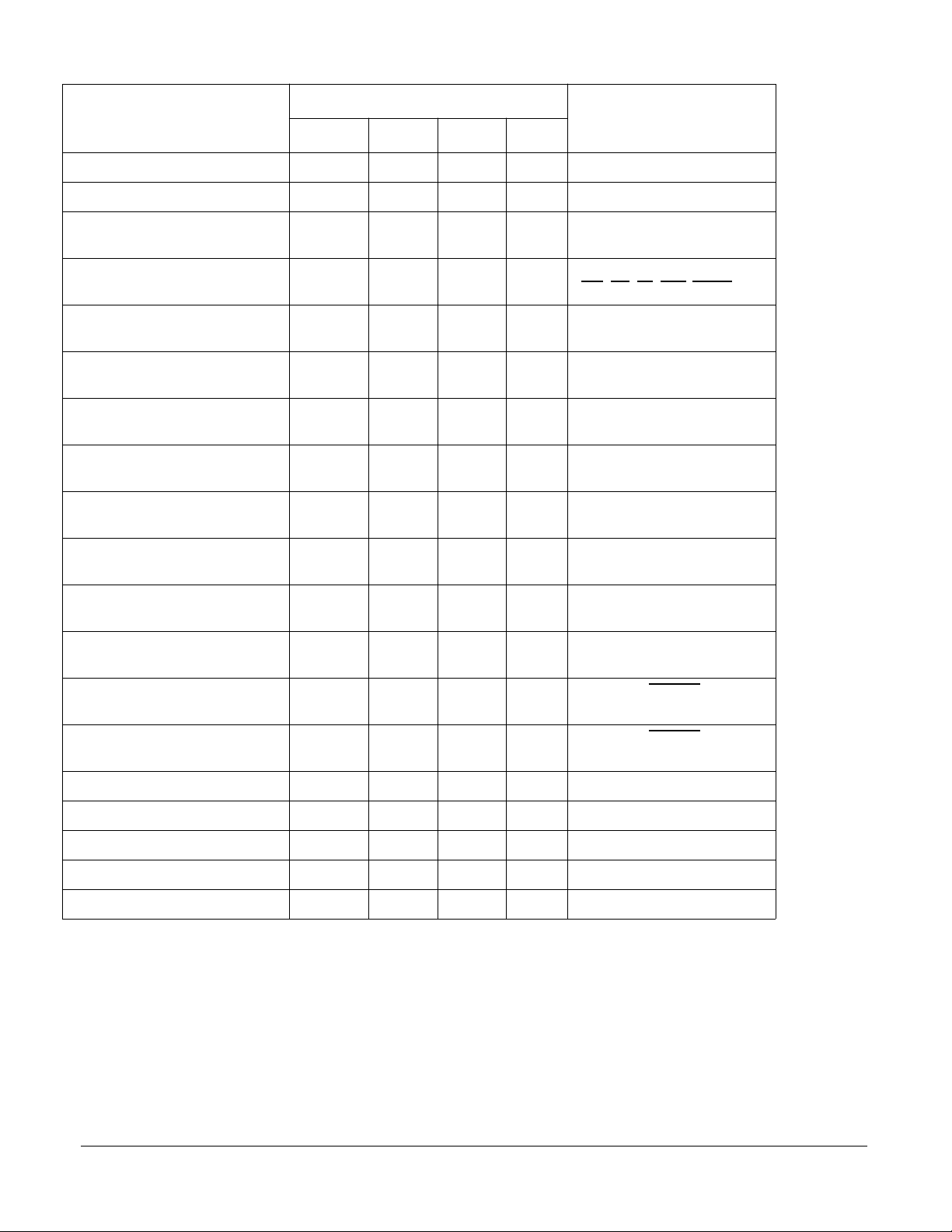

Electrical Characteristics at 25 ° C

Parameters

Limits

Min. Typ. Max. Units

Conditions

V

CC

I

Blank 0.5 1.0 mA V

CC

I

8 digits

CC

I

Current

IP

(1)

, 16 dots/character 240 290 mA V

4.5 5.0 5.5 V

11 18

µ AV

(with pull-up)

I

Input leakage current

I

± 1

µ AV

(without pull-up)

V

Input Voltage High 2.0 V

IH

CC

VV

+0.3

V

Input Voltage Low GND

IL

0.8 V V

–0.3

V

Output Voltage Low

OL

0.4 V V

(Clock Pin)

V

Output Voltage High

OH

2.4 V VCC=4.5 V to 5.5 V,

(Clock Pin)

I

Output Current High

OH

–0.9 mA VCC=4.5 V, VOH=2.4 V

(Clock I/O)

I

Output Current Low

OL

1.6 2 mA VCC=4.5 V, VOL=0.4 V

(Clock I/O)

=5 V, V

CC

=5 V, “#” displayed in all

CC

IN

=5 V

eight digits

=5 V, V

CC

(WR

, CE, FL, RST, ClkSel)

=5 V, V

CC

=0 V to V

IN

=0 V to V

IN

CC

CC

(Clk I/O, A0–A3, D0–D7)

=4.5 V to 5.5 V

CC

=4.5 V to 5.5 V

CC

=4.5 V to 5.5 V,

CC

I

=1.6 mA

OL

I

=40 µA

OH

,

,

θ

Thermal Resistance,

JC

25 °C/W

Junction to Case

F

External Clock,

ext

Input Frequency

F

Internal Clock,

osc

Output Frequency

(2)

(2)

28 81.14 KHz VCC=5.0 V, CLKSEL=0

28 81.14 KHz VCC=5.0 V, CLKSEL=1

Clock I/O Buss Loading 240 pF

Clock Out Rise Time 500 ns V

Clock Out Fall Time 500 ns V

FM, Digit Multiplex Frequency 125 256 362.5 Hz

Blinking Rate 0.98 2 2.83 Hz

Notes:

1. Average I

2. Internal/external frequency duty factor is 50%.

measured at full brightness. Peak I

CC

CC

5

=

⁄

8

x I

I

(# displayed).

AVG

CC

=4.5 V, VOH=2.4 V

CC

=4.5 V, VOL=0.4 V

CC

2–134

PLCD5580/1/2/3/4

Loading...

Loading...