Siemens HYM328020GS-50, HYM328020GS-60, HYM328020S-50, HYM328020S-60 Datasheet

8M × 32-Bit Dynamic RAM Module HYM 328020S/GS-50/-60

• SIMM modules with 8 388 608 words by 32-bit organization

for PC main memory applications

• Fast access and cycle time

50 ns access time

90 ns cycle time (-50 version)

60 ns access time

110 ns cycle time (-60 version)

• Fast page mode capability

35 ns cycle time (-50 version)

40 ns cycle time (-60 version)

• Single + 5 V (± 10 %) supply

• Low power dissipation

max. 5280 mW active (-50 version)

max. 4840 mW active (-60 version)

CMOS – 88 mW standby

TTL –176 mW standby

• CAS-before-RAS refresh

RAS-only-refresh

Hidden-refresh

• 16 decoupling capacitors mounted on substrate

• All inputs, outputs and clocks fully TTL compatible

• 72 pin Single in-Line Memory Module (L-SIM-72) with 25.40 mm height

• Utilizes sixteen 4Mx4-DRAMs in SOJ packages

• 2048 refresh cycles / 32 ms

• Optimized for use in byte-write non-parity applications

• Tin-Lead contact pads (S- version)

• Gold contact pads (GS -version)

Semiconductor Group 1

1.96

HYM 328020S/GS-50/-60

8M × 32-Bit

The HYM 328020S/GS-50/-60 is a 32 MByte DRAM module organized as 8 388 608 words by

32-bit in a 72-pin single-in-line package comprising sixteen HYB 5117400BJ 4M × 4 DRAMs in 300

mil wide SOJ-packages mounted together with sixteen 0.2 µF ceramic decoupling capacitors on a

PC board.

The HYM 328020S/GS-50/-60 can also be used as a 16 777 360 words by 16-bits dynamic RAM

module by means of connecting DQ0 and DQ16, DQ1 and DQ17, DQ2 and DQ18, … , DQ15 and

DQ31, respectively.

Each HYB 5117400BJ is described in the data sheet and is fully electrical tested and processed

according to SIEMENS standard quality procedure prior to module assembly. After assembly onto

the board, a further set of electrical tests is performed.

The speed of the module can be detected by the use of four presence detect pins.

The common I/O feature on the HYM 328020S/GS-50/-60 dictates the use of early write cycles.

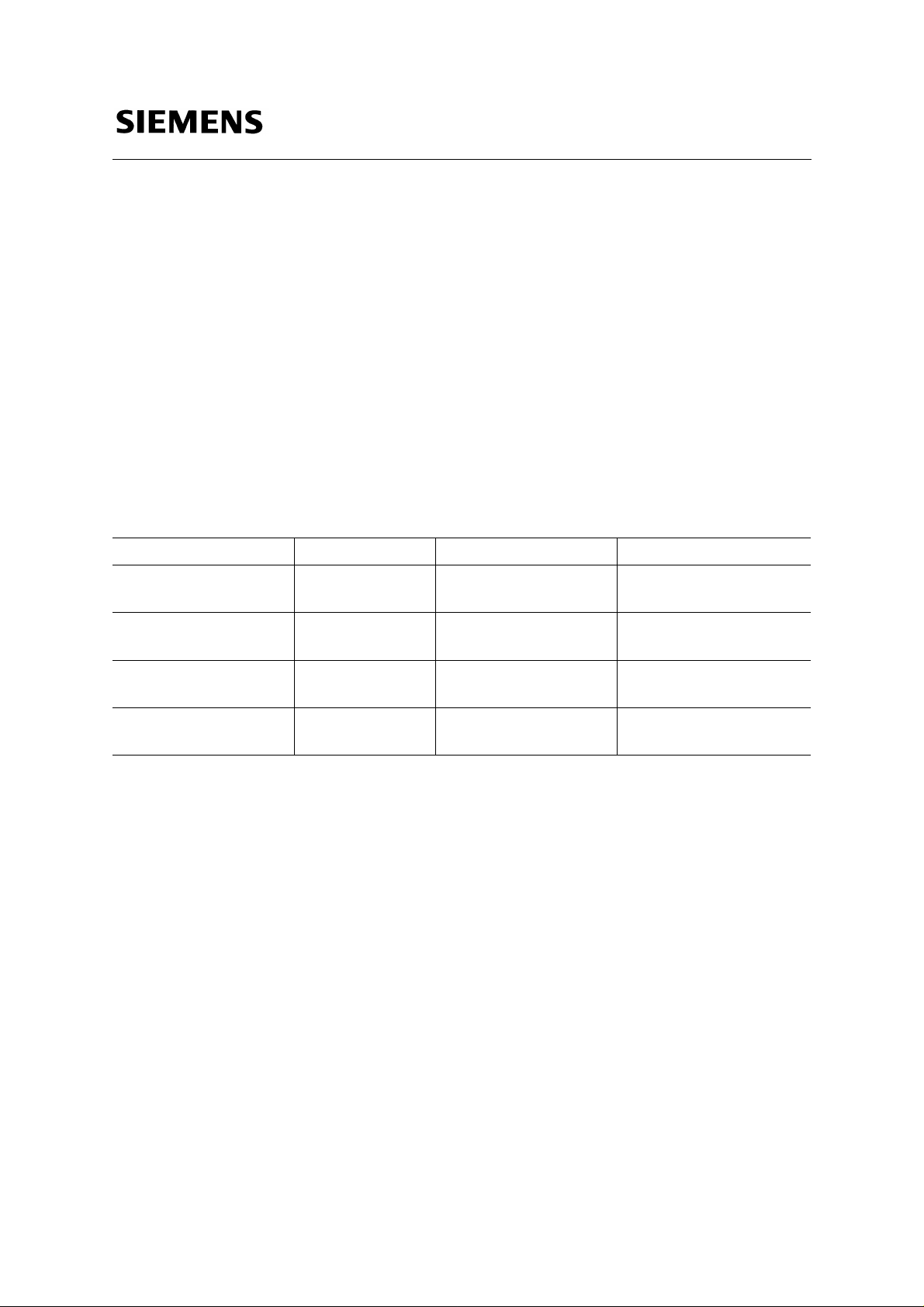

Ordering Information

Type Ordering Code Package Description

HYM 328020S-50 L-SIM-72-15 DRAM Module

(access time 50 ns)

HYM 328020S-60 Q67100-Q2001 L-SIM-72-15 DRAM Module

(access time 60 ns)

HYM 328020GS-50 L-SIM-72-15 DRAM Module

(access time 50 ns)

HYM 328020GS-60 Q67100-Q2008 L-SIM-72-15 DRAM Module

(access time 60 ns)

Semiconductor Group 2

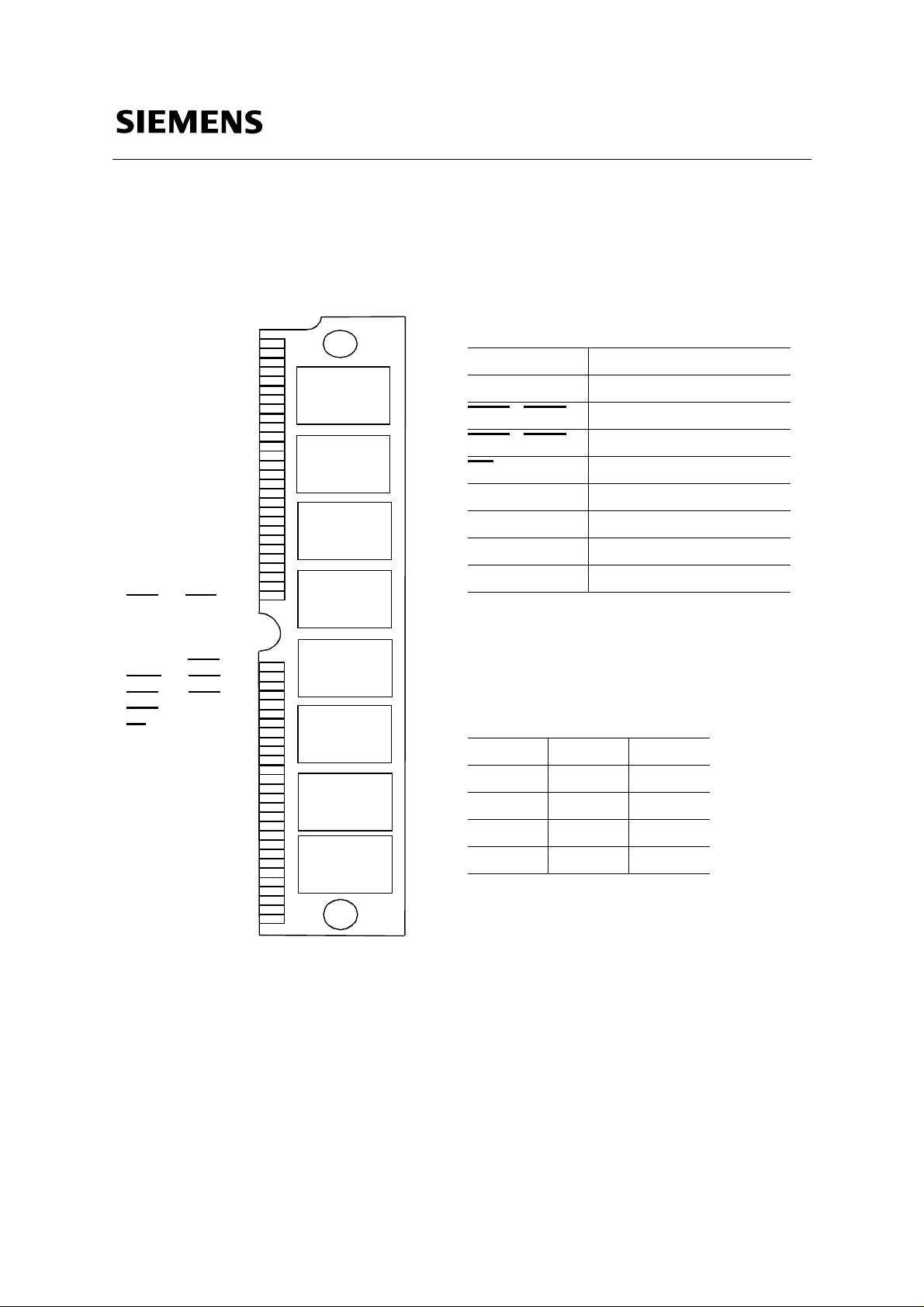

Pin Configuration

VSS 1 DQ0 2

DQ16 3 DQ1 4

DQ17 5 DQ2 6

DQ18 7 DQ3 8

DQ19 9 VCC 10

N.C. 11 A0 12

A1 13 A2 14

A3 15 A4 16

A5 17 A6 18

A10 19 DQ4 20

DQ20 21 DQ5 22

DQ21 23 DQ6 24

DQ22 25 DQ7 26

DQ23 27 A7 28

N.C 29 VCC 30

A8 31 A9 32

RAS3

33 RAS2 34

N.C. 35 N.C. 36

HYM 328020S/GS-50/-60

8M × 32-Bit

Pin Names

A0-A10 Address Inputs

DQ0-DQ31 Data Input/Output

- CAS3 Column Address Strobe

CAS0

- RAS3 Row Address Strobe

RAS0

WE

V

CC

V

SS

PD Presence Detect Pin

N.C. No Connection

Read/Write Input

Power (+ 5 V)

Ground

N.C. 37 N.C. 38

VSS 39 CAS0

41 CAS3 42

CAS2

CAS1

43 RAS0 44

RAS1

45 N.C. 46

47 N.C. 48

WE

DQ8 49 DQ24 50

DQ9 51 DQ25 52

DQ10 53 DQ26 54

DQ11 55 DQ27 56

DQ12 57 DQ28 58

VCC 59 DQ29 60

DQ13 61 DQ30 62

DQ14 63 DQ31 64

DQ15 65 N.C. 66

PD0 67 PD1 68

PD2 69 PD3 70

N.C. 71 VSS 72

40

Presence Detect Pins

-50 -60

PD0 N.C. N.C.

PD1

PD2

PD3

V

SS

V

SS

V

SS

V

SS

N.C.

N.C.

Semiconductor Group 3

Loading...

Loading...