Siemens SIMATIC S7-300 Series, CPU 314 IFM, CPU 315, CPU 315-2 DP, CPU 316-2 DP Reference Manual

...Page 1

DATASHEET

6ES7314-5AE03-0AB0

SIEMENS

OTHER SYMBOLS:

RGB ELEKTRONIKA AGACIAK CIACIEK

SPÓŁKA JAWNA

Jana Dlugosza 2-6 Street

51-162 Wrocław

Poland

biuro@rgbelektronika.pl

+48 71 325 15 05

www.rgbautomatyka.pl

www.rgbelektronika.pl

www.rgbelektronika.pl

www.rgbautomatyka.pl

Page 2

YOUR

PARTNER IN

MAINTENANCE

Repair this product with RGB ELEKTRONIKA

LINEAR

ENCODERS

ENCODERS

SERVO AMPLIFIERS

CNC

MACHINES

OUR SERVICES

PLC

SYSTEMS

CNC

CONTROLS

ORDER A DIAGNOSIS

INDUSTRIAL

COMPUTERS

POWER

SUPPLIERS

∠

MOTORS

SERVO

DRIVERS

At our premises in Wrocław, we have a fully equipped servicing facility. Here we perform all the repair

works and test each later sold unit. Our trained employees, equipped with a wide variety of tools and

having several testing stands at their disposal, are a guarantee of the highest quality service.

Buy this product at RGB AUTOMATYKA

OPERATOR

PANELS

BUY

∠

Page 3

Preface, Contents

SIMATIC

PLC S7-300,

CPU Specifications CPU 312 IFM

to CPU 318-2 DP

Reference Manual

CPUs

CPU 31x-2 as DP Master/DP

Slave and Direct Communication

Cycle and Reaction times

CPU Function, depending on

CPU and STEP 7 Version

Tips and Tricks

Appendix

Standards, Certificates and

Approvals

Dimensioned Drawings

List of Abbreviations

1

2

3

4

5

A

B

C

This manual is part of the documentation

package with the order number

6ES7398-8FA10-8BA0

Edition 10/2001

A5E00111190-01

This documentation can no longer be ordered under

the given number!

Glossary, Index

Page 4

Safety Guidelines

This manual contains notices intended to ensure personal safety, as well as to protect the products and

connected equipment against damage. These notices are highlighted by the symbols shown below and

graded according to severity by the following texts:

Danger

!

indicates that death, severe personal injury or substantial property damage will result if proper precautions

are not taken.

Warning

!

indicates that death, severe personal injury or substantial property damage can result if proper

precautions are not taken.

Caution

!

indicates that minor personal injury can result if proper precautions are not taken.

Caution

indicates that property damage can result if proper precautions are not taken.

Notice

draws your attention to particularly important information on the product, handling the product, or to a

particular part of the documentation.

Qualified Personnel

Only qualified personnel should be allowed to install and work on this equipment. Qualified persons are

defined as persons who are authorized to commission, to ground and to tag circuits, equipment, and

systems in accordance with established safety practices and standards.

Correct Usage

Note the following:

Warning

!

Trademarks

The reproduction, transmission or use of this document or its

contents is not permitted without express written authority.

Offenders will be liable for damages. All rights, including rights

created by patent grant or registration of a utility model or

design, are reserved.

Siemens AG

Bereich Automatisierungs- und Antriebstechnik

Geschaeftsgebiet Industrie-Automatisierungssysteme

Postfach 4848, D- 90327 Nuernberg

Index-2

Siemens Aktiengesellschaft A5E00111190

This device and its components may only be used for the applications described in the catalog or the

technical description, and only in connection with devices or components from other manufacturers which

have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed

correctly, and operated and maintained as recommended.

SIMATIC, SIMA TIC HMI and SIMATIC NET are registered trademarks of SIEMENS AG.

Third parties using for their own purposes any other names in this document which refer to trademarks

might infringe upon the rights of the trademark owners.

Disclaim of LiabilityCopyright W Siemens AG 2001 All rights reserved

We have checked the contents of this manual for agreement

with the hardware and software described. Since deviations

cannot be precluded entirely, we cannot guarantee full

agreement. However, the data in this manual are reviewed

regularly and any necessary corrections included in

subsequent editions. Suggestions for improvement are

welcomed.

Siemens AG 2001

Technical data subject to change.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 5

Preface

Purpose of the Manual

This manual gives you a brief overview of 312 IFM to 318-2 CPUS in an S7-300.

You can look up information on how to operate the system, its functions and

technical data of the CPUs.

Essential know-how

General knowledge of automation technology is required for comprehension of this

Manual. You should also be acquainted with basic STEP 7 software as described

in your Programming with STEP 7 V 5.1 Manual.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

iii

Page 6

Preface

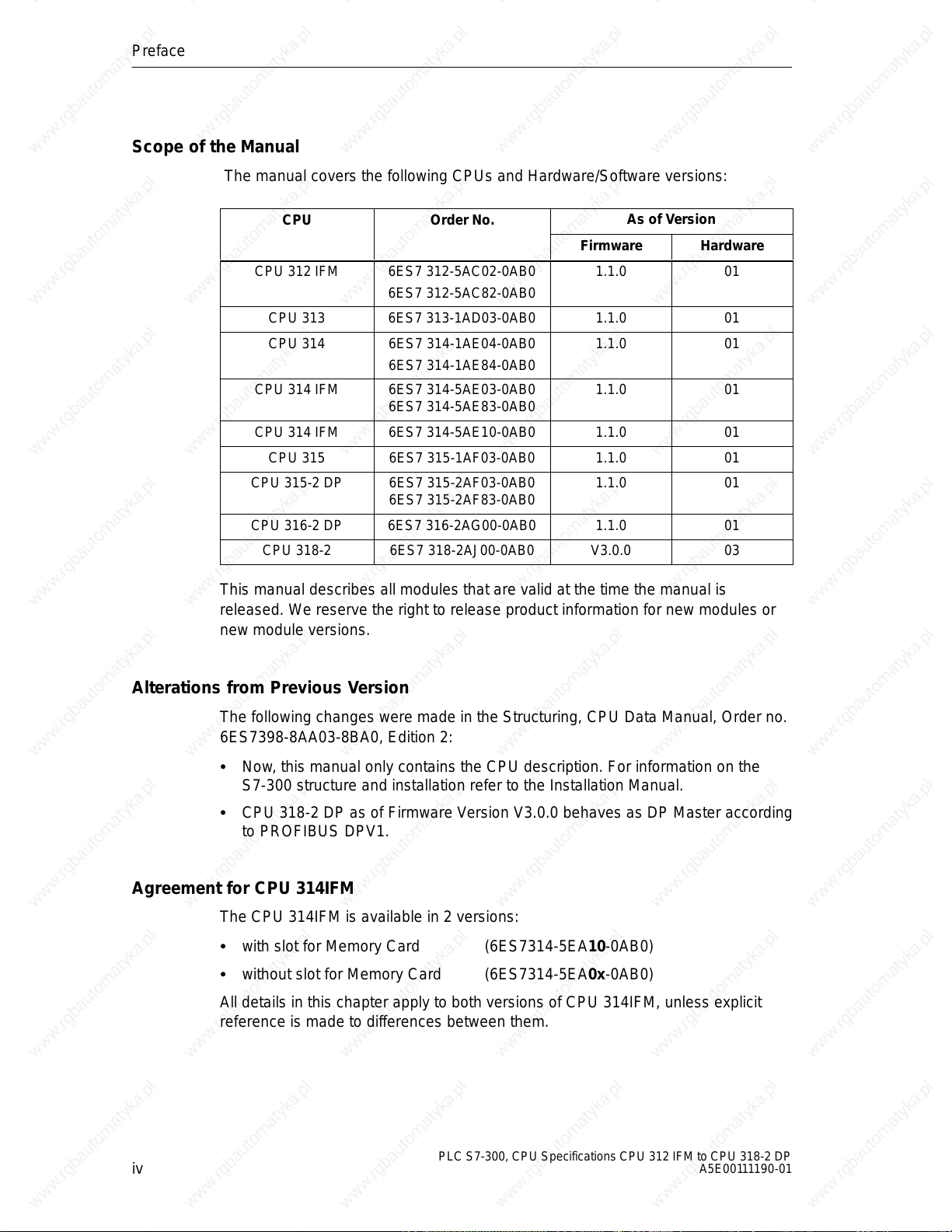

Scope of the Manual

The manual covers the following CPUs and Hardware/Software versions:

CPU Order No.

CPU 312 IFM 6ES7 312-5AC02-0AB0

6ES7 312-5AC82-0AB0

CPU 313 6ES7 313-1AD03-0AB0 1.1.0 01

CPU 314 6ES7 314-1AE04-0AB0

6ES7 314-1AE84-0AB0

CPU 314 IFM 6ES7 314-5AE03-0AB0

6ES7 314-5AE83-0AB0

CPU 314 IFM 6ES7 314-5AE10-0AB0 1.1.0 01

CPU 315 6ES7 315-1AF03-0AB0 1.1.0 01

CPU 315-2 DP 6ES7 315-2AF03-0AB0

6ES7 315-2AF83-0AB0

CPU 316-2 DP 6ES7 316-2AG00-0AB0 1.1.0 01

CPU 318-2 6ES7 318-2AJ00-0AB0 V3.0.0 03

As of Version

Firmware Hardware

1.1.0 01

1.1.0 01

1.1.0 01

1.1.0 01

This manual describes all modules that are valid at the time the manual is

released. We reserve the right to release product information for new modules or

new module versions.

Alterations from Previous Version

The following changes were made in the Structuring, CPU Data Manual, Order no.

6ES7398-8AA03-8BA0, Edition 2:

Now, this manual only contains the CPU description. For information on the

S7-300 structure and installation refer to the Installation Manual.

CPU 318-2 DP as of Firmware Version V3.0.0 behaves as DP Master according

to PROFIBUS DPV1.

Agreement for CPU 314IFM

The CPU 314IFM is available in 2 versions:

with slot for Memory Card (6ES7314-5EA10-0AB0)

without slot for Memory Card (6ES7314-5EA0x-0AB0)

All details in this chapter apply to both versions of CPU 314IFM, unless explicit

reference is made to differences between them.

iv

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 7

Approbation, Standards and Approvals

The SIMATIC S7-300 series conforms to:

Requirements and criteria to IEC 61131, Part 2

CE labeling

– EC Guideline 73/23/EEC on Low Voltages

– EC Guideline 89/336/EEC on electromagnetic compatibility (EMC)

Canadian Standards Association: CSA C22.2 Number 142, tested (Process

Control Equipment)

Underwriters Laboratories, Inc.: UL 508 registered (Industrial Control

Equipment)

Underwriters Laboratories, Inc.: UL 508 (Industrial Control Equipment)

Factory Mutual Research: Approval Standard Class Number 3611

C-Tick Australia

Preface

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

v

Page 8

Preface

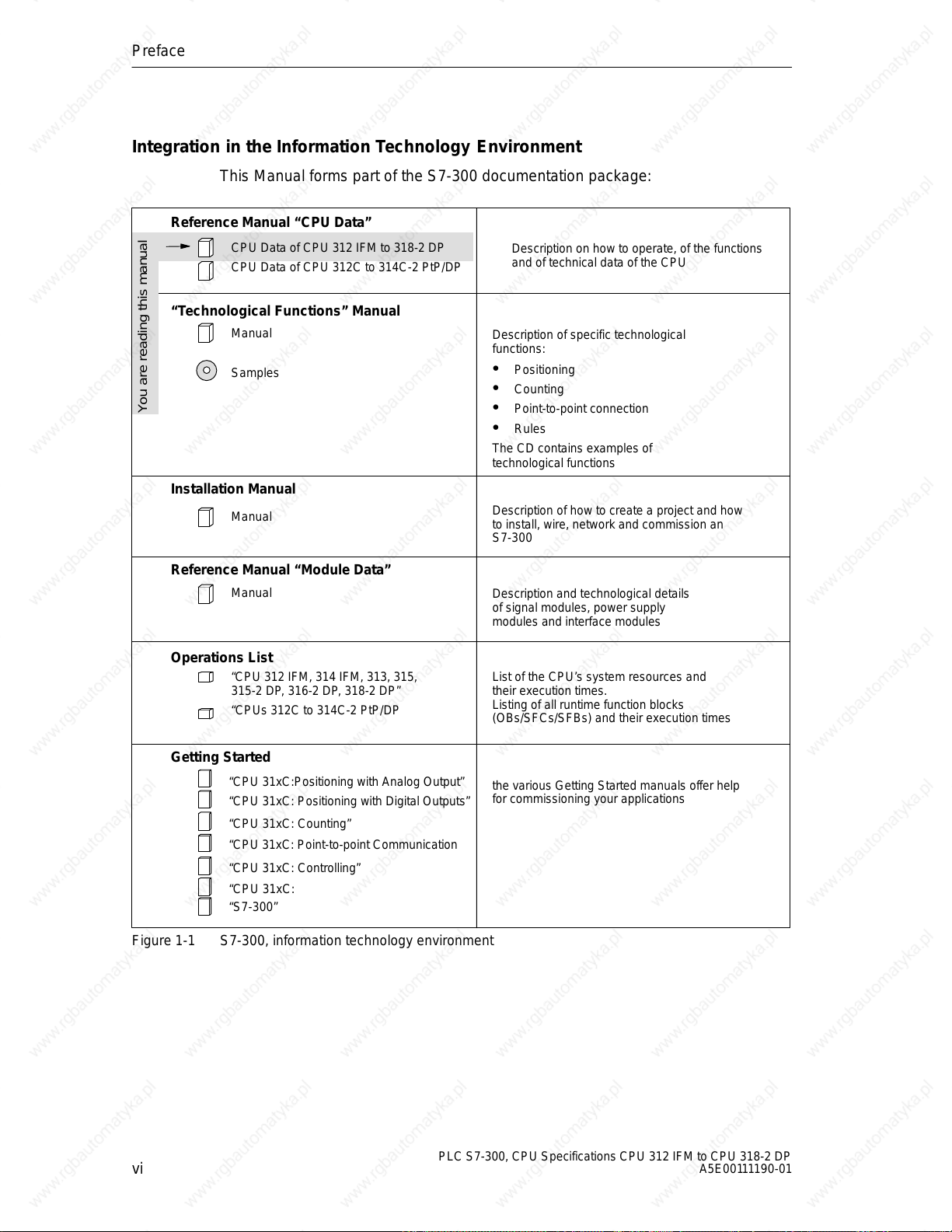

Integration in the Information Technology Environment

This Manual forms part of the S7-300 documentation package:

Reference Manual “CPU Data”

CPU Data of CPU 312 IFM to 318-2 DP

CPU Data of CPU 312C to 314C-2 PtP/DP

“Technological Functions” Manual

Manual

Samples

Description on how to operate, of the functions

and of technical data of the CPU

Description of specific technological

functions:

Positioning

Counting

You are reading this manual

Point-to-point connection

Rules

The CD contains examples of

technological functions

Installation Manual

Manual

Description of how to create a project and how

to install, wire, network and commission an

S7-300

Reference Manual “Module Data”

Manual

Operations List

“CPU 312 IFM, 314 IFM, 313, 315,

315-2 DP, 316-2 DP, 318-2 DP”

“CPUs 312C to 314C-2 PtP/DP

Getting Started

“CPU 31xC:Positioning with Analog Output”

“CPU 31xC: Positioning with Digital Outputs”

“CPU 31xC: Counting”

“CPU 31xC: Point-to-point Communication

“CPU 31xC: Controlling”

“CPU 31xC:

“S7-300”

Figure 1-1 S7-300, information technology environment

Description and technological details

of signal modules, power supply

modules and interface modules

List of the CPU’s system resources and

their execution times.

Listing of all runtime function blocks

(OBs/SFCs/SFBs) and their execution times

the various Getting Started manuals offer help

for commissioning your applications

vi

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 9

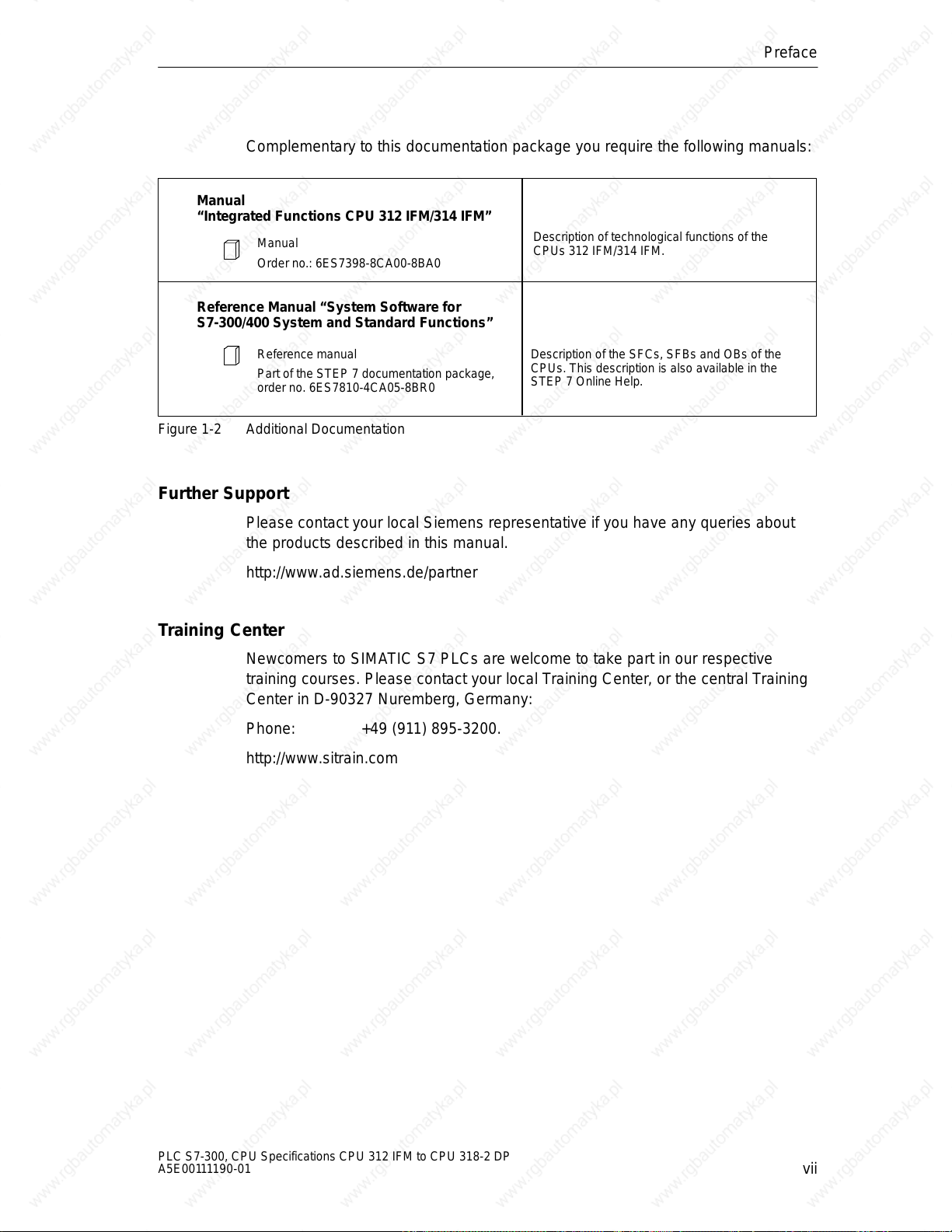

Complementary to this documentation package you require the following manuals:

Manual

“Integrated Functions CPU 312 IFM/314 IFM”

Manual

Order no.: 6ES7398-8CA00-8BA0

Reference Manual “System Software for

S7-300/400 System and Standard Functions”

Preface

Description of technological functions of the

CPUs 312 IFM/314 IFM.

Reference manual

Part of the STEP 7 documentation package,

order no. 6ES7810-4CA05-8BR0

Figure 1-2 Additional Documentation

Further Support

Please contact your local Siemens representative if you have any queries about

the products described in this manual.

http://www.ad.siemens.de/partner

Training Center

Newcomers to SIMATIC S7 PLCs are welcome to take part in our respective

training courses. Please contact your local Training Center, or the central Training

Center in D-90327 Nuremberg, Germany:

Phone: +49 (911) 895-3200.

http://www.sitrain.com

Description of the SFCs, SFBs and OBs of the

CPUs. This description is also available in the

STEP 7 Online Help.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

vii

Page 10

Preface

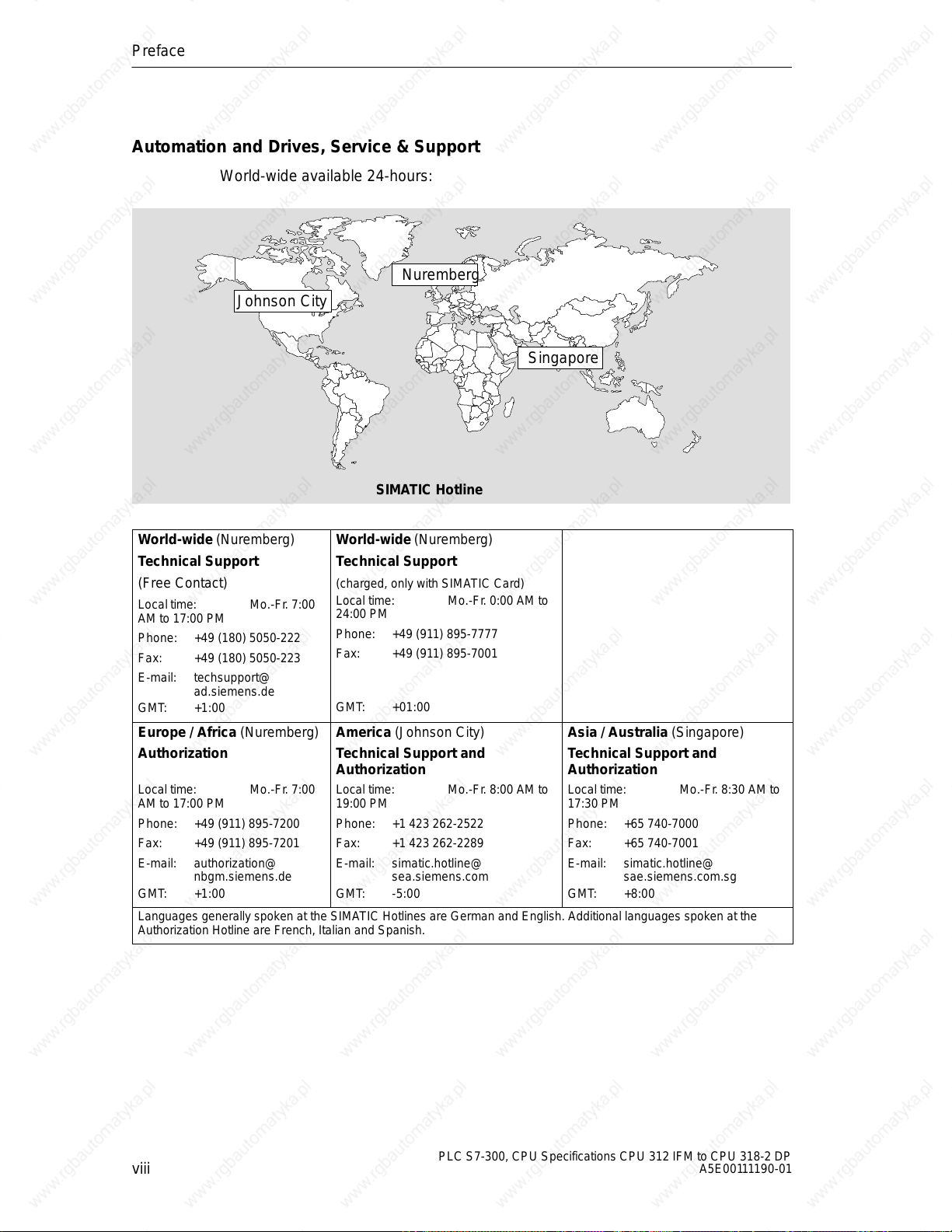

Automation and Drives, Service & Support

World-wide available 24-hours:

Nuremberg

Johnson City

SIMATIC Hotline

Singapore

World-wide (Nuremberg)

T echnical Support

(Free Contact)

Local time: Mo.-Fr. 7:00

AM to 17:00 PM

Phone: +49 (180) 5050-222

Fax: +49 (180) 5050-223

E-mail: techsupport@

ad.siemens.de

GMT: +1:00

Europe / Africa (Nuremberg)

Authorization

Local time: Mo.-Fr. 7:00

AM to 17:00 PM

Phone: +49 (911) 895-7200

Fax: +49 (911) 895-7201

E-mail: authorization@

nbgm.siemens.de

GMT: +1:00

Languages generally spoken at the SIMATIC Hotlines are German and English. Additional languages spoken at the

Authorization Hotline are French, Italian and Spanish.

World-wide (Nuremberg)

T echnical Support

(charged, only with SIMATIC Card)

Local time: Mo.-Fr. 0:00 AM to

24:00 PM

Phone: +49 (911) 895-7777

Fax: +49 (911) 895-7001

GMT: +01:00

America (Johnson City)

Technical Support and

Authorization

Local time: Mo.-Fr. 8:00 AM to

19:00 PM

Phone: +1 423 262-2522

Fax: +1 423 262-2289

E-mail: simatic.hotline@

sea.siemens.com

GMT: -5:00

Asia / Australia (Singapore)

Technical Support and

Authorization

Local time: Mo.-Fr. 8:30 AM to

17:30 PM

Phone: +65 740-7000

Fax: +65 740-7001

E-mail: simatic.hotline@

sae.siemens.com.sg

GMT: +8:00

viii

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 11

SIMATIC Documentation on the Internet

Documentation is available free of charge on the Internet under:

http://www.ad.siemens.de/support

Please use the Knowledge Manager offered at these locations for quick location of

your required documentation. Our Internet Forum offers a “Documentation”

conferencing room for your questions and solution proposals.

http://www.ad.siemens.de/support

Service & Support on the Internet

As a supplement to our provided documentation we offer our complete know-how

base on the Internet.

http://www.ad.siemens.de/support

There you will find:

Up-to-date product information (News), FAQs (Frequently Asked Questions),

Downloads, Tips and Tricks.

Preface

Our Newsletter always offers you the most up-to-date information on your

products.

The Knowledge Manager finds the right documents for you.

Users and specialists across the globe share their experiences in our Forum.

Your local service partner for Automation & Drives is found in our Service

Partner Database.

Information relating to on–site Service, repairs, spare parts and lots more is

available to you under the topic “Service”.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

ix

Page 12

Preface

x

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 13

Contents

1 CPUs

1.1 Control and Display Elements 1-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.1 Status and Fault Displays 1-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.2 Mode Selector Switch 1-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.3 Backup battery/accumulator 1-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.4 Memory card 1-6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.5 MPI and PROFIBUS-DP Interface 1-7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.1.6 Clock and Runtime Meter 1-10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Communication Options of the CPU 1-11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3 Test Functions and Diagnostics 1-19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.1 Testing Functions 1-19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.2 Diagnostics with LED Display 1-22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.3.3 Diagnostics with STEP 7 1-22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4 CPUs - Technical Specifications 1-24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.1 CPU 312 IFM 1-25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.2 CPU 313 1-37 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.3 CPU 314 1-40 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.4 CPU 314IFM 1-43 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.5 CPU 315 1-60 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.6 CPU 315-2 DP 1-63 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.7 CPU 316-2 DP 1-66 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.4.8 CPU 318-2 1-69 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2 CPU 31x-2 as DP Master/DP Slave and Direct Communication

2.1 Information on DPV1 Functionality 2-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 DP Address Areas of the CPUs 31x-2 2-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 CPU 31x-2 as DP Master 2-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.4 Diagnostics of the CPU 31x-2 as DP Master 2-6 . . . . . . . . . . . . . . . . . . . . . . . .

2.5 CPU 31x-2 as DP-Slave 2-13 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

xi

Page 14

Contents

2.6 Diagnosis of the CPU 31x-2 operating as DP-Slave 2-18 . . . . . . . . . . . . . . . . . .

2.6.1 Diagnosis with LEDs 2-19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.2 Diagnostics with STEP 5 or STEP 7 2-19 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.3 Reading Out the Diagnostic Data 2-20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.4 Format of the Slave Diagnostic Data 2-24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.5 Station Status 1 to 3 2-25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.6 Master PROFIBUS Address 2-27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.7 Manufacturer ID 2-27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.8 Module Diagnostics 2-28 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.9 Station Diagnostics 2-29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.6.10 Interrupts 2-31 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.7 Direct Data Exchange 2-32 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.8 Diagnosis with Direct Communication 2-33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3 Cycle and Reaction times

3.1 Cycle time 3-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Response Time 3-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Calculation Examples for Cycle Time and Response Time 3-10 . . . . . . . . . . . .

3.4 Interrupt response time 3-14 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Calculation Example for the Interrupt Response Time 3-16 . . . . . . . . . . . . . . . .

3.6 Reproducibility of Delay and Watchdog Interrupts 3-16 . . . . . . . . . . . . . . . . . . . .

4 CPU Function, depending on CPU and STEP 7 Version

4.1 Differences between CPU 3182 and CPUs 312 IFM to 3162 DP 4-2 . . . . . . .

4.2 The Differences Between the CPUs 312 IFM to 318 and

Their Previous Versions 4-6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 Tips and Tricks

A Standards, Certificates and Approvals

B Dimensioned Drawings

C List of Abbreviations

Glossary

Index

xii

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 15

Figures

1-1 Control and Display Elements of the CPUs 1-2 . . . . . . . . . . . . . . . . . . . . . . . . .

1-2 Status and Fault Displays of the CPUs 1-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-3 Principle of Connection Resource Allocation for CPU 318-2 1-15 . . . . . . . . . . .

1-4 The Principle of Forcing with S7-300 CPUs (CPU 312IFM to 316-2DP) 1-21 .

1-5 Display of the States of the Interrupt Inputs of the CPU 312 IFM 1-26 . . . . . . .

1-6 Front View of the CPU 312 IFM 1-27 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-7 Wiring diagram of the CPU 312 IFM 1-34 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-8 Basic Circuit Diagram of the CPU 312 IFM 1-36 . . . . . . . . . . . . . . . . . . . . . . . . . .

1-9 Display of the States of the Interrupt Inputs of the CPU 314 IFM 1-45 . . . . . . .

1-10 Front View of the CPU 314 IFM 1-46 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-11 Wiring diagram of the CPU 314 IFM 1-56 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-12 Basic Circuit Diagram of the CPU 314 IFM (Special Inputs

and Analog Inputs/Outputs) 1-57 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-13 Basic Circuit Diagram of the CPU 314 IFM (Digital Inputs/Outputs) 1-58 . . . . .

1-14 Connecting 2-wire measurement transducers to the analog inputs

of CPU 314 IFM 1-59 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-15 Wiring of 4-wire measurement transducers to the analog inputs

of CPU 314 IFM 1-59 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1 Diagnostics with CPU 315-2DP < 315-2AF03 2-8 . . . . . . . . . . . . . . . . . . . . . . .

2-2 Diagnostics with CPU 31x-2 (315-2DP as of 315-2AF03) 2-9 . . . . . . . . . . . . .

2-3 Diagnostic Addresses for DP Master and DP Slave 2-10 . . . . . . . . . . . . . . . . . .

2-4 Transfer Memory in a CPU 31x-2 operating as DP Slave 2-14 . . . . . . . . . . . . .

2-5 Diagnostic Addresses for DP Master and DP Slave 2-22 . . . . . . . . . . . . . . . . . .

2-6 Format of the Slave Diagnostic Data 2-24 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-7 Structure of the Module Diagnosis of the CPU 31x-2 2-28 . . . . . . . . . . . . . . . . .

2-8 Structure of the Station Diagnosis 2-29 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-9 Byte x +4 to x +7 for Diagnostic and Hardware interrupt 2-30 . . . . . . . . . . . . . .

2-10 Direct Communication using CPU 31x-2 2-32 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-11 Diagnostic address for receiver with direct communication 2-33 . . . . . . . . . . . .

3-1 Component Parts of the Cycle Time 3-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-2 Shortest Response Time 3-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3 Longest Response Time 3-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-4 Overview of the Bus Runtime on PROFIBUS-DP at 1.5 Mbps

and 12Mbps 3-9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4-1 Sample Configuration 4-4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B-1 Dimensioned Drawing of the CPU 312 IFM B-1 . . . . . . . . . . . . . . . . . . . . . . . . .

B-2 Dimensioned Drawing of the CPU 313/314/315/315-2 DP/316-2DP B-2 . . . .

B-3 Dimensioned Drawing of the CPU 318-2 B-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

B-4 Dimensioned Drawing of the CPU 314 IFM, Front View B-4 . . . . . . . . . . . . . . .

B-5 Dimensioned Drawing of the CPU 314 IFM, Side View B-5 . . . . . . . . . . . . . . .

Contents

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

xiii

Page 16

Contents

Tables

1-1 The Differences in Control and Display Elements Between CPUs 1-2 . . . . . .

1-2 Using a Backup Battery or Accumulator 1-5 . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-3 Memory Cards 1-6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-4 CPU Interfaces 1-7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-5 Characteristics of the Clock of the CPUs 1-10 . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-6 CPU Communication Options 1-12 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-7 Connection Resources for CPUs 312 IFM to 316-2 DP 1-14 . . . . . . . . . . . . . . .

1-8 Communication Resources for CPU 318-2 1-15 . . . . . . . . . . . . . . . . . . . . . . . . .

1-9 Diagnostic LEDs of the CPU 1-22 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-10 Start Information for OB 40 for the Interrupt Inputs

of the Integrated I/Os 1-26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-11 Start Information for OB 40 for the Interrupt Inputs

of the Integrated I/Os 1-44 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1-12 Characteristic Features of the Integrated Inputs and Outputs

of the CPU 314 IFM 1-50 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-1 Meaning of the BUSF LED of the CPU 31x-2 as DP Master 2-6 . . . . . . . . . . .

2-2 Reading Diagnostic Data with STEP 7 2-7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-3 Event Detection of the CPU 31x-2 as DP Master 2-11 . . . . . . . . . . . . . . . . . . . .

2-4 Evaluating RUN-STOP Transitions of the DP Slaves in the DP Master 2-12 . .

2-5 Example of an address area configuration for transfer memory 2-15 . . . . . . . .

2-6 Meaning of the BUSF LEDs in the CPU 31x-2 as DP Slave 2-19 . . . . . . . . . . .

2-7 Fetching diagnostic data with STEP 5 and STEP 7

in the master system 2-20 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-8 Event Detection of the CPU 31x-2 as DP Slave 2-23 . . . . . . . . . . . . . . . . . . . . .

2-9 Evaluating RUN-STOP Transitions in the DP Master/DP Slave 2-23 . . . . . . . .

2-10 Structure of Station Status 1 (Byte 0) 2-25 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-11 Structure of Station Status 2 (Byte 1) 2-26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-12 Structure of Station Status 3 (Byte 2) 2-26 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-13 Structure of the Master PROFIBUS Address (Byte 3) 2-27 . . . . . . . . . . . . . . . .

2-14 Structure of the Manufacturer Identification (Bytes 4 and 5) 2-27 . . . . . . . . . . .

2-15 Event Detection by CPU 31x-2 Acting as Receiver in

Direct Communication 2-33 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2-16 Evaluation of the Station Failure of the Sender During

Direct Communication 2-34 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-1 Operating System Processing Times of the CPUs 3-6 . . . . . . . . . . . . . . . . . . .

3-2 Process image update of the CPUs 3-7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-3 CPU-specific Factors for the User Program Processing Time 3-7 . . . . . . . . . .

3-4 Updating the S7 Timers 3-7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-5 Update Time and SFB Runtimes 3-8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3-6 Extending the Cycle by Nesting Interrupts 3-10 . . . . . . . . . . . . . . . . . . . . . . . . .

3-7 Response time of the CPUs to process interrupts 3-14 . . . . . . . . . . . . . . . . . . .

3-8 Diagnostic Interrupt Response Times of the CPUs 3-15 . . . . . . . . . . . . . . . . . .

3-9 Reproducibility of the Delay and Watchdog Interrupts of the CPUs 3-17 . . . . .

xiv

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 17

CPUs

In This Section

Section Contents Page

1.1 Control and Display Elements 1-2

1.2 CPU Communication Options 1-11

1.3 Test Functions and Diagnostics 1-19

1.4 CPUs - Technical Specifications 1-24

Agreement for CPU 314IFM

The CPU 314IFM is available in 2 versions:

with slot for memory card (6ES7314-5EA10-0AB0)

without slot for memory card (6ES7314-5EA0x-0AB0/

6314ES7314-5EA8x-0AB0)

All details in this chapter apply to both versions of the CPU314IFM unless explicit

reference is made to differences between them.

1

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-1

Page 18

CPUs

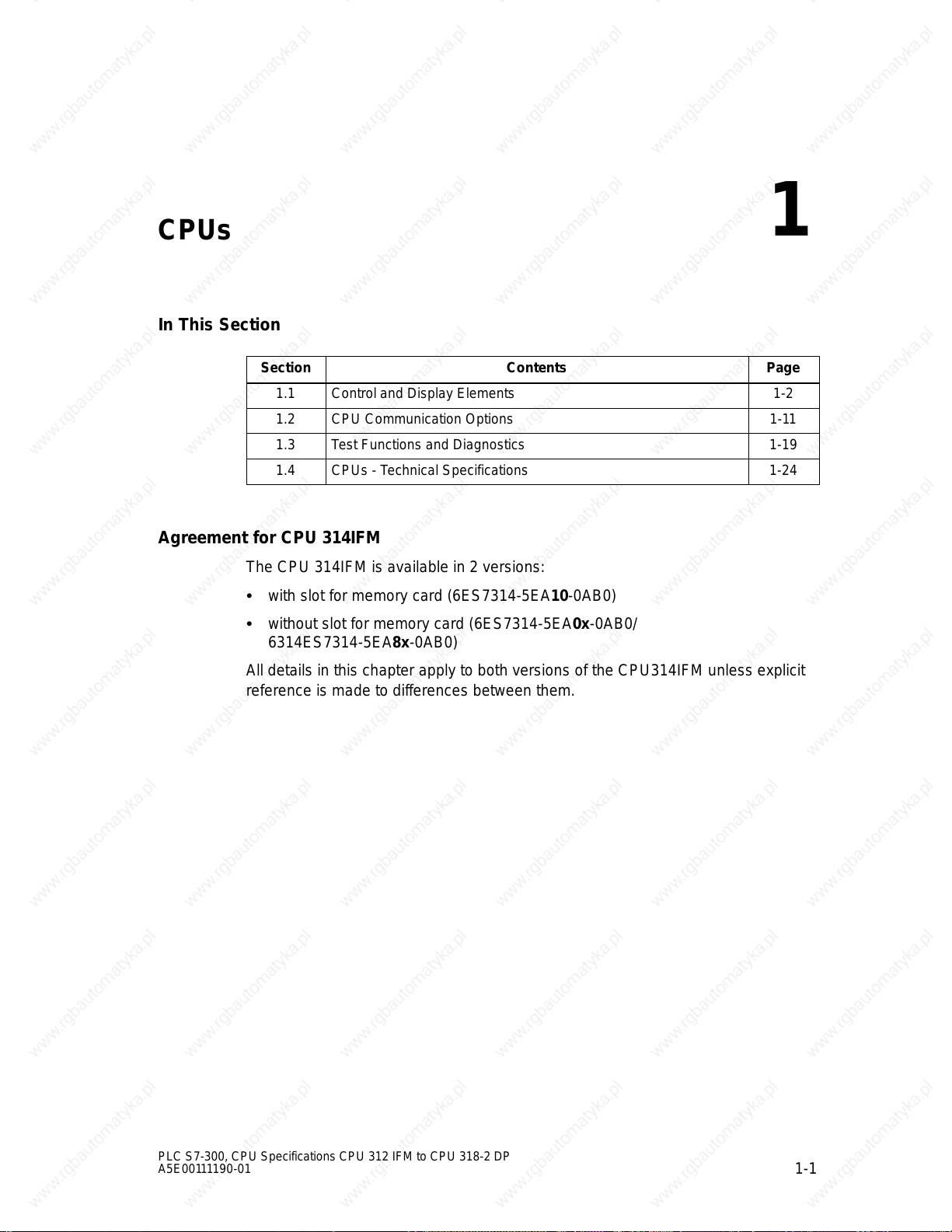

1.1 Control and Display Elements

Figure 1-1 shows you the control and display elements of a CPU.

The order of the elements in some CPUs might differ from the order shown in the

figure below. The individual CPUs do not always have all the elements shown here.

Table 1-1 shows you the differences.

Status and

fault LEDs

Status and

fault displays for

DP interface

Mode selector

Slot for memory

card

Compartment for backup

battery or rechargeable

battery

Connection for power supply

and system ground

Figure 1-1 Control and Display Elements of the CPUs

M

L

+M

Multipoint Interface

(MPI)

PROFIBUS-DP

interface

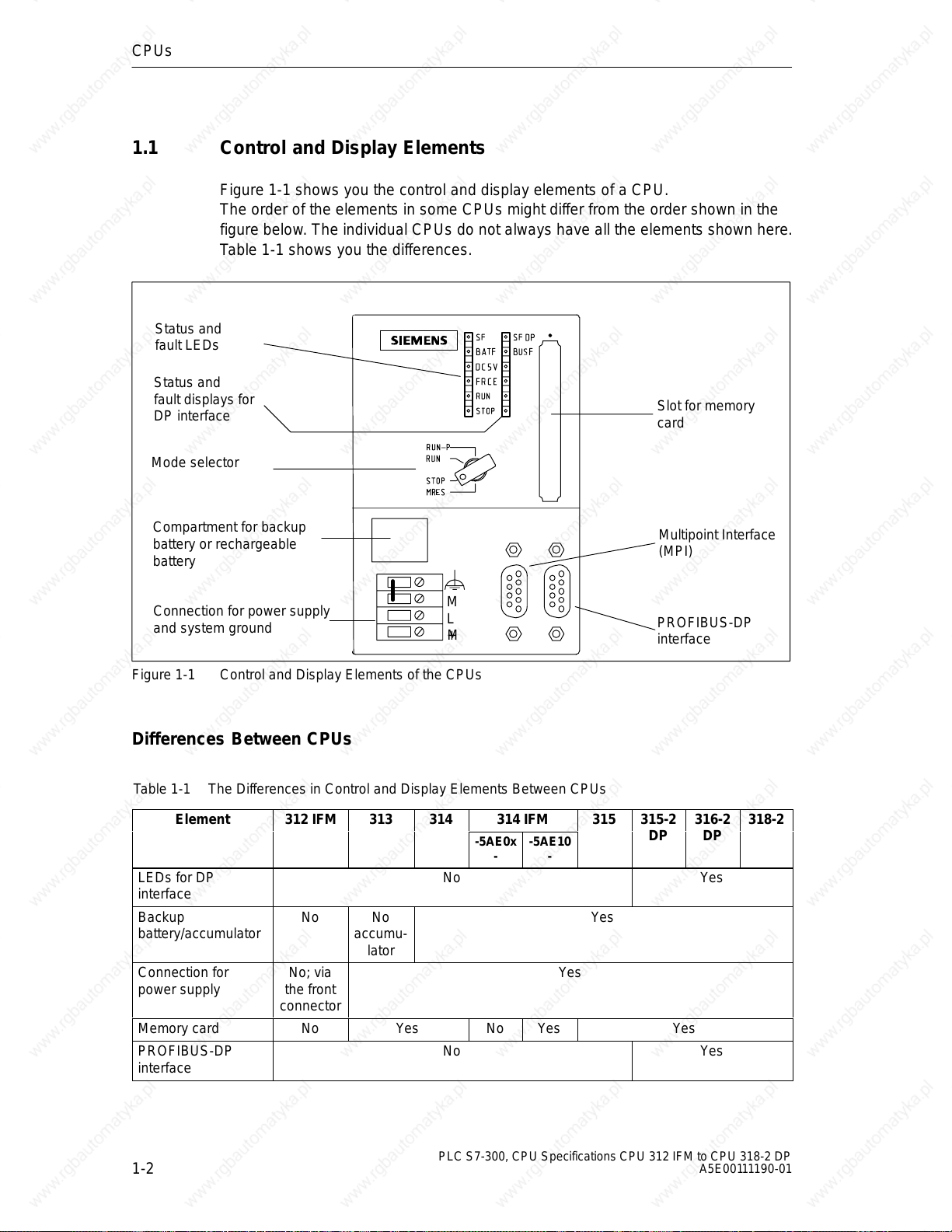

Differences Between CPUs

Table 1-1 The Differences in Control and Display Elements Between CPUs

Element 312 IFM 313 314

LEDs for DP

interface

Backup

battery/accumulator

Connection for

power supply

Memory card No Yes No Yes Yes

PROFIBUS-DP

interface

No No

accumu-

lator

No; via

the front

connector

No Yes

No Yes

314 IFM

-5AE0x--5AE10

315 315-2 316-2 318-2

DP DP

-

Yes

Yes

1-2

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 19

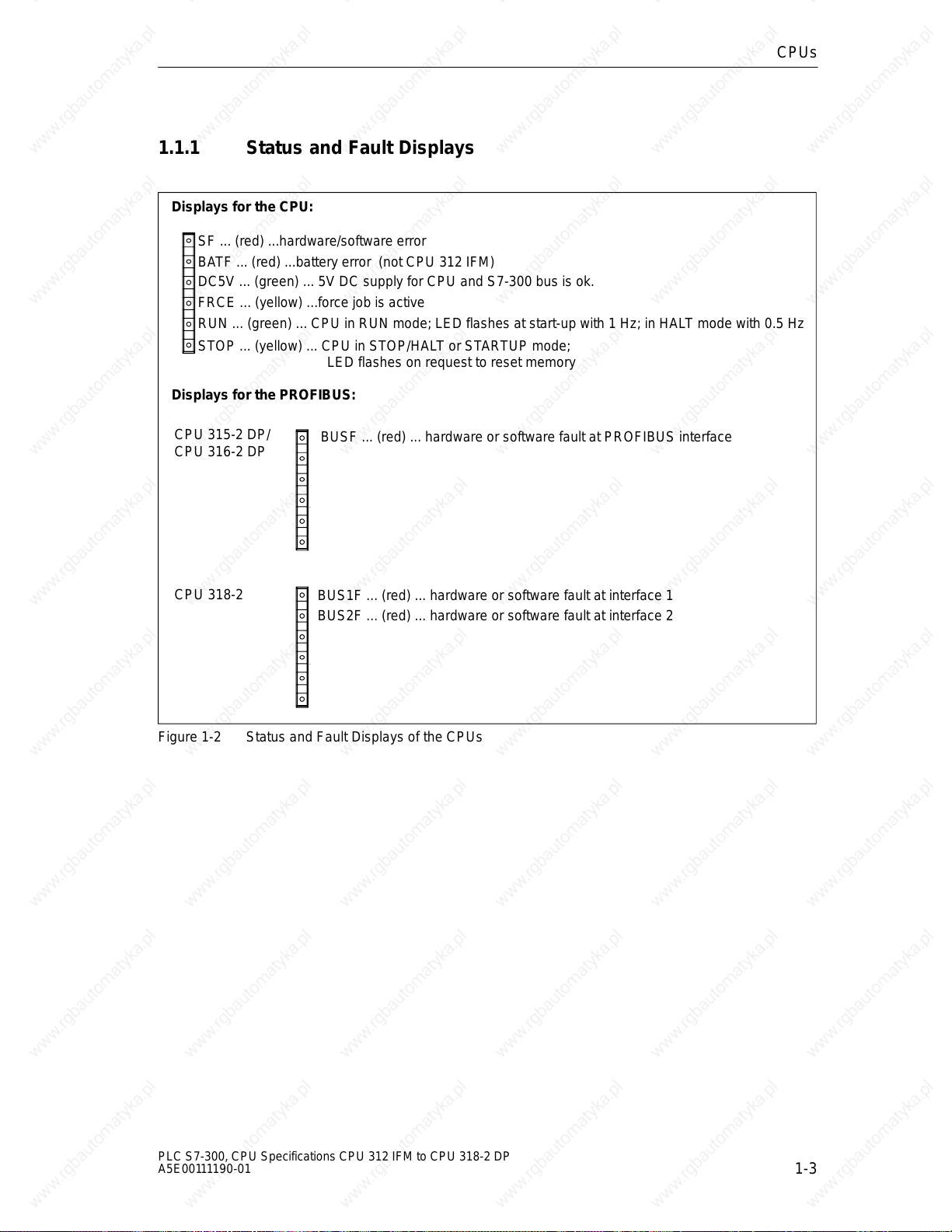

1.1.1 Status and Fault Displays

Displays for the CPU:

SF ... (red) ...hardware/software error

BATF ... (red) ...battery error (not CPU 312 IFM)

DC5V ... (green) ... 5V DC supply for CPU and S7-300 bus is ok.

FRCE ... (yellow) ...force job is active

RUN ... (green) ... CPU in RUN mode; LED flashes at start-up with 1 Hz; in HALT mode with 0.5 Hz

STOP ... (yellow) ... CPU in STOP/HALT or STARTUP mode;

LED flashes on request to reset memory

Displays for the PROFIBUS:

CPUs

CPU 315-2 DP/

CPU 316-2 DP

CPU 318-2

Figure 1-2 Status and Fault Displays of the CPUs

BUSF ... (red) ... hardware or software fault at PROFIBUS interface

BUS1F ... (red) ... hardware or software fault at interface 1

BUS2F ... (red) ... hardware or software fault at interface 2

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-3

Page 20

CPUs

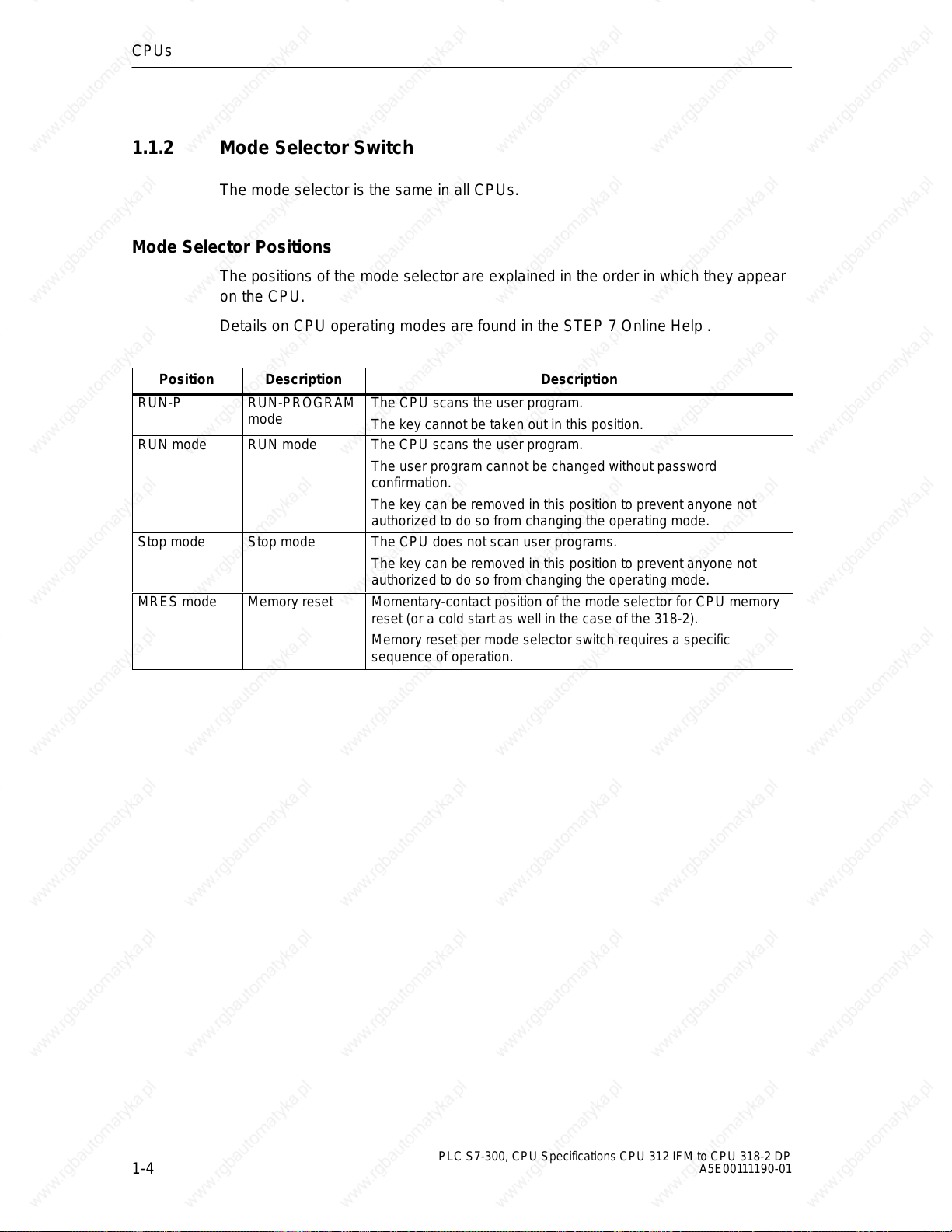

1.1.2 Mode Selector Switch

The mode selector is the same in all CPUs.

Mode Selector Positions

The positions of the mode selector are explained in the order in which they appear

on the CPU.

Details on CPU operating modes are found in the STEP 7 Online Help .

Position Description Description

RUN-P RUN-PROGRAM

mode

RUN mode RUN mode The CPU scans the user program.

Stop mode Stop mode The CPU does not scan user programs.

MRES mode Memory reset Momentary-contact position of the mode selector for CPU memory

The CPU scans the user program.

The key cannot be taken out in this position.

The user program cannot be changed without password

confirmation.

The key can be removed in this position to prevent anyone not

authorized to do so from changing the operating mode.

The key can be removed in this position to prevent anyone not

authorized to do so from changing the operating mode.

reset (or a cold start as well in the case of the 318-2).

Memory reset per mode selector switch requires a specific

sequence of operation.

1-4

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 21

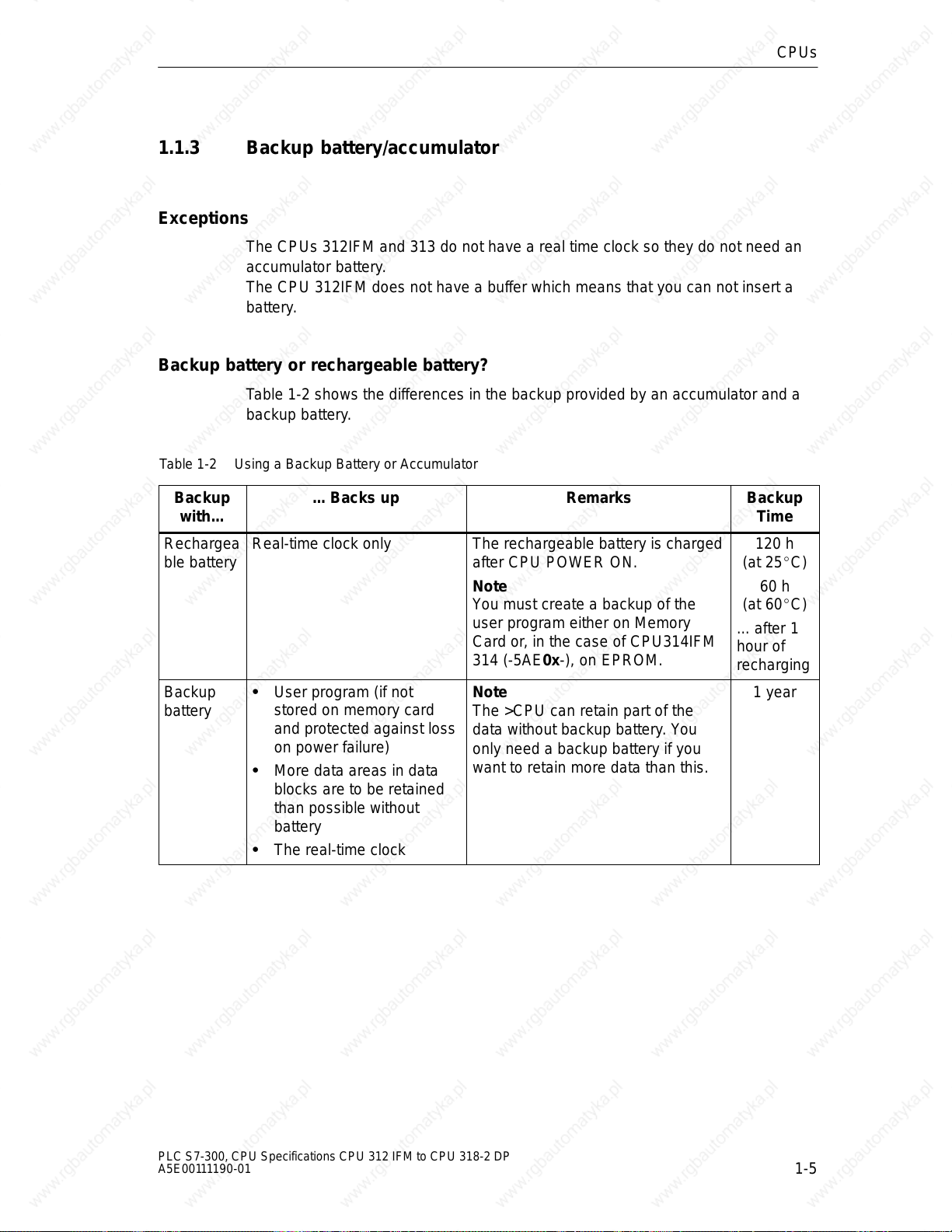

1.1.3 Backup battery/accumulator

Exceptions

The CPUs 312IFM and 313 do not have a real time clock so they do not need an

accumulator battery.

The CPU 312IFM does not have a buffer which means that you can not insert a

battery.

Backup battery or rechargeable battery?

Table 1-2 shows the differences in the backup provided by an accumulator and a

backup battery.

Table 1-2 Using a Backup Battery or Accumulator

CPUs

Backup

with...

Rechargea

ble battery

Backup

battery

... Backs up Remarks Backup

Real-time clock only The rechargeable battery is charged

after CPU POWER ON.

Note

You must create a backup of the

user program either on Memory

Card or, in the case of CPU314IFM

314 (-5AE0x-), on EPROM.

User program (if not

stored on memory card

and protected against loss

on power failure)

More data areas in data

blocks are to be retained

than possible without

battery

Note

The >CPU can retain part of the

data without backup battery. You

only need a backup battery if you

want to retain more data than this.

The real-time clock

Time

120 h

(at 25C)

60 h

(at 60C)

... after 1

hour of

recharging

1 year

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-5

Page 22

CPUs

then uploaded from the memory card to

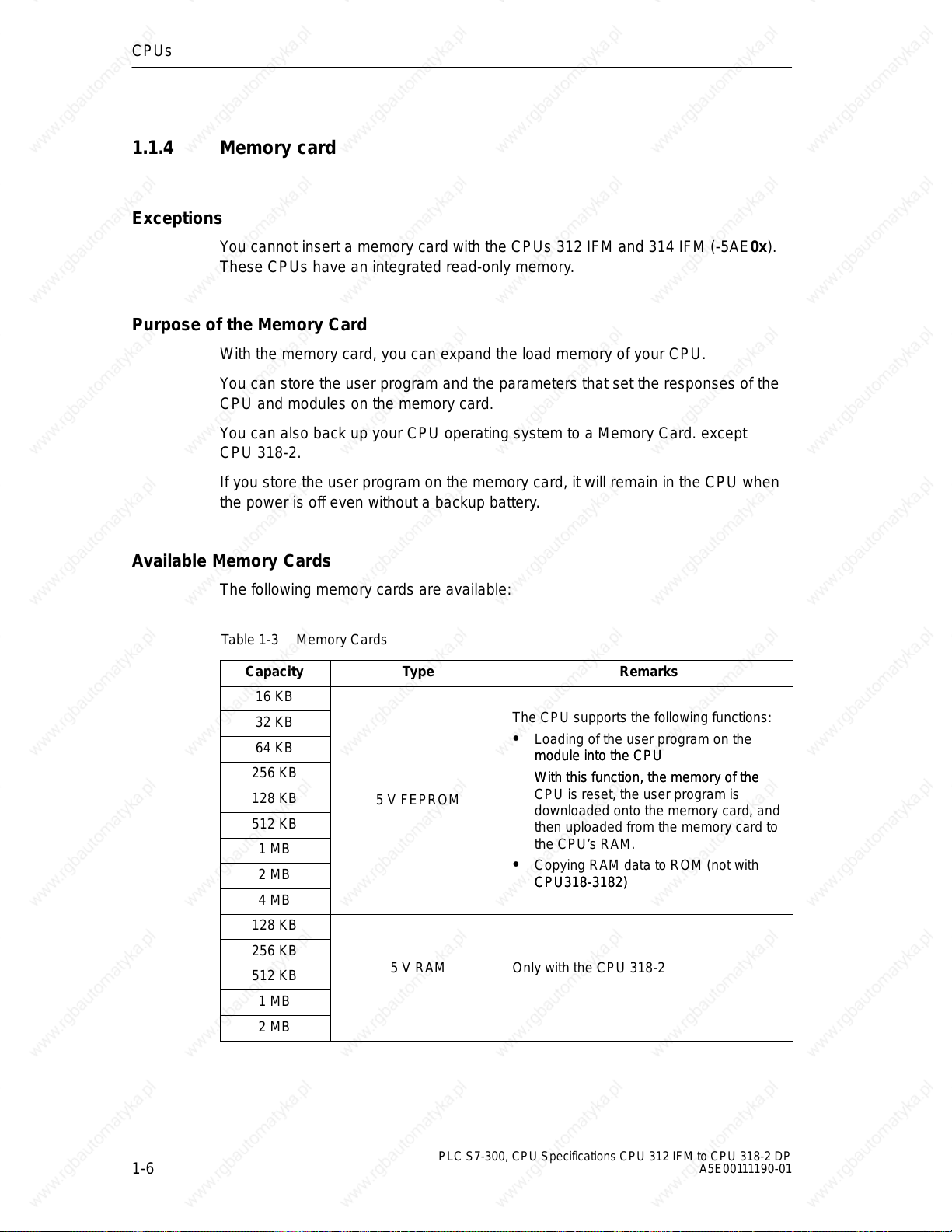

1.1.4 Memory card

Exceptions

You cannot insert a memory card with the CPUs 312 IFM and 314 IFM (-5AE0x).

These CPUs have an integrated read-only memory.

Purpose of the Memory Card

With the memory card, you can expand the load memory of your CPU.

You can store the user program and the parameters that set the responses of the

CPU and modules on the memory card.

You can also back up your CPU operating system to a Memory Card. except

CPU 318-2.

If you store the user program on the memory card, it will remain in the CPU when

the power is off even without a backup battery.

Available Memory Cards

The following memory cards are available:

Table 1-3 Memory Cards

Capacity

16 KB

32 KB

64 KB

256 KB

128 KB

512 KB

1 MB

2 MB

4 MB

128 KB

256 KB

512 KB

1 MB

2 MB

Type Remarks

The CPU supports the following functions:

Loading of the user program on the

module into the CPU

module into the CPU

With this function, the memory of the

With this function, the memory of the

5 V FEPROM

CPU is reset, the user program is

downloaded onto the memory card, and

then uploaded from the memory card to

the CPU’s RAM.

Copying RAM data to ROM (not with

CPU318-3182)

CPU318-3182)

5 V RAM Only with the CPU 318-2

1-6

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 23

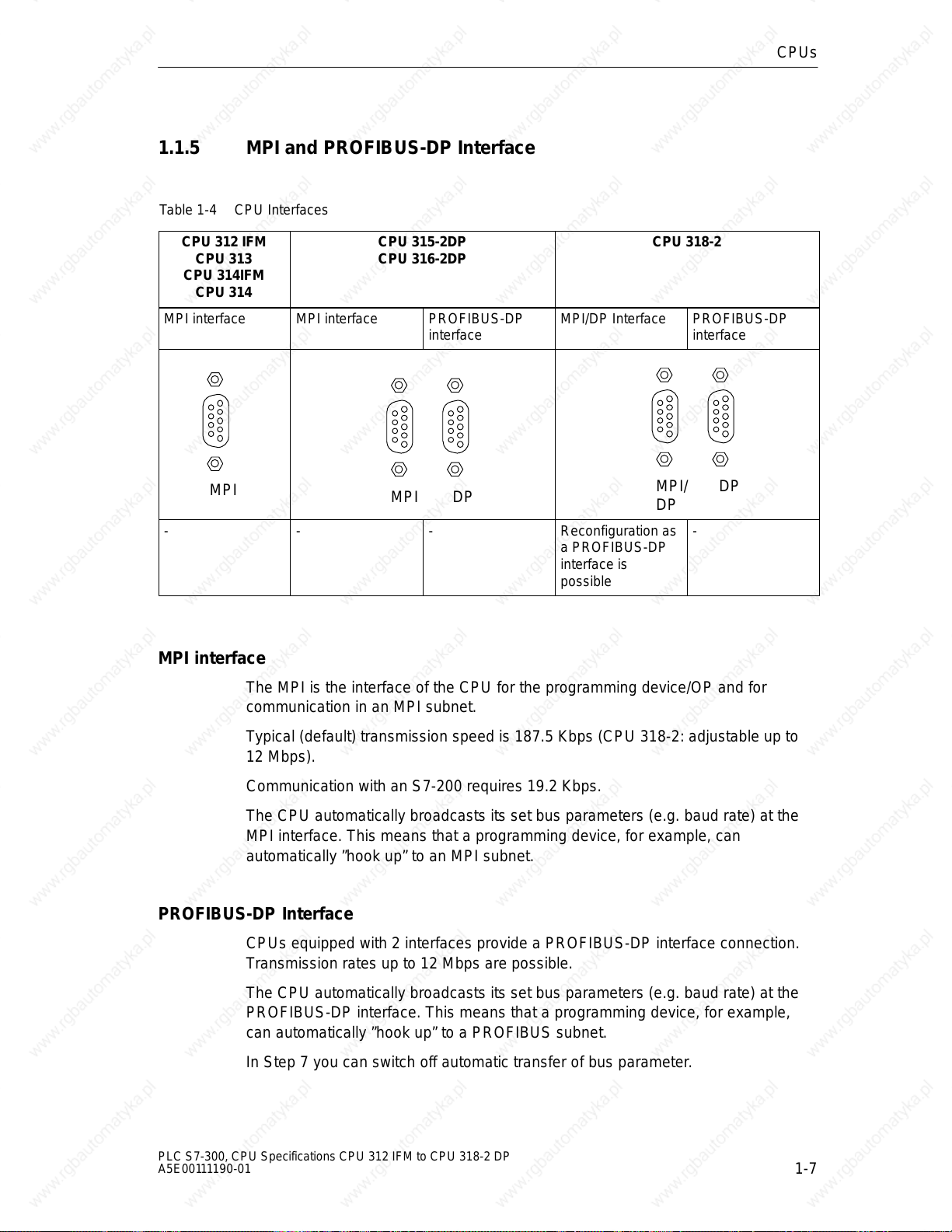

1.1.5 MPI and PROFIBUS-DP Interface

Table 1-4 CPU Interfaces

CPUs

CPU 312 IFM

CPU 313

CPU 314IFM

CPU 314

MPI interface MPI interface PROFIBUS-DP

MPI

- - - Reconfiguration as

CPU 315-2DP

CPU 316-2DP

MPI/DP Interface PROFIBUS-DP

interface

MPI DP

a PROFIBUS-DP

interface is

possible

CPU 318-2

MPI interface

The MPI is the interface of the CPU for the programming device/OP and for

communication in an MPI subnet.

MPI/

DP

interface

DP

-

Typical (default) transmission speed is 187.5 Kbps (CPU 318-2: adjustable up to

12 Mbps).

Communication with an S7-200 requires 19.2 Kbps.

The CPU automatically broadcasts its set bus parameters (e.g. baud rate) at the

MPI interface. This means that a programming device, for example, can

automatically ”hook up” to an MPI subnet.

PROFIBUS-DP Interface

CPUs equipped with 2 interfaces provide a PROFIBUS-DP interface connection.

Transmission rates up to 12 Mbps are possible.

The CPU automatically broadcasts its set bus parameters (e.g. baud rate) at the

PROFIBUS-DP interface. This means that a programming device, for example,

can automatically ”hook up” to a PROFIBUS subnet.

In Step 7 you can switch off automatic transfer of bus parameter.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-7

Page 24

CPUs

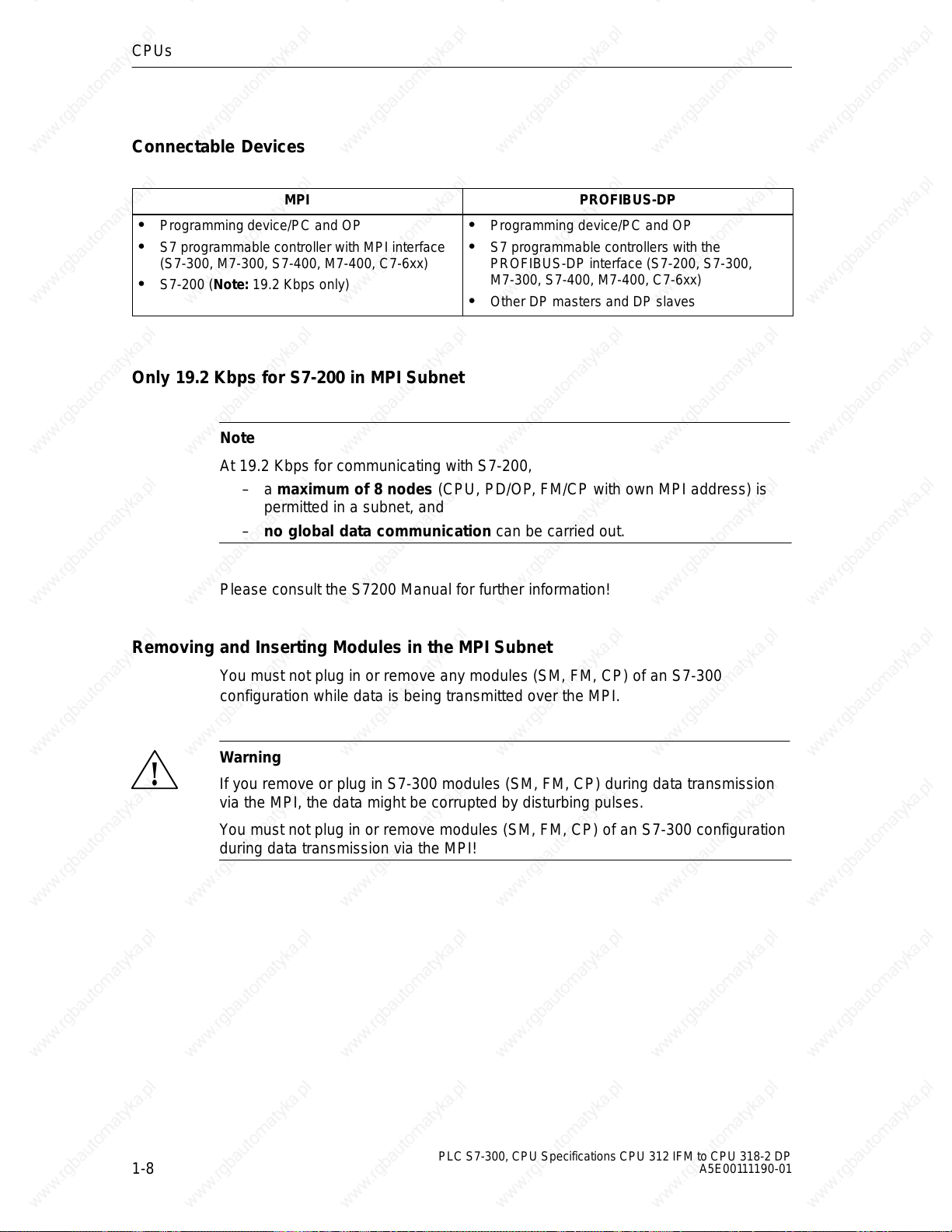

Connectable Devices

MPI PROFIBUS-DP

Programming device/PC and OP

S7 programmable controller with MPI interface

(S7-300, M7-300, S7-400, M7-400, C7-6xx)

S7-200 (Note: 19.2 Kbps only)

Only 19.2 Kbps for S7-200 in MPI Subnet

Note

At 19.2 Kbps for communicating with S7-200,

– a maximum of 8 nodes (CPU, PD/OP, FM/CP with own MPI address) is

permitted in a subnet, and

– no global data communication can be carried out.

Programming device/PC and OP

S7 programmable controllers with the

PROFIBUS-DP interface (S7-200, S7-300,

M7-300, S7-400, M7-400, C7-6xx)

Other DP masters and DP slaves

Please consult the S7200 Manual for further information!

Removing and Inserting Modules in the MPI Subnet

You must not plug in or remove any modules (SM, FM, CP) of an S7-300

configuration while data is being transmitted over the MPI.

Warning

!

If you remove or plug in S7-300 modules (SM, FM, CP) during data transmission

via the MPI, the data might be corrupted by disturbing pulses.

You must not plug in or remove modules (SM, FM, CP) of an S7-300 configuration

during data transmission via the MPI!

1-8

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 25

Loss of GD packets Following Change in the MPI Subnet During Operation

Warning

!

Loss of data packets in the MPI subnet:

Connecting an additional CPU to the MPI subnet during operation can lead to loss

of GD packets and to an increase in cycle time.

Remedy:

1. Disconnect the node to be connected from the supply.

2. Connect the node to the MPI subnet.

3. Switch the node on.

CPUs

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-9

Page 26

CPUs

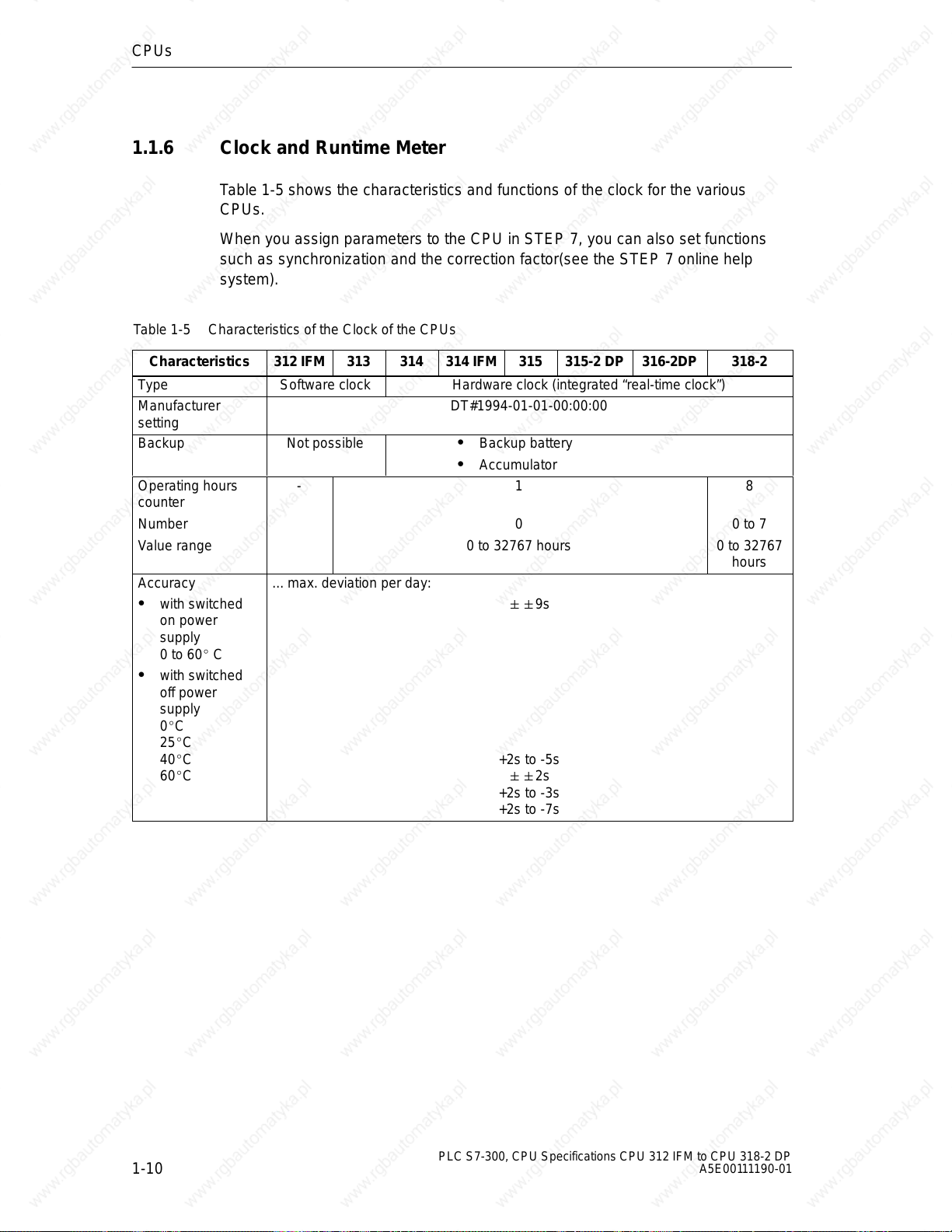

1.1.6 Clock and Runtime Meter

Table 1-5 shows the characteristics and functions of the clock for the various

CPUs.

When you assign parameters to the CPU in STEP 7, you can also set functions

such as synchronization and the correction factor(see the STEP 7 online help

system).

Table 1-5 Characteristics of the Clock of the CPUs

Characteristics

Type Software clock Hardware clock (integrated “real-time clock”)

Manufacturer

setting

Backup Not possible Backup battery

312 IFM 313 314 314 IFM 315 315-2 DP 316-2DP 318-2

DT#1994-01-01-00:00:00

Accumulator

Operating hours

counter

Number

Value range

Accuracy

with switched

on power

supply

0 to 60 C

with switched

off power

supply

0C

25C

40C

60C

- 1

0

0 to 32767 hours

... max. deviation per day:

9s

+2s to -5s

2s

+2s to -3s

+2s to -7s

8

0 to 7

0 to 32767

hours

1-10

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 27

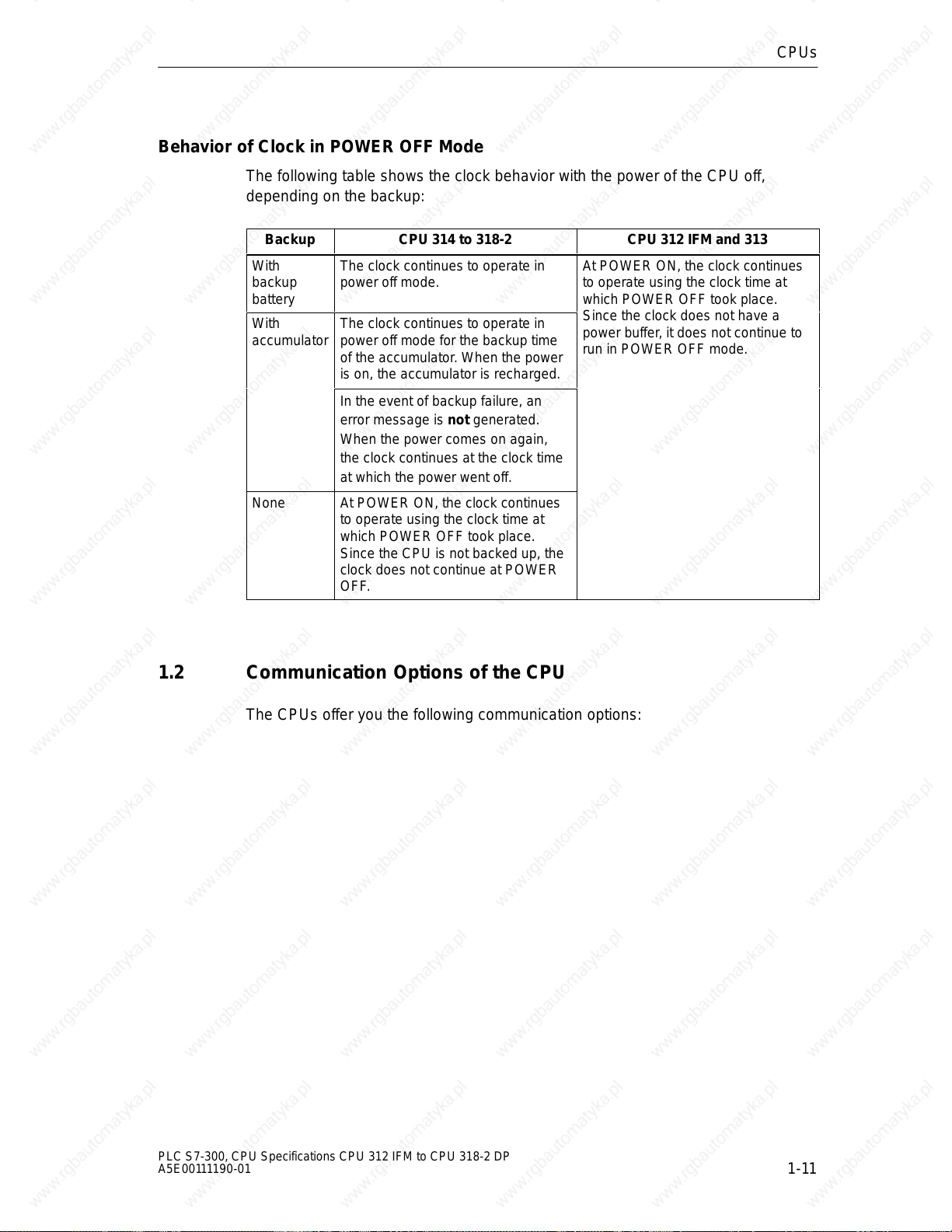

Behavior of Clock in POWER OFF Mode

The following table shows the clock behavior with the power of the CPU off,

depending on the backup:

Backup CPU 314 to 318-2 CPU 312 IFM and 313

With

backup

battery

With

accumulator

None At POWER ON, the clock continues

The clock continues to operate in

power off mode.

The clock continues to operate in

power off mode for the backup time

of the accumulator. When the power

is on, the accumulator is recharged.

In the event of backup failure, an

error message is not generated.

When the power comes on again,

the clock continues at the clock time

at which the power went off.

to operate using the clock time at

which POWER OFF took place.

Since the CPU is not backed up, the

clock does not continue at POWER

OFF.

CPUs

At POWER ON, the clock continues

to operate using the clock time at

which POWER OFF took place.

Since the clock does not have a

power buffer, it does not continue to

run in POWER OFF mode.

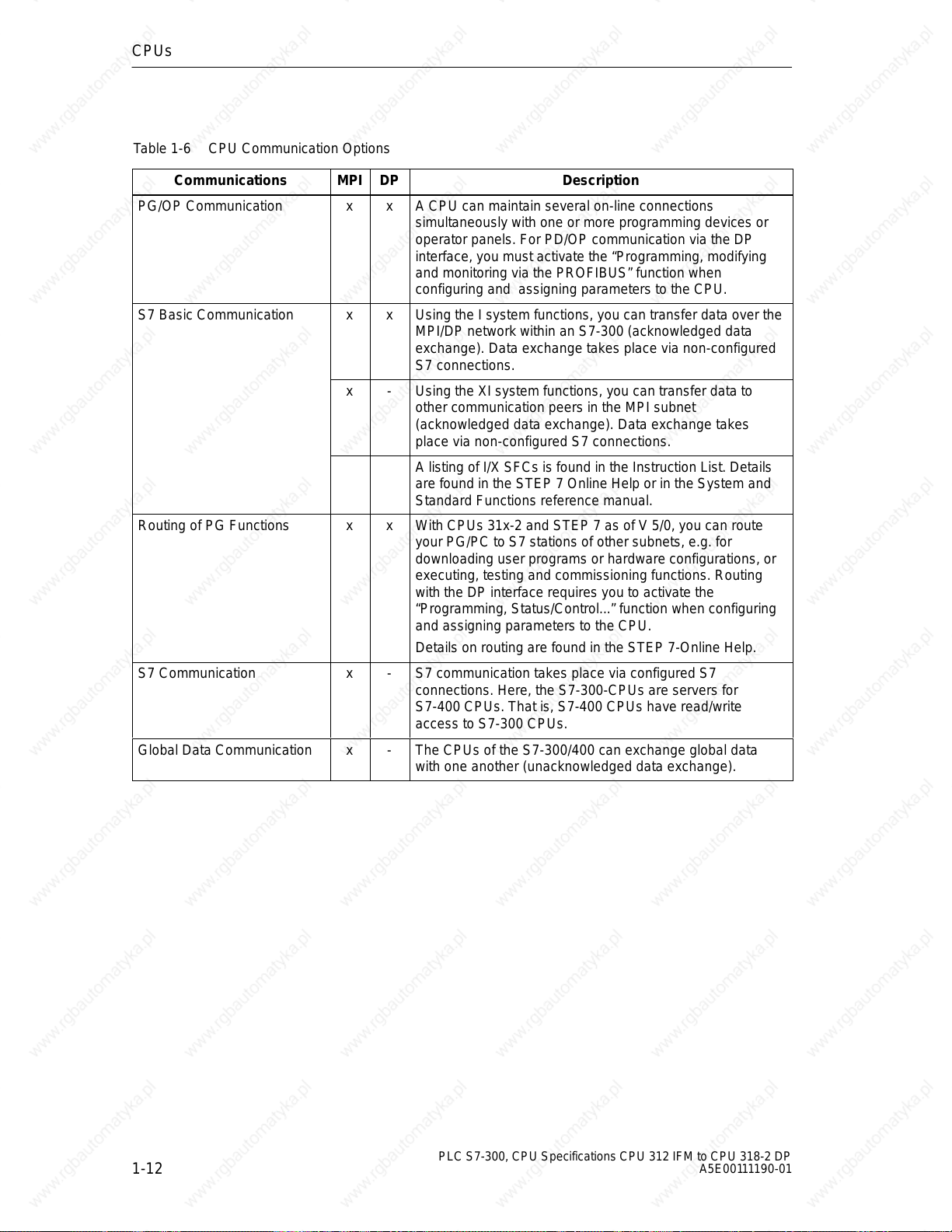

1.2 Communication Options of the CPU

The CPUs offer you the following communication options:

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-11

Page 28

CPUs

Table 1-6 CPU Communication Options

Communications

PG/OP Communication x x A CPU can maintain several on-line connections

S7 Basic Communication x x Using the I system functions, you can transfer data over the

Routing of PG Functions x x With CPUs 31x-2 and STEP 7 as of V 5/0, you can route

S7 Communication x - S7 communication takes place via configured S7

Global Data Communication x - The CPUs of the S7-300/400 can exchange global data

MPI DP Description

simultaneously with one or more programming devices or

operator panels. For PD/OP communication via the DP

interface, you must activate the “Programming, modifying

and monitoring via the PROFIBUS” function when

configuring and assigning parameters to the CPU.

MPI/DP network within an S7-300 (acknowledged data

exchange). Data exchange takes place via non-configured

S7 connections.

x - Using the XI system functions, you can transfer data to

other communication peers in the MPI subnet

(acknowledged data exchange). Data exchange takes

place via non-configured S7 connections.

A listing of I/X SFCs is found in the Instruction List. Details

are found in the STEP 7 Online Help or in the System and

Standard Functions reference manual.

your PG/PC to S7 stations of other subnets, e.g. for

downloading user programs or hardware configurations, or

executing, testing and commissioning functions. Routing

with the DP interface requires you to activate the

“Programming, Status/Control...” function when configuring

and assigning parameters to the CPU.

Details on routing are found in the STEP 7-Online Help.

connections. Here, the S7-300-CPUs are servers for

S7-400 CPUs. That is, S7-400 CPUs have read/write

access to S7-300 CPUs.

with one another (unacknowledged data exchange).

1-12

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 29

Connection Resources

Every communication connection requires a communication resource on the

S7 CPU as a management unit for the duration of the communication. Every

S7 CPU has a certain number of connection resources available to it according to

its technical specifications which can be assigned to various communication

services (PD/OP communication, S7 communication or S7 basic communication).

The distribution of connection resources differs between CPUs 312 IFM to 316-2

DP (see the table 3-6) and the CPU 318-2 (see Table 1-8):

CPUs

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-13

Page 30

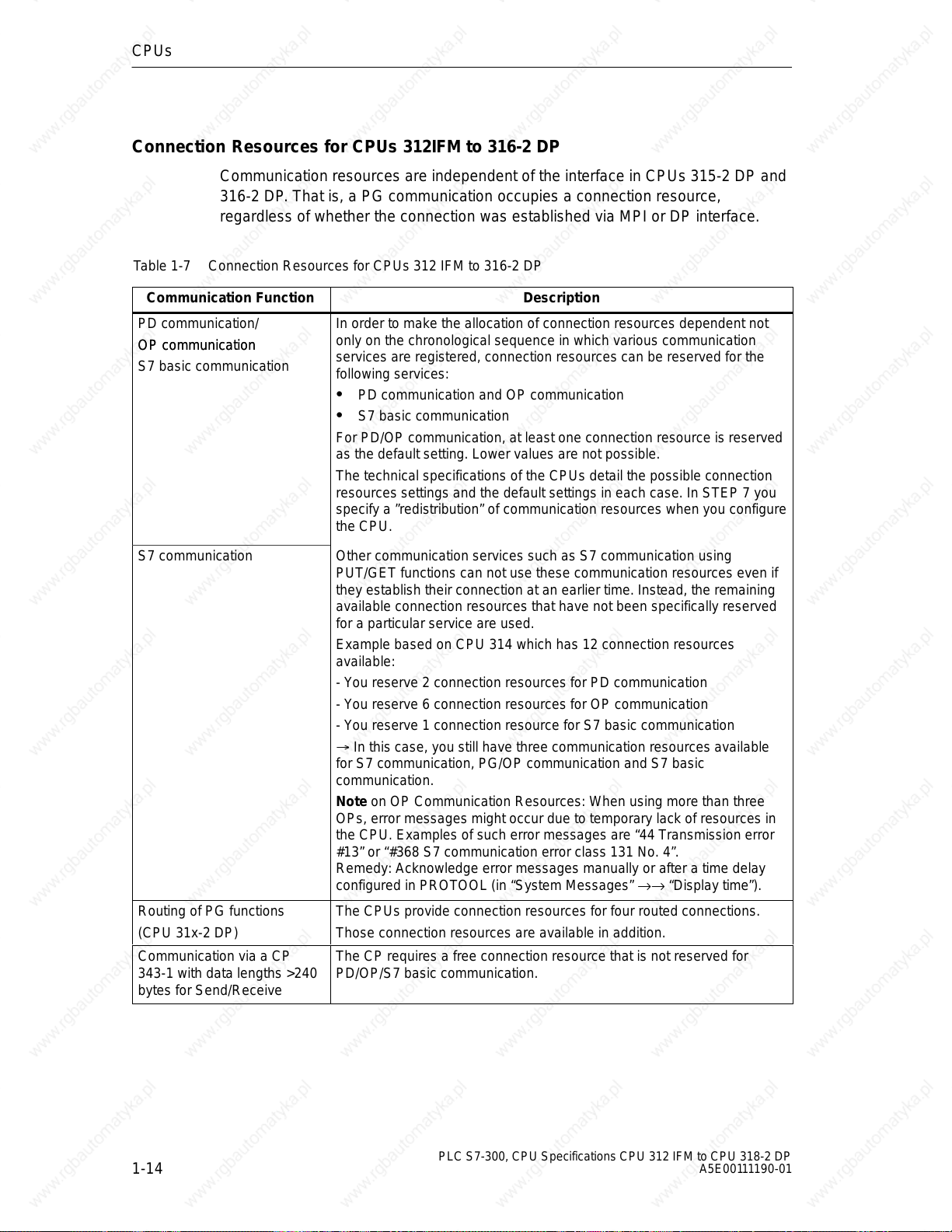

CPUs

Connection Resources for CPUs 312IFM to 316-2 DP

Communication resources are independent of the interface in CPUs 315-2 DP and

316-2 DP. That is, a PG communication occupies a connection resource,

regardless of whether the connection was established via MPI or DP interface.

Table 1-7 Connection Resources for CPUs 312 IFM to 316-2 DP

Communication Function

PD communication/

OP communication

OP communication

S7 basic communication

In order to make the allocation of connection resources dependent not

only on the chronological sequence in which various communication

services are registered, connection resources can be reserved for the

following services:

Description

PD communication and OP communication

S7 basic communication

For PD/OP communication, at least one connection resource is reserved

as the default setting. Lower values are not possible.

The technical specifications of the CPUs detail the possible connection

resources settings and the default settings in each case. In STEP 7 you

specify a ”redistribution” of communication resources when you configure

the CPU.

S7 communication Other communication services such as S7 communication using

PUT/GET functions can not use these communication resources even if

they establish their connection at an earlier time. Instead, the remaining

available connection resources that have not been specifically reserved

for a particular service are used.

Example based on CPU 314 which has 12 connection resources

available:

- You reserve 2 connection resources for PD communication

- You reserve 6 connection resources for OP communication

- You reserve 1 connection resource for S7 basic communication

In this case, you still have three communication resources available

for S7 communication, PG/OP communication and S7 basic

communication.

Note on OP Communication Resources: When using more than three

OPs, error messages might occur due to temporary lack of resources in

the CPU. Examples of such error messages are “44 Transmission error

#13” or “#368 S7 communication error class 131 No. 4”.

Remedy: Acknowledge error messages manually or after a time delay

configured in PROTOOL (in “System Messages” →→ “Display time”).

Routing of PG functions The CPUs provide connection resources for four routed connections.

(CPU 31x-2 DP) Those connection resources are available in addition.

Communication via a CP

343-1 with data lengths >240

bytes for Send/Receive

The CP requires a free connection resource that is not reserved for

PD/OP/S7 basic communication.

1-14

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 31

Connection Resources for CPU 318-2

Table 1-8 Communication Resources for CPU 318-2

CPUs

Communication Function

PD/OP communication The CPU 318-2 provides a total of 32 connection resources (with CPU

as connection terminal point) for these communication functions. Those

32 connection resources can be freely allocated to the various

communication functions.

S7 basic communication

When allocating connection resources, you should observe the following

points:

Description

The number of connection resources differs for each interface as

follows:

– MPI/DP Interface 32 communication resources

Routing of PD functions

– DP-SS: 16 communication resources

In the case of connections that do not have the CPU as their terminal

point (e.g. an FM or in the case of routing) you must deduct 2

connection resources from the total resources and 1 connection

S7 communication

resource per interface.

Figure 1-3 shows the principle of allocation of connection resources.

An example of how connection resources are dimensioned is found in

Chapter LEERER MERKER.

Principle of Connection Resource Allocation for CPU 318-2

CPU 318-2

32 connection resources for

connections via the MPI/DP

interface

Figure 1-3 Principle of Connection Resource Allocation for CPU 318-2

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

A total of 32 connection

resources for connections via

the MPI/DP and/or DP

interface

MPI/DP

DP

16 connection resources for

connections via the DP

interface

1-15

Page 32

CPUs

Interface Resources for CPU 318-2 - Example Calculation

1. Two network transitions by routing on the CPU

Resources used:

- 2 connection resources of the MPI/DP interface are used;

- 2 connection resources of the DP interface are used;

- all 4 connection resources available to both interfaces

are used;

2. 4 connections for S7 basic communication and PG/OP communication with the

CPU as connection terminal point via MPI/DP interface

Resources used:

- 4 connection resources of the MPI/DP interface are used;

- all 4 connection resources available to both interfaces

are used;

Resources still availabe:

- 26 connection resources of the MPI/DP interface;

- 14 connection resources of the DP interface;

- 24 of the connection resources available to both interfaces

Data Consistency for Communication

An essential aspect of the transmission of data between devices is its consistency.

The data that is transmitted together should all originate from the same processing

cycle and should thus belong together, i.e. be consistent.

If there is a programmed communication function such as X-SEND/ X-RCV which

accesses shared data, then access to that data area can be co-ordinated by

means of the parameter “BUSY” itself.

However, with S7 communication functions not requiring a block in the user

program of the 31x CPU (as server), e.g. PUT/GET or read/write operations via

OP communication, the dimension of data consistency must be taken into account

during programming. The following differences between CPUs 312IFM to 316-2 DP

and CPU 318-2 must be taken into account:

1-16

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 33

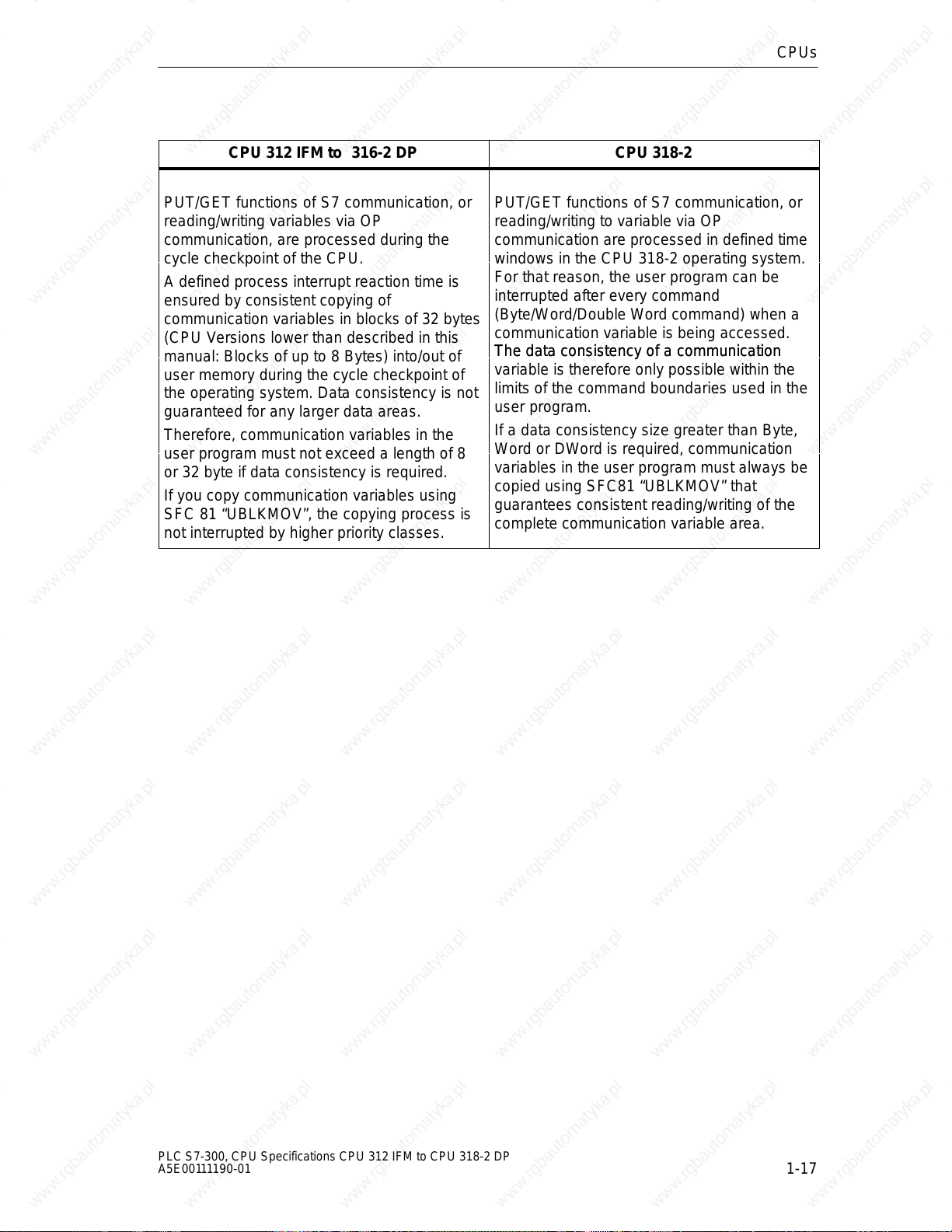

CPU 312 IFM to 316-2 DP CPU 318-2

CPUs

PUT/GET functions of S7 communication, or

reading/writing variables via OP

communication, are processed during the

cycle checkpoint of the CPU.

A defined process interrupt reaction time is

ensured by consistent copying of

communication variables in blocks of 32 bytes

(CPU Versions lower than described in this

manual: Blocks of up to 8 Bytes) into/out of

user memory during the cycle checkpoint of

the operating system. Data consistency is not

guaranteed for any larger data areas.

Therefore, communication variables in the

user program must not exceed a length of 8

or 32 byte if data consistency is required.

If you copy communication variables using

SFC 81 “UBLKMOV”, the copying process is

not interrupted by higher priority classes.

PUT/GET functions of S7 communication, or

reading/writing to variable via OP

communication are processed in defined time

windows in the CPU 318-2 operating system.

For that reason, the user program can be

interrupted after every command

(Byte/Word/Double Word command) when a

communication variable is being accessed.

The data consistency of a communication

The data consistency of a communication

variable is therefore only possible within the

limits of the command boundaries used in the

user program.

If a data consistency size greater than Byte,

Word or DWord is required, communication

variables in the user program must always be

copied using SFC81 “UBLKMOV” that

guarantees consistent reading/writing of the

complete communication variable area.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-17

Page 34

CPUs

Details

... on the communication topic are found in the STEP 7 Online Help and in the

manual Communication with SIMATIC.

... on communications SFCs/SFBs are found in the STEP 7 Online Help and in the

Standard and System functions reference manual.

Global Data Communication with S7-300 CPUs

Below you will find important features of global data communication in the S7-300.

Send/Receive Conditions

For the communication via GD circuits, you should observe the following

conditions:

Required for the GD packet transmitter is:

Reduction

ratio Transmitter

Required for the GD packet receiver is:

Reduction

time Transmitter

ratio Receiver

Non-observance of these conditions can lead to the loss of a GD packet. The

reasons for this are:

Cycle

Cycle

time Transmitter

timer eceiver

60 ms (CPU 318-2: 10 ms

Reduction

ratio Transmitter

Cycle

The performance capability of the smallest CPU in the GD circuit

Sending and receiving of global data is carried out asynchronously by the

sender and receiver.

Loss of global data is displayed in the status field of a GD circuit if you have

configured this with STEP 7.

Note

Note when communicating via global data: sent global data is not acknowledged

by the receiving partner!

The sender therefore receives no information on whether a receiver and which

receiver has received the sent global data.

Send Cycles for Global Data

In STEP 7 (as of Version 3.0), the following situation can arise if you set “Send

after every CPU cycle” with a short CPU cycle time (< 60 ms): the operating

system overwrites GD packets the CPU has not yet transmitted. Tip: Loss of

global data is displayed in the status field of a GD circuit if you have configured this

with STEP 7.

1-18

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 35

1.3 Test Functions and Diagnostics

The CPUs provide you with:

Testing functions for commissioning

Diagnostics via LEDs and STEP 7.

1.3.1 Testing Functions

The CPUs offer you the following testing functions:

Monitor Variables

Modify Variables

Forcing (note the differences between CPUs)

Monitor block

CPUs

Set Breakpoint

Details on the testing functions are found in the STEP 7 Online Help.

Important for the Status FB!

The STEP 7 function “Status FB” increases CPU cycle time!

In STEP 7 you can specify a maximum permissible increase in cycle time (not

CPU 318-2). In this case, in STEP 7 you must specify process mode for the CPU

parameters.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-19

Page 36

CPUs

Different Features of Forcing S7-300

Please note the different features of forcing in the different CPUs:

CPU 318-2 CPU 312IFM to 316-2DP

The variables of a user program with

fixed preset values (force values)

cannot be changed or overwritten by

the user program.

It is not permissible to force peripheral

or process image areas lying in the

range of consistent user data.

The following can be variables:

Inputs/outputs

Peripheral I/Os

Memory markers

You can force up to 256 variables.

The variables of a user program with

fixed preset values (force values) can

be changed or overwritten in the user

program.

(See Figure 1-4 on page 1-21)

The following can be variables:

Inputs/Outputs

You can force up to 10 variables.

1-20

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 37

Forcing with the CPU 312 IFM to 316-2 DP:

Caution

!

With S7-300 CPUs, forcing is the same as “cyclical modify”

Forced values in the input process image can be overwritten by write instructions

(e.g. T EB x, = E x.y, copying with SFC etc.) and peripheral read instructions (e.g.

L PEW x) in the user program, as well as by write instructions of PG/OP opera-

tions!

Outputs initialized with forced values only return the forced value if the user pro-

gram does not execute any write accesses to the outputs using peripheral write

commands (e.g. TPQB x ) and if no PG/OP functions write to these outputs!

Always note that forced values in the I/O process image cannot be overwritten by

the user program or PG/OP functions!

Execute force

job for inputs

CPUs

Execute force

job for inputs

PIO

transfer

Execute force

job for outputs

OS .... Operating system execution

Figure 1-4 The Principle of Forcing with S7-300 CPUs (CPU 312IFM to 316-2DP)

OS

PII

transfer

Forced

value

User program

Forced value

overwritten by T

PQW!

T PQW

PIO

transfer

Execute force

job for outputs

OS

Forced

value

PII

transfer

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-21

Page 38

CPUs

1.3.2 Diagnostics with LED Display

In Table 1-9, only the LEDs relevant to the diagnosis of the CPU and S7-300 are

listed. You will find the significance of the PROFIBUS-DP interface LEDs explained

in Chapter 2.

Table 1-9 Diagnostic LEDs of the CPU

LED

SF Comes on in

the event of

BATF Comes on

when

Stop Comes on

when

Flashes when

Hardware faults

Programming errors

Parameter assignment errors

Calculation errors

Timing errors

Faulty memory card

Battery fault or no backup at power on

I/O fault/error (external I/O only)

Communication error

The backup battery is missing, faulty or not charged.

Note Also lit if a rechargeable battery is installed. Reason:

The user program is not backed up the rechargeable battery.

The CPU is not processing a user program

The CPU requests a memory reset

1.3.3 Diagnostics with STEP 7

Description

1-22

Note

Please note that this is not a fail-safe or redundant system, regardless of its exi-

sting extensive monitoring and error reaction functions.

If an error occurs, the CPU enters the cause of the error in the diagnostic buffer.

You can read the diagnostic buffer using the programming device.

The CPU switches to STOP if an error or interrupt event occurs, or your user

program reacts accordingly with error or interrupt OBs. Details on STEP 7

diagnostic functions are found in the STEP 7 Online Help.

In the Instruction list you can find an overview

of the OBs you can use to react to respective error or interrupt events, as well

as of the OBs you can program in the respective CPU

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 39

CPU Reaction on Missing Error OB

If you have not programmed an error OB, the CPU reacts as follows:

CPU goes into STOP on missing ... CPU Remains in RUN with Missing ...

OB 80 (Runtime error)

OB 85 (Program cycle error)

OB 86 (Station failure in the PROFIBUS-

DP subnet)

OB 87 (Communication error)

OB 121 (Programming error)

OB 122 (Peripheral direct access

error)

CPU Behavior When There Is No Interrupt OB

If you have not programmed an interrupt OB, the CPU reacts as follows:

CPUs

OB 81 (Power break)

CPU goes into STOP on missing ... CPU Remains in RUN with Missing ...

OB 10/11 (TOD interrupt)

OB 20/21 (Delay interrupt)

OB 40/41 (Process interrupt)

OB 55 (TOD interrupt)

OB 56 (Delay interrupt)

OB 57 (for manufacturer-specific

interrupts)

OB 82 (Diagnostic interrupt)

OB 83 (Insertion/Removal interrupt)

Tip on OB35 (CPU 318-2: also OB32)

For the watchdog interrupt OB 35/32, you can specify times starting from 1 ms.

Note: The smaller the selected watchdog interrupt period, the more likely

watchdog interrupt errors will occur. You must take into account the operating

system times of the CPU in question, the runtime of the user program and the

extension of the cycle by active programming device functions, for example.

OB 32/35 (Watchdog interrupt)

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-23

Page 40

CPUs

1.4 CPUs - Technical Specifications

In This Section

You will find the technical specifications of the CPU.

You will find the technical specifications of the integrated inputs/outputs of the

CPU 312 IFM and 314 IFM.

You will not find the features of the CPU 31x-2 DP as a DP master/DP slave.

Refer to Chapter 2.

Section Contents Page

1.4.1 CPU 312 IFM 1-25

1.4.2 CPU 313 1-37

1.4.3 CPU 314 1-40

1.4.4 CPU 314 IFM 1-43

1.4.5 CPU 315 1-60

1.4.6 CPU 315-2 DP 1-63

1.4.7 CPU 316-2 DP 1-66

1.4.8 CPU 318-2 1-69

1-24

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 41

1.4.1 CPU 312 IFM

Special Features

Integrated I/Os (Wiring via 20-pole front connector)

No backup battery and therefore maintenance-free

An S7-300 with CPU 312 IFM can be mounted only on one rack

Integrated Functions of the CPU 312 IFM

Integrated Functions Description

Process interrupt Interrupt input means: inputs configured with this function trigger a process

interrupt at the corresponding signal edge.

Interrupt input options for the digital inputs 124.6 to 125.1 must be programmed

in STEP 7.

Counter The CPU 312 IFM offers these special functions as an alternative at the digital

inputs 124.6 to 125.1.

Frequency meter

For a description of the special functions “Counter” and “Frequency meter”,

please refer to the Integrated Functions Manual.

CPUs

“Interrupt Inputs” of the CPU 312 IFM

If you wish to use the digital inputs 124.6 to 125.1 as interrupt inputs, you must

program these in STEP 7 in the CPU parameters.

Note the following points:

These digital inputs have a very low signal delay. At this interrupt input, the

module recognizes pulses with a length as of approx. 10 to 50 s. Always use

shielded cable to connect active interrupt inputs in order to avoid interrupts

triggered by line interference.

Note The minimum pulse width of an interrupt trigger pulse is 50 s.

The input status associated with an interrupt in the input process image or with

LPIB always changes with ”normal” input delay of approx.3 ms.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-25

Page 42

CPUs

Start information for OB40

Table 1-10 shows the temporary (TEMP) variables of OB40 relevant for the

“Interrupt inputs” of the CPU 312 IFM. Refer to theSystem and Standard functions

reference manual for details on the process interrupt OB.

Table 1-10 Start Information for OB 40 for the Interrupt Inputs of the Integrated I/Os

Byte

6/7 OB40_MDL_ADDR WORD B#16#7C Address of the interrupt triggering

8 on OB40_POINT_ADDR DWORD See Figure 1-5 Signaling of the interrupt triggering

Variable Data Type Description

module (in this case, the CPU)

integrated inputs

Display of the Interrupt Inputs

In variable OB40_POINT_ADDR, you can view the interrupt inputs which have

triggered a process interrupt. Figure 1-5 shows the allocation of the interrupt inputs

to the bits of the double word.

Note: Several bits can be set if interrupts are triggered by several inputs within

short intervals (< 100 s). That is, the OB is started once only, even if several

interrupts are pending.

31 30

54 13

Reserved

2

0 Bit No.

PRIN from I124.6

PRIN from I 124.7

PRIN from I125.0

PRIN from I 125.1

1-26

PRIN: Process interrupt

Figure 1-5 Display of the States of the Interrupt Inputs of the CPU 312 IFM

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 43

Front View

CPUs

Status and

fault LEDs

Mode selector

Multipoint Interface

(MPI)

Figure 1-6 Front View of the CPU 312 IFM

I124.0

I1

I2

I3

I4

I5

I6

I7

I125.0

I1

Q124.0

Q1

Q2

Q3

Q4

Q5

Front connector,

used to connect

the integrated

I/O, power

supply and

system ground.

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-27

Page 44

CPUs

Technical Specifications of the CPU 312 IFM

CPU and Product Version

MLFB

Hardware version

6ES7 312-5AC02-0AB0

01

Firmware version V 1.1.0

Matching programming

package

Memory

Work memory

STEP 7 V 5.0;

Service Pack 03

integral 6 KB

Expandable no

Load memory

integral 20 KB RAM

20 KB EEPROM

Expandable FEPROM no

Expandable RAM no

Backup Yes

With battery no

Without battery 72 bytes retentive

Configurable

(data, flags, timers)

Processing times

Processing times for

Bit instructions 0.6 s minimum

W ord instructions 2 s minimum

Double integer math 3 s minimum

Floating-point math

instructions

Timers/Counters and their retentive characteristics

S7 counters 32

60 s minimum

Data areas and their retentive characteristics

Retentive data area as a

whole (inc. flags, timers,

counters)

Bit memories 1024

Adjustable retentivity MB 0 to MB 71

Preset MB 0 to MB 15

Clock memories 8 (1 memory byte)

Data blocks max. 63 (DB 0 reserved)

Size max. 6 KB

Adjustable retentivity max. 1 DB, 72 bytes

Preset No retentivity

Local data (non-alterable) max. 512 bytes

Per priority class 256 bytes

Blocks

OBs See Instruction List

Size max. 6 KB

Nesting depth

Per priority class 8

additional levels within

FBs max. 32;

Size max. 6 KB

FCs max. 32;

Size max. 6 KB

Address areas (I/O)

Peripheral address area

Digital

Adjustable retentivity from C 0 to C 31

Preset from C 0 to C 7

Counting range 1 to 999

IEC Counters Yes

Type SFBs

S7 timers 64

Adjustable retentivity No

Analog 256 to 383/256 to 383

Process image (cannot be

customized)

Digital channels 256+10 integrated/256+6

Analog channels 64/32

Timing range 10 ms to 9990 s

IEC Timers Yes

Type

SFBs

an error OB

– integrated

max. 1 DB, 72 data bytes

None

0 to 31/0 to 31

124,125 E/124 A

32 bytes+4 bytes

integrated/ 32 bytes+4

bytes integrated

integrated

1-28

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 45

CPUs

Configuration

Rack 1

Modules per module rack max. 8

DP Master

integral None

via CP Yes

S7 message functions

Simultaneously active

Alarm-S blocks

Time

Real-time clock Yes

None

Backed-up No

Accuracy See Section 1.1.6

Operating hours counter No

Clock synchronisation Yes

On PLC Master

On MPI Master/Slave

Testing and commissioning functions

Status/Modify Variables Yes

Variable Inputs, outputs, flags, DBs,

timers, counters

Number

– Monitor Variables

– Modify Variables

Force Yes

max. 30

max. 14

Variable Inputs, outputs

Number max. 10

Monitor block Yes

Single sequence

Breakpoint

Diagnostic buffer Yes

Number of entries

(non-alterable)

Yes

2

100

Communication functions

PD/OP communication Yes

Global data communication Yes

Number of GD packets

– Sender 1

– Receiver 1

Size of GD packets max. 22 bytes

– Number of which

consistent

S7 basic communication Yes

8 bytes

User data per job max. 76 bytes

– Number of which

consistent

S7 communication Yes (server)

32 bytes for X/I_PUT/_GET;

76 bytes for

X_SEND/_RCV

User data per job max. 160 bytes

– Number of which

consistent

S7-compatible

communication

Standard communication No

Number of connection

resources

32 bytes

No

6 for PD/OP/S7 basic/S7

communication

Reservation for

– PD communication

User-definable

Default

– OP communication

User-definable

Default

– S7 basic

communication

User-definable

Default

Interfaces

1. Interface

Functionality

max. 5

from 1 to 5

1

max. 5

from 1 to 5

1

max. 2

from 0 to 2

2

MPI Yes

DP Master No

DP Slave No

Galvanically isolated No

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

1-29

Page 46

CPUs

MPI

Services

– PD/OP

communication

– Global data

communication

– S7 basic

communication

– S7 communication Yes (server)

Yes

Yes

Yes

T ransmission rates 19.2; 187.5 Kbps

Dimensions

Assembly dimension

BHT (mm)

Weight Approx. 0.45 kg

Programming

Programming language STEP 7

Stored instructions See Instruction List

Nesting levels 8

System functions (SFCs) See Instruction List

System function blocks

(SFBs)

User program security Password protection

80125130

See Instruction List

Voltages, Currents

Power supply 24V DC

Permissible range 20.4 to 28.8 V

Current consumption (idle) typical 0.7 A

Inrush current typical 8A

l 2 t 0.4 A2s

External fusing for supply

lines (recommendation)

PG supply on MPI (15 to

30V DC)

Power losses typical 9 W

Battery No

Accumulator No

Integrated inputs/outputs

Addresses of integral

Circuit breaker; 10 A,

Type B or C

max. 200 mA

Digital inputs E 124.0 to E 127.7

Digital outputs A 124.0 to A 124.7

Integrated Functions

Counter 1 (see Integrated

Frequency meter up to 10 kHz max.

Functions)

manual

(see Integrated Functions)

manual

1-30

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 47

Technical Specifications of the Special Inputs of the CPU 312IFM

CPUs

Module-Specific Data

Number of inputs 4

I 124.6 to 125.1

Cable length

Shielded max. 100 m (109yd.)

V oltages, Currents, Potentials

Number of inputs that can

be triggered simultaneously

4

(horizontal

configuration)

up to 60°C

(vertical configuration)

up to 40°C

Status, Interrupts; Diagnostics

Status display 1 green LED per

Interrupts

4

4

channel

Process interrupt Configurable

Diagnostic functions None

Sensor Selection Data

Input voltage

Rated value

For “1” signal

I 125.0 and I 125.1

I 124.6 and I 124.7

For “0” signal

Input current

For “1” signal

I 125.0 and I 125.1

I 124.6 and I 124.7

Input delay time

For “0” to “1”

For “1” to “0”

Input characteristic

E 125.0 and E 125.1

E 124.6 and 124.7

Connection of 2-wire

BEROs

Permissible idle current

I 125.0 and I 125.1

I 124.6 and I 124.7

Time, Frequency

24V DC

15 to 30 V

15 to 30 V

-3 to 5 V

min. 2 mA

min. 6.5 mA

max. 50 s

max. 50 s

to IEC 1131, Type 1

to IEC 1131, Type 1

no

max. 0.5 mA

max. 2 mA

Internal conditioning time

for

Interrupt processing

Input frequency 10 kHz

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

max. 1.5 ms

1-31

Page 48

CPUs

Technical Specifications of the Digital Inputs of the CPU 312IFM

Note

Alternatively, you can configure the inputs I 124.6 and I 124.7 as special inputs, in

which case the technical specifications listed for the special inputs apply to the

inputs I 124.6 and I 124.7.

Module-Specific Data

Number of inputs 8

Cable length

Unshielded

Shielded

V oltages, Currents, Potentials

Number of inputs that can

be triggered simultaneously

max. 600 m

max. 1000 m

8

(horizontal

configuration)

up to 60°C

(vertical configuration)

up to 40°C

Galvanic isolation No

8

8

Status, Interrupts; Diagnostics

Status display 1 green LED per

channel

Interrupts None

Diagnostic functions None

Sensor Selection Data

Input voltage

Rated value

For “1” signal

For “0” signal

Input current

24V DC

11 to 30 V

-3 to 5 V

For “1” signal typical 7 mA

Input delay time

For “0” to “1”

For “1” to “0”

Input characteristic to IEC 1131, Type 2

Connection of 2-wire

BEROs

Permissible quiescent

current

1.2 to 4.8 ms

1.2 to 4.8 ms

Possible

max. 2 mA

1-32

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

Page 49

Technical Specifications of the Digital Outputs of the CPU 312IFM

CPUs

Module-Specific Data

Number of outputs 6

Cable length

Unshielded

Shielded

V oltages, Currents, Potentials

Total current of outputs (per

group)

max. 600 m

max. 1000 m

(horizontal

configuration)

up to 40°C

up to 60°C

(vertical configuration)

up to 40°C

Galvanic isolation No

Status, Interrupts; Diagnostics

Status display 1 green LED per

Interrupts None

Diagnostic functions None

max. 3 A

max. 3 A

max. 3 A

channel

Actuator Selection Data

Output voltage

For “1” signal min. L+ (-0.8 V)

Output current

For “1” signal

Rated value

Permissible range

0.5 A

5 mA to 0.6 A

For “0” signal

Residual current

Load impedance range 48 to 4 k

Lamp load max. 5 W

Parallel connection of 2

outputs

For dual-channel

triggering of a load

For performance

increase

Triggering of a digital input Possible

Switching frequency

For resistive load

For inductive load to

IEC947-5-1, DC 13

For lamp load

Inductive breaking voltage

limited internally to

max. 0.5 mA

Possible

Not possible

max. 100 Hz

max. 0.5 Hz

max. 100 Hz

typical V 30

Short-circuit protection of

the output

Response threshold

PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

yes, electronically

timed

typical 1 A

1-33

Page 50

CPUs

Wiring diagram of the CPU 312 IFM

Figure 1-7 shows the wiring diagram of the CPU 312 IFM. Use a 20-pole front

connector to wire the CPU’s integrated I/O.

Caution

!

The CPU 312 IFM has no reverse polarity protection. Polarity reversal destroys

the integrated outputs. Nonetheless, in this case the CPU does not switch to

STOP and the status displays are lit. In other words, the fault is not indicated.

I124.0

I1

I2

I3

I4

I5

I6

I7

I125.0