Page 1

PZ-43MR2E

PZ-50MR2E

SERVICE MANUAL

S12E6PZ50MR2E

PLASMA DISPLAY TV

(AVC SYSTEM)

PZ-43MR2E

MODELS

In the interests of user-safety (Required by safety regulations in some countries) the set should be restored

to its original condition and only parts identical to those specified should be used.

CONTENTS

Page

» IMPORT ANT SER VICE SAFETY PRECAUTION .....2

» SPECIFICATIONS................................................3

» OPERA TION MANUAL ........................................4

» DIMENSIONS ....................................................11

» REMOVING OF MAJOR PARTS........................12

» ADJUSTMENT PROCEDURES.........................14

» DESCRIPTION OF MAJOR IC FUNCTIONS ....20

» TROUBLE SHOOTING TABLE ..........................43

» PRINTED WIRING BOARD BLOCK DIAGRAM .. 50

» SYSTEM BLOCK DIAGRAM ............................. 52

» SIGNAL FLOW BLOCK DIAGRAM....................54

» DC/DC CONVERTER BLOCK DIAGRAM .........56

» POWER BLOCK DIAGRAM............................... 58

» PC I/F BLOCK DIAGRAM ..................................60

» OVERALL WIRING DIAGRAM...........................62

» DESCRIPTION OF SCHEMATIC DIAGRAM ..... 66

» WAVEFORMS .................................................... 67

» SCHEMA TIC DIAGRAM.....................................68

» PRINTED WIRING BOARD ASSEMBLIES...... 108

» P ARTS LIST .....................................................115

» P ACKING OF THE SET ................................... 139

PZ-50MR2E

Page

SHARP CORPORATION

Page 2

PZ-43MR2E

2

2

PZ-50MR2E

IMPORTANT SERVICE SAFETY PRECAUTION

Ë

Service work should be perfomed only by qualified service technicians who are thoroughly familiar with all safety checks and the servicing guidelines which follow:

WARNING

1. For continued safety, no modification of any circuit

should be attempted.

2. Disconnect AC power before servicing.

CAUTION: FOR CONTINUED PROTECTION

AGAINST A RISK OF FIRE REPLACE ONLY WITH

SAME TYPE F701 (T2A, 250V), F702 (T2A, 250V)

AND F1702 (T4AL, 250V) FUSE.

BEFORE RETURNING THE RECEIVER

(Fire & Shock Hazard)

Before returning the receiver to the user, perform

the following safety checks:

1. Inspect all lead dress to make certain that leads are

not pinched, and check that hardware is not lodged

between the chassis and other metal parts in the

receiver.

2. Inspect all protective devices such as non-metallic

control knobs, insulation materials, cabinet backs,

adjustment and compartment covers or shields,

isolation resistor-capacitor networks, mechanical

insulators, etc.

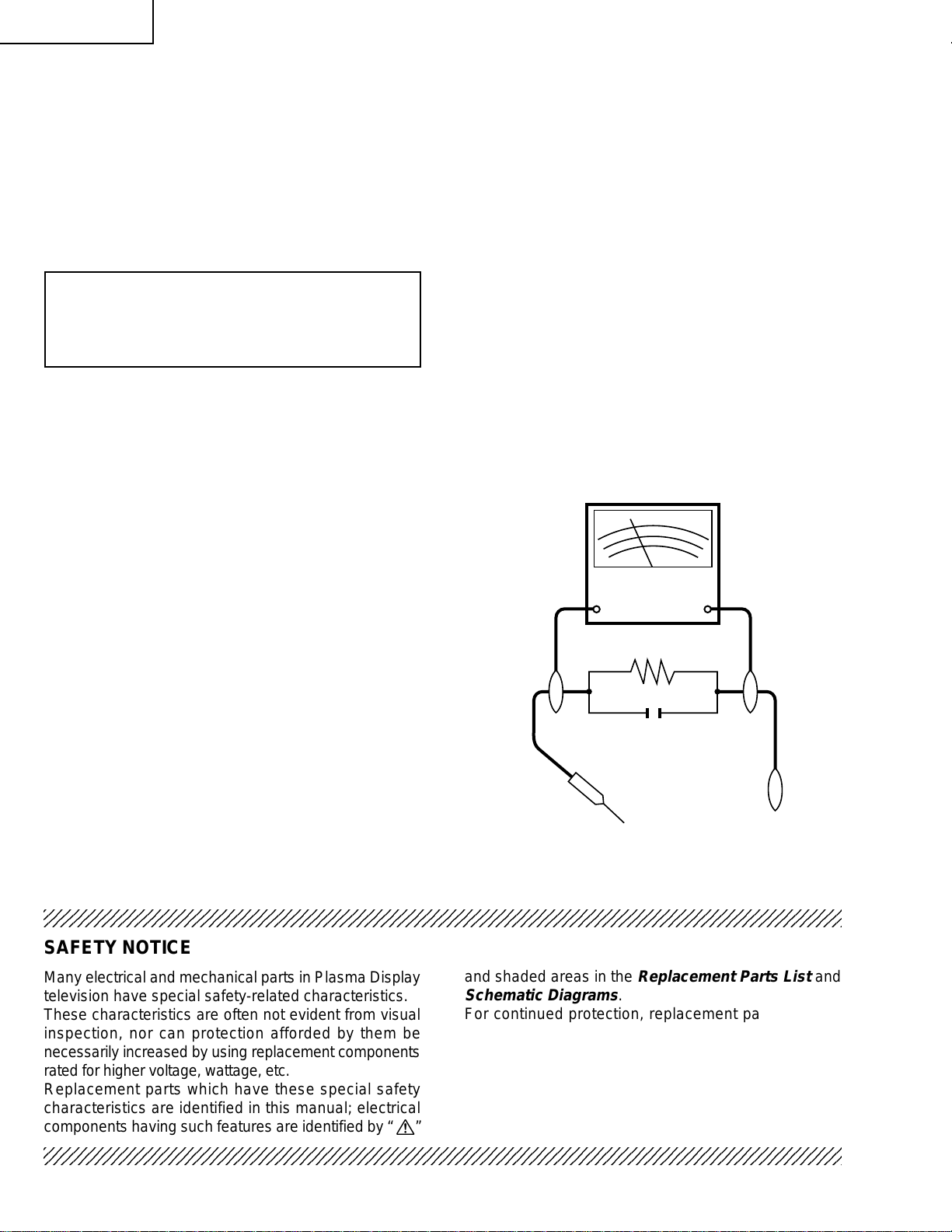

3. To be sure that no shock hazard exists, check for

leakage current in the following manner.

» Plug the AC cord directly into a 110~240 volt AC outlet,

and connect the DC power cable into the receiver's

DC jack. (Do not use an isolation transformer for this

test).

» Using two clip leads, connect a 1.5k ohm, 10 watt

resistor paralleled by a 0.15µF capacitor in series

with all exposed metal cabinet parts and a known

earth ground, such as electrical conduit or electrical

ground connected to an earth ground.

» Use an AC voltmeter having with 5000 ohm per volt,

or higher, sensitivity or measure the AC voltage drop

across the resisor.

» Connect the resistor connection to all exposed metal

parts having a return to the chassis (antenna, metal

cabinet, screw heads, knobs and control shafts,

escutcheon, etc.) and measure the AC voltage drop

across the resistor.

All checks must be repeated with the AC cord plug

connection reversed. (If necessary, a nonpolarized

adaptor plug must be used only for the purpose of

completing these checks.)

Any reading of 35V peak (this corresponds to 0.7

milliamp. peak AC.) or more is excessive and

indicates a potential shock hazard which must be

corrected before returning the monitor to the owner.

DVM

AC SCALE

50k ohm

10W

0.15 µF

TEST PROBE

TO EXPOSED

METAL PAR TS

CONNECT TO

KNOWN EARTH

GROUND

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

SAFETY NOTICE

Many electrical and mechanical parts in Plasma Display

television have special safety-related characteristics.

These characteristics are often not evident from visual

inspection, nor can protection afforded by them be

necessarily increased by using replacement components

rated for higher voltage, wattage, etc.

Replacement parts which have these special safety

characteristics are identified in this manual; electrical

and shaded areas in the

Schematic Diagrams

For continued protection, replacement parts must be

identical to those used in the original circuit.

The use of a substitute replacement parts which do not

have the same safety characteristics as the factory

recommended replacement parts shown in this service

manual, may create shock, fire or other hazards.

components having such features are identified by “ å”

234567890123456789012345678901212345678901234567890123456789012123456789012345678901234567890121

2

Replacement Parts List

.

and

Page 3

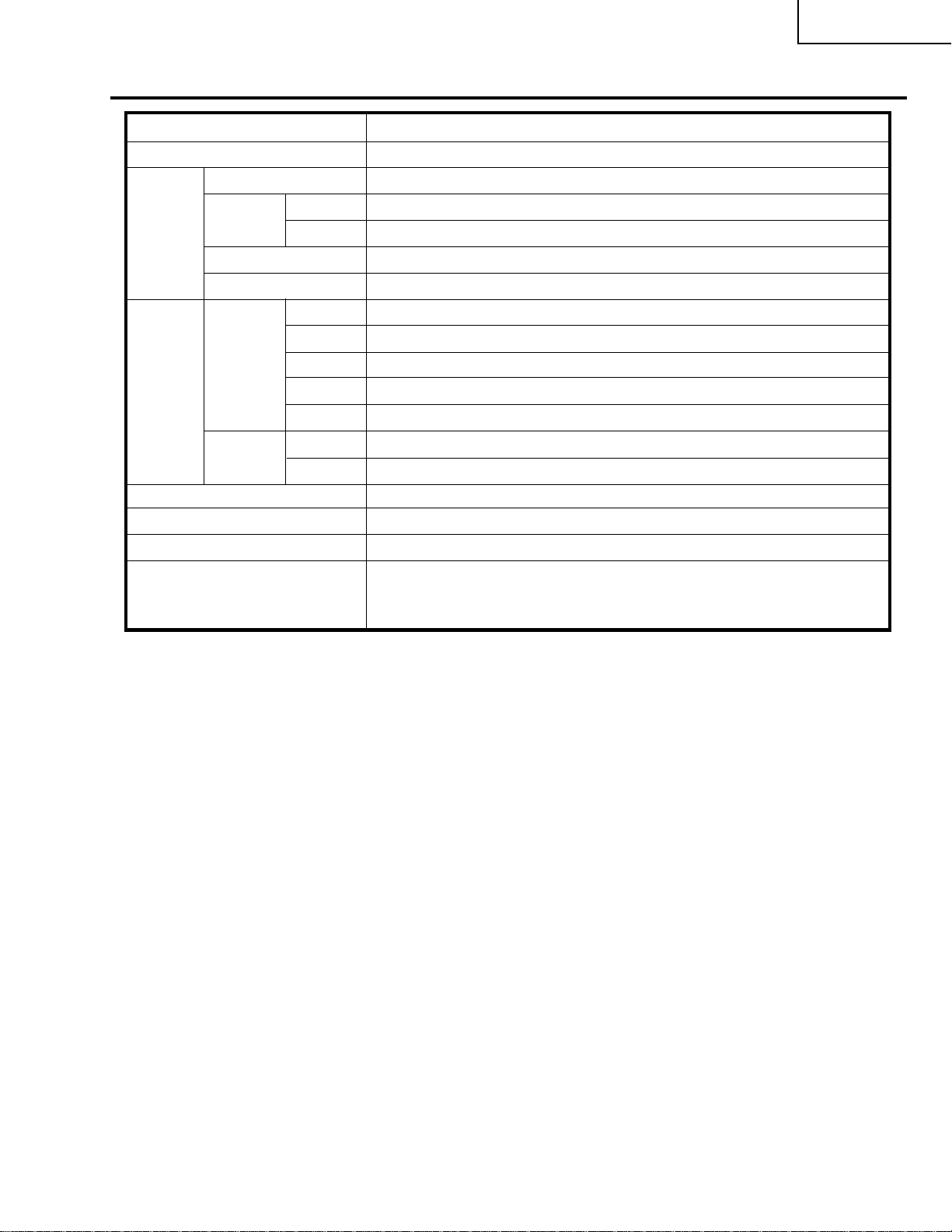

Specifications

Item AVC System, Model: PZ-50MR2E, PZ-43MR2E

Colour System

PAL/SECAM/NTSC 3.58/NTSC 4.43/PAL 60

TV

Function

B/G, D/K, I, L/L’

VHF/UHF E2–E69ch, F2–F10ch, I21–I69ch, IR A–IR Jch

CATV

Hyper-band, S1–S41ch

Auto Channel Preset

99 ch, Auto Preset, Auto Label, Auto Sort

STEREO NICAM/IGR

Terminals SCART (AV in, RGB in, TV out)

INPUT 2

SCART (AV in/out, S-VIDEO in, AV Link)

INPUT 3

SCART (AV in/out, S-VIDEO in, RGB in), Component

ANTENNA 75 q Din Type for VHF/UHF in

INPUT 4 S-VIDEO, AV in

PC INPUT

15 Pin mini D-Sub, Audio in

Audio (Variable, Fixed), S-VIDEO out, AV out

Power Requirement

AC 220–240 V, 50/60 Hz, 40 W (0.8 W Standby)

Dimensions

430 (W), 70 (H), 330 (D) mm

Weight

4.4 kg

Accessories

Power cord, Remote control unit, Two AA size batteries, System cable,

Two operation manuals

Receiving System

Tuner

Rear INPUT 1

Front

• Design and specifications are subject to change without notice.

AV OUTPUT

PZ-43MR2E

PZ-50MR2E

3

Page 4

PZ-43MR2E

PZ-50MR2E

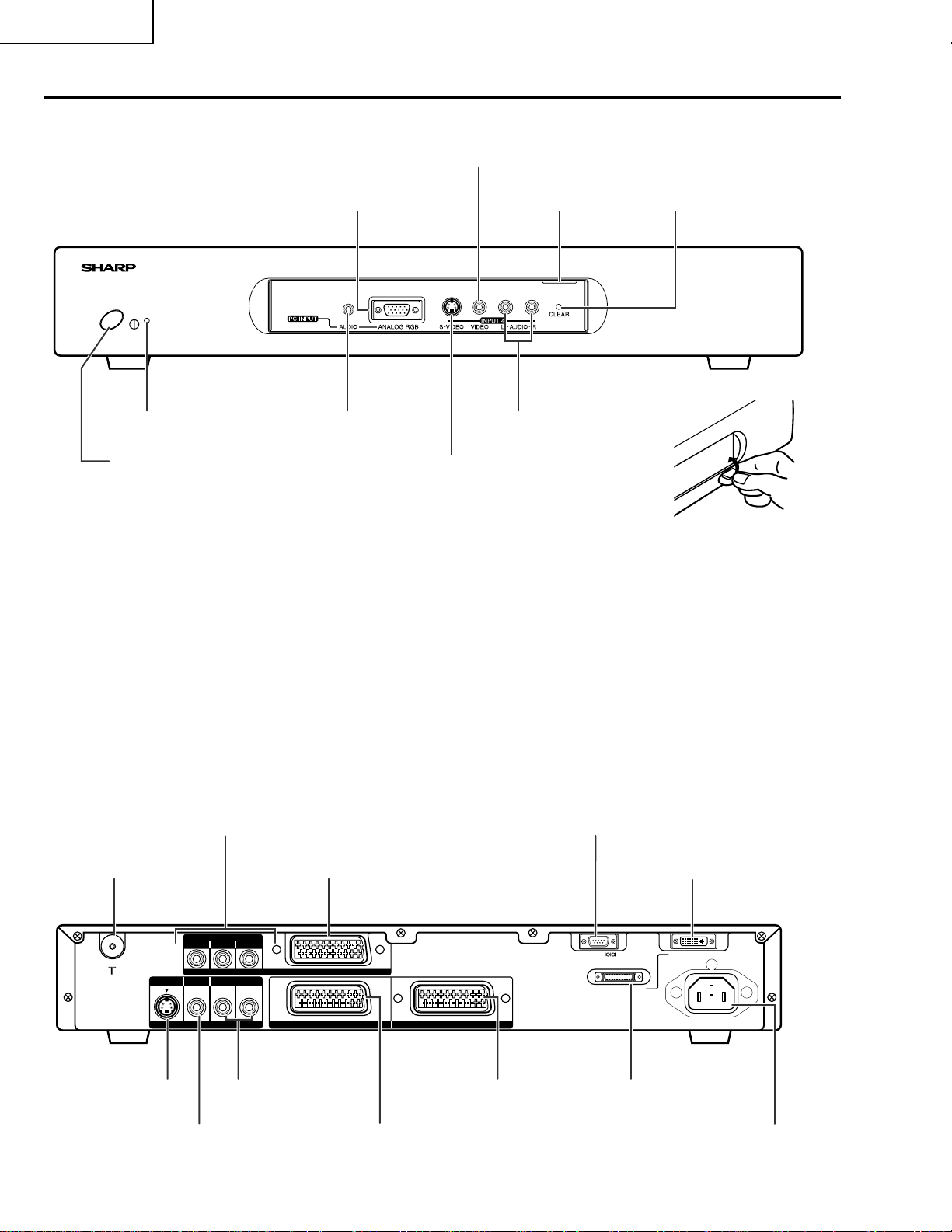

Operation Manual

AVC System

Front view

PC INPUT terminal (ANALOG RGB)

STANDBY/ON indicator

PC INPUT terminal

INPUT 4 terminal (VIDEO)

Door knob

INPUT 4 terminals (AUDIO)

CLEAR button*

(AUDIO)

POWER button

INPUT 4 terminal (S-VIDEO)

(How to open the door)

* If the AVC System is switched on but it does not appear to be operating correctly, it may need resetting. In this

case press CLEAR on the front of the unit as shown in the diagram. Press CLEAR lightly with the end of a

ballpoint pen or other pointed object.

This will reset the System as shown below.

• AV MODE resets to STANDARD

• TV channel resets to channel 1

• Dual screen resets to normal

• Audio setting initialises

• SRS resets to Off

• Image position is initialised

A

• Pressing CLEAR will not work if the System is in standby mode (indicator lights red).

• Pressing CLEAR will not delete channel preset or password. See Page for initialising factory preset settings when you

know your password. See Page or initialising factory preset values when you have forgotten your password.

Rear view

INPUT 3 terminals

(Y, P

B(CB), PR(CR

))

RS-232C terminal

ANTENNA INPUT terminal

S-VIDEO VIDEO

AV OUTPUT

AV OUTPUT terminal

(S-VIDEO)

AV OUTPUT terminal

(VIDEO)

INPUT 3 terminal (SCART)

COMPONENT

PB(CB)

PR(CR)Y

R - AUDIO - L

INPUT 3

AV OUTPUT terminals

(AUDIO)

INPUT 2 INPUT 1

INPUT 1 terminal

(SCART)

INPUT 2 terminal

(SCART)

4

DISPLAY OUTPUT-1 ter minal

RS-232C DISPLAY OUTPUT-1

DISPLAY OUTPUT-2

AC INPUT

220–240V

DISPLAY OUTPUT-2 terminal

AC INPUT terminal

Page 5

PZ-43MR2E

PZ-50MR2E

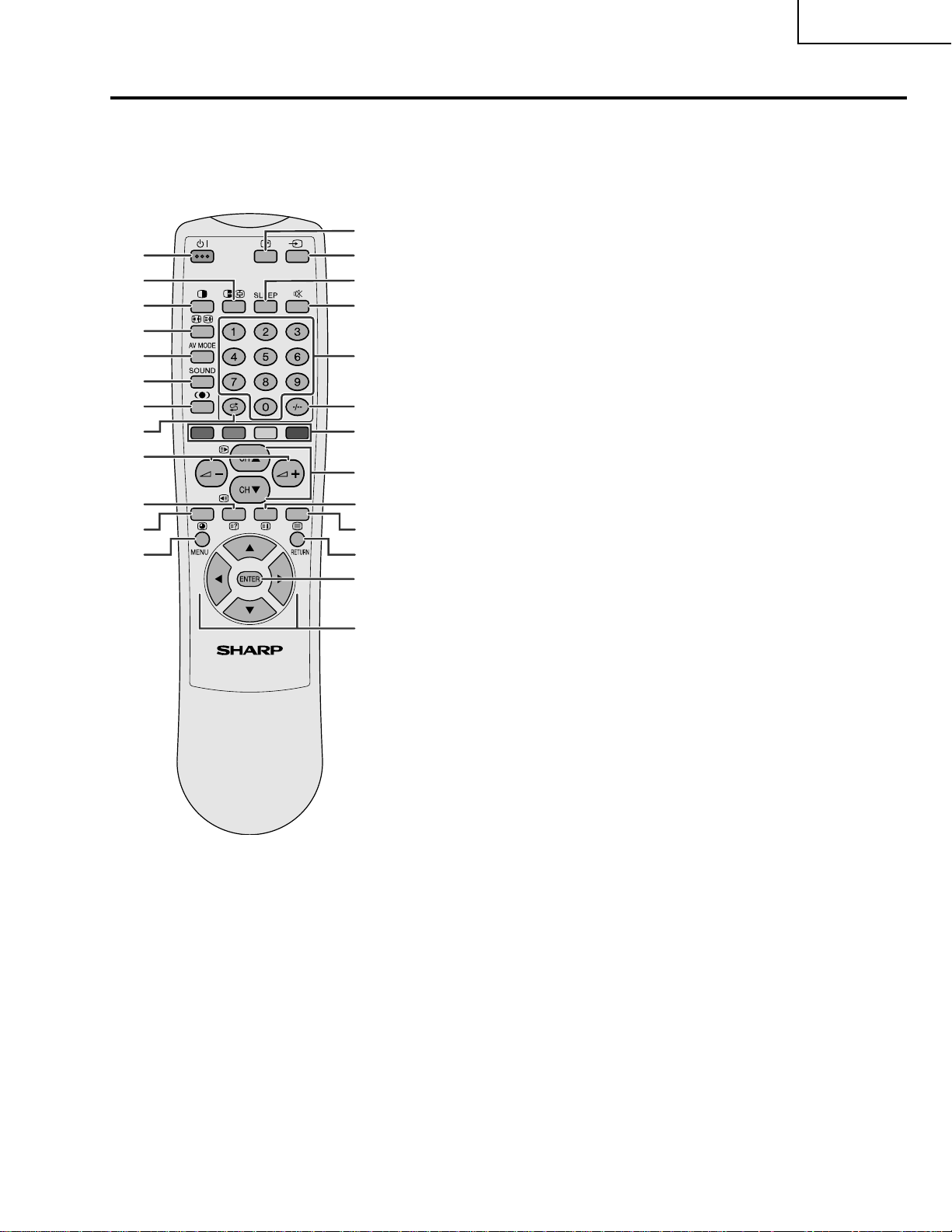

Remote control unit

13

1

2

3

14

15

16

4

5

17

6

7

8

18

19

9

20

10

11

12

21

22

23

24

25

A

• When using the remote control unit, point it

at the Plasma Display TV (Panel Unit).

* “TV”, “INPUT1”, “INPUT2”, “INPUT3”,

“INPUT4” and “PC” modes can each store

the WIDE mode setting separately.

The same for AV mode and volume.

1 a (STANDBY/ON)

To switch the power on and off.

2 du (FREEZE/HOLD for TELETEXT)

TV/External input mode: Change the still image mode.

TELETEXT mode: Freeze a multi-page on screen while other

pages are automatically updated. Press d again to return to the

normal image.

3 c (DUAL screen)

Set the dual picture mode. Press c again to return to normal view.

4 fv (WIDE MODE/ T/B/F)*

TV/External input mode: Change the wide image mode.

TELETEXT mode: Set the area of magnification. (full/upper half/

lower half)

5 AV MODE*

Select a video setting. AV MODE (STANDARD, DYNAMIC, MOVIE,

GAME, USER) PC MODE (STANDARD, USER)

6 SOUND

Select the sound multiplex mode.

7 h (SRS and FOCUS)

Select SRS and FOCUS Sound System.

8 A (FLASHBACK)

Press to return to the previous channel in normal viewing mode.

Press to return to the previous page in TELETEXT mode.

9 il/ik (VOLUME)*

Set the volume.

10 (Reveal hidden for TELETEXT)

k

TELETEXT mode: Display hidden characters.

11 j (SUBPAGE for TELETEXT)

TELETEXT mode: Change the picture mode for sub-page selecting.

12 MENU

Display the Menu screen.

13 C (CHANNEL INFORMATION)

Display the channel information and time.

14 b (INPUT SOURCE)

Select an input source. (TV, INPUT 1, INPUT 2, INPUT 3, INPUT 4,

PC)

15 SLEEP

Set the SLEEP TIMER.

16 e (MUTE)

Mute the sound.

17 0 – 9

TV/External input mode: Set the channel.

TELETEXT mode: Set the page.

18 o (Digit for channel select)

Change the digits of the selected TV channel.

19 Colour (RED/GREEN/YELLOW/BLUE)

TELETEXT mode: Select a page.

20 CHa/CHb(w/x )

TV/External input mode: Select the channel.

TELETEXT mode: Set the page.

21 l (TOP Overview for TELETEXT)

TELETEXT mode: Display an index page for CEEFAX/FLOF

information. TOP OVER VIEW for TOP programme.

22 m (TELETEXT)

Select the TELETEXT mode. (all TV image, all TEXT image, TV/TEXT

image)

23 RETURN

MENU mode: Return to the previous menu screen.

24 ENTER

Execute a command.

Return to the initial image position after moving with a/b/c/d.

25 a/b/c/d (Cursor)

Select a desired item on the setting screen.

Move the picture on the screen.

5

Page 6

PZ-43MR2E

L

PZ-50MR2E

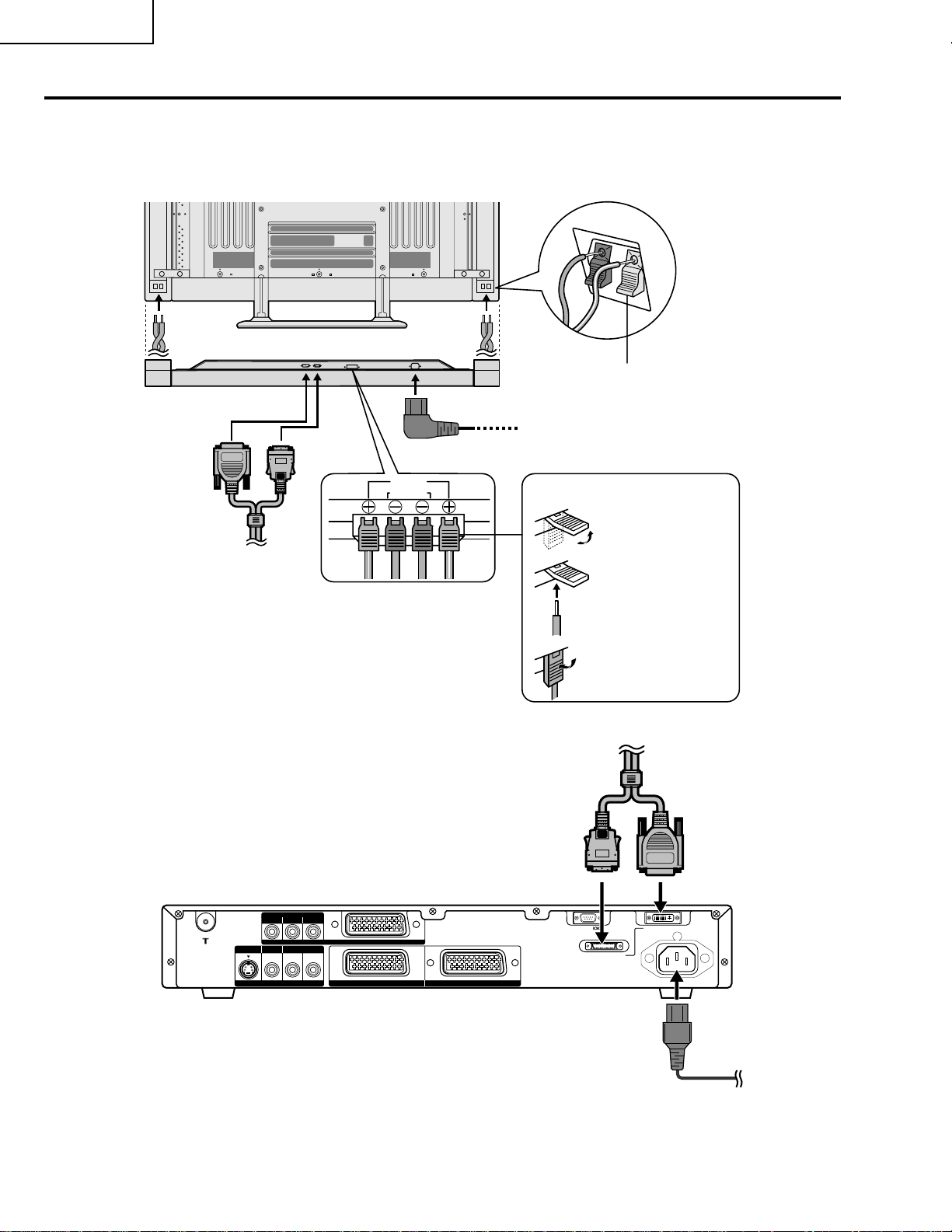

Preparation

Setting the system

1.

Connecting the system cable, the power cor d and the speaker cables to the Plasma Displa y TV (Panel

Unit)

Plasma Display TV (Panel Unit) (rear view)

Black

Red

Speaker cable

Speaker cable

(bottom view)

(WHITE)

(GRAY)

Red

Black

System cable

Speaker cables

(GRAYeGRAY with white stripe)

A

• Two speaker cables of different lengths are supplied. As

shown in the diagram, connect the longer speaker cable

to the left speaker and the shorter to the right.

2.

Connecting the system cable and the power cord to the AVC System

Power cord

As you apply pressure to this part,

insert the speaker cable. It is

important to match polarity when

connecting the speaker cables to the

terminals.

Insert the speaker cable

Lift up the snap clip.

Insert the wire into

the hole of the

connector.

Lower the snap clip

to grip the wire in

place.

System cable

(GRAY)

(WHITE)

AVC System (rear view)

COMPONENT

PB(CB)

PR(CR)Y

INPUT 3

AV OUTPUT

R - AUDIO - L

INPUT 2 INPUT 1

S-VIDEO VIDEO

• TO PREVENT RISK OF ELECTRIC SHOCK, DO NOT TOUCH UN-INSULATED PARTS OF ANY CABLES WITH THE

POWER CORD CONNECTED.

6

RS-232C DISPLAY OUTPUT-1

DISPLAY OUTPUT-2

AC INPUT

220–240V

Power cord

Page 7

PZ-43MR2E

PZ-50MR2E

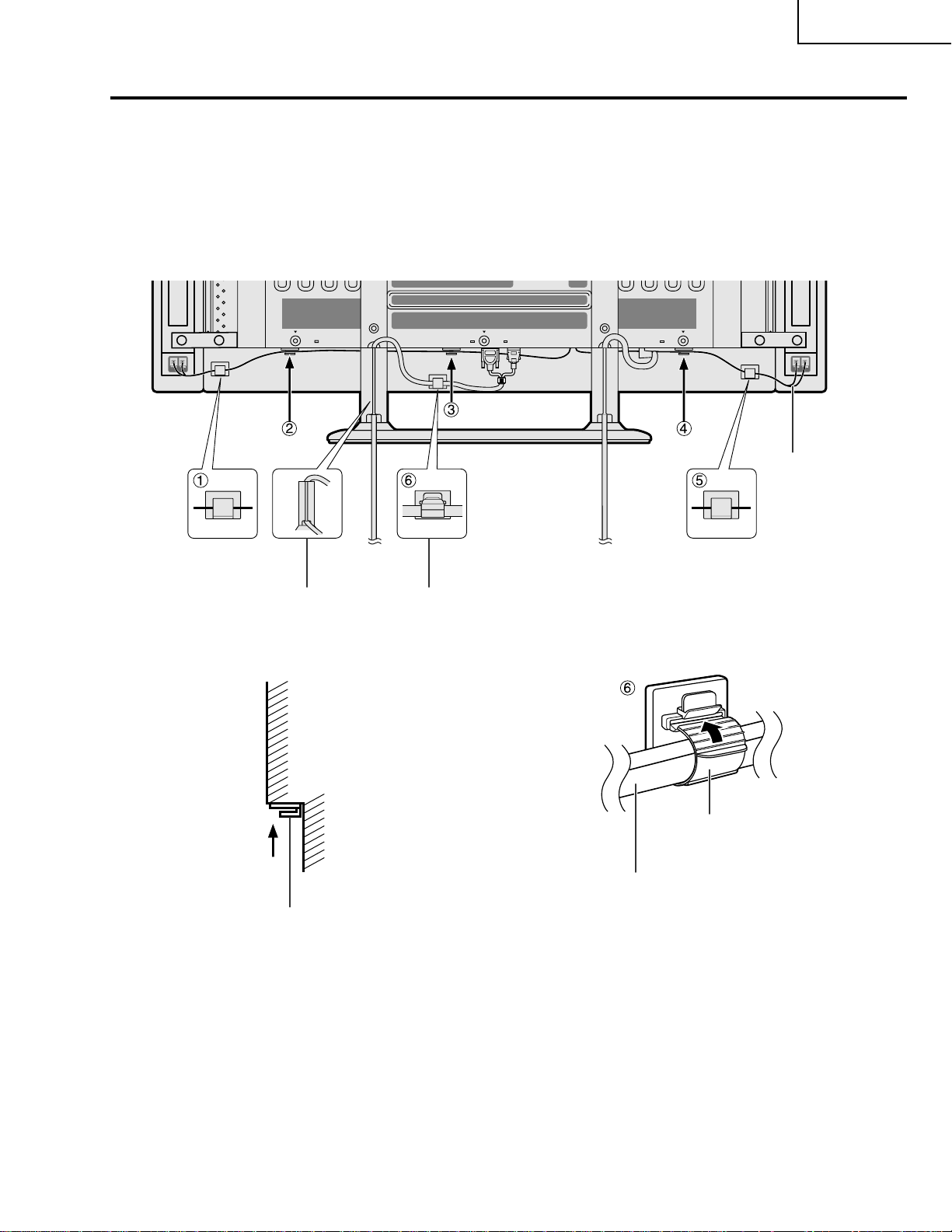

preparation

How to route cables

A system cable clamp and five speaker cable clamps are included with the system for cable management. Follow the

diagram below for correct cable management.

As viewed from the rear of the display.

Speaker cable

Speaker cable clamp

Wedge the power cord and the

system cable into the groove on the

stand.

Stick the speaker cable clamps

(2 – 4) to the surface as shown.

System cable

Power cord

Speaker cable clamp

System cable clamp

System cable clamp

System cable

7

Page 8

PZ-43MR2E

L

PZ-50MR2E

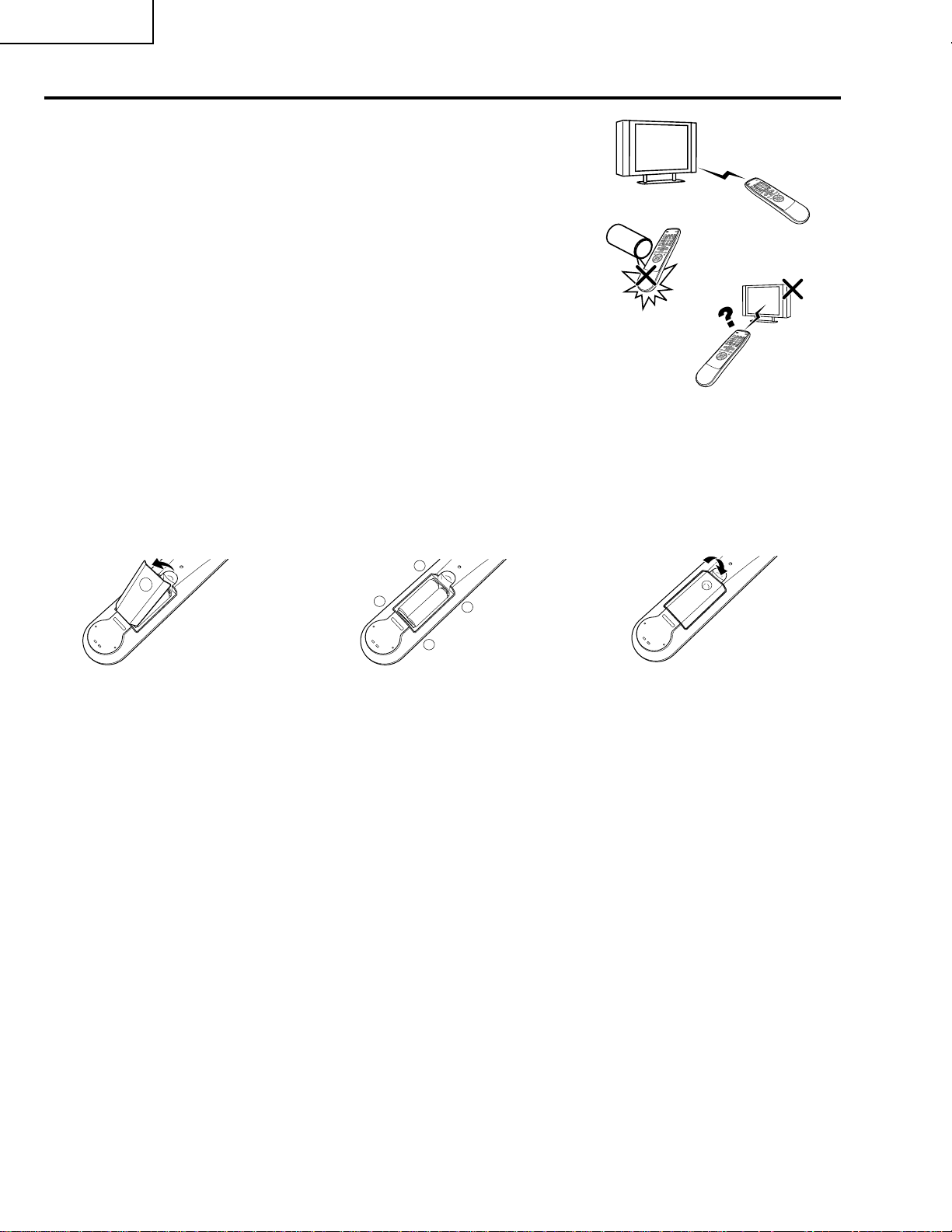

preparation

Using the remote control unit

Use the remote control unit by pointing it towards the remote sensor window.

Objects between the remote control unit and sensor window may pr event proper

operation.

Cautions regarding remote control unit

• Do not expose the remote control unit to shock.

In addition, do not expose the remote control unit to liquids, and do not place

in an area with high humidity.

• Do not install or place the remote control unit under direct sunlight.

The heat may cause deformation of the unit.

• The remote control unit may not work properly if the remote sensor window of

the Plasma Display TV (Panel Unit) is under direct sunlight or strong lighting.

In such case, change the angle of the lighting or Plasma Display TV , or operate

the remote control unit closer to the remote sensor window.

Inserting the batteries

If the remote control unit fails to operate Plasma Display TV functions, r eplace the batteries in the remote control

unit.

1

Open the battery cover.

2

Insert batteries (two AA size

batteries, supplied with product).

+

_

• Place batteries with their terminals

corresponding to the (e) and (f)

indications in the battery compartment.

_

+

3

Close the battery cover.

Cautions regarding batteries

Improper use of batteries can result in chemical leakage or explosion. Be sur e to follow the instructions below.

• Do not use manganese batteries. When you replace the batteries, use alkaline ones.

• Place the batteries with their terminals corresponding to the (e) and (f) indications.

• Do not mix batteries of different types. Different types of batteries have different characteristics.

• Do not mix old and new batteries. Mixing old and new batteries can shorten the life of new batteries or cause

chemical leakage in old batteries.

• Remove batteries as soon as they have worn out. Chemicals that leak from batteries can cause a rash. If you

find any chemical leakage, wipe thoroughly with a cloth.

• The batteries supplied with this product may have a shorter life expectancy due to storage conditions.

• If you will not be using the remote control unit for an extended period of time, remove the batteries from it.

• WHEN DISPOSING OF USED BATTERIES, PLEASE COMPLY WITH GOVERNMENTAL REGULATIONS OR

ENVIRONMENTAL PUBLIC INSTRUCTION'S RULES THAT APPLY IN YOUR COUNTRY/AREA.

8

Page 9

PZ-43MR2E

L

PZ-50MR2E

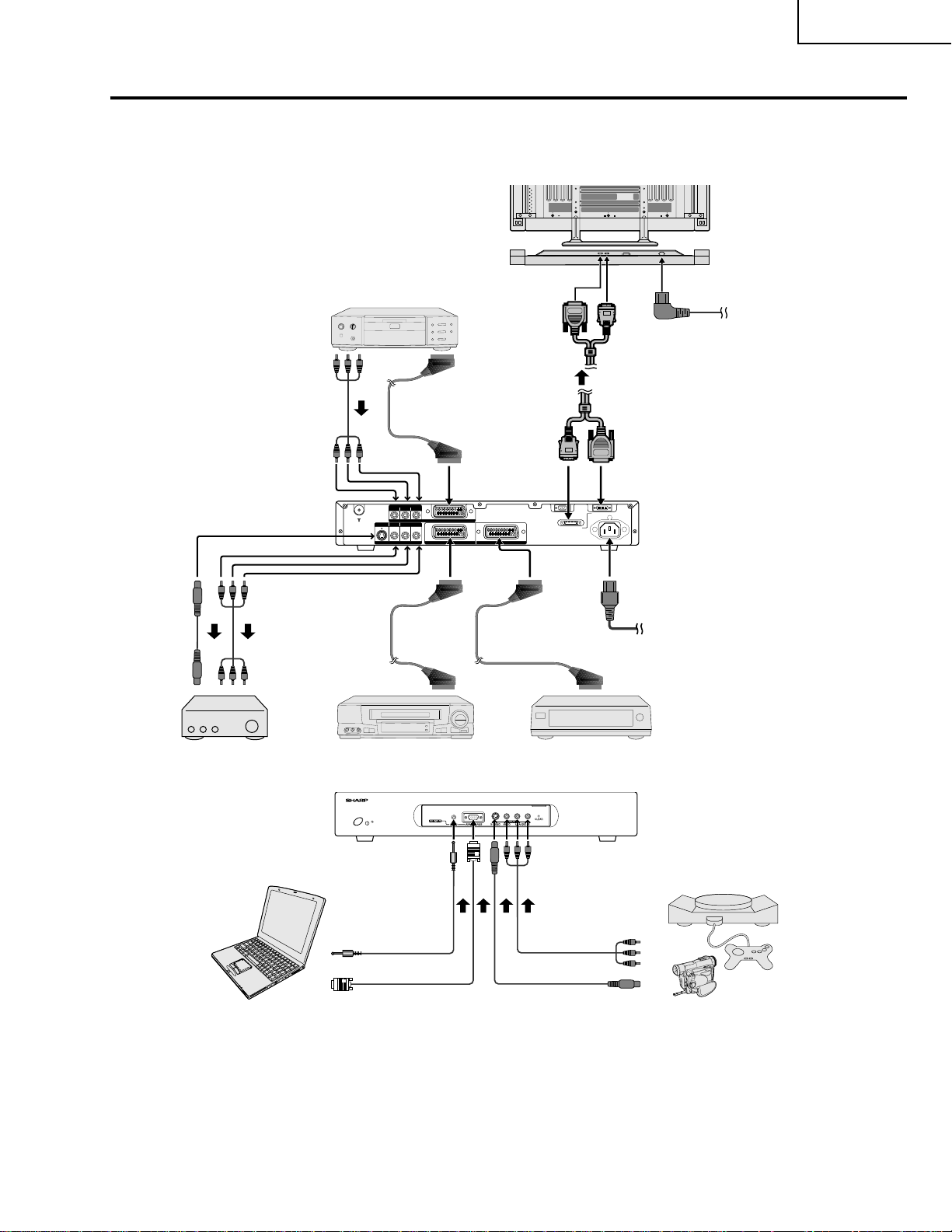

Using external equipment

Y ou can connect many types of external equipment to your Plasma Display TV, like a decoder, VCR, DVD player ,

computer, game console and camcorder. T o view external source images, select the input sour ce fr om b on

the remote control unit or INPUT on the Plasma Display TV (Panel Unit).

Plasma Display TV

(Panel Unit)

(rear view)

(bottom view)

DVD player

Power cord

AV Receiver

(Built-in T uner Amp)

S-VIDEO VIDEO

VCR

AV OUTPUT

COMPONENT

PB(CB)

R - AUDIO - L

PR(CR)Y

INPUT 3

INPUT 2 INPUT 1

RS-232C DISPLAY OUTPUT-1

DISPLAY OUTPUT-2

Decoder

AVC System

(rear view)

AC INPUT

220–240V

Power cord

AVC System

(front view)

Computer

Game console/Camcorder

• To protect all equipment, always turn off the AVC System before connecting to a decoder, VCR, DVD player, computer,

game console, camcorder or other external equipment.

• The S-video signal only outputs when “Input 2” or “Input 3” is selected for “Y/C”, or when from the INPUT 4 terminal (SVIDEO). Only the S-video signal can output from the INPUT 4 terminal (S-VIDEO).

A

• Please refer to the relevant operation manual (DVD player, computer, etc.) carefully before making connections.

9

Page 10

PZ-43MR2E

PZ-50MR2E

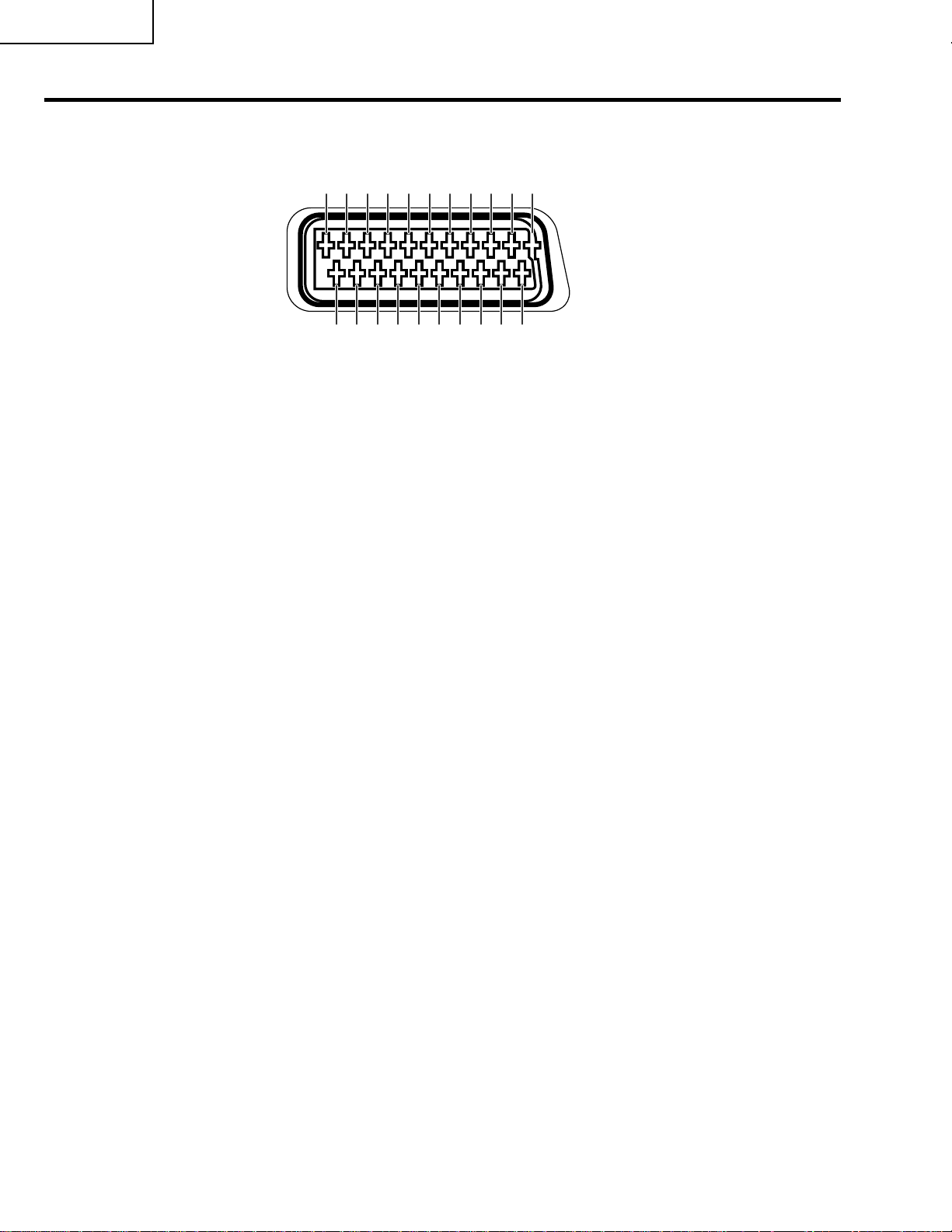

Appendix

Connecting pin assignments for SCART

Various audio and video devices may be connected via the SCART terminals.

13579111315171921

2468101214161820

SCART (INPUT 1)

1. Audio right output

(TV Monitor out)

2. Audio right input

3. Audio left output

(TV Monitor out)

4. Common earth for audio

5. Earth for blue

6. Audio left input

7. Blue input

8. Audio-video control

9. Earth for green

10. Not used

11. Green input

12. Not used

13. Earth for red

14. Not used

15. Red input

16. Red/Green/Blue control

17. Earth for video

18. Earth for Red/Green/Blue

control

19. Video output

(TV Monitor out)

20. Video input

21. Plug shield

SCART (INPUT 2)

1. Audio right output

2. Audio right input

3. Audio left output

4. Common ear th for audio

5. Earth

6. Audio left input

7. Not used

SCART (INPUT 3)

1. Audio right output

2. Audio right input

3. Audio left output

4. Common earth for audio

5. Earth

6. Audio left input

7. Blue input

8. Audio-video control

9. Earth

10. AV LINK control

11. Not used

12. Not used

13. Earth

14. Not used

8. Audio-video control

9. Earth

10. Not used

11. Green input

12. Not used

13. Earth

14. Not used

15. Chroma S-Video input

16. Not used

17. Earth for video

18. Earth

19. Video output

20. Video input/S-video input

21. Plug shield

15. Red input/Chroma S-Video

input

16. Red/Green/Blue control

17. Earth for video

18. Earth

19. Video output

20. Video input/S-video input

21. Plug shield

10

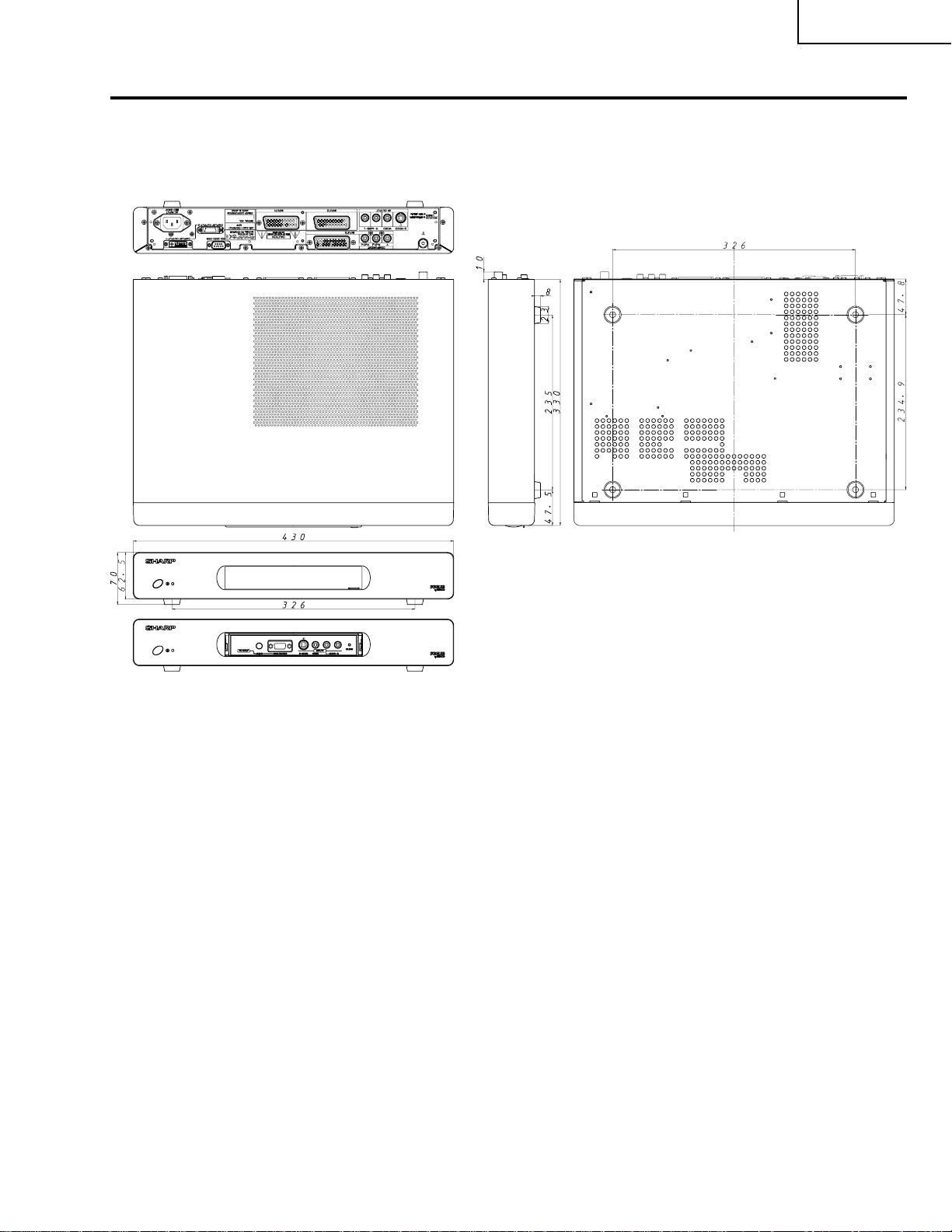

Page 11

Dimensions

PZ-43MR2E

PZ-50MR2E

(Unit: mm)

11

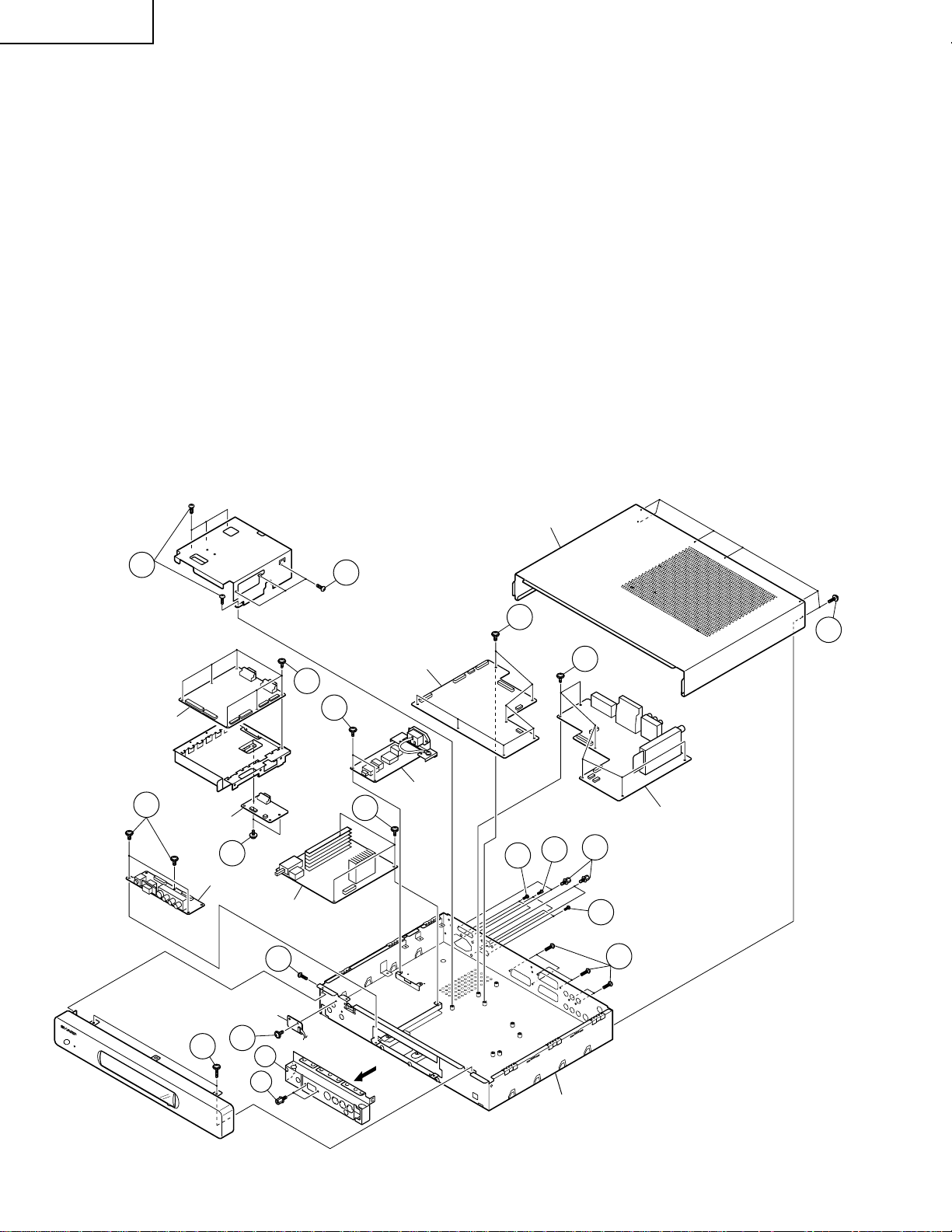

Page 12

PZ-43MR2E

PZ-50MR2E

REMOVING OF MAJOR PARTS

1. Remove the six lock screws from the back of the top cabinet. Slide the top cabinet backward and detach it.

2. Remove the three lock screws from the front panel. Undo the three hooks at the top and the four hooks at the

bottom, and detach the front panel.

3. Remove the two hexagonal shafts from the front shield. Undo the two hooks on both sides and detach the

front shield.

4. Remove the three lock screws from the front unit and detach this unit.

5. Remove the one lock screw from the LED unit and detach this unit.

6. Remove the PC I/F unit and SR unit assemblies.

6-1. Remove the two hexagonal shafts each from the system cable (white) terminal and the RS-232C terminal,

both on the PC I/F unit.

6-2. Remove two lock screws from the system cable (gray) terminal also on the SR unit.

6-3. Remove the two lock screws from the PC I/F unit bracket.

6-4. Remove the four lock screws from the PC I/F unit and SR unit assemblies. Take out these assemblies.

6-5. Remove the three lock screws from the brackets of the PC I/F unit and SR unit assemblies. Detach the

shield.

6-6. Remove the six lock screws from the PC I/F unit. Detach this unit from the bracket.

6-7. Remove the two lock screws from the SR unit. Detach this unit from the bracket.

7. Remove the seven lock screws from the main unit and detach this unit.

6-4

PC I/F Unit

4

SR Unit

6-7

Front Unit

6-6

Power Unit

2

9-2

6-5

10

Main Unit

EMC Unit

Top Cabinet

7

9-1

6-3

1

8-2

AV Unit

6-1

6-2

8-1

2

LED Unit

5

11

10

Bottom Cabinet

12

Page 13

8. Remove the AV unit.

8-1. Remove the six lock screws from the AV unit.

8-2. Remove the six lock screws from the AV unit and detach this unit.

9. Remove the EMC unit assemblies.

9-1. Remove the two lock screws from the EMC unit bracket.

9-2. Remove the two lock screws from the EMC unit and detach this unit.

10. Remove the three lock screws from the power unit and detach this unit.

PZ-43MR2E

PZ-50MR2E

13

Page 14

PZ-43MR2E

PZ-50MR2E

ADJUSTMENT PROCEDURES

Ë

Procedure for turning ON the power

1. Connecting the system

» Using the system cable, connect the Panel Unit and the AVC System.

» Connect the Panel Unit to the AC power source.

» Connect the AVC System to the AC power source.

2. Procedure for turning ON the power

» Turn ON the AC power switch located on the Panel Unit.

The STANDBY/ON indicator on the Panel Unit will start blinking in red.

(When the AC POWER button on the AVC System is not ON, the STANDBY/ON indicator on the Panel Unit

always blinks in red.)

» Turn ON the POWER button located on the AVC System.

The ST ANDBY/ON indicator on the AVC System will be illuminated in green. Simultaneously , the power indicator

on the Panel Unit will change from blinking in red to illumination in green. Now the system has started up.

» If the STANDBY/ON indicator on the AVC System is illuminated in red, press the POWER button located on the

remote control unit and the MAIN POWER button located on the Panel Unit. The STANDBY/ON indicators on

the Panel Unit and the AVC System will change from red to green. Now the system has started up.

Ë

Procedure for upgrading the software

(1)With the power being OFF, open the top cabinet for the AVC System and then set the slide switch from the

NORMAL position to the WRITE position by inserting a needle-like insulator into the cutout located between

the WHITE port on the rear of the shield case for the PC I/F unit and the RS-232C port.

(2)Connect the PC having the program installed, to the AVC System using the cross cable for the RS-232C port

(for the details of the program, see Appendix).

(3)Open the MS-DOS window on the PC and then go to the directory in which the software is installed.

(4)Start up the system to which the AVC System and Panel Unit have been connected.

(5)Run “vup.bat (tentaive name)” at the MS-DOS prompt. The software will be upgraded.

(6)Load the file “civc_XXXXa.bhxmain.bhxosd.bhxt (tentaive name)”. It will take approximately a few minutes

until the file has been loaded. Never turn OFF the power or operate the system during this rewriting period.

(7)After the file has been loaded, turn OFF the Panel Unit and the AVC System and then return the slide switch in

the above step 1 from the WRITE position to the NORMAL position. Now the software has been upgraded.

Ë

Procedure for adjusting each part of AVC System

» The adjustments were made to the best settings at factory. If any setting deviates or if any readjustment is

regarded as necessary when any part is replaced, perform the following steps.

» Any parameter that has been changed within the process adjustment is stored on the memory . If any readjustment

is required, write down the current value before changing it.

» Use a stable AC power source.

» If the program is upgraded, it will take approximately 1 minute for the EEPROM to be initialized before any video

appears. Therefore, you will need to wait for this time period. Do not turn OFF the power or operate the system

during the period.

» If the program is rewritten, write down the parameters that have been changed within the process adjustment

(see “5”.OSD menu and parameters displayed at manual adjustment), initialize the EEPROM, and then reenter

the recorded values.

14

Page 15

3. Entering a special mode

1 Entering the process adjustment mode

[Steps]

(1)When using the remote control unit:

Using the system cable, properly connect the Panel Unit and the AVC System, and then turn ON the

power.

After the system has started up, press the PROCESS ADJ button located on the remote control unit.

(2)When using buttons on the main unit:

Using the system cable, properly connect the Panel Unit and the AVC System.

Turn ON the power while holding down the INPUT and CH UP buttons located the Panel Unit.

[Description]

Various adjustments can be made manually.

2 Entering the inspection process mode

[Steps]

After the system has started up, press the PROCESS ADJ button located on the remote control unit.

Set the parameter SIGNAL INFO to 1 on page 6 or 7 of the PROCESS ADJUSTMENT A MODE MENU.

Subsequently, make the necessary adjustments in accordance with the above menu.

3 Procedure for setting up delivery

[Steps]

After the system has started up, press the DELIVERY SETUP button located on the remote control unit.

(Within the adjustment process, the channel settings remain unchanged. Once you exit the process adjustment

mode, the channel settings entered in the delivery adjustment mode become valid.)

[Description]

The user’s adjustment parameters and others will be set to the default values. The channel settings will also

be initialized.

PZ-43MR2E

PZ-50MR2E

4. Exiting a special mode

(1)Process adjustment mode: Press the PROCESS ADJ button located on the remote control unit or turn OFF the

power.

(2)Inspection process mode: Set the parameter SIGNAL INFO to 0 on page 6 or 7 of the PROCESS ADJ A MODE

MENU or turn OFF the power.

(3)Delivery setup: After the delivery setup has been finished, the process adjustment mode is automatically

selected. To exit the process adjustment mode, press the PROCESS ADJ button located on the remote control

unit or turn OFF the power.

5. OSD menu and parameters displayed at manual adjustment

* The default values may slightly differ depending upon the program version to be rewritten.

* The settings are not initialized to the default values by merely rewriting the program. (See the paragraph for

Preparation for adjustment.)

(1)Descriptions of special buttons in process adjustment mode

Cursor UP key : Proceeds to the previous page.

Cursor DOWN key: Returns to the next page.

VOL UP key : Increases the adjusted value by 1.

VOL DOWN key : Decreases the adjusted value by 1.

Cursor LEFT key : Decreases the adjusted value by 10.

Cursor RIGHT key : Increases the adjusted value by 10.

CH UP key : Moves up the cursor.

CH DOWN key : Moves down the cursor .

15

Page 16

PZ-43MR2E

PZ-50MR2E

Ë

Organization of process adjustment screen

Page Input Source HDCP

INPUT1 No SIG1/16 HDCP:ON EUROPE EUROPE

Maker Select

Ë +Badj3.3V

Ë +Badj2.5V

KEY WRITE

Ë DATA COPY

INDUSTRY INIT

CENTER Version

OSD Version

CVIC Version

TTXP V ersion

MONITOR Version

PANEL Version

FLASH Version

MONITOR Model

Model Select MONITOR

STANDBY TYPE

SHARP

127

024

OFF

OFF

OFF

MR MAIN E 2001/11/28K

MR OSD 2001/09/10 A

W2001/10/02 17:28 X2001/10/02 V2001/09/12 09:12

TTX PRG 068

F6 91 xx

-00

-05

01

1

0

Destination for MAIN unit Destination for AV unitDistinguish Signal

Parameter display

Ë

+B Adj3.3V

Ë

+B Adj2.5V

Ë

P AL Y CONTRAST

Ë

PAL COLOR GAIN

Ë

MAIN CR GAIN PAL

Ë

MAIN SUBBRIGHT 15K

Ë

MAIN CONTRAST 15K

Ë

SUB P AL Y

Ë

SUB PAL COLOR GAIN

Ë

PEAK ACL SW

Ë

SECAM Y CONTRAST

Ë

SECAM COLOR GAIN

Ë

MAIN CR GAIN SECAM

Ë

N358 Y CONTRAST

Ë

N358 COLOR GAIN

Ë

MAIN CR GAIN N358

Ë

N358 TINT

Ë

COMP 15K Y CONTRAST

Ë

COMP 15K COLOR GAIN

Ë

MAIN CR GAIN COMP15K

Ë

COMP HDTV SUB BRIGHT

Ë

COMP HDTV CONTRAST

Ë

DA TA COPY

Setting range

0 ~ 255

0 ~ 255

0~ 63

0~ 63

0 ~ 255

0~ 63

0~ 15

-30 ~ 30

0~ 63

OFF/ON

0~ 63

0~ 63

0 ~ 255

0~ 63

0~ 63

0 ~ 255

-30 ~ 30

0~ 63

0~ 68

0 ~ 255

0~ 63

0~ 15

OFF/ON

Description

3.3 V adjustment

2.2 V adjustment

P AL Y level adjustment

PAL colour density adjustment

P AL Cr level adjustment

Pedestal level adjustment (15 k)

PCB input amplitude adjustment (15 k)

Sub P AL Y level adjustment

Sub PAL colour density adjustment

SECAM Y level adjustment

SECAM colour density level adjustment

SECAM Cr level adjustment

N358 Y level adjustment

N358 colour density adjustment

N358 Cr level adjustment

N358 tone adjustment

COMP 15 k Y level adjustment

COMP 15 k colour density adjustment

COMP 15 k Cr level adjustment

COMP HDTV black level adjustment

COMP HDTV Y level adjustment

COMP HDTV colour density adjustment

The values for the above parameters should be written down before the EEPROM is replaced on

the AVC system.

Note: The contents on the adjustment process menu may be somewhat different depending on

the program's version-up.

16

Page 17

PZ-43MR2E

PZ-50MR2E

6. Procedures before and after replacing the PC I/F unit

1) Before replacing the PC I/F unit, write down the values for the parameters listed on the 2nd and 3rd pages of

the Adjustment Process A screen.

If the values for the parameters cannot be written down because the PC I/F unit is completely broken or for any

other reason, make all the adjustments in accordance with the paragraph for Adjustment procedure and

parameters, rather than the following procedures. (End)

Set the parameters listed on the 2nd and 3rd pages of the Adjustment Process A screen to the values you have

written down.

7. Adjustment parameters

1) Analog adjustment

(1) Prior adjustment for AVC system chassis

Adjustment item Description Adjustment procedure

1 Destination check 1. Call the process adjustment mode.

2. Check that the destination is “Europe”.

2 AVC center 3.3V

adjustment

3 AVC center 2.5V

adjustment

Connect DC voltmeter to

TP1702.

Connect DC voltmeter to

TP1701.

Adjust output voltage of DC/DC 5 V line to

3.3 V .

Adjusted value: 3.25~3.29 V

Adjust output voltage of DC/DC 2.5 V line to

2.6 V .

Adjusted value: 2.60~2.64 V

(2) PAL signal adjustment

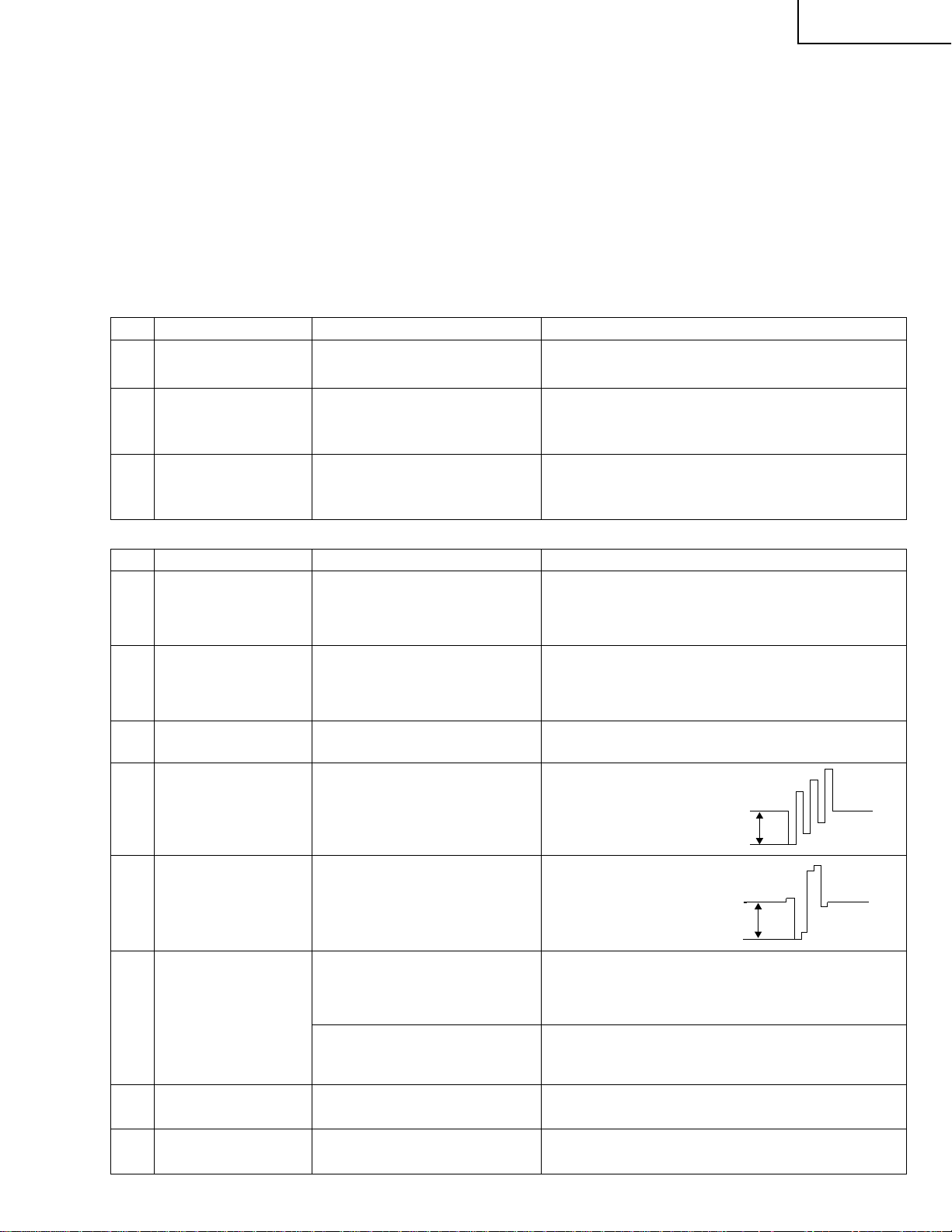

Adjustment item Description Adjustment procedure

1 Setup 1. Set colour system to “PAL”.

2. Select PAL source.

100% colour bar signal including 100% white, such

as split field colour bar

2 Tuner Y level

adjustment

3 PAL Y CONTRAST

adjustment

4 PAL COLOR GAIN

adjustment

1. Adjust TP1101 so that the Y signal without the

chroma component should be 1.00 ±0.05 Vp-p

(between the bottom of sync signal and the white

peak).

1. Adjust TB1274_MAIN output (TP803) to

0.7 ±0.05 Vp-p.

1. Adjust TB1274_MAIN

output (TP802) to

0.35 ±0.025 Vp-p.

0.35V

5 MAIN CR GAIN PAL

adjustment

6 MAIN CONTRAST

adjustment

Press the DUAL screen button. Select the special DUAL screen settings for adjustment

7 SUB PAL Y adjustment 1. Adjust TB1274_SUB output (TP806) to

8 SUB PAL COLOR

GAIN adjustment

1. Adjust TB1274_MAIN output

(TP801) to 0.35 ±0.05 Vp-p.

0.35V

Turn off the PEAK ACL control. Adjust the output

(TP815) of IC810 to have 1.1 ±0.05 Vp-p from the

pedestal level.

(so that the same video source is reflected on MAIN/

SUB).

0.9 ±0.05 Vp-p.

1. Adjust TB1274_SUB output (TP805) to

0.9 ±0.05 Vp-p.

17

Page 18

PZ-43MR2E

0.35V

0.35V

0.35V

0.35V

PZ-50MR2E

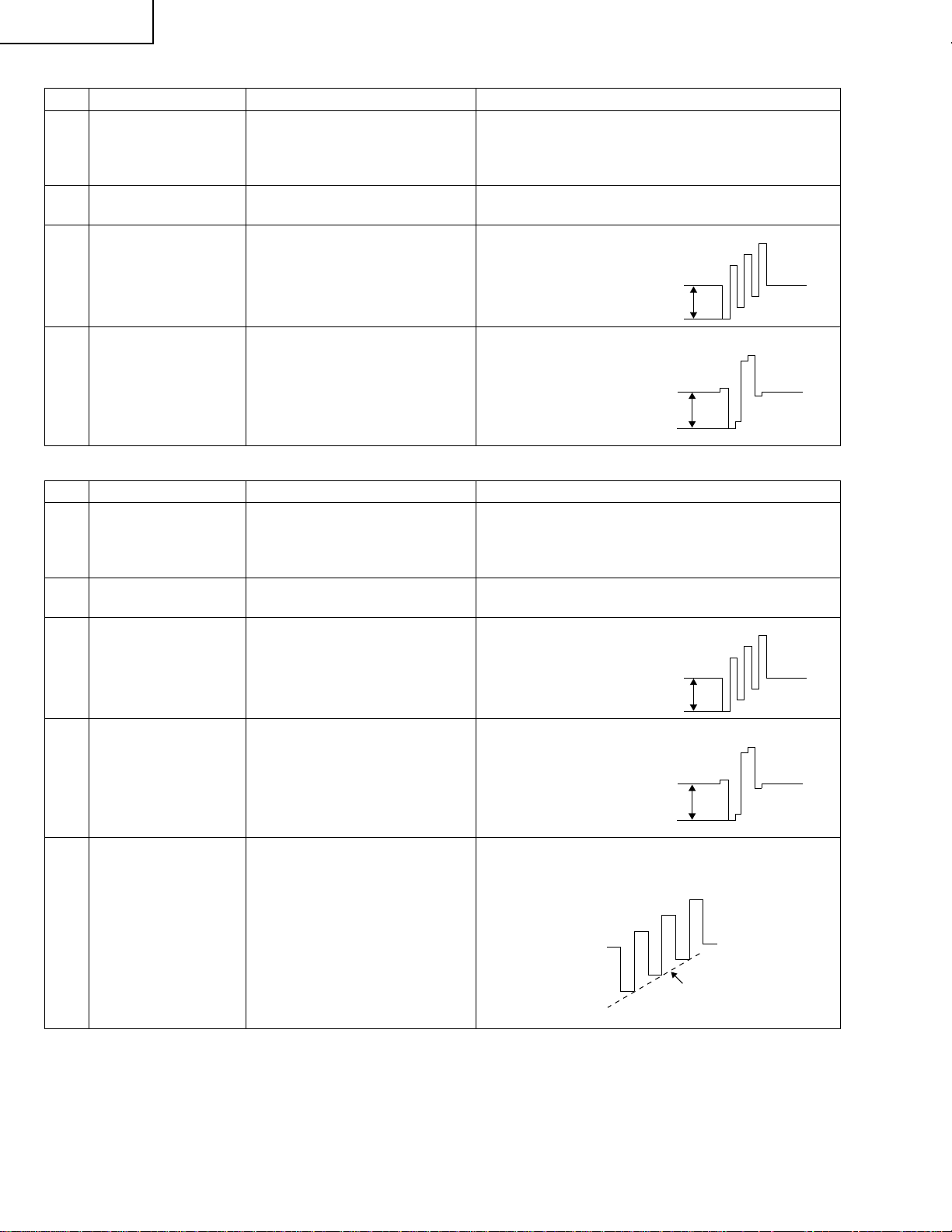

(3) SECAM signal adjustment

Adjustment item Description Adjustment procedure

1 Setup 1. Set colour system to SECAM.

2. Select SECAM source.

100% colour bar signal including 100% white, such

as split field colour bar

2 SECAM Y CONTRAST

adjustment

3 SECAM COLOR GAIN

adjustment

1. Adjust TB1274_MAIN output (TP803) to

0.7 ±0.05 Vp-p.

1. Adjust TB1274_MAIN

output (TP802) to 0.35

±0.025 Vp-p.

4 MAIN CR GAIN

SECAM adjustment

1. Adjust TB1274_MAIN

output (TP801) to 0.35

±0.025 Vp-p.

(4) N358 signal adjustment

Adjustment item Description Adjustment procedure

1 Setup 1. Set colour system to N358.

2. Select N358 source.

100% SMPTE colour bar or similar colour bar

signal including 100% white.

2 N358 Y CONTRAST

adjustment

3 N358 COLOR GAIN

adjustment

4 MAIN CR GAIN N358

adjustment

1. Adjust TB1274_MAIN output (TP803) to

0.7 ±0.05 Vp-p.

1. Adjust TB1274_MAIN

output (TP802) to 0.35

±0.025 Vp-p.

1. Adjust TB1274_MAIN

output (TP801) to 0.35

±0.025 Vp-p.

5 N358 TINT adjustment 1. Adjust TB1274_MAIN output (TP802) so that

waveform becomes as illustrated below:

Smoothed

18

Page 19

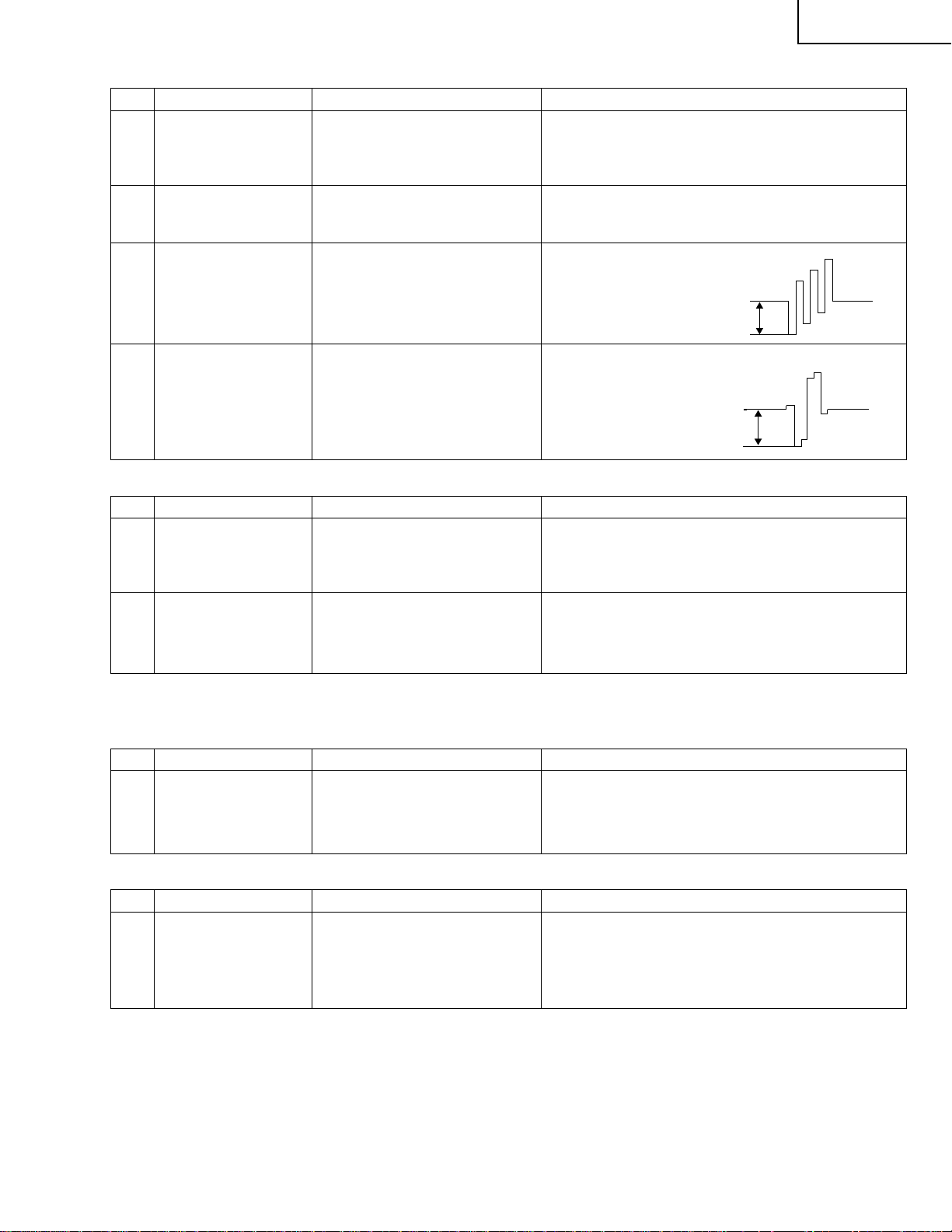

(5) Component 15k Hz signal adjustment

Adjustment item Description Adjustment procedure

1 Setup 1. Select component 15k Hz.

2. Select component source.

100% colour bar signal including 100% white, like

split field colour bar

2 COMP 15k

CONTRAST

adjustment

3 COMP 15k COLOR

GAIN adjustment

Adjust TB1274_MAIN output (TP803) to 0.7 ±0.05 Vp-p.

Adjust TB1274_MAIN output

(TP802) to 0.35 ±0.025 Vp-p.

PZ-43MR2E

PZ-50MR2E

0.35V

4 MAIN CR GAIN COMP

15k adjustment

Adjust TB1274_MAIN output

(TP801) to 0.35 ±0.025 Vp-p.

0.35V

(6) Component HDTV signal adjustment

Adjustment item Description Adjustment procedure

1 Setup 1. Input HDTV (1080i) component signal.

2. Select component source.

100% colour bar signal including 100% white, like

split field colour bar

2 COMP HDTV

CONTRAST

adjustment

Turn off the PEAK ACL control.

Adjust the output (TP815) of pin (11) of IC810 to have

1.1 ±0.05 Vp-p from the pedestal level.

2. Factory settings

(1) Data Copy

Adjustment item Description Adjustment procedure

1 DATA COPY 1. Using the adjustment key, set “ON” in the DATA

COPY line. Wait until “OFF” is displayed instead.

Finally turn off the power to quit the process

adjustment mode.

(2) Factory Setting

Adjustment item Description Adjustment procedure

1 INDUSTRY INIT Move the cursor to the INDUSTRY INIT line. Using the

Vol.UP key, turn off and on again, and press ENTER. "/

/////////" appears, telling that the program is now being

settings are complete. Be sure to wait until the sign

goes out.

* Then turn off the AC power supply of the AVC system. (Be careful not to use the power switches of the remote control unit

and A VC system.)

19

Page 20

PZ-43MR2E

PZ-50MR2E

DESCRIPTION OF MAJOR IC FUNCTIONS

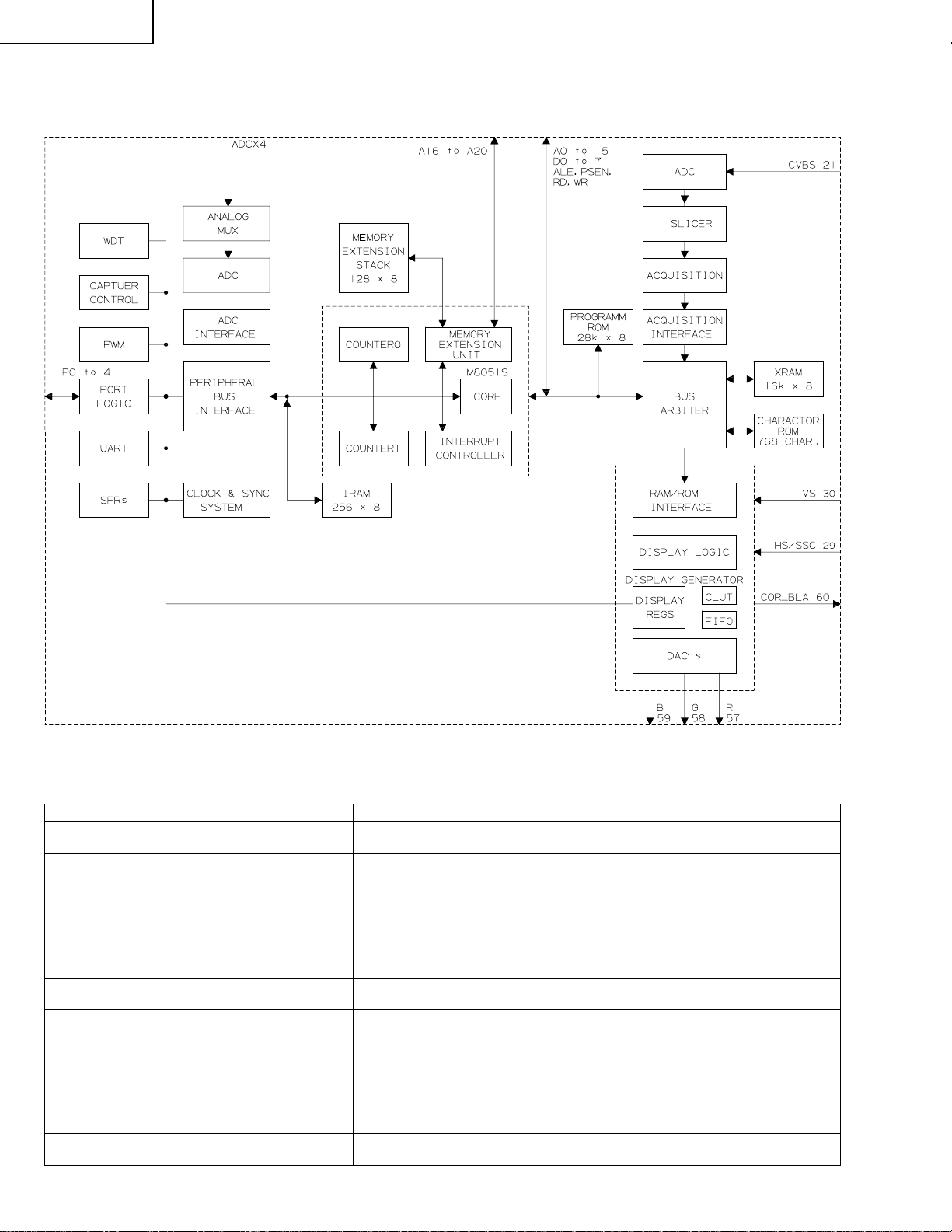

Æ Description of Main ICs

»»

» IC1301 (CXA2069Q)

»»

This IC is a 7-input, 3-output selector.

The video signals other than those for the PC, components and RGB input, which have been input from each input

connector and the tuner, and all the audio signals are sent to the IC1301 and then selected.

Output 1 is used internally and output 3 in the monitor output.

When the S video input is output to the monitor, Y and C signals are mixed in this IC.

The video signals sent to the IC1301 are then input to the YC separation circuits, IC405 (main) and IC402 (sub).

The audio signals are input to the PC I/F Unit via IC2501 (sound processor).

»»

» IC1401 (MM1519XQ)

»»

This IC is a 4-input, 8-output video selector for component input.

The AV3 component input, AV1, RGB input, and Teletext RGB signals are input to the IC1401. The output signals

go to the main, sub, and component channels.

»»

» IC1601 (SDA5550M).

»»

This IC is a microprocessor for Teletext.

Video signals are input to the IC1601, which then decodes the Teletex data and outputs it as RGB data.

»»

» IC2501 (IX3371CE)

»»

This IC is used to decode audio signals.

It serves as both the S IF decoder and the selector for the input audio data.

»»

» IC801/IC802 (TB1274AF)

»»

This IC synchronizes video and chroma signals for PAL/NTSC/SECAM colour televisions.

Its video circuit includes a high-performance image quality compensation circuit and its chroma circuit a PAL/

NTSC/SECAM automatic selection circuit. The P AL-M/N clock signals at 4.43 and 8.58 MHz are internally generated

for colour demodulation.

The PAL/SECAM demodulation circuit uses a base band signal processing system with built-in IH DL and is

therefore adjustment-free.

The IC801/IC802 has 4 lines for YC signal input, 2 lines for RGB signal input, and 2 lines for colour difference

signal input. It receives colour different signals for the main and sub channels from IC405 (main), IC402 (sub), and

IC1401 in the former stage, and provides 1 line for colour difference signal output.

»»

» IC803 (CXA2101Q)

»»

This IC consists of a base band signal processing section for colour different input, an RGB signal processing

section, and a 4-line video switch (including HV synchronizing signal processing).

Input selection is performed by INPUT-SEL (I2C BUS). YCbCr , HD YPbPr , GBR and their respective HV synchronizing

signals are input to each line.

As the multi-scanning compliance range, a horizontal scanning frequency of 15~60 kHz can be input.

»»

» IC1901 (IX3566CE)

»»

This IC is FPGA for the synchronizing system.

It creates sand castle pulses for IC803 and generates horizontal blanking signals.

»»

» IC604 (TA1318AF)

»»

This IC synchronizes TV component signals.

The IC804 incorporates the necessary functions for measuring the frequency of input signals and synchronous

replay into a single chip, and is applicable for horizontal synchronous replay (15.75, 31.5, 33.75, and 45 kHz) and

vertical synchronous replay (525I, 525P, 625I, 750P, 1125I, 1125P, PAL 100 Hz, and NTSC 120 Hz).

20

Page 21

PZ-43MR2E

PZ-50MR2E

»»

» IC405/IC402 (CXD2064Q)

»»

This IC is a comb filter in the applicable field for both the NTSC and P AL systems. It performs the Y/C separation

of the main and sub channel video signals that have been output from IC1801.

»»

» IC407/IC404 (ML6428C1)

»»

This IC is a 6.7 MHz low-pass filter.

»»

» IC810/IC804 (IX3473CE)

»»

This IC is a 6.7 MHz low-pass filter incorporating a 6 dB amplifier.

»»

» IC811 (IX3474CE)

»»

This IC is a 30 MHz low-pass filter incorporating a 6 dB amplifier.

»»

» IC1702 (FA3675CE)

»»

This IC is designed to control the 6-channel PWM switching regulator.

With 5 step-up switching regulator lines incorporated, the IC converts +10V to +2.5V, +3.3V and +5.8V.

Also with a step-down switching regulator line incorporated, the IC converts +10V to +6.0V , -5.0V, +12V and +35V .

The lines are individually turned on and off.

Æ

Description of Functions of Main ICs on PC I/F Unit

»»

» IC4 (CXA3506R)

»»

This IC is an A/D converter that incorporates a 3-channel, 8-bit, 120 MSPS amplifier and PLL. It is used for the

video signals input to the PC I/F unit on the main channel in the 1-screen and 2-screen modes, and also for the

video signals input from the front for the PC.

The video signals (analog RGB) from the CN6 are input to IN1 of IC4.

For the PC, the video signals (analog RGB) from CN8 are input to IN2 of IC4.

The input video signals are converted into digital signals and then sent to IC25.

»»

» IC310 (TLC5733A)

»»

This IC is a 3-channel, 8-bit, 20 MSPS A/D converter.

It is used for the sub-channel of the video signals input to the PC I/F Unit in the 2-screen mode.

The video signals (analog Y, Cb, Cr) from CN6 are input to IC310.

The video signals input to this IC are converted into digital signals and then sent to IC25.

»»

» IC25 (IX3434CE)

»»

This IC performs the I/P conversion and scaling to match the digitalized video with the output resolution, and also

the data conversion.

It has two input lines, V0 and V1. The V0 line is used to process the RGB, composite, and skirt signals input to the

480i and 580i components for the sub-channel in the 2-screen mode. The V1 line is used to process all the signals

as well as V1 for the main channel in the 1-screen and 2-screen modes.

The IC25 detects what resolution is input from the input synchronizing signal; creates H synchronization in

accordance with the frequency division ratio; creates the clamp signal in accordance with the input synchronizing

signal; and performs the data matrix conversion.

The video signals input to this IC is sent to IC413.

»»

» IC413 (SiI168)

»»

This IC is a panel link transmitter.

It converts the 8-bit RGB video data output from IC25 into the differential TMDS signals and then digitally transmits

the converted signals to the monitor.

The TMDS signals are transmitted at the frequency 10 times higher than the clock frequency.

»»

» IC1 (IX3270CE)

»»

This IC is a 1-chip RISC microprocessor.

It performs communication with the monitor and operates the system.

The IC1 also controls each IC in the AVC system and partially manages the power source.

»»

» IC405 (uPD4721)

»»

This IC is an RS-232 line driver receiver conforming to the EIA/TIA-232-E standard.

The IC405, when connected to a PC, allows for externally controlling the system.

It is also applicable for upgrading IC1.

21

Page 22

PZ-43MR2E

PZ-50MR2E

» The information shown in the list is basic information and may not correspond exactly to that shown in the schematic diagrams.

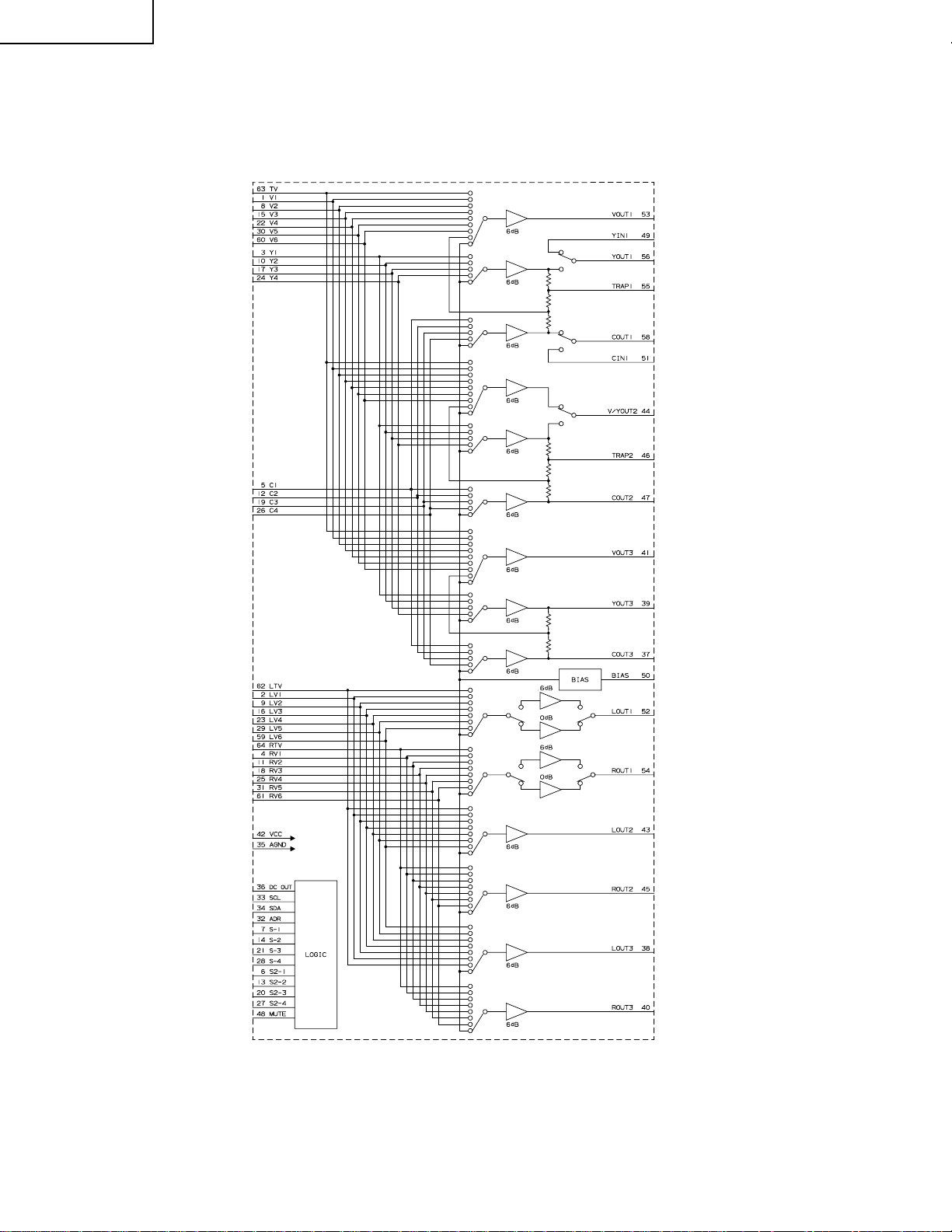

Ë VHiCXA2069Q-1 (ASSY: IC1301)

» S2-Compatible, 7-Input/3-Ouput AV Switch

» Block Diagram

22

Page 23

» Pin Function

Pin No. Pin Name I/O Pin Function

63

1

8

15

22

30

60

3

10

17

24

49

5

12

19

26

51

62, 2

9, 16

23, 29

59, 64

4, 11

18, 25

31, 61

53

41

44

56

39

58

47

37

52

43

38

54

45

40

6

13

20

27

7

14

21

28

32

33

34

36

55

46

48

50

TV

V1

V2

V3

V4

V5

V6

Y1

Y2

Y3

Y4

YIN1

C1

C2

C3

C4

CIN1

LTV, LV1

L V2, LV3

L V4, LV5

L V6, RTV

RV1, RV2

RV3, RV4

RV5, RV6

VOUT1

VOUT3

V/YOUT2

YOUT1

YOUT3

COUT1

COUT2

COUT3

LOUT1

LOUT2

LOUT3

ROUT1

ROUT2

ROUT3

S2-1

S2-2

S2-3

S2-4

S-1

S-2

S-3

S-4

ADR

SCL

SDA

DC OUT

TRAP1

TRAP2

MUTE

BIAS

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

O

I

I

I

I

Video signal input.

Composite video signal input

Y/C-separated signal input terminal for luminance signal input.

YIN1 to feed in the Y/C-separated signal of VOUT1 output.

Y/C-separated signal input terminal for chrominance signal input.

CIN1 to feed in the Y/C-separated signal of VOUT1 output.

Audio signal input terminal.

Video signal output terminal for composite video signal output.

Video signal output terminal for selection between composite video signal output and

luminance signal output by I2C Bus control.

Video signal output terminal for luminance signal output.

Video signal output terminal for chrominance signal output.

Audio signal output terminal.

Used to detect C signal-superimposed, S2-compatible DC level. 4:3 video signal when

below 1.3V. 4:3 letterbox signal when between 1.3V and 2.5V . 16:9 image squeeze

signal when above 2.5V. To be pulled down to GDN at 100KΩ to produce 4:3 video

signal when open.

Used to switch between composite video and S signals. Detection results to be written

in status register. S signal when below 3.5V. Composite video signal when above 3.5V.

To be pulled up to 5V at 100KΩ to produce composite video signal when open.

Used to select I2C Bus slave address. 90H when below 1.5V. 92H when above 2.5V.

90H also when the terminal is open.

I2C Bus signal input terminal.

I2C Bus signal input terminal.

Used to feed out S2-compatible DC level to be superimposed on COUT3 output. DC to

be superimposed by connecting to COUT3 output via a capacitor. Control to be made

by I2C Bus. S2-specified output impedance of 10 ±3KΩ to be realized by adding an

external resistance of 4.7KΩ.

Subcarrier trap circuit to be connected.

Audio signal output mute terminal. Mute off when below 1.3V. Mute on when above

2.5V. Mute off when the terminal is open.

Internal reference bias (Vcc/2) terminal. To be connected to GND with a capacitor in

between.

PZ-43MR2E

PZ-50MR2E

23

Page 24

PZ-43MR2E

PZ-50MR2E

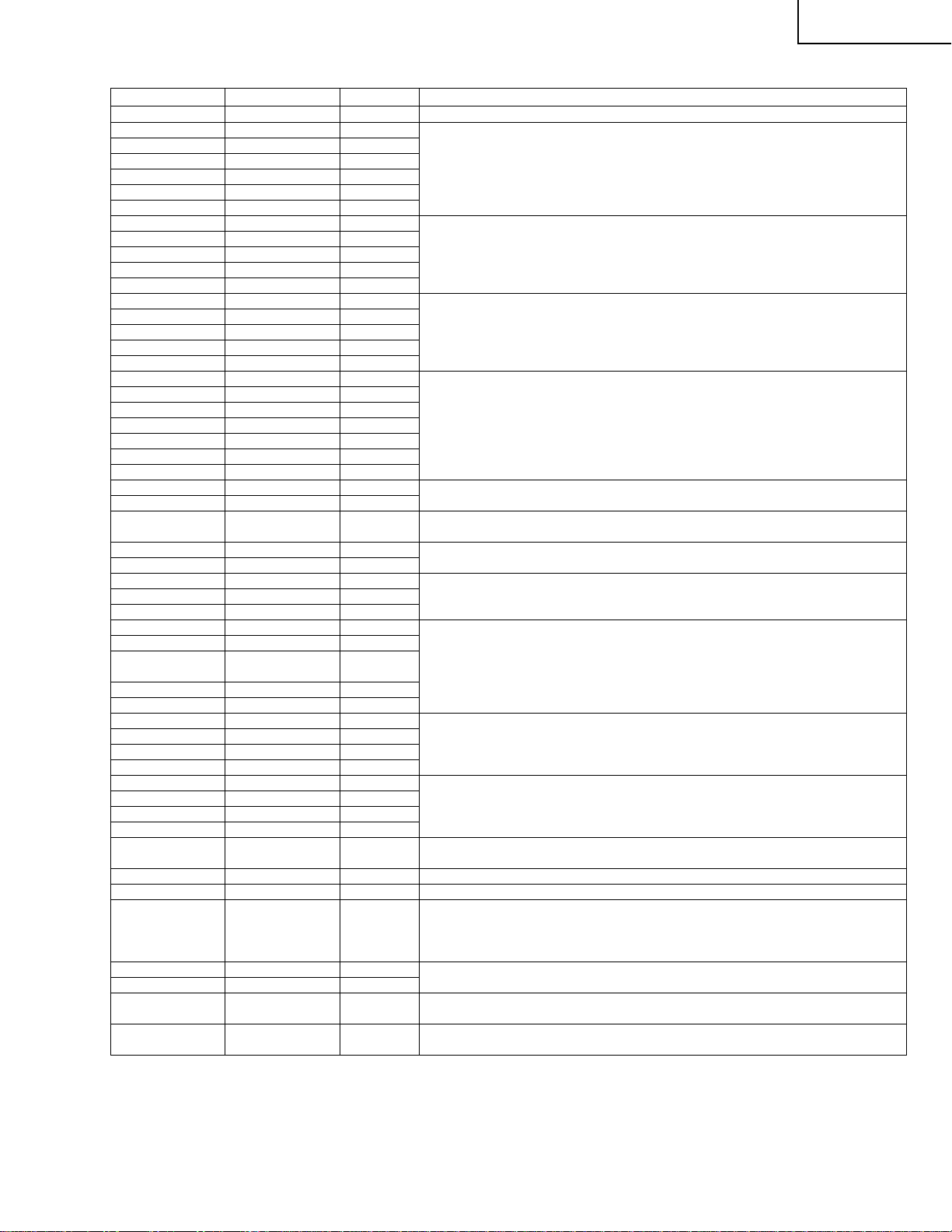

Ë VHiMM1519XQ-1(IC1401)

» Component Input Video Switch

» Block Diagram

24

Page 25

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

11

12

13

21

22

23

4, 14, 39, 45, 52,

58

51

5

15

53

59

24

6, 8, 16, 18, 33,

35, 37, 41, 43, 47,

49, 54, 56, 60, 62

7

9

17

19

55

57

61

63

10

20

32

64

25

26

27

28

29

30

31

34

36

38

40

42

44

46

48

50

VIDEO 1-L1

VIDEO 1-L2

VIDEO 1-L3

VIDEO 2-L1

VIDEO 2-L2

VIDEO 2-L3

VIDEO 3-L1

VIDEO 3-L2

VIDEO 3-L3

VCC

AVCC

VIDEO 2-Y

VIDEO 3-Y

TUNER-Y

VIDEO 1-Y

DGND

GND

VIDEO 2-Pb

VIDEO 2-Pr

VIDEO 3-Pb

VIDEO 3-Pr

TUNER-Pb

TUNER-Pr

VIDEO 1-Pb

VIDEO 1-Pr

VIDEO 2-SW

VIDEO 3-SW

MONO-SW

VIDEO 1-SW

ADDRESS

SDA

SCL

DVCC

L3 OUT

L2 OUT

L1 OUT

Pr OUT 3

Pb OUT 3

Y OUT 3

Pr OUT 2

Pb OUT 2

Y OUT 2

Pr OUT 1

Pb OUT 1

Y OUT 1

—

—

—

—

I/O

—

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

O

O

O

O

Line input of D-terminal

Analog power supply (9V)

Y -signal input

GND

Pb, Pr signal input

Switch line of D-terminal

Slave address select pin

Data input of I2C bus

Clock input of I2C bus

Digital power supply (5V)

Line output for monitor

Video signal output

PZ-43MR2E

PZ-50MR2E

25

Page 26

PZ-43MR2E

PZ-50MR2E

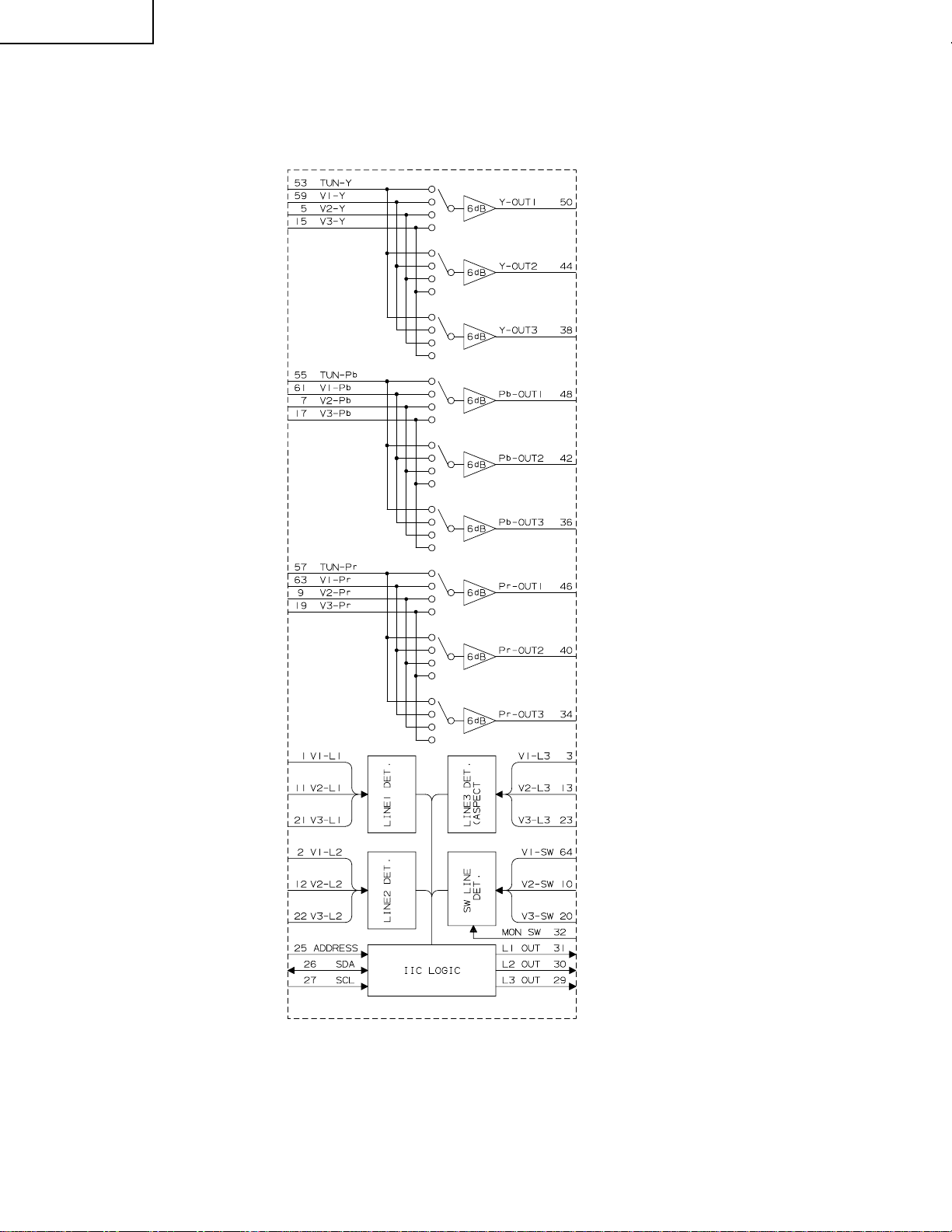

Ë VHiSDA5550M-1 (ASSY: IC1601)

» Stereo Audio DAC

» Block Diagram

» Pin Function

Pin No. Pin Name I/O Pin Function

99, 1, 3, 4, 2, 100,

98, 96

97, 94, 93, 89, 86,

84, 82, 79, 81, 83,

90, 85, 77, 78, 76,

71, 69

70, 68, 67

9, 10, 11, 12, 13,

14, 15, 16

41, 42, 43, 44, 45,

46, 47, 62

24, 25, 26, 27

D0-D7

A0-A16

A17-A19/

P4.0, P4.1, P4.4

P0.0-P0.7

P1.0-P1.7

(PWM)

P2.0-P2.3

(ADC)

I/O

O

I/O

I/O

I/O

Data bus for external memory or data RAM.

Address bus for external program memory or data RAM.

After power-on P4.0,P4.1,P4.4 work as additional address lines A17…A19.

In port mode, these port lines act as bi-directional I/O port with internal pull-up

resistors. Port pins that have ‘1’ written to them are pulled high by the internal pull-up

resistors and in that state can be used as inputs.

Port 0 is a 8-bit open drain bi-directional I/O-port. Port 0 pins that have 1 written to

them float: in this state they can be used as high impedance inputs.

Port is a 8-bit bi-directional multifunction I/O port with internal pull-up resistors. Port 1

pins that have 1 written to them are pulled high by the internal pull-up resistors and in

that state can be used as inputs.

The secondary functions of port 1 pins are:

Port bits P1.0-P1.5 contain the 6 output channels of the 8-bit pulse width modulation

unit.

Port bits P1.6-P1.7 contain the two output channels of the 14-bit pulse width

modulation unit.

I

Port 2 is a 4-bit input port without pull-up resistors.

Port 2 also works as analog input for the 4-channel-ADC.

26

Page 27

» Pin Function

Pin No. Pin Name I/O Pin Function

31, 32, 33, 34, 35,

36, 37, 38

48, 49

5

17

18

19

20

21

29

30

50

52

53

57

58

59

60

64

65

72

80

87

88

95

6, 73

22, 56

8, 40, 75, 92

7, 39, 74, 91,

23, 55

28, 51, 54, 61, 63,

66

P3.0-P3.7

P4.2-P4.3(P4.7)

XROM

ENE

STOP

OCF

EXTIF

CVBS

HS/SC

VS/P4.7

RST

XT AL2

XT AL1

R

G

B

BLANK/COR

WR

RD

FL_PGM

FL_RST

ALE

PSEN

FL_CE

VDD2.5

VDDA2.5

VDD3.3

VSS

VSSA

—

I/O

I/O

I/O

—

—

—

—

—

—

—

Port 3 is an 8-bit bi-directional I/O port with internal pull-up resistors, Port 3 pins that

have 1 written to them are pulled high by the internal pull-up resistors and in that state

can be used as inputs,

To use the secondary functions of Port 3, the corresponding output latch must be

programmed to a one (1) for that function to operate. The secondary functions are as

follows:

» Alternate function

P3.0 : ODD/EVEN indicate output

P3.1 : external extra interrupt 0 (INTX0)/UART(TXD)

P3.2 : interrupt 0 input/timer 0 gate control input)INT0)

P3.3 : interrupt 1 input/timer 1 gate control input)INT1)

P3.4 : counter 0 input (T0)

P3.5 : counter 1 input (T1) or In master mode HS or VCS output.

P3.7 : external extra interrupt 0 (INTX1)/UART (RXD)

Port 4 is a bi-directional I/O port with internal pull-up resistors.

Port 4 pins that have 1 written to them are pulled high by the internal pull-up resistors

and in that state can be used as inputs.

Secondary functions

P4.2: RD, Read line. This signal is same as the to output of the pin RD available in

some packages.

P4.3: WR write line. This signal is same as the output of the pin WE, which is only

I

I

I

O

I

I

I

O

I

O

O

O

O

O

O

I

I

O

O

I

available in some package.

This pin must be pulled low to access external ROM.

Enable Emulation

Only if this pin set to zero externally, STOP and OCF are operational. ENE has an

internal pull-up resistor which switches automatically to non-emulation mode if ENE is

not connected.

STOP

Emulation control line; Driving a low level during the input phase freezes the real time

relevant internal peripherals such as timers and interrupt controller.

Opcode Fetch

Emulation control line; A high level driven by the controller during output phase

indicates the beginning of a new instruction.

CVBS input for the acquisition circuit.

In slave mode Horizontal sync input or sandcastle input for display synchronization .In

master mode HS or VCS output.

Vertical sync input/output for display synchronization.

Can also be used as digital input P4.7.

Furthermore this pin can be selected as an ODD/EVEN indicator alternatively to P3.0.

A low level on this pin resets the device. An internal pull-up resistor permits power-on

reset using only one external capacitor connected to Vss.

Output of the inverting oscillator amplifier.

Input of the inverting oscillator amplifier.

Red

Green

Blue

Contrast reduction and blanking.

Control output; indicates a write access to the internal XRAM; can be used as a write

strobe for writing data into an external data RAM by a MOVX instruction.

This signal is also available as P4.3.

Control output; indicates a read access to the internal XRAM; can be used for latching

data from the data bus into an external data RAM by a MOVX instruction.

This signal is also available as P4.2.

All the pins prefix by Flax are test pins which must be left open.

All the pins prefix by Flax are test pins which must be left open.

Address Latch Enable.

Program Store Enable

is a control output signal which is usually connected to OE input line of the external

program memory to enable the data output.

All the pins prefix by Flax are test pins which must be left open.

Supply voltage (2.5V).

Supply voltage for analog components (2.5V).

Input/output (3.3V).

Ground (0V).

Ground for analog components.

PZ-43MR2E

PZ-50MR2E

27

Page 28

PZ-43MR2E

PZ-50MR2E

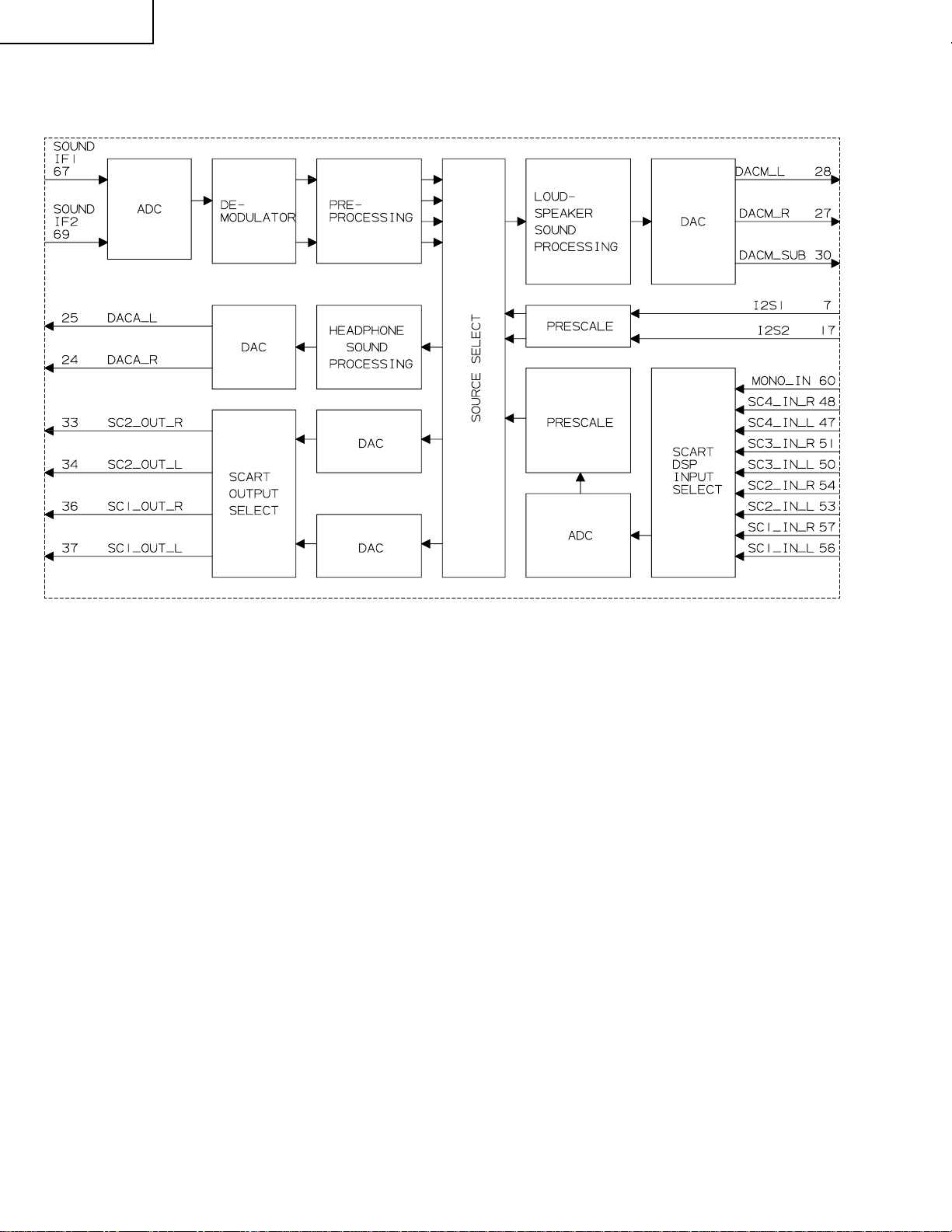

Ë RH-iX3371CEZZ (ASSY: IC2501)

» Multi Standard Sound Processor

» Block Diagram

28

Page 29

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

4

5

6

7

8

9

10

11, 12, 13

14, 15, 16

17

18, 19, 20

21

22, 23

24

25

26

27

28

29

30

31, 32

33

34

35

36

37

38

39

40

41, 42

43, 44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61, 62

63, 64

65, 66

67

68

69

70

71

72

73

74

75, 76

77

78

79

80

NC

I2C_CL

I2C_DA

I2S_CL

I2S_WS

I2S_DA_OUT

I2S_DA_IN1

ADR_DA

ADR_WS

ADR_CL

DVSUP

DVSS

I2S_DA_IN2

NC

RESETQ

NC

DACA_R

DACA_L

VREF2

DACM_R

DACM_L

NC

DACM_SUB

NC

SC2_OUT_R

SC2_OUT_L

VREF1

SC1_OUT_R

SC1_OUT_L

CAPL_A

AHVSUP

CAPL_M

NC

AHVSS

AGNDC

NC

SC4_IN_L

SC4_IN_R

ASG4

SC3_IN_L

SC3_IN_R

ASG2

SC2_IN_L

SC2_IN_R

ASG1

SC1_IN_L

SC1_IN_R

VREFTOP

NC

MONO_IN

AVSS

NC

AVSUP

ANA_IN1+

ANA_INANA_IN2+

TESTEN

XTAL_IN

XTAL_OUT

TP

AUD_CL_OUT

NC

D_CTR_I/O_1

D_CTR_I/O_0

ADR_SEL

STANDBYQ

—

I/O

I/O

I/O

I/O

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

I/O

I/O

Not connected

I2C clock

I2C data

I2S clock

O

I

O

O

O

I

I

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

I

I

I2S word strobe

I2S data output

I2S1 data input

ADR data output

ADR word strobe

ADR clock

Digital power supply 5V

Digital ground

I2S2-data input

Not connected

Power-on-reset

Not connected

Headphone out, right

Headphone out, left

Reference ground 2

Loudspeaker out, right

Loudspeaker out, left

Not connected

Subwoofer output

Not connected

SCART 2 output, right

SCART 2 output, left

Reference ground 1

SCART 1 output, right

SCART 1 output, left

Volume capacitor AUX

Analog power supply 8V

Volume capacitor MAIN

Not connected

Analog ground

Analog reference voltage

Not connected

SCART 4 input, left

SCART 4 input, right

Analog Shield Ground 4

SCART 3 input, left

SCART 3 input, right

Analog Shield Ground 2

SCART 2 input, left

SCART 2 input, right

Analog Shield Ground 1

SCART 1 input, left

SCART 1 input, right

Reference voltage IF A/D converter

Not connected

Mono input

Analog ground

Not connected

Analog power supply 5V

IF input 1

IF common(can be left vacant, only if IF input 1 is also not in use)

IF input 2(can be left vacant, only if IF input 1 is also not in use)

Test pin

Crystal oscillator

Test pin

Audio clock output (18.432MHz)

Not connected

D_CTR_I/O_1

D_CTR_I/O_0

I2C Bus address select

Stand-by (low-active)

PZ-43MR2E

PZ-50MR2E

29

Page 30

PZ-43MR2E

PZ-50MR2E

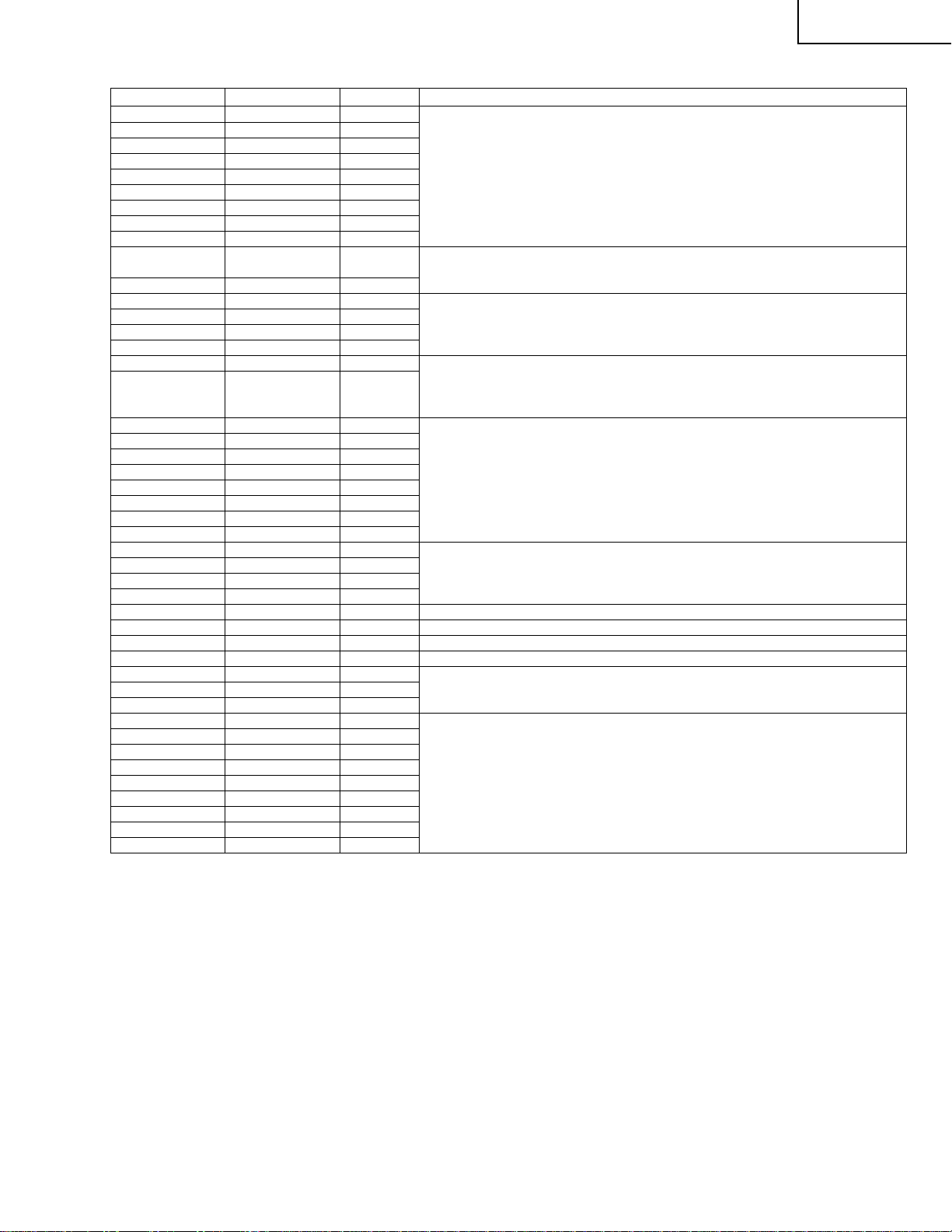

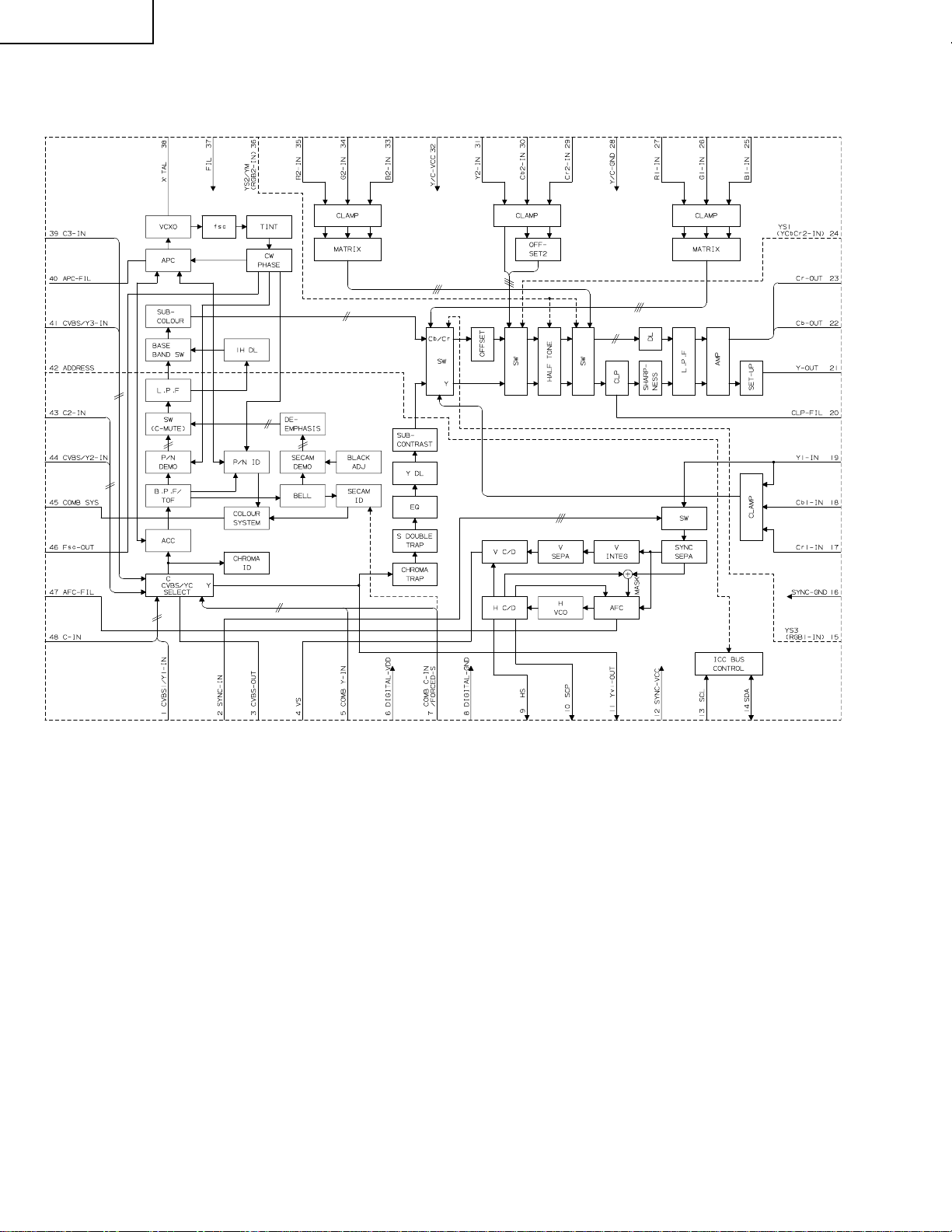

Ë VHiTB1274AF-1Q (ASSY: IC801, IC802)

» VIDEO/CHROMA Processor

» Block Diagram

30

Page 31

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

CVBS1/Y1-IN

SYNC-IN

CVBS-OUT

VS

COMB Y -IN

D-VDD

COMB C-IN

D-GND

HS

SCP

Yvi-IN

SYNC-VCC

SCL

SDA

YS3

(RGB1-in)

SYNC-GND

Cr1-IN

Cb1-IN

Y1-IN

CLP-FIL

Y-OUT

Cb-OUT

Cr-OUT

YS1

(YVbC2-IN)

B1-IN

G1-IN

R1-IN

Y/C-GND

Cr2-IN

Cb2-IN

Y2-IN

Y/C-VCC

B2-IN

G2-IN

R2-IN

YS2/YM

(RGB2-IN)

FIL.

X’TAL

C3-IN

APC-FIL

CVBS3/Y3-IN

ADDRESS

C2-IN

CVBS2/Y2-IN

COMB SYS

Fsc-OUT

AFC-FIL

C1-IN

I

I

O

O

I

—

I

—

O

O

O

—

I

I/O

I

—

I

I

I

—

O

O

O

I

I

I

I

—

I

I

I

—

I

I

I

I

—

—

I

—

I

I

I

I

O

O

—

I

CVBS1 or Y1-IN signal input.

Sync signal input.

CVBS or Y+C signal output terminal.

Counted-down vertical sync signal output.

Input of Y signal coming from comb filter. Open when not used.

DDS/BUS/V-CD/H-CD block power supply. DC5V (standard).

Input of C signal coming from comb filter. Open when not used.

DDS/BUS/V-CD/H-CD block grounding terminal.

H-AFC-processed horizontal sync signal output.

Sand Castle Pulse output. Clamping pulse and horizontal blanking pulse outputs.

Output of sync input Y signal selected with Video-SW.

SYNC/HVCO block power supply. DC5V (standard).

I2C BUS SCL terminal.

I2C BUS SDA terminal.

Selector switch for main signal and RGB1 input signal. YS3 input effective only when

“RGB1-ENB” is set at “enable” in bus setting.

SYNC/HVCO block grounding terminal.

Y1/Cb1/Cr1 signal input.

Y clamp filter to be connected.

Y/Cb/Cr signal output.

Selector switch for main signal and Y/Cr/Cb2 input signal.

RGB1 signal input. This input is selected at YS3 or I2C BUS.

Y/C/Text/Video-SW/1HDL block grounding terminal.

Y2/Cb2/Cr2 signal input. This input is selected at YS1.

Open when not used.

Y/C/Text/Video-SW/1HDL block power supply. DC5V (standard)

RGB2 signal input. This input is selected at YS2.

Open when not used.

Selector switch for main signal and RGB2 input signal.

Connected to Y/C-VCC terminal.

16.2MHz crystal oscillator to be connected.

Chroma signal input. Open when not used.

Chroma demodulation filter to be connected.

CVBS3 or Y3 signal input. Open when not used.

Slave address to be preset.

Chroma signal input. Open when not used.

CVBS2 or Y2 signal input. Open when not used.

Received color system judgment result to be output from this pin and pin 46.

Subcarrier output.

AFC detection filter to be connected.

Chroma signal input. Open when not used.

PZ-43MR2E

PZ-50MR2E

31

Page 32

PZ-43MR2E

PZ-50MR2E

Ë VHICXA2101Q-1 (ASSY: IC803)

» Baseband Video Signal Processor

» Block Diagram

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

IN2-H

IN2-V

IN2-1

IN2-2

IN2-3

Vcc-MAT

IN3-H

IN3-V

IN3-1

IN3-2

IN3-3

GND-MAT

IN4-H

IN4-V

IN4-1

IN4-2

IN4-3

I

I

I

I

I

—

I

I

I

I

I

—

I

I

I

I

I

IN2-H : Independent horizontal sync signal input terminal.

IN2-V : Independent vertical sync signal input terminal.

IN2 line signal input terminal.

Selector line and sync processor line power terminal.

IN3-H : Independent horizontal sync signal input terminal.

IN3-V : Independent vertical sync signal input terminal.

IN3 line signal input terminal.

Selector line and sync processor line grounding terminal.

IN4-H : Independent horizontal sync signal input terminal.

IN4-V : Independent vertical sync signal input terminal.

IN4 line signal input terminal.

32

Page 33

» Pin Function

Pin No. Pin Name I/O Pin Function

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

37

39

36

38

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

V-PH

IN5-H

IN5-V

IN5-1

IN5-2

IN5-3

H-PH

YG-OUT

YG-IN

IREF-SYNC

VS-OUT

HS-OUT

Vcc-OUT

SCP-IN

VTIM-IN

HP-IN

GND-OUT

R-OUT

G-OUT

B-OUT

R-SH

G-SH

B-SH

IK-IN

PABL-FIL

ABL-FIL

ABL-IN

YS/YM-1

LR1-IN

LG1-IN

LB1-IN

YS/YM-2

LR2-IN

LG2-IN

LB2-IN

ADDRESS

DPIC-C

SCL

SDA

DPIC-MUTE

CLP-C

VM-OUT

VM/SHP/COL-OFF

YCBCR-SW

ECR-IN

ECB-IN

EY -IN

V1-IN

H1-IN

CR1-IN

CB1-IN

Y1-IN

GND-SIG

IREF-YC

Vcc-SIG

SELCR-IN

SELCB-IN

SELY-IN

SELY-OUT

SELCB-OUT

SELCR-OUT

SELH-OUT

SELV-OUT

I

I

I

I

I

O

I

O

O

O

I

I

I

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

O

I

I

I

I

I

I

I

I

I

—

—

I

I

I

O

O

O

O

O

Vsync peak holding capacitor connection terminal.

IN5-H : Independent horizontal sync signal input terminal.

IN5-V : Independent vertical sync signal input terminal.

IN5 line signal input terminal.

Hsync peak holding capacitor connection terminal.

Sync separation composite video signal output terminal.

Sync separation composite video signal input terminal.

Reference current setting terminal (about 4.6V)

Used to select between IN1-line HV and IN2/IN5-line selector output HV by I2C BUS

“YCBCR/MAT” and feed out the signal in positive polarity.

RGB line power terminal.

Sand-Castle-Pulse input terminal.

V timing pulse input terminal.

H pulse input terminal.

RGB line grounding terminal.

RGB signal output terminal.

Output to be made at 2.6Vp-p with 100IRE white input.

RGB AKB sample-and-hold terminal.

Reference pulse to return to this terminal.

Peak ABL peak holding terminal.

Used to form LPF for ABL control signal.

ABL control signal input terminal.

YM1/YS1 control input terminal. Input level to be of 3 values.

VM turning-off function also available when YM and YS have reached their specified values.

Analog RGB1 signal input terminal.

YM2/YS2 control input terminal. Input level to be of 3 values.

VM turning-off function also available when YM and YS have reached their specified values.

Analog RGB2 signal input terminal.

I2C BUS slave address setting terminal.

Capacitor to be connected for grounding in order to detect the black signal in dynamic

picture (black stretching).

I2C BUS standard SCL (Serial Clock) input terminal.

I2C BUS standard SDA (Serial Data) input terminal.

Used to control MUTE of dynamic picture (black stretching).

Y line clamp capacitor connection terminal.

VM output terminal to feed out Y signal’s differential waveform in positive polarity.

Used to turn off VMÅASHARPNESS and COLOUR. Input level to be 3 values

Used to switch between INT and EXT SW input signals. External input terminal to be

selected at High level.

External Y, Cb, and Cr input terminals.

IN1-line HV input terminal. Positive-polarity input.

IN1-line Y, Cb, and Cr input terminals.

Y color difference signal processor grounding terminal.

Reference current setting terminal (mainly for Y color difference signal processing line).

Y color difference signal processor power terminal.

Used to feed in selector outputs Y, Cb, and Cr through clamp capacitor.

IN2- thru IN5-line selector output terminals.

Used to feed out Y-, Cb-, and Cr-converted signals.

IN2 thru IN5 selector HV output terminals.

PZ-43MR2E

PZ-50MR2E

33

Page 34

PZ-43MR2E

PZ-50MR2E

Ë RH-iX3566CEZZ (ASSY: IC1901)

» PLD (Programmable Logic Device)

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

TDI

VD1

SP_HD

GND

SP_VD

SP_CP

TMS

HD3

VCC

VD3

GND

MODEA

MODEB

MODEC

SELA

GND

VCC

SELO

HD2

VD2

HDS

VDS

US_VD

GND

US_HD

TCK

TEXT_VD

TEXT_HD

VCC

GND

PL_BLK

TDO

PLCP

PL_HD

PL_VD

GND

GCLK1

OE1

GCLRn

OE2/GCLK2

VCC

CNR_CP

CNR_HBLK

HD1

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

I/O

—

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

I/O

—

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

I/O

I/O

—

—

I/O

I/O

I/O

Ground

Power supply (3.3V)

Ground

Ground

Power supply (3.3V)

Ground

Power supply (3.3V)

Ground

I

I

I

I

Ground

External clock input. 16MHz

Power supply (3.3V)

34

Page 35

Ë VHiTA1318AF-1 (ASSY: IC604)

» Sync Processor

» Block Diagram

PZ-43MR2E

PZ-50MR2E

35

Page 36

PZ-43MR2E

PZ-50MR2E

» Pin Function

Pin No. Pin Name I/O Pin Function

3

1

11

4

2

10

5

6

7

8

20

9

24

12

13

15

14

16

17

18

21

19

22

23

HD1-IN

HD2-IN

HD3-IN

VD1-IN

VD2-IN

VD3-IN

ANALOG GND

AFC FILTER

HVCO

VCC

DAC1

(V . SYNC output)

DAC2

(H/C. SYNC output)

DAC3

CP-OUT

HD1-OUT

HD2-OUT

DIGITAL GND

SDA

SCL

ADDRESS SW

SYNC1-IN

SYNC2-IN

VD1-OUT

VD2-OUT

—

—

—

—

O

O

O

O

O

O

—

I/O

O

O

I

I

I

I

I

I

I

I

I

I

Input the horizontal synchronizing signal.

It’s polarity corresponds to both positive and negative.

Input from this pin does not be synchronized internally.

Input the horizontal vertical signal.

It’s polarity corresponds to both positive and negative.

Input from this pin does not be synchronized internally.

The GND pin for analog circuit block.

Connect the filter for horizontal AFC. The frequency of the horizontal output is varied

by the volyage at this pin.

Connect the ceramic oscillator for horizontal oscillator.

The VCC pin. (9.0V)

DAC1 output pin. When TEST mode, VD or vertical sync signal to frequency counter

circuit is output.

DAC2 output pin. When TEST mode, HD or composite sync signal to frequency

counter circuit is output.

DAC3 output pin. This pin is open-collector system. When TEST mode, test pilses for

the shipping is output.

Clamp pulse output pin. CP mode at synchronization circuit is output.

HD output pin. This pin is open-collector system.

HD1/HD2 does not be synchronizing and they are output from this pin.

It’s polarity is switched by BUS write function.

The GND pin for logic circuit block.

The SDA pin for I2C BUS.

The SCL pin for I2C BUS.

Slave address switch.

Input a signal to separate sync signal.

VD output pin. This pin is open-collector system.

VD1/VD2 does not be synchronizing and they are output from this pin.

It’s polarity is switched by BUS write function.

36

Page 37

Ë VHiCXD2064Q-1 (ASSY: IC402, IC405)

» Digital Comb Filter

» Block Diagram

PZ-43MR2E

PZ-50MR2E

37

Page 38

PZ-43MR2E

PZ-50MR2E

» Pin Function

Pin No. Pin Name I/O Pin Function

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15, 28, 32, 33, 35,

16, 27, 34

18, 29, 36

17

19

20

21

22

23

24

25

26

30

31

37

38

39

40

41

42

43

44

45

46

47

48

CLPO

ADIN

RB

ADVS

ADVD

RT

ACO

DAVD

AYO

DAVS

VG

VRF

IRF

VB

TEST

DVDD

DVSS

MOD2

MOD1

VEH3

VEH2

VEH1

PNR

DTR

NTPL2

NTPL1

APCN

TRAP

FIN

CKSL

PLSL

MCKO

ADCK

CPO

PLVS

VCV

PLVD

CLVD

CLPEN

CLVS

O

I

O

—

—

O

O

—

O

—

O

I

O

O

I

—

—

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

I

O

—

I

—

—

I

—

Built-in clamp circuit current output terminal. To be connected to ADIN when built-in

clamp is used.

Comb filter analog input (A/D converter) terminal.

A/D converter reference bottom voltage. (standard 0.52V)

A/D converter analog grounding terminal.

A/D converter analog power terminal. (5.0V)

A/D converter reference top voltage. (standard 2.6V)

Analog chroma signal output terminal. Resistance to be added between this pin and

GND for obtaining the output.

D/A converter analog power terminal. (5.0V)