Page 1

CIRCUIT DIAGRAM

CODE: 00ZMX3500NC1/

DIGITAL FULL COLOR

MULTIFUNCTIONAL SYSTEM

デジタルフルカラー複合機

MX-3500N/4500N

MX-3501N/4501N

MX-3500FN/4500FN

MODEL

[1] BLOCK DIAGRAM / ブロック図 . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

[2] CIRCUIT DIAGRAM / 回路図. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

[3] AC POWER LINE DIAGRAM / AC 電源ライン図 . . . . . . . . . . . . . . 3-1

[4] DC POWER LINE DIAGRAM / DC 電源ライン図 . . . . . . . . . . . . . . 4-1

[5] SIGNAL LIST / 信号リスト . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

MX-3501FN/4501FN

CONTENTS

安全性・信頼性確保のため部品は、必ず正規のものをご使用ください。

印部品は、安全上重要な部品です。交換をする時は、安全および性能維持のため必ず指定の部品をご使

用ください。

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with

specified ones for maintaining the safety and performance of the set.

This document has been published to be used

SHARP CORPORATION

for after sales service only.

The contents are subject to change without notice.

Page 2

CONTENTS

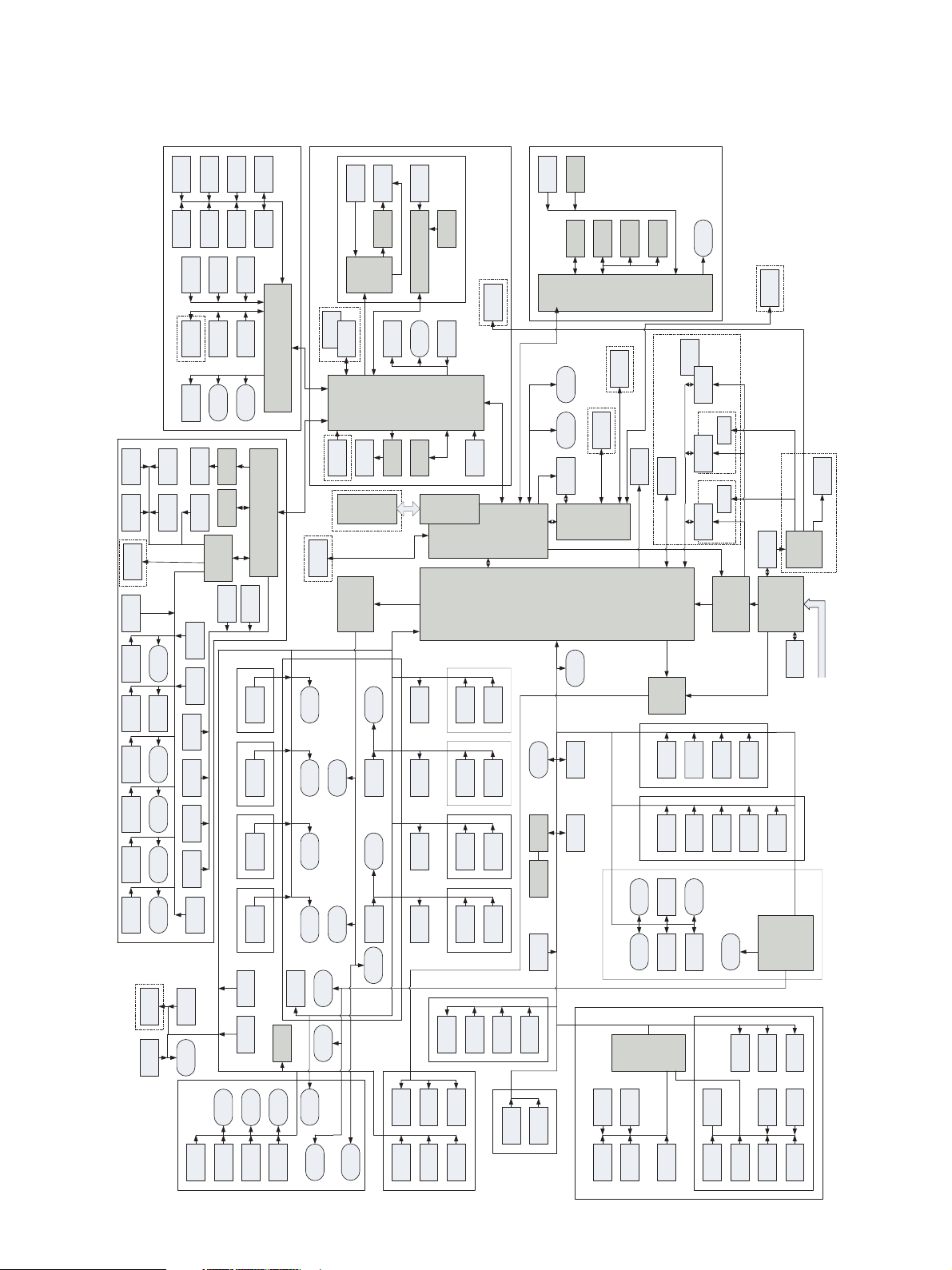

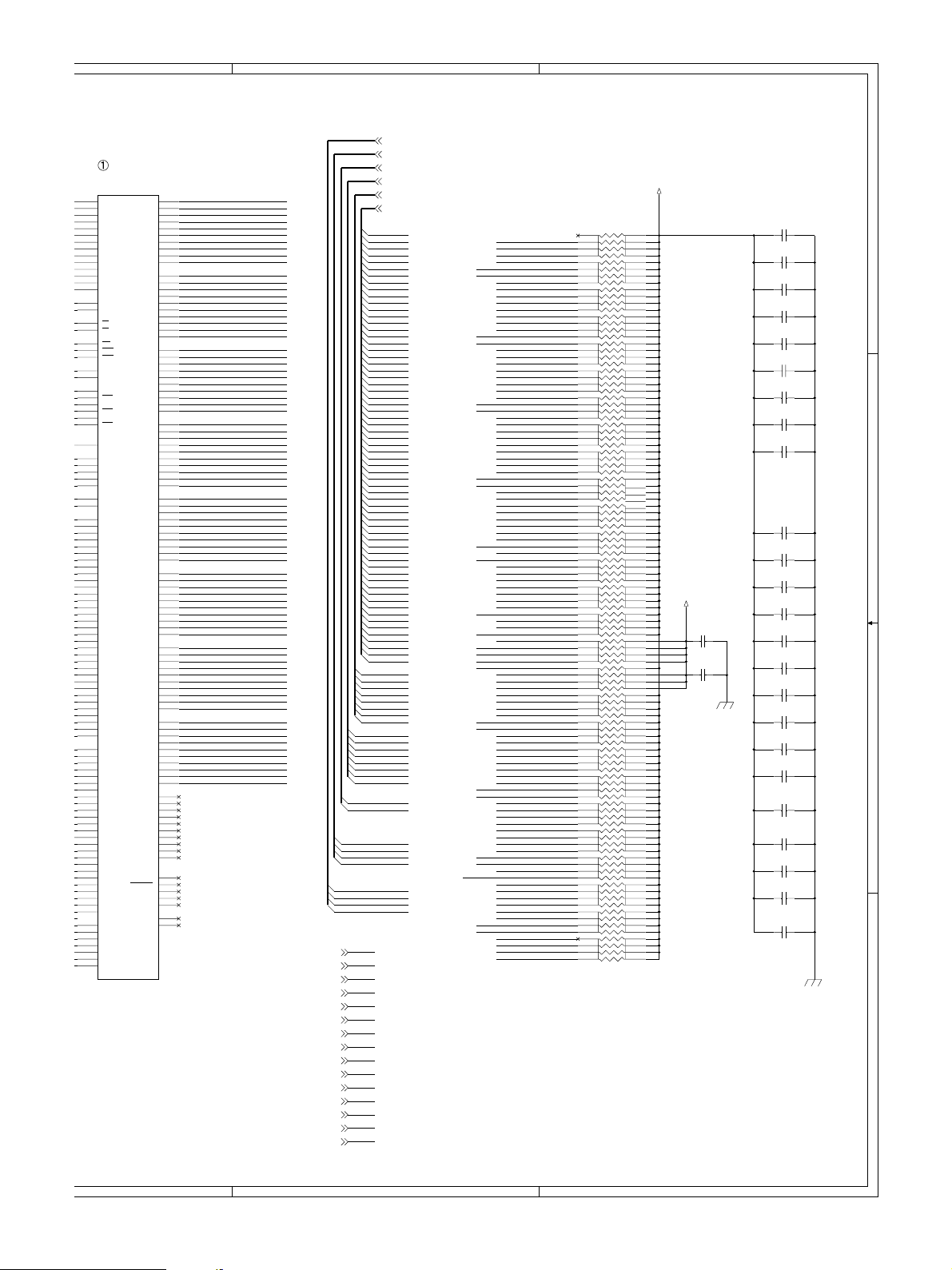

[1] BLOCK DIAGRAM

1. SYSTEM BLOCK DIAGRAM. . . . . . . . . . . . . . 1-1

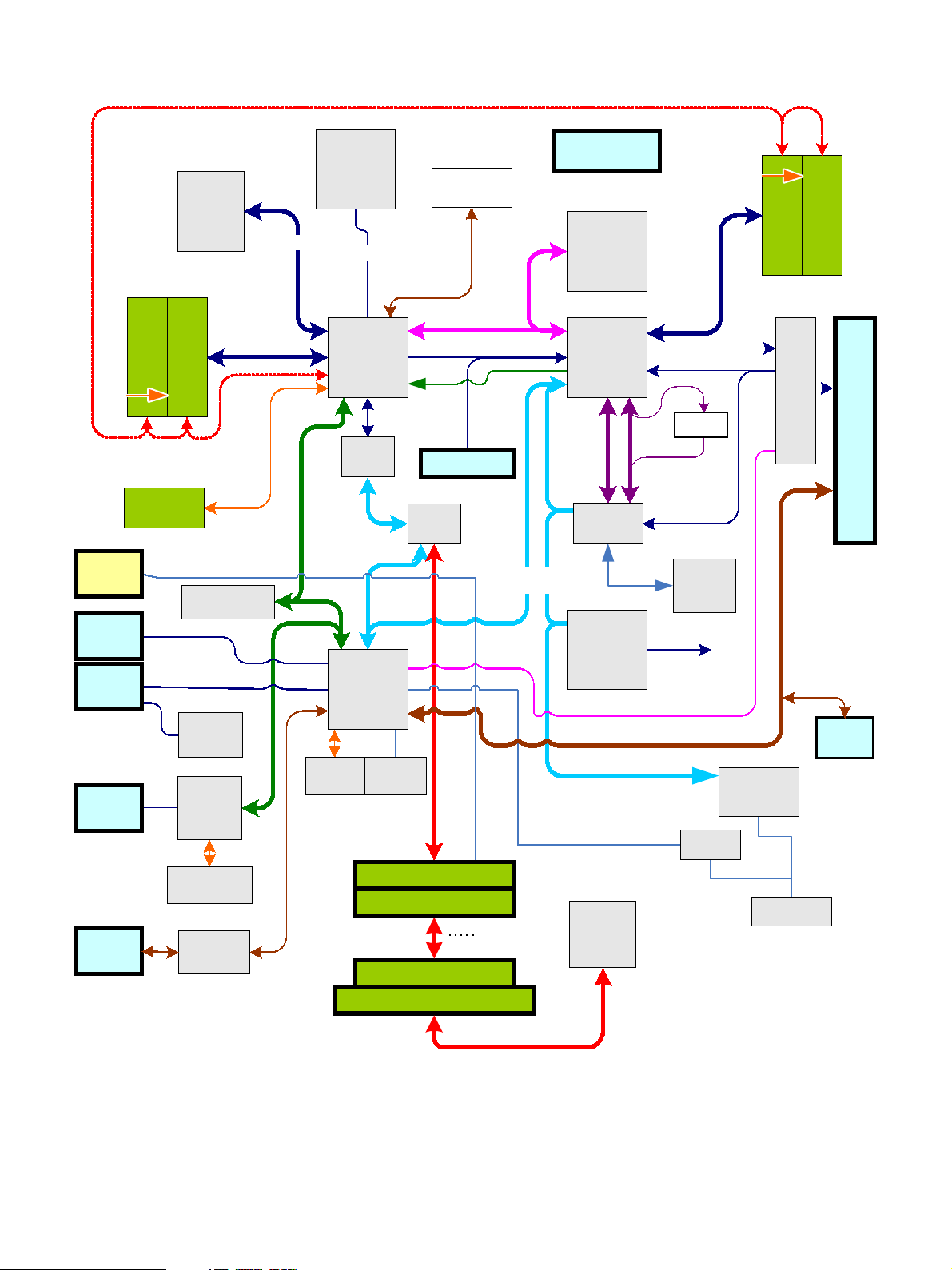

2. MFP CONTROLLER PWB . . . . . . . . . . . . . . . 1-2

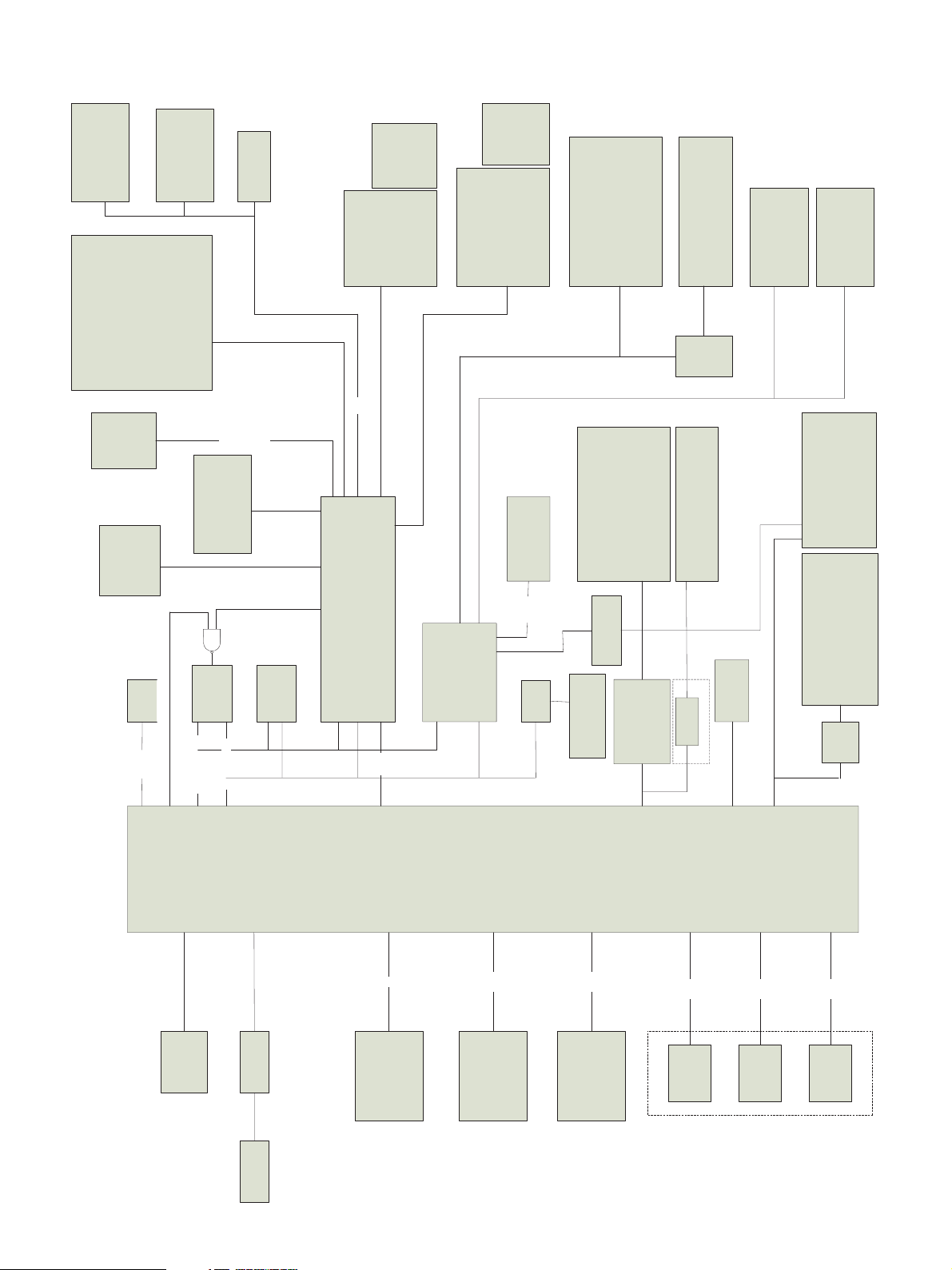

3. PCU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

4. SCANNER CONTROL PWB . . . . . . . . . . . . . . 1-4

5. SERIAL COMMUNICATION . . . . . . . . . . . . . . 1-5

6. FAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

[2] CIRCUIT DIAGRAM

1. MFP CONTROLLER PWB . . . . . . . . . . . . . . . 2-1

2. PCU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

3. MOTHER PWB . . . . . . . . . . . . . . . . . . . . . . 2-121

4. SCANNER CONTROL PWB . . . . . . . . . . . . 2-131

5. DSPFcnt PWB (MX-3501N/4501N). . . . . . . 2-159

6. DSPF DRIVER PWB

(MX-3501N/4501N) . . . . . . . . . . . . . . . . . . . 2-175

7. DSPF MEMORY PWB

(MX-3501N/4501N) . . . . . . . . . . . . . . . . . . . 2-181

8. LSU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . 2-193

9. OPERATION PWB . . . . . . . . . . . . . . . . . . . 2-205

10. DRIVER MAIN PWB . . . . . . . . . . . . . . . . . . 2-207

11. DRIVER SUB PWB . . . . . . . . . . . . . . . . . . . 2-209

12. DISCHARGE LAMP PWB . . . . . . . . . . . . . . .2-211

13. LCD INVERTER PWB. . . . . . . . . . . . . . . . . 2-212

14. CCD-F PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-213

15. CCD-R PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-223

16. DOCUMENT-CONTROL PWB . . . . . . . . . . 2-233

17. SCAN INPUT SUPPORT PWB . . . . . . . . . . 2-241

18. LD PWB. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-243

19. BD PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-244

20. HL PWB. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-245

21. LVDS-J PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-249

22. LVDS-P PWB. . . . . . . . . . . . . . . . . . . . . . . . 2-251

23. RIGHT-DOOR I/F PWB . . . . . . . . . . . . . . . . 2-253

24. WH PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-255

25. POWER SW PWB. . . . . . . . . . . . . . . . . . . . 2-256

26. AC POWER PWB . . . . . . . . . . . . . . . . . . . . 2-257

27. DC POWER PWB . . . . . . . . . . . . . . . . . . . . 2-263

28. REVERSING SINGLE PASS FEEDER

(MX-3500N/4500N) . . . . . . . . . . . . . . . . . . . 2-271

29. DESK (MX-DEX3/DEX4). . . . . . . . . . . . . . . 2-273

30. LARGE CAPACITY TRAY (MX-LCX1) . . . . 2-275

31. FINISHER (MX-FNX1). . . . . . . . . . . . . . . . . 2-277

32. PUNCH MODULE (MX-PNX1A/B/C/D) . . . . 2-281

33. SADDLE STITCH FINISHER

(MX-FNX2) . . . . . . . . . . . . . . . . . . . . . . . . . 2-285

34. PAPER PASS UNIT (MX-RBX1) . . . . . . . . . 2-291

35. FAX (MX-FXX1/MX-3500FN/MX-4500FN/

MX-3501FN/MX-4501FN) . . . . . . . . . . . . . . 2-293

[3] AC POWER LINE DIAGRAM

1. AC POWER LINE DIAGRAM (120V) . . . . . . . 3-1

2. AC POWER LINE DIAGRAM (200V) . . . . . . . 3-2

3. AC POWER LINE DIAGRAM (100V

(JAPAN)) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

[4] DC POWER LINE DIAGRAM

1. DC POWER LINE DIAGRAM . . . . . . . . . . . . . 4-1

[5] SIGNAL LIST

[1] ブロック図

1. システムブロック図 . . . . . . . . . . . . . . . .

2. MFP コントローラ PWB . . . . . . . . . . . . .

3. PCU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

4. スキャナコントロール PWB . . . . . . . . . .

5. シリアル通信 . . . . . . . . . . . . . . . . . . . . .

6. FAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

[2] CIRCUIT DIAGRAM

1. MFP コントローラ PWB . . . . . . . . . . . . .

2. PCU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-85

3. マザー PWB. . . . . . . . . . . . . . . . . . . . . . .

4. スキャナコントロール PWB . . . . . . . . . .

5. DSPFcnt PWB (MX-3501N/4501N). . . . . . . 2-159

6. DSPF DRIVER PWB

(MX-3501N/4501N) . . . . . . . . . . . . . . . . . . . 2-175

7. DSPF MEMORY PWB

(MX-3501N/4501N) . . . . . . . . . . . . . . . . . . . 2-181

8. LSU PWB . . . . . . . . . . . . . . . . . . . . . . . . . . 2-193

9. 操作 PWB . . . . . . . . . . . . . . . . . . . . . . . .

10. ドライバーメイン PWB. . . . . . . . . . . . . .

11. ドライバーサブ PWB . . . . . . . . . . . . . . .

12. 除電ランプ PWB . . . . . . . . . . . . . . . . . . .

13. LCD インバーター PWB . . . . . . . . . . . . .

14. CCD-F PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-213

15. CCD-R PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-223

16. DOCUMENT-CONTROL PWB . . . . . . . . . . 2-233

17. SCAN INPUT SUPPORT PWB . . . . . . . . . . 2-241

18. LD PWB. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-243

19. BD PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-244

20. HL PWB. . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-245

21. LVDS-J PWB . . . . . . . . . . . . . . . . . . . . . . . . 2-249

22. LVDS-P PWB. . . . . . . . . . . . . . . . . . . . . . . . 2-251

23. 右ドア I/F PWB . . . . . . . . . . . . . . . . . . . .

24. WH PWB . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-255

25. 電源スイッチ PWB . . . . . . . . . . . . . . . . .

26. AC 電源 PWB . . . . . . . . . . . . . . . . . . . . .

27. DC 電源 PWB . . . . . . . . . . . . . . . . . . . . .

28. 両面原稿自動送り装置

(MX-3500N/4500N) . . . . . . . . . . . . . . . . . . . 2-271

29. 給紙デスク (MX-DEX3/DEX4). . . . . . . . .

30. 大容量給紙トレイ (MX-LCX1). . . . . . . . .

31. フィニッシャー (MX-FNX1) . . . . . . . . . .

32. パンチユニット (MX-PNX1A/B/C/D). . . .

33. サドルフィニッシャー

(MX-FNX2) . . . . . . . . . . . . . . . . . . . . . . . . . 2-285

34. 中継ユニット (MX-RBX1) . . . . . . . . . . . .

35. FAX (MX-FXX1/MX-3500FN/MX-4500FN/

MX-3501FN/MX-4501FN) . . . . . . . . . . . . . . 2-293

[3] AC 電源ライン図

1. AC POWER LINE DIAGRAM (120V) . . . . . . . 3-1

2. AC POWER LINE DIAGRAM (200V) . . . . . . . 3-2

3. AC POWER LINE DIAGRAM (100V

(JAPAN)) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

[4] DC 電源ライン図

1. DC POWER LINE DIAGRAM . . . . . . . . . . . . . 4-1

[5] 信号リスト

. . . . 1-1

. . . . 1-2

. . . . 1-4

. . . . 1-5

. . . . 2-1

. . 2-121

. . 2-131

. . 2-205

. . 2-207

. . 2-209

. . .2-211

. . 2-212

. . 2-253

. . 2-256

. . 2-257

. . 2-263

. . 2-273

. . 2-275

. . 2-277

. . 2-281

. . 2-291

Page 3

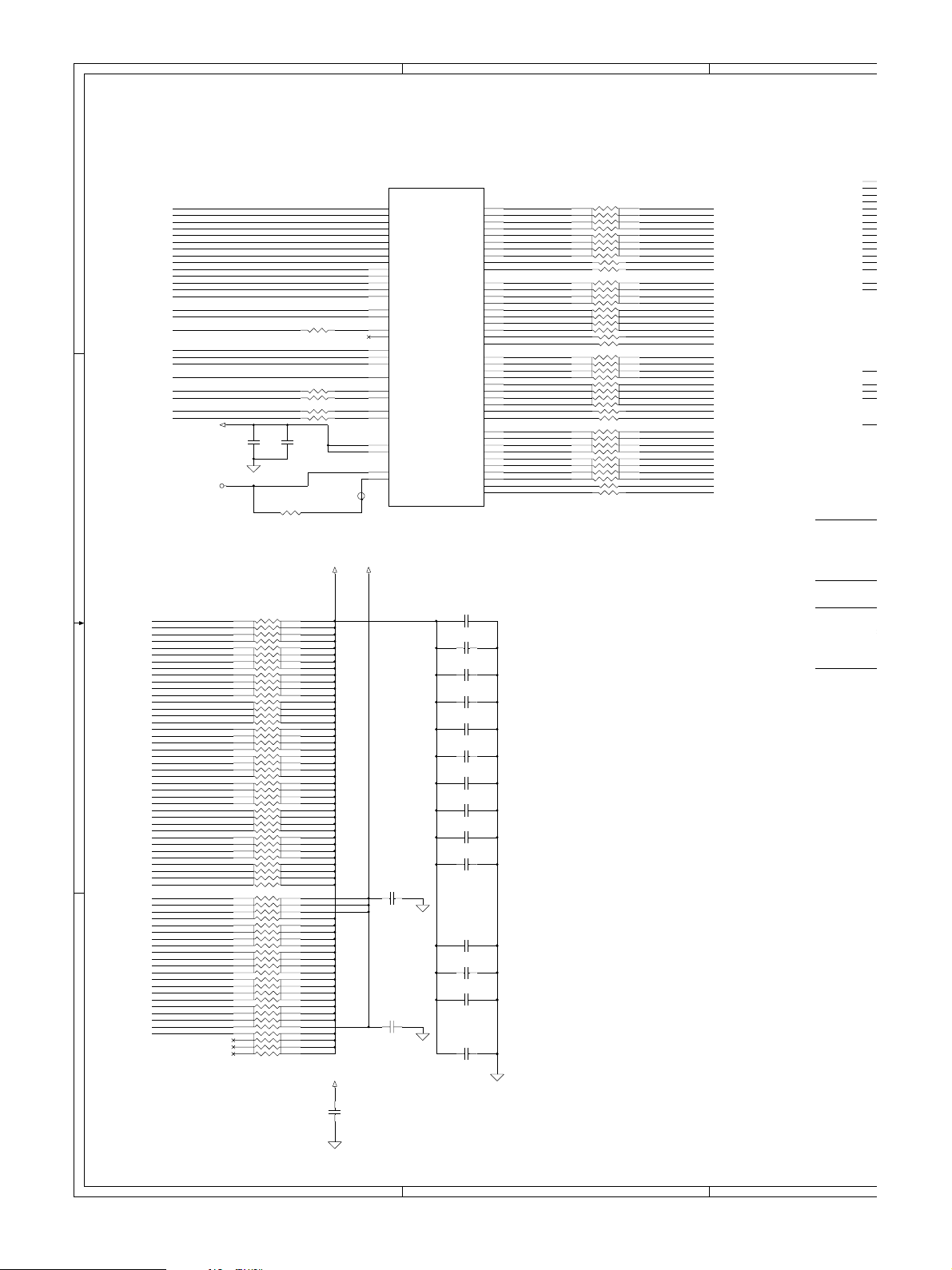

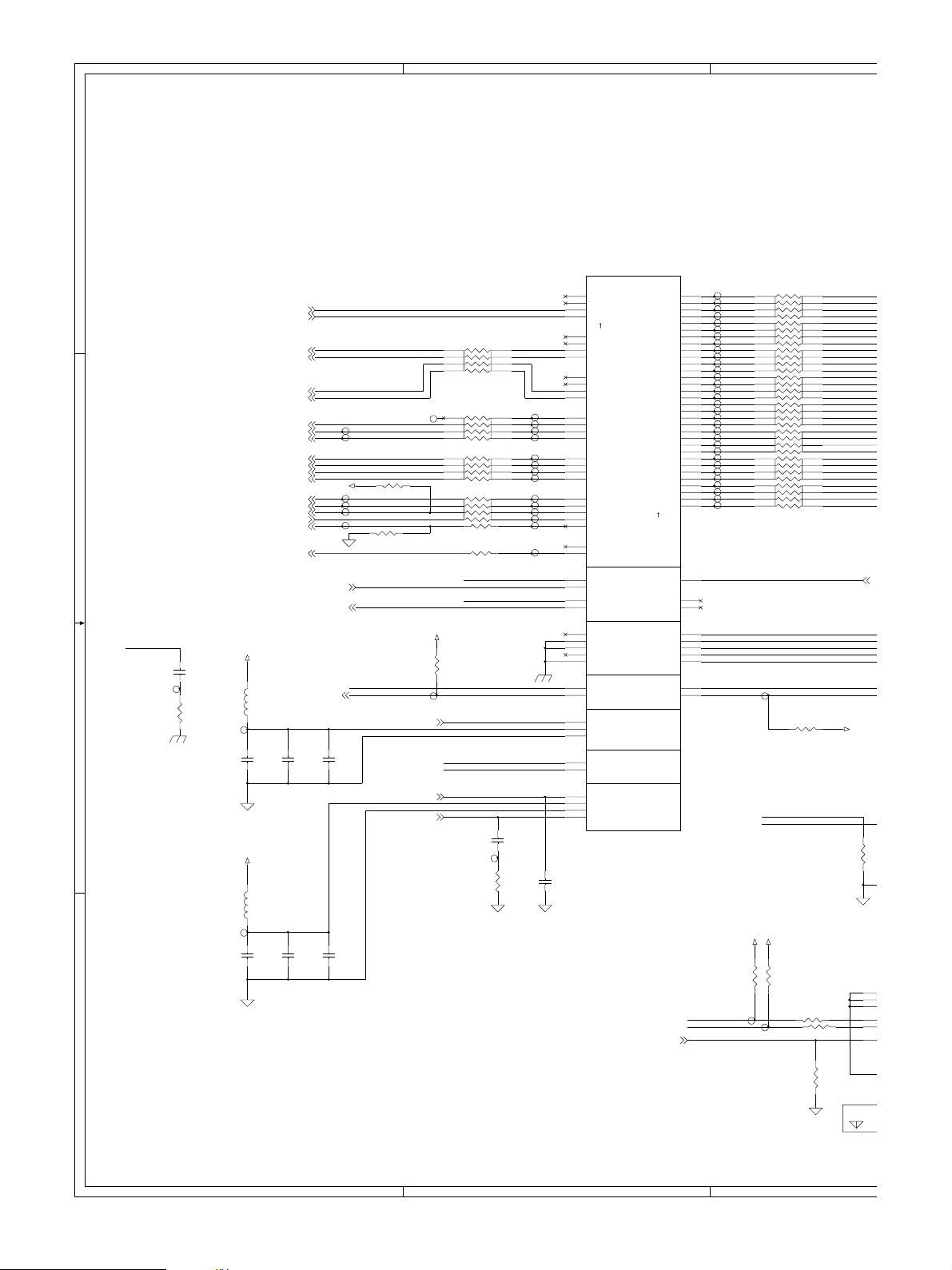

MX3500N

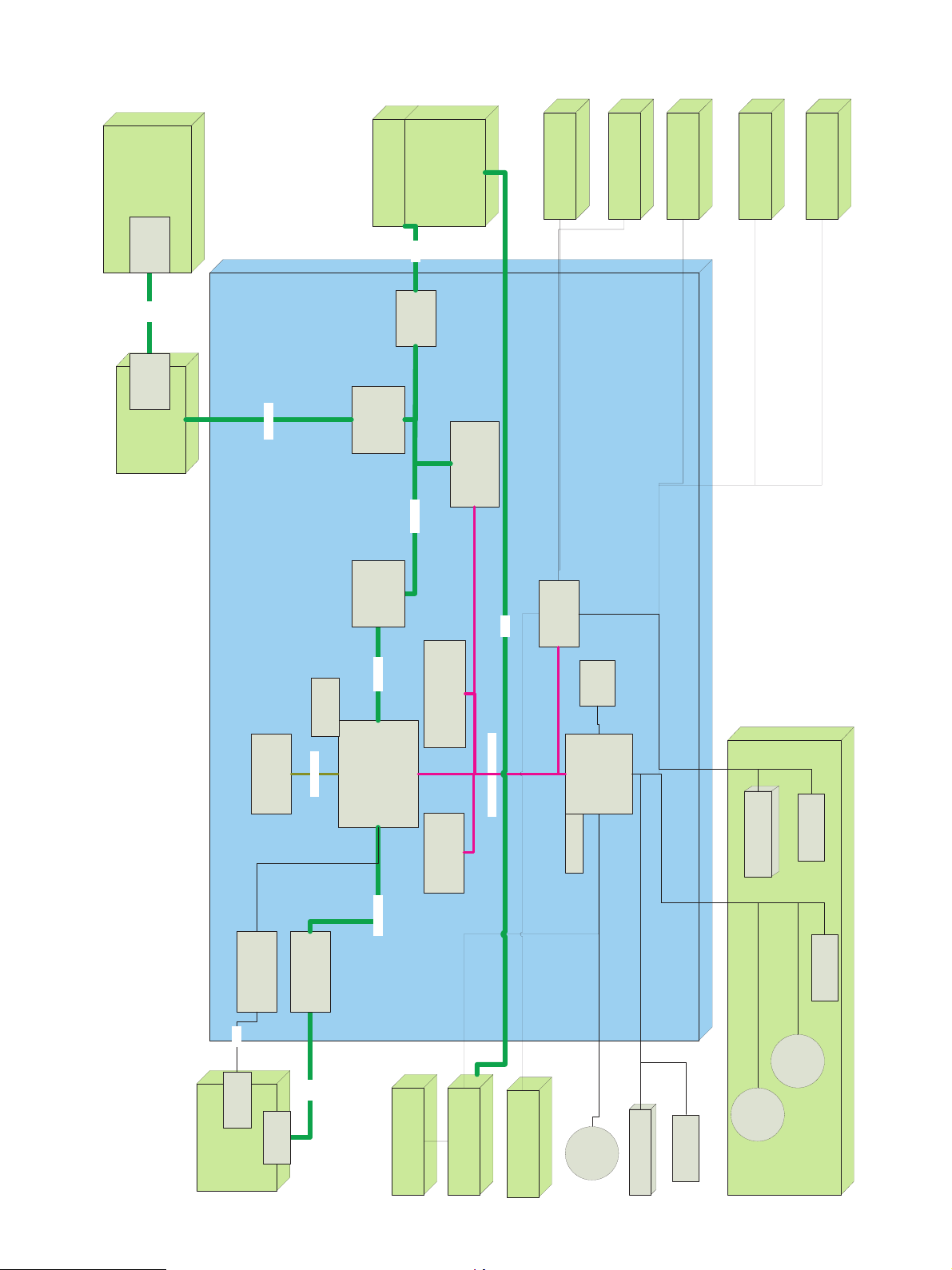

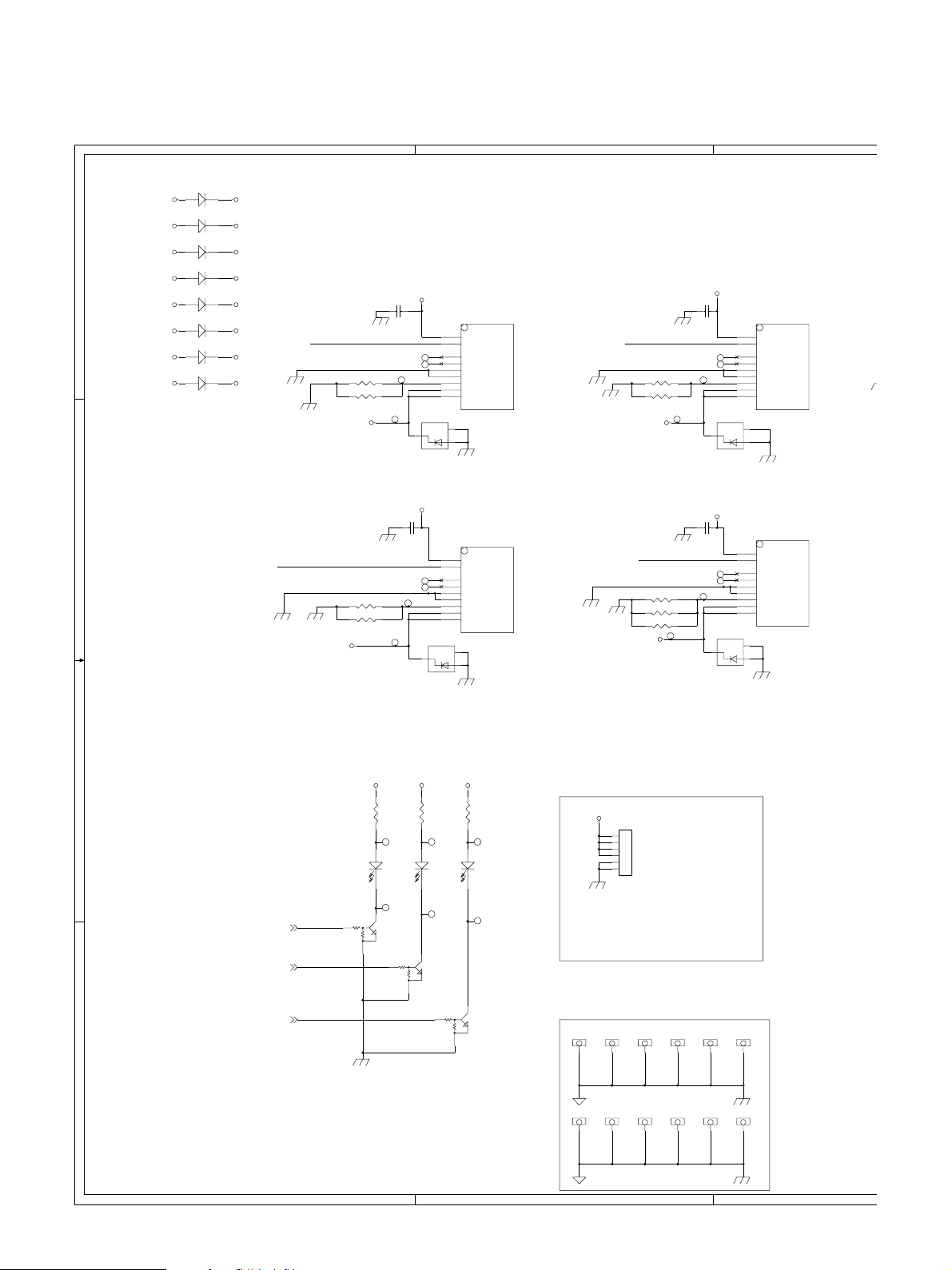

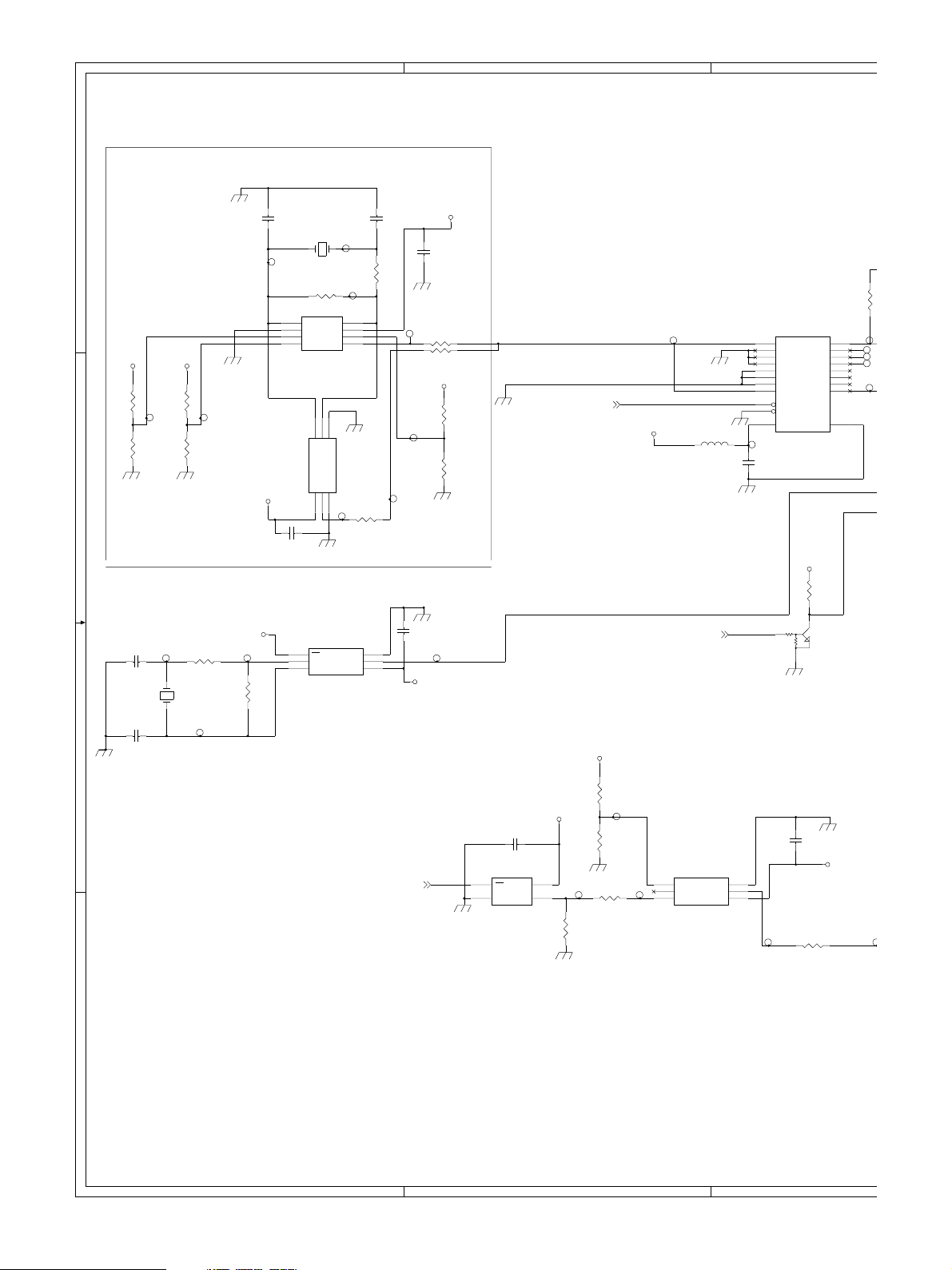

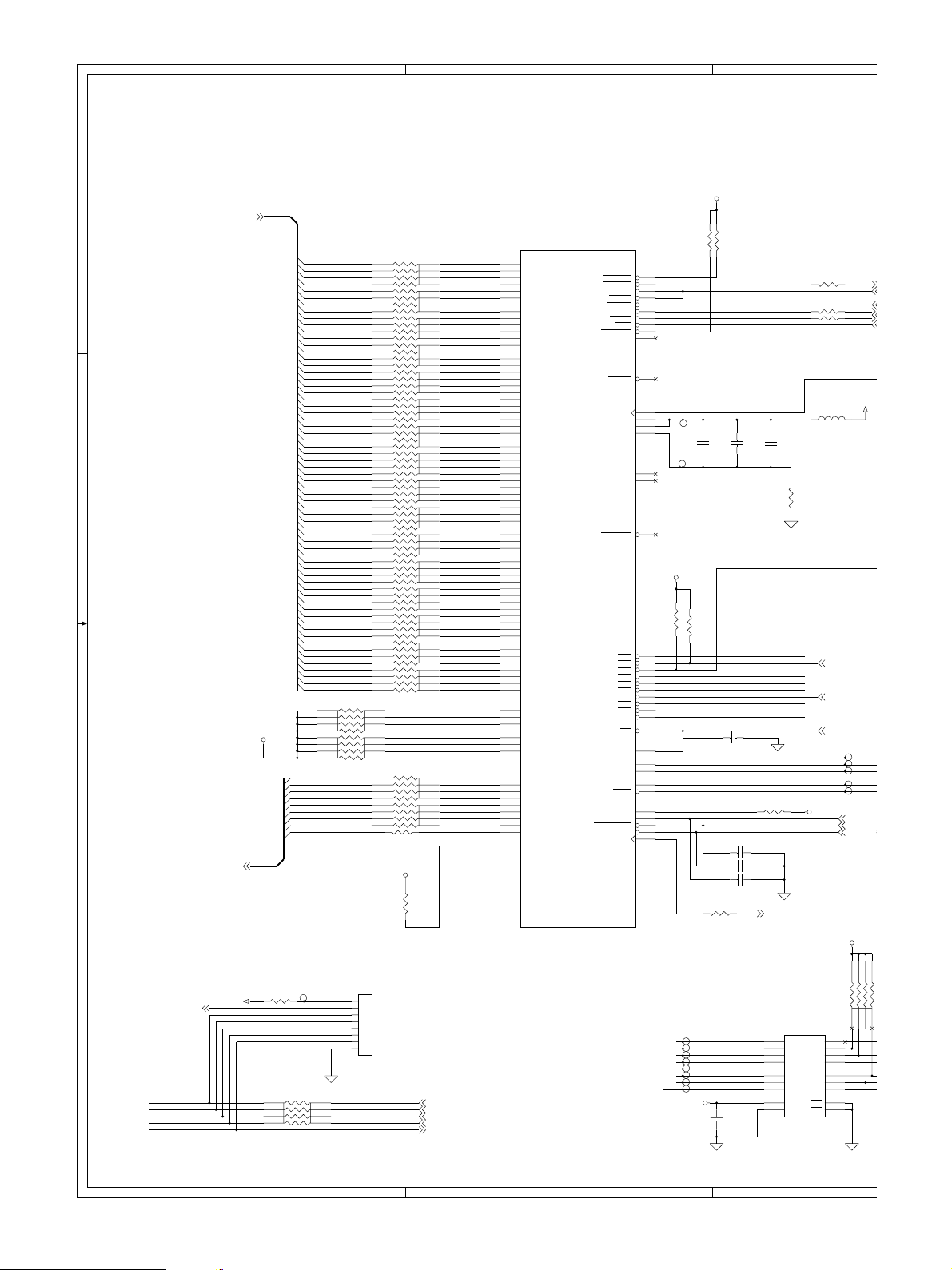

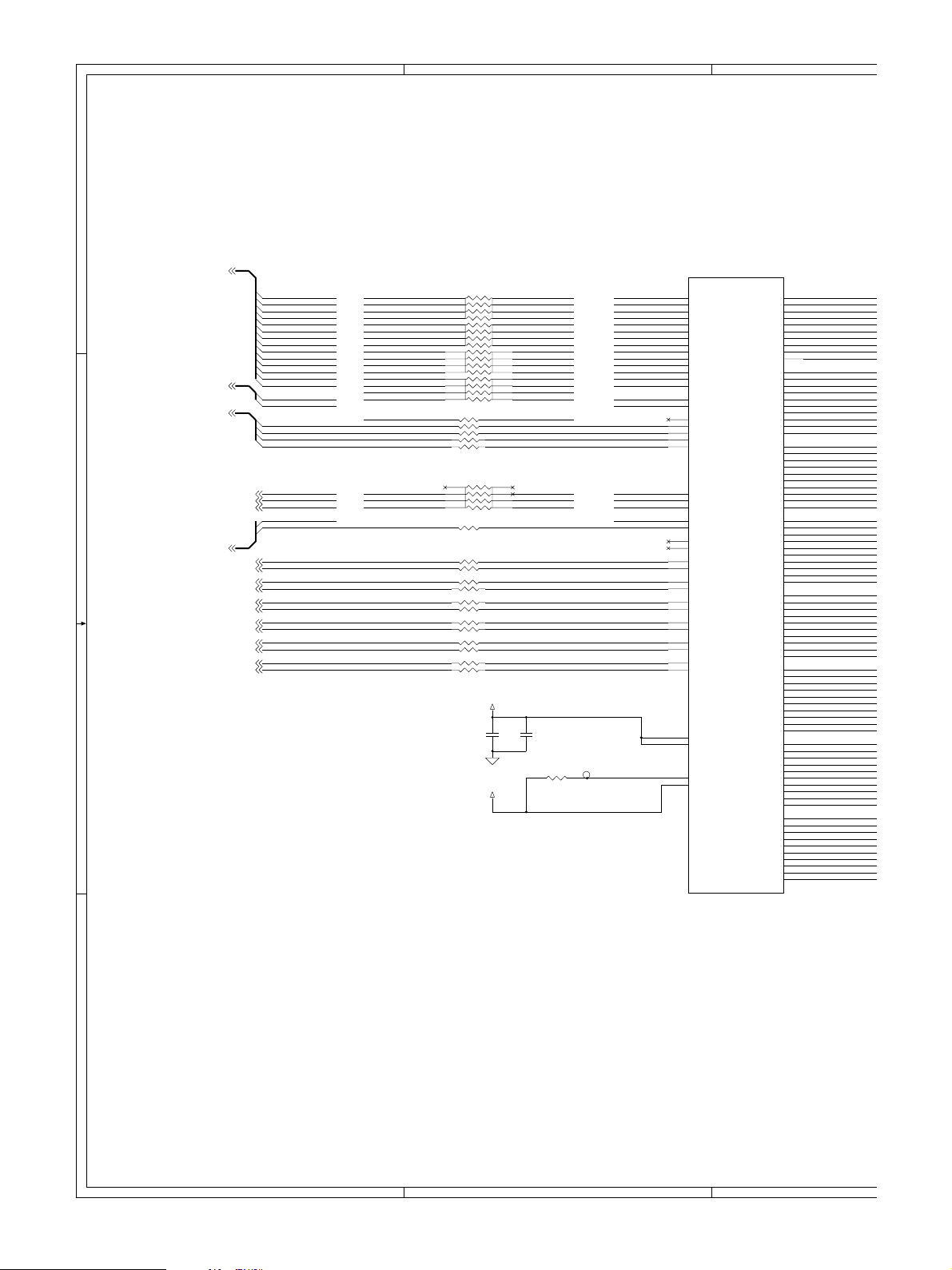

[1] BLOCK DIAGRAM / ブロック図

Circuit Diagram

1. SYSTEM BLOCK DIAGRAM / システムブロック図

SPED

SCOV

LCD

PANEL

TOUCH

ORS_PD

PWB

BD_K

TH1_LSU

SPPD1 SOCD

SPPD2

SPLS1

SPFC SRRC

SPPD3

SPLS2

OPERATION UNIT

SPPD4

SPPD5 SPWS

PWB

OPTION

SGS STMPS

SPFM

RSPF

SPRM

AUDITOR

OPTION

RSPF UNIT

CL

SPED2

SPLS1

SPLS2

STMPS

OPTION

STLD SPED 1

STUD

STRRCSTRRBC

PWB

CL INVERTER

CCD

PWB

SCOV

DSPF DRIV ER

SPRANDOMSPOD

SPPD1

SPPD2

SPPD3SPPD4SPPD5

DSPFcnt PWB

PWB

SOCD

ROCD

CARD

OPTION

SCANNER UNIT

OPTION

FAX 1

OPTION

Thereis a st andards

setting model

Only J apan

DM_CL

PWB

INVERTE R

PWB

LVDS

PNC

ORS_ LED

CL

READER

PWB

CL INVERTER

PWB

DOCC

If DOCC PWB

is used,

replace it with

SCNINPWB.

PWB

POWER SW

OPE

PWB

DHS1

OPTION

MIM

OCSW

PWB

SCNC

CCD

PWB

MHPS

PWB

SCN IN

LSU UNIT

MOTHER

PWB

PWB

PWB

LD_K

HDDFM CPUFM

OPTION

HDD

PWB

PWB

LD_C

LD_Y

LD_M

PWB

LSUCNT

EFI

OPTION

FAX 2

LSUSS

PWB

MFPC

OPTION

PGM

USB HUB

OPTION

FIN 1K

FIN INNER

COINVENDER

DH_DE SK DH_LCC

DESK LCC

DHSW

DH1

Standards : Only Japan

WH

PWB

OPTION

PCU

PWB

DRIVER SUB

DVM_CL

TCS_Y

PWB

PSFM

HL

PWB

CSS2

OZFM

CPFD2

UNIT

CPED2

CLUD2

AC

DCPS

PWB

MSW

AC IN

PAP ER FEED 2

1TC

CSS1

SPOMSPFFAN SPFM SLUMSPUM SPFC

SRRC SRRBC STRC

DSPF UNIT

PNC

OPTION

1TNFD

WTN M

DSW_ F

DVCRUM_ C DVCRUM_M DVCRUM_Y

DVCRUM_K

TONER_K UNIT TONER _C UNIT T ONE R_MUNIT T ONER_Y UNIT

1TUD_CL

1TUD_K

POFM_F

POFM_ R

TNM_C TNM_M TNM_Y

TNM_K

RRM

1TURC

PROCESS DRIVE UNIT

2TC

ADUM_L

FUM

OSM

DVM_K

DM_K

DHPD_K DHPD_CL

BTM

HL1_U

TCS_C TCS_M

DVTYP_C DVTYP_M DVTYP_Y

MC

DL_K DL_MDL_C DL_Y

TCS_K

DV_ KUNIT DV_ CUNIT DV_M UNIT DV_ Y UNIT

DVTYP_K

DSW_ R

PAPER FEED DRIV E UNIT

PCS

REGS_F

PCSS

REGS_R

REGIST SENSOR UNI T

HL2_L

HL3_U

PPD1

PPD2

POD3

CPFD1

CLUD1

UNIT

CPED1

DSW_C

CSPD1 CSPD2

PAPER FEED 1

CLUM2

CLUM1

RD I/ F

TFD3

CPFM

CPUC2

PFM

CPFC

CPUC1

PWB

MPUC

MPLD1

PWB

DRIVER MAIN

MPFS

MPGS

MTOP1

MTOP2

PS UNIT

POD1

TFD2

POD2

DERIVERY UNI T

POM

HPOS

ADMH

TH1_FU

TH2_FU

TH3_FU

FUSER UNIT

APPD1

APPD2

RIGHT DOOR UN IT

MPWD

DSW_ADU

MANUAL PAPER FEED UNIT

MPFD

MPED

TH/HUD_ M

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 1

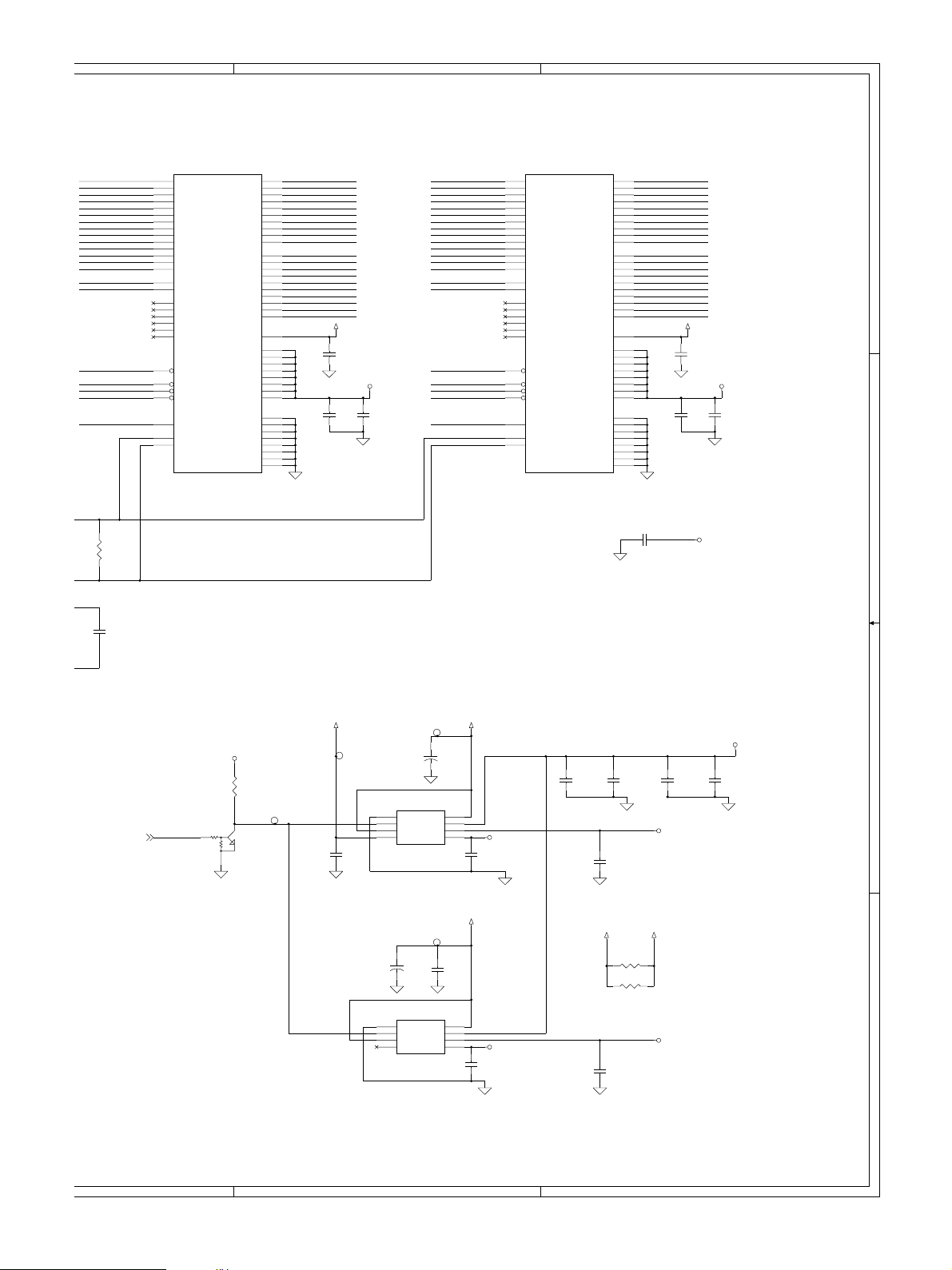

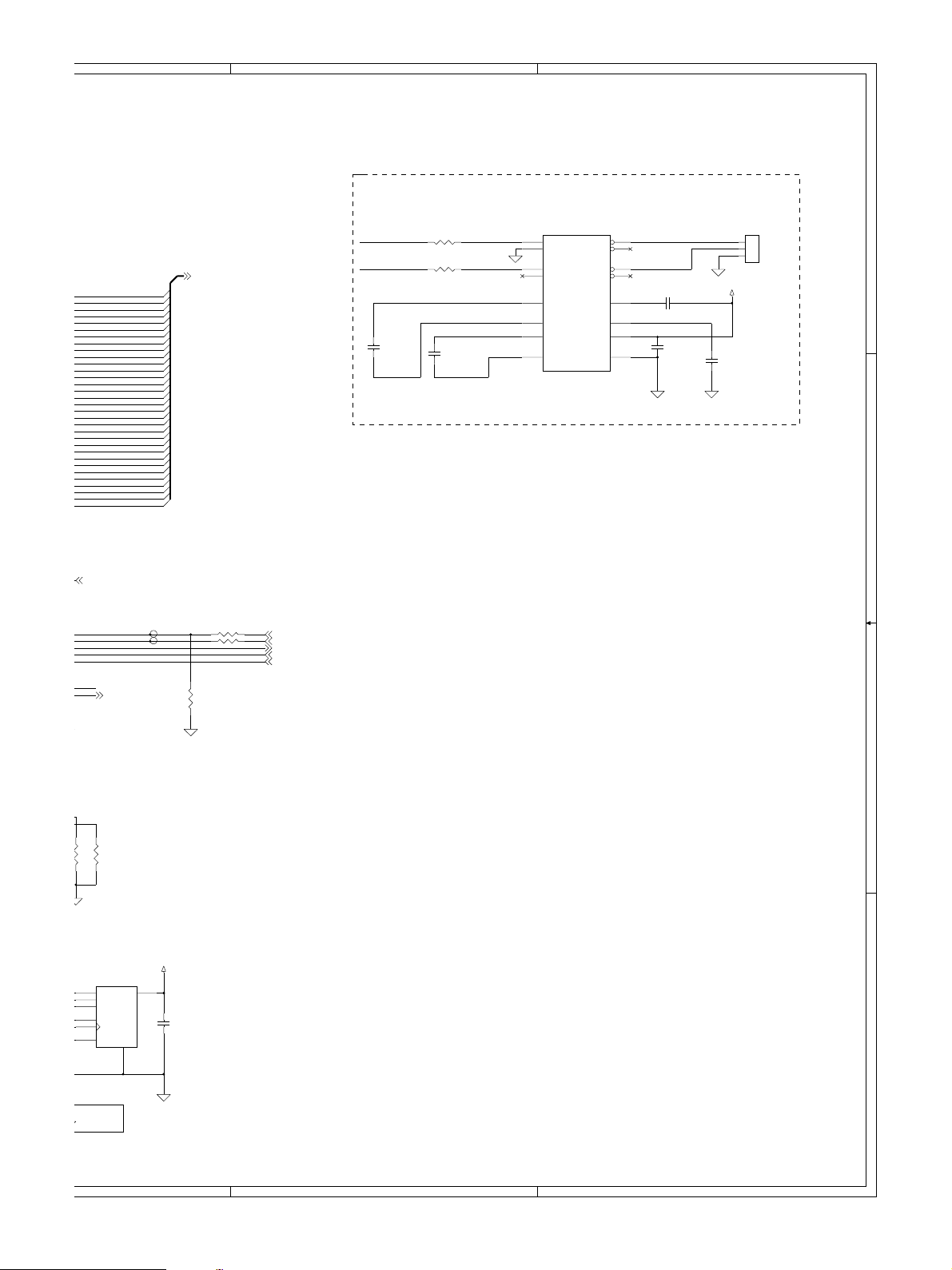

Page 4

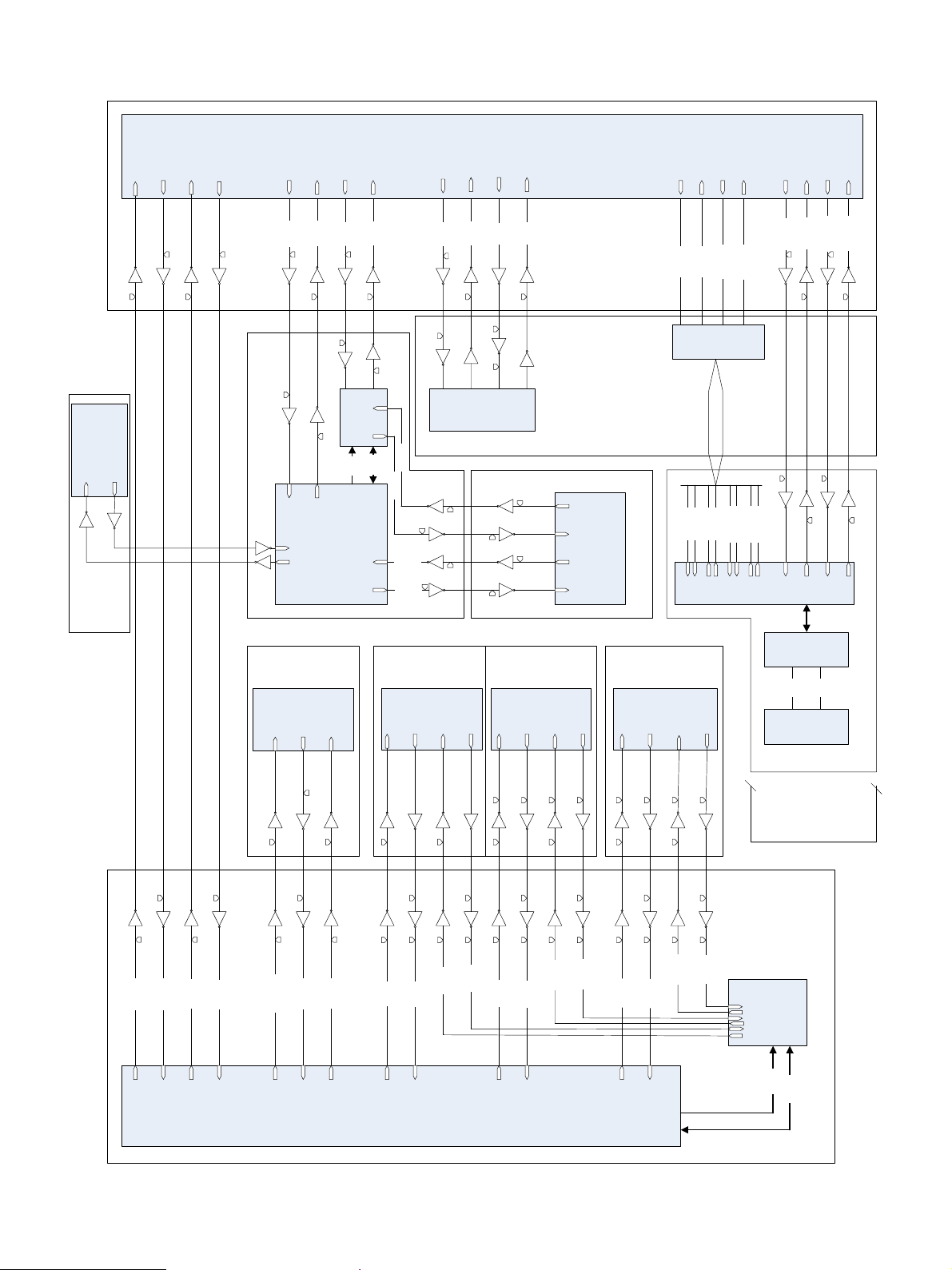

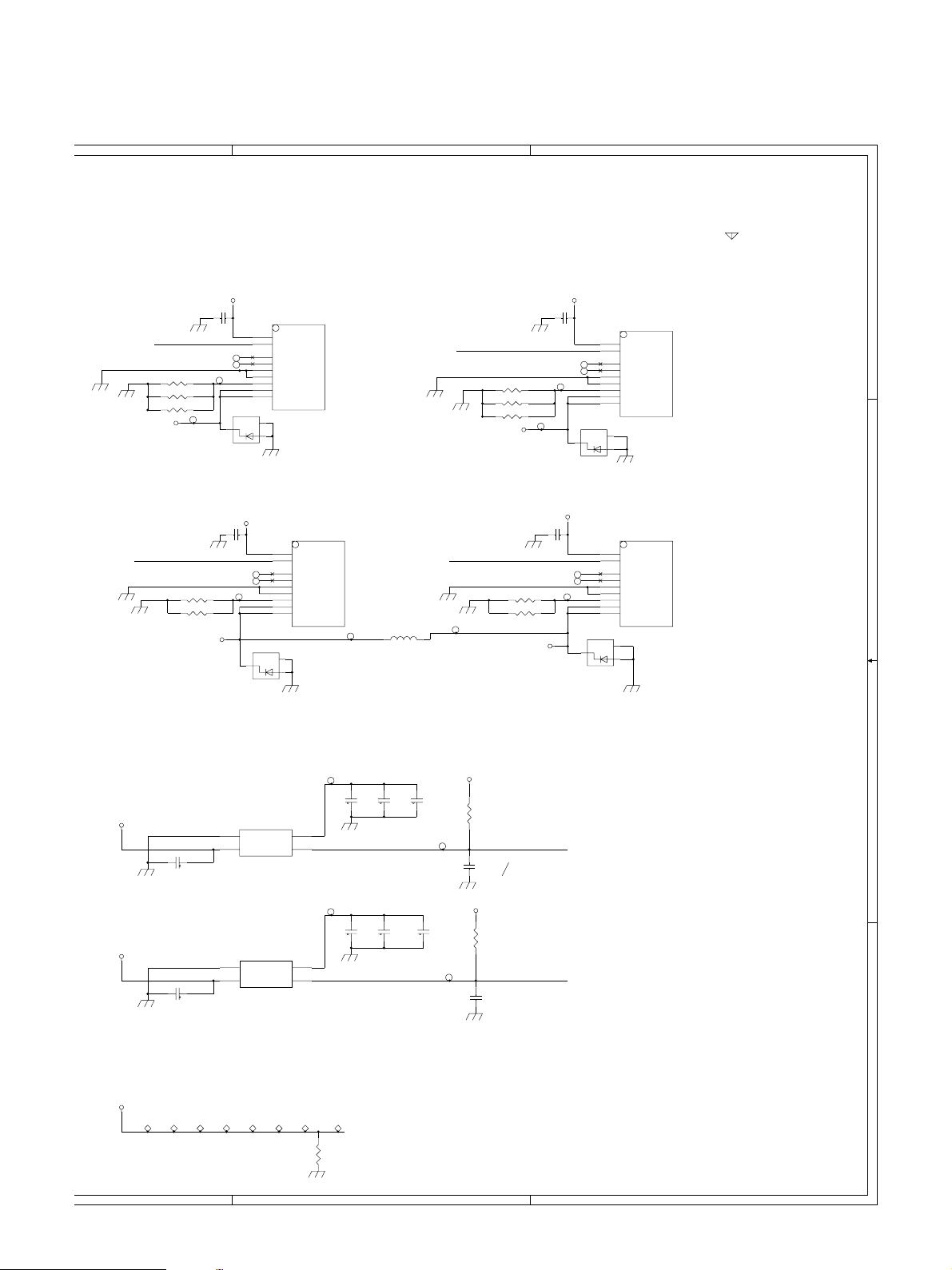

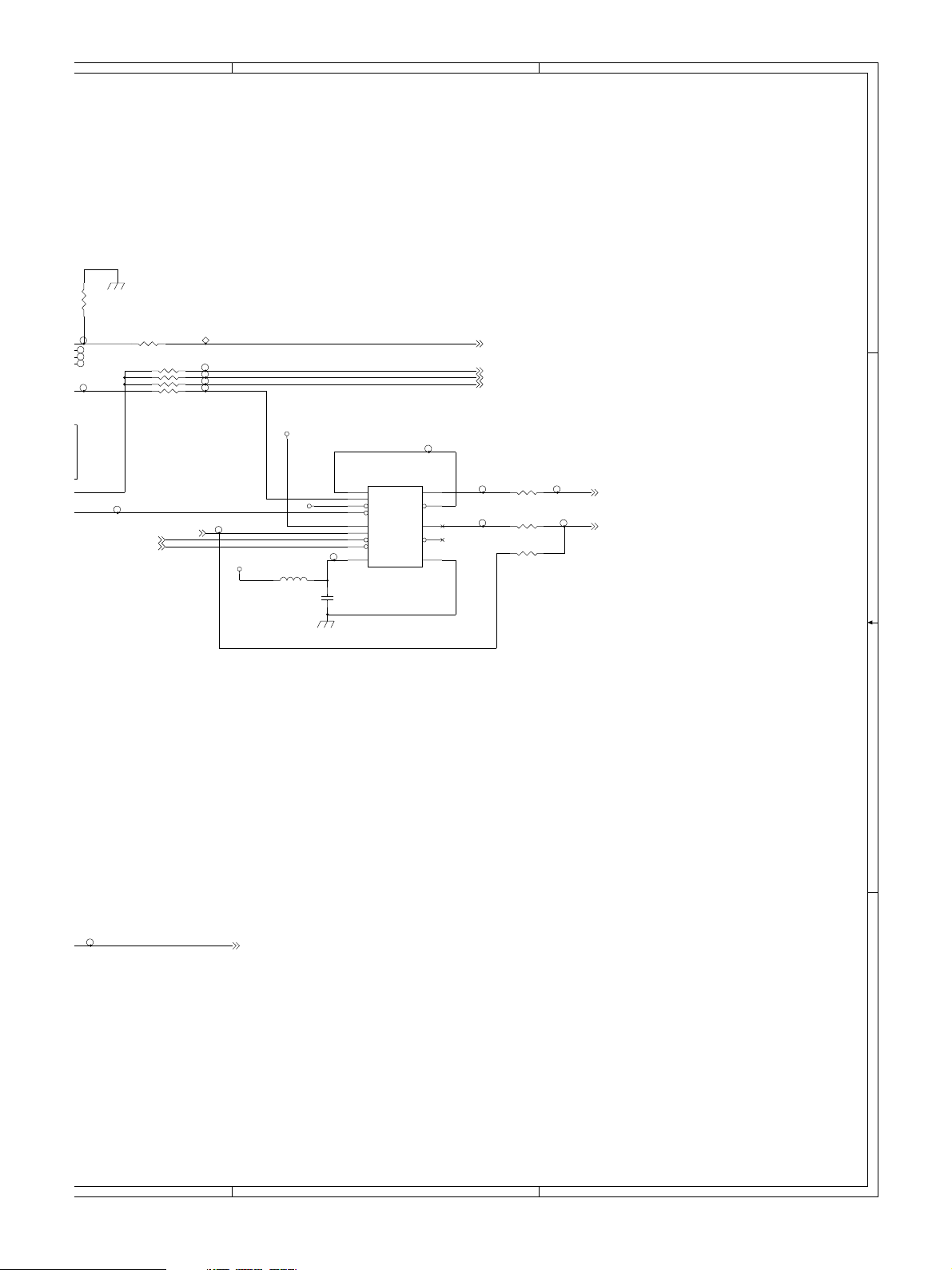

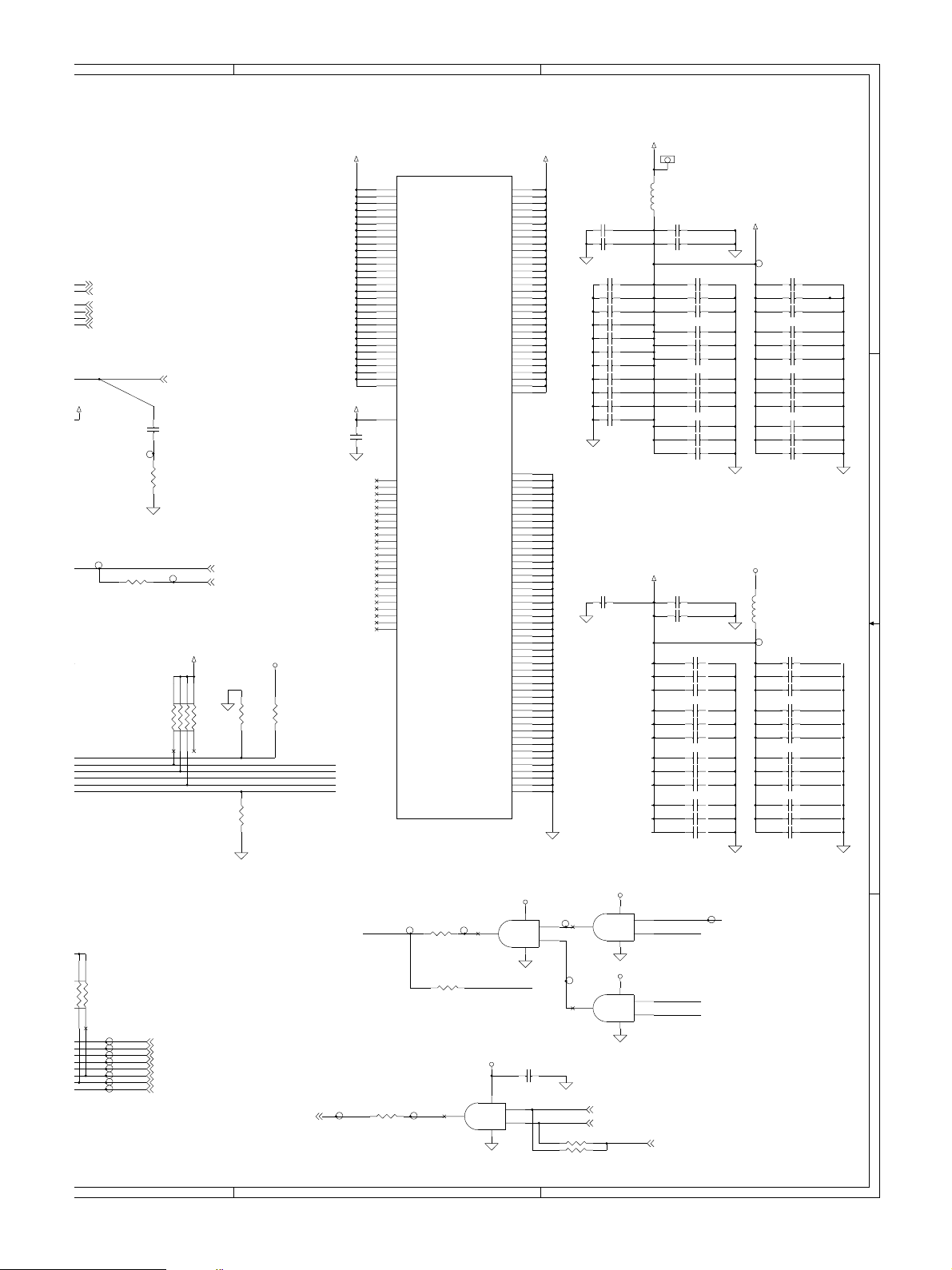

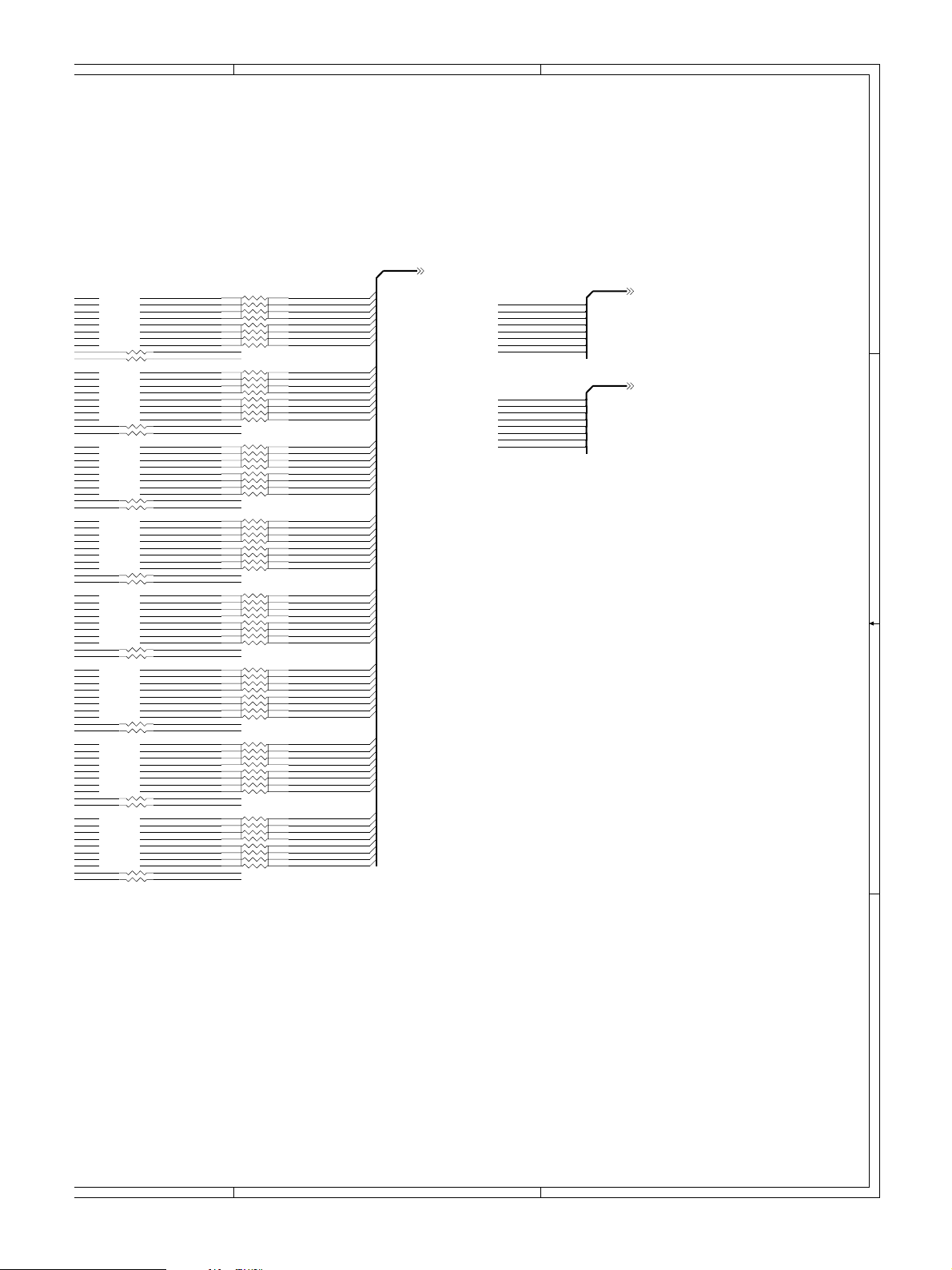

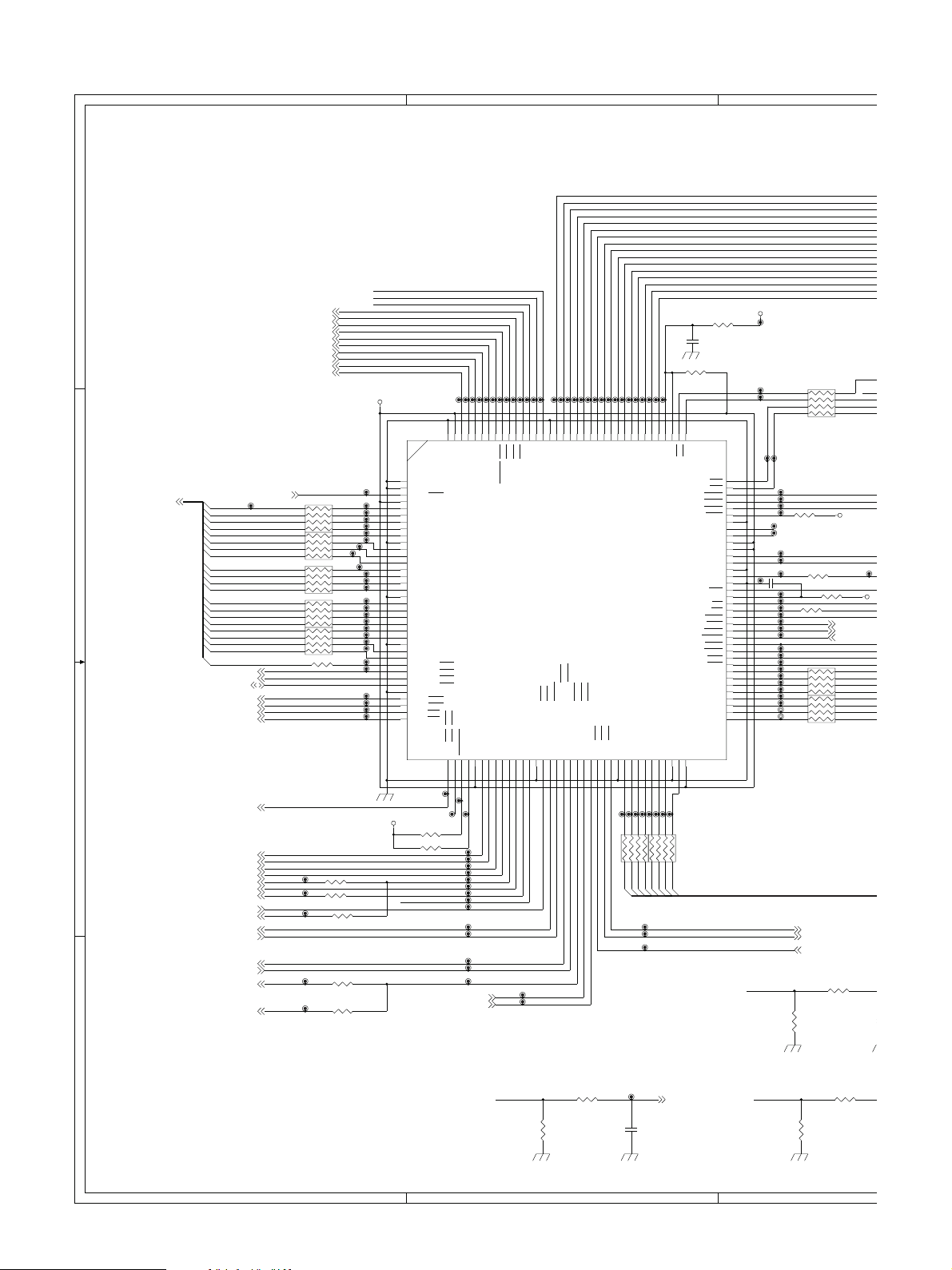

2. MFP CONTROLLER PWB / MFP コントローラ PWB

I2C(Ch.0)

Piano

SW

USB

DEV

USB

HOST

LAN

JACK

RIC

(RS232C)

DIMM2

SO-DIMM

SO-DIMM

EEPROM

256Kbits

Expansion

PCI connector

USB-D

USB-H

VBUS

SW

Ether

MAC

LAN

EEPROM

2Kbits

RS232C

Transceiver

DDR

SDRAMx2

32bits width

DDR bus 1

DIMM1

I2C(Ch.0)

I2C (Ch.1)

MicroWire

DDR bus 2

64bits width

UART

RM7065C

RM7965

PCI bus 1

EEPROM

2Kbits

CPU

SYSAD bus

SYSTEM

VIDEOIF

ASIC

574

X5

EFI connector

244/

245

IF

ASIC

I2C

SDR

SDR

SDRAM

LOCAL bus

(ROM bus)

72pinDIMM Socket

72pinDIMM Socket

72pinDIMM Socket

100pinDIMM Socket

UART

for Debug

PCI bus 2

SCAN OUT IF

(Image process)

LOCAL bus

(LSI bus)

connector

IMG-C Bus

EXPAND

FLASH

Mem.x2

ATA

IDE

ASIC

ICU

ASIC

IMG

ASIC

IO

IDE bus

IMG-B Bus

(Image process)

ICU-IMG IF

FLASH IF

DDR bus 3

64bits width

LSU IF

SCAN IN IF

Patch

IMG-A Bus

(Auto Color)

FLASH

Control

signals

OPE IF

UART

RTC

SRAM

Battery

DIMM4

DIMM3

SO-DIMM

SO-DIMM

LVDS

LVDSIC

385/386/047/048

ENGINE IF

PCU

SCN

FAX 1st

UART

FAX

2nd

connector

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 2

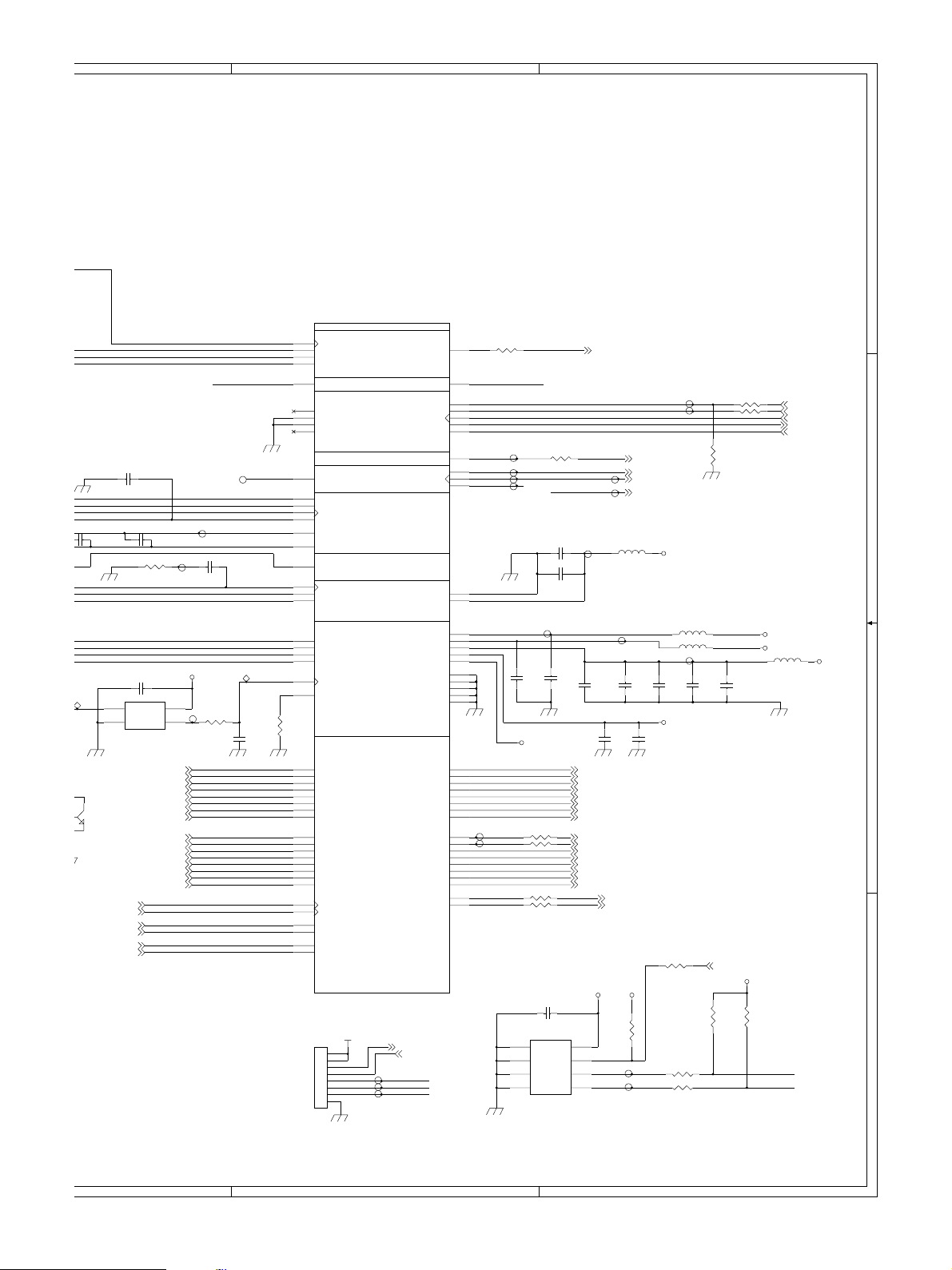

Page 5

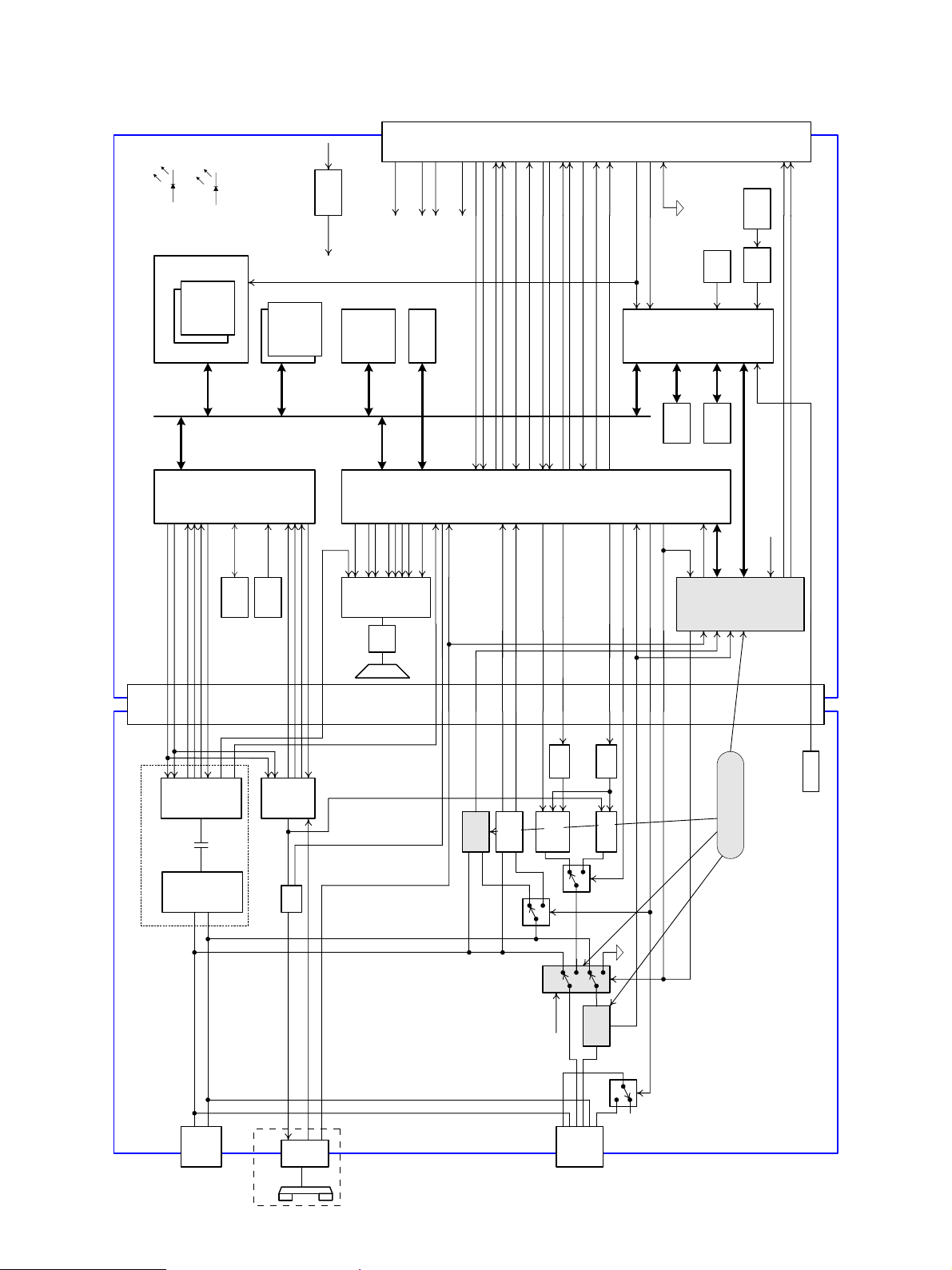

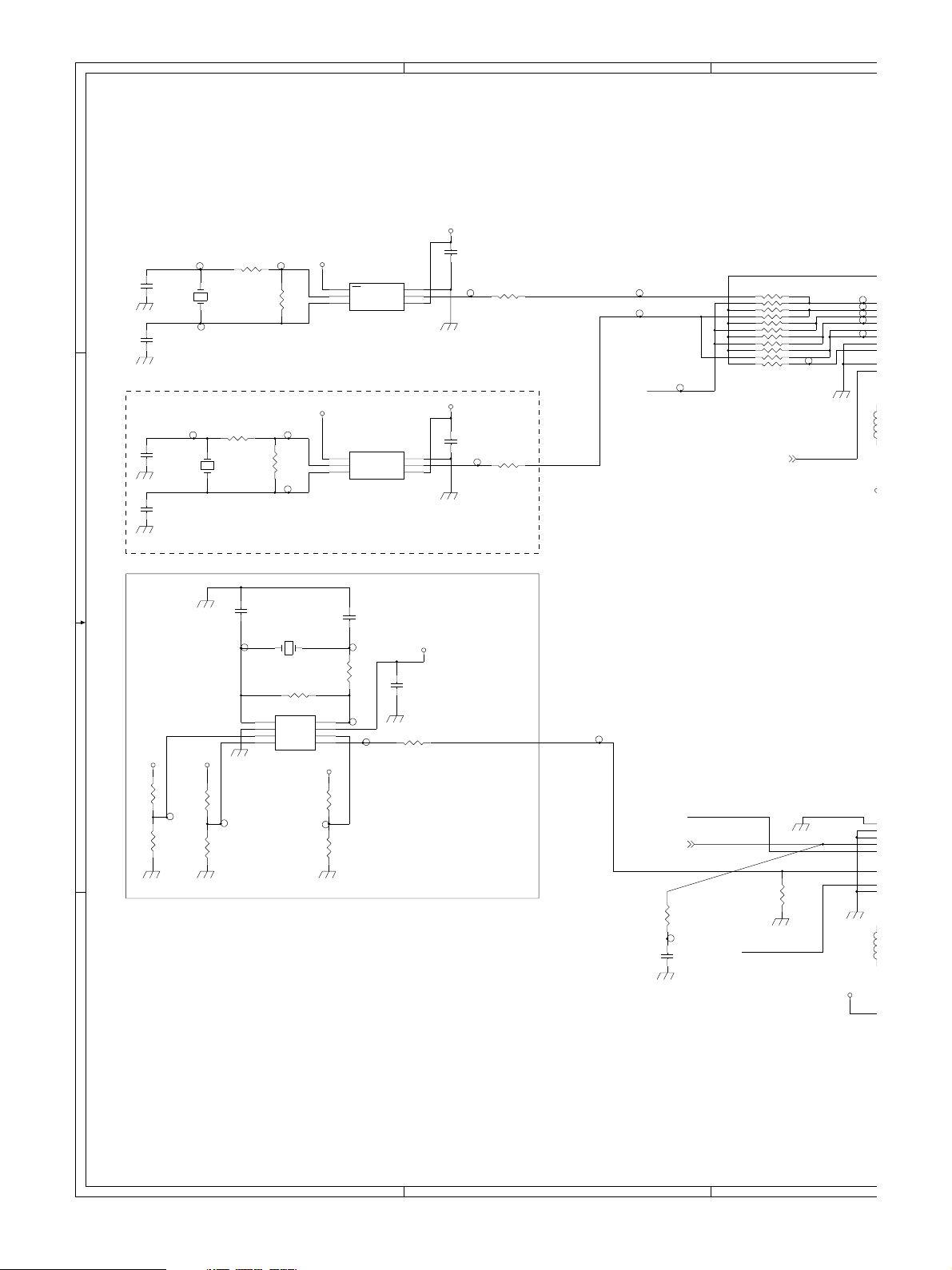

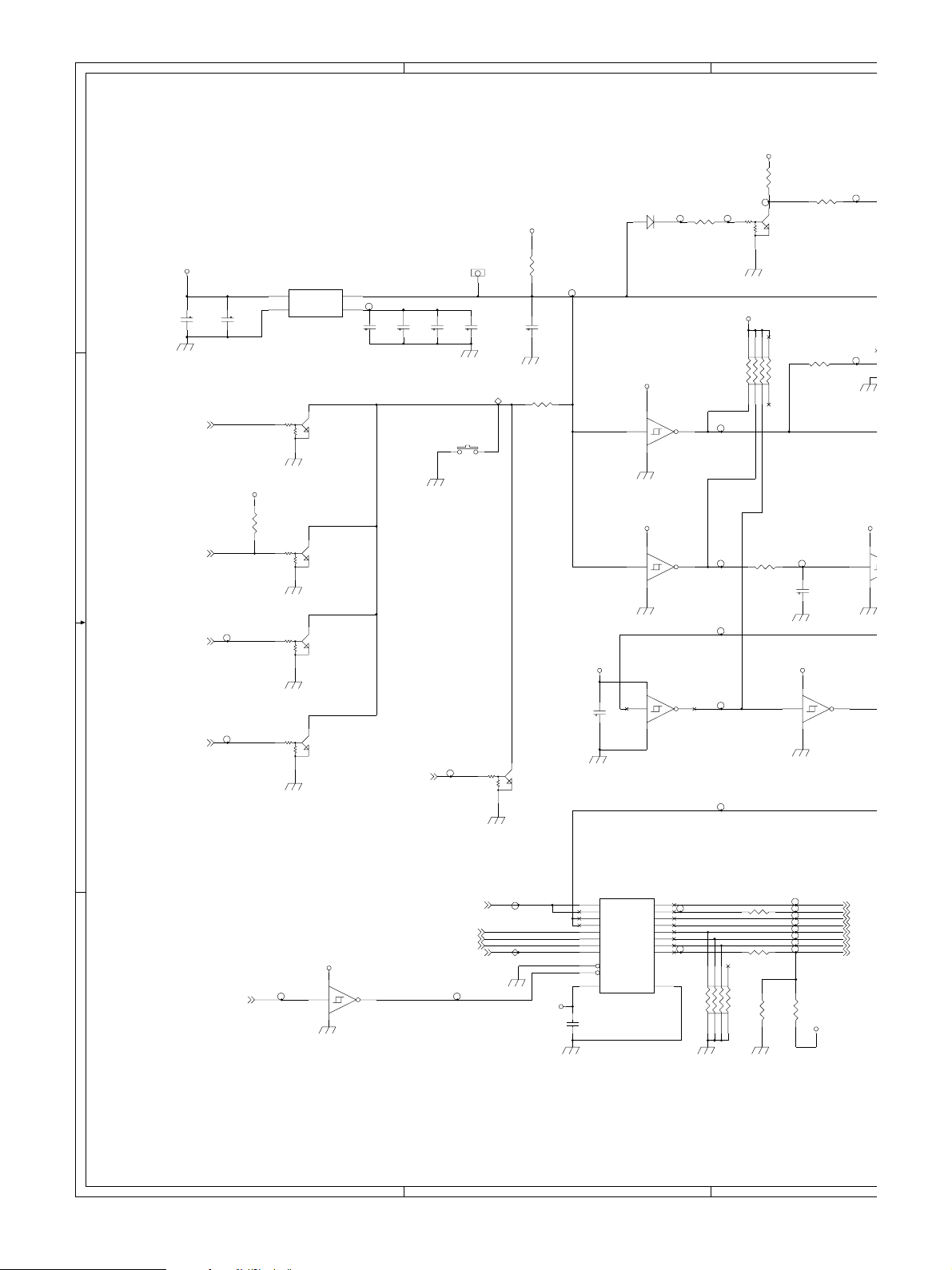

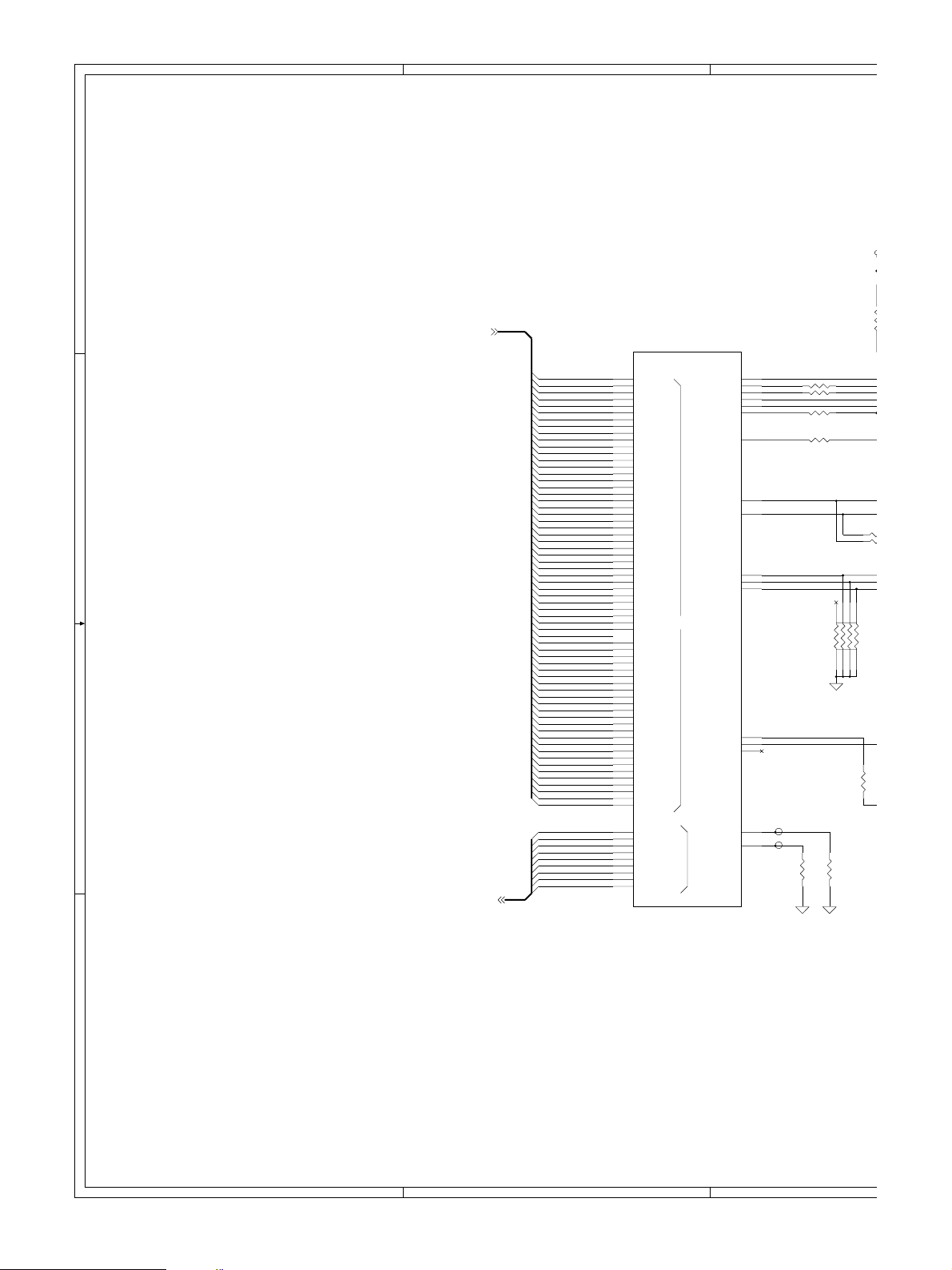

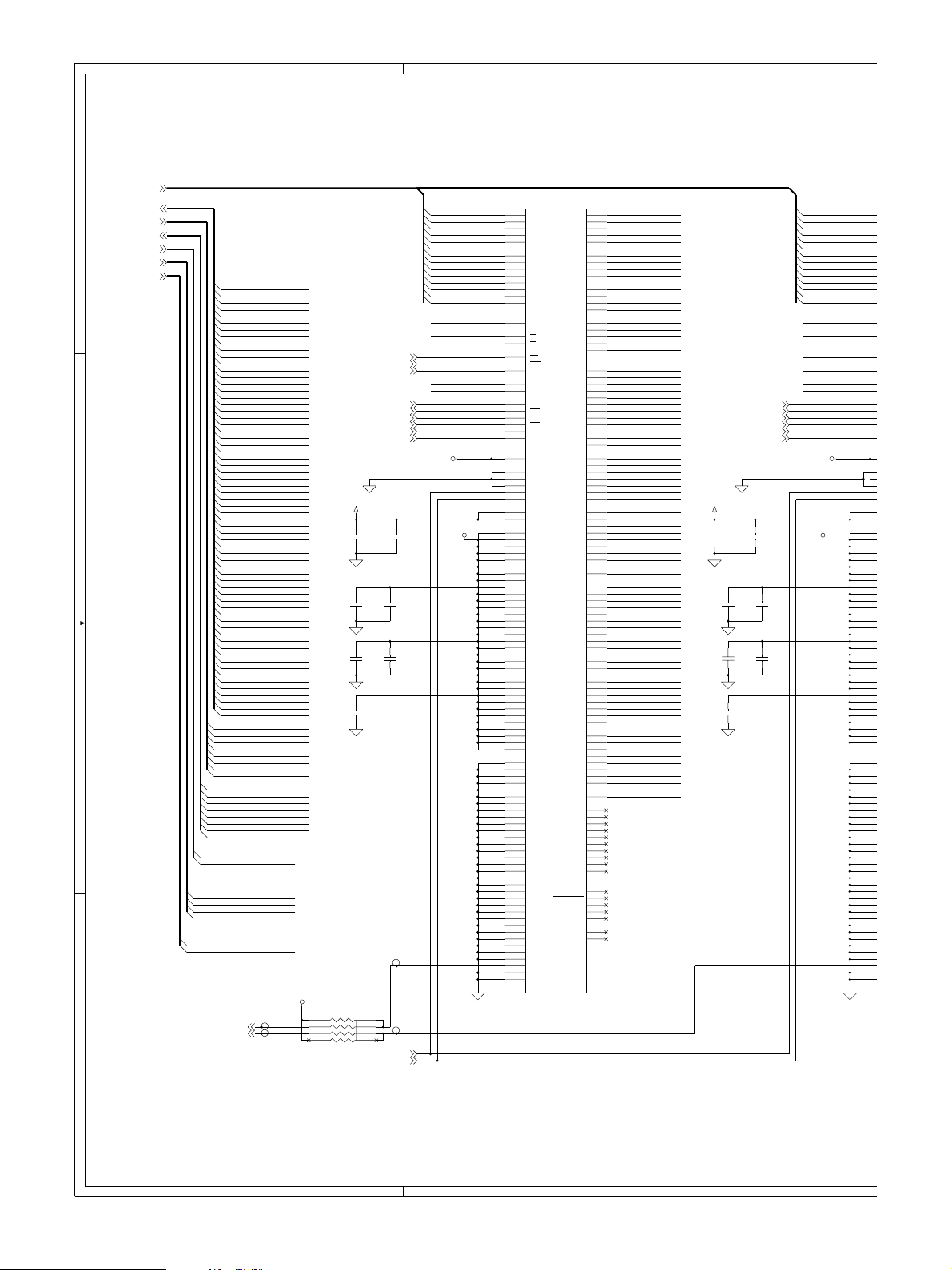

3. PCU PWB

Drum Mot or B K(DM_K) /

Resist Motor(RRM) / PSF Motor(PFM)

MC / TC unit

HL c ont rol

HL_UM/ LM/ US

IC6

EEPROM

s

u

B

I2C

Drum Mot or CL(DM_CL)

(64kbit)

PS FAN (PSFM) /

FAN Mot or Cont rol

BeltMotor (BTM)

Fuser Mot or(FUM)

DC Mo to r Co nt rol

DV Mot or BK(DVM_K)/

DV Mot or CL (DVM_CL)

Paper Feed Mot or(CPFM)

Shifter Motor(OSM)/

Stepping Motor Control

Pout Motor(POM) / ADU Motor(ADML) /

HV

Fuser unit

Count er

PNC_CL

PNC_K /

(Optional)

Mech anical

Load output

Pout FAN

(POFM_F/ POFM_R)

Ozone FA N(OZFM) /

Dru m Lamp

(DL_K/C/M/Y)

(Optional)

CV_COPY

Sensor Input

CV_CLCOPY /

COIN VENDOR

POD3 / POD2

Sensor Input

CLUD1 / CL UD2 /

CSPD1 / CSPD2/

POD1

Sensor Input

APPD1 / APPD2

CSS11- 14 / CSS21- 24

PWM

/LSUSS2(Optional)/

PCSS/ CPFC / LSUSS1

Load control Output

MPUC / MPFS / 1TURC

MPGS / CPU C1 / C PUC2/

DHPD_CL/ DHPD_K /

DSW_F / DSW_R/DSW_C/

CPFD1 / CPFD2/ HPOS / PPD1 /

1TUD_K /1TUD_CL

Sensor Input

DVSET (K/C/M/Y)

MUX

DRDET (K/C/M/Y)

HC151

Toner Motor

(TNM_K/C/M/Y)

Syncronous Motor

Waste Toner Motor(WTNM)

DC Mot or

Lift Up Motor

(CLUM1/CLUM2)

3- wired s erial

r(TH_UM/ LM/ US)

o

AnalogI nput

(FUCLNM)

Fuser Cleani ng Mot or

Sync ronous Mot or

IC9

PMC ASIC

Flash Write Protect

IC5

SRAM

(16Mbit)

FLASH ROM

DATAB us[15:0]

AddressBus[ 20:0]

(1Mbit)

CLOCK

IC8

I/ O A SIC

CRUM

CRUM_K/C/M/Y

s

u

B

C

2

I

IC7

Sensor Input

Mot or Lo ck Det e ct

MPFD/MPED/CPWD11-12

TFD2/ 1TNFD/ WENDD / WINID

CSS1 / CPED2 / CSS2 / CPED1

FAN_LD1- 2 / DVMC_LD / DVMB_LD /

Conv

IC71

D/ A

(TCS/ REGS cont)

DFF

LCX574

(Optional)

Coin v endor

Load Control Output

IC27/ IC30/ IC 31/ IC37

Sensor Input

PFM_LD / FUM_LD

MUX

DSW_ADU/ T FD3 /

THOPEN_UM/ LM/ US

FuserThermistoropendetect

HC151x5

MPLD/ MTOP1/ MTOP2/ MPED

PPD2

Sensor Input

MUX

HC151

RD I/ F PWB

Resist sensor (REGS_F/ R)

Toner Det ect or(TCS_K/ C/ M/ Y)

Fuser Ther mist

Proces s Cont . sensor (P CS_K/ CL )

AnalogI nput

LSU Thermistor(TH1_LSU)

DV det ec tor (DV TYP_C/ M/ Y/ K)

Temp/ Humsensor(TH_M/ HUD_M)

Mult i- bypass t ray wi dth sensor (MPWD)

IC73

MUX

Analog

IC4

RESETIC

IC1

CPU

H8S/ 2373

IC2

X1

Spread

Spectrum

Xt al

19.6608MHz

FW

Supply

DC P ower

UART

To

Via

MFPC

Mot her

UART

To

Via

LSU

Mot her

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 3

Optional

UART

LCC

UART

FINISHER

UART

DESK

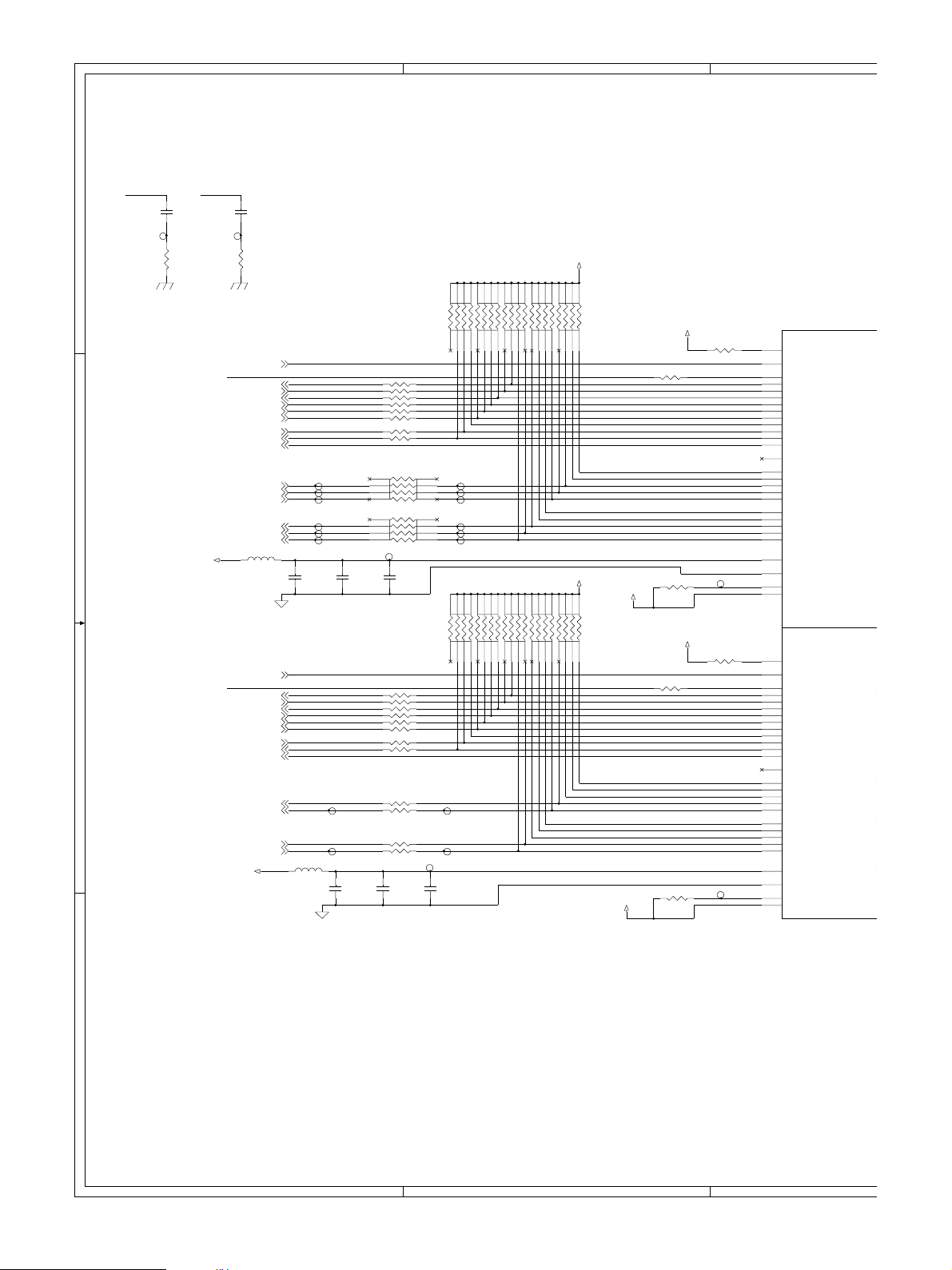

Page 6

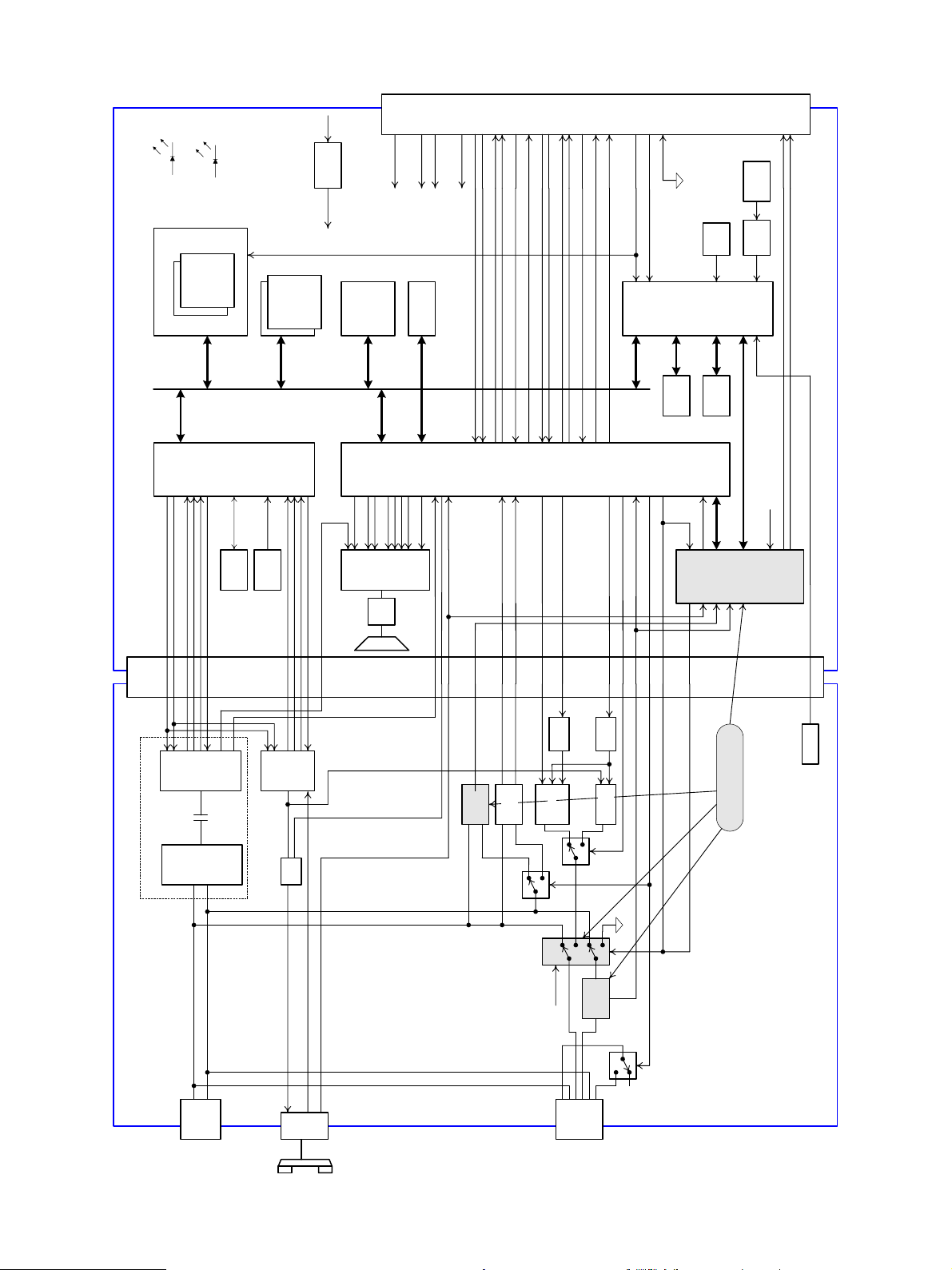

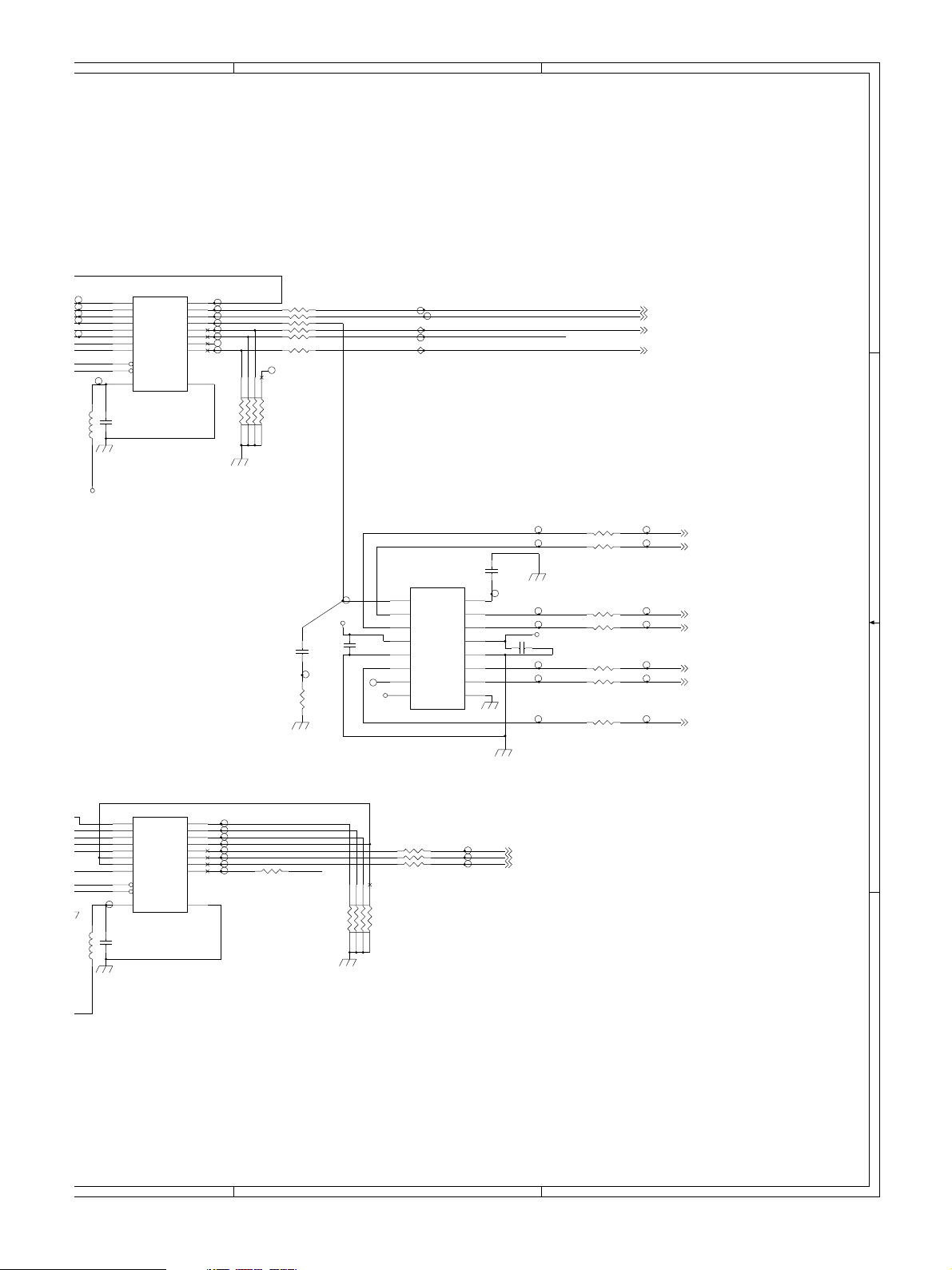

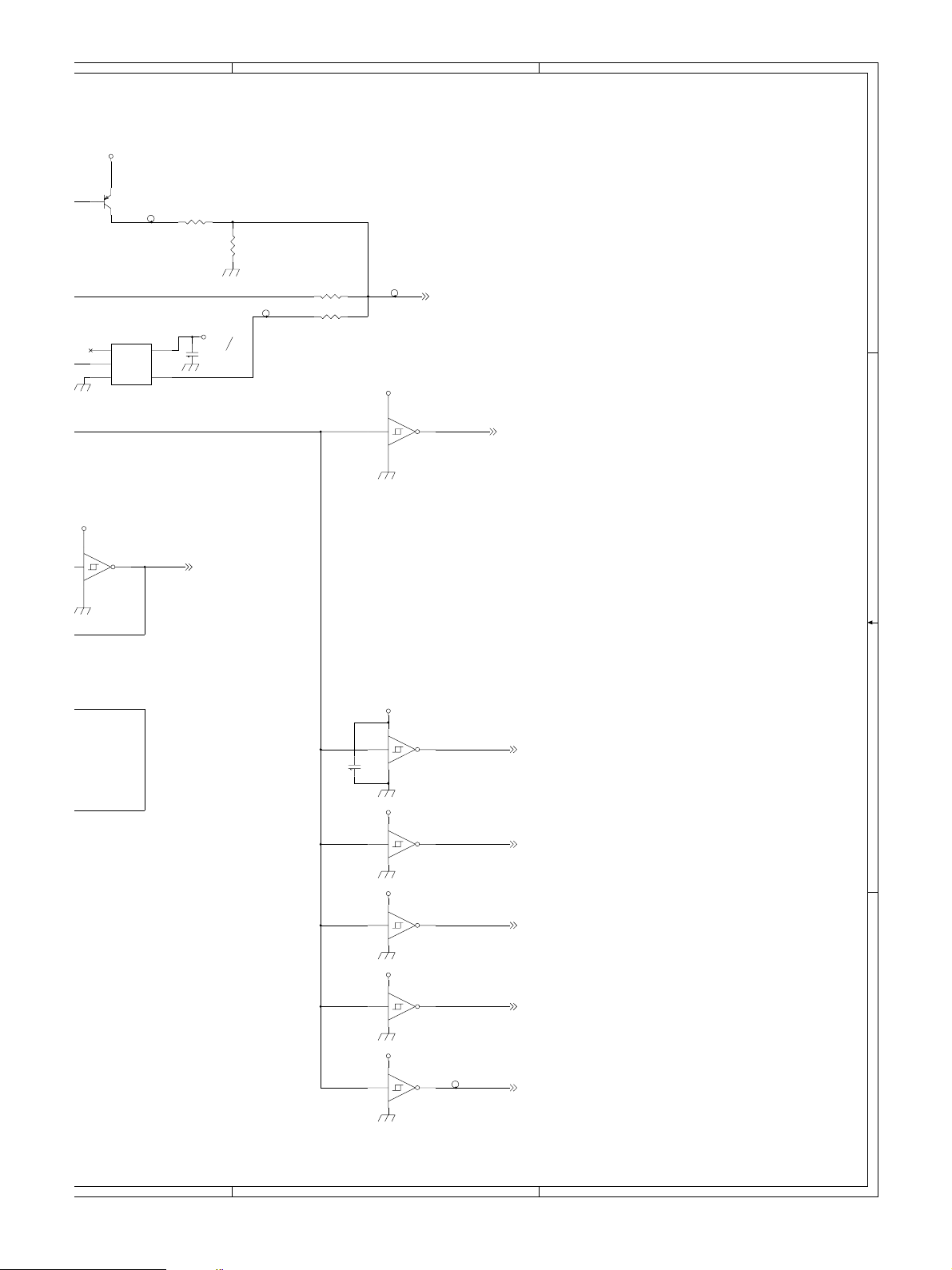

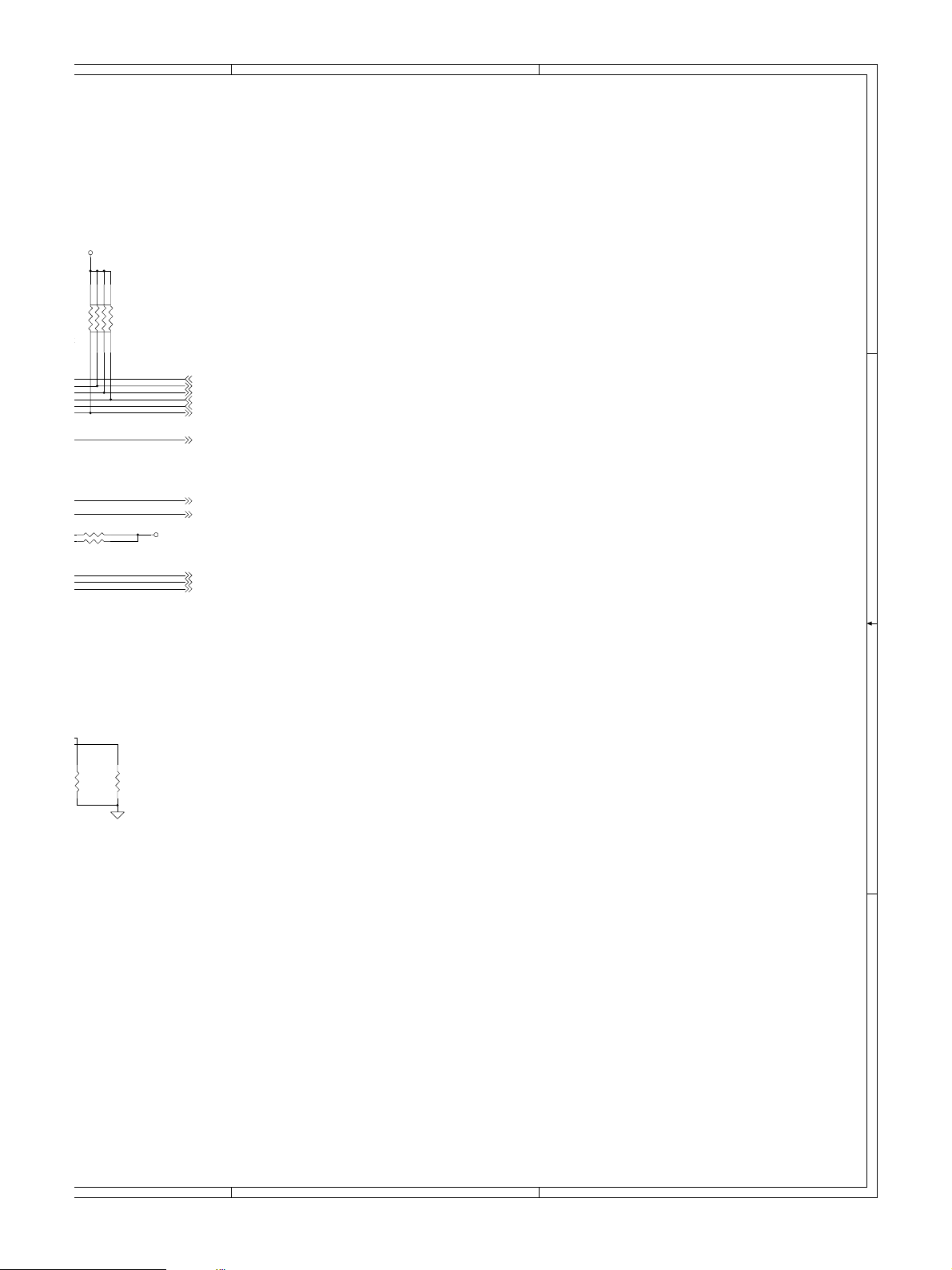

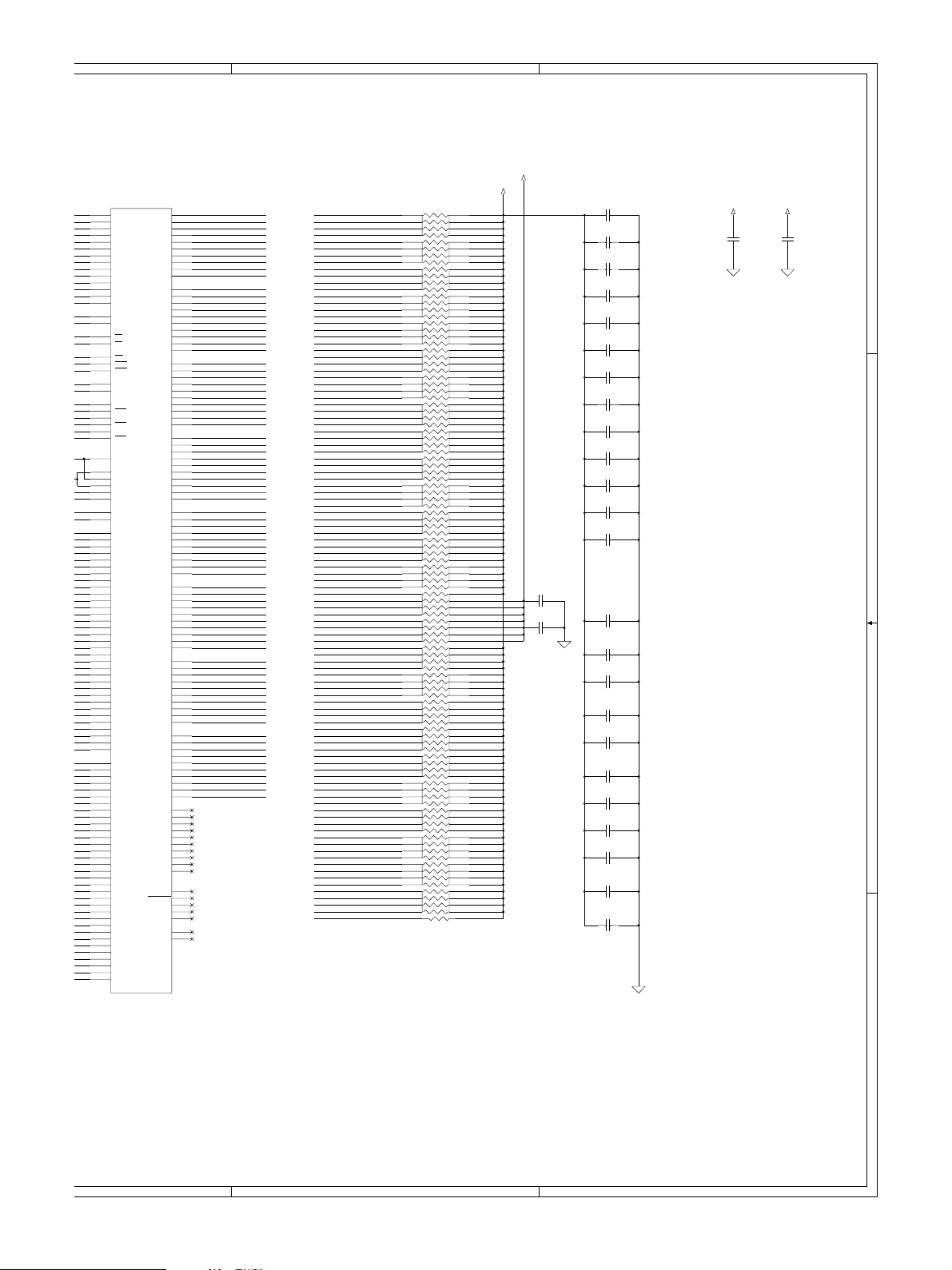

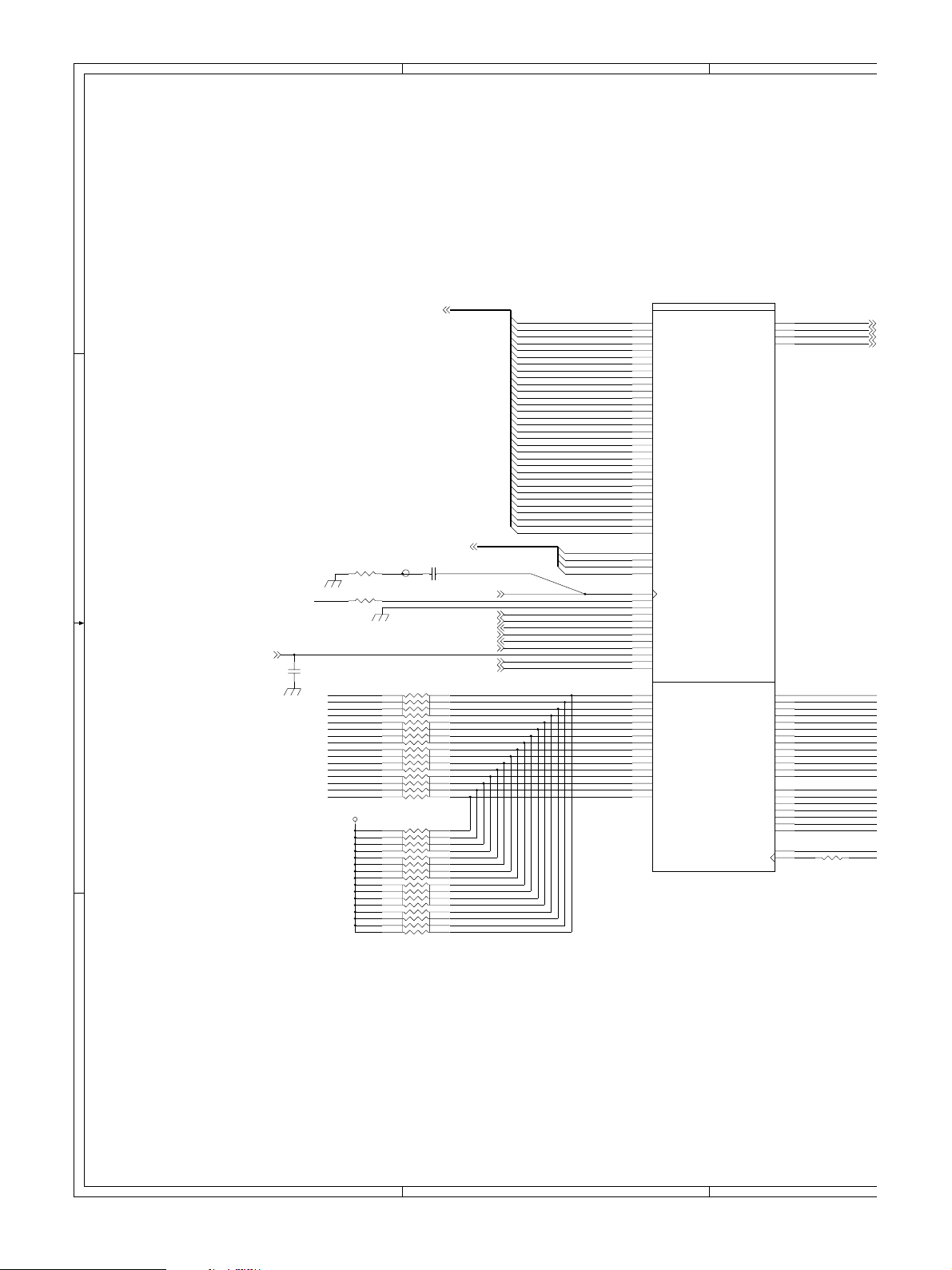

4. SCANNER CONTROL PWB / スキャナコントロール PWB

Or

SCNINPCB

28bit

LVDS Driver

DSPFcntPCB

LVDS

28bit

LVDS Receiver

BUFFER

RGB8bit*3

DSPFMemoryPCB

24bit BUS

BUFFER

24bit BUS

(MFP PCB)

DOCC PCB

Mother PCB

<Engine /Contr oller>

LVDS

28bit

LVDS Driver

/CS4

CPT A SIC

RGB8bit*3

LVDS

CARD READER

/CS5

IO ASIC

AUDITOR

OCSW

ࡔࣂġĩĪ

ࡔࣂġĩอĪ

RGB8bit*3

XTAL

28.795 MHz

or 22.7425MHz

SDRA M

128Mbit

SDRA M BUS

4bit * 2

LVDS Driver

SCNcntPWB

LVDS

4bit * 2

LVDS Receiver

CCD P CB

With AFE& LVDS

30bit

LVDS Receiver

LVDS

30bit

LVDS Driver

/CS3

SCAN ASIC

RGB10bit*3

8Mb it

/CS0

(/ CS0 RESERVE)

FlashROM<So cket>

ADDRESS/ DATA BUS

1Mb it

/CS2

SRAM

LCD

INVERTER PCB

PANEL PCB

I2C

32Kbit

EEPROM

CPU

H8S/2373

XTAL

19. 6608 MHz

MOTOR

SCAN NER

MHPS

LAMP UN

STMP UN

MOTOR

RSPF FEED

CLUTCH

PHOTO

SENSO R

MOTOR

RSPF RVS

RSPF Unit

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 4

Page 7

5. SERIAL COMMUNICATION / シリアル通信

TxD[1]

RxD[1]

P.U.

CTS[1]

RTS[1]

P.D.

O.C.

Schmit Inv.

P.U.

P.D.

O.C.

Schmit Inv.

TxD[2]

nTxD_SCN

RxD[2]

RTS[2]

CTS[2]

CTS_SCN

RTS_SCN

nRxD_SCN

P.D.

O.C.

P.D.

O.C.

Schmit Inv.

P.U.

P.U.

TxD[PIC]

nTxD_PIC

P.D.

O.C.Schmit Inv.

RxD[PIC]

nRxD_PIC

P.U.

CLR[PIC]

CLR_PIC

O.C.O.C

REQ[PIC]

P.U.

REQ_PIC

Schmit Inv.

MFPC

I/F ASIC

TxD[3]

TxD_FAX(D)

RxD[3]

RxD_FAX(D)

TxD[4]

TxD_FAX(CS)

RxD[4]

RxD_FAX(CS)

RTS[3]

DTR_FAX(D)

P.D.

CTS[3]

DSR_FAX(D)

O.C.

P.U.

RTS[4]

DTR_FAX(CS)

Schmit Inv.

CTS[4]

DSR_FAX(CS)

P.D.

O.C.

P.U.

CPU

RxD

DOCC

H8S/2320

TxD

O.C.

Schmit Inv.

(Optional)

Schmit Inv.

SCN Cnt

P.U.

O.C Schmit Inv.

P.U.

O.C

LVDS

PIC

Mother MFPC

P.U.

P.D.

P.U

P.U.

P.U

P.U.

I/O

Schmit Inv.

O.C. O.C.

Schmit Inv.

I/O

P.D.

CPU

H8S/2373

TxDRxD

TxD_FAX(D)+

TxD_FAX(D)-

RxD_FAX(D)+

RxD_FAX(D)-

TxD_FAX(CS)+

TxD_FAX(CS)-

RxD_FAX(CS)+

RxD_FAX(CS)-

New

ASIC

P.U.

O.C

Schmit Inv.

O.C Schmit Inv.

Schmit Inv.

P.D.

P.D.

DSR_SCAN

DTR_SCAN

P.U.

P.D.

RxD_SCAN

P.D.

TxD_SCAN

O.C. O.C. SchmitInv.Schmit Inv.

P.U.

P.U.

O.C

Schmit Inv.

P.D.

TxD

RxD

CPU

RxD

TxD

O.C

O.C Schmit Inv.

Schmit Inv.

P.D.

I/O ASIC

µPD65892GC

A[4:0]

D[15:8]

H8S/2373

TxDRxD

DSPF Cnt (for C-Jupiter)

CPU

TxD

SH7706

RxD

PIC

1st FAX

LSU

LSU ASIC

TxD

RxD

SCK

TxD

RxD

CPU

M30843FWGP

I/O

FINISHER

(Optional)

I/O

RxD

TxD

CPU

H8/3684

I/O

DESK

(Optional)

I/O

TxD

RxD

CPU

H8/3687

I/O

LCC

(Optional)

I/O

(for FG Model)

nPCU_RxD

TxD0

P.D.

O.C.

P.U. P.U.

TxD2

Schmit Inv.

O.C.

TxD_FIN

CPU

P.U.

P.U.

H8S/2373

RSV_DAT

RxD1

Schmit Inv.

Schmit Inv.

P.U.

Schmit Inv.

Schmit Inv.

P.D.

SCK_LSU

SCK1

Schmit Inv.

P.U.

P.U.

O.C.

P.D.

RxD0

Schmit Inv.

nPCU_TxD

PCU_DSR

I/O port

P.U.

O.C.

Schmit Inv.

P.D.

PCU_DTR

I/O port

TRANS_DAT

TxD1

P.U.

Schmit Inv.

P.D.

RxD2

RxD_FIN

Schmit Inv.

P.U.

O.C.

O.C.

P.U.

P.U. P.U.

DTR_FIN

O.C.

O.C.

DSR_FIN

P.U. P.U.

P.U.

TxD3

O.C.

O.C.

TxD_DSK

P.U.

P.U.

P.U.

RxD_DSK

RxD3

P.U.

P.U.

P.U.

PCU

2nd FAX

(Optional)

(same as 1st)

O.C.

O.C.

O.C.

O.C.

P.U. P.U. P.U.

P.U. P.U. P.U.

DTR_DSK

DSR_DSK

O.C.

TxD4

C

C

xD_L

T

O.C.

O.C.

O.C.

O.C.

O.C.

O.C.

O.C.

P.U. P.U.

P.U. P.U.

P.U. P.U.

DSR_LCC

DTR_LCC

C

C

L

_

RxD

RxD4

I/O ASIC

A[4:0]

103

µPD65892GC-

D[15:8]

O.C.

P.U. P.U.

O.C.

P.U.

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 5

Page 8

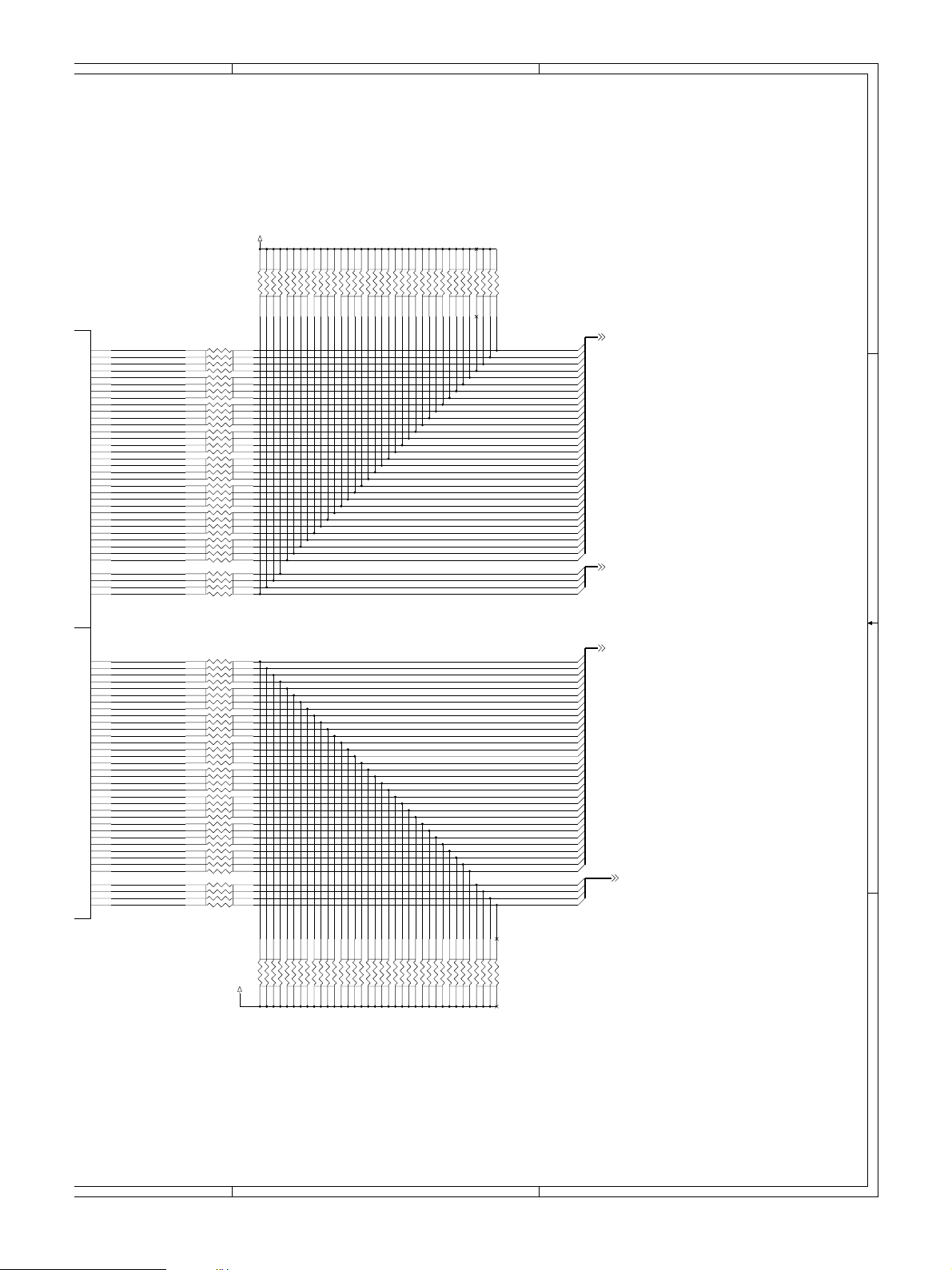

6. FAX

A. Except Japan

FLASH ROM PWB

FAX MAIN PWB

16bit

POWER LED

PROGRAM

32bit

FLASH ROM

IF

MFP

connector

+12V

+5V2

+3.3V

STATUS LED

RESET IC

(PST591IMT)

RESET- +3.3V

RES_FAX-

FAX_RXD(D)+

FAX_TXD(D)+

FAX_TXD(D)-

FAX_RXD(D)-

FAX_CTS(D)-

FAX_RTS(D)-

FAX_TXD(CS)+

FAX_TXD(CS)-

FAX_RXD(CS)+

FAX_RXD(CS)-

FAX_CTS(CS)-

RE S_MFP-

FAX_RTS(CS)-

FFVPP

CNCT_FAX-

MSW_MON-

Voltage

Regulator

1.9V

X’TAL

14.7456MHz

Spred

Spectrum

PLED

WUP_FAX-

8Mb x 2

WORK

32bit

SDRAM

MEMORY

64Mbit x 2

MEMORY

FAX IMAGE

16bit

Not install

FLASH ROM

16bit

16Mbit

E2PROM

(CAT24W02)

I2C

32bit

JTAG

JTAG

debug

connector

CPU

SH7706

UART

Debug

connector

UART

TE/LIU

connector

Silicon DAA

AFE_CLK

Si3044 CHIP SET

AFE_RES-

AFE_ASPCLK

AFE_ABITCLK

AFE_ARXD

AFE_ATXD

Si3021

Si3015

MODEM

(MN195006E)

2bit

connector

EYE pattern

X’TAL

24.576MHz

AFE_BSPCLK

AFE_BBITCLK

AFE_BRXD

VOICE

Si3000

CODEC

MSG(Analog)

AMP

AFE_BTXD

SPK(Analog)

BZ

Speaker

EN_BZON-

EN_SPKON-

circuit

Speaker

Speaker

VOLA

VOLB

VOLC

Sound

Input select

connector

VOLD

volume

SPMUTE-

detection

RGDT-(CI detection)

RHS-

HDMUTE-

CI-

CI

detection

circuit

HS1-

Pola rit y

HS2-

reversal

detection

MR relay

NEW ASIC

CION

150VON

-150V

DCDC

ringer

Pseudo-

EC relay

48VON

48V

DCDC

output circuit

Voice message

ECON

EXHKD-

MRON

SON1

SON2

CID-

Download

PIC

Operation in 1W/7W

+5V2

(PIC16F627A)

microcomputer

energy-save mode

TELID

Voltage level

LIU PWB

MJ1

(LINE)

Srelay

+5V2

Externally-

detection circuit

connected hook

Speaker

Microphone

OFF fook detection

BT relay

MJ2

(TEL)

Handset

(Japan only)

Handset

connector

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 6

Page 9

B. Japan

FAX MAIN PWB

FLASH ROM PWB

16bit

POWER LED

PROGRAM

32bit

IF

MFP

Υ·Η

+12V

+5V2

+3.3V

E2PROM

(CAT24W02)

I2C

RES_FAX-

FAX_RXD(D)+

FAX_TXD(D)+

FAX_TXD(D)-

FAX_RXD(D)-

FAX_CTS(D)-

FAX_RTS(D)-

FAX_TXD(CS)+

FAX_TXD(CS)-

FAX_RXD(CS)+

FAX_RXD(CS)-

FAX_CTS(CS)-

STATUS LED

8Mbȿ2

FLASH ROM

WORK

32bit

SDRAM

MEMORY

64Mbitȿ2

RESET IC

(PST591IMT)

RESET- +3.3V

MEMORY

FAX IMAGE

16bit

ྚ

FLASH ROM

16Mbit

16bit

RE S_MFP-

FAX_RTS(CS)-

FFVPP

32bit

CNCT_FAX-

MSW_MON-

JTAG

JTAG

DŽǟNjǟưƹƻljƹǁ

CPU

Voltage

1.9V

SH7706

UART

DŽǟNjǟưƹǟ

Regulator

ǔLJǁƻljƹǁ

X’TAL

14.7456MHz

Spred

Spectrum

PLED

WUP_FAX-

UART

TE/LIU

Υ·Η

ΏςϋDAA

Si3044 CHIP SET

AFE_CLK

AFE_RES-

AFE_ASPCLK

AFE_ABITCLK

AFE_ARXD

AFE_ATXD

Si3021

Si3015

MODEM

(MN195006E)

2bit

Υ·Η

EYEΩΗȜϋ

X’TAL

24.576MHz

VOICE

AFE_BSPCLK

AFE_BBITCLK

AFE_BRXD

AFE_BTXD

Si3000

CODEC

MSG(Ʋdžǜƹǟ)

AMP

NEW ASIC

BZ

VOLA

VOLB

VOLC

VOLD

SPMUTE-

EN_BZON-

EN_SPKON-

ٝႹ

වႁ୨ఢ

إၾ୨ఢ

ΑάȜȜ

ΑάȜ

Υ·Η

ΑάȜȜ

SPK(ͺυΈ)

RGDT-ĩCIĪ

RHS-

HDMUTE-

CI-

HS1-

HS2-

CION

150VON

48VON

ECON

EXHKD-

MRON

48V

-150V

DCDC

DCDC

SON1

SON2

CID-

Θ;ϋυȜΡ

PICζͼϋ

(PIC16F627A)

+5V2

TELID

ഩգτασ

൲

ٝႹ

ٝႹ

CI

ޭ

݀যςϋ΄

ႁٝႹ

إǓưƿƱƽǟ

1W,7WજΥκȜΡশ

ECςτȜ

MRςτȜ

LIU JPN PWB

MJ1

(LINE)

SςτȜ

+5V2

ٝႹ

ٸ୪έΛ·

ΑάȜ

ζͼ·

OFFέΛ·

BTςτȜ

MJ2

NjǞDžǟƿưDž

Υ·Η

(TEL)

ΧϋΡΓΛΠ

MX-3500N/4500N/3501N/4501N BLOCK DIAGRAM / ブロック図 1 – 7

Page 10

CP30

Q3

DTC114YUA

E

B

C

10K

47K

CP36

D41 X_1SS355

AK

CP280

TP12

HK-4

R9 21.0KF

D45 X_1SS355

AK

R12 267KF

CP25

D2

LT1F67AF

AK

CP29

MOD5

MPD-0634B

VIN_5V

1

ONxOFF

2

N.C.

4

N.C.

5

GND

6

GND

7

ADJ

8

VOUT

9

VOUT

10

3PIN : NONE

4,5PIN Must be left N.C.

CP279

R19

470J

C2

10uF(2012)

R5 1.50KF

TP14

HK-4

D42 X_1SS355

AK

CP34

Q2

DTC114YUA

E

B

C

10K

47K

CP43

D44 X_1SS355

AK

D36

RB461F

K

N

A

CP14

D1

LT1 F6 7 AF

AK

TP11

HK-4

CP15

CP48

R1 3.16KF

TP5

HK-4

R18

470J

C9

10uF(2012)

CP18

CP22

CP47

R2 1.50KF

MOD1

MPD-0634B

VIN_5V

1

ONxOFF

2

N.C.

4

N.C.

5

GND

6

GND

7

ADJ

8

VOUT

9

VOUT

10

3PIN : NONE

4,5PIN Must be left N.C.

TP8

HK-4

CP16

R13 267KF

TP6

HK-4

D32

RB461F

K

N

A

D3

LT1F67AF

AK

D47 X_1SS355

AK

C10

10uF(2012)

CP46

TP15

HK-4

D33

RB461F

K

N

A

CP40

CP281

D48 X_1SS355

AK

D46 X_1SS355

AK

C1

10uF(2012)

TP9

HK-4

CP42

R14 21.0KF

D43 X_1SS355

AK

R17

470J

MOD6

MPD-0634B

VIN_5V

1

ONxOFF

2

N.C.

4

N.C.

5

GND

6

GND

7

ADJ

8

VOUT

9

VOUT

10

3PIN : NONE

4,5PIN Must be left N.C

R4 3.16KF

CP31

R104 21.0KF

Q1

DTC114YUA

E

B

C

10K

47K

D37

RB461F

K

N

A

CN27

BM06B-SRSS-TB

1

1

2

2

3

3

4

4

5

5

6

6

TP4

HK-4

TP13

HK-4

CP26

TP10

HK-4

CP13

MOD2

MPD-0634B

VIN_5V

1

ONxOFF

2

N.C.

4

N.C.

5

GND

6

GND

7

ADJ

8

VOUT

9

VOUT

10

3PIN : NONE

4,5PIN Must be left N.C

TP7

HK-4

DC_ON_OFF_CTL_CORE

DC_ON_OFF_CTL_CORE

DC_ON_OFF_CTL_CORE

DC_ON_OFF_CTL_IO

CPU_CORE1.3V

+1.8V

ISC_CORE1.2V

+5V_IN

+3.3V

DGND

DGND

DGND

DGND

DGND

DGND

DGND DGND

+5V_IN

+5V_IN

+5V_IN

DGND DGND

DGND

DGND

+3.3V +3.3V +3.3V

DGND

DGND

+5V_IN

DGND

DGND

DGND

DGND

DGND

DGND

CPU_CORE1.3V

ISC_CORE1.2V

SYSTEM2.5V

+2.5VEAST

+3.3V

+1.8V

+1.2VICU

+1.2VIMG

+5V_IN

+5V_IN

+5V_IN

+5V_IN

+5V_IN

+5V_IN

+5V_IN

+5V_IN

GPO_LED1_ON{43}

GPO_LED2_ON{43}

GPO_LED3_ON{43}

5

5

4

4

3

3

D

C

B

A

MFPC PWB (DC power)

MX3500N

[2] CIRCUIT DIAGRAM / 回路図

Circuit Diagram

1. MFP CONTROLLER PWB / MFP コントローラ PWB

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 1

Page 11

e

e

3

2

1

1/42

AS1

QPWBX1673FCZZ

3PIN : NONE

+5V_IN

ft N.C.

DGND

DGND

SYSTEM2.5V

R3 68.1KF

R6 68.1KF

R105 68.1KF

C3

10uF(2012)

DGND

DC_ON_OFF_CTL_IO

CP27

CP19

CP17

CP23

K

10

RB461F

N

A

D34

1

2

4

5

6

7

8

9

MOD4

VIN_5V

ONxOFF

N.C.

N.C.

GND

GND

ADJ

VOUT

VOUT

MPD-0634B

DGND

4,5PIN Must be left N.C.

DGND

DC_ON_OFF_CTL_IO

R7 68.1KF

R8 68.1KF

DGND

R112 68.1KF

+2.5VEAST

C4

10uF(2012)

DGND

CP28

+5V_IN

CP20

CP21

CP24

K

RB461F

D35

10

N

A

3PIN : NONE

+5V_IN

ft N.C.

DC_ON_OFF_CTL_CORE DC_ON_OFF_CTL_CORE

DGND

DGND

C11

10uF(2012)

R10 1.50KF

R15 1.50KF

+1.2VICU

DGND

CP32

CP37

CP38

K

4,5PIN Must be left N.C.

MOD7

1

VIN_5V

2

ONxOFF

4

N.C.

5

N.C.

6

GND

7

GND

8

ADJ

9

VOUT

10

VOUT

MPD-0634B

RB461F

N

A

D38

DGND DGND

CP44

12

L1

X_BLM21PG600SN1(2012)

DGND

CP41

R11 1.50KF

DGND

R16 1.50KF

10uF(2012)

+1.2VIMG

C12

DGND

+5V_IN

CP35

CP33

CP39

10

RB461F

K

D39

1

2

4

5

6

7

8

9

1

2

4

5

6

7

8

9

MOD3

MOD8

N

A

VIN_5V

ONxOFF

N.C.

N.C.

GND

GND

ADJ

VOUT

VOUT

MPD-0634B

DGND

VIN_5V

ONxOFF

N.C.

N.C.

GND

GND

ADJ

VOUT

VOUT

MPD-0634B

3PIN : NONE

4,5PIN Must be left N.C.

3PIN : NONE

4,5PIN Must be left N.C.

D

C

+5V_IN

+5V_IN

DGND

DGND

C20

0.1uF(B)

C24

0.1uF(B)

CP45

C18

C17

0.01uF

CP50

0.01uF

DGND

C21

0.01uF

DGND

C22

X_1000pF

IC1

1

GND

2

VDD

BU4241F

IC2

1

GND

2

VDD

BU4238F

VOUT

VOUT

3

CT

4

3

CT

4

C19

0.01uF

C23

X_1000pF

CP49

CP51

+5V_IN

+5V_IN

R20

4.7KJ

C802

1000pF

DGND

DGND

R21

4.7KJ

C803

1000pF

B

DC_ON_OFF_CTL_IO

DC_ON_OFF_CTL_CORE

A

+5V_IN

BP28

BP29

BP30BP25

BP31

BP47

R700

47KJ

DGND

2

1

BP27

BP26

3

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 2

Page 12

CP69

CP57

L3 BLM15AG121SN1(1005)

12

R53

X_470J

C34

X_15pF(CH)

R61

0J

CP78

CP76

R28 33J

C25

0.1uF(B)

C39

X_0.1uF(B)

CP

R22 220J

R25 0J

R36 X_0J

CP

R93

47KJ

R26 33J

X3

X_16.6666MHz(SMT)

IC8

X_MK5814SLFTR

Xin

1

VSS

2

S1

3

S04SSCLK

5

FRSEL

6

VDD

7

Xout

8

CP

IC6

X_ASM3P2474AF-06OR

Xin/CLKIN

3

VSS

6

x1/x2

1

MODOUT

5

VDD

4

Xout

2

CP88

R54 1MJ

R38 33J

CP6

R56

X_47J

CP53

C30

X_15pF(CH)

C27

10pF(CH)

R58

X_0J

R40 33J

CP

R42 X_220J

R37 33J

R27 X_0J

CP5

C36

X_10pF(CH)

C384

150pF

CP3

IC3

ASM3P2780AF-06OR

Xin/CLKIN

3

VSS

6

PD

1

MODOUT

5

VDD

4

Xout

2

CP2

R122

1KJ

CP81

R23

1MJ

R24

33J

CP54

R47

X_33J

CP111

R44

X_1MJ

X2

X_25.000MHz(SMT)

R32 X_0J

R63

0J

CP

C37

X_10pF(CH)

CP55

CP56

C26

10pF(CH)

R59

X_0J

CP7

CP

C31

X_0.1uF(B)

R34 X_0J

CP4

CP1

CP77

Not Assemble

L2 BLM15AG121SN1(1005)

12

R29 X_0J

CP115

CP52

X1

32.875MHz(SMT)

R64

X_0J

CP

R57

X_0J

CLK66BASE

CLK25SOSBASE

GPO_nICUIMGCLKENB

CLK33BASE

CLK66M

ICUSYSCLK33_2BASE

CLK66BASE

+3.3V

+3.3V+3.3V

+3.3V

+3.3V

+3.3V

+3.

+3.3V

+3.3V

DGND

DGND

DGND

DGNDDGNDDGND

DGND

DGND

DGND

DGND

DGND

DGND

DGND

+3.3V

DGND

DGND

DGND

DGND

IMGICUCLK_BASE{5}

GPO_nICUIMGCLKENB{43}

or

ASM3P2812AF-08SR

5

5

4

4

3

3

D

C

B

A

MFPC PWB (Global clock 1)

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 3

Page 13

3

2

1

2/42

D

CP58

CP59

CP62

CP63

CP66

CP74

12

DGND

L2 BLM15AG121SN1(1005)

+3.3V

IC4

2

1A1

4

1A2

6

1A3

8

1A4

11

2A1

13

2A2

15

2A3

17

2A4

1

1G

19

2G

VCC20GND

SN74LVC244APWR

C29

0.1uF(B)

1Y1

16

1Y2

14

1Y3

12

1Y4

9

2Y1

7

2Y2

5

2Y3

3

2Y4

10

CP61

CP64

CP70

CP65

CP71

CP67

CP73

817263

DGND

R31 56J

R30 47J

R39 220J

R33 47J

R35 220J

R41 47J

CP282

54

BR1

47KJx4

CP68

BP32

CP72

BP1

CP75

ICUSYSCLK33_2BASE

SA_MST_CLK {13}

CLOCK3333 {43}

ICUSYSCLK33_1 {38}

IMGSYSCLK33 {40}

CP60

18

C

C40

X_150pF

CP98

R52

X_68J

DGND

PCICLK_BASE2

CP91

+3.3V

C32

0.1uF(B)

+3.3V

CP93

IC5

1

REFIN

2

OUTA1

3

OUTA2

4

VDD

5

GND

6

OUTB1

7

OUTB2

8

S2

CY23S09SXC1T

CLKOUT

OUTA4

OUTA3

GND

OUTB4

OUTB3

CP86 R48 47J

R49 33J

CP89

C35

10pF(CH)

DGND

CP94

16

15

14

13

VDD

12

11

10

9

S1

DGND

C28 0.1uF(B)

DGND

+3.3V

CP83

CP79

CP92

CP96

CP99

R43 33J

R46 47J

R50 33J

R51 33J

R55 33J

CP87

CP90

CP84

CP80

CP95

CP97

CP100

IF_PCI1_CLK {23}

PCI1_EXT {33}

SA_PCI1_CLK {12}

MAC_PCI1_CLK {17}

SA_PCI2_CLK {12}

IDE_PCI2_CLK {16}

ICU_PCI2_CLK {36}

Extend PCI CN.

I/F ASIC

SYSTEM ASIC PCI1

PCI-Eather

SYSTEM ASIC PCI2

PCI-IDE Controller

ICU-ASIC

B

CP114

12

L3 BLM15AG121SN1(1005)

3

C41

0.1uF(B)

DGND

2

4

6

8

11

13

15

17

1

19

IC9

1A1

1Y1

1A2

1Y2

1A3

1Y3

1A4

1Y4

2A1

2Y1

2A2

2Y2

2A3

2Y3

2A4

2Y4

1G

2G

VCC20GND

SN74LVC244APWR

CP102

18

CP103

16

CP104

14

CP105

12

CP287

9

CP288 R66 33J

7

CP289

5

CP109

3

10

R123

33J

CLK66M

817263

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 4

54

DGND

R67 33J

R68 33J

BR2

47KJx4

2

CP107

CP110

CP113

ICU_SOCLK {36}

IMG_OBCLKI {41}

IMG_OCCLKI {41}

A

1

Page 14

CP120

R87

220J

R83

X_0J

C50

0.1uF(B)

R72 X_33J

L4

BLM15AG121SN1(1005)

12

CP147

CP

C47

27pF(CH)

C46

27pF(CH)

CP145

C51

0.1uF(B)

CP137

CP131

CP12

C785

0.1uF(B)

CP11

R77

X_0J

R92 0J

CP150

CP119

R74

X_0J

R102

0J

CP149

C42

15pF(CH)

CP117

IC91

ASM3P2474AF-06OR

Xin/CLKIN

3

VSS

6

x1/x2

1

MODOUT

5

VDD

4

Xout

2

R88

1MJ

CP133

CP

IC13

ASM3P2779AF-06OR

Xin/CLKIN

3

VSS

6

PD

1

MODOUT

5

VDD

4

Xout

2

IC11

SN74LVC244APWR

1A1

2

1A2

4

1A3

6

1A4

8

2A1

11

2A2

13

2A3

15

2A4

17

1G

1

2G

19

1Y1

18

1Y2

16

1Y3

14

1Y4

12

2Y1

9

2Y2

7

2Y3

5

2Y4

3

VCC20GND

10

CP144

R81

X_0J

CP135

R69

220J

R97 22J

R82

X_0J

C45

0.1uF(B)

R91

22J

X6

SG8002JF(27.5000MHz/ST MODE)

ST

1

GND2OUT

3

VDD

4

IC14

ASM3P2474AF-06OR

Xin/CLKIN

3

VSS

6

x1/x2

1

MODOUT

5

VDD

4

Xout

2

CP148

CP118

R78

X_0J

C97

0.1uF(B)

C44

0.1uF(B)

R70

1MJ

CP

CP146

C43

15pF(CH)

R85

10KJ

X4

25.0000MHz(SMT)

CP153

R99

X_0J

X5

14.7456MHz(SMT)

CP116

R96

100J

IC10

X_MK5812SLFTR

Xin

1

VSS

2

S1

3

S04SSCLK

5

FRSEL

6

VDD

7

Xout

8

Q4

DTC114YUA

E

B

C

10K

47K

R722

100KJ

CLK50

CLKUARTBASE

+3.3V+3.3V

+3.3V

+3.3V

+3.3V

DGND

DGND

DGND

DGNDDGND

DGND

DGND

DGND

DGND

+3.3V

DGND

DGND

+3.3V

+3.3V

DGND

DGND

+3.3V

+3.3V

DGND

+3.3V

DGND

DGND

DGND

+3.3V

DGND

DGND

GPO_nSMICCLKENB{43}

GPO_nIFCLKENB{43}

GPO_nBCCLKSTOP{43}

or

ASM3P2812AF-08SR

5

5

4

4

3

3

D

C

B

A

MFPC PWB (Global clock 2)

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 5

Page 15

3

2

1

3/42

D

DGND

R71

47KJ

CP290

CP291

CP292

CP121

CP128

R73 47J

CP139

VSYNC_SET{40}

VSYNC_RESET{40}

R75 33J

R79 33J

R76 33J

R80 100J

SEGOVSYNC_N_P{37}

BP13

CP124

CP126

CP129

CP130

CP1090

+3.3V

L5

BLM15AG121SN1(1005)

+3.3V

+3.3V

CP142

12

DGND

C49

0.1uF(B)

IC12

2

D1

3

CK1

4

S1

1

R1

12

D2

11

CK2

10

S2

13

R2

VCC14GND

SN74LVC74APWR

SMIC_CLK {13}

SA_UART_CLK {13}

IF_UART_CLK0 {20}

IF_UART_CLK1 {20}

CP134

R84 56J

CP140

CP136

R86 47J

R543 X_22J

5

Q1

6

QB1

9

Q2

8

QB2

7

CP138

CP141

IF_SYSCLK {20}

IBVSYNCB {41}

C

B

CP151

IMGICUCLK_BASE {4}

A

3

2

1

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 6

Page 16

CP385

Q5

DTC114YUA

E

B

C

10K

47K

Q8

DTC114YUA

E

B

C

10K

47K

BP38

BP44

CP276

BR3

10KJx4

81

72

63

54

R704

2.2KJ

CP277

CP183

CP676

Q9

DTC114YUA

E

B

C

10K

47K

CP177

R110

X_10KJ

CP155

R121

X_10KJ

CP179

C57

1000pF

CP163

Q26

DTC114YUA

E

B

C

10K

47K

IC15

BU4242F

GND

1

VDD

2

CT

3

VOUT

4

CP165

CP166

IC16F

SN74LVC14APW

13 12

147

CP161

CP175

CP169

C55

X_0.01uF

SW1

X_SKQMBAE010

C62

0.1uF(B)

CP160

Q6

DTC114YUA

E

B

C

10K

47K

C59

0.1uF(B)

IC16E

SN74LVC14APWR

11 10

147

IC16C

SN74LVC14APWR

5 6

147

IC18

SN74LVC244APWR

1A1

2

1A2

4

1A3

6

1A4

8

2A1

11

2A2

13

2A3

15

2A4

17

1G

1

2G

19

1Y1

18

1Y2

16

1Y3

14

1Y4

12

2Y1

9

2Y2

7

2Y3

5

2Y4

3

VCC20GND

10

R111

1KJ

CP173

CP159

D40

X_1SS355

AK

IC16B

SN74LVC14APWR

3 4

147

Q7

DTC114YUA

E

B

C

10K

47K

R315 0J

CP174

BR4

47KJx4

817263

54

C56

0.1uF(B)

R106

10KJ

C52

0.01uF

CP293

CP172

CP162

CP535

TP1

HK-4

C54

X_0.01uF

CP181

R113

10KJ

IC17F

SN74LVC14APWR

13 12

147

R109

100J

C60

0.1uF(B)

R142 33J

9

147

CP164

CP278

CP168

C740

0.1uF(B)

CP599

R708

15KJ

R703

15KJ

C53

X_0.01uF

CP158

CP180

R707 X_33J

SA_VCCNG_3.3V

DGND

DGND

+3.3V

DGND

+3.3V

DGND

+3.3V

DGND

+3.3V

DGND

+3.3V

DGND

DGND

DGND

+3.3V

DGND

+3.3V

+3.3V

DGND

+5V_IN

+3.3V

DGND

DGND

DGND

DGND

+3.3V

DGND

DGND

DGND

+3.3V

DGND

DGND

+3.3V

GPO_SELFRST{43}

RES_MFP_MT{31}

RES_MFP_FAX2{29}

JTAGICE_RESET{7}

V33_RTN_JIG1{17,20}

CPU_MODECLK_2.5V{7}

CPU_MO

GPO_nSOFTRST_PCI2{43}

GPO_nSOFTRST_IMG{43}

GPO_nSOFTRST_PCI1{43} nPCI1_RS

nPCI2_RS

nIMGASIC

SA_VCCOK_2.5V{7,8}

nIOGA_R

SA_CPURST_2.5V{7,8}

RESET_G

nSYSTEM

SRAM_CE

SELF_RESET by MPU

Force Reset by Another PWB

5

5

4

4

3

3

D

C

B

A

MFPC PWB (ReSet Tree)

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 7

Page 17

G

3

2

1

4/42

+3.3V

EC

78

Q25

B

2SB1198K

CP386

R706

X_1KJ

R705

X_47KJ

D

DGND

R107 33J

CP157

IC88

X_SN74LVC1G04DCK

1

76

2

DGND

+3.3V

147

9 8

DGND

4APWR

A_RST {43}

M_CE2_DELAY {7}

STEM_RST {13}

ET_GOOD {17,20}

I2_RST {16,36}

I1_RST {17,23,33}

GASIC_RST {40,42}

_MODECLK_3.3V {20}

VCC

NC

Y=/A

A

GND3Y

IC16D

SN74LVC14APWR

5

4

+3.3V

C736

X_0.1uF(B)

DGND

nIFASIC_RST_BASE {19}

R120 X_33J

+3.3V

+3.3V

C61

0.1uF(B)

+3.3V

+3.3V

+3.3V

+3.3V

11 10

CP156

147

1 2

DGND

147

1 2

DGND

147

3 4

DGND

147

5 6

DGND

147

9 8

DGND

147

DGND

SRAM_CE2_BASE {7,19}

IC16A

SN74LVC14APWR

IC17A

SN74LVC14APWR

IC17B

SN74LVC14APWR

IC17C

SN74LVC14APWR

IC17D

SN74LVC14APWR

CP184

IC17E

SN74LVC14APWR

nFROM_RST1 {25}

nFROM_RST2 {25}

nFROM_RST3 {25}

nFROM_RST4 {25,26}

nFROM_RST5 {25}

nFROM_RST6 {26}

C

B

A

3

2

1

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 8

Page 18

D

CP196

R135

10J

BR41

47Jx4

81

72

63

54

R117 47J

CP206

C66

1000pF

CP195

CN1

X_SM08B-SRSS-TB

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

R130 10KJ

R114 47J

BR32

47Jx4

81

72

63

54

CP209

CP185

BR14

47Jx4

81

7

2

63

54

CP190

IC19A

RM7965

SYSAD35

A5

SYSAD33

A7

SYSAD32

A8

SYSADC1

A10

SYSADC2

A13

SYSAD62

A14

SYSAD60

A16

SYSAD3

B6

SYSAD2

B7

SYSAD1

B8

SYSADC5

B9

SYSADC0

B10

SYSADC3

B11

SYSADC6

B12

SYSAD30

B14

SYSAD29

B15

SYSAD34

C7

SYSAD0

C9

SYSADC4

C10

SYSADC7

C11

SYSAD31

C13

SYSAD61

C14

SYSAD63

D13

SYSAD28

D15

SYSAD5

E1

SYSAD59

E20

SYSAD36

F2

SYSAD4

F3

SYSAD27

F18

SYSAD58

F19

SYSAD38

G1

SYSAD6

G2

SYSAD37

G3

SYSAD26

G18

SYSAD57

G19

SYSAD25

G20

SYSAD7

H1

SYSAD39

H2

SYSAD40

H3

SYSAD8

H4

SYSAD24

H17

SYSAD56

H18

SYSAD55

H19

SYSAD23

H20

SYSAD9

J2

SYSAD54

J18

SYSAD22

J19

SYSAD41

K1

SYSAD10

K2

SYSAD42

K3

SYSAD11

K4

SYSAD53

K17

SYSAD21

K18

SYSAD52

K19

SYSAD20

K20

SYSAD43

L1

SYSAD44

L2

SYSAD12

L3

SYSAD51

L18

SYSAD19

L19

SYSAD50

L20

SYSAD13

M2

SYSAD45

M3

SYSAD18

M18

SYSAD49

M19

SYSAD14

N1

SYSAD46

N2

SYSAD47

N4

SYSAD48

N18

SYSAD16

N19

SYSAD17

N20

SYSAD15

P1

RSPSWAP

P2

PAC K

P3

COLDRESET

P17

BIGENDIAN

P19

RESET

P20

JTDI

R3

JTCK

R4

EXTRQST

R18

NMI

R19

PRQST

T1

JTDO

T2

INT9

T19

INT8

T20

MODECLOCK

U1

JTMS

U3

VALIDIN

U6

SYSCMD7

U13

INT3

U15

INT6

U18

INT7

U20

RDTYPE

V4

RDRDY

V5

SYSCMD3

V12

SYSCMD6

V13

INT2

V15

INT5

V16

INT4

V17

WRRDY

W5

RELEASE

W6

SYSCLK

W7

SYSCMD1

W11

SYSCMD2

W12

SYSCMD5

W13

SYSCMDP

W14

INT1

W16

MODEIN

Y4

VALIDOUT

Y5

SYSCMD0

Y11

SYSCMD4

Y13

SYSCMD8

Y14

INT0

Y17

VCCOK

P18

VCCP

Y7

VCCP

V6

VSSP

U7

VREF_IN

V10

SYSCLK

V7

VREF_IN

B13

HSTL_SEL

A11

JTRST

T4

VCCIO/JTAGSEL

U5

RM7065C/7965 1/2

R132

47J

C67

0.1uF(B)

IC20

SN74LVC244APWR

A1

2

A2

4

A3

6

A4

8

1OE

1

Y1

18

Y2

16

Y3

14

Y4

12

VCC

20

GND

10

A5

11

A6

13

A7

15

A8

17

Y5

9

Y6

7

Y7

5

Y8

3

2OE

19

R116 10KJ

BR8

47Jx4

81

72

63

54

BR45 10Jx4

81

72

63

54

CP197

C68

10uF(2012)

R118 47J

CP295

L7

BLM15AG121SN1(1

12

R145 4.7KJ

C121

0.01uF

BR30

47Jx4

81

72

63

54

CP199

R134 33J

BR36

47Jx4

81

72

63

54

BR11

47Jx4

81

72

63

54

BR28

47Jx4

81

72

63

54

CP203

BR42

47Jx4

81

72

63

54

CP213

BR34

47Jx4

81

72

63

54

BR37

10KJx4

81

72

63

54

BR26

47Jx4

81

72

63

54

CP208

R133

10KJ

C100

220pF

C94

220pF

CP198

BR12

47Jx4

81

72

63

54

CP211

R115 10KJ

C98

220pF

BR5

47Jx4

81

72

63

54

81

726354

R143 2.2KJ

BR22

47Jx4

81

72

63

54

BR23

47Jx4

81

72

63

54

C99

220pF

CP212

BR38

10KJx4

81

72

63

54

BR16

47Jx4

81

72

63

54

CP205

RJ1

150J

BR18

47Jx4

81

72

63

54

BR20

47Jx4

81

72

63

54

CPU_JTDO

SA_SYSAD32

SA_SYSAD31

SA_SYSAD36

SA_SYSAD56

SA_SYSAD41

SA_SYSAD54

SA_SYSAD21

SA_SYSAD2

SA_SYSAD27

SA_SYSAD39

SA_SYSAD63

SA_SYSAD29

SA_SYSAD37

SA_SYSAD44

SA_SYSAD45

SA_SYSAD18

SA_SYSAD35

SA_SYSAD9

SA_SYSAD34

SA_SYSAD26

SA_SYSAD57

SA_SYSAD25

SA_SYSAD20

SA_SYSAD46

SA_SYSAD8

SA_SYSAD49

SA_SYSAD33

SA_SYSAD10

SA_SYSAD53

SA_SYSAD13

SA_SYSAD19

SA_SYSAD61

SA_SYSAD6

SA_SYSAD40

SA_SYSAD48

SA_SYSAD62

SA_SYSAD0

SA_SYSAD7

SA_SYSAD14

SA_SYSAD3

SA_SYSAD58

SA_SYSAD22

SA_SYSAD47

SA_SYSAD30

SA_SYSAD38

SA_SYSAD1

SA_SYSAD4

SA_SYSAD43

SA_SYSAD52

SA_SYSAD50

SA_SYSAD5

SA_SYSAD60

SA_SYSAD16

SA_SYSAD17

SA_SYSAD28

SA_SYSAD59

SA_SYSAD42

SA_SYSAD11

SA_SYSAD55

SA_SYSAD12

SA_SYSAD24

SA_SYSAD23

SA_SYSAD51

SA_SYSAD15

SA_JTCLK_PU

ICU_INT_2.5V

SA_JTDI_PU

SA_JTMS_PU

PCI1_PME_2.5V

SA_JTRST_PD

IF_INT_2.5V

SYSAD44

SYSAD45

SYSAD46

SYSAD47

SYSAD52

SYSAD53

SYSAD54

SYSAD55

SYSAD28

SYSAD29

SYSAD30

SYSAD31

SYSAD40

SYSAD41

SYSAD42

SYSAD43

SYSAD4

SYSAD5

SYSAD6

SYSAD7

SYSAD12

SYSAD13

SYSAD14

SYSAD15

SYSAD48

SYSAD49

SYSAD50

SYSAD51

SYSAD24

SYSAD25

SYSAD26

SYSAD27

SYSAD36

SYSAD37

SYSAD38

SYSAD39

SYSAD0

SYSAD1

SYSAD2

SYSAD3

SYSAD8

SYSAD9

SYSAD10

SYSAD11

SYSAD20

SYSAD21

SYSAD22

SYSAD23

SYSAD32

SYSAD33

SYSAD34

SYSAD35

SYSAD16

SYSAD17

SYSAD18

SYSAD19

SYSAD60

SYSAD61

SYSAD62

SYSAD63

SYSAD56

SYSAD57

SYSAD58

SYSAD59

SA_SYSCMD1

SA_SYSCMD4

SA_SYSCMD7

SA_SYSCMD5

SA_SYSCMD6

SA_SYSCMD2

SA_SYSCMD0

SA_SYSCMD3

SA_SYSCMD8 SYSCMD8

SYSCMD7

SYSCMD6

SYSCMD5

SYSCMD4

SYSCMD3

SYSCMD2

SYSCMD1

SYSCMD0

nPOF_2.5V

PCI_INT1_2.5V

PCI1_PME_2.5V

nPOF_2.5V

MODEDAT_2.5V

PCI_INT2_2.5V

nFAX_WU_2.5V

nFAX_WU_2.5V

nIMGINT

ICU_INT_2.5V

IF_INT_2.5V

PCI_INT2_2.5V

nCPUINT3

SA_EXTRQST

SA_RSPSWAP

SA_JTAGSEL

CPU_V

SYSTEM2.5V

SYSTEM2.5V

SYSTEM2.5V

SYSTEM2.5V

SYSTEM2.5V

+3.3V

SYSTEM2.5V

+3.3V

SA_NMI_2.5V {8}

SA_CPURS

SA_VCCO

SA_COLDR

SA_SYSAD[63:0]{8}

SA_SYSCMD[8:0]{8}

CPU_MODECLK_2.5V

{6}

CPU_JTDO {44}

CPU_JTDI_PU {44}

TEST_JTCK1 {13,44}

TEST_JTRST1 {13,20,44}

TEST_JTMS1 {13,44}

JTAGICE_RESET{6}

SA_INT_2.5V {8}

nREQ_PIC_INT_O

5

5

4

4

3

3

D

C

B

A

MFPC PWB (CPU RM6065C/7965)

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 9

Page 19

63

V

3

2

1

5/42

CPU_CORE1.3V

12

C830

C831

C832

0.1uF(B)

C833

0.1uF(B)

C834

0.1uF(B)

C835

0.1uF(B)

C836

0.1uF(B)

C837

0.1uF(B)

C839

0.1uF(B)

C838

0.1uF(B)

C841

0.1uF(B)

C842

0.1uF(B)

C840

0.1uF(B)

+2.5V_CPU

C863

TP2

HK-4

L6

BLM21PG600SN1(2012)

6A

C64

10uF(2012)

C65

10uF(2012)

C95

10uF(2012)

C96

10uF(2012)

C101

0.1uF(B)

C103

0.1uF(B)

C105

0.1uF(B)

C109

0.1uF(B)

C108

0.1uF(B)

C111

0.1uF(B)

C113

0.1uF(B)

C115

0.1uF(B)

C117

0.1uF(B)

C119

0.1uF(B)

C122

0.1uF(B)

C124

0.1uF(B)

C71

0.1uF(B)

C73

0.1uF(B)

C74

0.1uF(B)

C76

0.1uF(B)

C78

0.1uF(B)

C80

0.1uF(B)

C82

0.1uF(B)

C84

0.1uF(B)

C86

0.1uF(B)

C88

0.1uF(B)

C90

0.1uF(B)

C92

0.1uF(B)

SYSTEM2.5V

CPU_VCCINT

CP186

C72

0.01uF

C63

0.01uF

C75

0.01uF

C77

0.01uF

C79

0.01uF

C81

0.01uF

C83

0.01uF

C85

0.01uF

C87

0.01uF

C89

0.01uF

C91

0.01uF

C93

0.01uF

L8

BLM18PG121SN1(1608)

2A

12

CP192

C102

0.01uF

C104

0.01uF

C106

0.01uF

C107

0.01uF

C110

0.01uF

C112

0.01uF

C114

0.01uF

C116

0.01uF

C118

0.01uF

C120

0.01uF

C123

0.01uF

C125

0.01uF

D

C

B

+2.5V_CPUCPU_VCCINT

IC19B

W15

VCCINT

W8

VCCINT

V14

VCCINT

V11

VCCINT

V8

VCCINT

U14

VCCINT

U11

VCCINT

U10

VCCINT

U8

VCCINT

T18

VCCINT

R17

VCCINT

P4

VCCINT

N17

VCCINT

N3

VCCINT

L17

C69

0.1uF(B)

W10

VCCINT

L4

VCCINT

J3

VCCINT

G17

VCCINT

G4

VCCINT

F17

VCCINT

F4

VCCINT

E3

VCCINT

D14

VCCINT

D11

VCCINT

D10

VCCINT

D8

VCCINT

D7

VCCINT

C15

VCCINT

C12

VCCINT

C8

VCCINT

Y16

VCCJ

Y10

NC

Y8

NC

NC

W9

NC

V9

NC

R2

NC

E19

NC

E18

NC

E2

NC

D20

NC

D18

NC

D6

NC

D3

NC

D1

NC

C17

NC

C16

NC

C6

NC

C5

NC

C4

NC

B16

NC

B5

NC

A17

NC

A4

NC

SA_RELEASE_2.5V {8}

SA_RDY_2.5V {8}

SA_VALIDIN_2.5V {8}

SA_VALIDOUT_2.5V

SA_PRQST_2.5V {8}

SA_PACK_2.5V {8}

PU_VCCINT

SN1(1005)

CP194

GINT

INT_OC {29}

{8}

R144 0J

{8}

SA_CPUCLK_2.5V {8}

C70

X_150pF

CP189

R119

1KJ

CP191

+3.3V

817263

54

nIMGINT {40}

nRTCINT {27}

BR265

10KJx4

SYSTEM2.5V

R125

X_10KJ

R126

0J

VCCINT=30 pcs.

+3.3V

V{8}

196

195

197

199

198

CCOK_2.5V {6,8}

OLDRST_2.5V {8}

PURST_2.5V {6,8}

R131

2.2KJ

SA_JTDI_PU

SA_JTCLK_PU

CPU_JTDO

SA_JTMS_PU

SA_JTRST_PD

RM7065C/7965 2/2

RM7965

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

VCCIO

A1

A20

B2

B19

C3

C18

D4

D5

D9

D12

D16

D17

E4

E17

J4

J17

M4

M17

T3

T17

U4

U9

U12

U16

U17

V3

V18

W2

W19

Y1

Y20

A2

VSS

A3

VSS

A6

VSS

A9

VSS

A12

VSS

A15

VSS

A18

VSS

A19

VSS

B1

VSS

B3

VSS

B4

VSS

B17

VSS

B18

VSS

B20

VSS

C1

VSS

C2

VSS

C19

VSS

C20

VSS

D2

VSS

D19

VSS

F1

VSS

F20

VSS

J1

VSS

J20

VSS

M1

VSS

M20

VSS

R1

VSS

R20

VSS

U2

VSS

U19

VSS

V1

VSS

V2

VSS

V19

VSS

V20

VSS

W1

VSS

W3

VSS

W4

VSS

W17

VSS

W18

VSS

W20

VSS

Y2

VSS

Y3

VSS

Y6

VSS

Y9

VSS

Y12

VSS

Y15

VSS

Y18

VSS

Y19

VSS

1uF(1608:B)

1uF(1608:B)

1uF(1608:B)

CP201

CP202

6

8

SYSTEM2.5V

147

SYSTEM2.5V

147

IC87B

SN74LVC08APWR

4

SA_INT_2.5V

5

ICU_INT_2.5V

IC87C

SN74LVC08APWR

9

IF_INT_2.5V

10

PCI_INT2_2.5V

CP200

SYSTEM2.5V

IC87A

SN74LVC08APWR

R148

X_0J

R146

0J

CP297

CP298

nCPUINT3

54

BR43

4.7KJx4

3

PCI_INT1_2.5V

147

1

2

A

CP204

3

CP214

CP207

CP210

CP215

CP216

CP218

CP217

nFAX_WU_INT {29}

PCI1_INTA_PU {12,17,23,33}

PCI1_PME {17,23}

nPOF {32}

IF_INT1 {21}

ICU_INTR {37}

PCI2_INTA_PU {12,16,36}

MODEDAT_3.3V {20}

SYSTEM2.5V

R214

47J

SRAM_CE2{27}

CP219

CP220

147

11

2

C733

IC87D

SN74LVC08APWR

12

13

0.1uF(B)

R195 X_0J

R298 X_0J

SRAM_CE2_BASE {6,19}

SRAM_CE2_DELAY {6}

GPO_SRAMCE2 {43}

1

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 10

Page 20

BR46

10KJx4

8

1

R14

X_1

R141 0J

R151

10KJ

R140 22J

IC21F

Image_System_Chip_15

cpu_sysad[63]

C30

cpu_sysad[62]

E31

cpu_sysad[61]

E25

cpu_sysad[60]

E27

cpu_sysad[59]

E29

cpu_sysad[58]

F31

cpu_sysad[57]

F23

cpu_sysad[56]

F26

cpu_sysad[55]

F27

cpu_sysad[54]

F29

cpu_sysad[53]

F34

cpu_sysad[52]

F33

cpu_sysad[51]

C33

cpu_sysad[50]

D34

cpu_sysad[49]

B32

cpu_sysad[48]

B30

cpu_sysad[47]

E18

cpu_sysad[46]

D18

cpu_sysad[45]

D20

cpu_sysad[44]

A18

cpu_sysad[43]

B18

cpu_sysad[42]

A20

cpu_sysad[41]

A19

cpu_sysad[40]

F21

cpu_sysad[39]

E20

cpu_sysad[38]

E23

cpu_sysad[37]

C22

cpu_sysad[36]

D22

cpu_sysad[35]

C25

cpu_sysad[34]

C26

cpu_sysad[33]

D27

cpu_sysad[32]

C29

cpu_sysad[31]

D30

cpu_sysad[30]

E32

cpu_sysad[29]

E26

cpu_sysad[28]

E28

cpu_sysad[27]

E30

cpu_sysad[26]

F32

cpu_sysad[25]

F24

cpu_sysad[24]

F25

cpu_sysad[23]

F28

cpu_sysad[22]

G29

cpu_sysad[21]

E34

cpu_sysad[20]

E33

cpu_sysad[19]

C34

cpu_sysad[18]

A32

cpu_sysad[17]

B31

cpu_sysad[16]

A31

cpu_sysad[15]

C18

cpu_sysad[14]

D19

cpu_sysad[13]

C21

cpu_sysad[12]

D21

cpu_sysad[11]

F19

cpu_sysad[10]

B19

cpu_sysad[9]

E19

cpu_sysad[8]

F22

cpu_sysad[7]

F20

cpu_sysad[6]

E24

cpu_sysad[5]

D23

cpu_sysad[4]

D24

cpu_sysad[3]

D25

cpu_sysad[2]

D26

cpu_sysad[1]

D28

cpu_sysad[0]

D29

cpu_syscmd[8]

A27

cpu_syscmd[7]

B26

cpu_syscmd[6]

A26

cpu_syscmd[5]

B25

cpu_syscmd[4]

A25

cpu_syscmd[3]

B24

cpu_syscmd[2]

A24

cpu_syscmd[1]

B23

cpu_syscmd[0]

A23

cpu_bus64en(PU)

H30

cpu_osrd_en(PU)

J29

cpu_clko

A30

cpu_vccok

A29

cpu_rst_skip_l(PU)

AP32

cpu_release_l(PU)

A22

cpu_pack_l

B22

cpu_validout_l

B20

cpu_ready_l

A21

cpu_validin_l

B21

cpu_nmi_l

A28

cpu_prqst_l(PU)

F18

cpu_reset_l

B29

cpu_intr_l

B27

cpu_coldrst_l

B28

funk_test

AE32

bisr_test

C4

Image_System_Chip 6/8

SYSAD I/F

PU

PU

R150

10KJ

CP223

R317

CP222

R139 22J

BR47

47KJx4

817263

54

R207

R138 22J

BUS64EN_WITHPU_3.3V

OUTSTANDEN_WITHPU

SA_SYSAD47

SA_SYSAD61

SA_SYSAD2

SA_SYSAD52

SA_SYSAD26

SA_SYSAD6

SA_SYSAD27

SA_SYSAD43

SA_SYSAD20

SA_SYSAD60

SA_SYSAD11

SA_SYSAD15

SA_SYSAD45

SA_SYSAD14

SA_SYSAD34

SA_SYSAD49

SA_SYSAD1

SA_SYSAD22

SA_SYSAD41

SA_SYSAD9

SA_SYSAD24

SA_SYSAD18

SA_SYSAD50

SA_SYSAD37

SA_SYSAD54

SA_SYSAD62

SA_SYSAD36

SA_SYSAD55

SA_SYSAD56

SA_SYSAD32

SA_SYSAD40

SA_SYSAD23

SA_SYSAD46

SA_SYSAD44

SA_SYSAD4

SA_SYSAD29

SA_SYSAD53

SA_SYSAD51

SA_SYSAD31

SA_SYSAD63

SA_SYSAD48

SA_SYSAD13

SA_SYSAD10

SA_SYSAD42

SA_SYSAD19

SA_SYSAD7

SA_SYSAD35

SA_SYSAD38

SA_SYSAD39

SA_SYSAD58

SA_SYSAD16

SA_SYSAD5

SA_SYSAD59

SA_SYSAD17

SA_SYSAD0

SA_SYSAD33

SA_SYSAD28

SA_SYSAD8

SA_SYSAD30

SA_SYSAD57

SA_SYSAD21

SA_SYSAD3

SA_SYSAD12

SA_SYSAD25

SA_SYSCMD2

SA_SYSCMD8

SA_SYSCMD0

SA_SYSCMD7

SA_SYSCMD5

SA_SYSCMD4

SA_SYSCMD6

SA_SYSCMD3

SA_SYSCMD1

SYSTEM

SA_SYSAD[63:0]{7}

SA_SYSCMD[8:0]{7}

5

5

4

4

3

3

D

C

B

A

MFPC PWB (SYSTEM ASIC1-1 CUP BUS)

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 11

Page 21

3

STEM2.5V

6

Jx4

81726354

SA_RELEASE_2.5V {7}

SA_RDY_2.5V {7}

SA_VALIDIN_2.5V {7}

SA_VALIDOUT_2.5V {7}

SA_PRQST_2.5V {7}

SA_PACK_2.5V {7}

SA_CPUCLK_2.5V {7}

2

1

6/42

D

7 10KJ

7 10KJ

R147

X_10KJ

R149

X_10KJ

SYSTEM2.5V

SA_INT_2.5V {7}

SA_NMI_2.5V {7}

SA_VCCOK_2.5V {6,7}

SA_COLDRST_2.5V {7}

SA_CPURST_2.5V {6,7}

C

B

A

3

2

1

MX-3500N/4500N/3501N/4501N CIRCUIT DIAGRAM / 回路図 2 – 12

Page 22

R1

R635 33J

R638

22J

BR377

22Jx4

81

72

63

54

R648

22J

R1

R1

R1

R165

49.9F

BR380

22Jx4

81

72

63

54

R644

22J

R636 33J

R641

22J

R1

R651 22J

R1

C127

0.01uF

C126

0.1uF

R639

22J

R647

22J

R652

22J

IC21A

Image_System_Chip_15

ddr1_vref[0]

H4

ddr1_vref[1]

AE4

ddr1_cke[0]

R5

ddr1_cke[1]

T6

ddr1_ba[0]

U4

ddr1_ba[1]

V3

bzrset_ddr1

C2

bzvdd_ddr1

E3

ddr1_ras_l

V6

ddr1_we_l

W1

ddr1_cas_l

V4

ddr1_dat[63]

AJ2

ddr1_dat[62]

AJ4

ddr1_dat[61]

AJ1

ddr1_dat[60]

AG5

ddr1_dat[59]

AH1

ddr1_dat[58]

AE5

ddr1_dat[57]

AG2

ddr1_dat[56]

AE6

ddr1_dat[55]

AF5

ddr1_dat[54]

AG1

ddr1_dat[53]

AF3

ddr1_dat[52]

AG4

ddr1_dat[51]

AD6

ddr1_dat[50]

AC5

ddr1_dat[49]

AE3

ddr1_dat[48]

AD4

ddr1_dat[47]

AB6

ddr1_dat[46]

AC4

ddr1_dat[45]

AC2

ddr1_dat[44]

AB4

ddr1_dat[43]

AA4

ddr1_dat[42]

AA6

ddr1_dat[41]

AB2

ddr1_dat[40]

Y5

ddr1_dat[39]

AB1

ddr1_dat[38]

AA3

ddr1_dat[37]

Y4

ddr1_dat[36]

Y6

ddr1_dat[35]

AA1

ddr1_dat[34]

W4

ddr1_dat[33]

Y2

ddr1_dat[32]

W6

ddr1_dat[31]

R2

ddr1_dat[30]

P4

ddr1_dat[29]

P1

ddr1_dat[28]

N4

ddr1_dat[27]

M4

ddr1_dat[26]

P3

ddr1_dat[25]

N1

ddr1_dat[24]

K4

ddr1_dat[23]

N2

ddr1_dat[22]

P6

ddr1_dat[21]

L4

ddr1_dat[20]

N3

ddr1_dat[19]

M2

ddr1_dat[18]

N6

ddr1_dat[17]

L5

ddr1_dat[16]

L1

ddr1_dat[15]

J1

ddr1_dat[14]

L6

ddr1_dat[13]

J5

ddr1_dat[12]

J2

ddr1_dat[11]

H1

ddr1_dat[10]

K5

ddr1_dat[9]

K6

ddr1_dat[8]

H2

ddr1_dat[7]

G4

ddr1_dat[6]

G1

ddr1_dat[5]

H5

ddr1_dat[4]

J6

ddr1_dat[3]

G5

ddr1_dat[2]

F2

ddr1_dat[1]

F3

ddr1_dat[0]

C1

ddr1_ad[13]

V5

ddr1_ad[12]

R1

ddr1_ad[11]

T2

ddr1_ad[10]

V2

ddr1_ad[9]

R4

ddr1_ad[8]

T1

ddr1_ad[7]

U6

ddr1_ad[6]

T5

ddr1_ad[5]

U1

ddr1_ad[4]

U2

ddr1_ad[3]

T4

ddr1_ad[2]

U3

ddr1_ad[1]

V1

ddr1_ad[0]

U5

ddr1_dm[7]

AH2

ddr1_dm[6]

AF2

ddr1_dm[5]

AC1

ddr1_dm[4]

AA2

ddr1_dm[3]

P2

ddr1_dm[2]

M1

ddr1_dm[1]

J4

ddr1_dm[0]

F4

ddr1_dqs[7]

AH4

ddr1_dqs[6]

AD5

ddr1_dqs[5]

AB3

ddr1_dqs[4]

W5

ddr1_dqs[3]

R6

ddr1_dqs[2]

M5

ddr1_dqs[1]

J3

ddr1_dqs[0]

F1

ddr1_clko_l[6]

AK3

ddr1_clko_l[5]

AE1

ddr1_clko_l[4]

K1

ddr1_clko_l[3]

AK2

ddr1_clko_l[2]

AD1

ddr1_clko_l[1]

K3

ddr1_clko_l[0]

E1

ddr1_clko[6]

AL2

ddr1_clko[5]

AE2

ddr1_clko[4]

L2

ddr1_clko[3]

AK1

ddr1_clko[2]

AD2

ddr1_clko[1]

K2

ddr1_clko[0]

E2

ddr1_cs_l[4]

AG6

ddr1_cs_l[3]

AH5

ddr1_cs_l[2]

Y1

ddr1_cs_l[1]

W2

ddr1_cs_l[0]

H6

Image_System_Chip 1/8

DDR1 I/F

R642

22J

R1

R650

22J

R645

22J

R640 33J

R1

R1

BR379

22Jx4

81

72

63

54

R637 33J

R1

R646

22J

R1

R1

R1

R1

R1

R643

22J

R649

22J

CP252

BR378

22Jx4

81

72

63

54

BR381

22Jx4

81

72

63

54

R1

BZRSET_DDR1

SA_DDR1DQ3

SA_DDR1DQ7

SA_DDR1DQ6

SA_DDR1DQ2

SA_DDR1DQ5

SA_DDR1DQ0

SA_DDR1DQ4

SA_DDR1DQ1

SA_DDR1DQ9

SA_DDR1DQ15

SA_DDR1DQ8

SA_DDR1DQ13

SA_DDR1DQ10

SA_DDR1DQ14

SA_DDR1DQ11

SA_DDR1DQ12

SA_DDR1DQ18

SA_DDR1DQ16

SA_DDR1DQ21

SA_DDR1DQ19

SA_DDR1DQ20

SA_DDR1DQ23

SA_DDR1DQ22

SA_DDR1DQ17

SA_DDR1DQ31

SA_DDR1DQ25

SA_DDR1DQ24

SA_DDR1DQ27

SA_DDR1DQ26

SA_DDR1DQ28

SA_DDR1DQ30

SA_DDR1DQ29

SA_DDR1DQ36

SA_DDR1DQ35

SA_DDR1DQ34

SA_DDR1DQ32

SA_DDR1DQ37

SA_DDR1DQ33

SA_DDR1DQ39

SA_DDR1DQ38

SA_DDR1DQ44

SA_DDR1DQ45

SA_DDR1DQ46

SA_DDR1DQ40

SA_DDR1DQ43

SA_DDR1DQ42

SA_DDR1DQ47

SA_DDR1DQ41

SA_DDR1DQ51

SA_DDR1DQ48

SA_DDR1DQ53

SA_DDR1DQ52

SA_DDR1DQ50

SA_DDR1DQ54

SA_DDR1DQ55

SA_DDR1DQ49

SA_DDR1DQ56

SA_DDR1DQ63

SA_DDR1DQ60

SA_DDR1DQ59

SA_DDR1DQ58

SA_DDR1DQ57

SA_DDR1DQ62

SA_DDR1DQ61

SA_DDR1CKE0

SA_DDR1AD11

SA_DDR1AD9

SA_DDR1AD7

SA_DDR1AD4

SA_DDR1AD2

SA_DDR1AD1

SA_DDR1AD10

SA_DDR1AD6

SA_DDR1AD5

SA_DDR1AD3

SA_DDR1RAS

SA_DDR1AD0

SA_DDR1CLK3_P

SA_DDR1CLK4_N

SA_DDR1CLK6_P

SA_DDR1CLK2_N

SA_DDR1CLK1_P

SA_DDR1CLK6_N

SA_DDR1CLK4_P

SA_DDR1CLK5_P

SA_DDR1CLK5_N

SA_DDR1CLK2_P

SA_DDR1CLK3_N

SA_DDR1CLK1_N

SA_DDR1BA0

SA_DDR1CAS

SA_DDR1WE

SA_DDR1AD13

SA_DDR1BA1

SA_DDR1AD0

SA_DDR1AD1

SA_DDR1AD2

SA_DDR1AD3

SA_DDR1AD4

SA_DDR1AD5

SA_DDR1AD6

SA_DDR1AD7

SA_DDR1AD8

SA_DDR1AD9

SA_DDR1AD10

SA_DDR1AD11

SA_DDR1AD12

SA_DDR1AD13

SA_DDR1AD12

SA_DDR1CKE0

SA_DDR1CKE1

SA_DDR1AD8

SA_DDR1BA0

SA_DDR1BA1

SA_DDR1WE

DDR1_CKE0

DDR1_CKE1

DDR1_CS4

DDR1_CS2

DDR1_CS1

DDR1_CS3

DDR1_WE

DDR1_RAS

DDR1_CAS

DDR1_AD8

DDR1_AD6

DDR1_AD3

DDR1_AD7

DDR1_AD9

DDR1_AD2

DDR1_AD10

DDR1_AD5

DDR1_AD1

DDR1_AD4

DDR1_AD11

DDR1_AD0

DDR1_AD13

DDR1_BA0

DDR1_BA1

DDR1_CLK1_N

DDR1_CLK6_P

DDR1_CLK2_N

DDR1_CLK2_P

DDR1_CLK5_N

DDR1_CLK3_N

DDR1_CLK3_P

DDR1_CLK4_P

DDR1_CLK5_P

DDR1_CLK1_P

DDR1_CLK4_N

DDR1_CLK6_N

DDR1_AD12

SA_DDR1RAS

SA_DDR1CAS

SA_DDR1CS1

SA_DDR1CS2

SA_DDR1CS3

SA_DDR1CS4

DDR1_AD12

DDR1_CKE0

DDR1_AD11

DDR1_AD9

DDR1_AD7

DDR1_AD8

DDR1_AD6

DDR1_AD5

DDR1_AD3

DDR1_AD4

DDR1_AD2