Sharp LH5PV8512N-12 Datasheet

LH5PV8512

CMOS 4 M (51 2K × 8 ) Pseudo-Static RAM

FEATURES

•• 524,288 words × 8 b it organ izatio n

•• CE acce ss time ( t

CEA

): 120 ns (MAX.)

•• Cycle ti me (t

RC

): 190 ns (MIN.)

•• Power supp ly :

+3.0 V ± 0.15 V (Operating )

+2.2 V to +3.15 V (Data retention)

•• Power consu mption (MAX.):

126 mW (Operatin g)

95 µW (Standby = CMOS input level )

221 µW (Self-refresh = CMOS input level )

•• Available for address refresh,

auto-refres h, a nd se lf-re fresh mode s

•• 2,048 refresh cycle s/32 ms

•• Addres s non -multip le

•• Not design ed or ra ted as radiation

hardene d

•• Packa ge:

32-pi n , 525 -mil S OP

•• Package materi al: Plastic

•• Substrate material: P-type silicon

•• Process : Silicon-g ate CMOS

•• Operatin g temperature: 0 - 70°C

DESCRIPTION

The LH5PV8512 is a 4M bit Pseudo-Static RAM with

a 524,288 word × 8 bit organization. It is fabricated

using silicon-gate CMOS process technology.

A PSRAM uses on-chip refresh circuitry with a DRAM

memory cell for pseudo-static operation which el iminates external clock inputs, while having the same

pinout as industry standa rd SRAMs. Moreover, due to

the functional similarities between PSRAMs and

SRAMs, existing 512K × 8 SRAM sockets can be filled

with the LH5P V8512N with li ttle or no changes. The

advantage is the cost saving rea lized with the lower

cost PSRAM.

The LH5PV8512 has the ability to fill the gap between

DRAM and SRAM by offering low cost, low power

standby and simple interface.

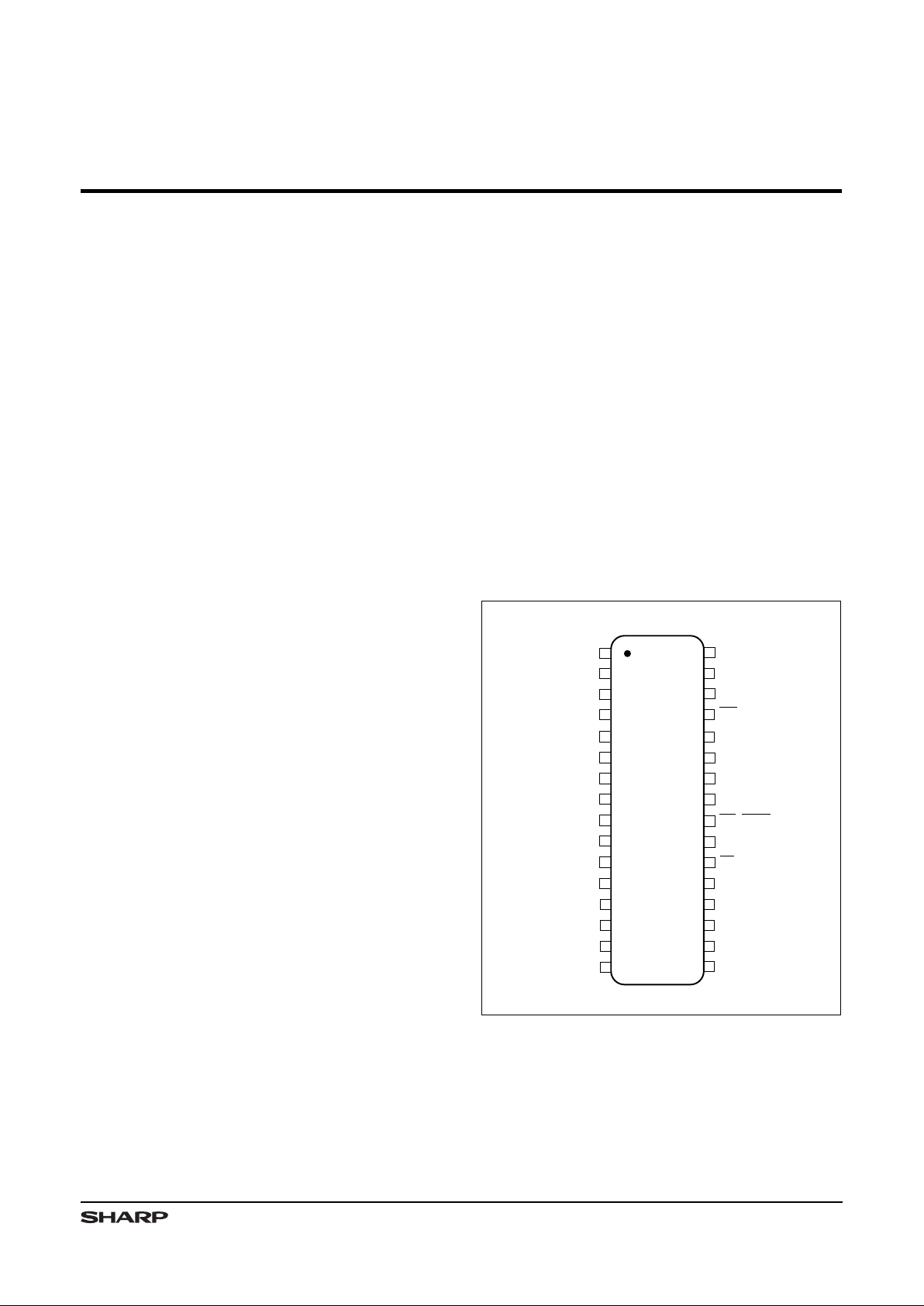

PIN CONNECTIONS

TOP VIEW

1

2

3

4

5

6

9

10

A

2

A

5

Vcc

28

27

26

25

24

23

20

17

A

7

A

6

7

8

A

3

A

4

22

21

A

14

A

12

A

13

A

8

A

11

A

10

CE

I/O

7

I/O

6

I/O

3

11

12

13

32

31

30

29

WE

A

1

14

15

16

19

I/O

5

18

I/O

4

I/O

1

I/O

2

V

SS

A

0

I/O

0

A

9

A

16

A

18

OE/RFSH

5PV8512-1

32-PIN SOP

A

17

A

15

Figure 1. Pin Connections

1

PIN DESCRIPTION

PIN NAME FUNCTION

A0 - A

18

Addre ss input

WE Write e nab le inp ut

OE/RFSH

Outpu t e nab le i np ut

Refre sh contro l input

PIN NAME FUNCTION

CE

Chip e nab le inp ut

I/O0 - I/O

7

Data i npu t/o utp ut

V

CC

Power sup ply

GND Ground

I/O

1

CLOCK

GENERATOR

CE

A

12

A

13

A

14

A

3

A

4

A

5

A

6

A

7

A

8

A

9

A

11

A

10

A

2

A

1

A

0

COLUMN

ADDRESS

BUFFER

ROW

ADDRESS

BUFFER

REFRESH

ADDRESS

COUNTER

DATA

IN

BUFFER

DATA

OUT

BUFFER

I/O

SELECTOR

COLUMN

DECODER

SENSE

AMPS

MEMORY

ARRAY

ROW

DECODER

EXT/INT

ADDRESS

MUX.

REFRESH

CONTROLLER

REFRESH

TIMER

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

V

BB

GENERATOR

V

CC

A

15

A

16

5PV8512-2

I/O

0

12

11

10

9

8

7

6

5

27

26

23

25

4

28

3

31

2

22

16

32

13

14

15

17

18

19

20

21

OE/

RFSH

24

A

17

30

A

18

1

WE 29

V

SS

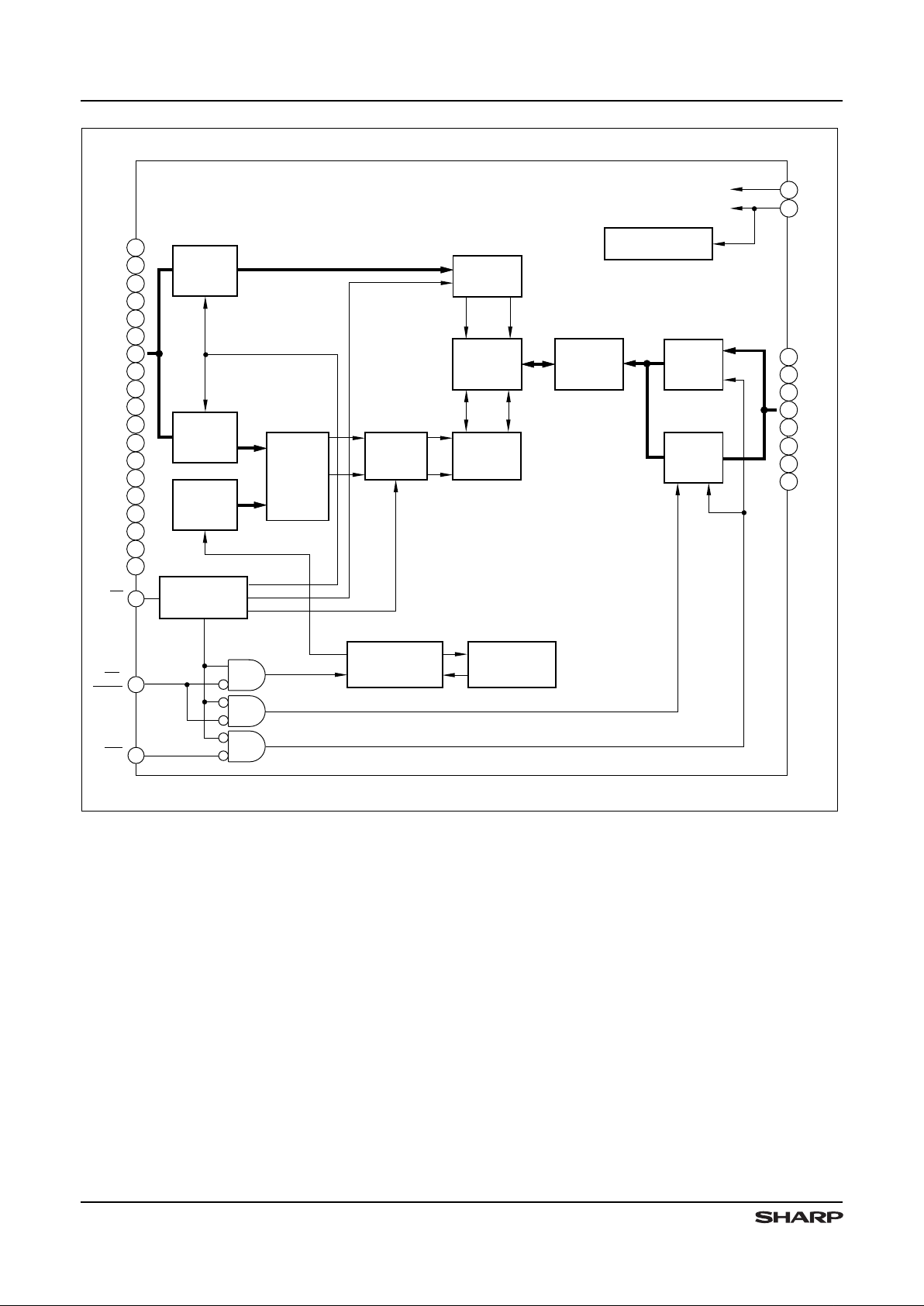

Figure 2. LH5PV8512 Block Diagram

LH5PV8512 CMOS 4M (512K × 8) Pseudo-Static R AM

2

TRUTH TABLE

CE OE/RFSH WE I/O

0 - 7

MODE

L L H Output data Read

L X L Input data Write

L H H High-Z

CE only refresh

H L X High-Z Auto-refresh

H H X High-Z Standby

NOTES:

1. X = H or L

2. I f

RF SH = L, it is necessary to meet t

OEH

and t

OCD

.

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT NOTE

Appli ed v ol tage on al l p ins V

T

-0.5 to +4.6 V 1

Operat ing te mpe ratu re T

OPR

0 to +70

°C

Storag e t emp era ture T

STG

-65 to +150

°C

Output sh ort ci rcu it c urr ent

I

O

50 mA

Power dis sipati on P

D

600

mW

NOTE:

1. The maximum applicable voltage on any pin with respect to V

SS

.

RECOMMENDED DC OPERATING CONDITIONS (TA = 0 to +70°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT NOTE

Suppl y v olt age

V

CC

2.85 3.0 3.15 V 1

V

SS

00 0 V

Input vol tage

V

IH

2.4

4.5 V

V

IL

-0.5 0.6 V

NOTE:

1. When t he supply voltage falls down under the above recommended supply voltage by temporarily power-down, a wait time longer than

400 ms is necessary at VCC = 0 V before the next po wer-up. Af ter the supply voltage rises and gets stable, a pause of 100 µs wit h

CE = RFSH = VIH and 8 dummy cycles are also necessary after the rises.

PIN CAPACITANCE (TA = +25°C, f = 1 MHz, VCC = 3.0 V)

PARAMETER CONDITIONS S YMBOL MIN. MAX. UNIT NOTE

Input cap acitan ce

A

0

- A

18

C

IN1

8pF1

WE, OE/RFSH C

IN2

8pF1

CE C

IN3

8pF1

Input/ out put ca pac ita nce I/O

0

- I/O

7

C

OUT1

10 pF 1

NOTE:

1. Th is parameter is samp led and not 100% tested.

CMOS 4M (512K × 8) Pseud o -S tatic RAM LH5PV8512

3

DC ELECTRICAL CHARACTERISTICS (TA = 0 to +70°C, VCC = 3.0 V ± 0.15 V)

PA RA METER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Average su ppl y c urr ent in no rmal

operat ion

I

CC1

tRC = 190 ns 40 mA 1

Average su ppl y c urr ent in st and by

mode

I

CC2

CE, OE, RFSH = VIH

0.5 mA

CE, OE, RFSH = VCC - 0.2 V 30 mA

Average su ppl y c urr ent in se lf-r efr esh

cycle

I

CC3

CE = VIH

OE/RFSH = V

IL

0.5 mA

CE = VCC - 0.2 V,

OE, RFSH = 0.2 V

70 mA

Input lea kag e c urr ent I

LI

0 V ≤ VIN ≤ VCC + 0.3 V

0 V on all other pins

-5 5 µA

I/O le aka ge cur ren t

I

LO

0 V ≤ V

OUT

≤ VCC + 0.3 V

Input/output pins in High-Z

-5 5 µA

Output HI GH vol tag e V

OH

I

OUT

= -1 mA 2.4

V

Output LO W v olt age V

OL

I

OUT

= 2.1 mA

0.4 V

NOTE:

1. The in put/output pins are in high impedance state. I

CC1

depends on the cycle time.

LH5PV8512 CMOS 4M (512K × 8) Pseudo-Static R AM

4

Loading...

Loading...