LH5PV16256

CMOS 4M (256 K × 16) Pseudo-Static RAM

FEATURES

•• 262,144 words × 16 bit orga nization

•• Powe r supp ly: +3.0 ± 0.15 V

•• Access time: 120 ns (MAX.)

•• Cycle ti me: 190 ns (MIN.)

•• Power consu mption (MAX.):

126 mW (Operating)

94.5 µW (Stand by = CMOS input level)

220.5 µW

(Self-refresh = CMOS input level )

•• LVT TL compati ble I/ O

•• Available for address refresh,

auto-refres h, a nd se lf-re fresh mode s

•• 2,048 refresh cycle s/32 ms

•• Addres s non -multip le

•• Available for byte write mode usin g

UWE

and

LWE pins

•• Packa ge:

44-pi n , TSOP (Type II)

•• Process : Sili con-g ate CMOS

•• Op eratin g te mpera tu re: 0 - 70°C

•• Not designed or rated a s rad iation

hardene d

DESCRIPTION

The LH5PV16256 is a 4M bit Pseudo-Static RAM with

a 262,144 words × 16 bit organi zation.

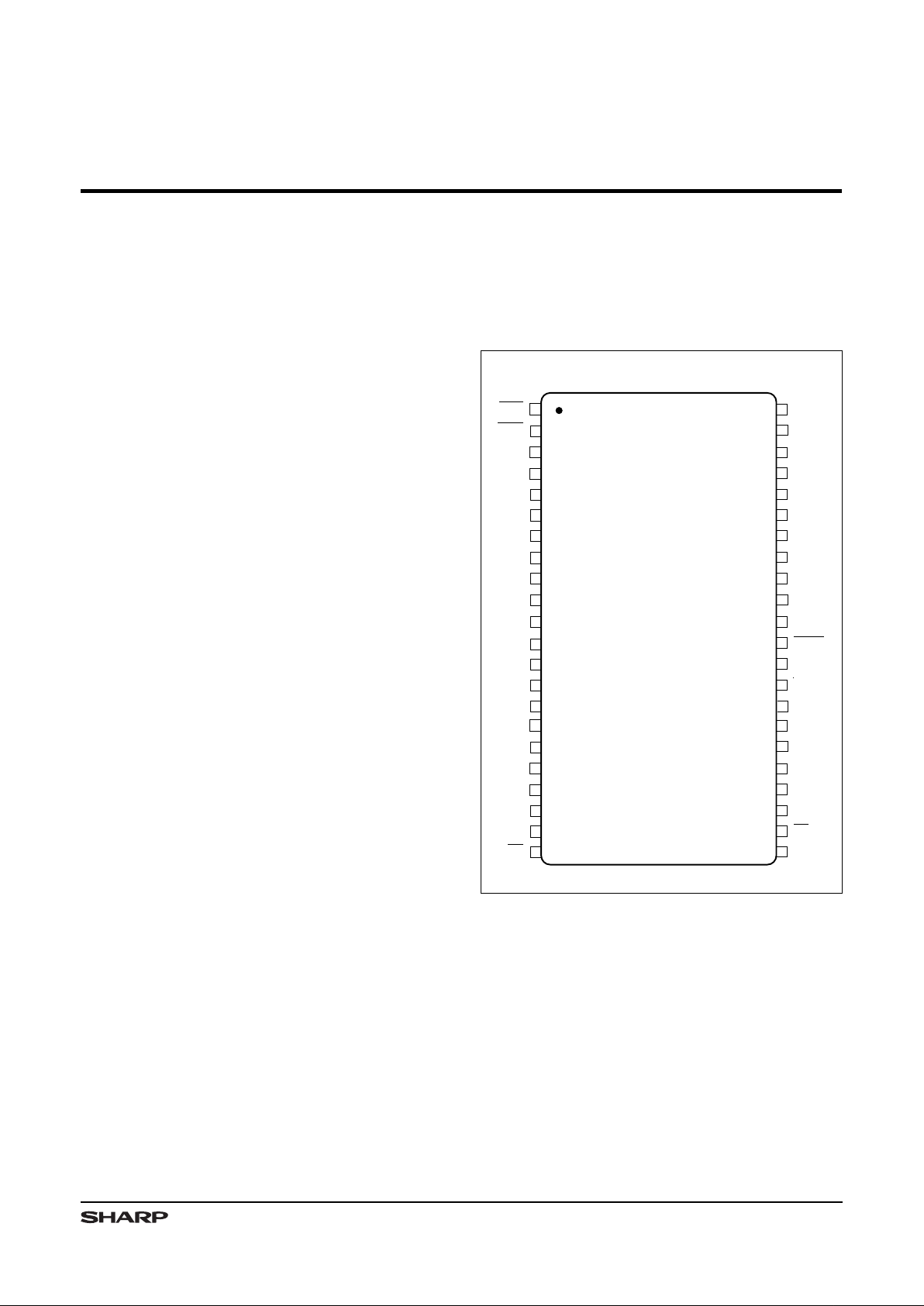

PIN CONNECTIONS

2

3

4

5

6

9

10

7

8

UWE

11

1

44

43

42

41

38

37

40

39

36

35

GND

I/O

15

44-PIN TSOP (Type II)

12

15

13

14

33

32

34

31

30

LWE

A

1

A

0

A

3

A

4

V

CC

V

CC

I/O

6

I/O

13

I/O

14

I/O

11

I/O

12

I/O

10

I/O

9

RFSH

I/O

7

I/O

5

5PV16256S-1

A

5

A

17

CS

A

16

A

15

A

14

A

13

17

18

19

20

21

22

A

11

16

29

28

27

26

23

25

24

I/O

3

A

12

A

9

A

10

CE

I/O

1

I/O

2

OE

I/O

0

GND

A

2

A

6

A

8

A

7

I/O

4

I/O

8

TOP VIEW

Figure 1. Pin Connections

1

PIN DESCRIPTION

PIN NAME FUNCTION

A7 - A

17

Row a ddr ess in put

A

0

- A

6

Colum n a ddr ess in put

UWE, LWE Upper /lo wer wri te ena ble in put

OE Outpu t e nab le i np ut

RFSH Refre sh input

CE Chip ena ble in put

PIN NAME FUNCTION

CS Chip s ele ct inp ut

I/O

8

- I/O

15

Upper byt e data input /output

I/O

0

- I/O

7

Lower byt e data input /output

V

CC

Power sup ply

GND Ground

I/O

1

CLOCK

GENERATOR

CS

A

5

A

4

A

3

A

10

A

11

A

12

A

13

A

14

A

15

A

16

A

6

A

17

A

9

A

8

A

7

COLUMN

ADDRESS

BUFFER

ROW

ADDRESS

BUFFER

REFRESH

ADDRESS

COUNTER

DATA

IN

BUFFER

DATA

OUT

BUFFER

I/O

SELECTOR

COLUMN

DECODER

SENSE

AMPS

MEMORY

ARRAY 8M

ROW

DECODER

EXT/INT

ADDRESS

MUX.

REFRESH

CONTROLLER

REFRESH

TIMER

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

V

BB

GENERATOR

GND

V

CC

A

2

A

1

5PV16256S-2

I/O

0

RFSH

OE

21

20

19

18

17

16

15

14

13

12

10

9

8

7

6

5

4

11

33

24

44

35

25

26

27

28

29

30

31

32

CE

22

A

0

3

LWE

UWE

2

1

A0 A

6

A7 -

A

17

I/O

9

I/O

10

I/O

11

I/O

12

I/O

13

I/O

14

I/O

15

I/O

8

36

37

38

39

40

41

42

43

GND

23

V

CC

34

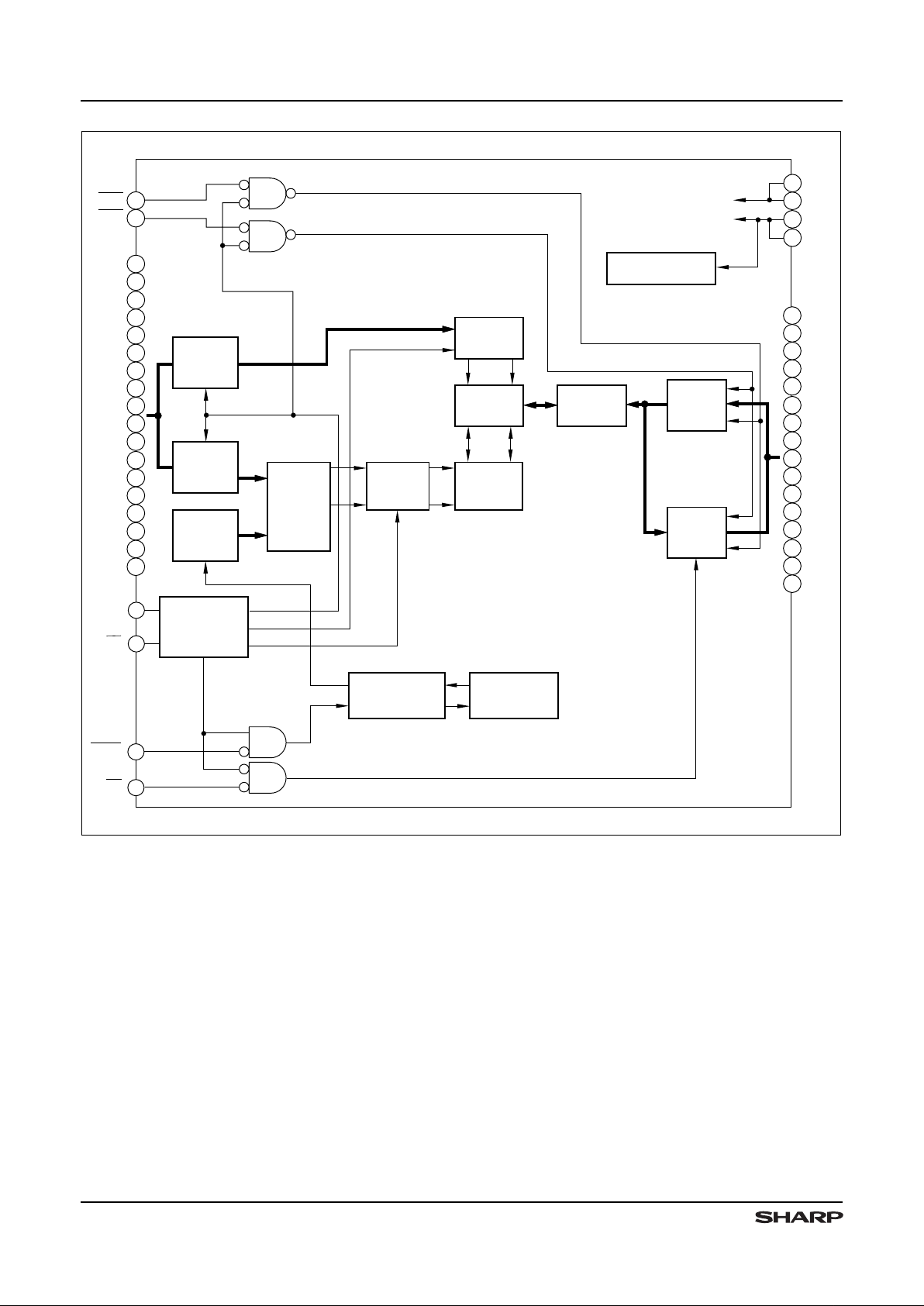

Figure 2. LH5PV16256 Block Diagram

LH5PV16256 CMOS 4M (256 × 16) Pseudo-S tatic RAM

2

TRUTH TABLE

CE CS RFSH OE UWE LWE MODE I/O

0 - 7

I/O8 - 15

L H H L H H Word Read Output data Output data

LHH X

HL

Write

Lower byte write Input data

Don’ t c are

L H Upper byte write Don’t care

Inpu t da ta

L L Word write Input data Input data

H H Invalid High-Z High-Z

H X L X X X Auto refresh High-Z High-Z

L L H X X X CS standby High-Z High-Z

H X H X X X Standby High-Z High-Z

NOTES:

H = High

L = Low

X = Don’t care

REQUIREMEN TS

2WE control

Please do not se parate the UWE and LWE operation timing intentionally in the same write cycle s. Each of the

UWE/LWE should satisfy the timing specifications individually.

Refresh after self-refresh or data retention mode

•• If address refresh is used during normal read/write cycles, the first address refresh must be executed within

15 µs after self-refresh or data retention mode ends and the address refresh must be executed continuously f or

2,048 refresh cycles.

•• If distributed auto-refresh is used during normal read/write cycles, the first auto-refresh must be executed within

15 µs after self-refresh or data retention mode ends.

•• If burst auto-refresh is used during normal read/write cycles, the first auto-refresh must be executed within

15 µs after self-refresh or data retention mode ends, and the auto-refresh must be executed continuously fo r

2,048 refresh cycles.

Bypass capacitor for power supply noise reduction

Because a PSR AM operates dynamically like a DRAM, it is recommended to put bypass capacitors between V

CC

and GND to absorb power supply noise due to the peak current.

CMOS 4M (256 × 16) Pseudo-Static RAM LH5PV16256

3

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT NOTE

Suppl y v olt age V

T

-0.5 to +4.6 V 1

Output sh ort ci rcu it c urr ent I

O

50 mA

Power dis sipati on

P

D

600 mW

Operat ing te mpe ratu re T

OPR

0 to +70 °C

Storag e t emp era ture T

STG

-65 to +150

°C

NOTE:

1. The maximum applicable voltage on any pin with respect to GND.

RECOMMENDED OPERATING CON DITIONS (TA = 0 to +70°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT NOTE

Suppl y v olt age

V

CC

2.85 3.0 3.15 V 1

GND 0 0 0 V 1

Input vol tage

V

IH

2.0

V

CC

+ 0.3 V

V

IL

-0.3 0.8 V

NOTE:

1. The supply voltage with all VCC pins must be on t he same level. The supply voltage with all GND pins must be on the sam e level.

PIN CAPACITANCE (TA = 0 to +70°C, f = 1 MHz, VCC = 3.0 V ± 0.15 V)

PARAMETER CONDITIONS SYMBOL MIN. MAX. UNIT

Input cap acitan ce

A

0

- A

17

C

IN1

8pF

UWE, LWE

OE, RFSH

C

IN2

8pF

CE, CS C

IN3

8pF

Input/ out put ca pac ita nce I/O

0

- I/O

15

C

OUT1

10 pF

DC ELECTRICAL CH ARACTERISTICS (TA = 0 to +70°C, VCC = 3.0 V ± 0.15 V)

PA RA METER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Operat ing cu rre nt i n n orm al o pe rati on I

CC1

tRC = tRC (MIN.) 40 mA 1, 2

Standb y c urr ent I

CC2

CE, RFSH = VIH (MIN.) 1mA1

CE, RFSH = VCC - 0.2 V 30 mA 1

Self-r efr esh av era ge c urr ent I

CC3

CE = VIH (MIN.)

RFSH = VIL (MAX.)

1mA1

CE = VCC - 0.2 V,

RFSH = 0.2 V

70 mA 1

Input lea kag e c urr ent I

LI

0 V ≤ VIN ≤ 6.5 V

0 V on all other pins

-10 10

µA

Output le aka ge cur ren t I

LO

0 V ≤ V

OUT

≤ VCC + 0.3 V

Input/output pins in High-Z

state

-10 10

µA

Output HI GH vol tag e V

OH

I

OUT

= -1 mA 2.4

V

I

OUT

= -100 µA

V

CC

- 0.2

V

Output LO W v olt age

V

OL

I

OUT

= 1 mA

0.4 V

I

OUT

= 100 µA

0.2 V

Data r ete nti on v ol tag e V

R

2.2 3.15 V

NOTES:

1. The in put/output pins are in high impedance state.

2. I

CC1

depends on the cycle time.

LH5PV16256 CMOS 4M (256 × 16) Pseudo-S tatic RAM

4

AC ELECTRICAL CH ARACTERISTICS

1,2,7

(TA = 0 to +70°C, VCC = 3.0 V ± 0.15 V)

PARAMETER SYMBOL MIN. MAX. U NIT NOTES

Random re ad, wri te cyc le tim e t

RC

190

ns

Random mo dif y w rite cy cl e ti me t

RMW

250

ns

CE pul se wid th t

CE

120 10,000 ns

CE pre cha rge ti me t

P

60 ns

Addres s s etu p t ime

t

AS

0 ns 3

Row ad dre ss hol d t ime fro m

CE t

RAH

30

ns 3

Column ad dre ss hol d t ime fro m CE t

CAH

120

ns

CS set up tim e f rom CE t

CS S

0

ns

CS hol d t ime fro m CE t

CSH

30

ns

Read c omm and se tup ti me

t

RCS

0 ns 11

Read c omm and ho ld time

t

RCH

0 ns 9

CE acc es s t ime t

CE A

120 ns 4

OE acces s time t

OEA

60 ns 4

CE to out put in Low -Z t

CLZ

20

ns

OE to out put in Low -Z t

OLZ

0 ns

Write d isa ble to out put in Lo w-Z

t

WLZ

0 ns 11

Chip d isa ble to ou tpu t i n Hi gh- Z t

CHZ

030ns

Output disable to outp ut in High-Z t

OHZ

030ns

WE to out put in Hig h-Z

t

WHZ

0 30 ns 9, 13

Write c omma nd pul se wid th

t

WCP

35

ns 13

Write c omma nd set up tim e

t

WCS

35 10,000 ns 10, 13

Write c omma nd hol d t ime t

WCH

120 10,000 ns 12, 13

Data s etu p t ime fro m w rite di sab le t

DS W

30 ns 5, 12, 13

Data s etu p t ime fro m c hip di sab le

t

DSC

30 ns 5

Data h old ti me f rom wri te dis abl e t

DHW

0

ns 5, 11, 13

Data h old ti me f rom ch ip dis abl e t

DHC

30

ns 5

Data h old ti me f rom co lum n a ddre ss t

OH

0

ns

Column ad dre ss hol d t ime fro m c hip di sab le t

AHC

20 ns 5

Column ad dre ss hol d t ime fro m w rite di sab le

t

AHW

0 ns 5, 13

Transiti on time (r ise an d fa ll)

t

T

350ns

Output disable set up time t

ODS

0

ns

Output di sab le hol d t ime t

ODH

15

ns

Refres h time interv al (2048 cyc le) t

REF

32 ms 6

Auto r efr esh cy cle ti me

t

FC

190 ns 6

Refres h d ela y t ime fro m

CE

t

RFD

90 ns

Refres h p uls e w idt h ( Aut o re fre sh) t

FAP

80 1,000 ns 8

Refres h p rec har ge time (A uto re fres h) t

FP

40

ns

CE del ay tim e f rom ref res h en ab le

(Auto ref resh)

t

FCE

190 ns

Refres h p uls e w idt h ( Sel f re fre sh) t

FAS

8,000

ns 8

CE del ay tim e f rom ref res h pr ech arg e

(Self ref resh)

t

FRS

600 ns

VCC reco ver y t ime fro m d ata ret ent ion t

R

5

ms

Refres h s etu p h old ti me t

FS

0 ns

Refres h d isa ble ho ld tim e

t

RDH

15 ns

Chip d isa ble de lay ti me from

RFSH t

RDD

15

ns

CMOS 4M (256 × 16) Pseudo-Static RAM LH5PV16256

5

Loading...

Loading...