Sharp LH5P832N-12, LH5P832N-10, LH5P832D-12, LH5P832D-10, LH5P832-12 Datasheet

...

LH5P832

CMOS 256K (32K × 8) Pseudo-Static RAM

FEATURES

•• 32,768 × 8 bit organ ization

•• Access time: 100/120 ns (MAX.)

•• Cycle ti me: 160/190 ns ( MIN.)

•• Powe r consu mp tion:

Operating : 357.5/303 mW

Standb y: 16.5 mW

•• TTL compatible I/O

•• 256 refresh cycle/4 ms

•• Auto refresh is execu te d by internal

counter (controlled by

OE/RFSH pin)

•• Self refresh is execu ted by internal timer

•• Sing le +5 V p owe r su ppl y

•• Packa ges:

28-pi n , 600 -mil DIP

28-pi n , 300 -mil SK-DIP

28-pi n , 450 -mil S OP

DESCRIPTION

The LH5P832 is a 256K bit Pseudo-Static RAM organized as 32,768 × 8 bits. It is fabricated using silicon-gate CMOS process technology.

The LH5P832 uses convenient on-chip refresh circuitry with a DRAM memory cell for pseudo static

operation. This simplifies external clock inputs, while

providing the same simple, non-multiplexed pinout as

industry standard SRAMs. Moreover, due to the functional similarities between PSRAMs and SRAMs, many

32K × 8 SRAM sockets can be filled with the LH5P832

with little or no changes. The advantage is the cost

savings realized with th e lower cost PSRAM.

The LH5P832 PSRAM has the ability to fill the gap

between DRAM and SRAM by offering low c ost, low

standby power, and a simple interface.

Three methods of refresh control are provided for

maximum versatility. A ‘CE-Only’ refresh cycle refreshes the addressed row of memory cells t ransparently . All 256 rows must be refreshed or accessed every

four milliseconds. ‘Auto Refresh’ automatically cycles

through a different row on every OE/RFSH clock pulse,

accomplishing the row refreshes without the need to

supply row addresses externally. ‘Self Refresh’ further

simplifies the r efresh requirements by eliminating the

need for address inputs and clock pulses entirely. An

automatic timer senses time periods when memory

accesses have ceased, and provides full refresh of all

rows of memory without any external assistance.

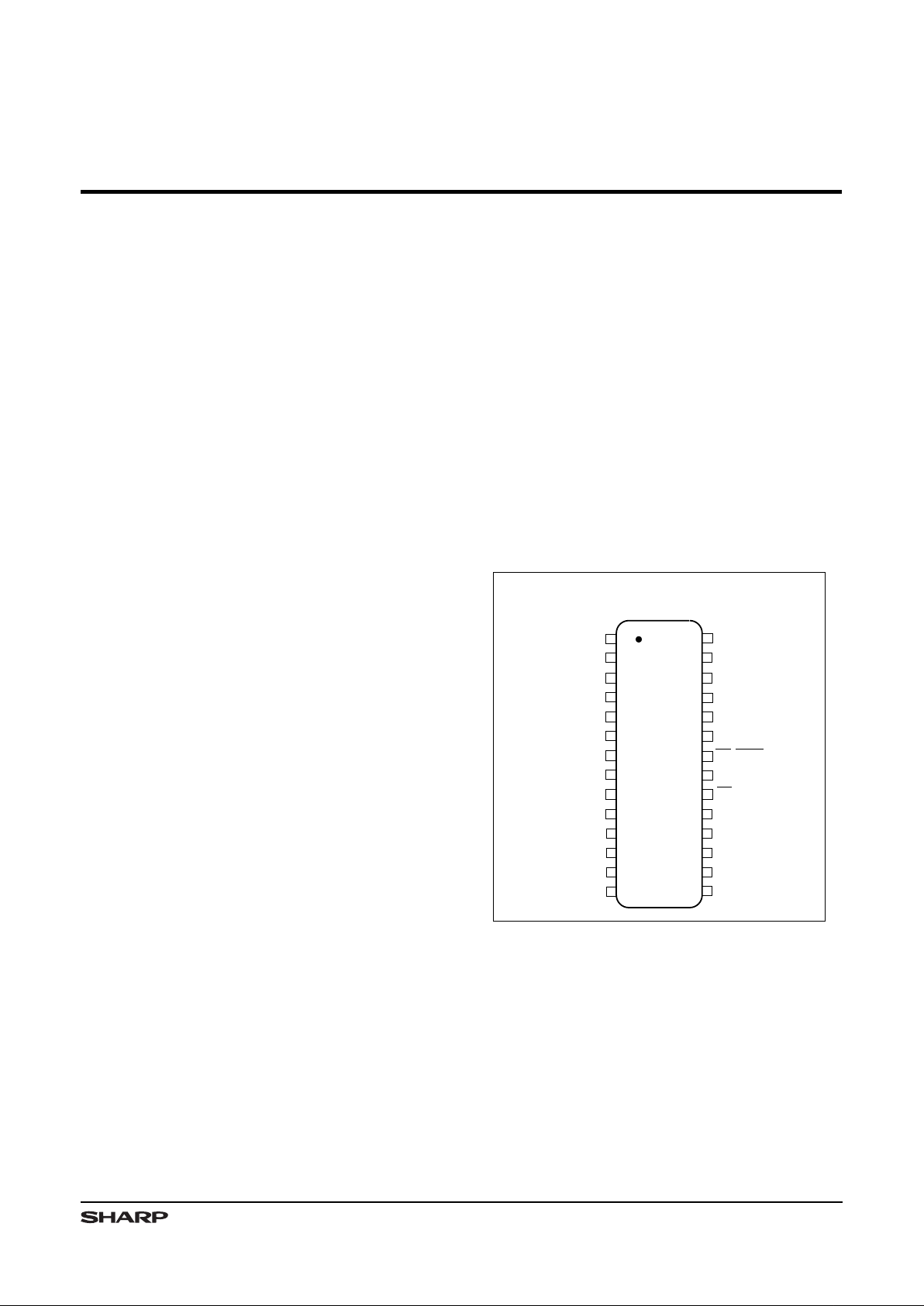

PIN CONNECTIONS

TOP VIEW

1

2

3

4

7

8

A

2

A

5

26

25

24

23

22

21

18

15

A

7

A

6

5

6

A

3

A

4

20

19

A

12

GND

A

8

A

11

A

10

CE

9

10

11

28

27 R/W

A

1

V

CC

12

17

16

A

0

I/O

1

A

9

13

14

OE/RFSH

I/O

2

I/O

3

I/O

7

I/O

6

I/O

5

I/O

4

I/O

8

5P832-1

A

14

A

13

28-PIN DIP

28-PIN SK-DIP

28-PIN SOP

Figure 1. Pin Connections for DI P, SK-DIP,

and SOP Packages

1

5P832-2

I/O

1

20

CLOCK

GENERATOR

27

22

CE

R/W

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

A

7

A

6

A

4

A

5

A

13

A

14

COLUMN

ADDRESS

BUFFER

ROW

ADDRESS

BUFFER

REFRESH

ADDRESS

COUNTER

DATA

IN

BUFFER

DATA

OUT

BUFFER

I/O

SELECTOR

COLUMN

DECODER

SENSE

AMPS

MEMORY

ARRAY

256 ROWS

128 COLUMNS

ROW

DECODER

EXT/INT

ADDRESS

MUX

I/O

2

I/O

3

I/O

4

I/O

5

I/O

6

I/O

7

I/O

8

V

BB

BIAS-GENERATOR

GND

V

CC

OE/

RFSH

16

17

18

19

15

13

12

11

2

23

21

24

26

1

4

7

8

3

6

25

5

9

28

14

A

0

10

SELF-REFRESH

TIMER

AUTO-REFRESH

CONTROLLER

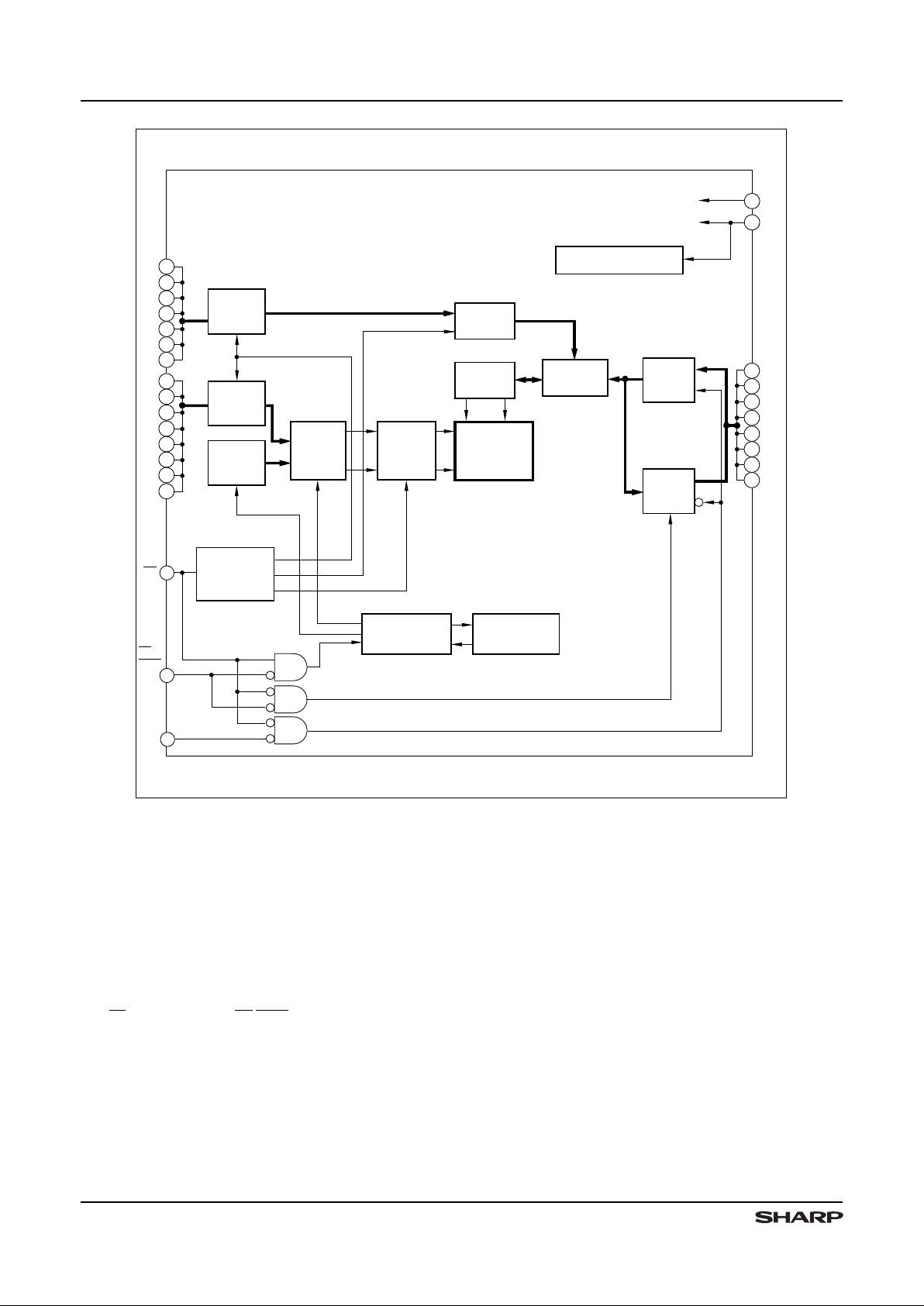

Figure 2. LH5P832 Block Diagram

PIN DESCRIPTION

SIGNA L PIN N AME

R/W Read/ Writ e in put

OE/RFSH Outpu t E nab le/ Ref res h in put

I/O

1

- I/O

8

Data inp uts and outpu ts

A

0

- A

7

Row a ddr ess in put s

SIGNAL PIN NAME

A8 - A

14

Column Add res s inp uts

CE Chip E nab le inp ut

V

CC

Power sup ply

GND Ground

TRUTH TABLE

CE R/W OE/RFSH MODE I/O1 - I/O

8

I

CC

NOTE

L L X Write Data in Operating (I

CC1

)1

L H L Read Data out Operating (I

CC1

)

LHH

CE-Only Refresh High-Z Operating (I

CC1

)

H X L Auto Refresh High-Z Operating (I

CC1

) 1, 2

H X L Self Refresh High-Z Self Refresh (I

CC3

) 1, 3

H X H Standby High-Z Standby (I

CC2

)1

NOTES:

1.

X = H or L 2.

OE Pulsewidth < 8 µs 3. OE Pulsewidth ≥ 8 µs

LH5P832 CMOS 256K (32K × 8) Pseudo-Static RAM

2

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATI NG UNIT NOTE

Appli ed v ol tage on an y p in V

T

-1.0 to +7.0 V 1

Output sh ort ci rcu it c urr ent I

O

50 mA

Power dis sipati on P

D

600 mW

Operat ing te mpe ratu re

Topr 0 to +70 °C

Storage temperature Tstg -55 to +150

°C

NOTE:

1. Referenced to GN D

RECOMMENDED OPERATI NG CONDITIONS (TA = 0 to +70°C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT

Suppl y v olt age V

CC

4.5 5.0 5.5 V

Input vol tage

V

IH

2.4 VCC + 0.3 V

V

IL

-1.0 +0.8 V

CAPACITANCE (VCC = 5.0 V ±10%, TA = 0 t o +70°C, f = 1 MHz)

PARAMETER CONDITIONS SYMBOL MIN. MAX. UNIT

Input cap acitan ce

A

0

- A14, R/W C

IN1

8pF

CE, OE/RFSH C

IN2

5pF

Input/ out put ca pac ita nce

I/O

1

- I/O

8

C

OUT1

12 pF

DC CHARACTERISTICS (VCC = 5 V ± 10%, TA = 0 t o +70°C)

PARAMETER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Operat ing cu rre nt I

CC1

tRC = 160 ns 65 mA 1, 2

Operat ing cu rre nt I

CC1

tRC = 190 ns 55 mA 1, 2

Standb y c urr ent I

CC2

CE = VIH, OE/RFSH = V

IH

3mA1

Self r efr esh av era ge c urr ent I

CC3

CE = VIH, OE/RFSH = V

IL

3mA1

CPU in ter nal cy cle

averag e c urr ent

I

CC4

tRC = 160 ns 65 mA 1, 2

CPU in ter nal cy cle

averag e c urr ent

I

CC4

tRC = 190 ns 55 mA 1, 2

Input lea kag e c urr ent I

LI

0 V ≤ VIN ≤ 6 .5 V -10 10 µA

Output le aka ge cur ren t I

LO

0 V ≤ V

OUT

≤ VCC + 0.3 V -10 10 µA3

Output Hi gh vol tag e V

OH

I

OUT

= -1 mA 2.4 V

Output Lo w v olt age V

OL

I

OUT

= 4 mA 0.4 V

NOTES:

1. Specified values are with outputs open.

2. I

CC1

and I

CC4

depend on the cycle time.

3. The output pins are in high-impedance state.

AC TEST CONDITIONS

PARAMETER MODE NOTE

Input voltage amplitude 0.6 to 2.4 V

Input rise/fall time 5 ns

Timing re fer enc e l eve l 1.5 V

Output load conditions 1TTL gate, C

L

= 100 pF 1

NOTE:

1. In cludes scope and jig capacitance.

CMOS 256K (32K × 8) Pseudo-Stat ic R AM LH5P 832

3

Loading...

Loading...