LH538700A

CMOS 8 M (1M × 8) MROM

FEATURES

•• 1,048,5 76 w ords × 8 bi t organ izatio n

•• Access time: 100 ns (MAX.)

•• Power consu mption :

Operating : 55 0 mW (MAX.)

Standb y: 550 µW (MAX.)

•• Static operation

•• TTL compatible I/O

•• Three-state outputs

•• Singl e +5 V p owe r su ppl y

•• Packa ges:

32-pi n , 600 -mil DIP

32-pi n , 525 -mil S OP

32-pin, 400-mil TSOP (Type II)

DESCRIPTION

The LH538700A is an 8M-bit mask-programmable

ROM organize d a s 1,048,576 × 8 bits. It is fabricated

using sili con-gate CMOS process technology.

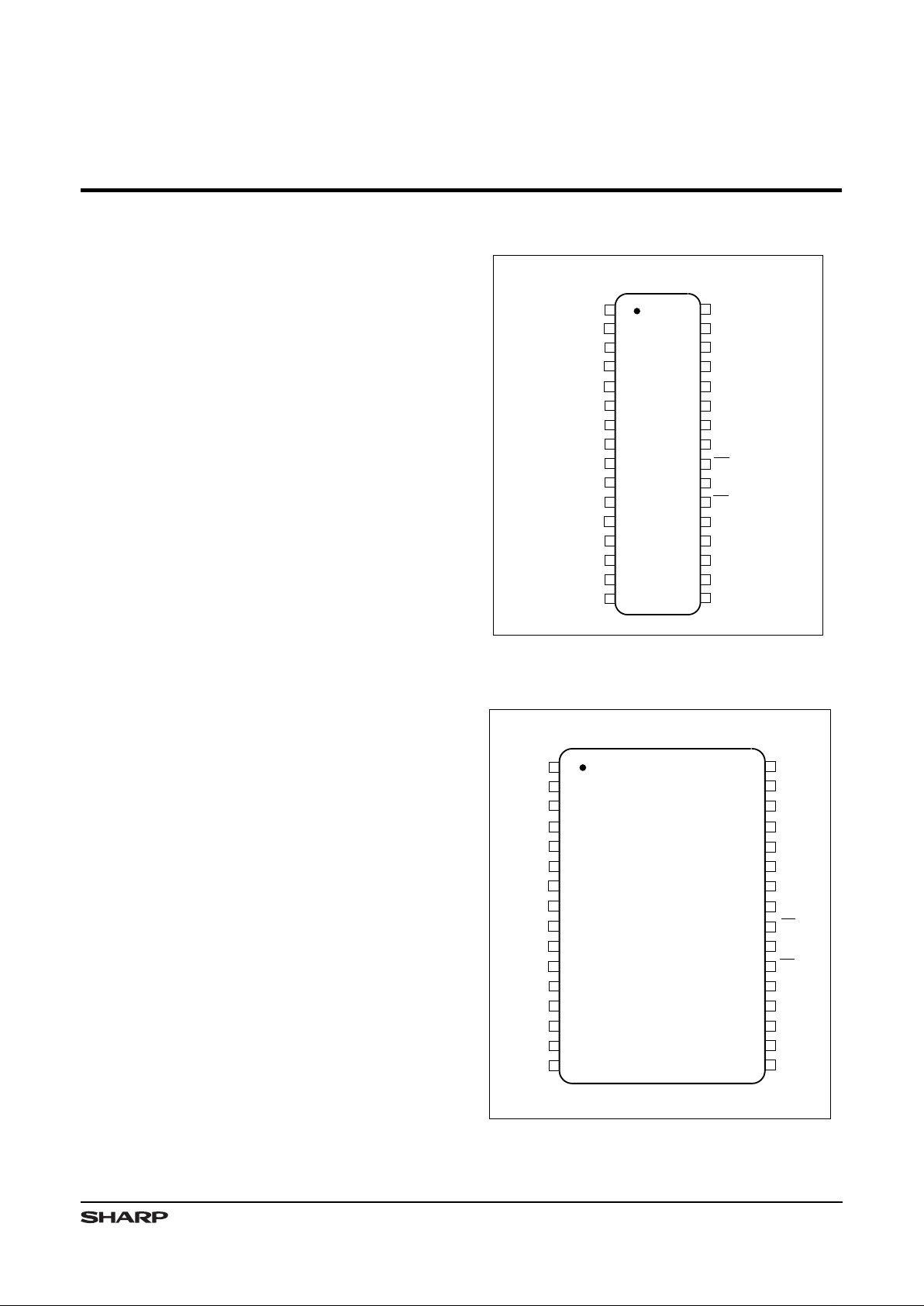

PIN CONNECTIONS

538700A-1

TOP VIEW

1

2

3

4

5

6

9

10A

2

A

5

V

CC

28

27

26

25

24

23

20

17

A

7

A

6

7

8

A

3

A

4

22

21

A

15

A

12

GND

A

13

A

8

A

11

A

10

CE

D

7

D

6

D

3

11

12

13

32

31

30

29 A

14

A

1

14

15

16

19 D

5

18 D

4

D

1

D

2

A

0

D

0

A

9

A

16

OE

32-PIN DIP

32-PIN SOP

A

19

A

18

A

17

Figure 1. Pin Connections for DI P and

SOP Packages

538700A-2

TOP VIEW

2

3

4

5

8

9

A

4

A

7

29

28

27

26

25

24

21

18

A

15

A

12

6

7

23

22

A

14

D

4

10

11

12

31

30

A

2

13 20

19

A

3

32-PIN TSOP (Type II)

14

15

16 17 D

3

321

A

16

CE

A

18

A

13

A

9

A

11

OE

A

10

A

8

D

7

D

6

D

5

A

19

A

1

A

0

D

0

D

1

D

2

GND

NOTE: Reverse bend available on request.

A

6

A

5

V

CC

A

17

Figure 2. Pin Connections for TSOP Package

PRELIMINARY

1

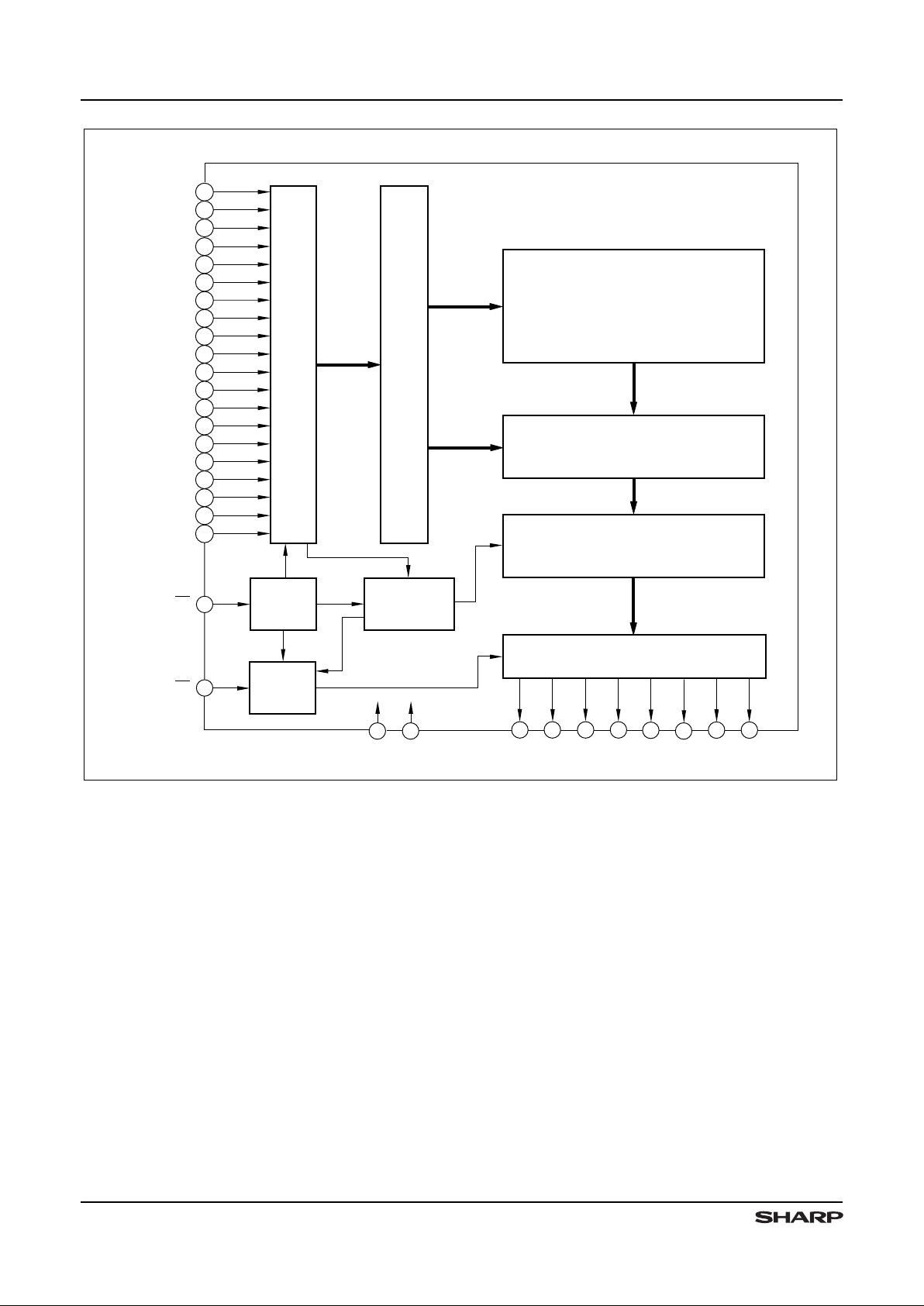

538700A-3

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

32

4

25

23

26

6

9

10

11

A

7

A

6

V

CC

A

4

18

19

20

13

21

D

0

MEMORY

MATRIX

(1,048,576 x 8)

SENSE AMPLIFIER

OUTPUT BUFFER

16

5

GND

D

1D2D3D4

D

5

D6D

7

17

14

15

8

27

A

5

7

A

13

28

ADDRESS BUFFER

CE

A

0

12

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

29

A

15

3

22

TIMING

GENERATOR

A

16

2

24

OE

A

17

30

A

18

31

A

19

1

Figure 3. LH538700A Block Diagram

PIN DESCRIPTION

SIGNAL PIN NAME

A0 – A

19

Addr ess in put

D

0

– D

7

Data ou tpu t

CE Chip en abl e i npu t

SIGNAL PIN NAME

OE Output ena ble in put

V

CC

Power supply (+5 V)

GND Ground

LH538700A PREL IMINARY CMOS 8M MROM

2

Loading...

Loading...