Sharp LH534A00T Datasheet

LH534A00

CMOS 4M (512K × 8) MROM

FEATURES

•• 524,288 w ords × 8 b it organ izatio n

•• Access time: 120 ns (MAX.)

•• Static operation

•• TTL compatib le I/O

•• Three-state outputs

•• Singl e +5 V po we r su ppl y

•• Powe r consu mption :

Operating : 357.5 mW (MAX.)

Standby: 550 µW (MAX.)

•• Package:

32-pi n , 8 × 20 mm

2

TSOP (Typ e I)

DESCRIPTION

The LH534A00 is a 4M-bit mask-programmable ROM

organized as 524,288 × 8 bits. It is fabricated using

silicon-gate CMOS process technology.

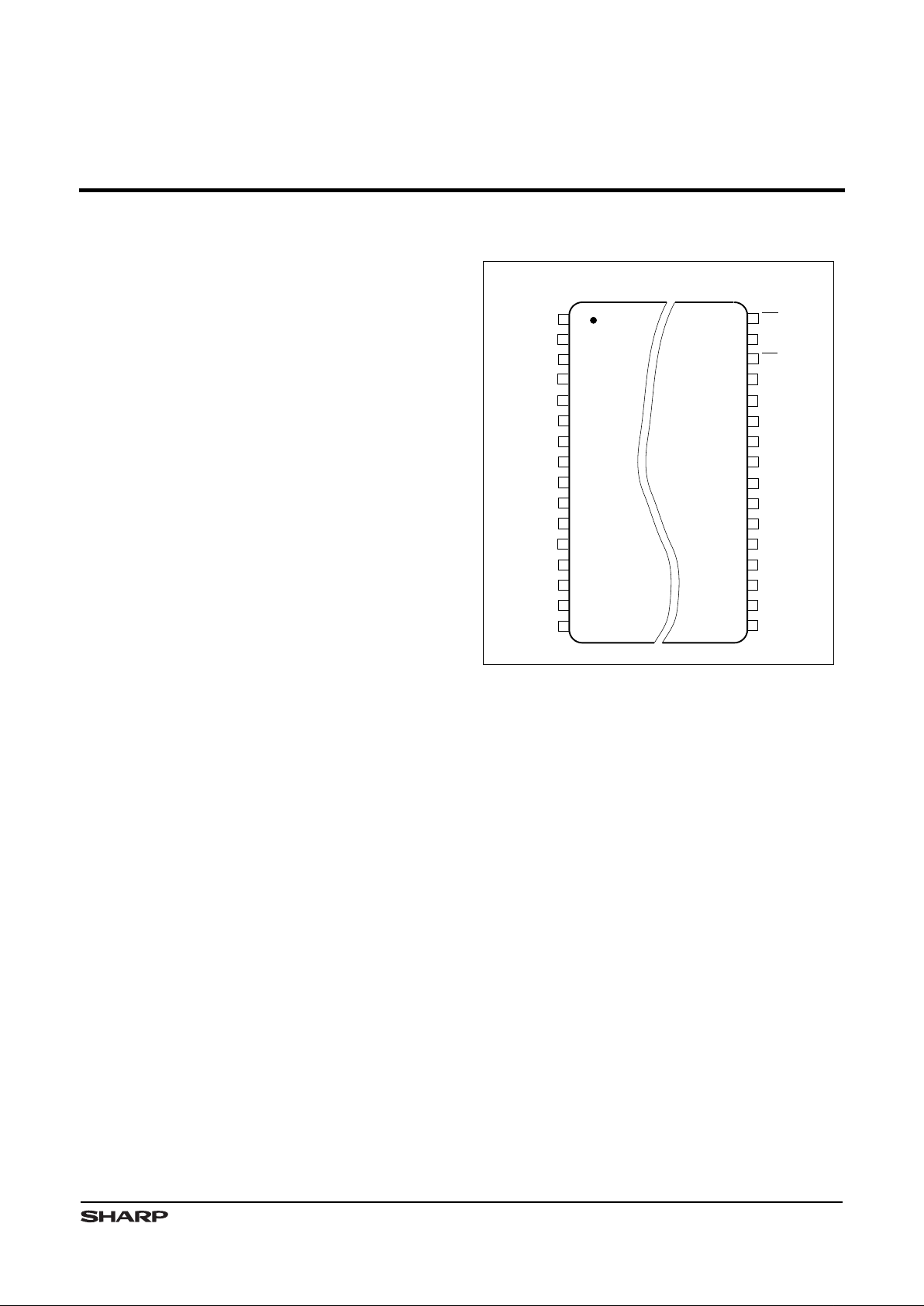

PIN CONNECTIONS

534A00-1

TOP VIEW

1

2

3

4

5

6

9

10A

16

NC

OE

28

27

26

25

24

23

20

17

A

14

A

17

7

8

A

18

V

CC

22

21

A

8

A

13

D

6

D

5

D

3

D

2

D

0

A

0

A

3

11

12

13

32

31

30

29 D

7

A

15

14

15

16

19 A

1

18 A

2

A

6

A

5

A

12

A

7

D

4

A

9

GND

32-PIN TSOP (Type I)

A

10

CE

A

11

A

4

D

1

Figure 1. Pin Connections for TSOP Package

1

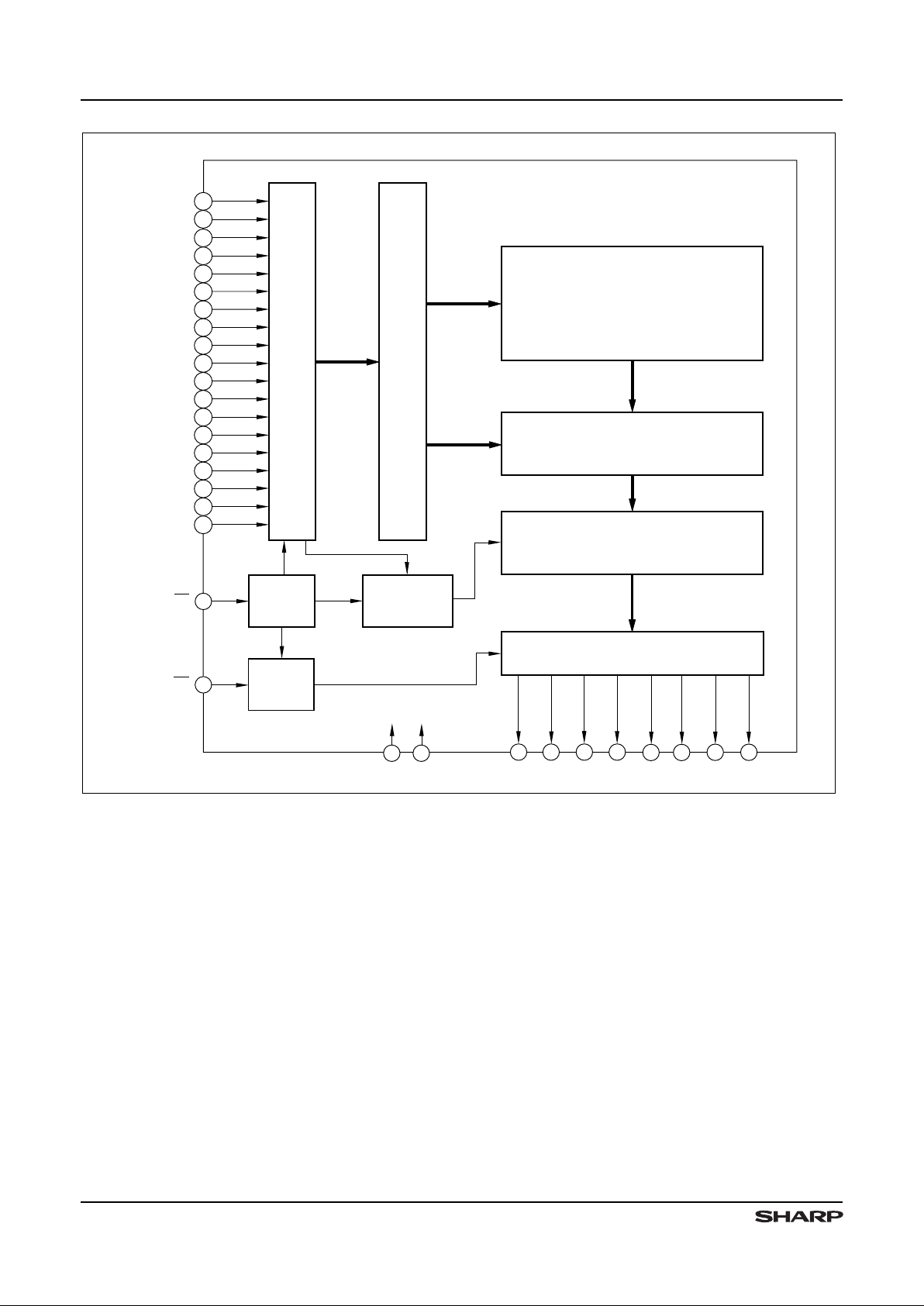

534A00-2

A

3

A

2

A

1

A

12

A

11

A

10

A

9

A

8

12

1

31

2

14

17

18

19

A

7

A

6

V

CC

A

4

26

27

28

21

29

D

0

MEMORY

MATRIX

(524,288 x 8)

SENSE AMPLIFIER

OUTPUT BUFFER

24

13

GND

D

1D2D3D4D5D6D7

25

22

23

16

3

A

5

15

A

13

4

ADDRESS BUFFER

CE

A

0

20

ADDRESS DECODER

COLUMN SELECTOR

CE

BUFFER

OE

BUFFER

A

14

5

A

15

11

30

TIMING

GENERATOR

A

16

10

32

OE

A

17

6

A

18

9

8

Figure 2 . LH534 A00 Block Diagram

PIN DESCRIPTION

SIGNAL PI N N AM E

A0 – A

18

Addres s i npu t

D

0

– D

7

Data o utp ut

CE Chip e nab le inp ut

SIGNAL PIN NAME

OE Output ena ble input

V

CC

Power sup ply (+5 V)

GND Ground

LH534A0 0 CMOS 4M MROM

2

Loading...

Loading...