Page 1

MODELS:

LC-26D44

LC-32D44

Training Course

Presentation By:

Jan Niemi

SEES Engineering Department

Issued: Sofía García

SEES Engineering Department

Training course: D44

1

May 2008

Page 2

1. Models introduction

2. Block Diagram

3. Software Updating

4. Service Mode

Index

5. LCD Adjust Process

6. Electrical Diagrams / PWB

SEES Engineering Department

Training course: D44

2

Page 3

Sizes:

26” & 32”

Type of cabinet:

- Bottom speakers.

- BK : Black Color.

- GY: Grey Color.

Models:

1. Models Introduction

LC-26/32D44EE-BK/GY → Continental

LC-26/32D44ES-BK/GY → Sweden Market

LC-26/32D44EK-BK/GY → United Kingdom

LC-26/32D44RU-BK/GY → Russian Market

SEES Engineering Department

Training course: D44

3

Page 4

LC-26D44 & LC-32D44 Models

• ASV & Black TFT LCD.

• HD Ready Panel (1366 x 768)

WXGA with 4ms response.

• Wide vision angle (H/V 176º).

• High brightness and contrast (1.500:1).

• Interlaced and progressive mode compatible (I/P).

• Built-in DVB-T Tuner.

• Multistandard Video and audio:

- Multistandard Video & audio .

- Video: PAL/SECAM & NTSC (AV only).

- TV: B/G, I, D/K, L & L’.

- Sound: NICAM & A2 (IGR).

• OSD multilanguage.

•

2 HDMI 1.2 inputs (Video Digital, Audio Digital

& Analog).

•

Analog mode PC input.

• Components Input ( 3RCA to 15pin D-sub adapter).

• RGB at EXT1/EXT2 Terminal.

• RS-232C.

• AV-Link at EXT2.

• Does not support CEC at HDMI.

• Active Backlight (dynamic contrast 10.000:1)

• Sleep Timer.

• Does not support “RC Path Through” by Pin Nº 9 of

1. Models Introduction (continued)

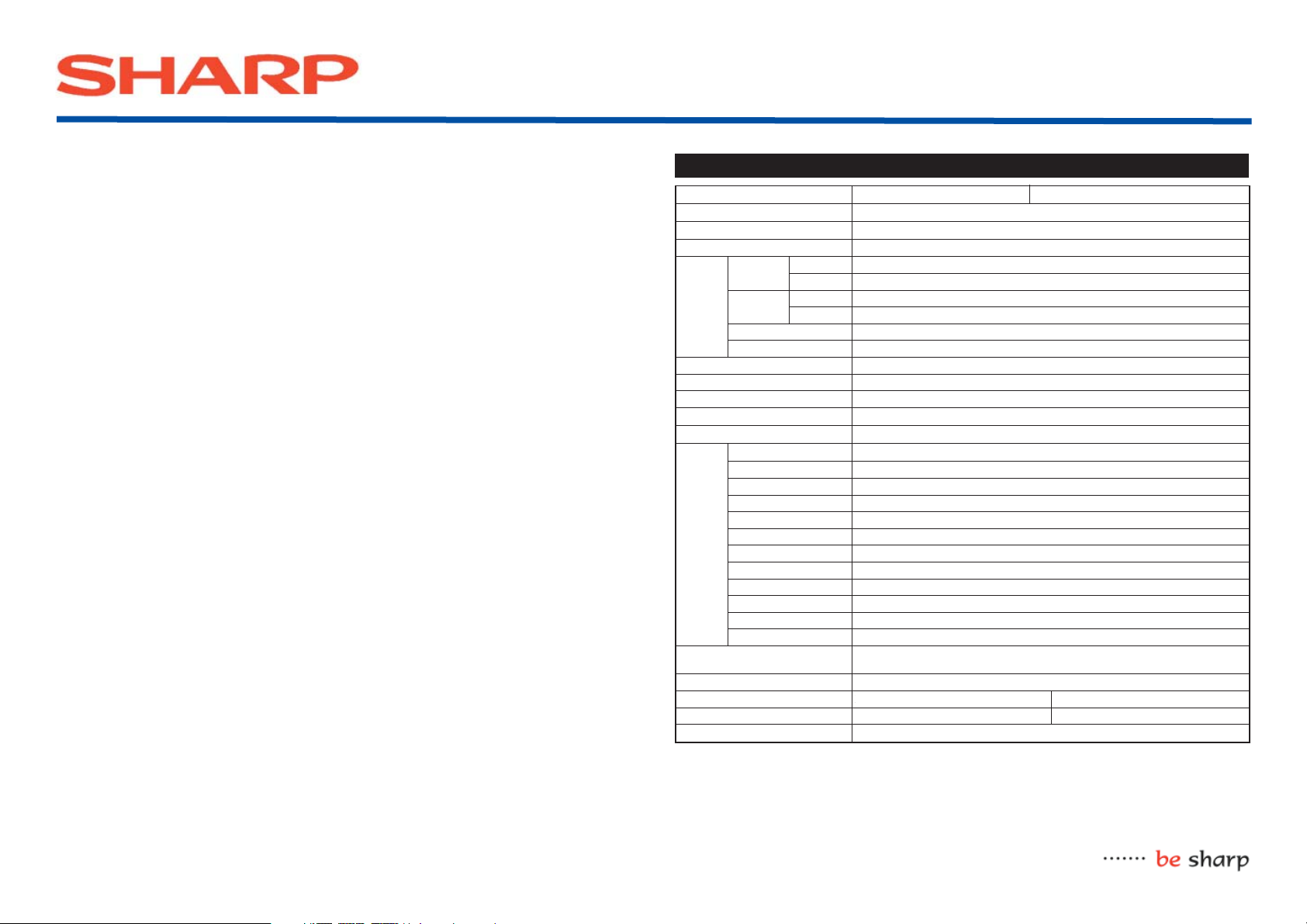

Specifications

Item

LCD panel

Resolution

Video Colour System PAL/SECAM/NTSC 3.58/NTSC 4.43/PAL 60

TV

Function

Brightness 450 cd/m2

Backlight life 60,000 hours (at Backlight Standard position)

Viewing angles H : 176° V : 176°

Audio amplifier

Speaker

Terminals Antenna

OSD language English/German/French/Italian/Spanish/Dutch/Swedish/Portuguese/Finnish/Turkish/Greek/

Power Requirement AC 220–240 V, 50 Hz

Power Consumption XXX W (0.9 W Standby) (Method IEC60107)

Weight XX.X kg (Display only), XX.X kg (Display with stand)

Operating temperature

• As a part of policy of continuous improvement, SHARP reserves the right to make design and specification changes for

TV-Standard Analogue CCIR (B/G, I, D/K, L, L’)

Digital DVB-T (2K/8K OFDM)

Receiving

Channel

TV-Tuning System Auto Preset 99 ch, Auto Label, Auto Sort

STEREO/BILINGUAL NICAM/A2

RS-232C 9 pin mini D-sub

EXT 1 SCART (AV input, Y/C input, RGB input, TV output)

EXT 2 SCART (AV input/output, Y/C input, RGB input, AV Link)

EXT 3 S-VIDEO (Y/C input), RCA pin (AV input)

EXT 4 Ø 3.5 mm jack (Audio input), 15 pin mini D-sub (PC)

EXT 5 Audio in, Component in

EXT 6 HDMI, Ø 3.5 mm jack (Audio input)

EXT 7 HDMI

C. I. (Common Interface) EN50221, R206001

OUTPUT RCA pin (Audio)

Headphones Ø 3.5 mm jack (Audio output)

product improvement without prior notice. The performance specification figures indicated are nominal values of production

units. There may be some deviations from these values in individual units.

VHF/UHF E2–E69ch, F2–F10ch, I21–I69ch, IR A–IR Jch, (Digital: E5–E69ch)

CATV Hyper-band, S1–S41ch

TV LCD 26”: LC-26D44E/S/K/RU TV LCD 32”: LC-32D44E/S/K/RU

26o LCD COLOUR TV, Model: LC-26D44E, LC-26D44S

26o Advanced Super View & BLACK TFT LCD

1,049,088 pixels (1,366 g 768)

10W g 2

Ø XX mm g 2, Ø XX mm g 2

UHF/VHF 75q Din type (Analogue & Digital)

Russian/Polish

95W (0,9 Standby) Method IEC60107)

10,5 Kg (With Stand) 13,0 Kg (With Stand)

0°C to k40°C

120W (0,9 Standby) Method IEC60107)

Service Connector.

SEES Engineering Department

Training course: D44

4

Page 5

2. Block Diagrams

Main ICs

IC207: COFDM DECODER (Coded Orthogonal Frequency Division Multiplexing)

Part Number : STV0362 SHARP Code: RH-IXB964WJZZQ

The STv0362 is a single-chip demodulator using COFDM and is intended for digital terrestrial receivers using compressed video, sound and data

services. It converts IF or base band differential signals to MPEG-2 transport stream format by processing OFDM carriers. The STv0362 is fully

compliant with the DVB-T specifi cation (ETS 300 744) and Nor Dig Unifi ed specifi cation.

IC1951: HDMI RECEIVER (High Defi nition Multimedia Interface)

Part number : Sii9025 SHARP Code : VHISII9025+-1Q

The Sii9025 is a compliant with the latest HDMI 1.2 (High Defi nition Multimedia Interface) specifi cation. Backward compatibility with DVI 1.0 allows

HDMI systems to connect to existing DVI 1.0 hosts. The SiI9025 is capable of receiving and outputting two channel digital audio at up to 192 kHzan excellent solution for Digital TVs. An S/PDIF port supports up to 192 kHz audio. The SiI9025 also comes pre-programmed with HDCP keys,

greatly simplifying the manufacturing process, while providing the highest level of HDCP key security.

This IC includes the main features show below:

1- Dual-Input HDMI 1.2, HDCP 1.1 and DVI 1.0 compliant receiver.

2- Integrated TMDSR core.

3- Digital video interface supports video processors:

• 24-bit RGB/YCbCr 4:4:4

• 16/20/24-bit YCbCr 4:2:2

• 8/10/12-bit YCbCr 4:2:2 (ITU BT.656)

• 12-bit DMO (Digital Multimedia Output) RGB/YCbCr 4:4:4 (clocked with rising & falling edges)

• Color Space Conversion for both RGB-to-YCbCr and YCbCr-to-RGB (both 601 and 709)

• Auto video mode configuration simplifies system firmware design

SEES Engineering Department

Training course: D44

7

Page 6

2. Block Diagrams (continued)

Main ICs

4- Digital audio interface supports high-end audio systems:

• One programmable I2S output for connection to low-cost DACs at 32-192kHz.

• S/PDIF output supports PCM, Dolby Digital, DTS digital audio transmission (32-192 kHz Fs) using IEC60958 and IEC61937.

• Auto audio error detection with programmable soft mute.

5- Integrated HDCP decryption engine for receiving protected audio and video content.

6- HDCP Built in Self Test (BIST) lowers cost to test HDCP operation.

7- Pre-programmed HDCP keys provide highest level of key security, simplifi es manufacturing.

IC1922 & IC1902: NVM OF HDMI (E-EDID)

Part Number : 24LC2BIN SHARP Code: VHI24LC2BIN-1Y

This IC is a 2-wire (I2C bus type) serial EEPROM this is electrically programmable. This EEPROM chip stores the data structure used to carry

confi guration information for optimal use of a display (EDID data).

IC4001: DIGITAL PROCESSOR MPEG 1/2 DECODER (Audio/Video)

Part Number : STI5105ALC SHARP Code: RH-IXC243WJZZQ

The STi5105ALC sets a new standard for set-top box decoder ICs, delivering outstanding performance, features and innovations to dramatically

reduce cost compared with previous generations. The Sti5105 features an even faster ST20CPU with direct map, single cycle caches to boost

performance.

Graphics and display capabilities have been enhanced with the provision of a blitter engine for formatting and fi nal display composition. Color

formats (CLUT8 and true color ARGB16) and display planes (background, still picture, video and OSD graphics) are provided. Overall system

performance benefi ts from the integration of SDRAM (DDR or SDR) external memory, that provides a unifi ed memory system with high bandwith

and low latency CPU access over a 16-bit interface.

System cost reduction is further promoted by the integration of additional peripheral and system services functions, such as VCXO, an enhancer

reset controller, DVB-CI support, smartcard power control and improved low power and standby functionality.

SEES Engineering Department

Training course: D44

8

Page 7

2. Block Diagrams (continued)

Main ICs

This IC includes the main features show below:

1- An enhanced ST20 32-bit VL-RISC CPU with a 200MHz clock, 4Kbytes of instruction cache, 4Kbytes of data cache and 2Kbytes of

embedded SRAM.

2- A 16-bit, 166MHz Shared Memory Interface, with support for 64- and 128-bit confi gurations.

3- A programmable External Memory Interface supporting 4 separately confi gurable banks of SRAM, Flash and DRAM.

4- An MPEG-2 (MP@ML) decoder, including trick modes such as smooth fast-forward and rewind.

5- A Graphics/Display unit with 4 display planes, alpha blending, antialiasing and antifl utter fi lters, subpicture decoder, and blitter

display compositor with separate OSD (On-Screen Display) controls for TV and VCR outputs.

6- PAL/NTSC/SECAM encoder.

7- CGMS, Teletext, WSS, VPS encoder.

8- MPEG-1 layer I/II audio subsystem with embedded DSP for all popular audio formats.

9- A full range of on-chip peripherals, including 2 UARTs, 3 parallel I/O banks, 1 smartcard interface, four PWM channels, 1 IR

transmitter/receiver, etc.

IC4252: NVM 64Kb-E2PROM FOR DIGITAL PROCESSOR (IC4001).

Part Number : BR24S64FVM-WTR SHARP Code: VHIBR24S64M-1Y

The BR24S64FVM is a 2-wire (I2C bus type) serial EEPROM that is electrically programmable. This IC stores all data related to the Digital Module

(Channels, User settings, etc.).

SEES Engineering Department

Training course: D44

9

Page 8

2. Block Diagrams (continued)

Main ICs

IC3001: Main CPU / VIDEO PROCESSOR.

Part Number: VCT7993P-FA-A1-H000 SHARP Code: RH-IXC354WJZZQ

The VCT 77VWP (VCT-Pro) family is dedicated to high-quality FPD and double-scan TV sets. The memory and program ROM are integrated in

the IC. Modular design and deep submicron technology allow the integration of audio, video, Teletext, OSD, and controller-related functionalities.

They cover the whole range of fl at-panel display TVs. Each member of the IC family contains the entire audio, video, up-conversion processing for

4:3 and 16:9 50/60 Hz progressive or 100/120 Hz interlaced stereo TV sets plus the control/data interface for fl at-panel displays. The integrated

microcontroller supports a powerful OSD and graphics generator with integrated Teletext acquisition.

The VCT 77vwP family provides a front-end video-processing unit with 4 CVBS-Y/C or component inputs for HDTV, EDTV and SDTV. A VBI slicer,

support of 2000 pages of Teletext, and a 3-D comb fi lter for PAL and NTSC (in certain versions) are also available. The front-end unit further allows

processing an SD and an HD source in parallel, thus enabling PiP and PaP functionality. Motion-adaptive de-interlacing, temporal noise reduction,

and fi lm mode detection are based on a unifi ed memory technology. Post-scaling in the display-processing block ensures the desired output format.

Display processing is supported by an 8-bit 8051-compatible controller. By means of powerful alpha blending, the graphics mixer composes the

output image from following image layers: the video layer, the OSD layer and the pixel graphics layer. The audio part consists of a multi-standard

sound IF demodulator and a base-band processor supporting all desired sound features in this range.

The VCT-Pro front-end video processing unit offers 16 analog video inputs (CVBS/Y/C, RGB/Y Cr Cb) as well as digital interfaces for SDTV and

HDTV. Latest 3D+ comb fi lter generation provides highest performance for PAL/NTSC signals.

A VBI slicer, supporting up to 2000 pages of Teletext completes the analog video front end. 3D-motion-adaptive de-interlacing, temporal noise reduction and fi lm mode detection are based on a unifi ed memory technology.

SEES Engineering Department

Training course: D44

10

Page 9

2. Block Diagrams (continued)

Main ICs

This IC includes the main features show below:

1- Stereo Decoder Audio Processing.

2- Video Front-end 3D Comb fi lter, PC Connectivity.

3- Motion Adaptive Deinterlacer.

4- Scaling, Display Processing and FPD Control.

5- Unifi ed Memory for Audio, Video and Teletext.

6- OSD and Teletext processor.

7- Main CPU (TV controller).

IC3051: NVM 64Kb-E2PROM FOR ANALOG PROCESSOR (IC3001).

Part Number: BR24S64FVM-WTR SHARP Code: VHIBR24S64M-1Y

The BR24S64FVM is a 2-wire (I2C bus type) serial EEPROM that is electrically programmable. This IC stores all data related to the Analog Module

(Channels, User settings, etc.)

IC2302: SUB-CPU AND PORT EXPANSOR.

Part Number: TMP86FS49AUG-6NU2 SHARP Code: RH-IXC009WJZZQ

This IC functions as ports Expansor of the main microcontroller (e.g leds, remote control, key, Power Supply supervisor, Audio mutes, LCD controller signals, temperature sensor, lamp error, etc..).

This microcontroller integrates 60KB of Flash memory, 2KB of RAM. It’s including 56 I/O pins (13 high current) with 2 UARTS, 1 I2C serial link, 16

channels of 10 bits A/D converters, 2 timers 16 bits.

SEES Engineering Department

Training course: D44

11

Page 10

2. Block Diagrams (continued)

Main ICs

IC1301: DIGITAL AUDIO POWER AMPLIFIER

Part Number: YDA147-SZE2 SHARP Code: VHIYDA147SZ-1Y

This IC is a Stereo 20W (10W+10W) digital audio power amplifi er. The IC is class D amplifi er equipped with the function for the dynamic self-adjustment of the output volume in proportion to the amplitude of the input signal. The company calls the function of automatic adjustment of the installed

output volume “DRC (dynamic range compression)”.

The modulation method adopted PWM. An external LC fi lter is unnecessary. It only has to supply the output signal directly to the speaker. It has the

output control function to prevent an excessive input to the speaker. The maximum output electric power can be set to an arbitrary size by external

resistance. Besides this, the protection function to overheating and the overcurrent was installed.

The switching operation of power MOS-FET is installed and the technology that carefully controls the slewing rate is installed. Moreover, the automatic offset calibration circuit that suppresses the pop noise when the power supply starts is built into.

IC8103: LCD CONTROLLER

Part Number: T3Z18AFG-0003 SHARP Code: VHIT3Z18AFG-1Q

This IC is a custom Gate Array of Toshiba. The alias of this IC is EAGLE2 and is marked as SHARP. This IC is generating all the necessary timing

signals for controlling the panel and the RSDS interface for data..

IC8101: NVM 256Kb -E2PROM FOR LCD CONTROLLER (IC8103)

Part Number: M24256-BWMN6TP SHARP Code: VHIM24256B +-1L

The BR24256B is a 2-wire (I2C bus type) serial EEPROM that is electrically programmable. This IC stores all data related to the LCD Controller

(Gamma, timings, etc…).

SEES Engineering Department

Training course: D44

12

Page 11

2. Block Diagrams (continued)

Main ICs

IC203: I2C BUS SELECTOR

Part Number: SN74LV4053APWR SHARP Code: VHILV4053AT-1Y

The SN74LV4053APWR is a high-speed CMOS analog multiplexer/demultiplexer backed by silicon gate CMOS technology. The multiplexer function includes the selection and mixing of analog and digital signals. The chip includes two independent 3 channels selectors. A digital signal through

the control terminal turns on the switch of a corresponding channel. This IC is selecting if the Tuner is controlled from VCT-Pro (ATV mode) or from

OFDM decoder (DTV mode).

IC1201: NVM OF PC INPUT (EDID)

Part Number: BRC21F SHARP Code:VHIBR24C21F-1Y

This IC is a 2-wire (I2C bus type) serial EEPROM this is electrically programmable. This EEPROM chip stores the data structure used to carry

confi guration information for optimal use of a display (EDID data).

IC1501: RS-232 TRANSCEPTOR

Part Number: ISL83220 SHARP Code: VHIISL83220-1Y

This ISL83220 is a 3.0V to 5.5V powered RS-232 transceiver (emitter/receiver), +/-15kV ESD protected, with a maximum data rate of 250 kbps.

SEES Engineering Department

Training course: D44

13

Page 12

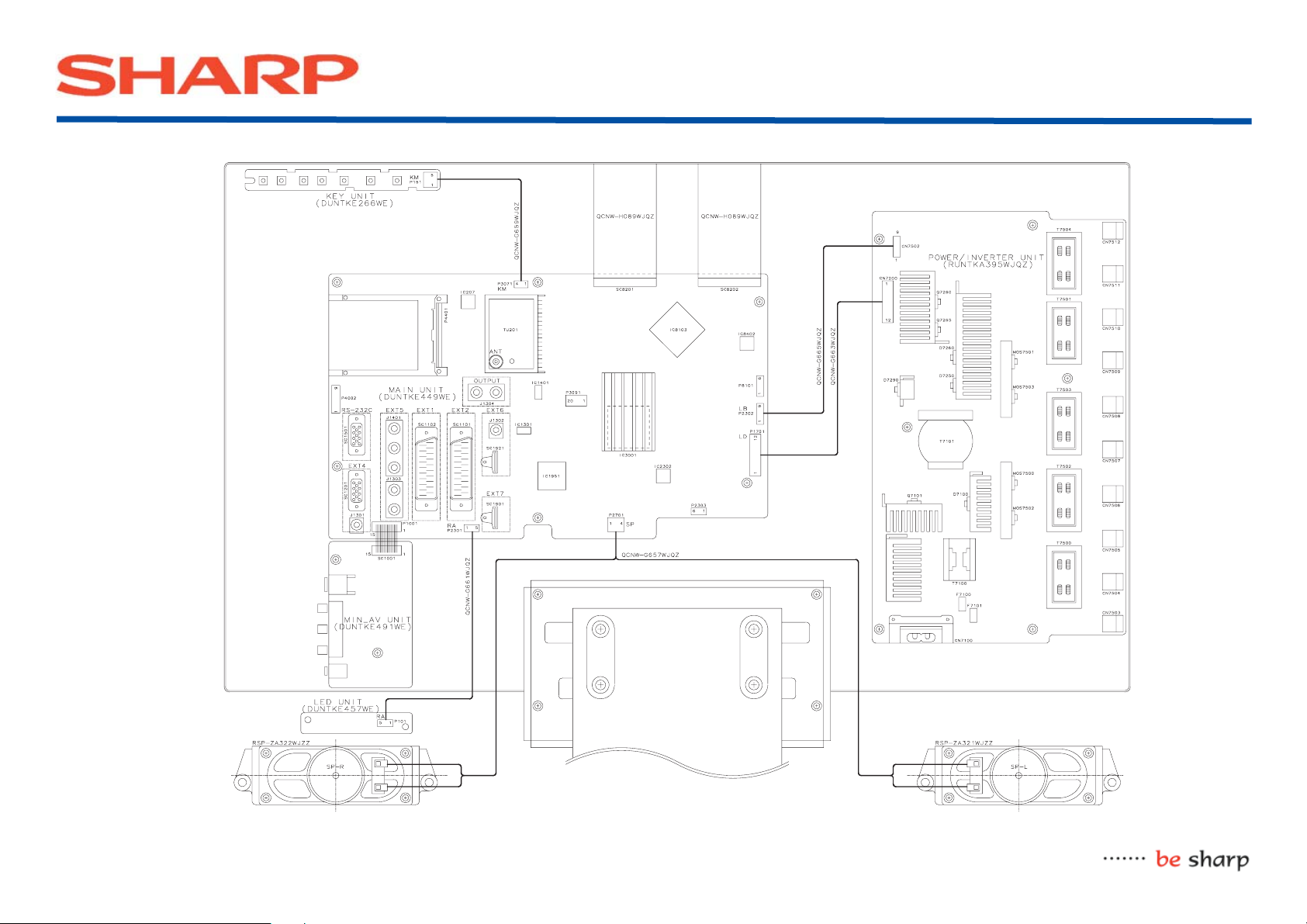

Overall Wiring Diagram 26”

2. Block Diagrams (continued)

SEES Engineering Department

Training course: D44

18

Page 13

ޓ

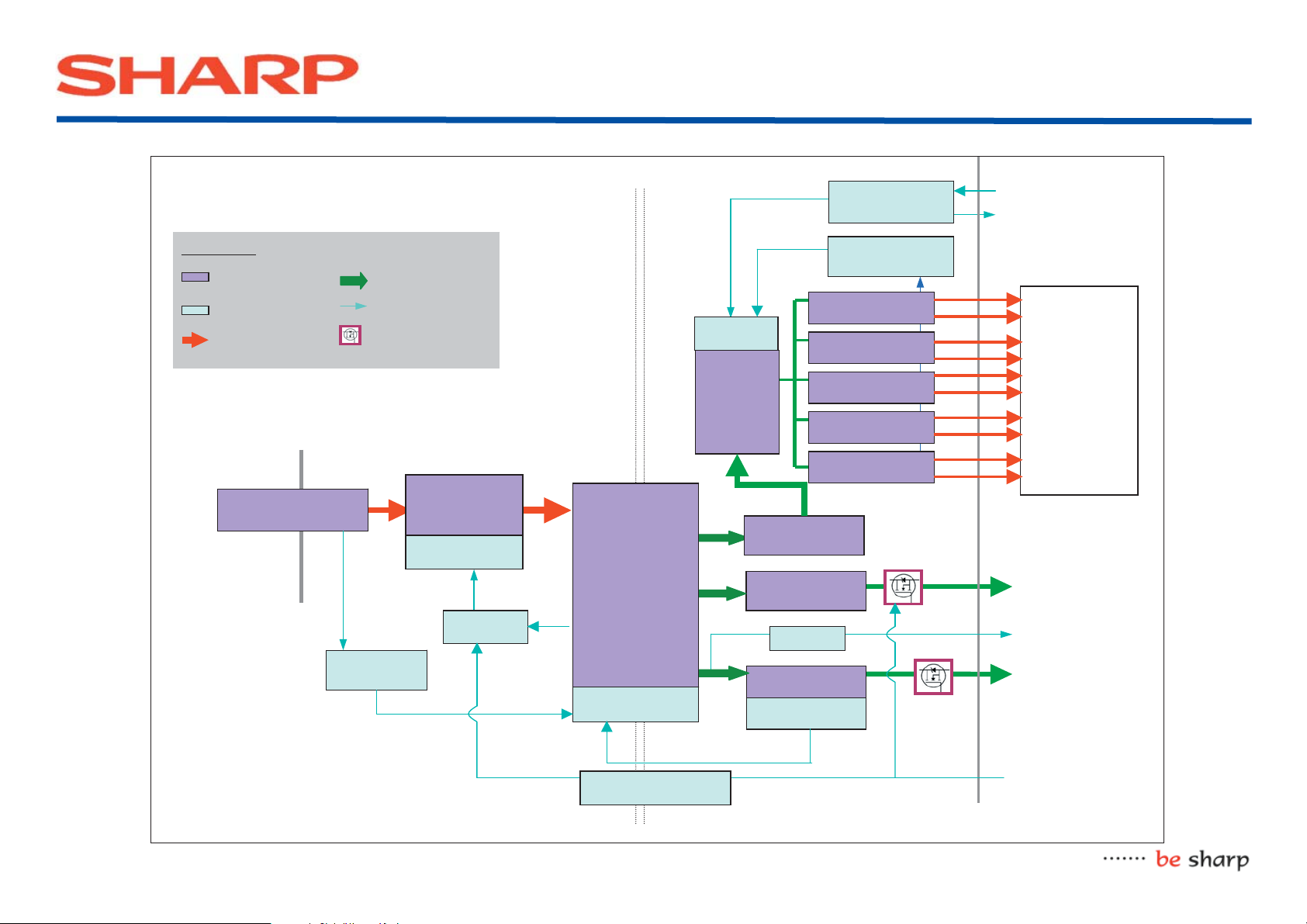

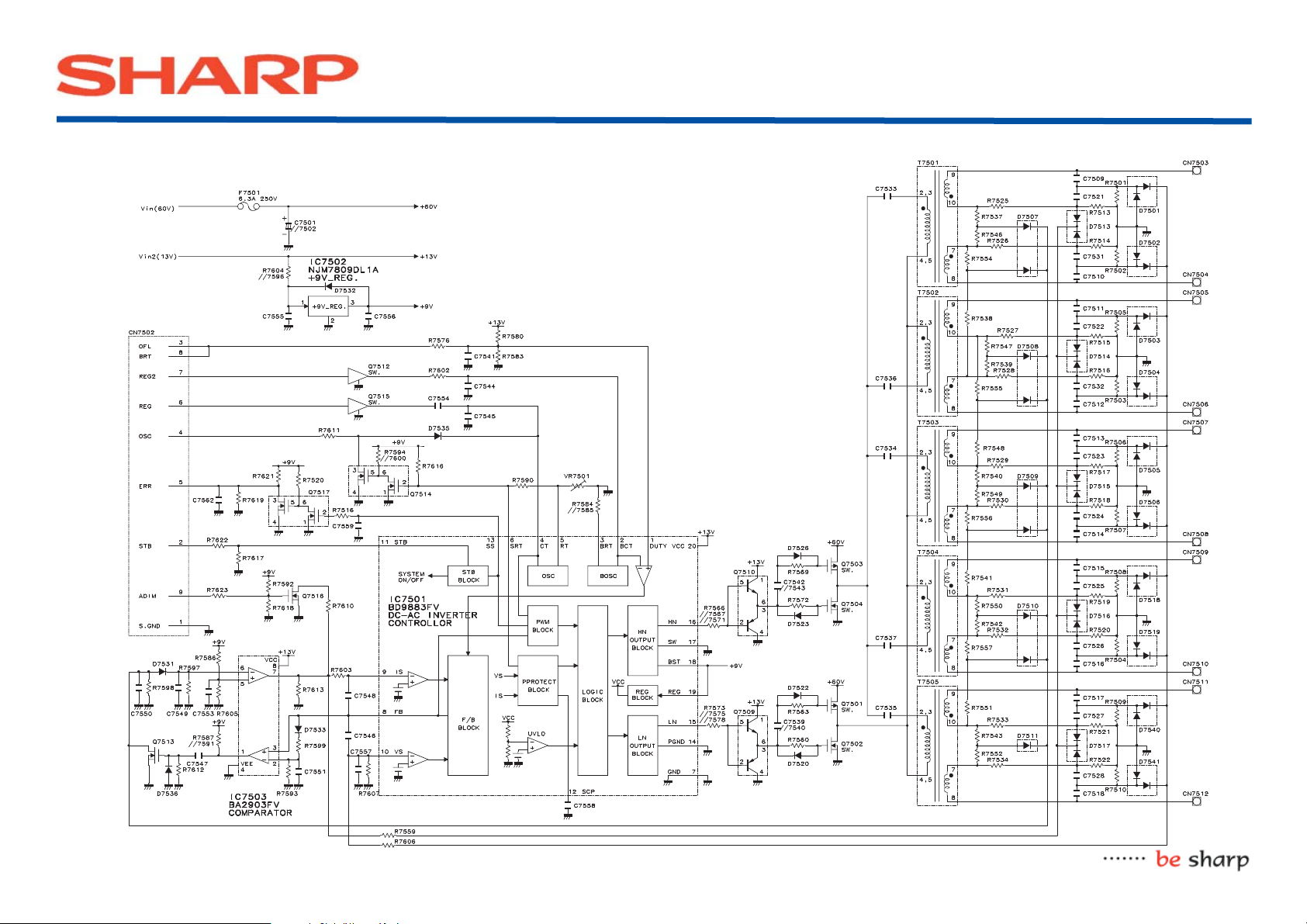

RUNTKA395WJQZ Power Supply & Inverter Block Diagram (26”)

Comments

Comments

Power Block

Signal Block

High Voltage

path

EMI Filter + Rectifier

AC Input

220~240Vac

High Current path

Signal path

ON/OFF switch

AC Brown out

PFC

BUCK CAP.

L7103 & Q7305

DCM controller

U7300

VCC

C7108

FLYBACK

T7101

Controller

U7101

Controller

IC7500

FULL

Bridge

MOS7500

MOS7502

MOS7501

MOS7503

38V O/P rectifier

13V O/P rectifier

5V O/P rectifier

5V Feedback Loop

Dimming Control,

Other I/O signal

1ψ2 Transformer

1ψ2 Transformer

1ψ2 Transformer

1ψ2 Transformer

1ψ2 Transformer

AC_DET

U7102

Feedback,

Protections

Q7265

Q7291

STB, OFL1,OSC,

REG,REG2,BRT,ADIM

ERR

Lamp Open & Shorted

+

-

+

-

+

-

+

-

+

-

CCFL

10lamps

8.5mA

1700V Typ.

33.9KHz Typ.

OFL=150Hz

20% min

38V*1.8A

S13V*2A

13V*0.5A

AC-DETECT

BU5V* 1A

SEES Engineering Department

ON/OFF Feedback Loop

U7203

Primary Secondary

Training course: D44

20

PS_ON

System Interface

Page 14

RUNTKA396WJQZ Power Supply Block Diagram (32”)

PS_ON

2. Block Diagrams (continued)

HALF

BRIDGE

Nº 1

CURRENT

SENSOR

Nº2

REG

STBY ON/UNDERV.

SEES Engineering Department

AC DET

PS_ON

60/13V OVERVOLTAGE

BU+5V REG

Training course: D44

21

13V OVERVOLT.

60V OVERVOLT.

13V SHORT DET

60/13V REG

Page 15

RUNTKA396WJQZ Inverter Block Diagram (32”)

2. Block Diagrams (continued)

SEES Engineering Department

HIGH CURRENT LAMP

LOW VOLT LAMP

LAMP OPEN

SHORT CIRCUIT PROTECTION

TIMER LATCH

C7558=GROUND PROT DISABLED

Training course: D44

22

Page 16

3. Software Updating

HOW TO UPDATE THE SOFTWARE

VCTPro SOFTWARE UPDATE

There are 4 methods to update software in the VCTpro:

• RS-232C HyperTerminal Method

• RS-232C Tera Term Method

NOTE: (RS-232C method is allowed when the TV is working properly and the action should be only software upgrade)

• I2C Method

• PCMCIA Card Method (NEW!!)

DIGITAL SOFTWARE UPDATE

There are 2 methods to update the Digital Board Software on Flash Memory (IC4203) throught the Digital Processor

(IC4001):

• PCMCIA CARD (Compact Flash Memory) Method

NOTE: The PCMCIA method is only compatible with those PCs running XP Windows Version.

• Jig RS-232 WinUpload Method (From PC through RS-232C COM port)

SEES Engineering Department

Training course: D44

23

Page 17

HOW TO ENTER TO SERVICE MODE

Press the “POWER” key on the set of running TV set to force off the power.

•

While holding down the “VOL (-)” and “INPUT” keys on the set at once, plug in the AC power cord to turn on the power.

•

The letter “K”, appears on the screen.

Next, hold down the “VOL (-)” and “P (-)” keys on the set at once. Multiple lines of character string appearing on the

•

screen indicate that the set is now in the adjustment Process mode. If you fail to enter the adjustment mode (the display

is the same as normal start-up), retry the procedure. (Another procedure)

To exit of Service Mode, after the adjustment is done, unplug the AC power cord to force off the power. (When the

•

power is turned off with the remote controller, once unplug the AC power cord and plug it in again. In this case, wait 10

seconds before plugging.)

4. Service Mode

Main Key operation in adjustment process mode

Remote controller key Main unit key Function

P (Λ / V) P (Λ / V) Moving an item (line) by one (UP/DOWN)

VOL (+/-) VOL (+/-) Changing a selected item setting (+1/-1)

Cursor (UP / DOWN) ———— Turning a page (PREVIOUS / NEXT)

Cursor (LEFT / RIGHT) ———— Changing a selected line setting (+10/-10)

SEES Engineering Department

INPUT SOURCE

on remote controller

OK ———— Executing a function

INPUT button Input source switching (toggle switching)

(TV→DTV→EXT1→EXT2→EXT3→EXT4→EXT5→EXT6

→EXT7)

Training course: D44

55

Page 18

K

K

K

K

4. Service Mode (continued)

Display Description

The colors of K letter that shown on the screen when TV is at Inspection Mode are as follows:

Red Picture adjustment: without making adjustments. (SRC or after delete NVM )

Grey Picture adjustment is doing. (SEES)

Light Blue All picture adjustments have been completed. (SEES)

Dark Blue The TV has been forced INSPECTION MODE from Panel Control keys (INPUT + VOL▼ + AC ON).

In this mode, the colors classification does not work, and the state of adjustments must be checked directly in results

line.

K

K

K

Size adjust

Model adjust

26D44

K

T: Tuner Level adjustment

1= Adjust done

0= Adjust not done

T W

1 1

W: White Balance adjustment

1= Adjust done

0= Adjust not done

SEES Engineering Department

Training course: D44

56

Page 19

j

4. Service Mode (continued)

Service Mode Menu

The character string in brackets [ ] will appear as a page title in the adjustment process menu header.

Page Line Item DescriptionRemarks (Adjustment detail, etc.)

[INFO]1/11

1

Main Version

2

DevVersion

3

DevLoader Version

4

PIC Version

5

TEMP SENSOR

6

NORMALSTANDBY CAUSE

7

ERROR STANDBY CAUSE

[INIT]2/11

1

FactoryInit

2

Inch Setting

3

PUBLIC MODE

4

Center Acutime

5

RESET

6

B

acklight Acutime

7

RESET

8

Picture Read Pos X

9

Picture Read Pos Y

10

Picture Read

[PAL. SECAM. N358]3/11

1

RF-AGC ADJ

2

PAL+TUNER ADJ

3

PAL ADJ

4

TUNER ADJ

5

CONTRAST SD

SECAM CB OFFSET

6

SECAM C

7

8

9

12COMP 15K ADJ

1 HDTV CONTRAST 32 Contrast adjustment

1

2

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

R OFFSET

TUNER A DAC

RF AGC

[COMP 15K]4/11

COMP 15K CONTRAST

[HDTV]5/11

[SMPTE]6/11

RF-AG

C ADJ

PAL+TUNER ADJ

PAL ADJ

TUNER ADJ

CONTRAST SD

SECAM CBOFFSET

SECAM CR OFFSET

TUNER A DAC

RF AGC

[M GAMMA INFO]7/11

MGAMMA IN 1

MGAMMA IN 2

MGAMMA IN 3

MGAMMA IN 4

MGAMMA IN 5

MGAMMA IN 6

MGAMM

A WRITE

MGAMMA RESET

LTX7E XX.XXXZ (YYYY/MM/DD X)

1.xxx (xx/xx/xxxx) x

x.xxx

x.x

xx.xx

xxx

[X]0

xxHxxM (X5

(--/EURO/UK/ITALY/FRANCE/RUSSIA)ENTER

(--/EURO/RUSSIA/SWEDEN) ENTER

(--/26/32/37/45)

(26/32)

OFF/ON

XxH xxM

OFF/ON

XxH xxM

OFF/ON

0

0

ON/OFF

ENTER

ENTER

ENTER

ENTER

32

1

1

32

20

ENTER

40

32

)

40

ENTER

ENTER

ENTER

ENTER

32

1

1

32

20

160

320

480

640

800

960

OFF/ON

OFF/ON

Main microprocessor version(VCTP)

DigitalModule version

DigitalModule

PIC version

Temp inside cabinet (near panel)

Last status which cause standby

Error standby cause

Total

Initialization to factory settings

Defi ned by software version

Initialization data for different panel sizes

PUBLIC MODE flag setting

Main operating hours (Not Operative)

Main operating

Backlight operating hours

Back

x-axis setting of picture data

y-axis setting of picture data

Start/stop of picture data

RF AGC auto adjustment

PALTUNER auto adjustment

PAL auto adjustment

TUNER auto adjustmen

SD contrast adjustment

SECAMcontrast adjustment

SECAMcontrast adjustment

TUNER DAC adju

RF AGC adjustment

COMP 15K auto adjustment

Contrast adjustment

RF AGC auto adjustment

PALTUNER auto adjustment

PAL auto adjustment

TUNER auto adju

SD contrast adjustment

SECAMcontrast adjustment

SECAMcontrast adjustment

TUNER

RF AGC adjustment

W/B adjustment,g

W/B adjustment,gradation 2 input setting

W/B adjustment,gradation 3 input setting

W/B adjustment,gradation 4 input setting

W/B adjustment,gradation 5 inpu

W/B adjustment,gradat

EEP writing of adjustment values

Initialization of adjustment values

loader version

operating time before error

hours reset

light operating hours reset

DAC adjustment

(VCTPro)

(STi5105)

t

stment

stment

radation 1 input setting

ion 6 input setting

t setting

[M GAMMA 1-3]8/11

1

MGAMMA R 1

2

MGAMMA G 1

3

MGAMMA B 1

4

MGAMMA R 2

5

MGAMMA G 2

6

7

8

9

10

1

2

3

Page Line Item DescriptionRemarks (Adjustment detail, etc.)

4

5

(Continued)

6

7

8

9

10

1

2

3

4

5

6

7

8

9

10

1

2

3

MMA B 2

MGA

MGAMMA R 3

MGAMMA G 3

MGAMMA B 3

MGAMMA WRITE

[M GAMMA 4-6]9/11

MGAMMA R 4

MGAMMA G 4

AMMA B 4

MG

MGAMMA R 5

[M GAMMA 4-6]9/11

MGAMMA G 5

MGAMMA B 5

MGAMMA R 6

MGAMMA G 6

MGAMMA B 6

MGAMMA WRITE

[ETC]10/11

EEP CLEAR

EEP CLEARB

STAND BY CAUSE RESET

INSTALLATION SW

AUTO

OPTION

COUNTRY

LERRRESET

LERRSTOP

LR

DTV C

I2C-OFF

[COM-BIAS]

LCD11/11

V COM ADJ

OSC FREQ 50

TEST PATTERN

OSC FREQ 60

PWM FREQ 50

0

0

0

0

0

0

0

0

0

OFF/ON

0

0

0

0

0

0

0

0

0

OFF/ON

OFF/ON

OFF/ON

OFF/ON

0/1

0

(--/EURO/RUSSIA/SWEDEN)

(--/EURO/UK/ITALY/FRANCE/RUSSIA)

0

0/1

0/1

ENTER

63 [0....127]

144

0 [0, 1....24]

144

1

W/B adjustment,gradation 1

W/B adjustment,gradation 1G adjustment value

W/B adjustment,gradation

W/B adjustment,gradation 2R adjustment value

W/B adjustment,gradation 2G adjustment value

W/B adju

stment,gradation 2B adjustment value

W/B adjustment,gradation 3R adjustment value

W/B adjustment,gradation 3G adjustment value

W/B adjustment,gradation 3B adjustment value

EEP writing of adjustment values

W/B adjustment,gradation 4R adjustment value

W/B adjustment,gradation 4G adjustment value

W/B adjustment,gradatio

W/B adjustment,

W/B adjustment,gradation 5G adjustment value

W/B adjustment,gradation 5B adjustment value

W/B adjustment,gradation 6R adjustment value

W/B adjustment,gradat

W/B adjustment,gradation 6B adjustment value

EEP writing of adjustment values

Restore NVM data to default values

Restore NVM data to default values except

adjustment data

Clearing of standby cause error list

0: unfinished 1:finish (The setting takes effect

the next time the power is turned on.)

Selected country

Lamp error

Stops Lamp Error feature

Restore DigitalModule NVM to default values

BUS STOP

0...127 COMBIAS ADJUSTMENT

TEST PATTERN 0 - OFF

1 - 24 PATTERNS

counter

1B adjustment value

n 4B adjustment value

gradation 5R adjustment value

ion 6G adjustme

R adjustment value

nt value

SEES Engineering Department

Training course: D44

57

Page 20

TUNER LEVEL ADJUSTMENT

Adjustment Point Adjustment Conditions Adjustment Point

1 Settings [Signal]

RF Signal

5. LCD Adjustment Process

Feed the PAL color bar signal (E-12CH) to TUNER. Signal level: 55 ± 1dB μV (75Ω LOAD)

[TUNER]

2 Auto adjustment

SEES Engineering Department

performance

Adjustment Process (See

Service Manual)

↑ 100% white

Bring the cursor on [TUNER ADJ] and press [OK].

[TUNER ADJ OK] appears when fi nished.

Training course: D44

58

Page 21

5. LCD Adjustment Process (continued)

W/B ADJUSTMENT FROM PC

1- Get ready the PC with COM port (RS-232C) running on Windows 95/98/

ME/2000/XP operating system, as well as the RS-232C cross cable.

2- Start the unit with the RS-232C cable connected.

3- Start the terminal software. (The freeware readily available on the Internet

will do.)

4- Make the following settings:

Baud rate 9.600 bps

Data LENGTH 8 bit

Parity bit None

Stop bit 1 bit

Flow control None

5- If the settings are correct, the terminal software indicates “ERR” against

pressing of the “ENTER” key.

6- After the setting are done correctly, it is possible to make an adjustment by

typing in the command shown in the table below and pressing the “ENTER” key

on the keyboard.

7- Command entry is successful if the terminal software indicates “OK” when

the “ENTER” is pressed. If “ERR” is shown, retry to enter the command.

8- Send the process mode switching command to switch from the RS232C operation mode to the process mode:

KRSW0001: “ERR” is returned.

KKT10037 : When “OK” is returned, the process mode becomes

active. When “ERR”, start over from KRSW0001.

9- Send each adjustment command.

SEES Engineering Department

Training course: D44

59

Lista de comandos RS-232C

Command Function Remarks

KYOF0000 Remote control disabled

OSDS0001 OSD display inhibited

SBSL0016 Light control level MAX

MSET0001 Background adjustment start

MSET0004 Initialization of adjustment value

LEV60928 Graduation 6 (928-graduation adjustment)

MG6G **** Adjustment of G of graduation 6 0000 ~ 4095

MG6R **** Adjustment of R of graduation 6 0000 ~ 4095

MG6B **** Adjustment of B of graduation 6 0000 ~ 4095

LEV50800 Graduation 5 (800-graduation adjustment)

MG5G **** Adjustment of G of graduation 5 Calculated value

MG5R **** Adjustment of R of graduation 5 0000 ~ 4095

MG5B **** Adjustment of B of graduation 5 0000 ~ 4095

LEV40656 Graduation 4 (656-graduation adjustment)

MG4G **** Adjustment of G of graduation 4 Calculated value

MG4R **** Adjustment of R of graduation 4 0000 ~ 4095

MG4B **** Adjustment of B of graduation 4 0000 ~ 4095

LEV30528 Graduation 3 (528-graduation adjustment)

MG3G **** Adjustment of G of graduation 3 Calculated value

MG3R **** Adjustment of R of graduation 3 0000 ~ 4095

MG3B **** Adjustment of B of graduation 3 0000 ~ 4095

LEV20352 Graduation 2 (352-graduation adjustment)

MG2G **** Adjustment of G of graduation 2 Calculated value

MG2R **** Adjustment of R of graduation 2 0000 ~ 4095

MG2B **** Adjustment of B of graduation 2 0000 ~ 4095

LEV10184 Graduation 1 (176-graduation adjustment)

MG1G **** Adjustment of G of graduation 1 Calculated value

MG1R **** Adjustment of R of graduation 1 0000 ~ 4095

MG1B **** Adjustment of B of graduation 1 0000 ~ 4095

MSET0003 Writing of adjustment value

NOTE: To ensure that TVs are not red, have changed the W/B

coordinates adjustment:

x: 270 y: 286

Page 22

HOTEL MODE

How to Enter in the Public Mode (Hotel Mode)

5. LCD Adjustment Process (continued)

There are three following ways to display the Public Mode setting screen.

1- On the process adjustment mode screen (2/33), set the “HOTEL MODE” Flag to ON.

Turn off the power, and turn it on again, pressing the CH▲ and Vol▲ keys of the main

unit at the same time.

2- Enter the Pass Word, and start the unit.

a) Turn on the power, pressing the INPUT and Vol▲ keys of the main unit at the

same time.

b) Display the Pass Word input screen.

c) Check the Pass Word by inputting three digits. If the Pass Word is , it

shifts to the Public Mode setting screen. In another case, the screen is erased, and it

operates in the ordinary mode.

3- By special R/C code: RC table LCD, SYS CORD: 0x78, RC DATA: (HEX) 0xC7,

(DEC) 199.

After one of sequence before mentioned, the TV will turn on showing the Public Mode

setting screen.

Public Mode

POWER ON FIXED [VARIABLE]

MAXIMUM VOLUME [60]

VOLUME FIXED [VARIABLE]

VOLUME FIXED LEVEL [0]

RC BUTTON [RESPOND]

PANEL BUTTON [RESPOND]

MENU BUTTON [RESPOND]

ON SCREEN DISPLAY [YES]

INPUT MODE START [NORMAL]

INPUT MODE FIXED [VARIABLE]

RESET

EXECUTE

Exiting the Public Mode screen

There are two following ways to exit the Public Mode setting screen.

1- Turn off the power.

2- Select “Execute” in the Public Mode to execute it.

SEES Engineering Department

Training course: D44

60

Page 23

5. LCD Adjustment Process (continued)

Public Mode Settings

1. POWER ON FIXED [VARIABLE FIXED]

When it is set to “FIXED” the TV is impossible to be switch off by Main Switch or Remote Control.

2. MAXIMUM VOLUME [0 60]

Is possible to set the maximum volume at limited level.

3. VOLUME FIXED [VARIABLE FIXED]

Is possible to fi x the sound volume at limited level.

When “FIXED” is selected the sound volume before limited is fi xed.

4.VOLUME FIXED LEVEL [0 60]

If “FIXED” has been selected, is possible to set a fi xed volume at the level that is choosen.

5. RC BUTTON [RESPOND NO RESPOND]

If “NO RESPOND” is selected, the remote control keys are inoperative.

6. PANEL BUTTON [RESPOND NO RESPOND]

If “NO RESPOND” has been selected, the set´s keys remain deactivated (Except POWER key).

7. MENU BUTTON [RESPOND NO RESPOND]

If “NO RESPOND” has been selected, “MENU” keys on the remote control, is inoperative.

8. ON SCREEN DISPLAY [YES NO]

If “NO” has been selected, the On Screen Display does not appear.

9. INPUT MODE START [ NORMALTV (X)DTVINPUT1 INPUT2INPUT3 INPUT4 INPUT5 INPUT6 INPUT7]

When any other item than “NORMAL” has been selected, the sets will start in a selected input mode at the next power-on.

10. INPUT MODE FIXED [VARIABLE FIXED]

If “FIXED” has been selected, any channels and input modes other than those selected at the start mode cannot be picked up.

11. RESET

Cancel all Public Mode settings. (It returns to the factory settings)

12. EXECUTE

Select this item, and press cursor RIGHT/LEFT keys on the remote control or VOL(+)/(-) keys on the LCD TV for confi rmation the functions settings.

SEES Engineering Department

Training course: D44

61

Page 24

()

Main 1/13 (TUNER.OFDM) Schematic Diagram

TL202

DC-POW2RF-AGC3MB(IF5V)

SIF5AFT

1

4

TL201

TL204

TL211

TL220

C201

33u

10V

ASX

TUNER ATV/DTV

B+ANT5V

Q202

RN4904

DUNTKE449WE01

R204

0

VIDEO-OUT7AS8SCL

TL219

R206

22

TU201

AA019WJQZ

SDA

6

9

TL205

TL207

TL206

2

4

1

3

FB201

0210TA

(0)

(0.02)

(0.02)

5.18

5.12

5.12

123

456

00

(3.3)0(5.09)

R209

1K

DTI2CSEL

AGC

10

TL231

!*

MB(5V)12NC13NC

11

TL203

C209

0.01u

25V

IF-AGC

GND

14

15

TL208

TL217

C207

470u

16V

ASX

C210

0.01u

25V

TL222

VIN5Vo

IC202

PQ1M335M

GND3Vc

1Nr2

C214

0.01u

25V

TL212

L263

12uH

IF(D2)17IF(D1)

16

TL209

TL210

C271

100u

16V

ASX

C216

0.1u

R211

3.9K

CNN

C269

0.1u

Z

25V

C213

0.01u K

R214

330

R213

10K

4.8

Q203

2SC3928AR

2.3

R212

1.6

150

ATV/DTV TUNER SELECTOR

SDA3

(3.3)

(0)

(0)

(0)

C219

0.1u

25V

4

C218

10u

KZA510WJPZ

5.16

Z

VDD

IC203

11Y20Y31Z4ZC50Z6

0

(3.3) (0)

C220

0.1u

Z

25V

16V

B+5V

SCL3

3.3

3.3

3.3 0 0

C221

10u

16V

KZA510WJPZ

C223

10u

16V

KZA510WJPZ

LV4053FT

R218

150

TL223

Vo

IC204

BH25FB1G

Vin2GND3Vc

1

C222

0.1u

25V

TL224

VOUT

IC205

MM3271AN

VDD2GND3CE

1

IFAGC

3.30

INH7VEE8G

00

Z

4NC5

C224

0.1u

25V

C225

0.01u

4Nr5

(0)

C226

0.1u Z

25V

Z

D

1D2D3

C215

10u

16V

KZA510WJPZ

K

(0)

5.18

5.18

4S5D6

G

5.18

5.18 0

(0)

(0)

(5.1)

IC261

SSM6J51TU

C256

0.1u

(5.09)0(5.09)0(5.09)(0)

0

9C10B11A120X131X14XC15Y116

00

R222

4.7K

2134

SDA3

(0)5.18

C217

0.1u

3

1

R223

22

(0)

(0)

5.18

5.18(0) 5.12

123

456

5.12

0

(5.1)0

(0)

(0)

R283

3.3K

3.3V

4

2

RN4904

C232

10u

16V

KZA510WJPZ

KZA510WJPZ

6. Electrical Diagrams

SIF

VIN1

Q262

DTV_CVBS

10P

R1031

F

330

C1031

47P

(CH)

FB1031

A188WJ

R1033

C1032

(CH)

L1031

10uH

D9Mj

C1033

47P

(CH)

10K

C1034

R1032

10u

330

F

R1034

16V

10K

ASX

VIDEO SELECTOR CVBS EXT3/

SVIDEO EXT3/CVBS DTV

HEADPHONES

AMPLIFIER

(1.76)0(0.4)0(0.9)

0

63

64

SCANMODE

L207

2.2uH

CNN

C238

10u

16V

KZA510WJPZ

L206

2.2uH

CNN

C240

10u

16V

KZA510WJPZ

C228

0.1u Z

25V

C236

C229

0.1u Z

0.1u Z

25V

25V

C230

1000P

C231

1000P

L204

C233

2.2uH

0.1u Z

CNN

25V

C227

10u

16V

KZA510WJPZ

L203

2.2uH

CNN

C235

0.1u Z

25V

TSCL

TSDA

L205

2.2uH

C237

CNN

0.1u Z

C234

25V

10u 16V

C248

C242

1000P

0.1u Z

25V

C249

C245

1000P

0.1u Z

25V

C243

0.1u Z

25V

R226

560

C246

R227

0.1u Z

560

25V

C239

1000P

C250

10P

(CH)

X201

SCA039WJ

C251

10P

(CH)

C241

1000P

C247

0.1u Z

25V

C244

1000P

0

1 RF_LEVEL

(1.77)

0

2 VDDA2V5

(1.75)

0

3OP

0

4OM

0

5 VDDA2V5_ISO

(0.83)

0

6 VDDA2V5

0

7REFF

(3.36)

0

8REFM

(1.7)

0

9 INCM

(1.7)

0

10 IM

0

11 IP

(3.29)

0

12 VDDA1V

(1.74)

0

13 VDDA2V5

(0.8)

0

14 XTAL0

0

15 XTAL1

0

16 VDDA2V5

C252

AGCBB18AGCRF19VDD1V20SCLT21SDAT22VDD0V0

1000P

17

00

R228

10K

R229

180

C253

0.1u

25V

VDD3V3

OFDM DECODER

(3.3)0(3.3)0(3.3)0(3.3)0(3.35)0(0.1)

C254

0.1u

Z

25V

Z

S+8V

2.5

2SC3928AR

000

AUX_CLK

23

C1035

10u

16V

KZA510WJPZ

5.18

R1035

F

33

1.79

R1036

Q1031

160 F

(1.74)0(1.7)

IC207

IXB964WJ

VDD1V25CS026CS127D RCLK

24

00

(1.5)0(1.5)0(1.5)0(0.74)0(1.5)

R230

10K

R1010

3.9K

R1006

6.8K

C1018

10u

16V

KZA510WJPZ

IC1001

NJM2234V

KZA510WJPZ

Q1001

IMH23T110

123

456

R1013

56

1/4W

00000

VDD3V3

28

R232

R231

10K

10K

R233

22

C1005

C1007

0.01u

0.1u

Z

25V

25V

IN12SW13IN24SW2

1

C1008

10u

16V

R1011

100

C1012

47u

C1009

16V

22u

R1012

ASY

35V

56

ASX

1/4W

2

1

4

3

R1014

1.8K

C1010

22u

35V

ASX

R234

10K

SDA30SCL31VDD1V32RESET

29

00

3

1

C255

0.01u

K

4

2

FE_SDA

FE_SCL

5

IN36Vcc7OUT8GND

C1011

10u

16V

KZA510WJPZ

R1015

82 1/2W

R1018

C1014

(CH)

IC1002

NJM4558M

1234

4.2 4.2 4.0 0

C1015

C1013

47P

(CH)

R1016

10K

TL215TL213

(1.6)0(1.2)0(3.3)0(3.35)

0

49

GPIO150VDD3V351VDD1V52GPIO853GPIO754GPIO655VDD1V56VDD3V357GPIO558GPIO459GPIO360GPIO261GPIO062VDD1V

(1.6)

48ERROR

(1.6)

47D8

46STR_OUT

(3.3)

45VDD1V

(3.35)

44CLK_OUT

(3.3)

43D7

(3.3)

42D6

41VDD3V3

40D5

(1.74)

39D4

(0.7)

38VDD1V

37D3

(1.7)

36D2

(3.35)

35D1

(1.5)

34VDD3V3

(1.5)

33D0

0

(1.5)

(1.5)

TL214

FERESET

10K

47P

33P

(CH)

R1019

1.2K

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

C1017

0.1u

CYB

(SW1.SW2)=

00: 1 CVBS

10: 2 S-VIDEO

*1: 3 DTV CVBS

R1017

100

R1020

1.2K

C1016

33P

(CH)

4.04.24.28.0

5678

TL216

R236

47

R237

47

R238

47

P1001

MA012WJ

TL1001

S_PLG

15

TL1002

S_Y

14

TL1003

VIN7

VIN8

HP_PLG

EXT_DTV

SV1JSW

R1022

10K

3

4

1

2

HPOUTR

2

1

3

C1019

22u

16V

ASX

FEVALID

R239

47

8

6

4

2

R240

47

8

6

4

2

2

1

4

4

3

R1021

R1023

10K

10K

HPOUTL

HP_MUTE

DTV_CVBS

FERESET

FE_SCL

FE_SDA

FESTROUT

7

5

3

1

7

5

3

1

HPOUTL

HPOUTR

HP_PLG

VIN7

VIN8

TL1004

C1006

0.1u

TL1005

CYB

TL1006

TL1007

TL1008

TL1012

TL1009

TL1010

TL1011

SIF

VIN1

SDA3

SCL3

IFAGCI

HP_MUTE

EXT_DTV

SV1JSW

DTI2CSEL

GND

13

S_C

12

GND

11

CVBS

10

GND

9

IN3L

8

GND

7

IN3R

6

HP_PLG

5

GND

4

HP_L

3

GND

2

HP_R

1

VD

TO MAIN2(TERMINAL)

IN3R

IN3L

TO MAIN4(DTV STI5105)

DTV_CVBS

FEERROR

FERESET

FE_SCL

FE_SDA

TO MAIN6(DTV CI)

FEVALID

FESTROUT

FECLK

FED7

FED6

FED5

FED4

FED3

FED2

FED1

FED0

TO MAIN7(VCT-PRO)

HPOUTL

HPOUTR

HP_PLG

VIN7

VIN8

SIF

VIN1

SDA3

SCL3

IFAGCI

TO MAIN8(UCON/PANEL_IF)

HP_MUTE

EXT_DTV

SV1JSW

TL232

DTI2CSEL

TO MAIN10(POWER SUPPLY)

B+5V

B+ANT5V

S+8V

TO MiniAV

SEES Engineering Department

Training course: D44

62

Page 25

Main 2/13 (TERMINAL) Schematic Diagram

TO MAIN1(TUNER,OFDM)

PC_IN (BLACK)

SC1201

NA770WJ

TL1201

TL1202

TL1203

FL1201

N0003TA

EXT2 CVBS OUTPUT DRIVER

FL1202

N0003TA

SLOWSW_2I

VIN18

VIN_2

CVO2

VIN15

VIN16

VIN17

SLOWSW_1I

VIN3

VIN_1

VIN6

VIN5

VIN9

FL1203

N0003TA

R1201

75

1/4W

C1101

10u

16V

KZA510WJPZ

IN3L

IN3R

FB1201

A188WJ

IN3L

IN3R

TL1204

16

TL1205

6

TL1206

1

11

TL1208

7

2

12

8

3

13

9

TL1209

4

14

TL1207

10

5

15

17

C1201

0.1u

K

C1202

0.1u

K

C1203

0.1u

K

R1203

75

R1202

1/4W

75

1/4W

D1104

EXA520WJ

5.1V

IC1101

MM1506XN

C1102

0.1u

4

IN2

25V

Z

5

GND

6

IN1

D1101

C1103

EXA512WJ

0.1u

4V

16V

CYB

D1102

C1104

EXA512WJ

0.1u

4V

16V

CYB

D1103

C1105

EXA512WJ

0.1u

4V

16V

CYB

R1102

39K

R1101

15K F

D1105

EXA512WJ

4V

D1106

EXA512WJ

4V

D1107

EXA512WJ

4V

DUNTKE449WE01

FB1202

0061TA

R1204

220

FB1203

0061TA

D1203

D1204

EXA523WJ

EXA523WJ

5.6V

5.6V

FB1204

0061TA

FB1205

0061TA

D1205

D1207

EXA523WJ

5.6V

EXA523WJ

12

3

D1201

1SS226

R1103

15K F

VCC

OUT

SW

F

FB1101

0077TA

D1112

EXA512WJ

4V

D1109

EXA520WJ

5.1V

5.6V

12

12

3

3

D1206

D1202

1SS226

1SS226

PC_H

VIN19_PCR

VIN20_PCG

VIN21_PCB

R1111

39K F

FB1103

0077TA

C1120

C1109

100P

(CH)

B+5V

C1114

0.01u

3

2

1

R1104

0

R1105

0

R1106

0

D1110

EXA554WJ

15V

C1110

100P

(CH)

C1111

0.1u

16V

CYB

C1112

0.1u

16V

CYB

C1113

0.1u

16V

CYB

KZA510WJPZ

K

D1113

EXA520WJ

5.1V

C1115

10u

16V

KZA510WJPZ

R1117

10u

75

16V

1/4W

C1121

220u 16V

ASY

R1113

68

1/4W

OUTV

C1122

220u

16V

ASY

FL1101

N0017TA

RED/C2

R1107

75

1/4W

FL1102

N0017TA

GREEN2

R1110

75

1/4W

FL1103

N0017TA

BLUE2

R1112

75

1/4W

FB1102

0077TA

R1121

0

IN1FSW

R1109

C1161

100

100P

1/4W

(CH)

R1118

75

1/4W

R1108

68

1/4W

R1115

0

R1116

0

R1114

0

R1206

47K

2

3

1

R1207

47K

D1208

KDS184

R1205

220

EDID NVM PC

PLUG&PLAY

PC_V

R1125

D1114

100

R1126

EXA512WJ

1/4W

75

4V

1/4W

FL1107

N0017TA

FL1104

N0017TA

TL1101

TL1113

TL1111

TL1102

21

TL1104

TL1109

TL1105

SLOWSW1 IN1_L

TL1107

TL1103

20

TL1106

19

21

R1122

75

1/4W

TL1112

TL1108

TL1110

FL1105

N0017TA

FL1106

N0017TA

OUTTNV

RED/C1

R1124

R1123

75

75

1/4W

1/4W

1/4W

D1209

R1210

EXA523WJ

5.6V

C1204

0.1u

CZF

TL1210

0

4.4

7

8

VCLK

VCC

1234

0000

IC1201

BR24C21F

FB1104

0077TA

AVLINK

D1116

EXA550WJ

13V

IN2_L

R1130

220

R1129

0

TL1128TL1129

TL1125

123456789

TL1126

TL1123

123456789

TL1130

TL1127

TL1122

TL1124

FL1110

N0017TA

OUTTNR

OUTTNL

FB1106

0077TA

FB1105

0077TA

D1117

EXA520WJ

5.1V

1K

6

SCL

FB1107

0077TA

FB1108

0077TA

IN2_R

OUT2R

OOUT2L

IN1_R

SC1102

ZA161WJ

C1130

0.01u

TL1211

1

2

3

4

5

6

7

8

R1208

100

R1209

1K

D1115

EXA554WJ

15V

C1127

220P

C1162

100P

(CH)

IN2FSW

SLOWSW2

R1128

0

TL1116

TL1120

TL1118

TL1114

14151617181920

101112

13

TL1119

TL1121

1415161718

101112

13

TL1115

TL1117

FL1108

FL1109

N0017TA

N0017TA

GREEN1

BLUE1

R1127

75

C1128

220u

16V

ASY

C1129

220u

16V

ASY

6. Electrical Diagrams (continued)

COMP AUDIO_IN

J1303

FA061WJ

PC AUDIO_IN

TL1303

FB1301

0077TA

J1301

J0008GE

HDMI AUDIO_IN

4.24.4

5

SDA

J1302

J0008GE

GND

R1137

1K

C1133

C1137

100P

1000P

(CH)

R1138

1K

C1134

C1138

100P

1000P

(CH)

R1139

220

TL1131

1/10W

FB1109

C1135

0077TA

330P

C1136

330P

FB1110

0077TA

R1136

220

1/10W

SC1101

ZA161WJ

INPUT2

TL1133

TL1132

INPUT1

FB1111

0077TA

FB1112

0077TA

R1133

0

R1131

C1139

220

1/10W

470P

C1131

R1134

100K

330P

R1132

220

1/10W

C1140

C1132

R1135

470P

330P

100K

IC1102

MM1506XN

IN1

SW

6

1

2

GND

OUT

5

K

3

IN2

VCC

4

FB1303

TL1305

0077TA

2

3

1

TL1301

C1303

C1301

220P

220P

TL1304

FB1302

0077TA

FB1304

TL1306

0077TA

2

3

1

TL1302

C1304

C1302

220P

220P

C1147

1u

10V

TVB

R1142

100K

C1146

1u

R1143

10V

100K

TVB

C1153

C1144

10u

470P

16V

R1147

KZA510WJPZ

100

3

4

1

2

C1154

10u

16V

KZA510WJPZ

C1145

470P

R1155

560K

Q1102

IMH23T110

R1145

1K

C1141

C1148

R1148

100P

1000P

100K

(CH)

R1146

1K

C1142

C1149

R1149

100P

1000P

100K

(CH)

C1151

10u

16V

KZA510WJPZ

3

4

1

2

C1152

R1144

10u

100

16V

KZA510WJPZ

R1154

560K

Q1101

IMH23T110

C1150

10u

16V

KZA510WJPZ

EXT1 CVBS OUT-

C1143

1u

10V

PUT DRIVER

R1301

R1307

1K

R1302

1K

R1305

100K

C1305

1000P

CH

R1303

R1308

1K

R1304

1K

R1306

100K

C1306

1000P

CH

D1121

EXA535WJ

8.2V

C1159

10u

16V

KZA510WJPZ

3

1

C1160

R1153

10u

330

16V

KZA510WJPZ

D1120

EXA535WJ

8.2V

123

R1151

560K

C1155

1u

10V

TVB

C1156

1u

10V

TVB

D1118

EXA535WJ

8.2V

C1157

10u

16V

KZA510WJPZ

1

3

C1158

R1152

10u

330

16V

KZA510WJPZ

D1119

EXA535WJ

8.2V

123

R1150

560K

C1307

1000P

CH

R1309

C1309

1K

1u

CH

100K

R1310

TVB

1K

C1310

1u

CH

TVB

C1308

1000P

R1311

C1311

1K

1u

100K

CH

R1312

TVB

CH

1K

C1312

1u

CH

TVB

Q1107

2SA1530AR

4.4

3.8

AOUT2R

0

3

4

4

1

2

2

R1157

2.7K

4.4

3.8

AOUT2L

0

Q1108

456

2SA1530AR

S2_MUTE

Q1105

2SA1530AR

4.4

3.8

AOUT1R

0

2

2

1

4

4

3

R1156

2.7K

4.4

3.8

AOUT1L

0

Q1106

2SA1530AR

456

S_MUTE

CVO1

B+3.3V

TL1307

PC_AL

FB1305

0077TA

PC_AR

C1314

56P

(CH)

C1313

HDMI_AL

1000P

HDMI_AR

R1313

R1315

100K

1K

C1315

1u

10V

TVB

COMP_AR

COMP_AL

AIN2L

AIN2R

C1325

10u

16V

ASX

C1326

0.1u

25V

IC1301

NJM2750M

STEREO

AUDIO

AIN3L

SELECTOR

(CNT2,CNT1)=

00: EXT3

01: HDMI

10: COMP

11: PC

AIN3R

11

5

9

4

TL1502

8

3

TL1503

7

2

TL1504

6

1

10

TL1501

RS232C

SC1501

NA769WJ

MONI AUDIO_OUT

1234

TL1309

TL1308

TL1310

FB1306

0077TA

C1317

56P

R1319

R1314

(CH)

100K

1K

R1320

220

R1316

C1328

1K

100P

(CH)

C1319

10u

16V

KZA510WJPZ

C1318

1000P

R1318

100K

R1317

1K

C1316

1u

10V

TVB

Q1301

3.9

2SA1530AR Q1302

FB1309

AIN4L

A188WJ

C1330

C1327

1u

CH

10u

TVB

16V

KZA510WJPZ

Z

1K

R1331

12

13

14

15

VCC

OUT_A16GND

Vref

IN3A

CNT2

IN1A

IN2A

IN4A6IN1B7IN2B

CNT1

1

2

3

4

5

4.4 0 4.4 0

C1333

C1332

1u

16V

TVB

IN3L

TL1507

TL1506

TL1508

TL1509

TL1505

1u

16V

TVB

HDMI_AL

PC_AL

FB1501

0061TA

FB1502

0061TA

12

3

D1501

MA3120WA

100P

(CH)

C1320

10u

16V

KZA510WJPZ

R1321

560

R1322

1K

R1332

OUT_B

C1321

AIN4R

1K

IN3R

TL1311

R1324

220

R1323

100K

C1322

10u

16V

KZA510WJPZ

0

C1331

1u

CH

TVB

4.44.48.94.40

0

R1502

100

1/10W

R1503

100

1/10W

12

3

D1503

MA3120WA

J1304

FA061WJ

1234

TL1312

C1324

100P

(CH)

C1329

100P

(CH)

C1323

10u

16V

KZA510WJPZ

R1325

560

R1327

1K

4.5

4.5

3.9

0

9

10NC11

IN3B

IN4B

8

4.4

HDMI_AR

PC_AR

COMP_AR

C1501

10u

16V

KZA510WJPZ

R1329

1K

Q1303

IMH23T110

R1326

560K

456

123

R1328

560K

R1330

1K

2SA1530AR

C1401

10u 16V

KZA510WJPZ

R1401

22

EXT_DTV

EXT_DTV

HDMI_PC

COMP_AL

C1502

0.1u

R1504

25V

10K

IC1501

ISL83220

10NC11

12NC13

14

15

16

T1_in

T1_out

GND

Vcc

SHDN

C1+

C1-5C2+6C2-7V-8R1_in

1EN2

3V+4

C1505

C1503

0.1u

25V

RS232

C1506

C1504

0.1u

0.1u

0.1u

25V

25V

TRANSCEIVER

COMP_IN

J1401

GA131WJ

1234567

TL1405

TL1404

TL1403

TL1401

TL1402

R1406

R1407

R1408

0

0

0

R1403

R1402

75

1/4W

C1404

1u

10V

DTV_R

IN_Pr

TVB

C1405

C1409

1u

10V

1u

10V

TVB

TVB

10

11

12

SCL

MUXSEL

IC1401

SM5309AV

SDA13VDD14GND15OUT316VCC17OUT218GND19OUT120VCC21REF222REF123ADS

C1402

0.1u

25V

CZF

C1406

FB1402

0.1u

A188WJ

2

1

25V

25V

4

FB1401

A188WJ

3

9

R1_out

RS_RXD

RS_TXD

75

1/4W

C1408

10V

1u

DTV_B

IN_Pb

TVB

R1405

1.8K

MUXSEL=

L: A COMPONENT

H: B DTV_RGB

CZF

KZA510WJPZ

C1507

0.1u

K

2-IN,1-OUT,SWITCH

16V

CYB

0

1

1.4

2

4.8 1.5

3

C1508

0.1u

R1505

100

CZF

25V

R1506

10K

BU+5V

F

10u 16V

SW(L=IN1,H=IN2)

IC1502

MM1507XN

SW

OUT

VCC

AVLINK

R1404

75

1/4W

C1414

1u

10V

TVB

C1411

D

G

10u

KZA510WJPZ

IN1

GND

IN2

R1507

PC_H

PC_V

R1410

R1411

R1409

160 F

160 F

160 F

C1412

RS_TXD

1u

DTV_G

10V

IN_Y

TVB

RS_RXD

IN1A1IN1B2GND3ISET4NC5IN2A6IB2B7VCC8IN3A9IN3B

VIDEO SELECTOR

TO MAIN3(HDMI)

PC_H

PC_V

TO MAIN4(DTV STI5105)

DTV_R

DTV_B

DTV_G

RS_TXD

RS_RXD

COMP/DTV RGB

24

C1415

0.1u

16V

CYB

C1416

0.1u

16V

CYB

C1417

VIN19_PCR

0.1u

16V

CYB

C1413

16V

6

5

4

SM3K7002F

S

22K

VIN20_PCG

VIN21_PCB

1.4

VIN_1

VIN_2

0

Q1501

R1508

100

TO MAIN7(VCT-PRO)

VIN11

VIN12

VIN13

VIN19_PCR

VIN20_PCG

VIN21_PCB

SDA3

SCL3

AIN2L

AIN2R

AIN3L

AIN3R

AIN4L

AIN4R

AOUT1L

AOUT1R

AOUT2L

AOUT2R

SLOWSW_1I

SLOWSW_2I

CVO1

CVO2

VIN2

VIN3

VIN5

VIN6

VIN9

VIN15

VIN16

VIN17

VIN18

AVLINK_1

AVLINK_2

TO MAIN8(UCON/PANEL_IF)

SCART12

S_MUTE

S2_MUTE

IR_RS

HDMI_PC

EXT_DTV

TO MAIN10(POWER SUPPLY)

BU+3.3V

B+3.3V

BU+5V

B+5V

S+8V

SEES Engineering Department

Training course: D44

63

Page 26

Main 3/13 (HDMI) Schematic Diagram

6. Electrical Diagramas (continued)

TL1905

R1901

0

TO MAIN2(TERMINAL)

DUNTKE449WE01

20

1234567

22

20

1234567

22

RR0X1-

RR0X2-

RR0X2+

PC_H

PC_V

D1905

B+5V

TL1907

SC1901

ZA171WJ

101112131415161718

8

9

SC1921

ZA171WJ

8

9

RR0X0-

19

TL1906

0

Q1901

RDTC144EE

TL1912

101112131415161718

19

TL1910

TL1909

RR0XC-

0

Q1921

RDTC144EE

FB1941

A192WJ

C1941

Z

0.1u

25V

/1G2B31C341C251C161C071Y8GND

1

00000000

KDS184

2

TL1908

1

21

23

TL1901

TL1902

TL1919

R1903

1K

R1905

D1904

10K

KDS4148

R1904

10K

2.4

2.4

0

Q1902

0

0

RDTC144EE

2

1

21

23

R1923

1K

TL1911

TL1920

TL1921

R1924

3.3

D1923

10K

KDS4148

2.9

0

2.4

2.4

0

0

R1921

Q1922

10K

RDTC144EE

SYNC SELECT

B+5V

FB1901

A192WJ

3

R1907

R1PWR5V

DSDA1

RR1XC-

RR1XC+

RR1X0-

RR1X0+

DSCL1

RR1X1-

RR1X1+

RR1X2-

RR1X2+

D1906

KDS184

3

TL1922

R0PWR5V

DSDA0

RR0XC-

RR0XC+

RR0X0-

RR0X0+

DSCL0

RR0X1-

RR0X1+

RR0X2-

RR0X2+

1C0112C1122C2132C314A15/2G16VCC

(B,A)=

00:C0 HDMI

01:C1 PC

10:C2 *

11:C3 *

D1907

KDS4148

H1_SDA

H1_SCL

2

4

470K

1

3

G

S

D

Q1904

SM3K7002F

G

H1_SCL

S

D

Q1903

SM3K7002F

EDID HDMI NVM

PLUG&PLAY

FB1902

A192WJ

H0_SCL

H0_SDA

R1926

470K

1

3

2

4

G

S

D

Q1924

SM3K7002F

G

S

D

Q1923

SM3K7002F

EDID HDMI NVM

PLUG&PLAY

00000003.3

92Y10

IC1941

TVHC153T

56

D1909

RB520S30

R1911

27K

2

4

1

3

R1909

47K

H1_SDA

D1908

KDS4148

3

1

4

2

R1928

47K

4

123

C1906

0.1u

Z

25V

R1915

47K

TL1903

2

1

4

3

10

R1912

VCC

IC1902

24LC2BIN

EEPROM

1A02A13A24

0000

56

4

12

3

C1922

0.1u

Z

25V

R1933

47K

TL1923

3

4

1

2

R1930

10

VCC

IC1922

24LC2BIN

EEPROM

1A02A13A24

0000

HDMI_WS

HDMI_SCK

Q1905

RN4904

X1951

SCA146WJ

HOTP_CONT_1

CEC

HDMI_RSTO

HDMI_INT_I

TL1904

5.05.05.05.0

5

6

7WP8

SCL

SDA

Q1906

VSS

RDTC144EE

0

HDMI_WPO

5.0

0

Q1925

RN4904

HOTP_CONT_0

TL1924

5.05.05.05.0

5

6

7WP8

SCL

SDA

VSS

HDMI_PC

DHSYNC

DVSYNC

R1952

DINR[7]

DINR[6]

DINR[5]

DINR[4]

R1953

47

DINR[3]

DINR[2]

DINR[1]

DINR[0]

R1951

DINCK

R1954

47

DING[7]

DING[6]

DING[5]

DING[4]

R1955

47

DING[3]

DING[2]

DING[1]

DING[0]

R1956

DINB[7]

DINB[6]

DINB[5]

DINB[4]

R1957

DINB[3]

DINB[2]

DINB[1]

DINB[0]

C1907

C1908

0.1u

0.1u

25V

25V

C1952

10u

FB1951

16V

A192WJ

KZA510WJPZ

FB1953

A192WJ

+3.3V(D)_XTAL

+3.3V_IOVCC

FB1952

A192WJ

C1961

10u

16V

KZA510WJPZ

R1958

4.7K

C1960

1000P

47

+3.3V_IOVCC

78

56

34

12

C1954

1000P

78

56

34

12

47

HDMI_CLK

78

56

34

12

78

56

34

12

47

78

C1957

1000P

56

C1958

34

1000P

12

47

78

56

34

12

+3.3V_IOVCC

C1959

10u

16V

KZA510WJPZ

+3.3V(D)_REG

C1962

10u

16V

KZA510WJPZ

R1959

10K

3.3

3.3

3.3

3.3

1.8

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

3.3

1.8

3.3

3.3

3.3

3.3

3.3

1.8

3.3

3.3

3.3

HDMI-HS

C1965

1000P

TL1913

1.800

0

104

105

106

107

108

INT

GND

VCC

OGND

OVCC

109

CLK48B

110

Q23

111

Q22

112

Q21

0

113

Q20

114

VCC

0

115

GND

116

Q19

117

Q18

118

Q17

119

Q16

0

120

OGND

0

121

ODCK

122

OVCC

Q15

123

124

Q14

125

Q13

126

Q12

0

127

GND

128

VCC

0

129

Q11

0

130

Q10

131

Q9

132

Q8

0

133

Q7

134

OVCC

0

135

OGND

136

Q6

137

Q5

0

138

GND

139

VCC

140

Q4

0

141

Q3

0

142

Q2

143

Q1

144

Q0

OVCC6DACOVCC

OGND

HSYNC

VSYNC

1DE2

3

4

5

0

000

3.3

FB1954

A192WJ

C1966

1000P

1234567

R1960

47

8

DINEN

HDMI-VS

28.322MHz

R1965

1M

C1977

C1972

15P

12P

(CH)

C1969

0.1u

Z

25V

R1961

22K

R1962

4.7K

HDMI_RSTO

3.300

102

103

SCDT

RESET#

(CH)

R1966

1K

C1979

1000P

1.801.801.75

1.67

3.3

3.300

100NC101

96

97

98

99

TEST

XTALIN

REGVCC

XTALOUT

XTALVCC

89

90

91

92

93NC94

95

VCC

GND

OGND

DVCC2

DGND2

HDMI RECEIVER

IC1951

SII9025

HDMI 1.2

DECODER

COMP

AnRPr

VREF10RSET

DACGNDR

DACAVCC

DACAGND

7

8

000

3.3

3.3

C1970

1000P

DACGNDG

DACVCCR

AnGY18DACGNDB19DACVCCB20AnBPb

11

3.303.3

DACVCCG

12

13

14

15

16

17

0

0

0

0

0

3.3

3.3

TL1914

TL1915

TL1916

C1984

C1978

10u

16V

KZA510WJPZ

1000P

9

HDMI_SDO

R1968

R1969

R1970

22

22

22

C1986

1000P

88

OVCC

21

0

+3.3V_IOVCC

R1967

33

81NC82NC83NC84

85WS86

87

SD0

SCK

MCLKIN

MCLKOUT

DACDGND

VCC

GND

OVCC27CSDA28CSCL29DSDA130DSCL1

DACDVCC

OGND

22

23

24

25

26

0

0

1.8

1.8

3.3

3.3

3.3

C1990

0.1u

Z

25V

+1.8V_SIICVCC

C1989

C1991

1000P

1000P

2

4

R1971

22

1

3

SCL3

SDA3

C2000

1000P

C1996

0.1u

Z

25V

TL1917

R1973

33

0

1.803.300

1.80000000003.300

73

74

75

76

77

78

79

80

GND

VCC

SPDIF

MUTEOUT

DSDA032DSCL0

31

3.3

3.3

3.3

3.3

DSDA1

33

0

C1998

1000P

DSCL1

OVCC

OGND

R1PWR5V34R0PWR5V35DVCC

0

0

DGND

DVCC

72

AGND

3.3

71

R1X2+

3.3

70

R1X2-

3.3

69

AVCC

0

68

AGND

3.3

67

R1X1+

3.3

66

R1X1-

3.3

65

AVCC

0

64

AGND

3.3

63

R1X0+

3.3

62

R1X0-

3.3

61

AVCC

0

60

AGND

3.3

59

R1XC+

3.3

58

R1XC-

3.3

57

AVCC

0

56

ANTSTO

3.3

55

PVCC1

0

54

PGND

0

53

AGND

3.3

52

R0X2+

3.3

51

R0X2-

3.3

50

AVCC

0

49

AGND

3.3

48

R0X1+

3.3

47

R0X1-

3.3

46

AVCC

0

45

AGND

3.3

44

R0X0+

3.3

43

R0X0-

3.3

42

AVCC

0

41

AGND

3.3

40

R0XC+

3.3

39

R0XC-

3.3

38

AVCC

3.3

PVCC0

37

C2002

DGND

0.1u

25V

36

CZF

0

1.8

DSDA0

DSCL0

Z

+3.3VSIIAVCC

+3.3VSIIAVCC

FB1955

0210TA

B+1.8V

RR1X2+

RR1X2-

C2006

1000P

C2008

1000P

C2009

1000P

TL1918

C2012

1000P

C2014

1000P

C2015

1000P

C2016

1000P

C2004

1000P

RR1X1+

RR1X1-

RR1X0+

RR1X0-

RR1XC+

RR1XC-

C2010

1000P

RR0X2+

RR0X2-

RR0X1+

RR0X1-

RR0X0+

FB1957

RR0X0-

A192WJ

RR0XC+

RR0XC-

FB1956

A192WJ

R0PWR5V

R1PWR5V

TO MAIN7(VCT-PRO)

DHSYNC

DHSYNC

DVSYNC

DVSYNC

DINR[7]

DINR[6]

DINR[5]

DINR[4]

DINR[3]

DINR[2]

DINR[1]

DINR[0]

DING[7]

DING[6]

DING[5]

DING[4]

DING[3]

DING[2]

DING[1]

DING[0]

DINB[7]

DINB[6]

DINB[5]

DINB[4]

DINB[3]

DINB[2]

DINB[1]

DINB[0]

DINCK

DINEN

HDMI_SCK

HDMI_WS

HDMI_SDO

HDMI_INT_I

HDMI_RSTO

HDMI_WPO

HOTP_CONT_0

HOTP_CONT_1

SDA3

SCL3

TO MAIN8(UCON/PANEL_IF)

HDMI_PC

CEC

TO MAIN10(POWER SUPPLY)

BU+3.3V

B+1.8V

B+3.3V

B+5V

SEES Engineering Department

Training course: D44

64

Page 27

Main 4/13 (DTV STi5105) Schematic Diagram

()

DUNTKE449WE01

RESET

DTV CPU

TO MAIN5(DTV MEMORY)

B+2.5V_ST

LMIABE12

LMIABE11

LMIABE10

LMIABE9

LMIABE8

LMIABE7

LMIABE6

LMIABE5

LMIABE4

LMIABE3

LMIABE2

LMIABE1

LMIABE0

LMIBABE1

LMIBABE0

LMIDBE15

LMIDBE14

LMIDBE13

LMIDBE12

LMIDBE11

LMIDBE10

LMIDBE9

LMIDBE8

LMIDBE7

LMIDBE6

LMIDBE5

LMIDBE4

LMIDBE3

LMIDBE2

LMIDBE1

LMIDBE0

LMIDQSBE0

LMIRDNWRBE

NLMICASBE

NLMIRASBE

NLMICSBE

LMICLKENBE

LMINCLKBE

LMICLKBE

LMIDQMBE1

LMIDQSBE1

LMIDQMBE0

LMIVREF

FMIADDBE22

FMIADDBE21

FMIADDBE20

FMIADDBE19

FMIADDBE18

FMIADDBE17

FMIADDBE16

FMIADDBE15

FMIADDBE14

FMIADDBE13

FMIADDBE12

FMIADDBE11

FMIADDBE10

FMIADDBE9

FMIADDBE8

FMIADDBE7

FMIADDBE6

FMIADDBE5

FMIADDBE4

FMIADDBE3

FMIADDBE2

FMIADDBE1

FMIDATABE15

FMIDATABE14

FMIDATABE13

FMIDATABE12

FMIDATABE11

FMIDATABE10

FMIDATABE9

FMIDATABE8

FMIDATABE7

FMIDATABE6

FMIDATABE5

FMIDATABE4

FMIDATABE3

FMIDATABE2

FMIDATABE1

FMIDATABE0

NFMIOE

FMIRDNWR

NRESETOUT

FLASHWP

FE_SCL

FE_SDA

NFMICSA

B+2.5V_ST

FB4001

A192WJ

C4001

C4002

0.1u Z

1u

25V

6.3V

NLMIRASBE

NLMICASBE

C4011

0.1u

25V

LMIRDNWRBE

LMIDBE0

LMIDBE1

LMIDBE2

LMIDBE3

C4012

0.1u

25V

LMIDBE4

LMIDBE5

LMIDBE6

C4006

0.1u

25V

LMIDBE7

LMIDQSBE0

LMIDQMBE0

C4003

C4004

0.1u

0.01u

25V

25V

LMIDQMBE1

LMIDQSBE1

C4007

0.1u

25V

LMIDBE8

LMIDBE9

LMIDBE10

C4005

0.1u

25V

LMIDBE11

LMIDBE12

LMIDBE13

LMIDBE14

LMIDBE15

LMINCLKBE

LMICLKBE

C4010

0.1u

25V

LMICLKENBE

LMIABE12

LMIABE11

LMIABE9

LMIABE8

C4009

0.1u

25V

LMIABE7

LMIABE6

LMIABE5

LMIABE4

NLMICSBE

C4008

47u

6.3V

ASY

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

209

210

211

212

213

214

215

216