Page 1

GX20

3

20

3

6

VDDIO

R3

F

62 727170696867666561 6463

43

98

R0

CONFIDENTIAL

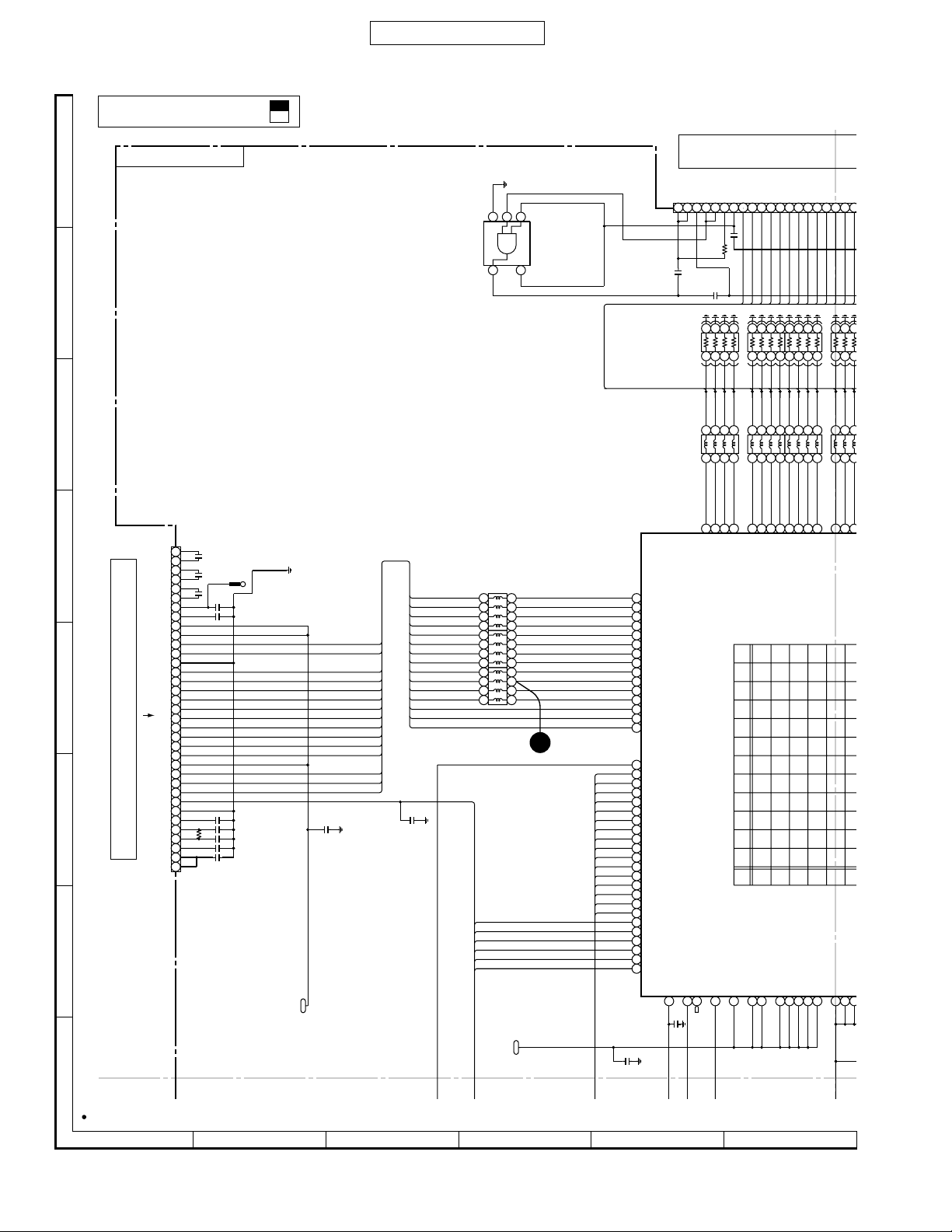

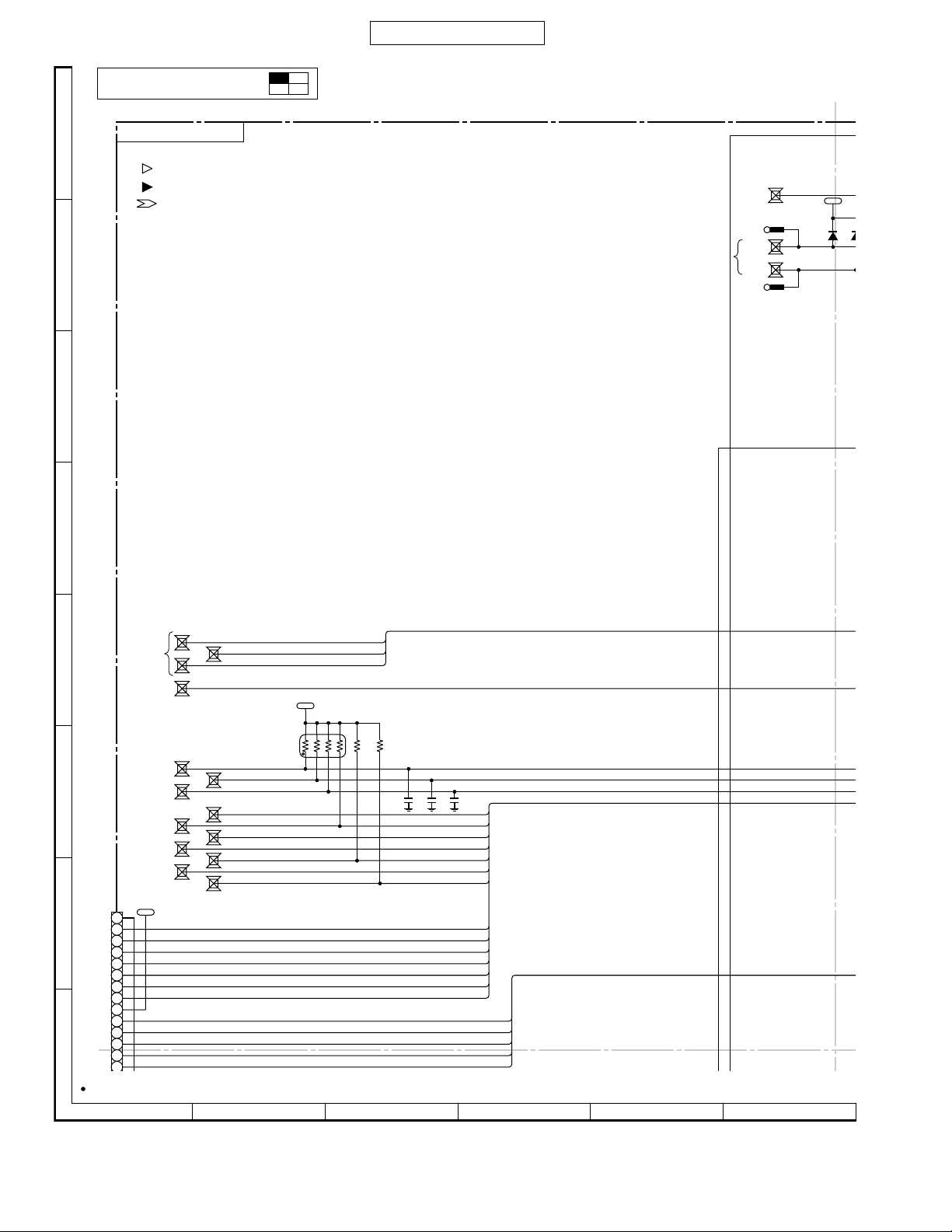

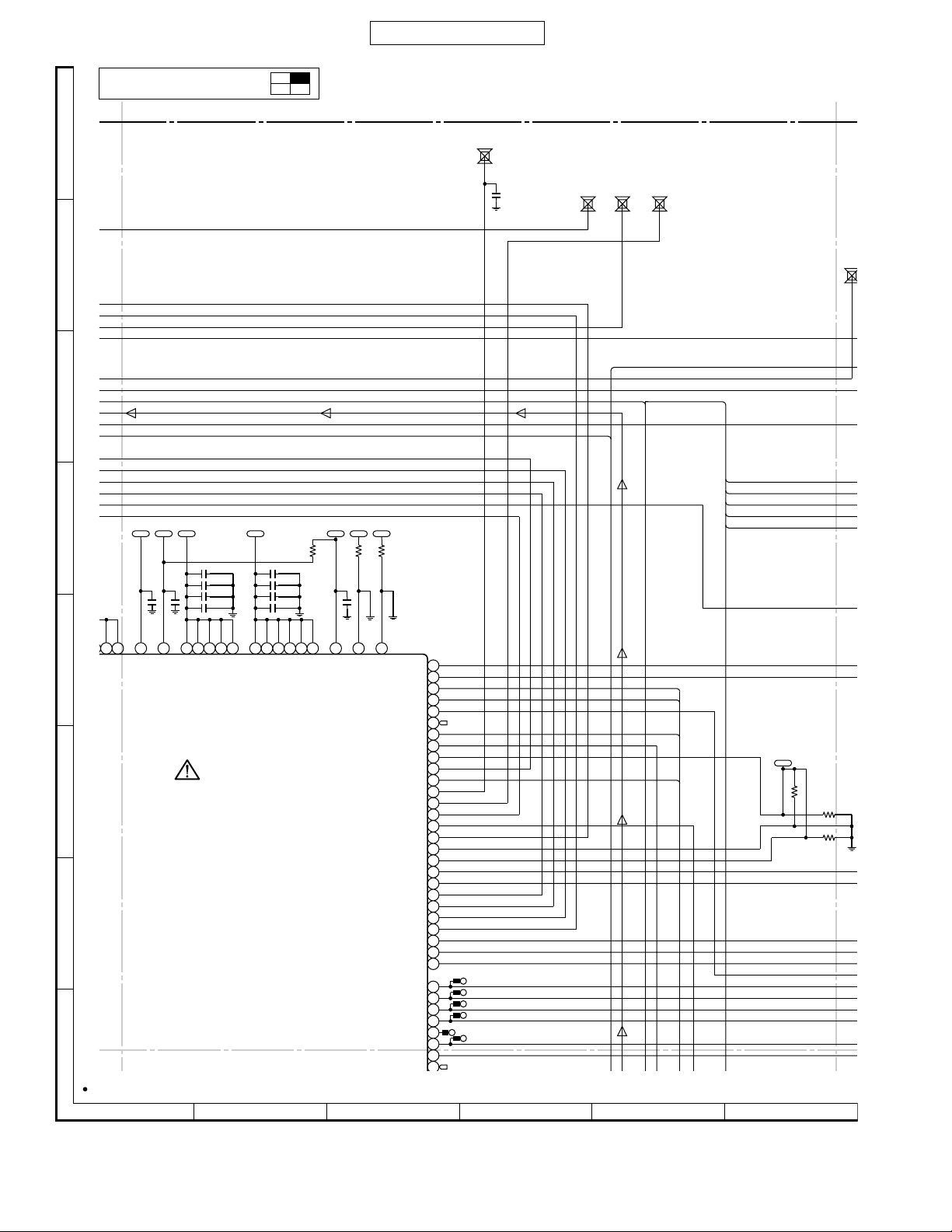

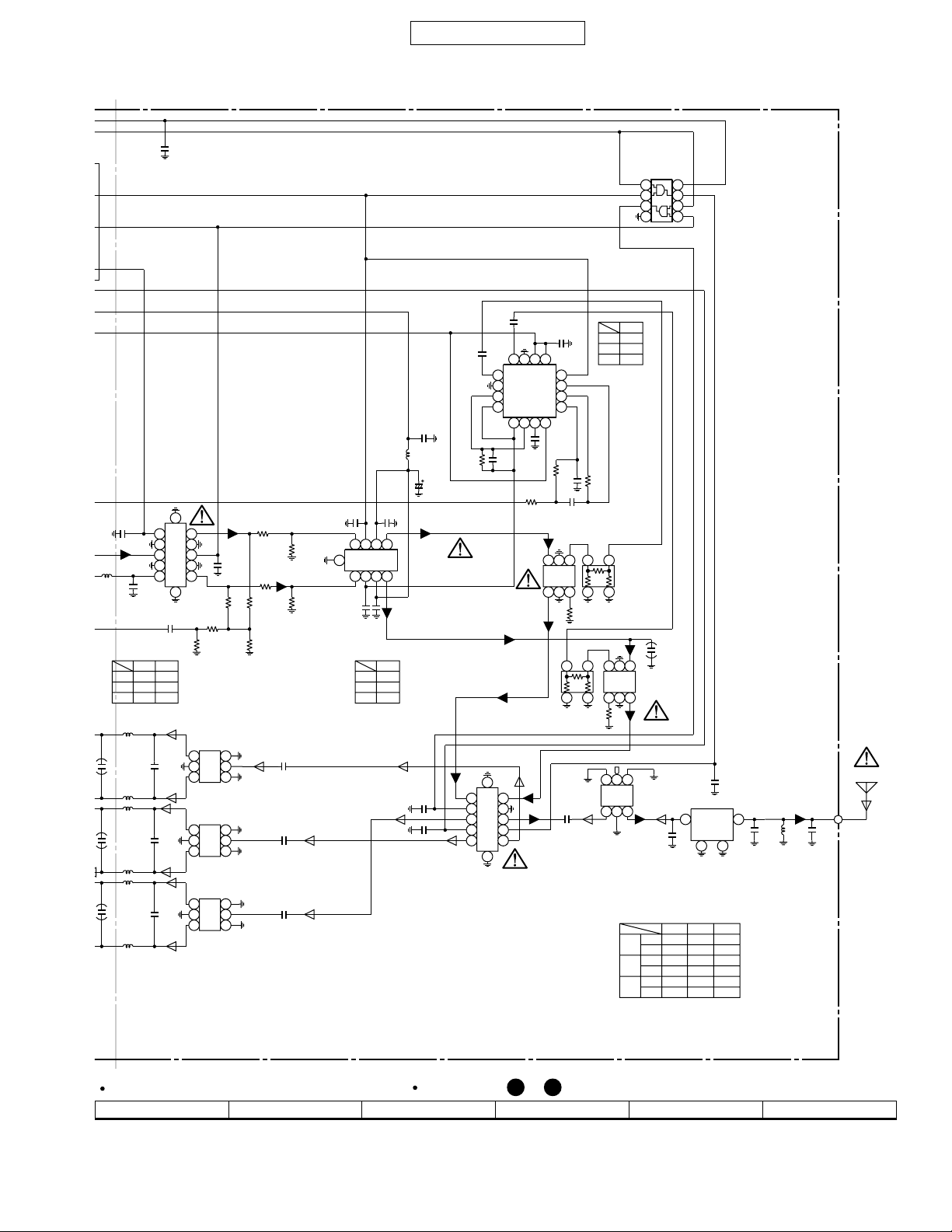

[4] Schematic diagram/wiring side of P.W.Board

MAIN PWB-A (1/3)

A

B

C

D

E

F

G

MAIN PWB-A(1/3)

C428

VEE

VDD

CKS

GND

FLM

WR

CSB

GND

1

C427

1

C425

1

C426

1

CK

LP

D7

D6

D5

D4

D3

D2

D1

D0

RD

RS

R424

V4

75K

V3

V2

V1

V0

V0

1234567891011121314151617181920212223242526272829303132333435

CN401

C418

1

CAPA3+

CAPA3-

CAPA2+

CAPA2-

CAPA1+

CAPA1-

VOUT

VREG

LCD001

EXTERNAL DISPLAY

RESB

TP419

C424

0.1

C423

1

C421

1

C420

1

C419

1

5-8 (6-C)

VINT

5-9 (11-B)

C422

0.1

SUBCKS

SUBCK

SUBFLM

SUBLP

SUBD7

SUBD6

SUBD5

SUBD4

SUBD3

SUBD2

SUBD1

SUBD0

SUBWR

SUBRS

SUBCS

SUBD6

SUBD4

SUBD2

SUBD0

SUBD3

SUBD1

SUBCKS

SUBLP

SUBCK

SUBFLM

SUBD7

SUBD5

SUBRS

SUBWR

SUBCS

/LCD_RESET

C473

100P

(CH)

IC405

TC7SZ08A

AND GATE

2

3

4

12

3

4

12

3

4

12

3

4

BUFOFF

LCD_INT

/LCD_WAIT

/RD

/WE

/LCD_CS

5-19 (10-G)

5678

5678

5678

VLCD

1

5

L447

L446

L445

26

DATA[0]

DATA[1]

DATA[2]

DATA[3]

DATA[4]

DATA[5]

DATA[6]

DATA[7]

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

VLCD

SUBDB6

5557 5860

SUBDB4

SUBDB2

SUBDB0

SUBDB3

66 6769707172

SUBDB1

27

SUBCKS

SUBLPIN

SUBCK

SUBFLMIN

SUBDB7

SUBDB5

78 8081

SUBRS

SUBWR_B

SUBCS_B

2122

RSP

DB0

DB1

DB2

DB3

DB4

DB5

DB6

93949596

DB7

DB8

DB9

DB10

106107108 110118119120121 122 123131 136

DB11

DB12

DB13

DB14

DB15

BUFOFF_B

LCDINT

WAIT_B

RD_B

46 47

WR_B

34 35

CS_B

C417

0.01

C416

0.1

T-COM

T-COMB4COMC

CN404

1234567

C449

4.7

XIN

RESET_B

56

54

TFT-COM

COMC

C448

1

1234

B4

L448

1234

XOUT

42

NC

78

6

78

6

87

G0G1G2G3G4

CAMCK

85

VCOMH

COMDC

5

G4G2G0

5

77

VDDPLL

2

B0

B3

B5G4G1

G0

B2G2B1

9

8

101112131415161718

C462

4.7

R433

56K

B0B1B2B3B4B5G0G1G2R0G5G4G3

5

6

5

6

89

R4

78

6

1234

78

6

1234

282930

39

B1

B3B4B5

13 14 15 16 17 18 19 20 21 22 23 24

25 26 27 28 29 30 31 32 33 34 35 36

B

C

VDDCORE

VDDCORE

VDDCORE

84

90

74

5

G3G1B5B3B1R4R2

5

86

38 484746454443424137 4039

D

VDDCORE

VDDCORE

139

143

78

1234

R0

78

L449

1234

101

R0

123456789101112

VDDCORE

151719

99

R2

123456789101112

A

VDDCORE

G3

12

8

L450

12

G5

19

78

7

636465

100

R1

G5

IC

LR

DI

50 605958575655545349 5251

E

VDDIO

VDDIO

232426

R3R1G5

6

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 1 SCHEMATIC DIAGRAM (1/24)

5 – 6

45

6

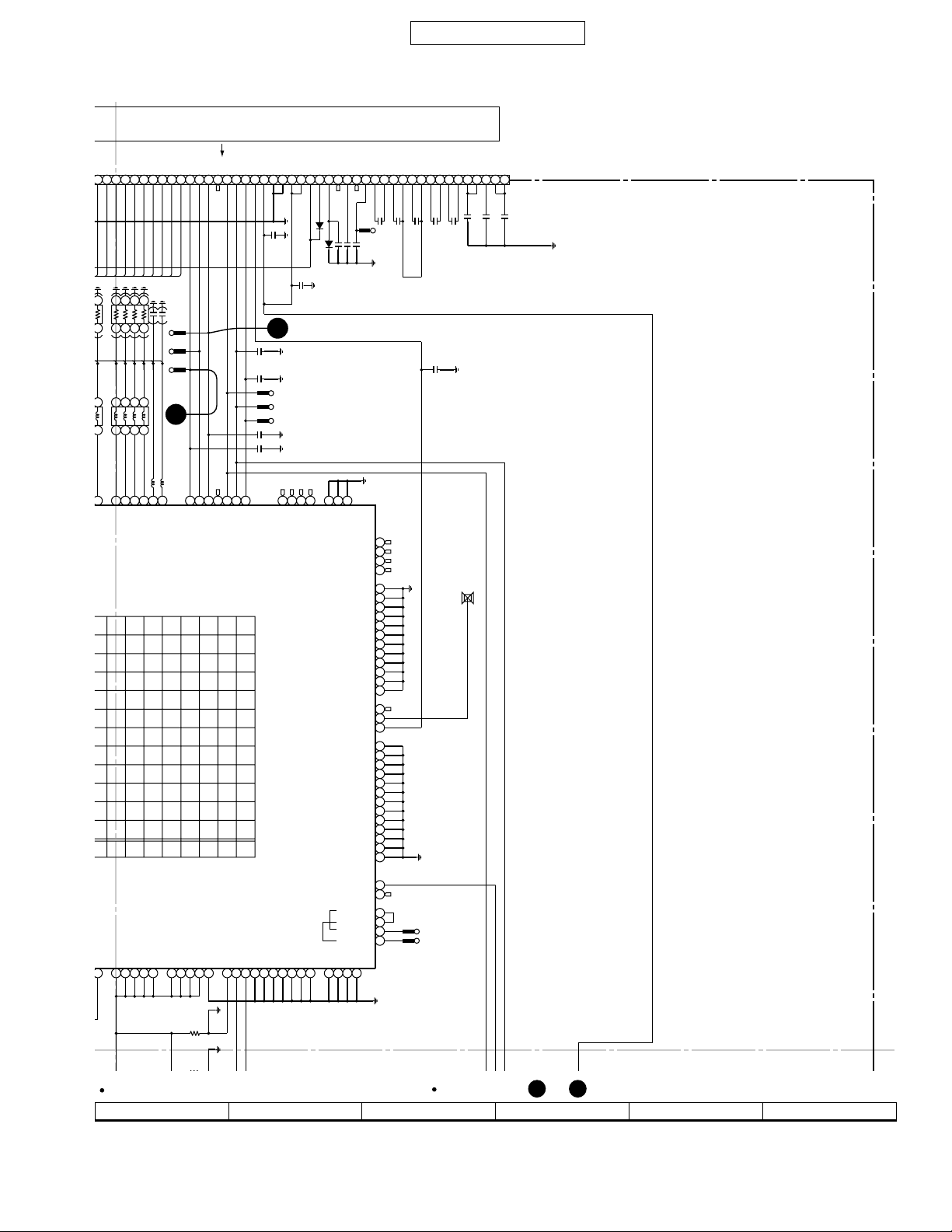

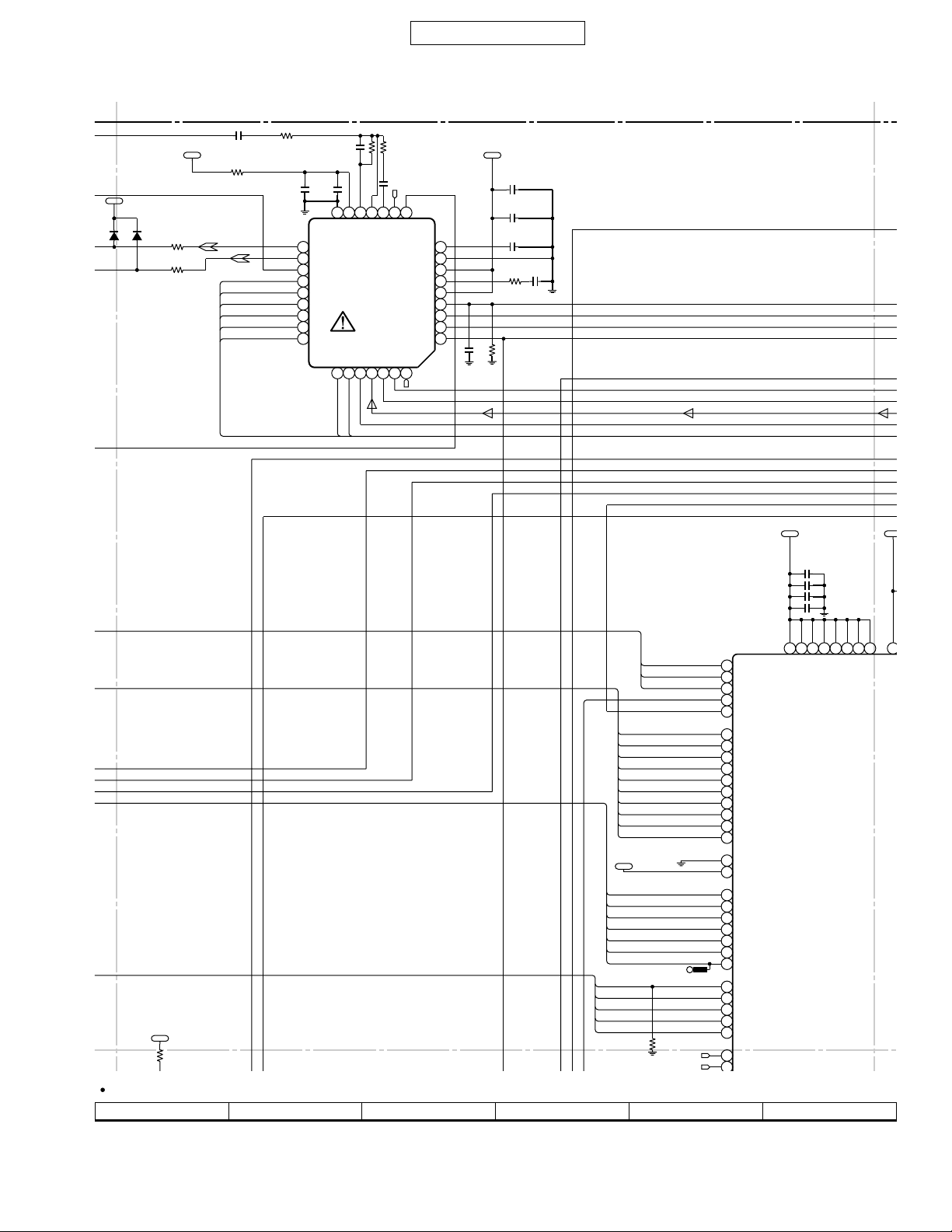

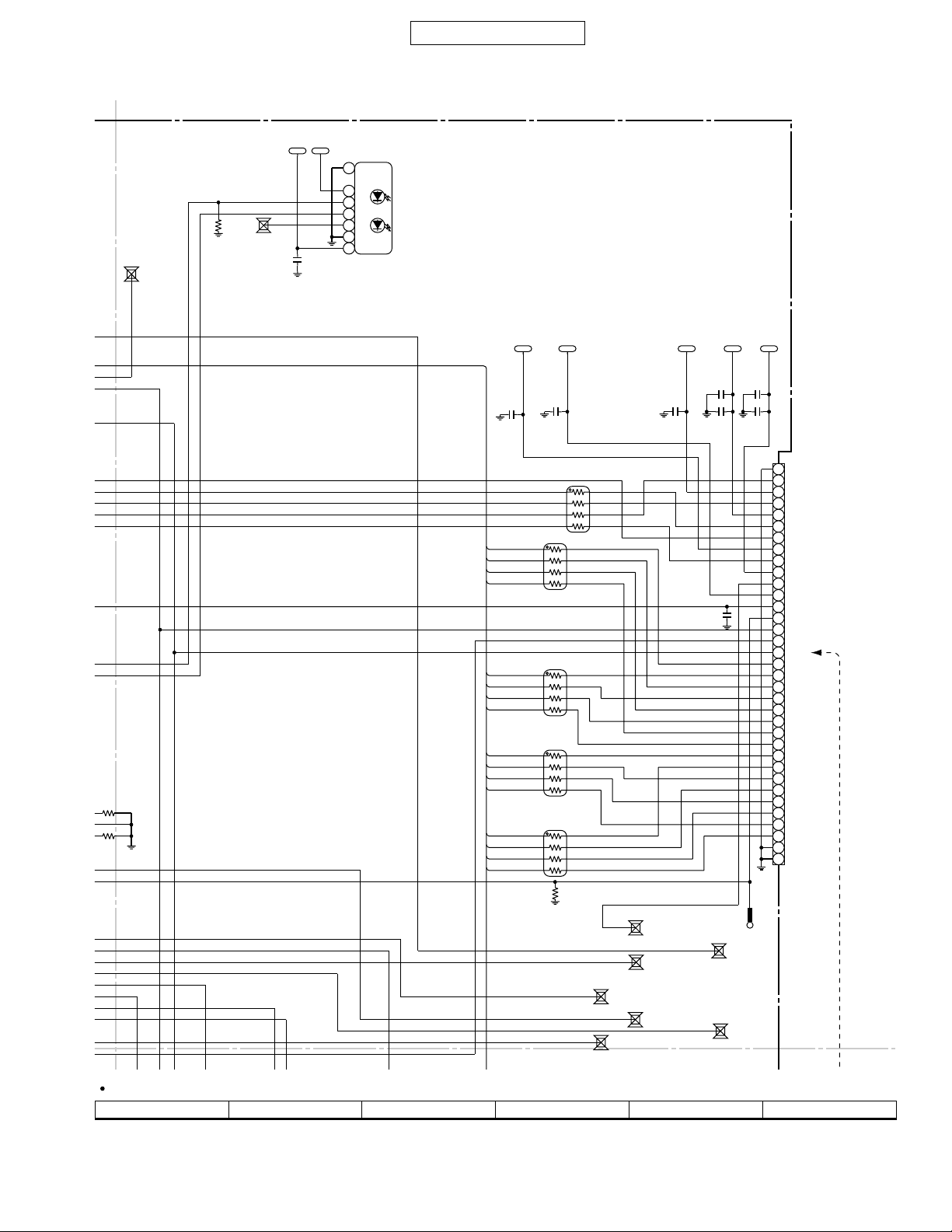

Page 2

CONFIDENTIAL

VDDCORE

G3

G2

GX20

LCD100

MAIN DISPLAY

VR

VS

G4

78

7

63

G5

R0

G5

5

6

R5R3R1

5

6

98

100

R1R3R5

R1

B2

L407

88

R3

R2

TP426

TP425

B0

TP424

24

L451

60 (100MHz)

L408

38

40

B0

B2

R4

R5R4R3R2R1R0G5G4G3

DCLK

60 (100MHz)

HSY

DCLK

HSYNC

505152

DCLK

HSYNC

VSY

SO

NC

VSYNC

NC

140

VSYNC

SE_DI/PORT7

RESET

CS

SI

SCLKR5GND

117

129

141

SE_CK/PORT1

SE_DO/PORT0

SE_LD1/PORT2

VCC

25

GND

C453

2.2

TP422

TP421

TP420

C474

10P(CH)

NC

103

EXCS_B0

VDC

VDC

C447

4.7

C472

10P(CH)

C469

10P(CH)

C471

10P(CH)

62

41

EXCS_B2

EXCS_B1

G3

161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960

451234

G5

8

L450

451234

65

IC403

LR38863

DISPLAY CONTROLLER

11911611510 9 110 111 11 2 113 114 117 118 12 0

107106100 101 102 103 104 105 108

38 484746454443424137 4039

50 605958575655545349 5251

62 727170696867666561 6463

F

E

D

98 9997

74 848382818079787773 7675

86 969594939291908985 8887

J

H

G

143142141140139138137136135134133

131128127121 122 123 124 125 126 129 130 132

PWMLCD/PORT4

L

K

M 144

VSS1

VSS2

VCL AMP

COM2

NC

NC

D409

1SS405

C450

1

C451

D408

RB520S30

NCNCNC

53

112

114

124

DA0

DA1

DCS_B

EXCS_B3

MP4_PLLCK

MP4_P0

GTDIO_B

MP4 RESET_B

BSPIXEL0

BSPIXEL1

BSPIXEL2

BSPIXEL3

BSPIXEL4

BSPIXEL5

BSPIXEL6

BSPIXEL7

BSCLK

BSBLK_B

BSVS_B

BSHS_B

PWM1/PORT8

PWM0/PORT3

HSWRD

HSEN

HSCK

TESTI

STKCHK

NC

NC

1

HSD7

HSD6

HSD5

HSD4

HSD3

HSD2

HSD1

HSD0

VDD2

TP430

C452

C5-

C454

1

C5+

C4-

1

C455

1

NC

NC

102

NC

NC

113

125126

137138

128

116

104105 109

NC

91 92

20

6873

5961

49

6789101112 13

32 33 3637

C4+

C3-

()

C3+

C2-

C457

C470

C2+

4.7

0.01

C1-

C1+

C458

4.7

5-8 (6-G)

BL_ICONT

VDC2

C459

G

VDC2

4.7

C460

VS

C461

4.7

2.2

SE_LD2/PORT5

SE_LD3/PORT6

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

PLLDIV0

PLLDIV1

PLLGND

GND

GND

GND

GND

GND

GND

SCANEN

PLLDIV2

232526

143

115

43

767982

97

132

135

()

345

141618

GND

31

444548

75

83

DUMMY1

DUMMY2

DUMMY3

DUMMY4

GND

GND

111

127

GND

142

130

NC

144

133 134

TP418

1

TP416

( ) : Not Mount The numbers24to26are waveform numbers shown in pages 5-4 ,5-5.

78 9

Figure 2 SCHEMATIC DIAGRAM (2/24)

10 11

12

5 – 7

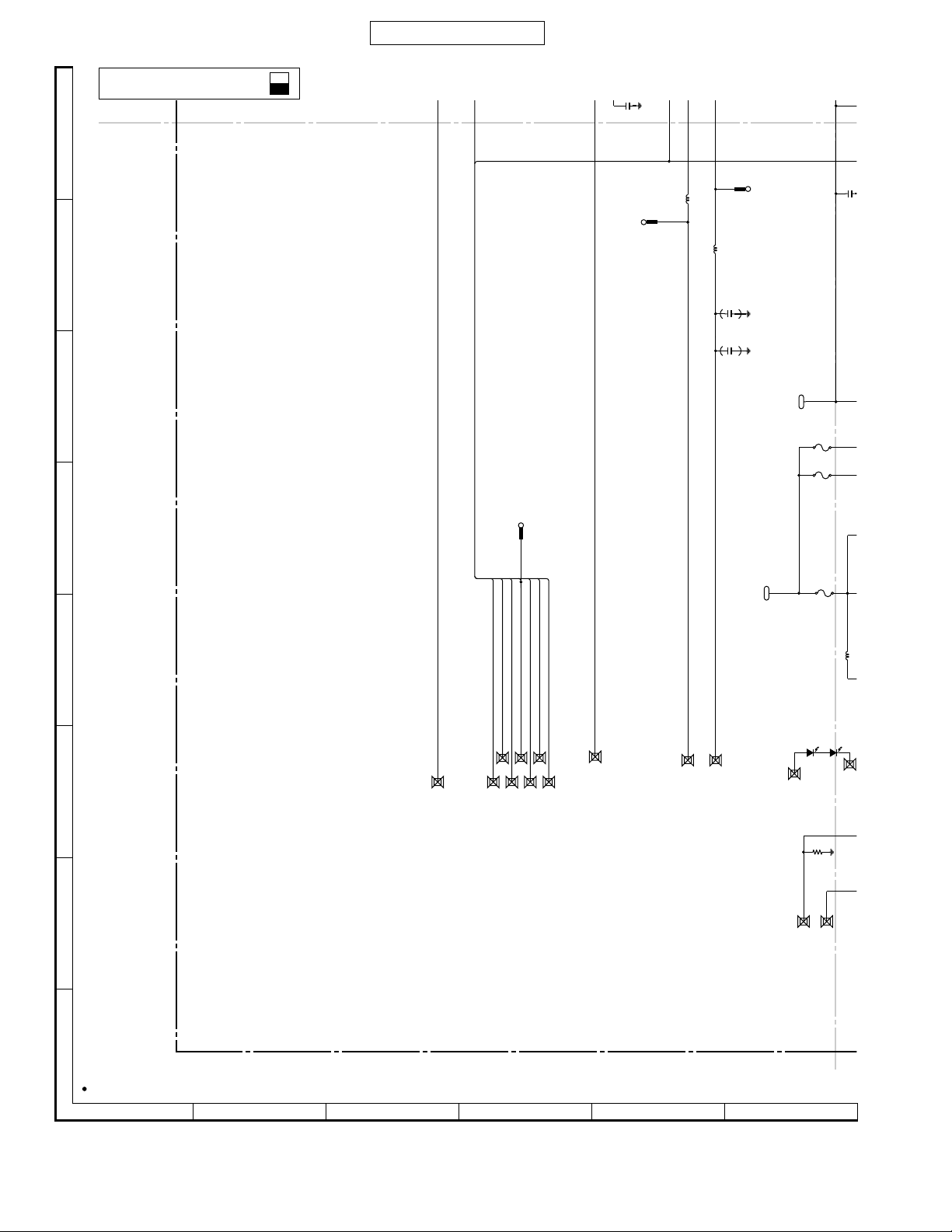

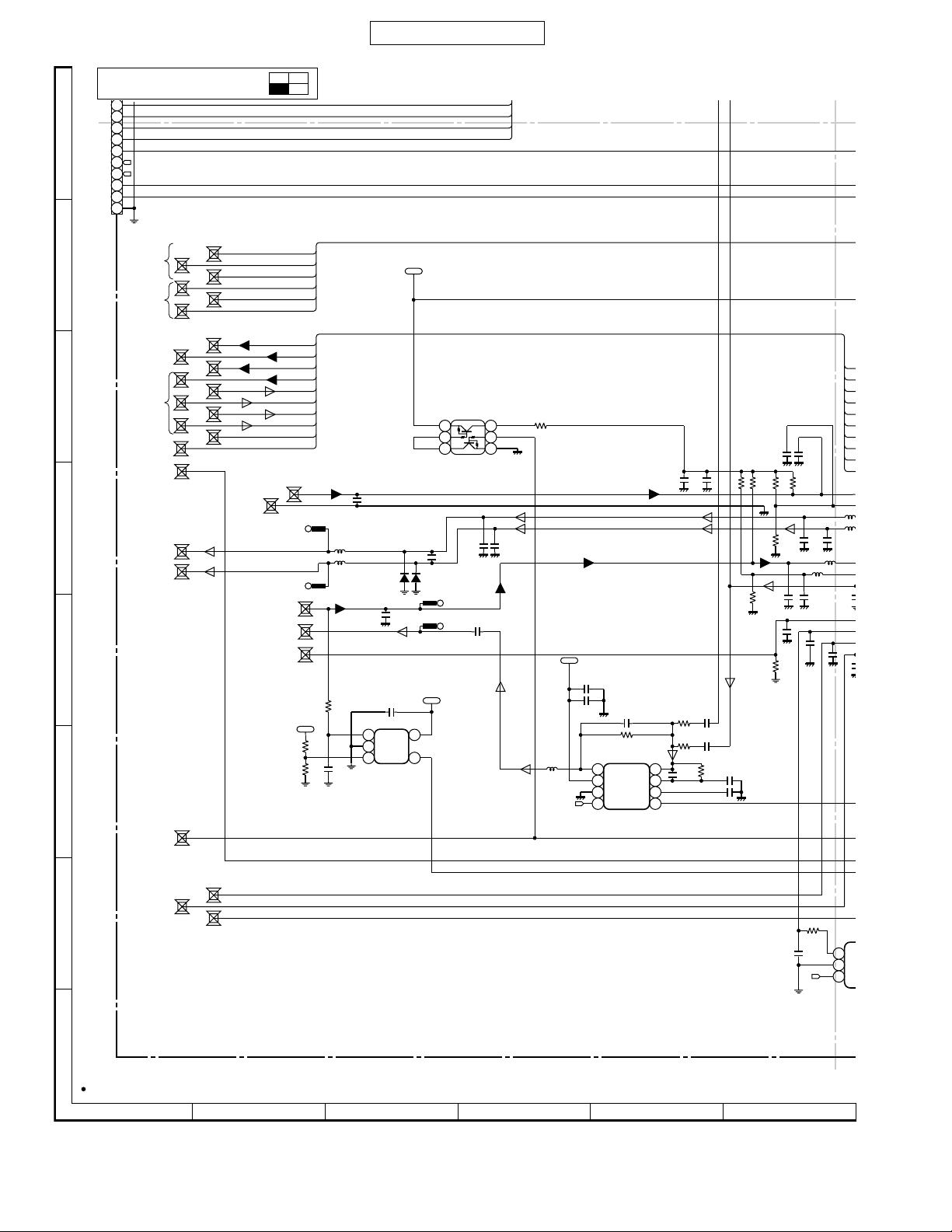

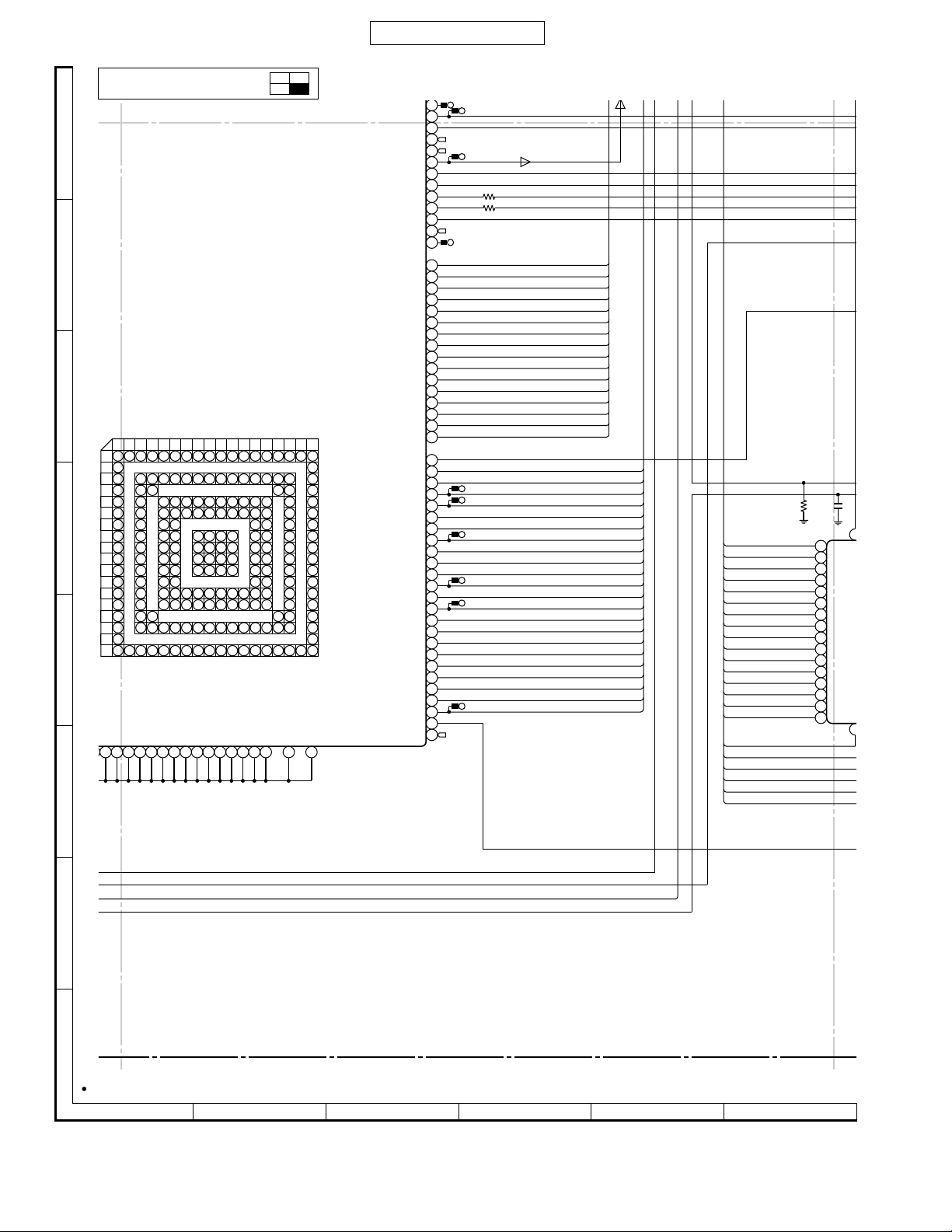

Page 3

GX20

V

G

9

C

A

MAIN PWB-A (1/3)

CONFIDENTIAL

5-1

/LCD_RESET

C416

0.1

TP415

L405

60 (100MHz)

TP414

L404

B

60 (100MHz)

C

5-6 (2-G)

LCD_RST

13M_CLK

D

TP404

/LCD_RESET,/RD,/WE,BUFOFF,/LCD_CS,LCD_INT,/LCD_WAIT

VBAT_AP

5-11 (7-B)

5-18 (3-B)

/LCD_WAIT

/LCD_CS

LCD_INT

BUFOFF

/WE

/RD

/LCD_RESET

E

VINT

FS402

Fuse

FS403

0.63A

Fuse

FS401

0.63A

Fuse

C41

0.1

1

L

2

F

G

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 3 SCHEMATIC DIAGRAM (3/24)

LCD_RST

5-17 (11-B)

G

LED_A

G

6

LED401

NSCW335

R455

470K

G

BL_ICONT

SUB_BL_ON

5-15 (11-H)

5-7 (9-E)

LED_K

CAMCLK

5-15 (11-G)

LED402

NSCW335T

/WE

/LCD_CSG/LCD_RESET

5-17 (10-A)

5-17 (10-A)

5-15 (10-H)

G

G

G

G

G

G

G

/LCD_WAIT

5-17 (11-B)

LCD_INT

5-15 (11-H)

/RD

BUFOFF

5-17 (11-B)

5-17 (11-A)

G

DATA[0-15]

5-17 (11-A)

G

13M_CLK

5-15 (11-G)

G

45

5 – 8

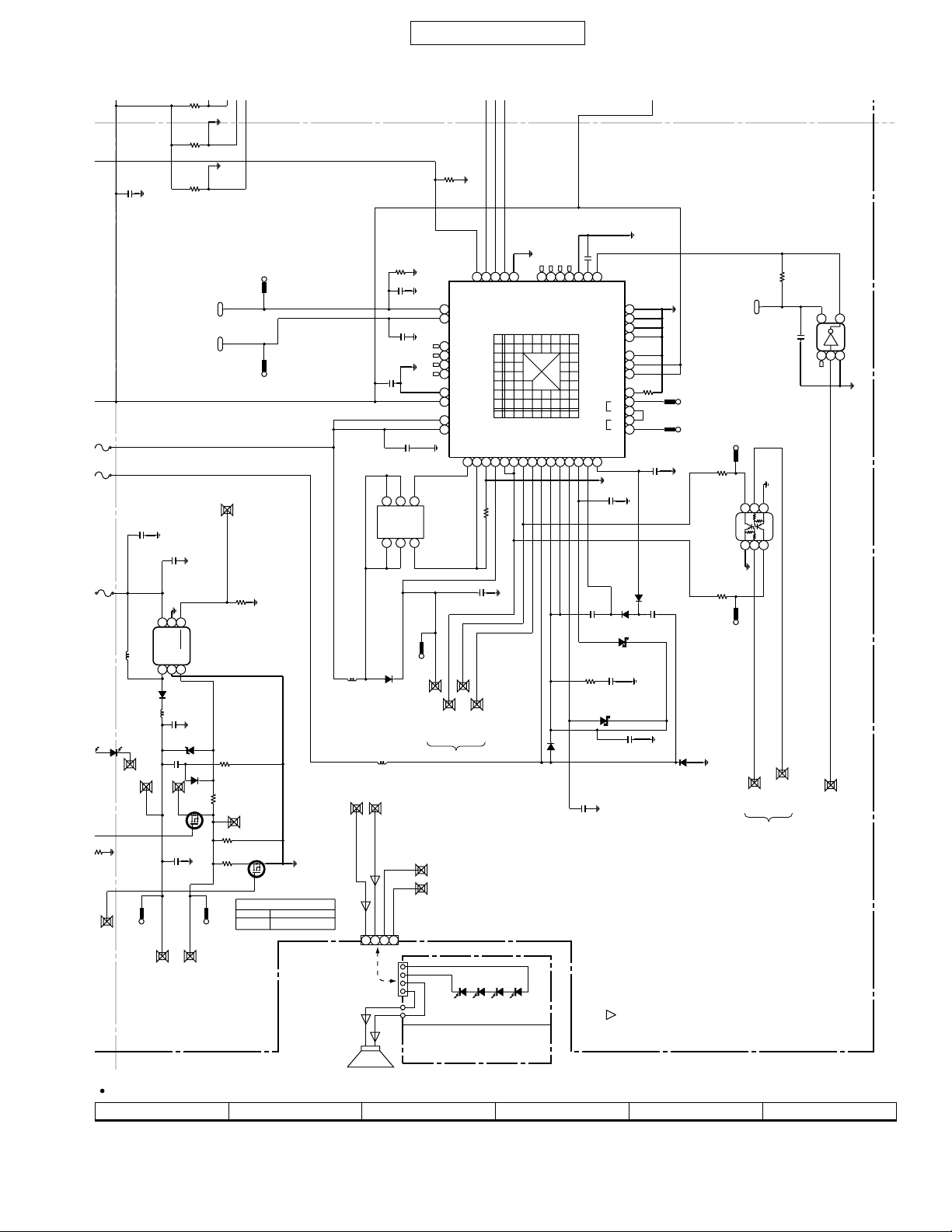

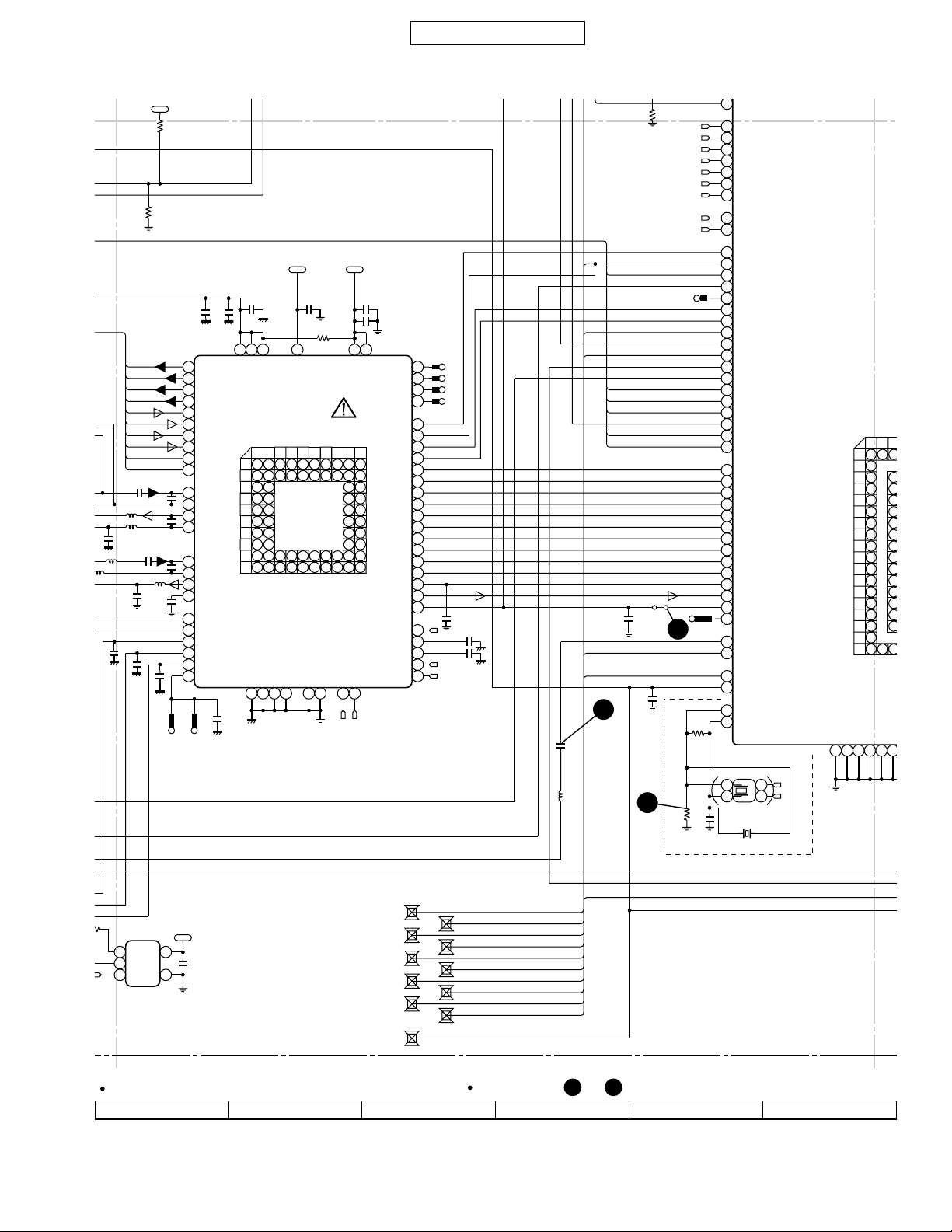

Page 4

5

4

7

Vcc

1

NC

G

5-13 (9-G)

IC406

4

3

2

TXON

5-18 (3-D)

GX20

TC7SZ04A

LOGIC

GND

CONFIDENTIAL

()

()

R413

100K

R410

1.2K

C413

1

CAMN

40

CAMP

28

CAPN2

NC

23

CAPP2

NC

CAPN1

NC

CAPP1

NC

15 16

CPIN

19 2021

VIO

VBAT2

46

VBAT1

4

C402

4.7

3.69V

0V

D

G

S

D

Q401

FDG311 N

4

5

0V

3.69V

C404

1

TP405

G

G

G

VPLUS2

LEDR_M

5-18 (3-B)

5-12 (1-D)

G

LED_K_M

LED_A

G

4

BACK LIGHT

FPC ASS'Y PWB-F

5-15 (11-C)

5-15 (12-C)

L410

33nH

G

LED_A

TP428

C465

100P(CH)

GND

Vin

GND

SW

123

D413

RB521S30

C463

100P(CH)

D410

RD22SL

LED_K

6.46V

0.09V

Q403

2SK3019

C468

0.22

G

LED_A

()

456

IC404

SHDN

LT1937

FB

DC-DC

C464

0.0022

G

G

R453

4.7

G

LED_K_M

-7V

+13V

G

PWM_CPU

R440

470K

R438

4.7K

D414

RB520S30

R437

1K

SD

G

0V

R454

220

0.09V

0V

TP429

ALL ON LOW LIGHT ON

TP413

TP412

5-15 (11-G)

LED_K_M

SD

0.01V

Q404

G

MCH3443

BL_ICONT

HL

C411

1

C409

0.1

3.69V

123

D

D

6

3.69V

L402

4.7∝H

D404

RB551V30

L401

4.7∝H

G

G

5-12 (1-D)

RECIVER_OUTN_REC

RECIVER_OUTP_REC

CN402

123

C415

0.1

S402

use

S403

.63A

use

C466

1

FS401

0.63A

Fuse

L411

22∝H

LED401

NSCW335T

G

LED_K

55

0K

G

BL_ICONT

5-7 (9-E)

EP100

EARPIECE

IC402

IX3053AF

POWER MANAGEMENT

NC

25

26

CLK

STRB

12345678

12345678

A

VPLUS2

INDEX

22

49

30

FRP

910111213141516

B

LEDR

10

49

17 18 19 20

C

LEDG

2

21 22 23 24

D

LEDB

11

5

LSO11

25 26 27 28

E

SW1

44

42

RSTB

TRSW

SENSP

12

17

R404

G

LEDG_M

LEDB_M

29

DATA

SENSN

18

0.1

NC

NC

6

13

LSO21

LSO12

29 30 31 32

F

VPLUS11

VPLUS12

27

47

D402

RB521S30

C414

0.1

NC

7

14

LSO22

WVOUT

33 34 3536 37 3839 40

41 42 4344 45 4647 48

H

G

BLED

FLED

43

363738

C405

1

()()

C401

0.1

32

33

VREF

GND

45

LEDCTL

GND3

24

GND2

GND1

3

TEST

CUR1

CUR2

34 35

IREF

31

T4

41

T3

48

T2

89

T1

1

SBD

VNEG

39

D406

RB521S30

()

D405

RD22SL

D403

RD22SL

C403

0.1

C408

1

D407

RB521S30

C406

1

RECEPTION SIGNAL

R407

120K

TP411

TP410

D401

RB520S30

R405

220

R403

4.7K

Q402

5-6 (2-G)

TP407

EMH11

TP406

VINT

0V

2.29V

5

6

2

1

0V

0V 0V

G

LEDG

5-14 (5-B)

4

3

()

C475

0.1

G

LEDR

( ) : Not Mount

78 9

Figure 4 SCHEMATIC DIAGRAM (4/24)

5 – 9

10 11

12

Page 5

GX20

CONFIDENTIAL

MAIN PWB-A (2/3)

A

B

MAIN PWB-A(2/3)

RECEPTION SIGNAL

TRANSMISSION SIGNAL

SPEAKER SIGNAL

5-18 (6-B)

5-18 (3-D)

VIB_CNT

SP1-1

SP2-1

TP110

TP 111

G

G

G

D102

VB

1SS388

C

D

G

E

5-18 (4-G)

5-18 (5-E)

5-18 (3-D)

F

G

H

5-18 (4-C)

5-18 (4-D)

5-18 (4-E)

5-18 (4-D)

)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

5-18 (3-C)

5-18 (3-E)

5-18 (4-D)

5-18 (3-C)

3.0V

VINT

G

G

G

G

G

G

G

G

G

G

GENIE_CHG

ADPDET

ADP

TXD

G

RTS

G

CONT2

G

SIMIO

SIMCLK

SIMRST

KEYPADROW[0-4],KEYPADCOL[0-4]

R104

5-18

(4-C, 6-E)

3.0V

10K

CONT1

5-12 (2-F)

5-19 (8-G)

RXD

CD

CTS

VINT

R113

10K

R191

10K

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 5 SCHEMATIC DIAGRAM (5/24)

()()()

ADP

RXD

TXD

RTS

CTS

CONT2

ADP

RXD

TXD

RTS

CTS

CONT2

CD

CD

JTAGEN

TCK

TMS

TDI

TDO

45

6

5 – 10

Page 6

CONFIDENTIAL

T

_

D102

GX20

1SS388

VBAT_AP

VIB_CNT

5-8 (6-D)

D103

1SS388

VBAT_AP

R172

1

R173

1

R182

2.2

DATA[7]

DATA[6]

DATA[5]

DATA[4]

DATA[3]

DATA[2]

C144

0.047

R124

27K

C132

10

17

18

19

20

21

22

23

24

25

C135

SPOUT1

SPOUT2

EXT2

D7

D6

D5

D4

D3

D2

C136

220P

(CH)

R122

0.1

14

15

16

EQ3

SPVSS

SPVDD

IC103

YMU759B

SOUND

D1D0/WR

28 29

27

26

DATA[1]

DATA[0]

R123

C137

68K

EQ2

EQ1

HPOUT-R

SDIN(/CS)

SYNC(A0)

SCLK(/RD)

31

30

18K

0.047

NC

10111213

VREF

HPOUT-L/MONO

PLLC

IFSEL

EXT1

CLK1

SDOUT

32

VSS

VDD

/RST

/IRQ

NC

5-18 (4-G)

VINT

C141

4.7

C142

0.1

C143

9

8

7

6

5

4

3

2

1

C145

0.1

C146

0.001

R128

3.3K

R143

470K

0.1

1.8

VCORE

5-19 (7-E)

C151

0.1

C153

0.1

1.8V

C150

0.1

C152

0.1

VR

3.0V

VINT

R188

470K

( ) : Not Mount

78 9

Figure 6 SCHEMATIC DIAGRAM (6/24)

SIMIO

SIMCLK

SIMRST

SIMEN

KEYPADROW[0]

KEYPADROW[1]

KEYPADROW[2]

KEYPADROW[3]

KEYPADROW[4]

KEYPADCOL[0]

KEYPADCOL[1]

KEYPADCOL[2]

KEYPADCOL[3]

KEYPADCOL[4]

3.0V

VINT

ADP

RXD

TXD

CD

RTS

CTS

CONT2

JTAGEN

TCK

TMS

TDI

TDO

R193

10K

TP109

NC

NC

10 11

196

SIMDATAIO

177

SIMCLK

195

GPIO_23

197

GPIO_24

157

GPIO_47

40

KEYPADROW[0]

54

KEYPADROW[1]

16

KEYPADROW[2]

53

KEYPADROW[3]

15

KEYPADROW[4]

KEYPADCOL[0]

14

KEYPADCOL[1]

33

KEYPADCOL[2]

32

KEYPADCOL[3]

13

KEYPADCOL[4]

51

GPIO_55

12

GPIO_56

148

USC[0]

146

USC[1]

133

USC[2]

145

USC[3]

134

USC[4]

125

USC[5]

131

USC[6]

178

JTAGEN

122

GPIO_18

198

GPIO_19

158

GPIO_20

199

GPIO_21

MC_CLK

50

MC

CMD

31

6267829798

120

VCC

VCC

VCC

VCC

VCC

[SIM RESET]

[SIM ENABLE]

[Camera RESET]

[Boot Control 1]

[Boot Control 0]

[External Connector 15pin]

[External Connector 6pin]

[External Connector 7pin]

[External Connector 9pin]

[External Connector 2pin]

[External Connector 10pin]

[External Connector 13pin]

[TCK]

[TMS]

[TDI]

[TDO]

12

130

VCC

132

VCC

160

VCC

8

VDDRTC

5 – 11

Page 7

GX20

F

TCK

T

P

D

M

E

A

MAIN PWB-A (2/3)

11

12

13

14

15

16

NC

17

NC

18

19

20

(

CONFIDENTIAL

TMS

TDI

TDO

B

5-18 (4-G)

5-18 (5-H)

5-18 (3-C)

5-18 (4-D)

5-18 (3-C)

C

5-18 (4-C)

5-18 (3-G)

5-18 (4-G)

5-18 (4-F)

G

G

G

G

G

G

G

G

TCXOOUT

G

G

G

G

G

G

G

G

G

5-18 (3-F)

MIC_INN_R

D

5-9 (8-F)

G

5-9 (9-F)

G

E

RECIVER_OUTP_REC

RECIVER_OUTN_REC

5-18 (4-G)

5-18 (4-F)

5-18 (4-D)

5-10 (2-E)

5-14 (6-F)

F

5-19 (8-A)

ADC_MTC

G

BS2

BS0

BS1

SYNTHDATA

SYNTHEN

SYNTHCLK

ITXP

ITXN

QTXP

QTXN

IRXP

IRXN

QRXP

QRXN

AFCDAC

RAMPDAC

5-18 (4-F)

MIC_INP_R

G

TP167

TP168

JAKMIC

JAKEAR

JAKDET

VINT

R195

R196

G

3.0V

620K

68K

C101

47P(CH)

L103

FERRITE BEADS

L104

FERRITE BEADS

D105

RSB6.8S

G

G

G

R197

120K

C198

1

5-19 (10-C)

2.45V

C102

47P(CH)

C103

0.1

C199

0.1

1

IN(+)

Vdd

2

Vss

Out

3

IN(-)

IC107

TC75S55E

ORE ANP.

VAN A

Q101

EMD9

2.46V 0V

5

2.44V

6

C182

47P

(CH)

D106

RSB6.8S

TP106

C104

TP107

10

3.0V

VINT

5

4

ADC_MTC

34

2

1

0V

0V

C183

47P(CH)

R106

470

VAMP

L102

FERRITE

BEADS

C107

0.1

NC

VANA_AD6521

RECIVER_OUTP

RECIVER_OUTN

5-19 (10-G)

C105

4.7

C110

0.0022

5

Vout1

6

V+

7

GND

8

Vout2

IC101

NJM2149R

SPEAKER AMP.

-Vin

+Vin

Vref

CD

R115

10K

4

3

2

1

C108

10

R116

10K

R118

10K

C112

47P(CH)

C124

0.1

C109

0.1

C125

0.1

R199

33K

C123

1

R107

R108

C115

1

3.3K

4.7K

IT

IT

Q

Q

IR

IR

Q

C127

47P(CH)

R112

2.2K

L107

C116

47P(CH)

L108

L105

FERRITE BEA

L106

FERRITE

BEADS

()

C188

FER

FER

BEA

C11

33

BA

0.01

Q

A

R

C

0.

C118

C126

47P(CH)

R109

1.5K

R110

3.3K

C114

R111

4.7K

47P

(CH)

C111

0.001

C113

0.001

C186

0.1

R184

470K

G

G

5-18 (4-C)

5-19 (11-B)

BATT_SENSE

G

MVBAT

G

5-19 (11-C)

ADIN_B

5-18 (3-E)

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 7 SCHEMATIC DIAGRAM (7/24)

5 – 12

45

C168

6

R149

470

V

3

0.1

2

G

1

N

NC

IC

L

TE

S

Page 8

N

2

4

8

8

2

0

2

4

6

8

6

0

4

0

9

VINT

TDO

C127

47P(CH)

L107

FERRITE BEADS

116

7P(CH)

L108

FERRITE

BEADS

5

RITE BEADS

L106

FERRITE

BEADS

C117

33P(CH)

BATT_SENSE

C188

0.01

()

ITXP

ITXN

QTXP

QTXN

IRXP

IRXN

QRXP

QRXN

AFCDAC

RAMPDAC

C129

C119

0.1

47P(CH)

C120

47P(CH)

C130

0.1

L110

33nH

C118

0.01

R188

470K

5-19 (7-E)

2.8V

VMEM

C131

0.1

C128

C181

47P(CH)

35

ITXP

31

ITXN

27

QTXP

23

QTXN

32

IRXP

28

IRXN

24

QRXP

20

QRXN

10

AFCDAC

43

RAMPDAC

54

VINNORP

64

VINNORN

62

VOUTNORP

61

VOUTNORN

C121

47P(CH)

44

VINAUXP

40

VINAUXN

63

VOUTAUXP

60

VOUTAUXN MCLKEN

()

6

AUXADC1

5

AUXADC2

15

AUXADC3

4

AUXADC4

16

AUXADC5

17

AUXADC6

()

TP171

TP175

0.1

C176

1

9

36

AVDD1

AVDD2

52

AVDD3

37

DVDD2

IC102

AD6521ACA

ANALOG BASEBAND

4

5

3

2

6

3

2

6

5124

13

16

15

14

22

26

30

TOP VIEW

34

38

42

49

47

48

46

50

58

59

5655

60

57

AUXADC1: JACK Detect

AUXADC2: Temperature

AUXADC3: Main Battery sence

AUXADC4: Main Battery voltage

AUXADC5: Battery Temperature

AUXADC6:

AGND4

AGND2

AGND1

AGND3

2

13

18

51

C200

A

B

C

D

E

F

G

H

J

K

0.001

1

1

11

21

25

29

33

37

41

45

39

R177

100K

7

17

51

61

DGND1

DGND3

49

1.8V

1

DVDD1

10

8

9

87

10

9

20

19

18

24

23

27

28

32

31

36

35

40

39

44

43

52

54

53

62

64

63

NC(REFCAP2)

NC(MICCAP)

19

53

NC

NC

VCORE

C133

0.1

59

DVDD3

IDACOUT

IDACREF

CONFIDENTIAL

C134

0.1

TP103

21

TCK

22

TMS

TDI

TDO

RXON

TXON

ARSM

ATS M

ASDI

ASFS

ASDO

BSDI

BSIFS

BSDO

BSOFS

VSDI

VSDO

VSFS

RESET

MCLK

BUZZER

PEFOUT

REFCAP

TP104

12

TP105

11

TP108

48

58

47

57

41

42

45

38

34

33

30

29

25

26

55

56

46

C138

C140

50

7

8

14

3

0.001

0.1

NC

NC

C139

NC

1

C148

100P

L109

FERRITE

13M_CLK

TCXOEN

PWRON

21

(CH)

BEADS

R193

TXON

BS2

CAM_ON

RFON

BS0

BS1

SYNTHEN

SYNTHDATA

SYNTHCLK

()

C191

0.001

23

10K

22

NC

NC

NC

NC

NC

NC

NC

NC

NC

TP123

TP122

R132

20M

R147

10M

C149

2P(CH)

199

GPIO_21

97

MC_CLK

50

MC_CMD

10

MC_DAT[0]

64

MC_DAT[1]

29

MC_DAT[2]

85

MC_DAT[3]

11

GPIO_22

176

DPLUS

121

DMINUS

27

GPO_00

48

GPO_01

200

GPO_02

180

GPO_03

181

GPO_04

7

GPO_05

26

GPO_06

182

GPO_07

202

GPO_08

203

GPO_09

204

GPO_10

167

GPO_11

183

GPO_16

184

GPO_17

161

GPO_18

186

GPO_19

168

GPO_20

162

GPO_21

46

CSDO

96

CSFS

25

CSDI

24

BSDO

3

BSOFS

2

BSDI

23

BSIFS

1

ASDO

19

ASDI

22

ASFS

6

GPO_29

47

CLKOUT_GATE

84

CLKOUT

4

GPIO_48

142

CLKIN

159

CLKON

63

PWRON

189

nRESET

49

OSCIN

28

OSCOUT

4

1

2

3

X102

32kHz

DGND SHIELD

GX20

[TDO]

[Not use]

[RXON]

[TXON]

[BS2]

[ADC_MTC]

[Not use]

[ARSM]

[ATSM]

[CAMERA Power on/off]

[IrDA Power on/off]

[RFON]

[BUFOFF]

[External AMP]

[BS0]

[BS1]

[SYNTHEN]

[LED Bright Control = Charge LED]

[SYNTHDATA]

[SYNTHCLK]

[13MHz Output]

NC

NC

GND

39

GND

52

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

GND

61

1

1

19

21

37

43

57

71

79

91

103

115

127

135

149

163

169

185

187

GND

65

2

3

3

2

2

3

4

5

7

8

9

10

11

12

13

15

16

17

18

188

GND

GND

81

86

149

70

C

5-18 (4-E)

V+

VO

3

4

2

GND

GND

1

5

NC

IC105

LM20BIM7

TEMPERATURE

SENSOR

( ) : Not Mount

2.715V

VT

C169

5-18 (3-D)

5-9 (12-F)

5-18 (4-D)

5-19 (7-B)

0.1

5-18 (6-B)

5-19 (11-C)

5-18 (6-F)

5-19 (11-E)

PWRON

5-18 (6-B)

5-19 (10-C)

5-18 (6-B)

CAM_ON

5-19 (8-H)

/RESET

TXON

SIMEN

EOC

G

G

G

G

G

G

G

G

G

G

RFON

TCXOEN

CHRDET

CHGEN

AMP_ON

G

The numbers

78 9

Figure 8 SCHEMATIC DIAGRAM (8/24)

TXON

RFON

PWRON

TCXOEN

SIMEN

CHRDET

EOC

CHGEN

CAM_ON

AMP_ON

/RESET

21to23

are waveform numbers shown in page 5-4.

10 11

12

5 – 13

Page 9

GX20

O

i

i

i

CONFIDENTIAL

MAIN PWB-A (2/3)

A

B

C

5-18

(4-G)

1.8V

2.85V

VSIM

C154

3.0V

VINT

C156

0.1

0.1

C155

0.1

C157

0.1

C159

0.1

C158

0.1

3.0V

C160

0.1

VINT

C161

0.1

C163

0.1

C162

0.1

D

VRTC

2.8V

VMEM

()

C164

3.0V

VINT

()

0.1

3.0V

VINT

()

5-18 (3-D)

FLIP_SW

G

()

DATA[0-15]

5-9

(12-F)

LEDR

5-9

5-18

(11-F)

(3-G)

KEY_BL_ON

LEDG

G

G

G

5-1

8

IR_

ADD[1]

ADD[19]

ADD[18]

ADD[17]

ADD[1]

ADD[2]

8

44

79

143

160

E

132

VCC

VCC

F

VSIM

VMEM

VDDRTC

VMEM

IC104

128

VMEM

170

VMEM

173

VMEM

41

VEXT

66

VEXT

68

110

VEXT

[Hardware revision monitor_0]

AD6529

DIGITAL BASEBAND

[Hardware revision monitor_1]

[Hardware revision monitor_2]

n]

]

]

G

]

]

n]

n]

H

[LCD controller RESET, Sub LCD RESET, Camera Power on]

[Camera Controller Interrupt]

[External Connector 12pin]

[External Connector 14pin]

[External Connector 16pin]

5

166

179

VINT

VEXT

VEXT

VEXT

[ADP3408 CHGEN]

[AMP Power on/off]

[Sub Backlight on]

[Not use]

[ADP3408 CHRDET]

[Not use]

[Genie Rx]

[ADP3408 EOC]

[Flip Switch Detection]

[Keypad Backlight on/off]

[LCD controller Interrupt]

[Genie Tx]

[Flash WP]

[Sound IC RESET]

[Sound IC Interrupt]

[Flash VPP]

[Not use]

[Flash_Memory_1 /CS]

[PSRAM /CS]

[SRAM /CS]

[Flash_Memory_2 /CS]

[Not use]

[LCD Controller /CS]

[Camera /CS]

194

VDDUSB

30

GPIO_00

VMC

GPIO_01

GPIO_02

GPIO_03

GPIO_04

GPIO_05

GPIO_06

GPIO_07

GPIO_08

GPIO_09

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_33

GPIO_34

GPIO_35

GPIO_36

GPIO_37

GPIO_38

GPIO_39

GPO_22

GPO_23

nROMCS1

nRAMCS1

nRAMCS2

nGPCS1

nAUXCS1

GPIO_42

GPIO_43

GPIO_44

126

124

113

114

112

101

102

89

100

90

77

99

78

88

76

69

70

56

55

36

20

18

35

17

34

75

42

140

191

154

172

192

141

193

155

[IrDA Tx]

[IrDA Rx]

NC

TP128

NC

TP147

TP148

TP149

TP150

TP151

CHGEN

AMP_ON

CHRDET

EOC

ADD[1-22]

5-12 (2-F)

5-17 (8-C)

3.0V

VINT

()

()

()

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 9 SCHEMATIC DIAGRAM (9/24)

45

6

5 – 14

Page 10

5-18 (6-D)

IR_ON

G

R150

470K

IR_SD

5-18 (6-D)

CONFIDENTIAL

5-19 (10-D)

3.0V

VINT

VIR

UN101

INFRARED PORT

7

SGND

LEDA

6

5

TXD

4

G

C170

4.7

RXD

3

SD

2

GND

Vcc

1

GX20

()

()

5-19 (10-D)

C192

1

DATA[0-15]

DATA[15]

DATA[13]

DATA[11]

DATA[9]

DATA[14]

DATA[12]

DATA[10]

DATA[8]

DATA[7]

DATA[5]

DATA[3]

DATA[1]

DATA[6]

DATA[4]

DATA[2]

DATA[0]

2.5V

VCCD

R162

0

R160

0

C194

1

3.0V

VINT

R161

0

R158

0

R157

0

5-19 (9-F)

3.1V

VCAM

C196

1

5-9 (7-B) 5-9 (7-C)

C177

1

+13V

-7V

C184

1

() ()

()

CN101

1234567891011121314151617181920212223242526272829303132333435

GND

A1

AVDD(3.1V)

A17

-7V

A18

A19

VDD1(2.5V)

A2

+13V

CLK

VDD2(3.0V)

RESET

CINT

RD

CS

WR

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

GND

GND

( ) : Not Mount

78 9

Figure 10 SCHEMATIC DIAGRAM (10/24)

5 – 15

R192

470K

5-8 (5-F)

CAMCLK

G

PWM_CPU

G

5-9 (8-D)

5-8 (4-F)

/LCD_RESET

G

G

G

/LCD_CS

5-8 (4-F)

5-8 (4-F)

LCD_INT

10 11

to LCD Curcuit

G

G

TP177

13M_CLK

5-8 (5-F)

5-8 (6-G)

SUB_BL_ON

12

Page 11

GX20

A16

SC

/CE1

13

60

TP128

A

B

C

D

E

F

MAIN PWB-A (2/3)

arge LED]

1

3

2

3

1

A

19

B

21

C

38

37

D

44 54

43

E

58

57

F

G

79

H

91

J

104 111105

103

K

116 123117

115

L

127

M

135

N

149

P

163

164 168167

R

169

170 179177 181 184183180176174 178171 182

T

185

U

187

189 196194 202192190

V

GND

GND

GND

GND

61

65

818386

TOP VIEW

9

10

8

5

7

26

47

61

GND

111

8

9

27

49

48 50

63

62

95 96

107 108

119 120

140 141

175172 173

GND

123

GND

129

11 12 13 14 15 16 17 18

11

107

30628

29

51 56

64

65 68 69 7066 67

9794 9892 9993

109

110

121

122

GND

GND

137

144

6

5

413

25

23

2422

39

45

46

60

59

106

118

GND

GND

GND

87

107

109

CONFIDENTIAL

192

nAUXCS1

[Not use]

[Not use]

[Not use]

[/UBS]

[/LBS]

[Not use]

[Not use]

GPIO_42

GPIO_43

GPIO_44

GPIO_45

GPIO_46

nRD

nWE

nHWR

nLWR

nWAIT

nADV

BURSTCLK

DATA[0]

DATA[1]

DATA[2]

DATA[3]

DATA[4]

DATA[5]

DATA[6]

DATA[7]

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

ADD[0]

ADD[1]

ADD[2]

ADD[3]

ADD[4]

ADD[5]

ADD[6]

ADD[7]

ADD[8]

ADD[9]

ADD[10]

ADD[11]

ADD[12]

ADD[13]

ADD[14]

ADD[15]

ADD[16]

ADD[17]

ADD[18]

ADD[19]

ADD[20]

ADD[21]

ADD[22]

ADD[23]

GPIO_40

[LCD Controller /CS]

[Camera /CS]

[Sound_IC /CS]

[LCD Controller /Wait]

12

31

52

GND

147

17

18

142

16

15

20

33

32

35436

34

42

40

41

53

55

777178767472 7573

8983 84

90888582 8680 8781

101

102100

113

11411 2

125

126124

133

134132130128 131129

147

148

146142138 143136 145139137 144

162

161154 155

160156152 157150 159153151 158

166165

186

204

200191 195 199193

203188 198 201197

VSSRTC

GND

153

GND

201

VSSUSB

9

156

TP151

141

193

155

NC

174

NC

TP130

175

151

165

185

187

188

171

190

116

118

115

119

127

117

136

135

150

138

149

164

163

139

152

169

21

45

38

60

37

59

74

43

73

58

57

72

71

80

94

95

92

93

91

106

104

103

108

105

NC

NC

TP129

R178

100

TP152

TP153

TP156

TP160

TP162

TP172

R171

100

DATA[0]

DATA[1]

DATA[2]

DATA[3]

DATA[4]

DATA[5]

DATA[6]

DATA[7]

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

ADD[1]

ADD[2]

ADD[3]

ADD[4]

ADD[5]

ADD[6]

ADD[7]

ADD[8]

ADD[9]

ADD[10]

ADD[11]

ADD[12]

ADD[13]

ADD[14]

ADD[15]

ADD[16]

ADD[17]

ADD[18]

ADD[19]

ADD[20]

ADD[21]

ADD[22]

ADD[1]

ADD[2]

ADD[3]

ADD[4]

ADD[5]

ADD[6]

ADD[7]

ADD[8]

ADD[9]

ADD[10]

ADD[11]

ADD[12]

ADD[13]

ADD[14]

ADD[15]

ADD[16]

ADD[17]

ADD[18]

ADD[19]

ADD[20]

ADD[21]

ADD[22]

R187

470K

()

66

A0

59

A1

-

58

A2

A3

57

65

A4

64

A5

56

A6

55

A7

14

A8

16

A9

15

A10

4

A11

8

A12

7

A13

6

A14

5

A15

G

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 11 SCHEMATIC DIAGRAM (11/24)

5 – 16

45

6

Page 12

GX20

to LCD Curcuit

3.0VV

5-14

(6-F)

3.0V

VINT

VINT

()

5-18

(6-B)

3.0V

VBACK

CONFIDENTIAL

DATA[0-15]

DATA [0-15]

TP176

G

G

5-8 (4-F)

5-8 (4-F)

/LCD_WAIT

/LCD_CS

5-8 (4-F)

G

/WE

DATA[0-15]

G

BUFOFF

LCD_RST

/RD

G

G

G

5-8 (4-F)

5-8 (5-F)

5-8 (4-F)

5-8 (3-F)

G

SUB_BL_ON

IC106

LRS1B24

C173

20191413 1615 1817

28272221 2423 2625

36353029 3231 3433

44433837 4039 4241

52514645 4847 5049

60595453 5655 5857

70696463 6665 686761 62 71 72

0.1

41

F/SC-Vcc

61

62

35

S-Vcc

NC

71

F-/OE

GND

9

21

F-/WE

GND

F-/WP

GND

29

TP137

22

63

70

30

/RST

F2-CE

S-/CE1

RY/-BY

NCNCNCNCNCNCNC

1

2

101112

NC

()

18

34

454647

60

66

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

CE2

SC-/CE1

S-A17

A16

24

13

59

58

57

65

64

56

55

14

16

15

4

8

7

6

5

676869

/LB

/UB

S-/OE

S-/WE

F1-/CE

123456789101112

123456789101112

A

B

C

D

E

F

G

H

F-A19

A21

A20

A18

F-A17

3

23

39

53

54

4-LEVEL

C174

0.1

C175

0.1

STACK MEMORY

363738

F-Vpp

F/SC-Vcc

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

T3

NC

T1

T2

48

72

31

32

NC

NC

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

51

52

43

44

27

28

26

20

50

49

42

40

33

25

19

17

DATA[0]

DATA[1]

DATA[2]

DATA[3]

DATA[4]

DATA[5]

DATA[6]

DATA[7]

DATA[8]

DATA[9]

DATA[10]

DATA[11]

DATA[12]

DATA[13]

DATA[14]

DATA[15]

()

TP139

TP138

TP140

TP141

TP142

GND

VDD1

A19

A18

( ) : Not Mount

78 9

Figure 12 SCHEMATIC DIAGRAM (12/24)

A17

A2

A1

5 – 17

GND

OD15

OD9

OD8

OD7

OD11

OD14

OD13

OD12

OD10

10 11

CA1001

CAMERA UNIT

OD6

OD5

OD4

OD3

OD2

OD1

OD0

GND

CTL3

MODE

CTL2

+13V

TEST4

Ð7V

AVDD

GND

CINT

CBREQ

RSTN

RDB

12

WRB

CSB

PWCK

424140393837363534333231302928272625242322212019181716151413121110987654321

VDD2

EXCK1

Page 13

GX20

P

1

5

5

CONFIDENTIAL

VBAT_BB

G

G

G

G

G

G

G

QTXP

G

TXON

G

G

G

G

G

5-13 (7-G)

KEYPADROW[2]

KEYPADROW[0]

KEYPADROW[1]

KEYPADROW[3]

KEYPADROW[4]

KEYPADCOL[1]

KEYPADCOL[2]

KEYPADCOL[3]

KEYPADCOL[4]

G

G

G

BS1

G

BACK_BATT

C202

G

G

G

G

G

G

G

G

G

G

G

G

G

G

1

IC201

XC6209B302MR

HIGH SPEED LDO

REGULATOR

Vout

5

1

Vin

2

Vss

4

NC

BATT_SENSE

ADPDET

CONT1

IRXN

QRXP

RFON

5-13 (9-G)

RTS

5-10 (2-F)

5-10 (2-F)

RXD

5-10 (6-A)

JAKDET

5-14 (4-A)

CTS

5-10 (2-F)

CD

5-12 (2-G)

MIC_INP_R

JAKEAR

TCXOOUT

JAKMIC

SIMRST

SIMCLK

RAMPDAC

BS2

BS0

NC

5-9 (9-E)

5-12 (2-G)

5-10 (2-F)

5-10 (2-F)

G

IRXP

G

G

G

QRXN

5-10 (2-F)

5-12 (2-E)

5-10 (2-G)

5-10 (2-F)

KEYPADCOL[0-4],

KEYPADROW[0-4]

100P(CH)

5-12 (2-D)

5-12 (2-E)

D202

RSB6.8S

5-12 (1-D)

5-12 (2-E)

5-12 (2-E)

VINT

VSIM

5-12 (1-C)

5-12 (2-B)

C241

47P(CH)

CE

3

LEDB_M

LEDG_M

VPLUS2

G

G

G

QTXN

ITXN

G

G

G

G

VT

POWONKEY

VBAT_BB

CHGIN

TP202

C204

1

5-12

(1-C)

V201

650P

C236

100P(CH)

C238

5-11 (10-A)

5-14 (1-D)

C242

33P

(CH)

2

1

OUT

VDD

NC

Vss

34

NC

VEXT_CN

V203

650P

C237

100P(CH)

C239

100P(CH)

C240

100P(CH)

D201

RSB6.8S

G

SYNTHDATA

G

G

SYNTHEN

C243

47P

(CH)

R204

IC204

R3111Q251C

VOLTAGE

DETECTOR

C246

100P

(CH)

TP217

5-10

G

(1-E)

SYNTHCLK

470K

SP1-1

SP2-1

5-12 (1-B)

3

P-G

P-D

4

G

5-13 (9-G)

A

MAIN PWB-A(3/3)

RECEPTION SIGNAL

TRANSMISSION SIGNAL

SPEAKER SIGNAL

RELAY FPC_A

PWB-C

LEDB

B

3

4

2

5

1

6

LED405

GM56271A

MOBILE

LIGHT

C

5-23 (11-B)

SP1

b

SP2

D

E

5-27 (10-A)

5-29 (10-G)

CN305

CN306

F

a

RELAY FPC_B PWB-D

1

BACK-UP

BATTERY

HOLDER

2

BAT100

BACK-UP

BATTERY

5-24 (1-E)

G

H

VBAT_AP

LEDR

VPLUS2

CN405

BACK_BATT

LEDG

DGND

GATEDR

VBAT_AP

VBAT_AP

VBAT_AP

VBAT_S

BATT_SENSE

ADP

ADPDET

CONT2

CONT1

IRXN

IRXP

QRXP

QRXN

QTXP

QTXN

ITXP

ITXN

ISENSE

DGND

TCXOEN

RFON

TXON

RTS

VEXT_ON

GENIE_CHG

RXD

VIB_CNT

JAKDET

FLIP_SW

CTS

TXD

CD(RS232C)

ADIN_B

POWONKEY

SP2

SP2

SP1

CN202

VBAT_BB

VBAT_BB

KEYPADROW2

KEYPADROW0

KEYPADROW1

KEYPADROW3

KEYPADROW4

AGND

MIC

MIC_GND

JAKEAR

KEYPADCOL0

KEYPADCOL1

KEYPADCOL2

KEYPADCOL3

KEYPADCOL4

DGND

TCXOOUT

DGND

JAKMIC

DGND

DGND

SIMRST

SIMIO

SIMCLK

VINT

VSIM

AFCDAC

RAMPDAC

KEY_BL_ON

BS2

BS1

BS0

SYNTHDATA

SYNTHCLK

SYNTHEN

CHGIN

DGND

VT

NC

CN201

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

GENIE_CHG

32

33

34

35

36

37

38

39

40

41

42

43

44

45

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

NC

40

5-8 (6-D)

VBAT_AP

LEDR_M

CONT2

5-9 (12-F)

5-13 (9-G)

G

VIB_CNT

FLIP_SW

TXD

ADIN_B

MIC_INN_R

AFCDAC

KEY_BL_ON

5-14 (5-A)

G

5-10 (2-F)

ADP

5-10

(2-G)

ITXP

KEYPADCOL[0]

SIMIO

5-12 (2-C)

2

P-S

N-S

5

G

3V3V0V

0V0V3V

1

N-G

N-D

6

Q201

SP1-1

SP2-1

5-15 (8-B)

5-15 (7-B)

5-10 (2-F)

5-13 (9-H)

5-17 (8-C)

R208

470K

FDC6322 C

BACK_BATT

SIMEN

CHGEN

IR_ON

ADPDET

CAM_ON

3.0V

VBACK

R214

G

5-13 (9-G)

TCXOEN

5-10 (6-B)

G

G

CHGIN

IR_SD

G

G

TP203

1

GND

7.5K

VDD

2

VO

C212

1

G

5-

CHGEN

G

G

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 13 SCHEMATIC DIAGRAM (13/24)

5 – 18

45

6

Page 14

C212

P203

)

GEN

1

GND

VDD

2

1

4

CE

3

VOUT

C219

5-13 (9-G)

PWRON

G

5-11 (12-D)

VCORE

VMEM

5-13 (8-B)

SIMEN

CHGIN

IC203

RQ5RW18B

1.8V REGULATOR

1.8V

TP205

C245

4.7

4.7

()

C232

0.1

ADPDET

()

5-10 (2-E)

5-13 (9-H)

AMP_ON

PWRONIN

C233

PWRONKEY

3.0V

VINT

PWRON

TCXOEN

CAM_ON

1.8V

2.8V

G

5-12 (1-F)

C210

10

0.1

()

G

ADC_MTC

C234

0.0047

C211

C205

C214

1

VBAT_BB

29

28

1

8

14

30

0.1

9

4

12

7

CHRIN

C213

1

AMP_ON

Q203

RT1N144 U

VBAT_BB

()

C216

TCXOEN

SIMEN

GATEIN

CHGEN

GATEDR

BATSNS

ISENSE

1

1

2

3

()

C215

0.1

()

C217

0.1

0V

0V

10

1

2

3

4

5

6

7

8

AGND

27

Vdd

GND

CE

C235

()

R211

68K

2.46V

23

R212

10K

2.44V

1

()

C220

0.1

2

19

22

MVBAT

CHRDET

VBAT

VBAT2

EOC

VRTCIN

ROWX

RESET

323130

25

28

26

24

23

27

29

22

TOP

21

20

VIEW

19

18

10

14

12

17

9

11

16

13

15

VAN

VTCXO

VMEM

VRTC

REFOUT

DGND

NC

NC

NC

DGND

11

10

17

24

32

NCNCNC

NC

Vin

1

5

Vout

2

Vss

4

CE

3

NC

NC

IC208

XC6209B252MR

C244

0.001

HIGH SPEED

LDO REGULATOR

5

Vout

4

ECO

IC205

R1160N301B

REGURATOR

C222

5

4

IC206

Vin

Vout

TK11131C

GND

Cont

Np(Vref)

REGULATOR

3

2

1

C218

0.01

100P

(CH)

IC207

R116018B

REGULATOR

Vdd

5

1

Vout

GND

2

CE

4

3

ECO

4

5

Vin

Vout

GND

Cont

Np(Vref)

123

C206

0.01

CONFIDENTIAL

VAN A

2.44V0V

Q204

2SA1989 SR

R215

8.2K

()

IC202

ADP3408ACP

POWER SUPPLY

5

6

13

31

16

C224

0.1

15

RESCAP

VSIM

18

VCORE

21

23

25

VMEM_OUT

20

VRTC_NO

3

26

C225

0.1

C223

10

C221

1

R232

1

5-15 (11-C)

LM252

FERRITE BEADS

1

C208

1

R216

C207

1

IC209

TK11130C

REGULATOR

2.99V

3.1V

VCAM

1

C231

2.2

R218

330

C229

2.2

C228

0.22

C227

Q205

2SA1955 A

R219

KEYPADROW[4]

KEYPADROW[4]

C230

2.2

Q207

EMD6

2.81V

4.7

R222

1.2K

2.87V 0V

2.86V

470K

0.05V

2.51V

C247

0.1

R223

1

2

4

5

6

470K

Vdd

GND

IC210

R3112Q261A

VOLTAGE DETECTOR

TP206

VLCD

5-12 (4-E)

3.0V

VAM P

VAM P

Out

TP214

VSIM

VCORE

VAN A

VMEM

3

2

1

VEXT_CN

VINT

4

3

Cd

C226

0.01

5-6 (4-H)

1.8V

VLCD

G

5-13 (9-G)

G

CHRDET

/RESET

G

2.85V

1.8V

2.45V

2.715V

VT

2.8V

2.8V

VIR

0V

2.5V

VCCD

2.5V

3.0V

VINT

TP213

TP218

5-12 (2-G)

BATT_SENSE

G

G

TP207

5-12 (3-B)

TP208

TP215

TP209

5-15 (8-A)

TP216

5-15 (10-C)

TP211

TP212

MVBAT

EOC

R227

1K

5-12 (1-G)

5-13 (9-G)

2.80V

VMEM

2.81V

3V

2.86V

NAME

VBAT

VSIM

VCORE

VAN A

VT

VMEM

VIR

VLCD

VEXT_CN

VINT

VINT_SW

VBACK

VRTC

VCAM

VTXVCO

VRF

VSYNTH

VTCXO

VCCD 2.5V

VAMP 3.0V

5-13 (9-H)

/RESET

G

Q208

EMD12

4

5

6

3

2

1

VOLTAGE

VBAT

2.85V

1.8V

2.45V

2.715V

2.8V

2.8V

1.8V

2.5V

3.0V

3.0V

3.0V

2.5V

3.1V

2.9V

2.9V

2.9V

2.9V

GX20

SIMEN

G

0V

0V

()

0V

( ) : Not Mount

78 9

Figure 14 SCHEMATIC DIAGRAM (14/24)

5 – 19

10 11

12

Page 15

GX20

A

CONFIDENTIAL

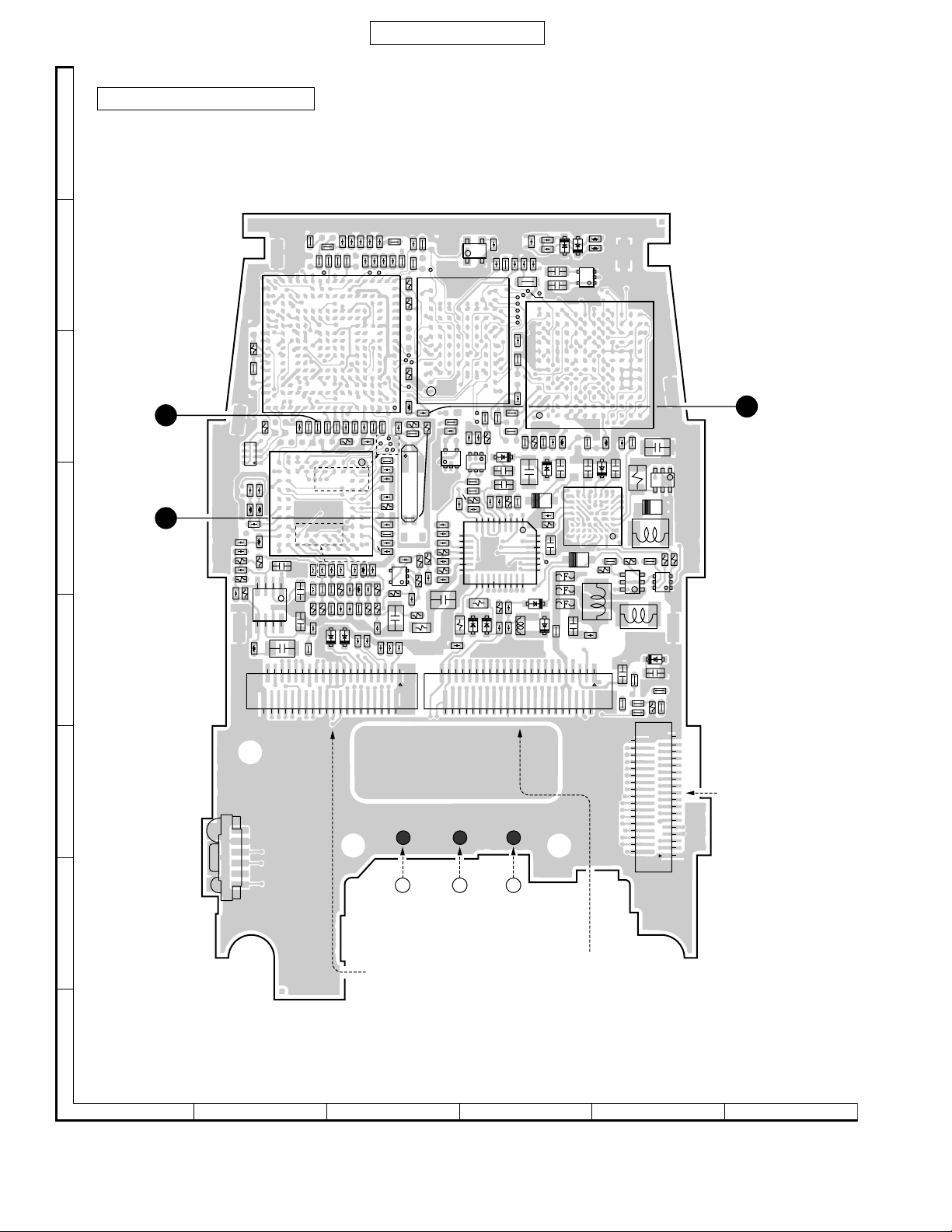

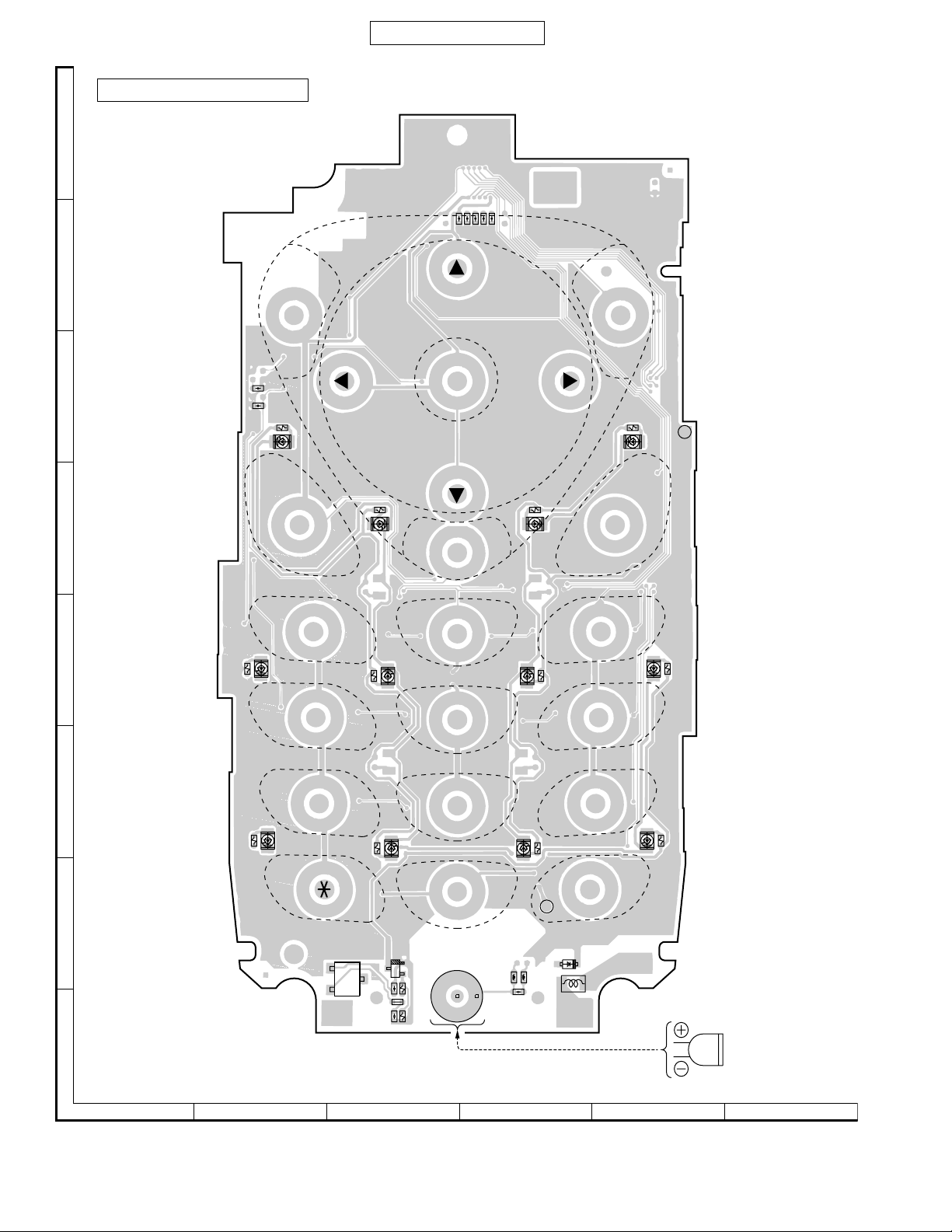

MAIN PWB-A (FRONT SIDE)

TP151

TP147

C416

L405

TP130

FS403

FS401

D413

C448

C414

C411

1020304044

D105

4

5

C462

IC403

C405

L103

D106

L104

C402

IC402

D410

FS402

C465

C466

2

3

IC405

1

L404

D401

C401

R440

C409

R437

6

IC404

L411

C404

34

30

20

10

2

R404

4

L401

C468

3

1

D402

C403

R192

D404

R405

Q402

CN101

L402

21

Q401

R403

35

25

5-34 (2-F)

FROM

15

CA1001

5

1

C155

C160

C161

C162

C163

C159

B

TP123 TP128 TP129

C157

C156

C158

R178

IC104

R188

C

22

C140

R113

R104

C114

C116

L107

D

23

C117

C125

R118

E

C120

L110

R116

C112

R199

4

IC101

C110

R115

58

L108

C115

C104

L102

R191

TP103

TP108

IC102

C127

C129

C119

C124

1

C123

C126

R110

C105

R111

C107

CN202

C154

C121

R112

C101

D201

TP162

TP156

L109

C164

R132

C149

C131

TP122

C118

TP104

C188

TP105

C186

R184

L106

C130

C138

C181

C139

C199

IC107

C113

L105

5

R108

C103

R197

C198

R107

C111

R109

C109

C236

C239

C237

D202

C238

C240

1

515253539 515253545 1

210203040

C191

R171

X102

34

1

C108

TP172

TP160

R187

IC406

R124

R195

C144

R196

R106

TP139

C148

C128

C137

C136

C132

R182

IC106

R147

C475

5

1

IC210

4

1

TP137

TP153

C133

C134

4

3

Q101

R128

C143

C146

10

C176

R123

15

16

R122

C135

17 25

R173

R172

V201

2

TP140

TP142

TP149

TP150

TP152

9

IC103

D102

3

C174

TP148

D407

C408

C145

C142

20

D103

C226

R177

R143

5

R438

V203

C175

C474

C406

C464

C463

CN201

C173

C415

R413

C141

1

30

D414

L410

C182

C102

C183

C417

D406

D405

R407

32

26

F

UN101

INFRARED

PORT

SOLDERSOLDERSOLDER

FROM RELAY

E

G

FPC_B

PWB-D

5-34 (4-B)

F

FROM

CA1001

5-34 (3-F)

FROM RELAY FPC_B

PWB-D

5-34 (4-A)

D

FROM RELAY

FPC_A

PWB-C

5-34 (1-B)

FROM RELAY FPC_A

PWB-C

5-34 (2-A)

H

12 3

45

6

Figure 15 WIRING SIDE OF P.W.BOARD (1/5)

5 – 20

Page 16

MAIN PWB-A (REAR SIDE)

25

26

24

TP414

TP406

TP407

TP405

TP416

TP415

TP208

TP411

TP215

TP410

TP412

FROM

BACK LIGHT FPC

ASS'Y PWB-F

5-34 (5-E)

TP424

C471

TP209

TP207

IC208

TP211

R219

TP212

TP168

TP426

TP428

TP429

C244

4

5

CN402

C230

C223

TP413

C413

TP167

14

3

TP217

Q205

C227

C229

1

TP422

C449

R433

C231

C213

TP419

R410

C247

CONFIDENTIAL

5-34 (5-F)

FROM

LCD100

TP420

TP418

10 20 30 40 50

2

1

51525

L407

L408

L448

L449

C224

R218

17

IC202

20

24

25

C228

C233

C232

L445

C425

C428

C426

C427

C424

C422

TP425

TP141

C469

L451

L450

R212

Q203

Q204

R215

101516

9

8

R227

5

C220

C225

1

32

30

35

C216

C234

C211

L446

CN401

34

TP421

CN404

C470

R211

Q208

13451

TP430

35

C472

C453

R216

C208

IC207

C205

L447

102030

TP138

45 55

C451

C450

C447

D409

D408

C221

IC205

51525

R232

C214

1

2

C454

R222

C452

45

34 5

C207

C200

C418

TP109

59

LM252

3

IC209

C421

R424

C423

60

C457

C455

R223

TP213

C218

3

C222

IC206

C246

C206

Q207

TP171

C419

C420

C235

45

1

C217

C458

5

IC201

1

C210

TP175

Q201

TP106

TP107

1

C461

C150

C243

C241

C215

4

1

R204

R208

C460

4

3

2

3

R214

R193

2

C219

D403

C459

C153

C151

C152

C242

C473

3

TP176

TP404

TP214

C204

TP218

C202

1

4

IC204

C212

TP203

IC203

TP205

C245

GX20

TP202

TP111

TP110

R160

R161

C194

R158

R162

R157

C184

C192

C196

C177

TP206

TP177

FROM

LCD001

5-34 (6-H)

The numbers

21to26

78 9

Figure 16 WIRING SIDE OF P.W.BOARD (2/5)

LED401

TP216

LED402

R150

IC105

4

5

R455

G

Q403

S

R454

R453

Q404

G

D

S

C169

3

1

R149

C168

C170

D

are waveform numbers shown in pages 5-4 ,5-5.

10 11

12

5 – 21

Page 17

GX20

F

CONFIDENTIAL

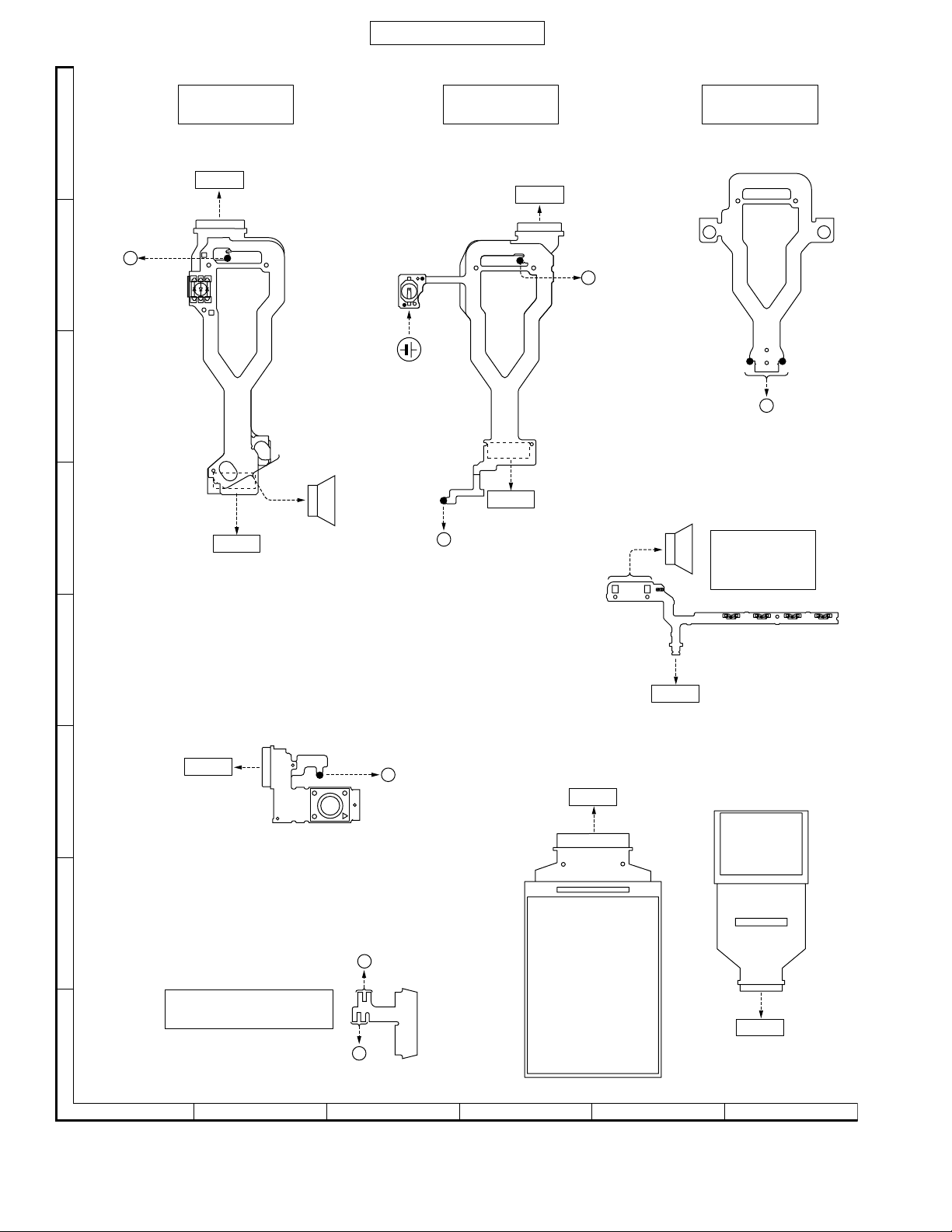

KEY PWB-B (1/2)

A

KEY PWB-B(1/2)

RECEPTION SIGNAL

FLEXIBLE PWB, SIDE SWITCH PWB-I

SIDE-DOWNSIDE-UP

TRANSMISSION SIGNAL

SPEAKER SIGNAL

B

TP328

TP329

TP330

TP344

C

V317

100P

CENTRE

D

RIGHT

UP

() () ()

1

V318

100P

D310

RSB6.8S

0

2

#

3

RIGHT SO

"VODAFONE

LIVE"

E

V321

100P

F

KEYPADCOL[0]

G

Down

PC

Printer

-

-

cable

-

Normal

Power(-)

(+)

17

8

Genie

load

--

H

---

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 17 SCHEMATIC DIAGRAM (15/24)

DOWN

LEFT

L305

KEYPADCOL[1]

5-27 (9-F)

VEXT_CN

4

7

C337

TP308

0.1

R310

KEYPADCOL[2]

5

8

KEYPADCOL[3]

V301

100P

45

6

9

()

SEND

LEFT SO

KEYPADCOL[4]

()

6

5 – 22

Page 18

KEYPADROW[0]

KEYPADROW0

KEYPADROW1

KEYPADROW2

CONFIDENTIAL

MO100

VIBRATOR

SP100

SPEAKER

KEYPADCOL2

1

4

7

On the FPC

SIDE-DOWN

0

2

5

8

CENTRE

RIGHT

DOWNKEYPADROW3

LEFT

On the FPC

SIDE-UP

KEYPADCOL3

#

3UP

6

9

TP451 and TP452 are

patterns for Vibrator.

KEYPADCOL4KEYPADCOL1KEYPADCOL0

RIGHT SOFT

"VODAFONE

LIVE"

SEND

LEFT SOFTKEYPADROW4

GOAST

NOTNOTNOT

NOT

NOT

NOT

END/

POWER

SP1

SP2

AGND

b

TP307

TP306

GX20

VVIB

DGND

5-18 (1-C)

TP305

RIGHT SOFT

"VODAFONE

LIVE"

SEND

LEFT SOFT

()

END/POWER

KEYPADROW[1]

KEYPADROW[2]

KEYPADROW[3]

KEYPADROW[4]

V313

100P

V314

100P

V315

100P

V316

100P

POWONKEY

CN303

BATTERY

CONTACT

BATT

SENSE

GND

5-30 (1-B)

BATT

G

1

2

3

()

TPB336

C338

0.1

TPB331

FS301

2.5A

T

T

Q306

RT1N144 U

23

0V 2.99V

0V

1

( ) : Not Mount

78 9

Figure 18 SCHEMATIC DIAGRAM (16/24)

5 – 23

GENIE_CHG

10 11

12

Page 19

GX20

0

0

A

B

C

D

KEY PWB-B (1/2)

CN302

EXTERNAL

CONNECTOR

RELAY FPC_C

PWB-E

-

-

-

-

Debug_Tx

-

-

-

Debug_Rx

-

GND

-

-

-

GND

-

5-26 (2-E)

5-29 (10-C)

CHGIN

TP347

TP348

-

-

-

-

"High"

-

TxD

TxD

-

-

RxD

RxD

-

-

-

-

-

-

-

-

--

CONT1

-

GND

-

-

-

-

-

-

GND

-

GND

---

-

-

COMMON MODE

4

Power(-)

-

FLashload_ON

Genie_CHG

TxD

-

RxD

ADPDET

"Low"

VCC

-

CONT2

-

AUX-OUT

DTR

CONT1

-

AUX-IN

-

RTS

CTS

GND

-

Power(+)

FL304

CONFIDENTIAL

17

FL303

FERRITE BEADS

L305

FERRITE BEADS

L306

FERRITE BEADS

L308

FERRITE BEADS

L309

FERRITE BEADS

L318

FERRITE BEADS

L316

FERRITE BEADS

L319

FERRITE BEADS

L313

FERRITE BEADS

L302

FERRITE BEADS

FL307

FERRITE BEADS

C353

0.1

(+)

TxD

ADP

RxD

VCC

GND

RTS

CTS

GND

CD

8

16

7

15

6

14

5

13

4

12

3

11

2

10

1

9

18

23

1

L307

FERRITE BEADS

D307

RSB6.8S

L310

FERRITE BEADS

L311

FERRITE BEADS

L312

FERRITE BEADS

R312

100

R314

100

R308

100

R309

100

R310

100

R316

100

R320

100

R321

100

R313

100

R315

100

R317

100

R319

100

V304

V305

15P

V319

100P

V307A

100P

15P

V301

100P

V302

V311

V303

15P

100P

100P

V308

15P

V306

V307

C328

100P

100P

1

V309

TP3

100P

0.9

5-18 (1-G)

E

a

JK301

HANDS FREE

CONNECTOR

V306A

TP301

100P

C304

47P(CH)

C335

C334

0.001

0.001

or 0.01

1

2

3

5

6

4

5-29 (9-C)

VSIM

2.85V

L303

FERRITE BEADS

L301

FERRITE BEADS

V320

100P

F

()

()

R363

1K

3

CLK I/O

2

RESET

1

Power

C303

0.1

CN301

SIM CARD

CONNECTOR

8

6

5

OP

4

GND

7

G

DGND

R305

20K

()

()

SIMIO

SIMCLK

SIMRST

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 19 SCHEMATIC DIAGRAM (17/24)

5 – 24

45

6

Page 20

CONFIDENTIAL

GX20

TP309

0.93V

R333

R334

470K

3.0V

VINT

470K

GENIE_CHG

ADPDET

CONT2

CONT1

R322

470K

RXD

RTS

CTS

TXD

TP311

1

2

3

TP313

TP314

TP315

Q301

UM6K1

23

0V

2.99V

0V

1

D301

HN2S01FU

1

NC

2

3

1

2

3

C316

0.1

6

5

4

1

2

3

4

VCC

GND

6

5

4

D302

HN2S01FU

6

5

4

8

7

6

5

NC

R332

470K

IC301

TC7WH04FK

ADP

LOGIC

CD

0V

0V

1

0V

2

3

Q302

UM6K1

0.01V

6

0V

5

0V

4

NC

1

NC

2

3

GND

VCC

5

4

IC308

TC7SZ04A

LOGIC

( ) : Not Mount

78 9

Figure 20 SCHEMATIC DIAGRAM (18/24)

5 – 25

10 11

TP322

TP323

MIC100

MICROPHONE

12

Page 21

GX20

A

CONFIDENTIAL

KEY PWB-B (1/2)

IC302

NJM2871F03

B

C

3.0V REGULATOR

1

CONT

GND

2

NB

VOUT

3

C340

0.1

D304

()

1SS388

VIN

D

VBAT

5

C342

0.1

4

C341

1

R325

1.2K

C330

R326

1

R327

68K

10K

HIGH SPEED LDO

1.67V

C321

1.68V

5-24 (2-C)

CHGIN

0.01

1.36V

E

TP321

TP320

()

VBAT

R335

1K

LED301

YPY1105C

Q303

2SC4617 R

0V

0V

Vin

1

Vout

Vss

2

ON/OFF

3

IC306

TK71635S

REGULATOR

1

2

3

Q305

CPH6311

R345

1.5K

R346

R338

820

R337

1.5K

R336

820

LED304

LED303

2.2

0.01

R348

0.18

(1/2W)

YPY1105C

D309

CUS01

D306

CUS01

D303

RB160M30

YPY1105C

VBAT

LED302

YPY1105C

TP346

TP345

5

C331

4

Np

C329

6

5

4

R339

820

LED305

YPY1105C

R340

820

LED306

YPY1105C

R341

820

LED307

YPY1105C

R342

820

LED308

YPY1105C

R343

1K

LED309

YPY1105C

R344

1K

LED310

YPY1105C

1K

()

()

()

LED311

YPY1105C

LED312

YPY1105C

()

()

()

TPB333

TPB335

VBAT

VBAT_BB

VBAT_AP

VBAT_S

5-29 (10-C)

IC303

TK11129CSIL

F

1

2.9V REGULATOR

G

D305

1SS388

TPB332

TPB334

C332

C349

2.2

22

5

Vin

Cont

1

GND

2

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 21 SCHEMATIC DIAGRAM (19/24)

4

Vout

Np(Vref)

3

C350

5 – 26

0.01

C318

2.9V

VTCXO

TP317

2.2

R349

2.2K

Q308

2SA1955 A

0V

2.9V

VSYNTH

45

2.9V

VRF

VTCXO

G

VSYNTH

G

VRF

5-30

(1-F)

6

Page 22

CONFIDENTIAL

RERAY FPC_A

PWB-C

5-18 (2-E)

CN405

GX20

()

()

()

()

Gnd

2

IC305

EW6671

HALL

C308

0.1

Out

Vdd

VINT

C347

0.1

3

C310

1

0.1

LM20BIM7

TEMPERATURE

SENSOR

R368

470

VO

3

GND

2

NC

NC

1

GND

2.715V

VT

V+

4

C348

5

0.1

IC307

5-22 (4-G)

VEXT_CN

1

NC

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

5-30 (1-E)

CONT1

G

IRXN

QRXP

QTXP

ITXP

TCXOEN

RFON

TXON TXD

RTS

IRXP

G

QRXN

G

QTXN

G

ITXN

G

G

G

G

( ) : Not Mount

78 9

Figure 22 SCHEMATIC DIAGRAM (20/24)

CN305

NC

CONT1

IRXN

IRXP

QRXP

QRXN

QTXP

QTXN

ITXP

ITXN

ISENSE

DGND

TCXOEN

RFON

TXON

RTS

VEXT_ON

5 – 27

DGND

DGND

GATEDR

VBAT_AP

VBAT_AP

VBAT_S

BATT_SENSE

ADP

ADPDET

CONT2

VIB_CNT

JAKDET

FLIP_SW

CTS

TXD

ADIN_B

2.715V

VBAT_SVBAT_AP

40

39

38

37

36

35

BATT_SENSE

34

33

32

31

VIB_CNT

30

JAKDET

29

28

27

26

CD

25

ADIN_B

24

10 11

VT

ADP

ADPDET

CONT2

CTS

CD

12

Page 23

GX20

A

B

C

KEY PWB-B (1/2)

TCXOEN

RFON

TXON

CONFIDENTIAL

C319

5

0.1

1

0V 2.88V

0V

0V

4

Vin

Vout

GND

Cont

Np(Vref)

2.9V REGULATOR

3

2

1

C320

Q304

EMG9

5

4

1

2

3

C323

TK11129CSIL

0.01

2

2.87V

3

1

IC304

R351

1.2K

R352

1.2K

R350

2.2K

Q309

2SA1955 A

TP319

2.9V

VRF

2.9V

VTXVCO

VRF

G

VTXVCO

G

5-30 (2-C)

D

E

TP324

L314

2

F

3

C326

47P(CH)

FERRITE BEADS

L315

FERRITE BEADS

()

D308

RSB6.8S

G

SIMCLK,SIMIO,SIMRST

H

NOTES ON SCHEMATIC DIAGRAM can be found on page 5-1.

12 3

Figure 23 SCHEMATIC DIAGRAM (21/24)

5 – 28

45

6

Page 24

TXON TXD

2-C)

CONFIDENTIAL

15

NC

TXON

16

17

VEXT_ON

18

GENIE_CHG

19

RXD

20

NC

RTS

GENIE_CHG

RXD

TXD

ADIN_B

POWONKEY

POWONKEY

26

CDRTS

25

ADIN_B

24

VT

23

22

21

GX20

CD

POWONKEY

5-30 (1-F)

TCXOOUT

KEYPADCOL[0]

KEYPADCOL[1]

KEYPADCOL[2]

KEYPADCOL[3]

KEYPADCOL[4]

G

JAKMIC

SIMRST

SIMIO

SIMCLK

5-30 (1-G)

AFCDAC

C352

0.01

G

RAMPDAC

5-30 (2-D)

5-24

(3-F)

VINT

VSIM

G

CN306

NC

NC

1

NC

KEYPADCOL0

2

KEYPADCOL1

3

KEYPADCOL2

4

KEYPADCOL3

5

KEYPADCOL4

6

DGND

7

8

TCXOOUT

9

DGND

10

JAKMIC

11

DGND

12

DGND

13

SIMRST

14

SIMIO

15

SIMCLK

VSIM VINT

16

VINT VSIM

17

18

AFCDAC

RAMPDAC

19

20

NC

KEYPADROW2

KEYPADROW0

KEYPADROW1

KEYPADROW3

KEYPADROW4

KEY_BL_ON

SYNTHDATA

VBAT_BB

VBAT_BB

DGND

MIC

MIC_GND

JAKEAR

BS2

BS1

BS0

SYNTHCLK

SYNTHEN

CHGIN

40

39

38

37

36

35

34

33

32

31