SGS Thomson Microelectronics VND810SP, VND810SP13TR Datasheet

®

July 2002 1/18

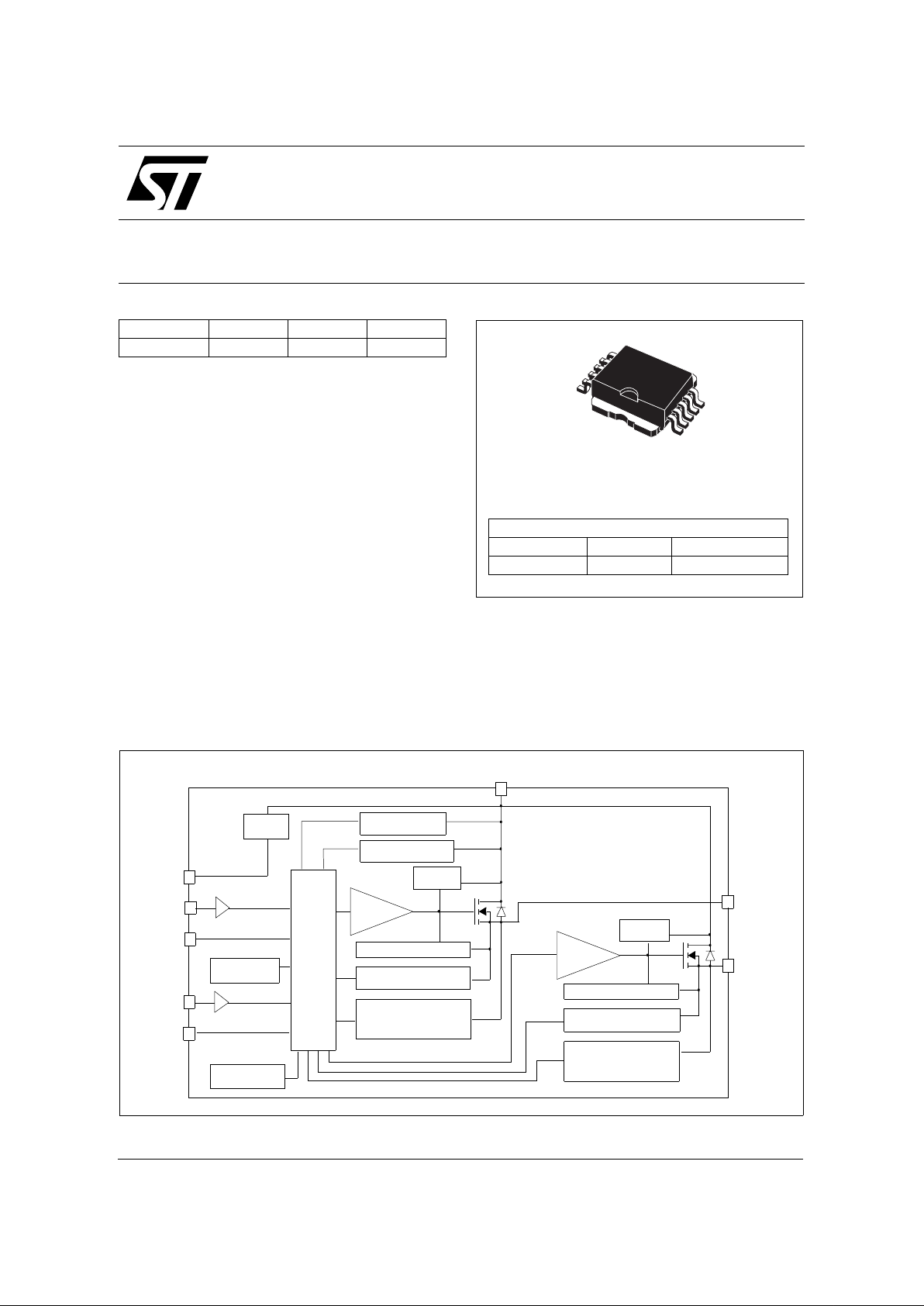

VND810SP

DOUBLE CHANNEL HIGH SIDE DRIVER

1

■ CMOS COMPATIBLE INPUTS

■ OPEN DRAIN STATUS OUTPUTS

■ ON STATE OPEN LOAD DETECTION

■ OFF STATE OPEN LOAD DETECTION

■ SHORTED LOAD PROTECTION

■ UNDERVOLTAGE AND OVERVOLTAGE

SHUTDOWN

■ PROTECTION AGAINST LOSS OF GROUND

■ VERY LOW STAND-BY CURRENT

■ REVERSE BATTERY PROTECTIO N (**)

DESCRIPTION

The VND810 SP is a monolithic de vice made by

using STMicroelectronics VIPower M0-3

Technology, intende d for d riving any k ind of l oad

with one side connected to ground.

Active VCC pin voltag e clamp protects th e dev ice

against low energy spikes (see ISO7637 transient

compatibility table). Active current limitation

combined with thermal sh utdown and automatic

restart protects the device against overloa d. The

device detects open load condition both in on and

off state. Output shorted to VCC is detected in the

off state. Dev ice auto mati cally tur ns off in c ase of

ground pin disconnection.

TYPE R

DS(on)

I

OUT

V

CC

VND810 SP 160 mΩ (*) 3.5 A (*) 36 V

1

10

PowerSO-10

™

ORDER CODES

PACKAGE TU B E T&R

PowerSO-10™ VND810SP VND810SP13TR

(*) Per each channel

BLOCK DIAGRAM

(**) See appl ic ation schema tic at page 8

OVERTEMP. 1

V

cc

GND

INPUT1

OUTPUT1

OVERVOLTAGE

LOGIC

DRIVER 1

STATUS1

V

cc

CLAMP

UNDERVOLTAGE

CLAMP 1

OPENLOAD ON 1

CURRENT LIMITER 1

OPENLOAD OFF 1

OUTPUT2

DRIVER 2

CLAMP 2

OPENLOAD ON 2

OPENLOAD OFF 2

OVERTEMP. 2

INPUT2

STATUS2

CURRENT LIMITER 2

2/18

VND810SP

ABSOLUTE MAXIMUM RATI NG

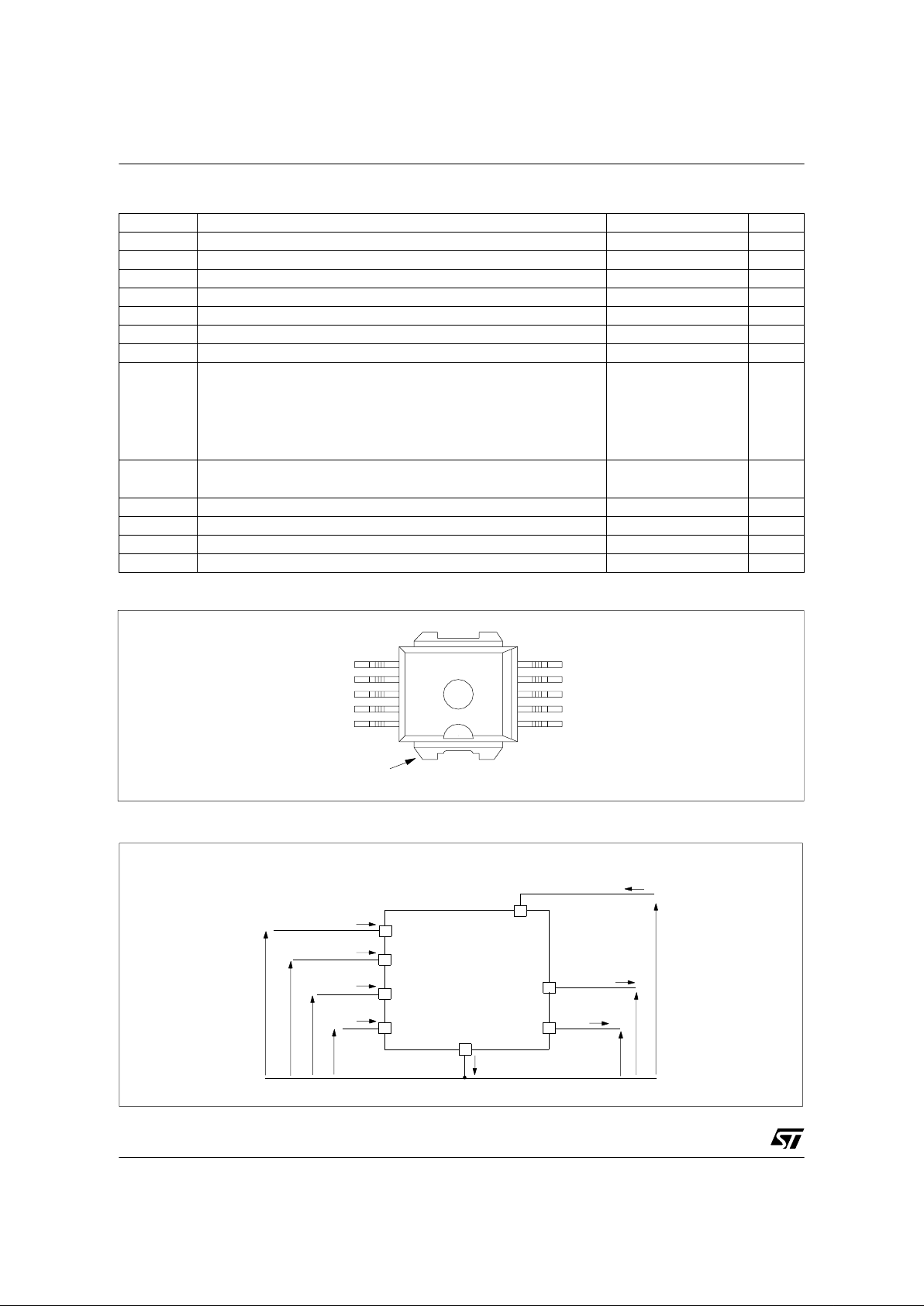

CONNECTION DIAGRAM (TOP VIEW)

Symbol Parameter Value Unit

V

CC

DC Supply Voltage 41 V

- V

CC

Reverse DC Supply Voltage - 0.3 V

- I

GND

DC Reverse Ground Pin Current - 200 mA

I

OUT

DC Output Current Internally Limited A

- I

OUT

Reverse DC Output Current - 6 A

I

IN

DC Input Curr ent +/- 10 mA

I

stat

DC Status Cur rent +/- 10 mA

V

ESD

Electros tatic Discharge (Human Body Model: R=1.5KΩ; C=100pF)

- INPUT

- STATUS

- OUTPU T

- V

CC

4000

4000

5000

5000

V

V

V

V

E

MAX

Maximum Switching Energy

(L=1.4mH; R

L

=0Ω; V

bat

=13.5V; T

jstart

=150ºC; IL=5A)

24 mJ

P

tot

Powe r Dissipation TC=25°C 52 W

T

j

Junction Operating Temperature Internally Limited °C

T

c

Case Operating Temperature - 40 to 150 °C

T

stg

Storage Temperature - 55 to 150 °C

1

CURRENT AND VOLTAGE CO NVENTIONS

1

2

3

4

5

6

7

8

9

10

11

OUTPUT 1

OUTPUT 1

N.C.

OUTPUT 2

OUTPUT 2

GROUND

INPUT 1

STATUS 1

STATUS 2

INPUT 2

V

CC

I

S

I

GND

OUTPUT 2

V

CC

GND

STATUS 2

INPUT 2

I

OUT2

I

IN2

I

STAT2

V

STAT2

V

IN2

V

CC

V

OUT2

OUTPUT 1

I

OUT1

V

OUT1

INPUT 1

I

IN1

STATUS 1

I

STAT1

V

IN1

V

STAT1

3/18

VND810SP

THERMAL DATA

(*) When mounted on a standard single-sided FR-4 board with 0.5cm2 of Cu (at least 35µm thick). Horizontal mounting and no artificial air

flow.

ELECTRICAL CHARACTERISTICS (8V<VCC<36V; -40°C< Tj < 150°C, unless otherwise specified)

(Per each channel)

POWER OUTPUTS

(**) Per device

SWITCHING (VCC=13V)

LOGIC INPUT

Symbol Parameter Value Unit

R

thj-case

Thermal R esistance Junction- case 2.4 °C/W

R

thj-amb

Thermal Resistance Junction-ambient 52.4 (*) °C/W

Symbol Parameter Test Conditions Min Typ Max Unit

V

CC

(**) Operating Supply Voltage 5.5 13 36 V

V

USD

(**) Undervoltage Shut-down 3 4 5.5 V

V

OV

(**) Ove rvoltage Shu t-down 36 V

R

ON

On State Resistance

I

OUT

=1A; Tj=25°C

I

OUT

=1A; VCC>8V

160

320

mΩ

mΩ

I

S

(**) Supply Current

Off State; V

CC

=13V; VIN=V

OUT

=0V

Off State; V

CC

=13V; VIN=V

OUT

=0V;

Tj=25°C

On State; V

CC

=13V; VIN=5V; I

OUT

=0A

12

12

5

40

25

7

µA

µA

mA

I

L(off1)

Off State Output Current VIN=V

OUT

=0V 0 50 µA

I

L(off2)

Off State Output Current VIN=0V; V

OUT

=3.5V -75 0 µA

I

L(off3)

Off State Output Current VIN=V

OUT

=0V; Vcc=13V; Tj =125°C 5 µA

I

L(off4)

Off State Output Current VIN=V

OUT

=0V; Vcc=13V; Tj =25°C 3 µA

Symbol Parame ter Test Condit ions Min Typ Max Unit

t

d(on)

Turn-on Delay Time

RL=13Ω from VIN rising edge to

V

OUT

=1.3V

30 µs

t

d(off )

Turn-off Delay Time

RL=13Ω from VIN falling edge to

V

OUT

=11.7V

30 µs

dV

OUT

/

dt

(on)

Turn-on Voltage Slope

RL=13Ω from V

OUT

=1.3V to

V

OUT

=10.4V

See

relative

diagram

V/µs

dV

OUT

/

dt

(off)

Turn-off Voltage Slop e

RL=13Ω from V

OUT

=11.7V to

V

OUT

=1.3V

See

relative

diagram

V/µs

Symbol Param eter Test Conditions Min Typ Max Unit

V

IL

Input Low Level 1.25 V

I

IL

Low Level Input Current VIN = 1.25V 1 µA

V

IH

Input High Level 3.25 V

I

IH

High Level Input Current VIN = 3.25V 10 µA

V

hyst

Input Hyst eresis Voltage 0.5 V

V

ICL

Input Clamp Voltage

I

IN

= 1mA

I

IN

= -1mA

66.8

-0.7

8V

V

1

4/18

VND810SP

ELECTRICAL CHARACTERISTICS (continued)

STATUS PIN

PROTECTIONS

OPENLOAD DETECTION

Symbol Parameter Test Conditions Min Typ Max Unit

V

STAT

Status Low Output Voltage I

STAT

= 1.6 mA 0.5 V

I

LSTAT

Status Leakage Current Normal Operation; V

STAT

= 5V 10 µA

C

STAT

Status Pin Input

Capacitance

Normal Operation; V

STAT

= 5V 100 pF

V

SCL

Status Clamp Voltage

I

STAT

= 1mA

I

STAT

= - 1mA

66.8

-0.7

8V

V

Symbol Parame ter Test Condit ions Min Typ Max Unit

T

TSD

Shut-down Temperature 150 175 200 °C

T

R

Reset Temp erature 135 °C

T

hyst

Ther ma l Hy steresi s 7 15 °C

t

sdl

Status Delay in Overload

Conditions

Tj>T

TSD

20 µs

I

lim

Current limitation

5.5V<V

CC

<36V

3.5 5 7.5

7.5

A

A

V

demag

Turn-off Output Clamp

Voltage

I

OUT

=1A; L= 6m H VCC-41 VCC-48 VCC-55 V

Symbol Param eter Test Conditions Min Typ Max Unit

I

OL

Openload ON State

Detectio n Threshold

V

IN

=5V 20 40 80 mA

t

DOL(on)

Openload ON State

Detection Delay

I

OUT

=0A 200 µs

V

OL

Openload OFF State

Voltage Detection

Threshold

VIN=0V 1.5 2.5 3.5 V

t

DOL(off)

Openload Detection Delay

at Turn Off

1000 µs

2

1

V

INn

V

STAT n

t

DOL(off)

OPEN LOAD STATUS TIMING (with external pull-up)

V

INn

V

STAT n

OVER TEMP STATUS TIMING

t

SDL

t

SDL

I

OUT

< I

OL

V

OUT

> V

OL

t

DOL(on)

Tj > T

TSD

5/18

VND810SP

1

t

t

V

OUTn

V

INn

80%

10%

dV

OUT

/dt

(on)

t

d(off)

90%

dV

OUT

/dt

(off)

t

d(on)

Switching time Waveforms

TRUTH TABLE

CONDITIONS INPUT OUTPUT STATUS

Normal Operation

L

H

L

H

H

H

Current Limitation

L

H

H

L

X

X

H

(T

j

< T

TSD

) H

(T

j

> T

TSD

) L

Overtemperature

L

H

L

L

H

L

Undervoltage

L

H

L

L

X

X

Overvoltage

L

H

L

L

H

H

Output Voltage > V

OL

L

H

H

H

L

H

Output Current < I

OL

L

H

L

H

H

L

6/18

VND810SP

1

1

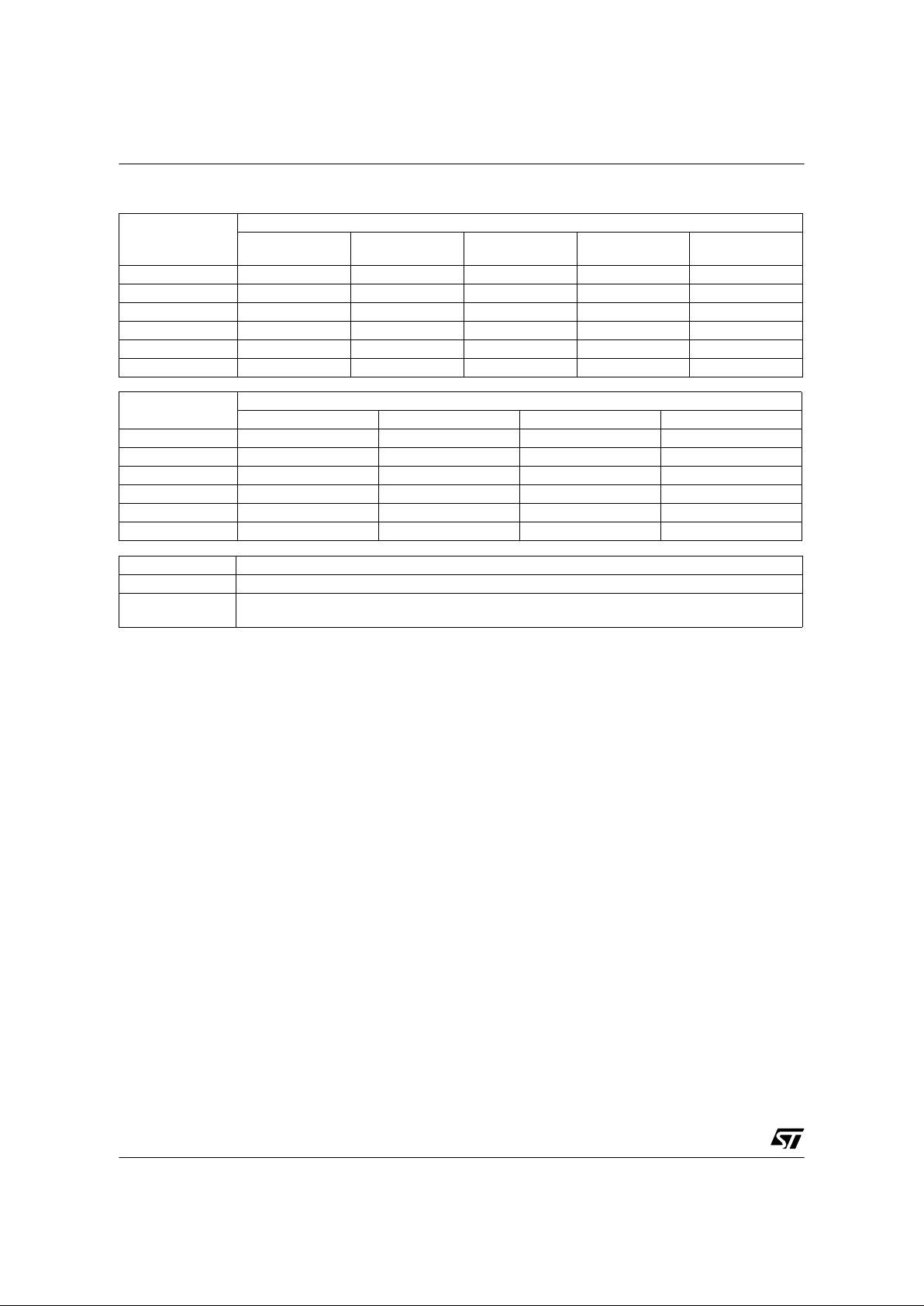

ELECTRICAL TRANS IENT REQUIREMENTS ON VCC PIN

ISO T/R 7637/1

Test Pulse

TEST LEVELS

I II III IV Delays and

Impedance

1 -25 V -50 V -75 V -100 V 2 ms 10 Ω

2 +25 V +50 V +75 V +100 V 0.2 ms 10 Ω

3a -25 V -50 V -100 V -150 V 0.1 µs 50 Ω

3b +25 V +50 V +75 V +100 V 0.1 µs 50 Ω

4 -4 V -5 V -6 V -7 V 100 ms, 0.01

Ω

5 +26.5 V +46.5 V +66.5 V +86.5 V 400 ms, 2

Ω

ISO T/R 7637/1

Test Pulse

TEST LEVELS RESULTS

IIIIIIIV

1CCCC

2CCCC

3aCCCC

3bCCCC

4CCCC

5CEEE

CLASS CONTENTS

C All functions of the device are perform e d as designe d after expos ure to distu rb ance.

E One or more functions of the device is not performed as designed after exp osure and cannot be

returned to proper operation without rep lacing the device.

Loading...

Loading...