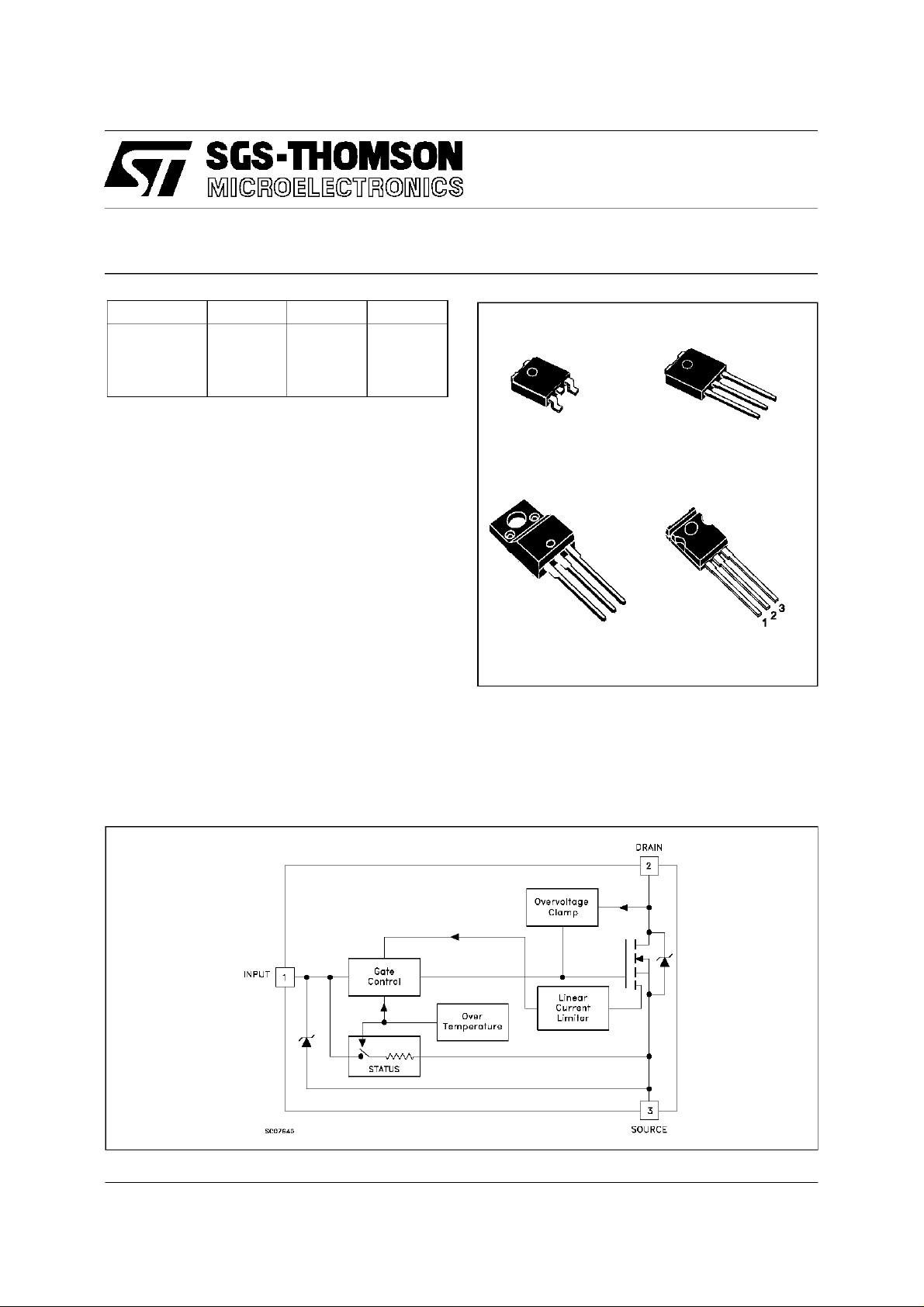

VND5N07/VND5N07-1

VNP5N07FI/K5N07FM

”OMNIFET”:

FULLY AUTOPROTECTED POWER MOSFET

TYPE V

VND5N07

VND5N07-1

VNP5N07FI

VNK5N07FM

■ LINEAR CURRENT LIMITATION

■ THERMALSHUTDOWN

■ SHORTCIRCUIT PROTECTION

■ INTEGRATEDCLAMP

■ LOW CURRENT DRAWN FROM INPUT PIN

■ DIAGNOSTICFEEDBACK THROUGH INPUT

clamp

70 V

70 V

70 V

70 V

R

DS(on)

0.2 Ω

0.2 Ω

0.2 Ω

0.2 Ω

I

lim

5A

5A

5A

5A

PIN

■ ESD PROTECTION

■ DIRECT ACCESS TO THE GATE OF THE

POWERMOSFET (ANALOGDRIVING)

■ COMPATIBLEWITH STANDARD POWER

MOSFET

DESCRIPTION

The VND5N07, VND5N07-1, VNP5N07FI and

VNK5N07FM are monolithic devices made using

SGS-THOMSON Vertical Intelligent Power M0

Technology, intended for replacement of

standard power MOSFETS in DC to 50 KHz

applications. Built-in thermal shut-down, linear

current limitation and overvoltage clamp protect

BLOCK DIAGRAM

3

1

DPAK

TO-252

ISOWATT220

IPAK

TO-251

3

2

1

SOT82-FM

3

2

1

the chip in harsh enviroments.

Faultfeedback can be detected by monitoringthe

voltageat the input pin.

June 1996

1/14

VND5N07/VND5N07-1/VNP5N07FI/VNK5N07FM

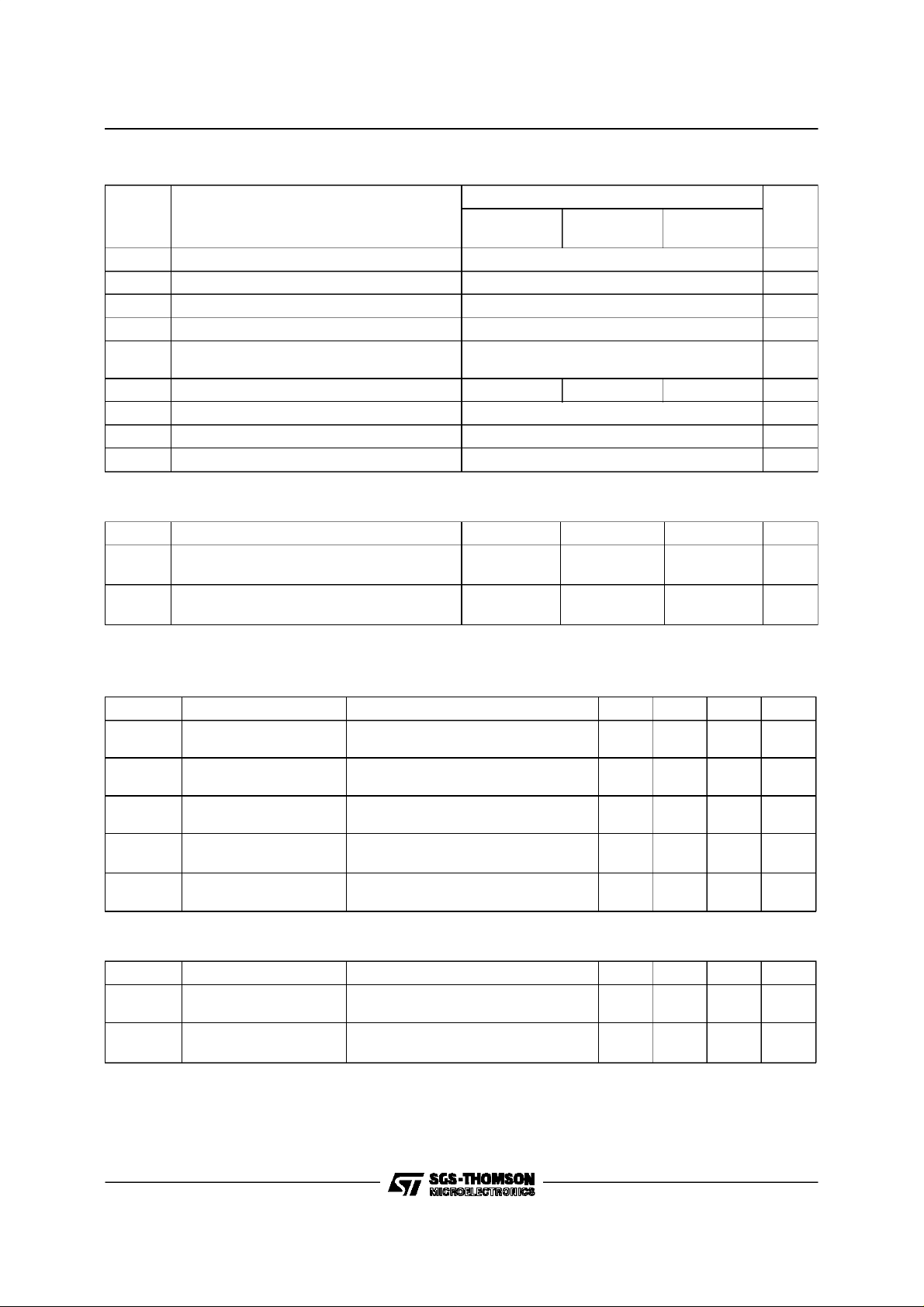

ABSOLUTEMAXIMUMRATING

Symbol Parameter Value Unit

V

V

Drain-source Voltage (Vin= 0 ) Internally Clam ped V

DS

V

Input Voltage 18 V

in

I

Drain Current Inte r nally Limited A

D

I

Reverse DC Output Current -7 A

R

Elect r os t at ic Discha rge (C= 100 pF,

esd

R=1. 5 KΩ)

P

T

Tot al Dis sipa t ion at Tc=25oC60249W

tot

T

Oper at ing Junction Tem perature Inte r nally Limited

j

T

Case Operating Temperature Internally Limited

c

Sto rage Tem perat ure -55 to 150

stg

THERMAL DATA

R

thj-case

R

thj-amb

Ther mal R es is t an ce J unc t i on-c ase

Max 3.75 5.2 14

Ther mal R es is t an ce J unc t i on-am b ient

Max 100 62.5 100

DPAK

IPAK

DPAK/IPAK ISOWAT T220 SOT82-FM

ISOWATT220 SOT-82FM

2000 V

o

C/W

o

C/W

o

C

o

C

o

C

ELECTRICAL CHARACTERISTICS (T

=25oC unlessotherwise specified)

case

OFF

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

V

CLAMP

Drain-source Clamp

ID= 200 mA Vin= 0 60 70 80 V

Volt age

V

CLTH

Drain-source Clamp

ID=2mA Vin=0 55 V

Thr eshold Vol ta ge

V

INCL

Input-Source Reverse

Iin=-1mA -1 -0.3 V

Clamp Voltage

I

DSS

I

ISS

Zer o I npu t V olt age

Drain Current (V

in

Supply Current from

V

=13V Vin=0

=0)

DS

=25V Vin=0

V

DS

VDS=0V Vin= 10 V 250 500 µA

50

200

Input Pin

ON (∗)

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

V

R

DS(on)

IN(th)

Input Thres hold

Volt age

St at ic Drain-sour ce On

Resistance

VDS=VinID+Iin=1mA 0.8 3 V

Vin=10V ID=2.5A

=5V ID=2.5A

V

in

0.200

0.280ΩΩ

µA

µA

2/14

VND5N07/VND5N07-1/VNP5N07FI/VNK5N07FM

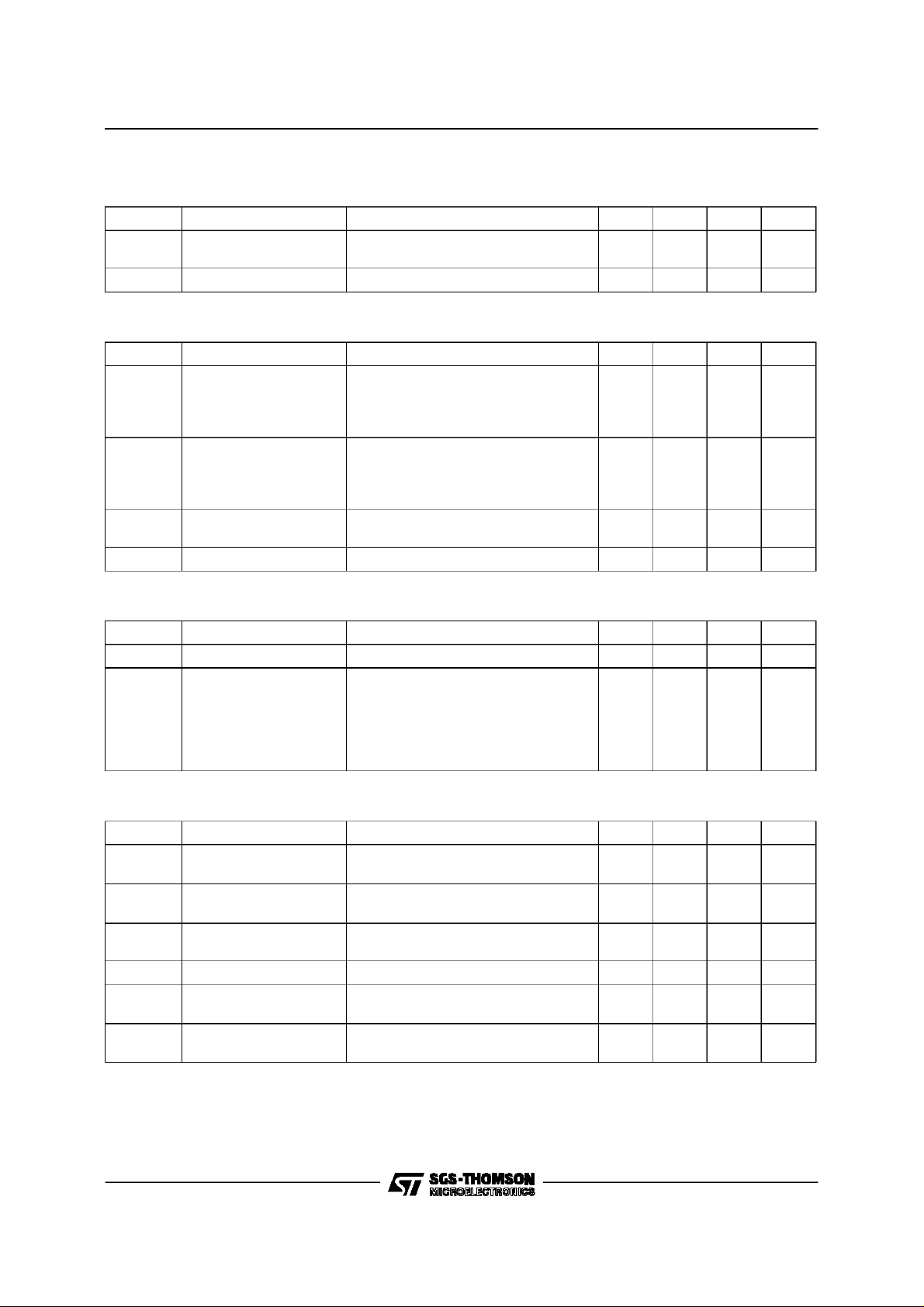

ELECTRICAL CHARACTERISTICS (continued)

DYNAMIC

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

g

(∗)Forward

fs

Tr ansc on ductance

C

Out put Capacit anc e V D S = 13 V f = 1 MHz Vin= 0 200 300 pF

oss

SWITCHING(∗∗)

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

t

d(on)

t

d(off)

t

d(on)

t

d(off)

(di/dt)

Q

Turn-on Delay Time

t

Rise Time

r

Turn-off Delay T ime

t

Fall T ime

f

Turn-on Delay Time

t

Rise Time

r

Turn-off Delay T ime

t

Fall T ime

f

Tur n-on Current Slope VDD=15V ID=2.5A

on

Total Input Charge VDD=12V ID=2.5A Vin= 10 V 18 nC

i

VDS=13V ID=2.5A 3 4 S

VDD=15V Id=2.5A

=10V R

V

gen

gen

=10Ω

(see figure 3)

VDD=15V Id=2.5A

=10V R

V

gen

= 1000 Ω

gen

(see figure 3)

50

60

150

40

150

400

3900

1100

100

100

300

80

250

600

5000

1600

80 A/µs

=10V R

V

in

gen

=10Ω

ns

ns

ns

ns

ns

ns

ns

ns

SOURCE DRAIN DIODE

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

V

(∗)ForwardOnVoltage ISD=2.5A Vin=0 1.6 V

SD

t

rr

Reverse Re covery

(∗∗)

Time

Reverse Re covery

(∗∗)

Q

rr

I

=2.5A di/dt=100A/µs

SD

=30V Tj=25oC

V

DD

(see test cir cuit, figure 5)

150

0.3

Charge

(∗∗)

I

RRM

Reverse Re covery

5.7

Current

PROTECTION

Symbol Parameter Test Cond ition s Min. Typ. Max. Unit

t

dlim

T

jsh

I

lim

Drain Current Limit Vin=10V VDS=13V

=5V VDS=13V

V

in

(∗∗) St ep Response

Current Lim it

Vin=10V

=5V

V

in

(∗∗) Overtem per at u r e

Shut dow n

(∗∗) O vertem perat ure Re s et 135

T

jrs

I

(∗∗) Fault Sink Current Vin=10V VDS=13V

gf

E

(∗∗) S i ngle Pulse

as

Avalanche Energy

(∗) Pulsed: Pulse duration = 300 µs, duty cycle 1.5 %

(∗∗) Parameters guaranteed by design/characterization

=5V VDS=13V

V

in

starting Tj=25oCVDD=20V

=10V R

V

in

=1KΩ L=10mH

gen

3.5

3.5

15

40

5

5

7

7

20

60

150

50

20

0.2 J

ns

µC

A

A

A

µs

µs

o

C

o

C

mA

mA

3/14

VND5N07/VND5N07-1/VNP5N07FI/VNK5N07FM

PROTECTION FEATURES

During normal operation, the Input pin is

electrically connected to the gate of the internal

power MOSFET. The device then behaves like a

standard power MOSFET and can be used as a

switch from DC to 50 KHz. The only difference

from the user’s standpoint is that a small DC

current (I

) flows into the Input pin in order to

iss

supplythe internalcircuitry.

The device integrates:

- OVERVOLTAGE CLAMP PROTECTION:

internally set at 70V, along with the rugged

avalanche characteristics of the Power

MOSFET stage give this device unrivalled

ruggedness and energy handling capability.

This feature is mainly important when driving

inductiveloads.

- LINEAR CURRENT LIMITER CIRCUIT: limits

the drain current Id to Ilim whatever the Input

pin voltage. When the current limiter is active,

the device operates in the linear region, so

power dissipation may exceed the capability of

the heatsink. Both case and junction

temperatures increase, and if this phase lasts

long enough, junction temperature may reach

the overtemperaturethreshold T

jsh

.

- OVERTEMPERATURE AND SHORT CIRCUIT

PROTECTION: these are based on sensing

the chip temperatureand are not dependent on

the input voltage. The location of the sensing

element on the chip in the power stage area

ensures fast, accurate detection of the junction

temperature. Overtemperaturecutout occurs at

minimum 150

restarted when the chip temperature falls

below135

o

C. The device is automatically

o

C.

- STATUS FEEDBACK: In the case of an

overtemperature fault condition, a Status

Feedback is provided through the Input pin.

The internal protection circuit disconnects the

input from the gate and connects it instead to

ground via an equivalent resistance of 100 Ω.

The failure can be detected by monitoring the

voltage at the Input pin, which will be close to

ground potential.

Additional features of this device are ESD

protection according to the Human Body model

and the ability to be driven from a TTL Logic

circuit (with a small increase in R

DS(on)

).

4/14

VND5N07/VND5N07-1/VNP5N07FI/VNK5N07FM

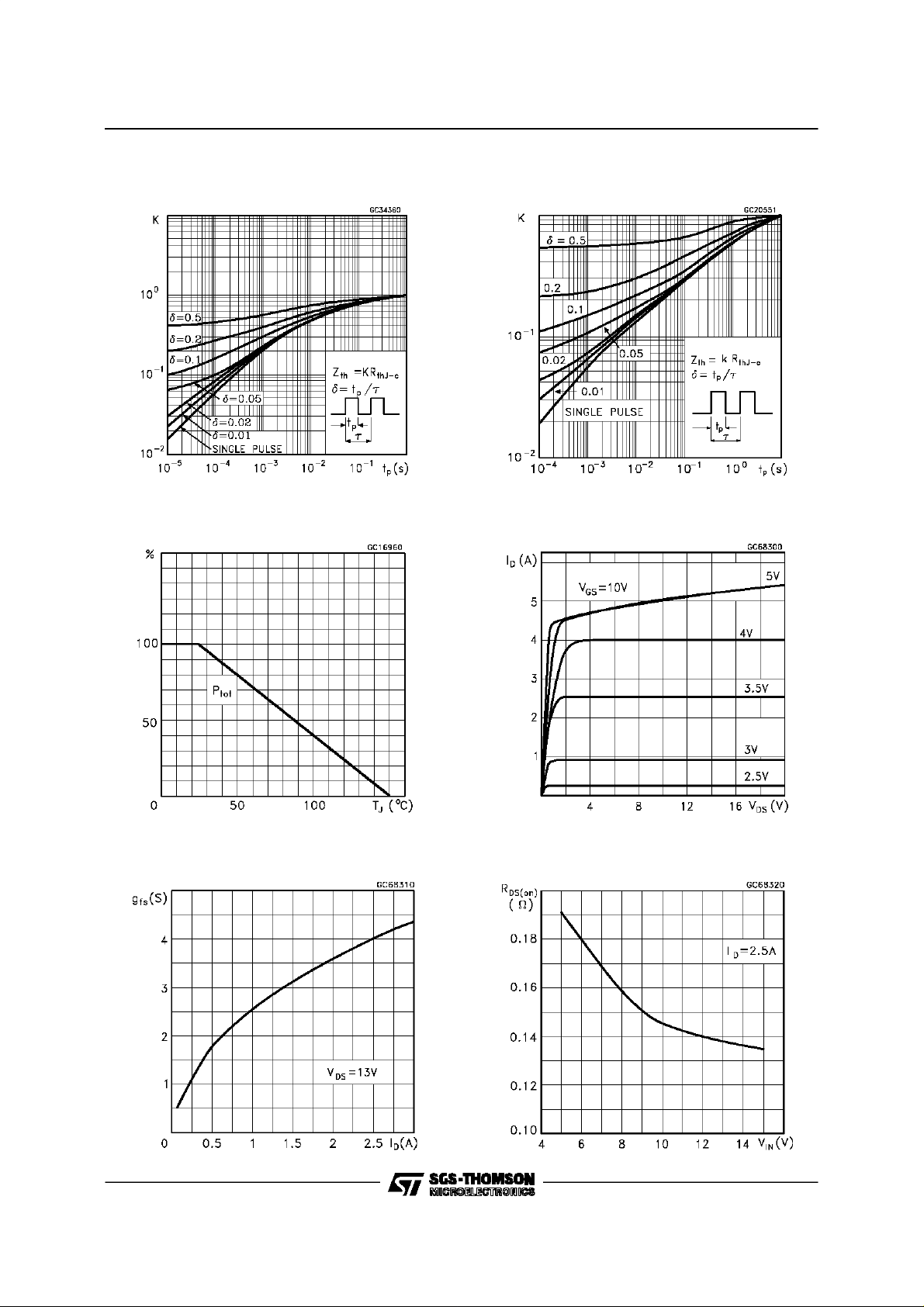

Thermal ImpedanceFor DPAK / IPAK

Derating Curve

ThermalImpedanceFor ISOWATT220

OutputCharacteristics

Transconductance

StaticDrain-SourceOnResistancevs Input

Voltage

5/14

Loading...

Loading...