®

VK05CFL

ELECTRONIC DRIVER FOR CFL APPLICATION

TYPE B

VK05CFL 520 V 0.25A 1.5A

■ EMITTER SWITCH POWER OUTPUT STAGE

■ INTEGRATED ANTIPARALLEL COLLECTOR

V

I

Crms

I

Peak

SOURCE DIODE

■ INTEGRATED DIAC FUNCTION

■ NOMINAL WORKING FREQUENCY

SETTABLE BY EXTERNAL CAPACI TO R

■ IGNITION FREQUENCY SET BY LOAD

DESCRIPTION

The VK05CFL is a m onolithic devi ce housed in a

standard SO-8 package, made by using

STMicroelectronics proprietary VIPower M3

Technology. T his device is intended both for the

low side and the high side driver in half bridge CFL

applications. This means that it is possible to

realize a complete H-bridge by using two

VK05CFL devices: one connected in HSD

configuration and the other connected in LSD

configuration. In the VK05CFL used in HSD

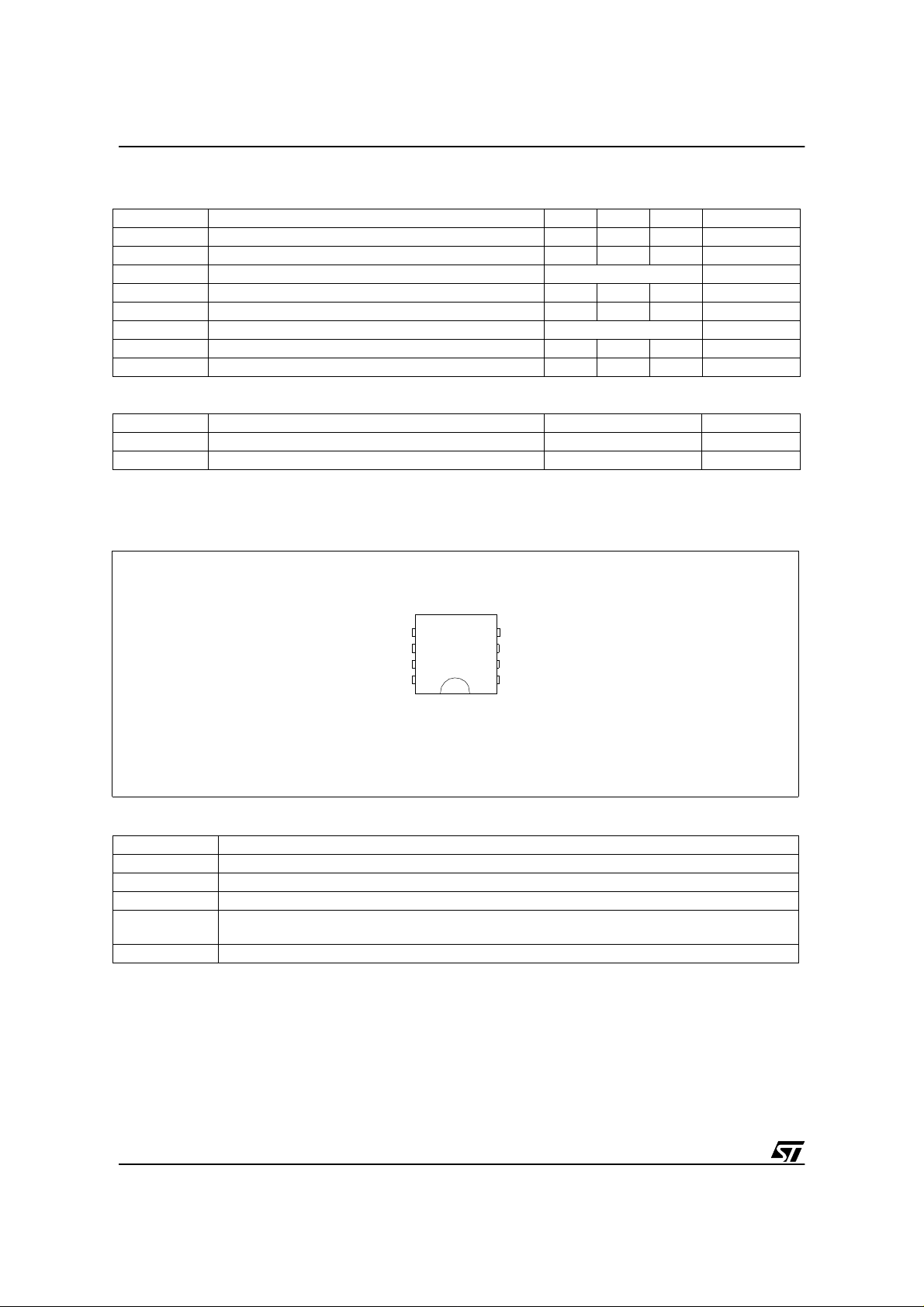

BLOCK DIAGRAM

SO-8

configuration, the diac pin must be connected to

source pin. B oth diac fu nctionality and disch arge

circuit for ext ernal diac capacitor are integrated.

By an external capac itor it is possible to choose

the nominal working fre quency without influence

on the ignition one.

Collector

diac

Diac

sec

osc

2Vref

R

5Vref

Septe m ber 2002 1/14

-

+

+

-

Source

VK05CFL

ABSOLUTE MAXIMUM RATING

Symbol Parameter Min Typ Max Unit

V

CS

I

sec

V

sec

I

CM

I

OSC

V

OSC

T

j

T

stg

THERMAL DATA

Symbol Parameter Value Unit

R

thj-lead

R

thj-amb

(*) When mounted on a standard single-sided FR-4 board with 100m m2 of Cu (at leas t 35µ m t hick).

CONNECTION DIAGRAM

Collector-Source Voltage 520 V

Input Current (sec ondary) -100 140 mA

Input Voltage (secondary) Internally limited V

Collector Peak Current -1.8 1.8 A

Osc Pin Current 100 mA

Osc Pin Voltage Internally limited V

Max Operating Junction Temperature -40 150 °C

Storage Temperature Range -55 150 °C

Thermal Resistance Junction - lead Max 15 °C/W

Thermal Resistance Junction - ambient Max 52 (*) °C/W

Collector

Collector

Collector

Collector

5

8

4

sec

osc

diac

1

Source

SO-8

PIN FUNCTIONS

Pin Name Pin Function

Collector Collector of the NPN high voltage transistor in the cascode configuration.

Sour ce Low vol ta ge Power MOSF ET source in th e cascode configurati o n and GROUND re f e ren ce.

diac Input of t he diac block t o start the s ystem up at the beginning.

sec

osc Output via to cha rge external capacitor necessary to set the steady state working frequency.

Connection with secondary winding of the voltage transformer, in order to trigger and to supply the

device.

2/14

VK05CFL

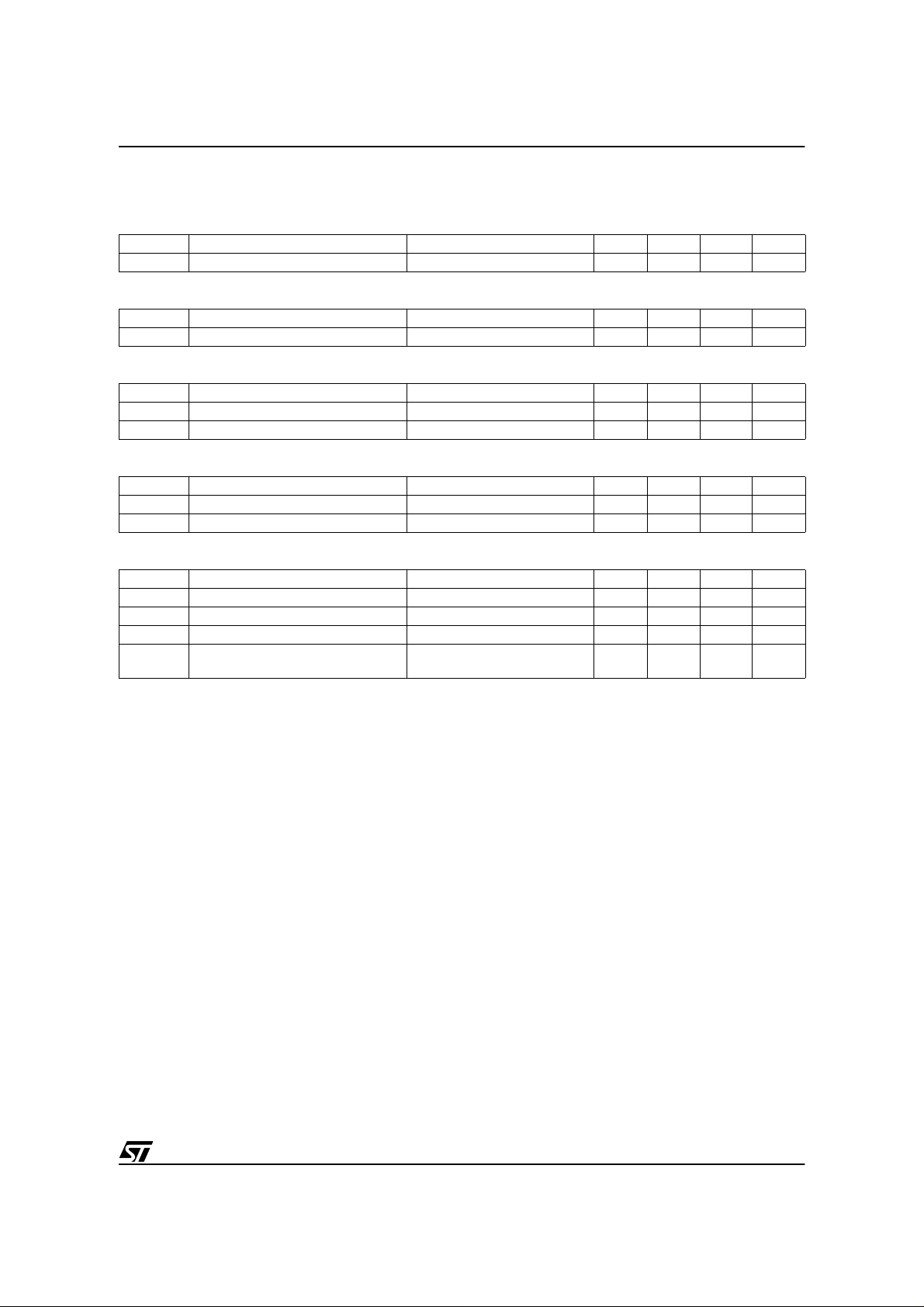

ELECTRICAL CHARACTERISTICS (T

=25°C unless otherwise specified)

case

FORWARD

Symbol Parameter Test Conditions Min Typ Max Unit

V

CS(sat)

Collector-Source Saturation Voltage V

=10V; IC=300mA 1.4 2.8

sec

REVERSE

Symbol Parameter Test Conditions Min Typ Max Unit

V

Collector-Source Reverse Voltage IC= -300mA -1 -1.5

CSr

OSC

Symbol Parameter Test Conditions Min Typ Max Unit

I

OSC

V

OSC(th)

Osc Output Current V

Osc Turn-off Voltage V

=10V; V

sec

=10V 1. 6 2

sec

=0V 300 µ

OSC

DIAC

Symbol Parameter Test Conditions Min Typ Max Unit

V

diac(thH)

V

diac(thL)

Diac On Threshold 28 31 35

Diac Off Threshold 18

SEC

Symbol Parameter Test Conditions Min Typ Max Unit

V

sec(clH)

V

sec(clL)

V

sec(on)

I

sec(on)

Sec Clamp Hig h I

Sec Clamp Low I

Sec Turn-on Voltage IC=10mA; V

Sec On Current

=20mA; V

sec

= -10mA 25

sec

V

=10V; V

sec

IC=300mA

=0V 22

OSC

=0V 3.5 4.5 5.5

OSC

=0V;

OSC

4

V

V

A

V

V

V

V

V

V

mA

3/14

VK05CFL

APPLICATION DESCRIPTION

Technology Overview

The VK05CFL is made by using STMicroelectronics proprietary VIPower M3-3 technology. This

technology allows the integration in the same chip both of the control part and the power stage. The power

stage is the “Emitter Switching”. It is ma de by putting in cascode co nfiguration a bipolar high voltage

darlington with a low voltage MOSFET. This configuration provides a good trade-off between the bipolars

low ON drop wi th high break down vo ltage in OFF sta te, and the M OSFETS hi gh swi tchin g speed. The

maximum theoretical working frequency is in the range of 300KHz.

Circuit description

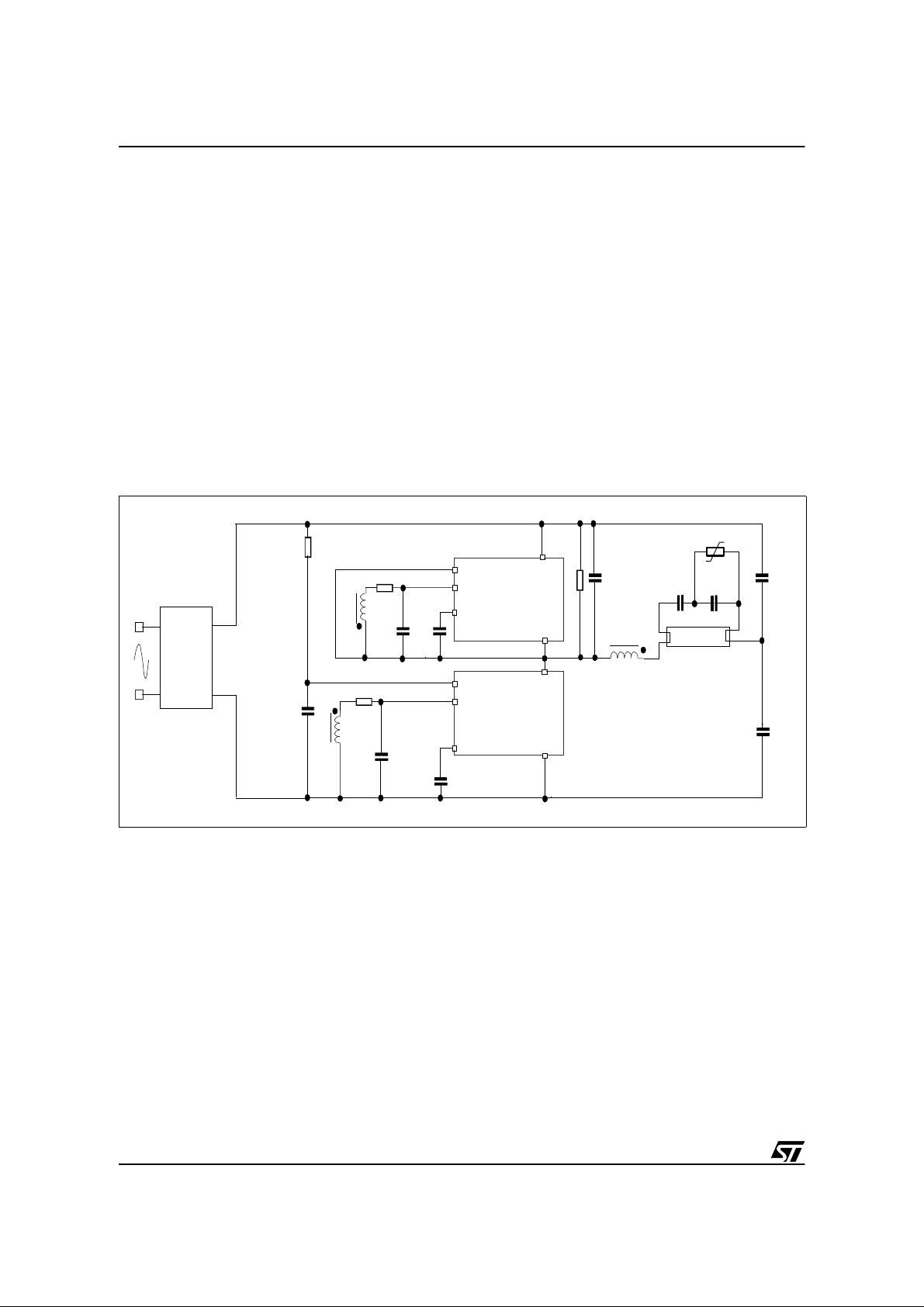

The electrica l scheme of the VK05CFL used as a self- oscillating c onverter to drive fluor escent tubes is

shown in Fig. 1.

Figur e 1: Application schematic

PTC

C4 C13

Tube

C2

Bridge

+

Inpu t F ilte r

R2

diac

sec

R4

L1s

C10

C8

R5

L2s

C11

C5

osc

diac

sec

VK05CFL

osc

C6

VK05CFL

Collector

Source

C ollector

Source

C7 C3

R1

Lp

This topology does not req uire the sat urable trans former to set t he working fre quency. Two secondary

windings are wound on the main ballast choke Lp. These windings have two functions:1) to trigger the ON

state and 2) to provide the power supply to the device. A good trade-off for the ratio between the primary

winding Lp and the two se condary windings i s 10:1; in ord er to minimize th e power dissip ated on the

resistors R4 - R5 and to guarantee sufficient voltage to supply the device.

The steady-state working frequency is set by the two capacitor C5 and C6. They are charged by a current

I

≈300µA. When the voltage on the capacitor reaches an internal fixed value the power stage is turned

cap

OFF. By choosing the same value for C5 and C6 the circuit will work with a duty-cycle of 50%. During the

start-up, as the res onance freq uency is hig her than the steady- state freq uency, the s econdary vol tage

falls lower than the device sustain voltage before the capacitor C5-6 is charged, switching OFF the device.

For this reason t he circui t can wo rk at different frequencies dur ing the start-up and steady-s t ate pha ses .

The resistor R 2 an d the cap ac itor C 8 a re nee ded to bias the int erna l d iac in the low side de v ice i n orde r

to start-up the system. In the high side d evice the diac pin must be connected to the midp oint. R1 is the

pull-up resistor and C7 is the snubber capacitor.

Input filt ering i s r eali zed by R 4-C10 and R5-C11. I t is necess ar y to ha ve a proper supp ly voltage on the

input pin.

4/14

1

VK05CFL

f

st up–

1

2π LcC4⋅

------------ -----------------

=

Functional description

When the circuit is supplied, the capacitor C8 is charged by the resistor R2 till the voltage across it

reaches the internal d iac thresho ld value (~ 30V). The l ow side swi tch is tu rned ON and c onsequently

current will flow from the HV rail to ground through the path formed by C3//C2, C4 and Lp (in case that the

pre-heating network is not present: PTC and C13 are not connected). The voltage drop on Lp is

“transferred” to the two secondary windings (wound in opposition) in order to confirm the ON state for the

low side device and the OFF state for the high side device. As soon as the low side device switches ON,

the capacitor C8 is discharged to ground by an internal HV diode to avoid diac restart.

In this preliminary phase the tube is OFF and the circu it will oscillate at the Lp-C4 series with (C3//C2)

resonance frequency

we can neglect C3//C2

As this frequency is higher than the steady-state one, the two devices will switch ON-OFF at this

frequency, as t he voltage on the tw o secondary windings fall s below the voltage need ed to keep the

device on.

As soon as the tube is ign it ed the r esonan c e freq uency i s red uced ≈(Lp-C3//C2) and the circuit will work

at the steady-state frequency fixed by the two capacitors C5 and C6.

It is possible to calculate the steady-state frequency by these formulae:

5

T

on

RC

-- -

ln⋅⋅=

2

(R = internal impedance)

1

-- -

TTont

2

f

=

Considering th e V K 05CFL bo ard: R =1 2KΩ; C5=C6=1.2nF ; t

the working frequency will be: f≈35KHz.

++=

1

--T

storagetdv()dt()⁄

≈400nsec; C 7= 680p F⇒t

storage

(dv)/(dt)

≈800nsec;

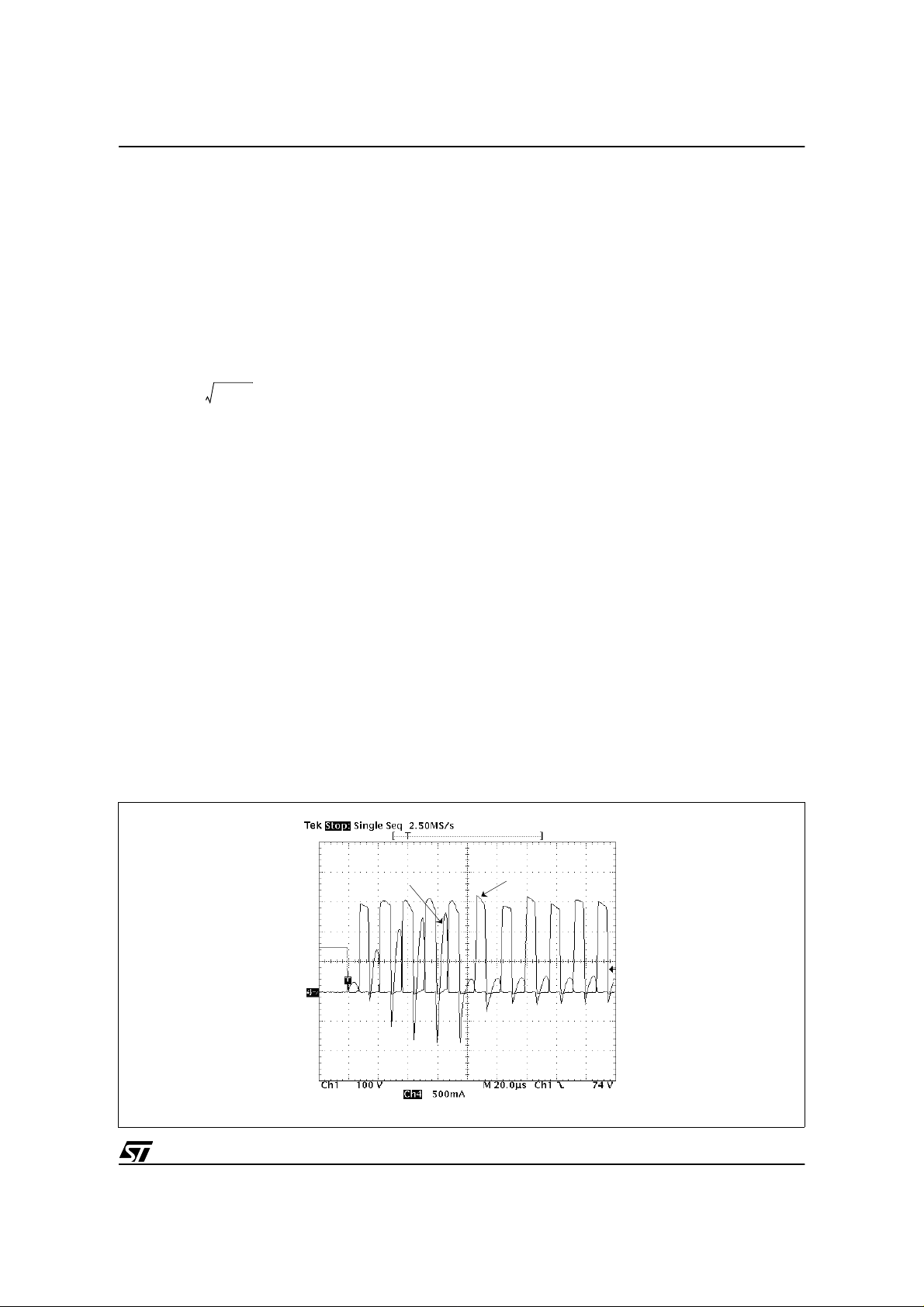

In figure 2 and figure 3, the start-up phase without preheating is reported , while in figure 4 the main

waveforms in steady-state are shown.

Figur e 2: Start-up phase

midpoint

device

I

5/14

Loading...

Loading...