SGS Thomson Microelectronics TDA7561 Datasheet

TDA7561

MULTIFUNCTION QUAD POWER AMPLIFIER

WITH BUILT-IN DIAGNOSTICS FEATURES

■ DMOS POWER OUTPUT

■ HIGH OUTPUT POWER CAPABILITY 4x25W/

4W @ 14.4V, 1KHZ, 10% THD, 4x35W EIAJ

■ MAX. OUTPUT POWER 4x60W/2W

■ FULL I2C BUS DRIVING:

–ST-BY

– INDEPENDENT FRONT/REAR SOFT PLAY/

MUTE

SELECTABLE GAIN 26dB - 12dB (FOR LOW

–

NOISE LINE OUTPUT FUNCTION)

2

C BUS DIGITAL DIAGNOSTICS

–I

■ FULL FAULT PROTECTION

■ DC OFFSET DETECTION

■ FOUR INDEPENDENT SHORT CIRCUIT

PROTECTION

■ CLIPPING DETECTOR

■ ESD PROTECTION

DESCRIPTION

The TDA7561 is a new BCD technology QUAD

BRIDGE type of car radio amplifier in Flexiwatt25

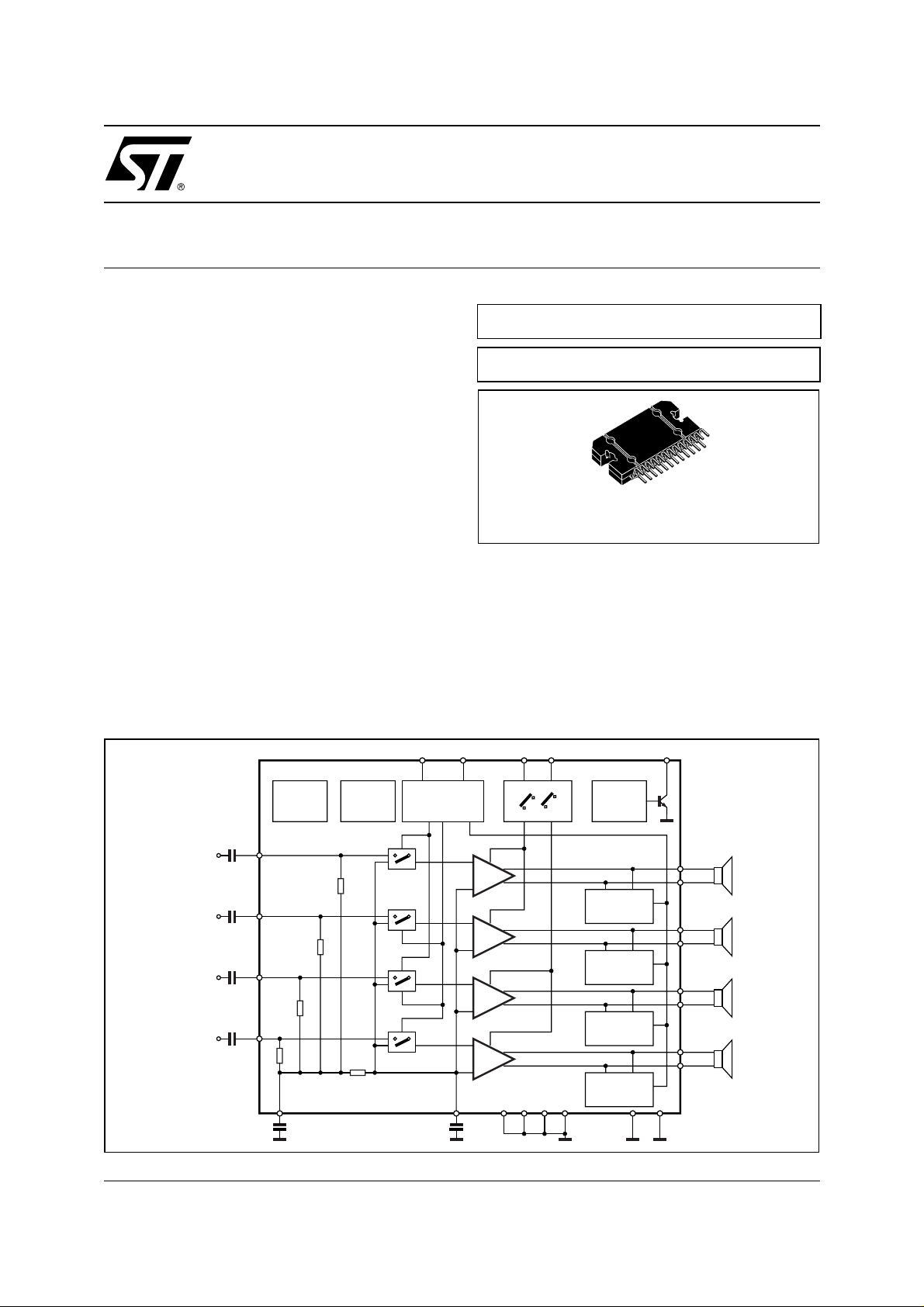

BLOCK DIAGRAM

MULTIPOWER BCD TECHNOLOGY

MOSFET OUTPUT POWER STAGE

FLEXIWATT25

package specially intended for car radio applications.

Thanks to the DMOS output stage the TDA7561 has

a very low distortion allowing a clear powerful

sound.This device is equipped with a full diagnostics

array that communicates the status of each speaker

through the I

figuration and behaviour of the device by means of

2

the I

2

C bus.The possibility to control the con-

C bus makes TDA 7561 a very flexible machine.

V

CC1VCC2DATA CD_OUTCLK

IN RF

IN RR

IN LR

December 2002

IN LF

REFERENCE

F

R

F

R

SVR RF RR LF LR TAB S_GNDAC_GND

D00AU1229

PROTECTION

& DUMP

I2C BUSTHERMAL

MUTE1MUTE2

12/26dB

12/26dB

12/26dB

12/26dB

CLIP

DETECTOR

SHORT CIRCUIT

PROTECTION &

DIAGNOSTIC

SHORT CIRCUIT

PROTECTION &

DIAGNOSTIC

SHORT CIRCUIT

PROTECTION &

DIAGNOSTIC

SHORT CIRCUIT

PROTECTION &

DIAGNOSTIC

PW_GND

OUT RF+

OUT RF-

OUT RR+

OUT RR-

OUT LF+

OUT LF-

OUT LR+

OUT LR-

1/19

TDA7561

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

Operating Supply Voltage 18 V

DC Supply Voltage 28 V

S

Peak Supply Voltage (for t = 50ms) 50 V

CK pin Voltage 6 V

Data Pin Voltage 6 V

Output Peak Current (not repetitive t = 100ms) 8 A

Output Peak Current (repetitive f > 10Hz) 6 A

Power Dissipation Tcase = 70°C 85 W

, TjStorage and Junction Temperature -55 to 150 °C

V

V

T

V

op

V

peak

V

CK

DATA

I

O

I

O

P

tot

stg

THERMAL DATA

Symbol Parameter Value Unit

R

th j-case

Thermal Resistance Junction to case Max. 1 °C

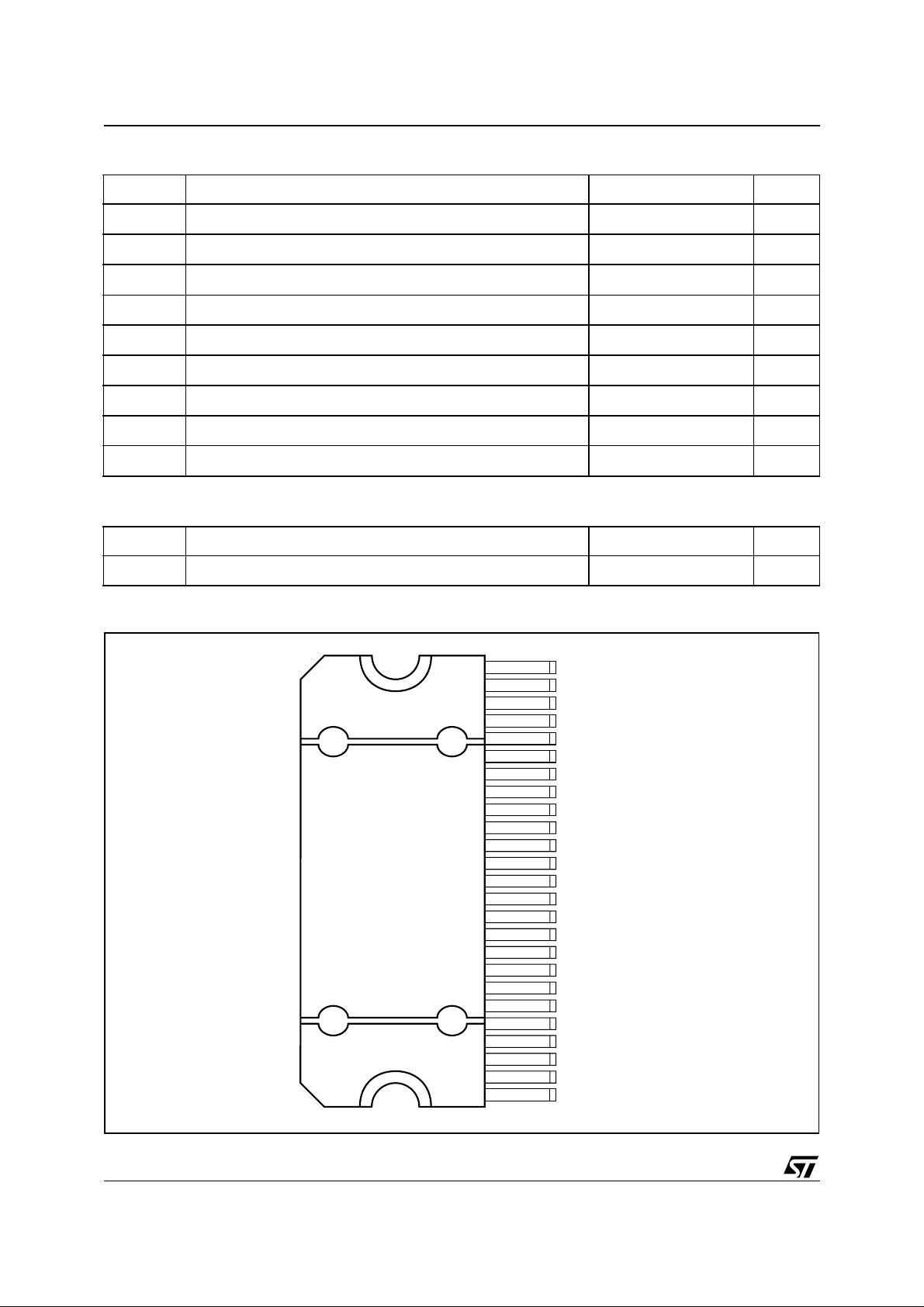

PIN CONNECTION

25

24

23

22

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

4

3

2

1

DATA

PW_GND RR

OUT RRCK

OUT RR+

V

CC2

OUT RFPW_GND RF

OUT RF+

AC GND

IN RF

IN RR

S GND

IN LR

IN LF

SVR

OUT LF+

PW_GND LF

OUT LFV

CC1

OUT LR+

CD-OUT

OUT LRPW_GND LR

TAB

D99AU1037

2/19

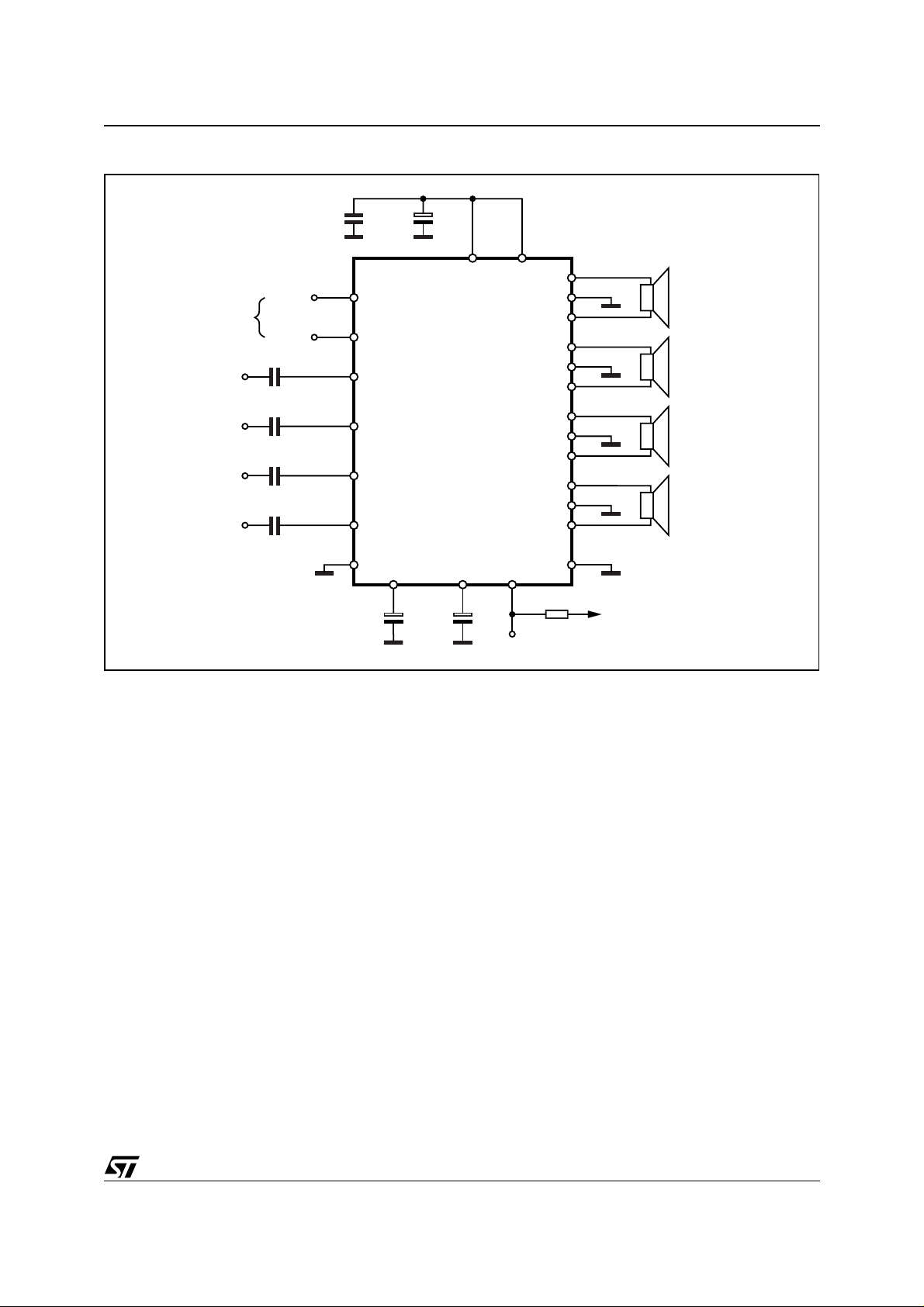

Figure 1. Tes t an d A pplication Ci rc ui t

TDA7561

I2C BUS

IN RF

IN RR

IN LF

IN LR

DATA

CLK

C1 0.22µF

C2 0.22µF

C3 0.22µF

C4 0.22µF

C8

0.1µF

S-GND

C7

3300µF

25

22

15

14

11

12

13

16 10 4

C5

1µF

C6

10µF

Vcc1 Vcc2

620

CD OUT

17

18

19

21

24

23

47K

+

OUT RF

+

OUT RR

+

9

8

7

+

5

2

3

TAB

1

V

OUT LF

OUT LR

D00AU1212

3/19

TDA7561

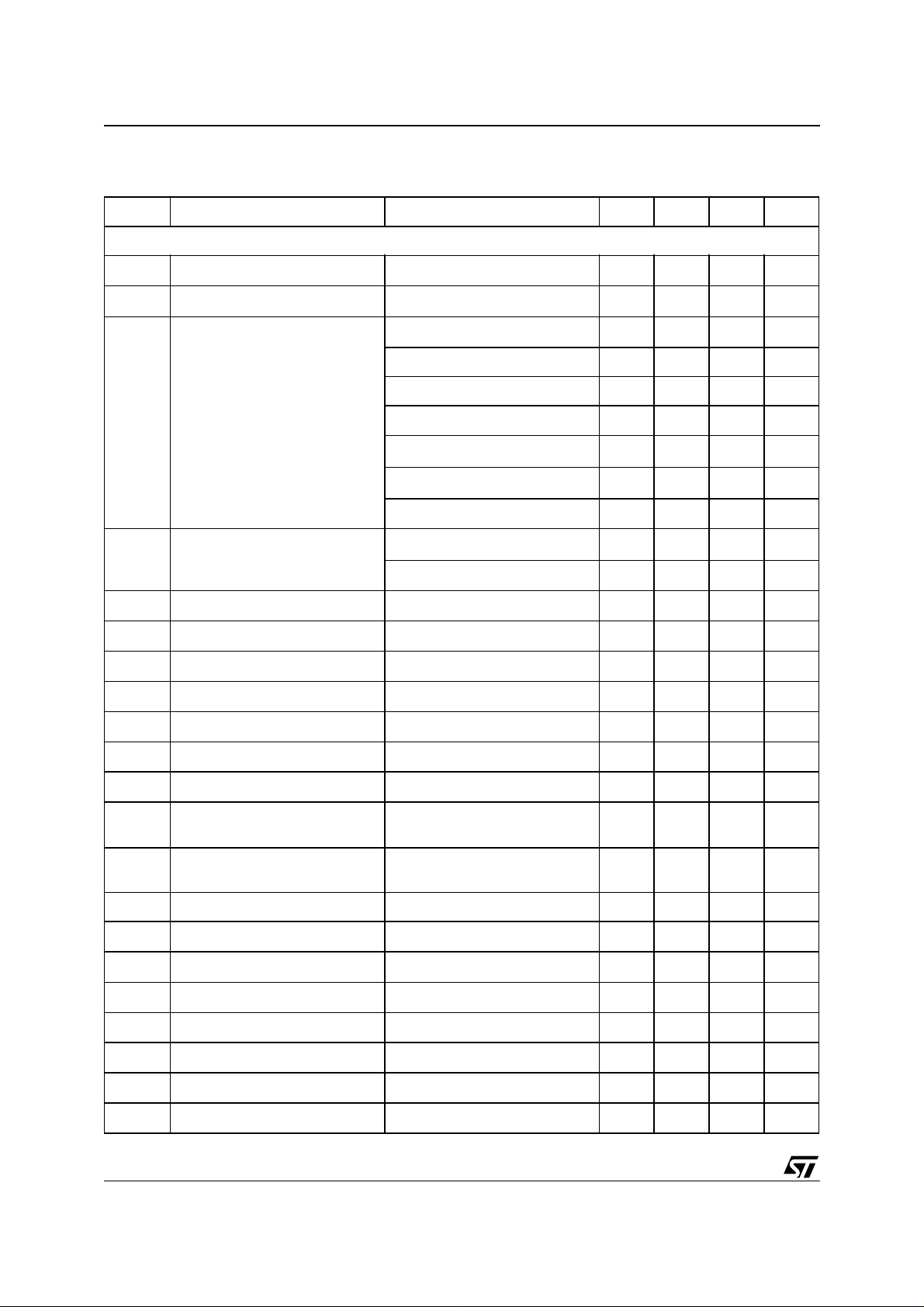

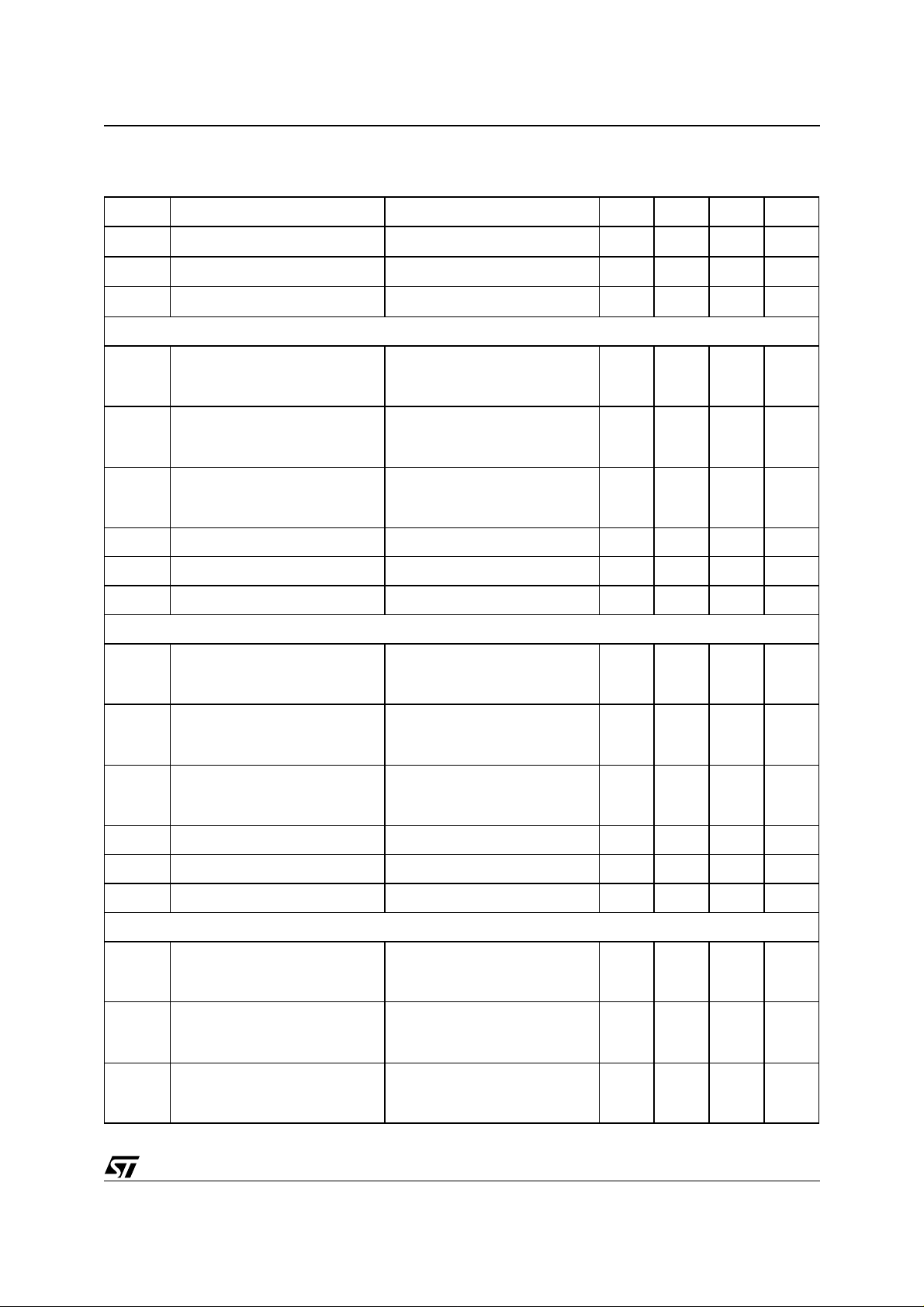

ELECTRICAL CHARACTERISTCS

(Refer to the test circuit, VS = 14.4V; RL = 4Ω; f = 1KHz;T

Symbol Parameter Test Condition Min. Typ. Max. Unit

POWER AMPLIFIER

= 25°C; unless otherwise specified).

amb

V

P

Supply Voltage Range 8 18 V

S

Total Quiescent Drain Current 150 300 mA

I

d

Output Power EIAJ (VS = 13.7V) 32 35 W

O

THD Total Harmonic Distortion

C

R

G

∆G

Cross Talk

T

Input Impedance 80 100 130 KΩ

IN

Voltage Gain 1 25 26 27 dB

V1

Voltage Gain Match 1 -1 1 dB

V1

THD = 10% 22 25 W

THD = 1% 20 W

= 2Ω; EIAJ (VS = 13.7V) 50 55 W

R

L

R

= 2Ω; THD 10%

L

R

= 2Ω; THD 1%

L

32 38 W

30 W

RL = 2Ω; MAX POWER 60 W

P

= 1W to 10W;

O

GV = 12dB; VO = 0.1 to 5V

RMS

f = 1KHz to 10KHz, RG = 600

Ω

50 60 dB

0.04 0.1 %

0.02 0.05 %

G

∆G

E

E

Voltage Gain 2 11 12 13 dB

V2

Voltage Gain Match 2 -1 1 dB

V2

Output Noise Voltage 1 Rg = 600Ω, 20Hz to 22kHz 35 80 µV

IN1

Output Noise Voltage 2 Rg = 600Ω; GV = 12dB

IN2

12 20 µV

20Hz to 22kHz

SVR Supply Voltage Rejection f = 100Hz to 10kHz;

50 60 dB

Vr = 1Vpk; Rg = 600Ω

BW Power Bandwidth 100 KHz

A

I

A

V

V

T

T

Stand-by Attenuation 90 110 dB

SB

Stand-by Current 25 100 µA

SB

Mute Attenuation 80 100 dB

M

Offset Voltage Mute & Play -100 0 100 mV

OS

Min. Supply Mute Threshold 7 7.5 8 V

AM

Turn on Delay D2/D1 (IB1) 0 to 1 20 40 ms

ON

Turn off Delay D2/D1 (IB1) 1 to 0 20 40 ms

OFF

4/19

TDA7561

ELECTRICAL CHARACTERISTCS

(Refer to the test circuit, VS = 14.4V; RL = 4Ω; f = 1KHz;T

(continued)

= 25°C; unless otherwise specified).

amb

Symbol Parameter Test Condition Min. Typ. Max. Unit

CD

CD

CD

Clip Det High Leakage Current CD off 0 15 µA

LK

Clip Det Sat. Voltage CD on; ICD = 1mA 150 300 mV

SAT

Clip Det THD level 1 2 %

THD

TURN ON DIAGNOSTICS 1 (Power Amplifier Mode)

Pgnd Short to GND det. (below this

Power Amplifier in st-by condition 1.2 V

limit, the Output is considered in

Short Circuit to GND)

Pvs Short to Vs det. (above this limit,

Vs -1.2 V

the Output isconsidered in Short

Circuit to V

Pnop Normal operation thresholds.

)

S

1.8 Vs -1.8 V

(Within these limits, the Output

is considered without faults).

Lsc Shorted Load det. 0.5 Ω

Lop Open Load det. 130 Ω

Lnop Normal Load det. 1.5 70 Ω

TURN ON DIAGNOSTICS 2 (Line Driver Mode)

Pgnd Short to GND det. (below this

Power Amplifier in st-by 1.2 V

limit, the Output is considered in

Short Circuit to GND)

Pvs Short to Vs det. (above this limit,

Vs -1.2 V

the Output isconsidered in Short

Circuit to V

Pnop Normal operation thresholds.

)

S

1.8 Vs -1.8 V

(Within these limits, the Output is

considered witho ut faults).

Lsc Shorted Load det. 1.5 &

Lop Open Load det. 400 &

Lnop Normal Load det. 4.5 200 &

PERMANENT DIAGNOSTICS 2 (Power Amplifier Mode or Line Driver Mode)

Pgnd Short to GND det. (below this

limit, the Output is considered in

Short Circuit to GND)

Pvs Short to Vs det. (above this limit,

Power Amplifier in Mute or Play,

one or more short circuits

protection activated

1.2 V

Vs -1.2 V

the Output is considered in Short

Circuit to V

Pnop Normal operation thresholds.

)

S

1.8 Vs -1.8 V

(Within these limits, the Output is

considered witho ut faults)

5/19

TDA7561

(V)

(V)

(V)

(W)

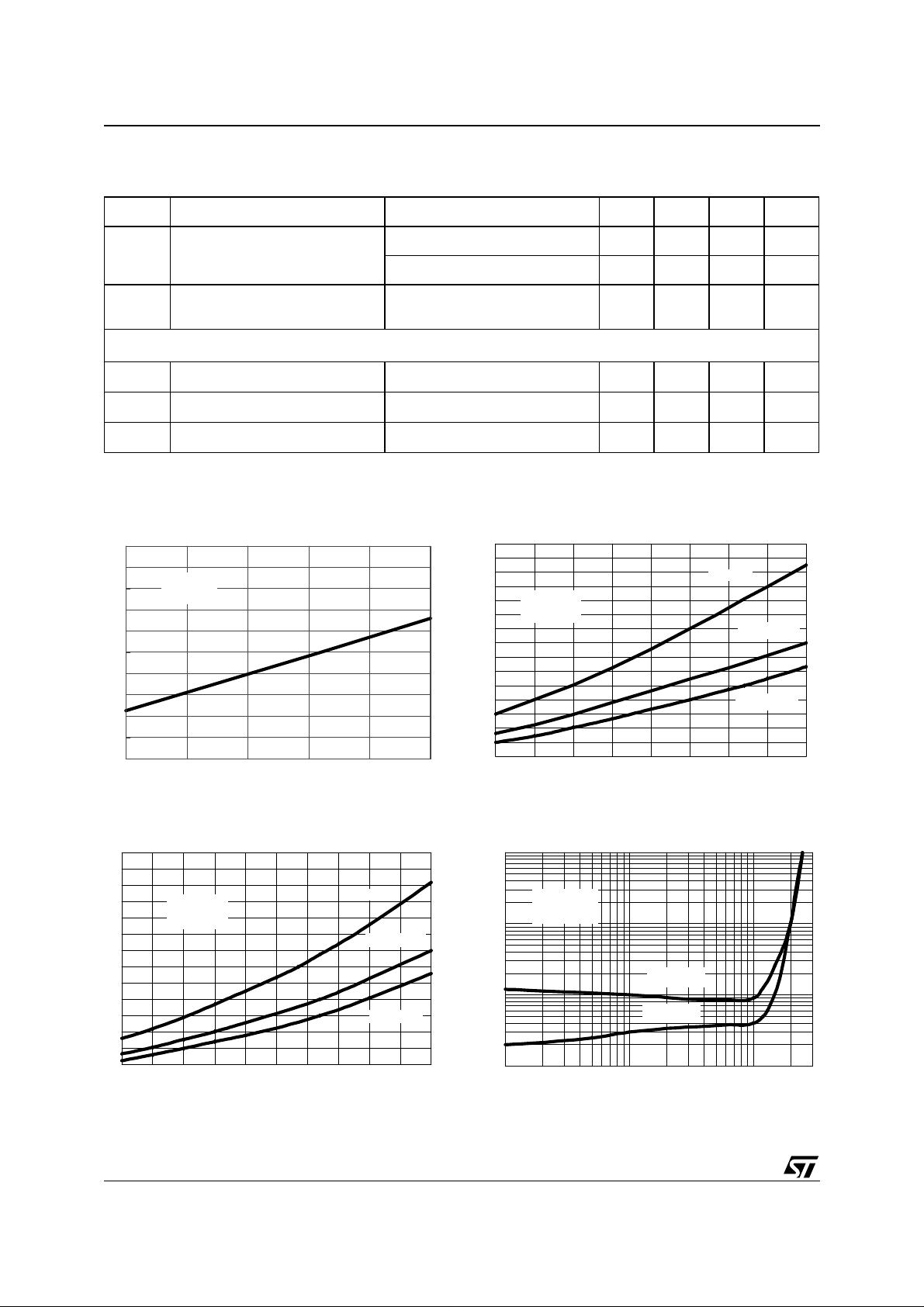

ELECTRICAL CHARACTERISTCS

(Refer to the test circuit, VS = 14.4V; RL = 4Ω; f = 1KHz;T

(continued)

= 25°C; unless otherwise specified).

amb

Symbol Parameter Test Condition Min. Typ. Max. Unit

L

Shorted Load det. Power Amplifier mode 0.5 Ω

SC

Line Driver mode 1.5 Ω

V

Offset Detection Power Amplifier in play, AC Input

O

1.5 2 2.5 V

signals = 0

2

I

C BUS INTERFACE

f

SCL

V

V

Figure 2. Quiescent Current vs. Supply Voltage

Id (mA)

250

230

210

190

170

150

130

110

90

70

50

8 1012141618

Clock Frequency 400 KHz

Input Low Voltage 1.5 V

IL

Input High Voltage 2.3 V

IH

Figure 4. Output Power vs. Supply Voltage (4Ω)

Po (W)

80

75

Vin = 0

NO LOADS

Vs

70

65

RL = 2 Ohm

60

f = 1 KHz

55

50

45

40

35

30

25

20

15

10

5

8 9 10 11 12 13 14 15 16

Vs

Po-max

THD= 10 %

THD= 1 %

Figure 3. Output Power vs. Supply Voltage (2Ω)

Po (W)

70

65

60

55

50

45

40

35

30

25

20

15

10

5

8 9 10 11 12 13 14 15 16 17 18

RL = 4 Ohm

f = 1 KHz

Vs

6/19

Po-max

THD= 10 %

THD= 1 %

Figure 5. Disto rti on v s. Out p ut Po wer (2Ω)

THD (%)

10

Vs = 14.4 V

RL = 4 Ohm

1

f = 10 KHz

0.1

f = 1 KHz

0.01

0.1 1 10

Po

Loading...

Loading...