SGS Thomson Microelectronics TDA7553, TDA7552, TDA7551, TDA7550R, TDA7550 Datasheet

TDA7550/R TDA7551

®

DIGITAL SIGN AL PROCESS IN G IC FOR SPEE CH AND

24-BIT, FIXED POINT, 50 MIPS DSP CORE

LARGE ON-BOARD PROGRAM ROM AND

DATA RAM (UP TO 16Kw ROM/RAM AND

16Kw RAM)

INTEGRAT ED ST EREO A/D AND D/A, 16 -BI T

SIGMA-DELTA

PROGRAMMABLE CODEC SAMPLE RATE

FROM 4 TO 48 kHz

ON-BOARD PLL FOR CORE CLOCK AND

CONVERTERS

MANAGEMENT OF EXTERNAL

FLASH/ SRAM/DR AM MEMORY BANK

I2C OR SPI SERIAL INTERFACE FOR EXTERNAL CONTROL

80-PIN TQFP, 0.65 mm PITCH

AUTOMOTIVE GRADE (FROM -40° C to

+85°C)

DESCRIPTION

The TDA755X family is a high performances, fully

programmable 24-bit, 50 MIPS Digital Signal

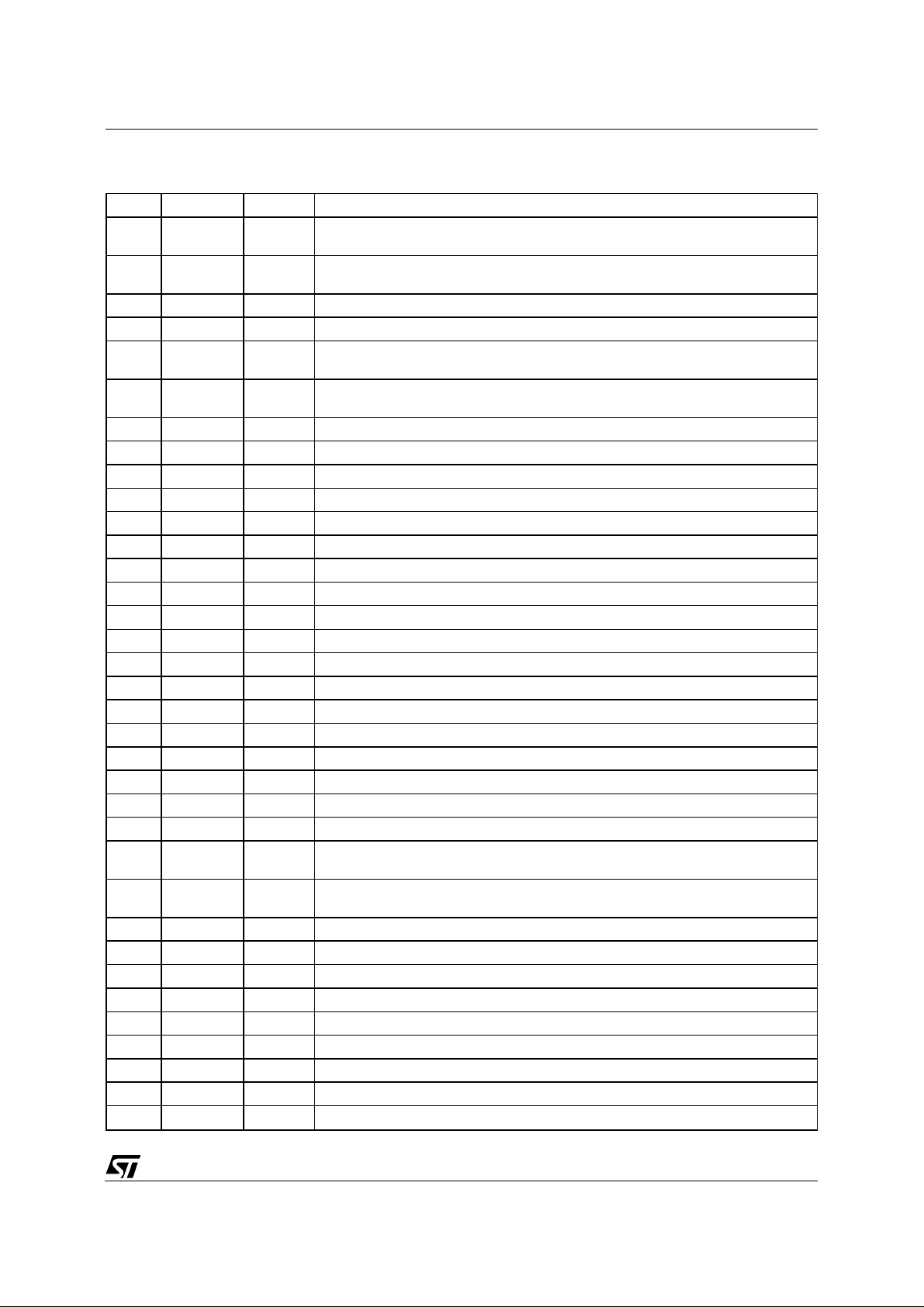

BLOCK DIAGRAM

TDA7552 TDA7553

AUDIO APPLICATIO NS

PRODUCT PREVIEW

TQFP80

Processor (DSP), designed to support several

speech and audio applications, as Automatic

Speech Recognition, Speech Synthesis, Speaker

Verification, Echo and Noise Cancellation. Software for these applications is licenced by Lernout

& Hauspie and NCTI.

It offers an effective solution for this kind of applications because of the A/D and D/A converters

and the big amount of memory integrated on chip.

MULTIPLEXED BUS

I2C/SPI

PORT

8

FLAGS

September 1999

This is preliminary information on a new product now in development. Details are subject to change without notice.

FLASH

INTERFACE

SAI ROM/RAM

DSP

CORE

PLL

DAC

ADC

RAM

L

R

L

R

ANALOG OUT

ANALOG IN

D99AU1020A

1/12

TDA7550R - TDA7550 - TDA7551 - TDA7552 - TDA7553

APPLICATIONS

Real time digital speech and audio processing:

compression, echo cancelling, noise cancelling,

speaker verification.

speech recognition, speech synthesis, speech

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DDP

VD, V

T

T

P

IN

op

stg

tot

Pads DC Supply Voltage –0.3 to VDD +0.3 V

Digital or Analog Input Voltage –0.3 to V

+0.3 V

DDP

Operating Temperature Range –40 to +85 °C

Storage Temperature Range –55 to +150 °C

Total Maximum Power Dissipation mW

PIN CONNECTION

DRDN

GND

ALE

XTO

PGND

PVCC

XTI

CLKOUT

VDD

GPIO4

GPIO7

REFCAP

VREF

CVDDA

TEST4

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

CGNDA

VINL

VINR

GND

VDD

VOUTL

VOUTR

CVDD

CGND

GPIO3

GPIO6

GPIO2

GND

VDD

SDA/SS

SCL/SCK

INTN

NRESET

DBRQN

DBOUT

EMI_AD5

EMI_AD6

VDD

GND

EMI_AD7

EMI_A8

EMI_A7

EMI_A10

EMI_A11

EMI_A12

EMI_A13

EMI_A14

EMI_A15

VDD

GND

EMI_A16

EMI_A17

EMI_A18

EMI_A19

EMI_A20

EMI_AD3

EMI_AD4

79

80

1

2

3

4

5

6

7

8

9

10

12

13

14

15

16

17

18

19

20

21 22 23 24 25

EMI_AD2

77

78

EMI_AD0

EMI_AD1

76

75 74 73 72 7071 69 68 67 66 65

26 27 28 29 30

311132 33 34 35 36

64 63 62 61

37 38 39 40

2/12

DWRN

EMI_A21

TEST1

TEST2

MISO

MOSI

VDD

GND

SDI

TEST3

SCK

LRCK

VDD

GND

SDO

GPIO1

GPIO0

DBCK

GPIO5

DBIN

TQFP80

TDA7550R - TDA7550 - TDA7551 - TDA7552 - TDA7553

PIN FUNCTIONS

N. Name Type Description

1 EMI_AD5 I/O EMI Multiplexed Address/Data Line 5. these pin acts as the EMI multiplexed

2 EMI_AD6 I/O EMI Multiplexed Address/Data Line 6. these pin acts as the EMI multiplexed

3 VDD I Digital power supply

4 GND I Ground

5 EMI_AD7 I/O EMI Multiplexed Address/Data Line 7. these pin acts as the EMI multiplexed

6 EMI_A8 O EMI Address Line 8. these pin acts as the EMI address line 8. The interface is

7 EMI_A9 O EMI Address Line 9. these pin acts as the EMI address line 9.

8 EMI_A10 O EMI Address Line 10. these pin acts as the EMI address line 10.

9 EMI_A11 O EMI Address Line 11. these pin acts as the EMI address line 11.

10 EMI_A12 O EMI Address Line 12. these pin acts as the EMI address line 12.

11 EMI_A13 O EMI Address Line 13. these pin acts as the EMI address line 13.

12 EMI_A14 O EMI Address Line 14. these pin acts as the EMI address line 14.

13 EMI_A15 O EMI Address Line 15. these pin acts as the EMI address line 15.

14 VDD I Digital power supply

15 GND I Ground

16 EMI_A16 O EMI Address Line 16. these pin acts as the EMI address line 16.

17 EMI_A17 O EMI Address Line 17. these pin acts as the EMI address line 17.

18 EMI_A18 O EMI Address Line 18. these pin acts as the EMI address line 18.

19 EMI_A19 O EMI Address Line 19. these pin acts as the EMI address line 19.

20 EMI_A20 O EMI Address Line 20. these pin acts as the EMI address line 20.

21 EMI_A21 O EMI Address Line 21. these pin acts as the EMI address line 21.

22 DWRN O EMI Write Enable. This pin serves as the write enable for the EMI

23 TEST1 I Test 1. Used for test: set to LOW for normal operation

24 TEST2 I Test 2. Used for test: set to HIGH for normal operation

25 MISO I/O SPI Master Output Slave Input Serial Data. Serial Data Output for SPI type serial

26 MOSI I/O SPI Master Input Slave Output Serial Data. Serial Data Input for SPI type serial

27 VDD I Digital Power Supply

28 GND I Ground

29 TEST3 I Test 3. Used for test: set to LOW for normal operation

30 SDI I SAI Data Input

31 SCK I/O SAI Bit Clock

32 LRCK I/O SAI Left/Right Clock

33 VDD I Digital power supply

34 GND I Ground

35 SDO O SAI Data Output

address and data line 5

address and data line 6

address and data line 7

designed to address up to 4 Mbytes of External Flash, EPROM or SRAM.

Port when in SPI master Mode and Serial Data Input when in SPI Slave Mode

Port when in SPI master Mode and Serial Data Output when in SPI Slave Mode

3/12

TDA7550R - TDA7550 - TDA7551 - TDA7552 - TDA7553

PIN FUNCTIONS

N. Name Type Description

36 GPIO1 I/O General Purpose I/O

37 GPIO0 I/O General Purpose I/O

38 GPIO5 I/O General Purpose I/O

39 DBCK I/O Debug port Bit Clock/Chip Status 1. The serial clock for the Debug Port is

40 DBIN I/O Debug port Serial Input/Chip Status 0. The serial data input for the Debug Port is

41 DBOUT I/O Debug Port Serial Output. This pin is the serial Data output for the Debug port.

42 DBRQN I Debug Port Request Input. This pin is used to request Debug Mode operation to

43 NRESET I System Reset. A low level applied to RESET input initializes the IC.

44 INTN I External interrupt line. When this line is asserted low the DSP may be interrupted.

45 SCL/SCK I/O I

46 SDA/SS I/O I2C Serial Data Line. Data line for I2C bus. Schmitt trigger input.

47 VDD I Digital Power Supply

48 GND I Ground

49 GPIO2 I/O General Purpose I/O

50 GPIO6 I/O General Purpose I/O

51 GPIO3 I/O General Purpose I/O

52 CGND I Ground for the internal CODEC cell

53 CVDD I Power Supply for the internal CODEC cell

54 VOUTR O Single-ended right channel analogue output from DAC

55 VOUTL O Single-ended left channel analogue output from DAC

56 VDD I Digital power supply

57 GND I Ground

58 VINR I Single-ended right channel analogue input to ADC

59 VINL I Single-ended left channel analogue input to ADC

60 CGNDA I Ground for the internal CODEC cell

61 TEST4 O Connect a 22K pull-down resistor

62 CVDDA I Power Supply for the internal CODEC cell

63 VREF O Voltage Reference from the CODEC cell

64 REFCAP O Voltage Reference Capacitor Bypass

65 GPIO7 I/O General Purpose I/O

66 GPIO4 I/O General Purpose I/O

67 VDD I Digital power supply

68 CLKOUT O Clock Output. Output Clock divided down from PLL

(continued)

provided. May also be used as GPIO9.

provided. May also be used as GPIO11.

May also be used as GPIO10.

Euterpe

2

C Serial Clock Line. Clock line for I2C bus. Schmitt trigger input.

I/O SPI Bit Clock. If SPI interface is enabled, it behaves as SPI bit clock.

I SPI Slave Select. If SPI interface is enabled, it behaves as Slave select line for

SPI bus.

4/12

Loading...

Loading...