DIGITALLY CONTROLLED AUDIO PROCESSOR

INPUTMULTIPLEXER

- 2 STEREO INPUTS

- SELECTABLEINPUT GAIN FOR OPTIMAL

ADAPTATIONTO DIFFERENT SOURCES

ONE STEREO OUTPUT

VOLUMECONTROL IN 1.0dB STEPS

TWOSPEAKERATTENUATORS:

- TWOINDEPENDENTSPEAKERCONTROL

IN 1.0dBSTEPS FOR BALANCEFACILITY

- INDEPENDENTMUTE FUNCTION

ALL FUNCTION ARE PROGRAMMABLE VIA

SERIALBUS

DESCRIPTION

The TDA7449L is a volume control and balance

(Left/Right) processor for quality audio applications in TV systems.

Selectable input gain is provided. Control of all

the functions is accomplishedby serialbus.

The AC signal setting is obtained by resistor net-

TDA7449L

LOW COST

DIP20

ORDERING NUMBER: TDA7449L

works and switches combined with operational

amplifiers.

Thanks to the used BIPOLAR/CMOSTechnology,

Low Distortion, Low Noise and DC stepping are

obtained.

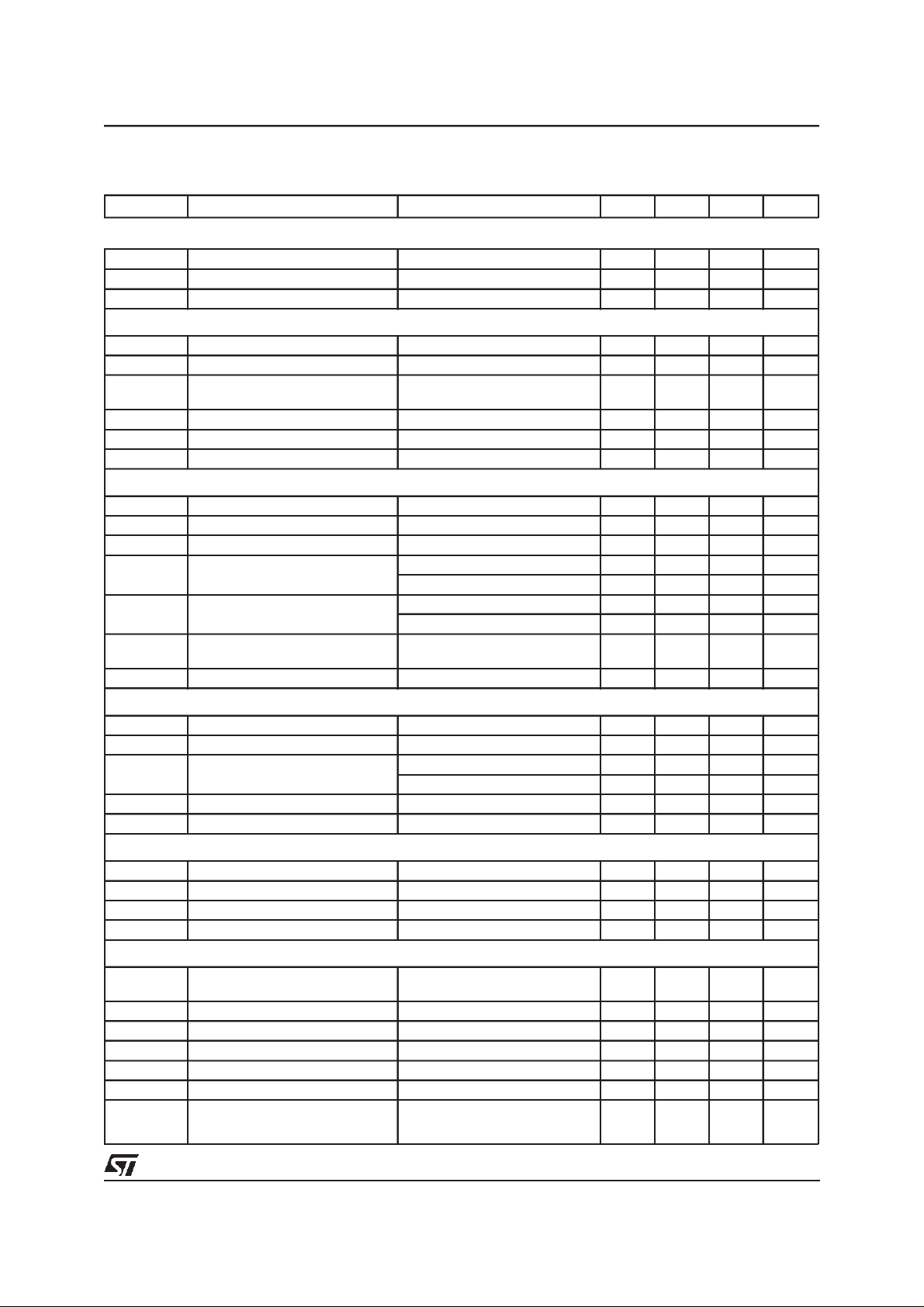

BLOCK DIAGRAM

L-IN1

L-IN2

R-IN1

R-IN2

MUXOUTL

8

100K

9

100K

7

100K

6

100K

INPUT

G

0/30dB

2dB STEP

G

MULTIPLEXER

+ GAIN

10

VOLUME

I2CBUS DECODER + LATCHES

VOLUME

11 1

MUXOUTR

SPKR ATT

LEFT

SPKR ATT

RIGHT

V

REF

SUPPLY

CREF

5

19

20

18

4

2

3

LOUT

SCL

SDA

DIG_GND

ROUT

V

S

AGND

D98AU868

April 1999

1/13

TDA7449L

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

T

amb

T

stg

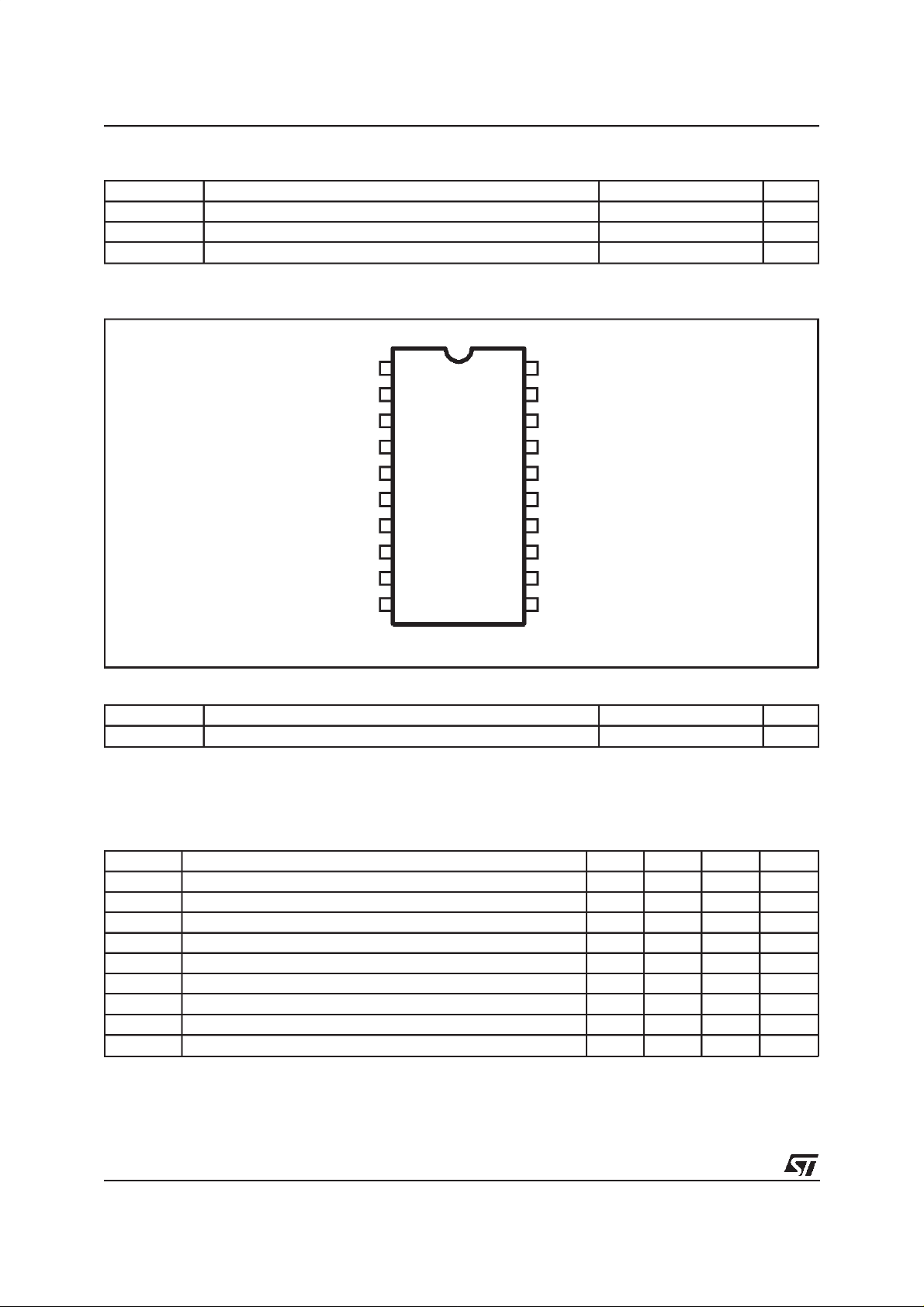

PIN CONNECTION

Operating Supply Voltage 10.5 V

Operating Ambient Temperature -10 to 85 °C

Storage Temperature Range -55 to 150 °C

CREF

V

PGND

ROUT

LOUT

R_IN2

R_IN1

L_IN1

L_IN2

1

2

S

3

4

5

6

7

8

9 N.C.

19

18

17

16

15

14

13

12

SDA20

SCL

DIG_GND

N.C.

N.C.

N.C.

N.C.

N.C.

MUXOUT(L) 10 MUXOUT(R)11

D98AU869

THERMAL DATA

Symbol Parameter Value Unit

R

thj-pin

Thermal ResistanceJunction-pins 150 °C/W

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

S

V

CL

THD Total Harmonic DistortionV = 1Vrms f = 1KHz 0.01 0.1 %

S/N Signal to Noise Ratio V

S

C

2/13

Supply Voltage 6 9 10.2 V

Max. input signal handling 2 Vrms

= 1Vrms (mode = OFF) 106 dB

out

Channel Separation f = 1KHz 90 dB

Input Gain in (2dBstep) 0 30 dB

Volume Control (1dB step) -47 0 dB

Balance Control 1dB step -79 0 dB

Mute Attenuation 100 dB

TDA7449L

ELECTRICALCHARACTERISTICS

R

= 600Ω, all controls flat (G = 0dB), unless otherwise specified)

G

(refer to the test circuit T

=25°C,VS= 9V,RL= 10KΩ,

amb

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

I

S

SVR Ripple Rejection 60 90 dB

Supply Voltage 6 9 10.2 V

Supply Current 7 mA

INPUT STAGE

G

G

R

V

S

inmin

inman

G

IN

CL

IN

step

Input Resistance 100 KΩ

Clipping Level THD = 0.3% 2 2.5 Vrms

Input Separation The selected input is grounded

80 100 dB

through a 2.2µ capacitor

Minimum Input Gain -1 0 1 dB

Maximum Input Gain 30 dB

Step Resolution 2 dB

VOLUMECONTROL

C

RANGE

A

A

V

A

VMAX

STEP

E

A

E

T

DC

mute

Control Range 45 47 49 dB

Max. Attenuation 45 47 49 dB

Step Resolution 0.5 1 1.5 dB

Attenuation Set Error AV= 0 to-24dB -1.0 0 1.0 dB

A

= -24 to -47dB -1.5 0 1.5 dB

V

Tracking Error AV= 0 to-24dB 0 1 dB

= -24 to -47dB 0 2 dB

A

V

DC Step adjacent attenuation steps

from 0dB to A

V

max

0

0.5

3mV

Mute Attenuation 80 100 dB

SPEAKERATTENUATORS

C

RANGE

S

V

A

STEP

E

A

DC

mute

Control Range 76 dB

Step Resolution 0.5 1 1.5 dB

Attenuation Set Error AV= 0 to-20dB -1.5 0 1.5 dB

A

= -20 to -56dB -2 0 2 dB

V

DC Step adjacent attenuation steps 0 3 mV

Mute Attenuation 80 100 dB

AUDIO OUTPUTS

V

CLIP

R

L

R

O

V

DC

Clipping Level d = 0.3% 2.1 2.6 V

Output Load Resistance 2 KΩ

Output Impedance 10 40 70

DC Voltage Level 3.8 V

mV

RMS

Ω

GENERAL

E

NO

E

S/N Signal to Noise Ratio Allgains 0dB; V

S

C

d Distortion A

Output Noise All gains = 0dB;

BW = 20Hz to 20KHz flat

Total TrackingError AV= 0 to-24dB 0 1 dB

t

A

= -24 to -47dB 0 2 dB

V

Channel Separation Left/Right 80 100 dB

=0;VI=1V

V

BUS INPUT

515µV

O =1VRMS ; 106 dB

; 0.01 0.08 %

RMS

3/13

TDA7449L

ELECTRICALCHARACTERISTICS

(continued.)

Symbol Parameter Test Condition Min. Typ. Max. Unit

BUS INPUT

V

IL

V

IH

I

IN

V

O

Input Low Voltage 1V

Input High Voltage 3 V

Input Current VIN= 0.4V -5 5

Output Voltage SDA

IO = 1.6mA 0.4 0.8 V

Acknowledge

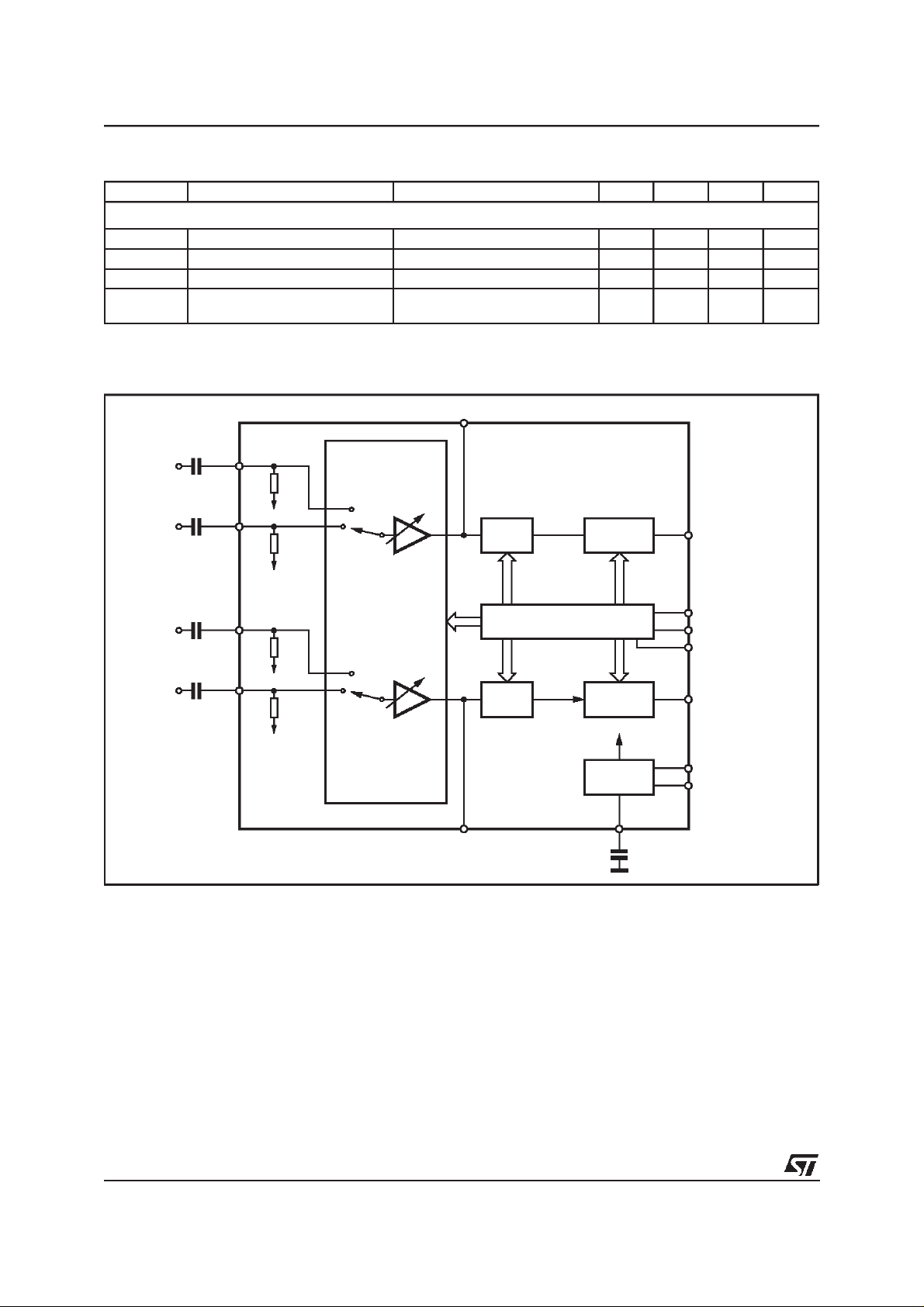

TEST CIRCUIT

MUXOUTL

10

8

L-IN1

0.47µF

L-IN2

0.47µF

R-IN1

0.47µF

100K

9

100K

7

100K

G

0/30dB

2dB STEP

VOLUME

I2CBUS DECODER + LATCHES

SPKR ATT

LEFT

19

20

18

5

LOUT

SCL

SDA

DIG_GND

A

µ

6

R-IN2

0.47µF

100K

INPUT MULTIPLEXER

G

+ GAIN

APPLICATIONSUGGESTIONS

The first and the last stages are volume control

blocks. The control range is 0 to -47dB (mute) for

the first one, 0 to -79dB (mute) for the last one.

Both of them have 1dB step resolution.

The very high resolutionallows the implementation

of systemsfreefromanynoisyacousticaleffect.

10µF

4

2

3

D98AU870

ROUT

V

S

AGND

VOLUME

11 1

MUXOUTR

SPKR ATT

RIGHT

V

REF

SUPPLY

CREF

The TDA7449L audioprocessor provides 2 bands

tonescontrol.

CREF

The suggested 10µF reference capacitor (CREF)

value can be reduced to 4.7µF if the application

requiresfasterpower ON.

4/13

TDA7449L

Figure 2:

Figure 4:

THD vs. frequency

Channelseparationvs. frequency

Figure3:

THDvs. R

LOAD

5/13

TDA7449L

2

C BUS INTERFACE

I

Data transmission from microprocessor to the

TDA7449L and vice versa takes place through

the 2 wires I

2

C BUS interface, consisting of the

two lines SDA and SCL (pull-up resistors to positive supply voltage must be connected).

Data Validity

As shown in fig. 3, thedata on the SDA line must

be stable during the high period of the clock. The

HIGH and LOW state of the data line can only

change when the clock signal on the SCL line is

LOW.

Start and Stop Conditions

As shown in fig.4 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred on the SDA line must contain 8 bits. Each byte must be followed by an ac-

Figure 3:

Data Validityon theI

2

CBUS

knowledgebit. The MSB is transferredfirst.

Acknowledge

The master (µP)puts a resistiveHIGH level on the

SDA line during the acknowledgeclock pulse (see

fig. 5). The peripheral (audio processor) that acknowledges has to pull-down (LOW) the SDA line

duringthisclock pulse.

The audio processor which has been addressed

has to generate an acknowledge after the reception of each byte, otherwise the SDAline remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can generate the STOP information in order to abort the

transfer.

Transmissionwithout Acknowledge

Avoiding to detect the acknowledge of the audio

processor,the µP canuse a simplertransmission:

simply it waits one clock without checking the

slaveacknowledging,and sends the new data.

This approach of course is less protected from

misworking.

Figure 4:

TimingDiagram of I

2

Figure 5: Acknowledgeon the I

6/13

CBUS

2

CBUS

TDA7449L

SOFTWARESPECIFICATION

InterfaceProtocol

The interface protocol comprises:

A start condition (S)

address

A subaddressbytes

A sequenceof data (N byte + acknowledge)

A stopcondition (P)

A chip addressbyte, containingthe TDA7449L

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10001000ACK ACK DATA ACK P

D96AU420

SUBADDRESS DATA 1 to DATA n

X DATA

XXB

ACK = Acknowledge

S = Start

P = Stop

A = Address

B = Auto Increment

EXAMPLES

No IncrementalBus

rect chip address, a subaddress with the B = 0

(no incremental bus), N-data (all these data concern the subaddressselected),a stop condition.

The TDA7449L receives a startcondition,the cor-

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10001000ACK ACK DATA ACK P

D96AU421

IncrementalBus

The TDA7449L receive a start conditions, the

correct chip address, a subaddresswith the B = 1

(incremental bus): now it is in a loop condition

with an autoincreaseof the subaddress whereas

CHIP ADDRESS

MSB LSB MSB LSB MSB LSB

S10001000ACK ACK DATA ACK P

D96AU422

SUBADDRESS DATA

XD3

XX0 D2D1D0

SUBADDRESS from ”XXX1000” to ”XXX1111”of

DATAare ignored.

The DATA 1 concern the subaddress sent, and

the DATA 2 concern the subaddress sent plus

one in the loop etc, and at the end it receivers the

stop condition.

SUBADDRESS DATA 1 to DATA n

XD3

XX1 D2D1D0

7/13

TDA7449L

POWERON RESET CONDITION

INPUT SELECTION IN2

INPUT GAIN 28dB

VOLUME MUTE

SPEAKER MUTE

DATA BYTES

Address = 88 HEX (ADDR:OPEN).

FUNCTIONSELECTION:First byte (subaddress)

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0

XXXB00 00INPUT SELECT

XXXB00 01INPUT GAIN

XXXB00 10VOLUME

XXXB00 11NOTUSED

XXXB01 00NOTUSED

XXXB01 01NOTUSED

XXXB01 10SPEAKER ATTENUATE ”R”

XXXB01 11SPEAKER ATTENUATE ”L”

B = 1: INCREMENTAL BUSACTIVE

B = 0: NO INCREMENTALBUS

X = DON’T CARE

SUBADDRESS

In IncrementalBus Mode, the three ”not used” functions must be addressedin any case. For example to

refresh ”Volume= 0dB”and Speaker_R= -40dB”,the followingbytes mustbe sent:

SUBADDRESS XXX10010

VOLUME DATA X0000000

NOT USED 1 DATA XXXX1111

NOT USED 2 DATA XXXX1111

NOT USED 3 DATA XXXX1111

SPEAKER_R DATA X0000010

INPUT SELECTION

MSB LSB

D7 D6 D5 D4 D3 D2 D1 D0

XXXXXX00 NOTALLOWED

XXXXXX01 NOTALLOWED

XXXXXX10 IN2

XXXXXX11 IN1

8/13

INPUT MULTIPLEXER

DATA BYTES (continued)

INPUT GAIN SELECTION

MSB LSB INPUT GAIN

D7 D6 D5 D4 D3 D2 D1 D0 2dB STEPS

0000 0dB

0001 2dB

0010 4dB

0011 6dB

0100 8dB

0 1 0 1 10dB

0 1 1 0 12dB

0 1 1 1 14dB

1 0 0 0 16dB

1 0 0 1 18dB

1 0 1 0 20dB

1 0 1 1 22dB

1 1 0 0 24dB

1 1 0 1 26dB

1 1 1 0 28dB

1 1 1 1 30dB

TDA7449L

GAIN = 0 to 30dB

VOLUMESELECTION

MSB LSB VOLUME

D7 D6 D5 D4 D3 D2 D1 D0 1dB STEPS

0 0 0 0dB

0 0 1 -1dB

0 1 0 -2dB

0 1 1 -3dB

1 0 0 -4dB

1 0 1 -5dB

1 1 0 -6dB

1 1 1 -7dB

0000 0dB

0 0 0 1 -8dB

0 0 1 0 -16dB

0 0 1 1 -24dB

0 1 0 0 -32dB

0 1 0 1 -40dB

X 1 1 1 X X X MUTE

VOLUME = 0 to 47dB/MUTE

9/13

TDA7449L

DATA BYTES (continued)

SPEAKERATTENUATE SELECTION

MSB LSB SPEAKER ATTENUATION

D7 D6 D5 D4 D3 D2 D1 D0 1dB

0 0 0 0dB

0 0 1 -1dB

0 1 0 -2dB

0 1 1 -3dB

1 0 0 -4dB

1 0 1 -5dB

1 1 0 -6dB

1 1 1 -7dB

0000 0dB

0 0 0 1 -8dB

0 0 1 0 -16dB

0 0 1 1 -24dB

0 1 0 0 -32dB

0 1 0 1 -40dB

0 1 1 0 -48dB

0 1 1 1 -56dB

1 0 0 0 -64dB

1 0 0 1 -72dB

1 1 1 1 X X X MUTE

SPEAKER ATTENUATION = 0 to-79dB/MUTE

PIN: 1

V

S

V

S

20K

CREF

20K

D96AU430

PINS: 4,5

ROUT

LOUT

D96AU434

V

S

24

20µA

10/13

TDA7449L

PINS: 6,7,8,9

V

S

IN

PIN:

19

PINS: 10,11

V

S

20µA

MUXOUT

100K

V

REF

D96AU425

PIN:

20

20µA

V

S

20µA

GND

D96AU491

20µA

SCL

SDA

D96AU423

D96AU424

11/13

TDA7449L

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.254 0.010

B 1.39 1.65 0.055 0.065

b 0.45 0.018

b1 0.25 0.010

D 25.4 1.000

E 8.5 0.335

e 2.54 0.100

e3 22.86 0.900

F 7.1 0.280

I 3.93 0.155

L 3.3 0.130

Z 1.34 0.053

mm inch

OUTLINE AND

MECHANICAL DATA

DIP20

12/13

TDA7449L

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are

subject to change without notice. This publicationsupersedes and replaces all informationpreviously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

Australia - Brazil - Canada- China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands-

Singapore - Spain - Sweden- Switzerland - Taiwan - Thailand - UnitedKingdom - U.S.A.

The ST logo is a registered trademark of STMicroelectronics

1999STMicroelectronics – Printed in Italy– All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

http://www.st.com

13/13

Loading...

Loading...