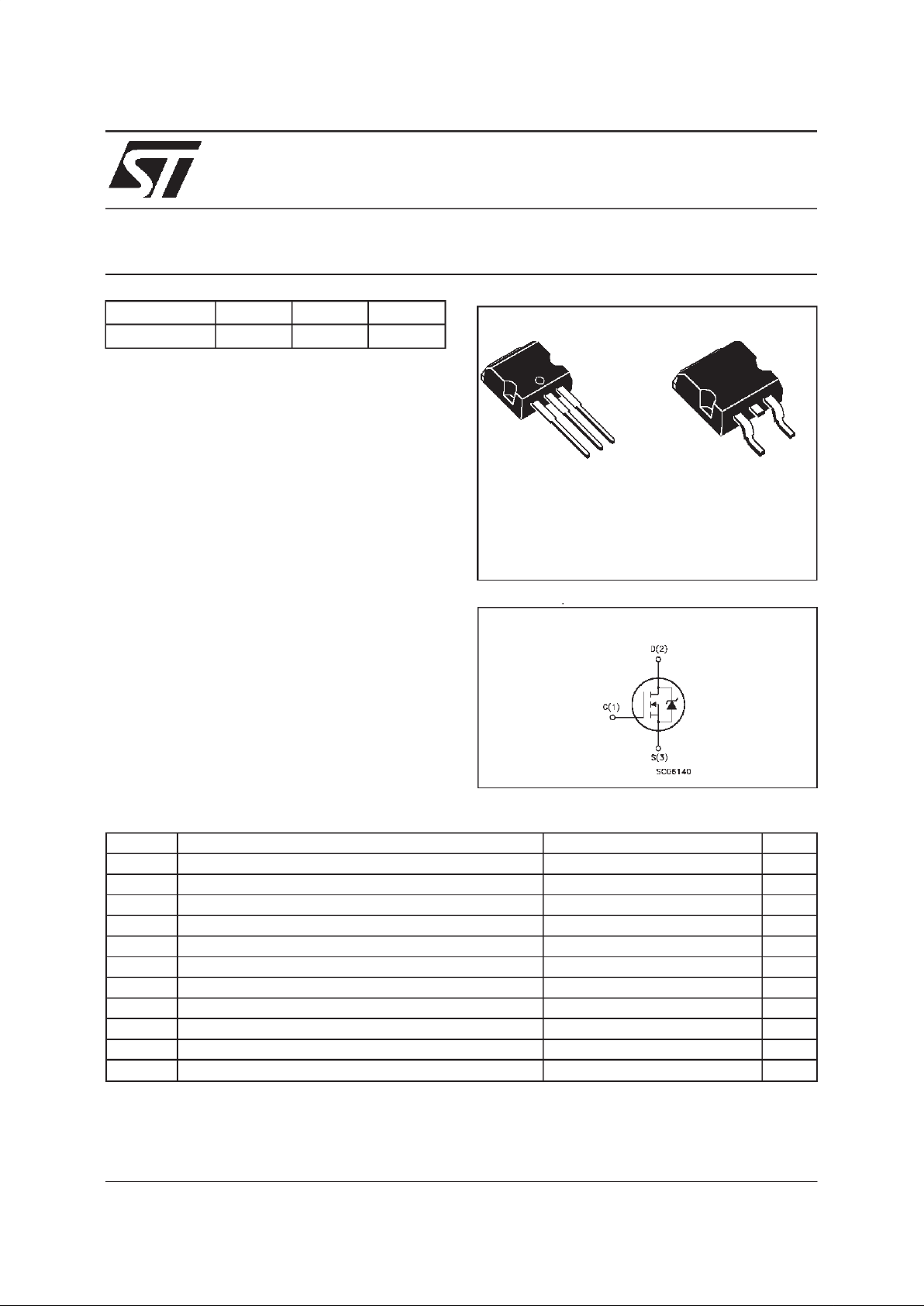

SGS Thomson Microelectronics STB10NC50 Datasheet

STB10NC50-1

N - CHANNEL 500V - 0.48Ω - 10A - I2PAK/D2PAK

PowerMESH MOSFET

PRELIMINARY DATA

■ TYPICALR

DS(on)

= 0.48 Ω

■ EXTREMELYHIGH dv/dt CAPABILITY

■ 100%AVALANCHETESTED

■ VERYLOW INTRINSIC CAPACITANCES

■ GATECHARGE MINIMIZED

DESCRIPTION

Using the latest high voltage MESH OVERLAY

process, STMicroelectronics has designed an

advanced family of power MOSFETs with

outstanding performances. The new patent

pending strip layout coupled with the Company’s

proprietary edge termination structure, gives the

lowest RDS(on) per area, exceptional avalanche

and dv/dt capabilities and unrivalled gate charge

and switching characteristics.

APPLICATIONS

■ HIGHCURRENT, HIGH SPEEDSWITCHING

■ SWITCHMODE POWER SUPPLIES(SMPS)

■ DC-AC CONVERTERS FOR WELDING

EQUIPMENTAND UNINTERRUPTIBLE

POWERSUPPLIESAND MOTORDRIVE

INTERNAL SCHEMATIC DIAGRAM

December 1999

1

2

3

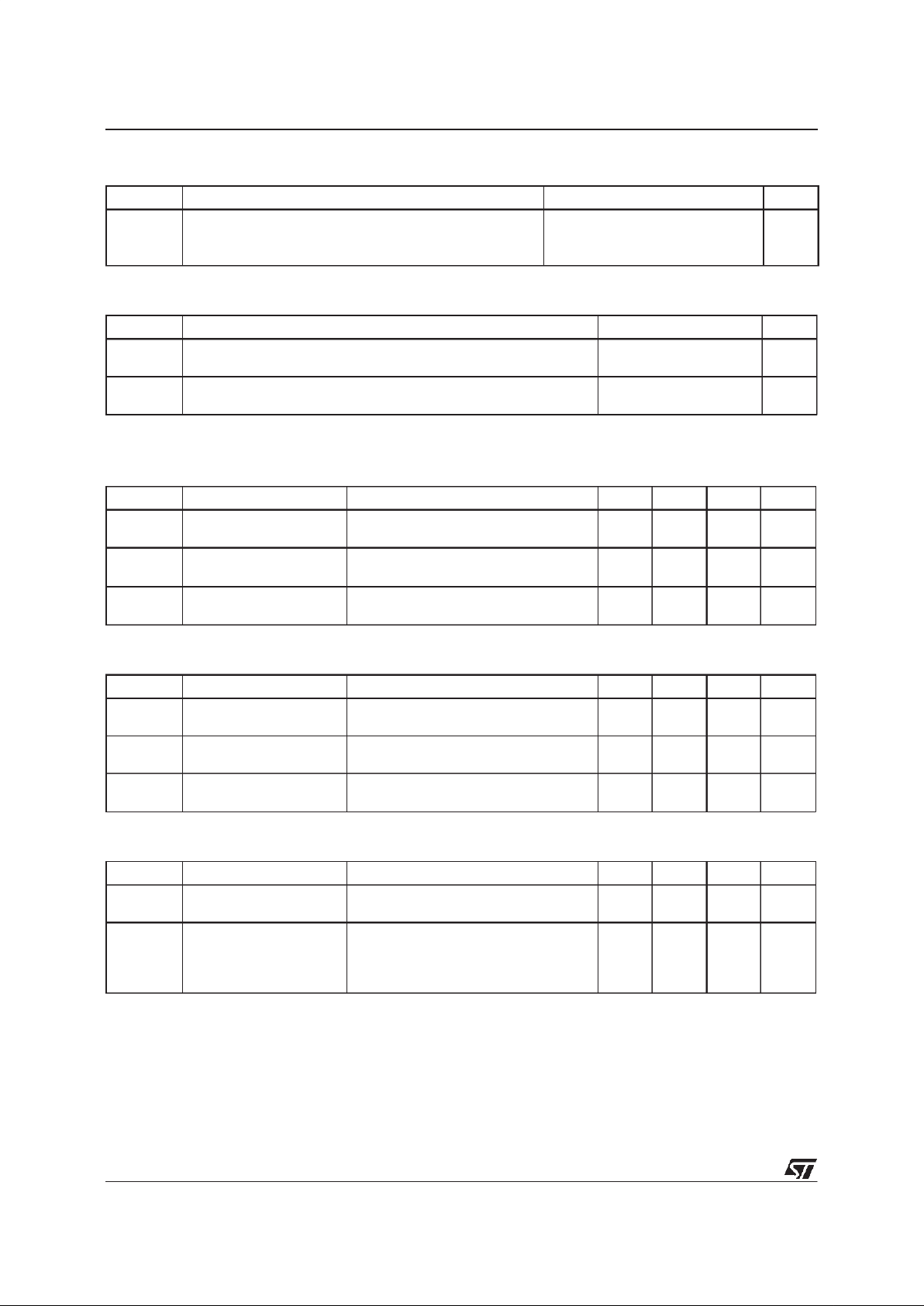

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

DS

Drain-sour ce Voltage (VGS=0) 500 V

V

DGR

Drain- ga t e V oltage (RGS=20kΩ)

500 V

V

GS

Gate-sourc e Voltage ± 30 V

I

D

Drain C urrent (con tinuous) at Tc=25oC10A

I

D

Drain C urrent (con tinuous) at Tc= 100oC6.3A

I

DM

(•) Drain C urrent (puls ed ) 40 A

P

tot

Total Dissipation at Tc=25oC135W

Derating Factor 1.08 W/

o

C

dv/ dt(

1) Peak Diod e Rec o very volt ag e slope 3 V/ns

T

stg

Sto rage T e m pe r ature -65 to 1 50

o

C

T

j

Max. O pe rating Junc t ion Temp eratur e 150

o

C

(•) Pulse width limited by safe operating area (1)ISD≤ 10 A, di/dt ≤100 A/µs,VDD≤ V

(BR)DSS

,Tj≤T

JMAX

I2PAK D2PAK

1

3

TYPE V

DSS

R

DS(on)

I

D

ST B10NC50-1 500 V < 0.52 Ω 10 A

1/7

THERMAL DATA

R

thj-case

Ther mal Resis t an ce Junc ti on-cas e Max 0.93

o

C/W

R

thj-amb

R

thc-sink

T

l

Ther mal Resis t an ce Junc ti on-ambien t Max

Thermal Resistance Case-sink Typ

Maximum Le ad Temper at u re F or Sold er ing P ur p os e

62.5

0.5

300

o

C/W

o

C/W

o

C

AVALANCHE CHARACTERISTICS

Symbol Para meter Max Val ue Uni t

I

AR

Avalanche Cu r rent, Repetitive or Not -R e petitive

(pulse width limite d by T

j

max)

10 A

E

AS

Single Pu lse Avalanche Energy

(starting T

j

=25oC, ID=IAR,VDD=50V)

550 mJ

ELECTRICAL CHARACTERISTICS (T

case

=25oC unless otherwisespecified)

OFF

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

V

(BR)DSS

Drain-sourc e

Break d own Voltage

I

D

=250µAVGS=0

500 V

I

DSS

Zero Gate Voltage

Drain Current (V

GS

=0)

V

DS

=MaxRating

V

DS

= Max Rating Tc=125oC

1

50

µA

µ

A

I

GSS

Gat e- b ody Leakage

Current (V

DS

=0)

V

GS

= ± 30 V

± 100 nA

ON(∗)

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

V

GS(th)

Gate Threshold

Voltage

V

DS=VGSID

= 250 µA

234V

R

DS(on)

Static Drain-source On

Resistanc e

VGS=10V ID= 5 A 0.48 0.52 Ω

I

D(on)

On State Drain Cu r rent VDS>I

D(on)xRDS(on)max

VGS=10V

10 A

DYNAMIC

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

g

fs

(∗)Forward

Tr ansconduc tance

VDS>I

D(on)xRDS(on)maxID

=5 A 10 S

C

iss

C

oss

C

rss

Input Capacit ance

Out put Ca pacita nce

Reverse T ransfer

Capacitance

VDS=25V f=1MHz VGS= 0 1480

210

25

pF

pF

pF

STB10NC50-1

2/7

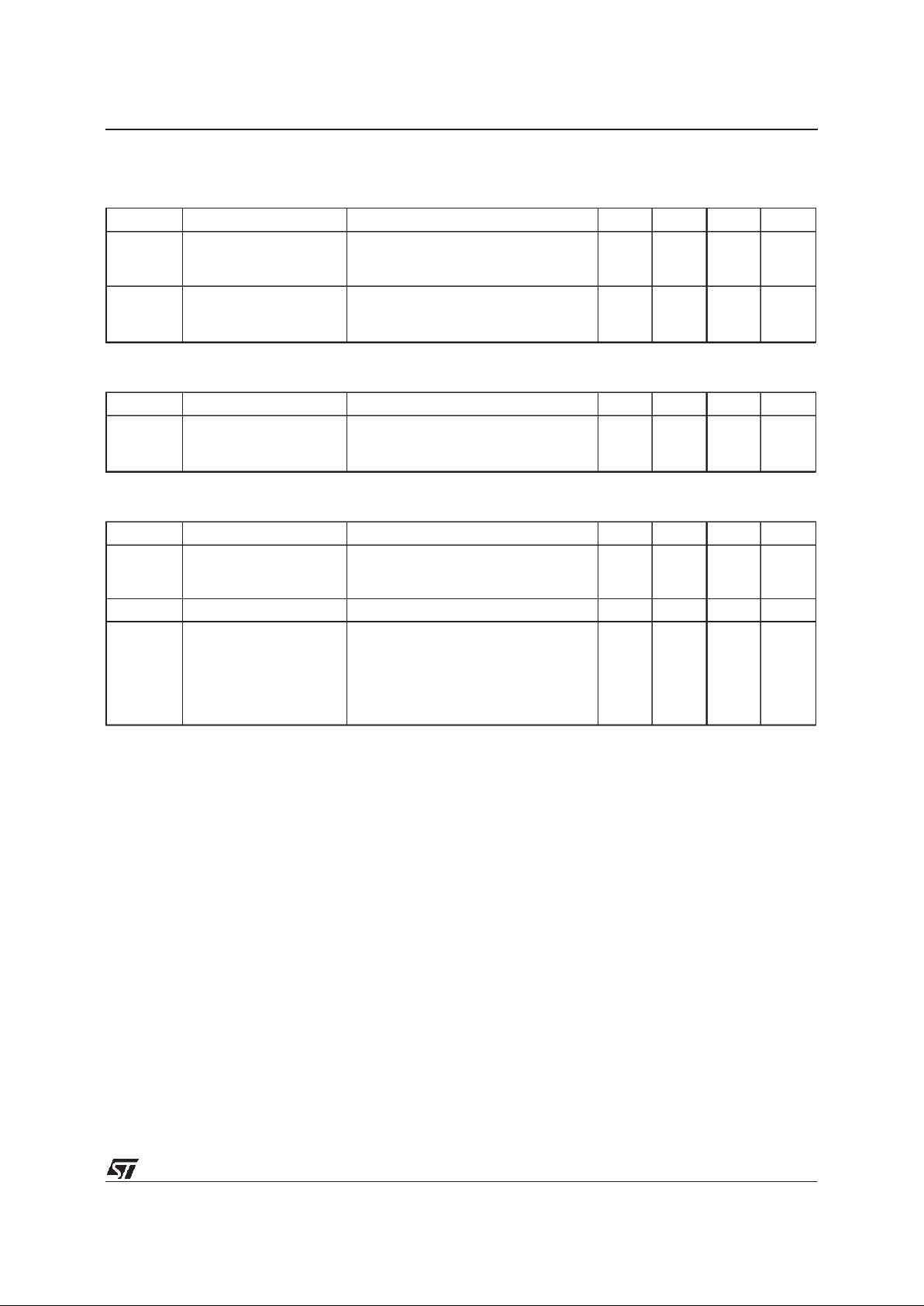

ELECTRICAL CHARACTERISTICS

(continued)

SWITCHINGON

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

t

d(on)

t

r

Turn-on Time

Rise Tim e

VDD= 250 V ID=5A

R

G

=4.7

Ω

VGS=10V

29

16

ns

ns

Q

g

Q

gs

Q

gd

Total Gate Charge

Gat e- Source Charge

Gate-Drain Charg e

VDD= 160 V ID=10A VGS=10V 41

12

19

49 nC

nC

nC

SWITCHINGOFF

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

t

r(Voff)

t

f

t

c

Off -voltage Rise Time

Fall Time

Cross-ov er T ime

VDD= 160 V ID=10A

R

G

=4.7 ΩVGS=10V

16

18

29

ns

ns

ns

SOURCEDRAINDIODE

Symbol Parameter Test Con ditions Min. Typ. M ax. Unit

I

SD

I

SDM

(•)

Source-drain C urrent

Source-drain C urrent

(pulsed)

10.6

42.4

A

A

V

SD

(∗) Forwar d O n V oltage ISD=10 A VGS=0 1.6 V

t

rr

Q

rr

I

RRM

Reverse Recover y

Time

Reverse Recover y

Charge

Reverse Recover y

Current

I

SD

=10 A d i/ dt = 100 A/µs

V

DD

=50V Tj= 150oC

560

4.9

17.5

ns

nC

A

(∗) Pulsed:Pulse duration = 300 µs, duty cycle 1.5 %

(•) Pulse width limited by safe operatingarea

STB10NC50-1

3/7

Loading...

Loading...