RF FRONT-END FOR DIGITAL RADIO

■ SINGLE CHIP RECEIVER FOR SATELLITE

DIGITAL TRA N S MI S SION

■ SUPERHETERODYNE RECEIVER WITH IF

OUTPUT

■ HIGH INPUT INTERCEPT POINT, LOW

MIXER NOISE

■ 54dB IF VGA GAIN RANGE

■ ADJUSTABLE RF GAIN

■ ADJUSTABLE IF GAIN

■ INTEGRATED RF VCO

■ INTEGRATED IF VCO

■ INTEGRATED SYNTHESIZER

2

■ I

CBUS COMPATIBLE PROGRAMMING

INTERFACE

■ UNREGULATED 2.7 V TO 3.3V VOLTAGE

SUPPLY

■ LOW COST EXTERNAL COMPONENTS

DESCRIPTION

The STA001 is an RF IC using STMicroelectronics

STA001

PRODUCT PREVIEW

TQFP44

ORDERING NUMBER: STA001

HSB2 High Speed Bipolar Technology for one chip solution for the Starman digital satellite radio receiver.

The STA001 is assembled in a TQFP44 package.

The frontend architecture is a double conversion receiver (see block diagram) .

The chip includes all the RF funct ions up to low IF

and manages the signals to and from the baseband.

BLOCK DIAGRAM

AGC1, AGC2

CE

VCO

:363.625- 373.75

I2CBUS INTERFACE

RF MIXER

1338.14 - 1375.4 MHz 117.0806 MHz

1st PLL

CHARGE

PUMP

SCL SDA

PHASE

DETECTOR

V

V

LNI, NLNI

TK1,

NTK1

ENRFOSC

V

V

DD1

SS1

FLT1

TLCK

DD2

SS2

PADJ1, PADJ2

SUPPLY1 :RF

LNA

LOCK

DETECTOR

SUPPLY2 :PLL1 +

Crystal osc .

CHANNEL SELECTION

November 2002

This is preliminary information on a new product now in development. Details are subject to change without notice.

SIP, SIN

IF1 BUFFER

SOP, SON

3.68MHz

:4

113.23KHz

:130

XOSEL

VGA

MUX

IF1 to IF2 MIXER

PHASE

DETECTOR

2nd PLL

OSC

REF

GADJ1, GADJ2

BUFFER

XTAL1, XTAL2

IF2 BUFFER

CHARGE

PUMP

: 1034

14.72MHz

SUPPLY4 :IF1,

IF2 &PLL2

VCO

SUPPLY3 :DIG.

V

DD4

V

SS4

RXI, NRXI

1.8366 Mhz

FLT2

TK2, NTK2

DIFFERENTIAL

SINGLE ENDED

M_CLK

VDD3

V

SS3

1/20

STA001

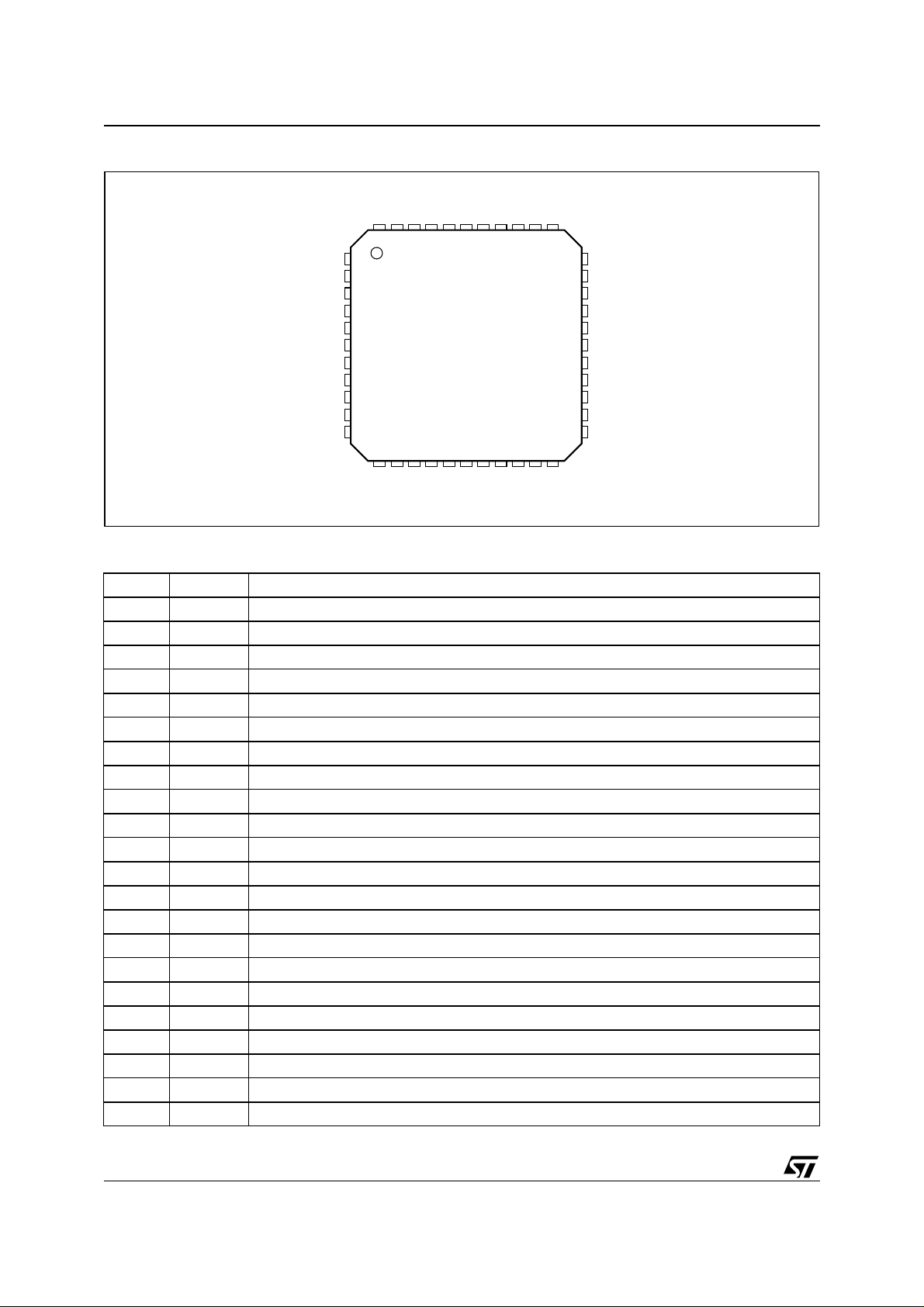

PIN CONNECTION

(Top view)

ENRFOSC

VDD1

SIP

SIN

VSS1

LNI

NLNI

VSS1

N.C.

PADJ1

PADJ2

VDD4

AGC2

AGC1

VSS4

SON

SOP

VSS4

44 43 42 41 3940 38 37 36 35 34

1

2

3

4

5

6

7

8

9

10

12 13 14 15 16

TK1

VDD2

NTK1

VDD2

FLT1

171118 19 20 21 22

VSS2

XTAL1

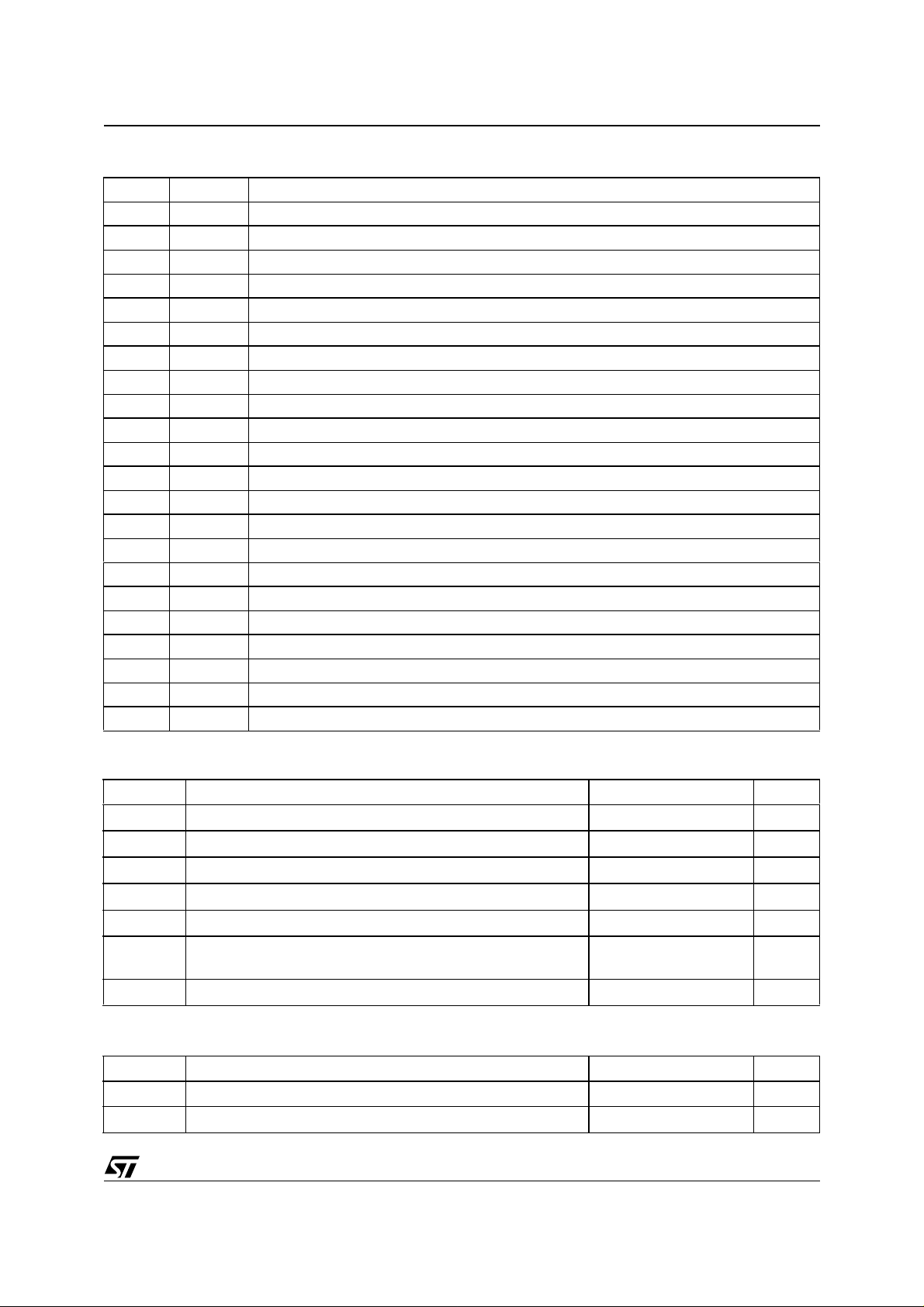

PIN FUNCTION

N° Pin Function

1 VDD1 Positive supply 1

2 SIP SAW filter input connection

3 SIN SAW filter input connection

4 VSS1 Negative supply 1

5 LNI RF input

6 NLNI RF input

7 VSS1 Negative supply 1

8 NC Not connected

9 PADJ1 RF gain adjust connection 1

10 PADJ2 RF gain adjust connection 2

11 ENRFOSC RF Oscillator enable

12 VDD2 Positive supply 2

13 TK1 1st PLL tank connection 1

14 NTK1 1st PLL tank connection 2

15 VDD2 Positive supply 2

16 FLT1 1st PLL loop filter connection

17 VSS2 Negative supply 2

18 XTAL1 Quartz oscillator connection 1

19 XTAL2 Quartz oscillator connection 2

20 REF External optional TCXO input

21 XOSEL Internal/external XO selection

22 TLCK Lock detector output

TK2

NTK2

REF

XTAL2

FLT2

VDD4

TLCK

XOSEL

33

RXI

32

NRXI

31

GADJ1

30

GADJ2

29

CE

28

VDD3

27

SCL

26

SDA

25

VSS3

24

M_CLK1

23

M_CLK2

D97AU602

2/20

STA001

PIN FUNCTION

(continued)

N° Pin Function

23 M_CLK2 Master clock differential output 1

24 M_CLK1 Master clock differential output 2

25 VSS3 Negative supply 3

26 SDA Da ta serial input

27 SCL Clock input

28 VDD3 Positive supply 3

29 CE Chip Enable

30 GADJ2 IF gain adjust connection 2

31 GADJ1 IF gain adjust connection 1

32 NRXI Low IF Signal output 2

33 RXI Low IF Signal output 1

34 FLT2 2nd PLL loop filter connection

35 VDD4 Positive supply 4

36 TK2 2nd PLL tank connection

37 NTK2 2nd PLL tank connection

38 VDD4 Positive supply 4

39 AGC2 VGA control pin 2

40 AGC1 VGA control pin 1

41 VSS4 Negative supply 4

42 SON SAW filter output connection

43 SOP SAW filter output connection

44 VSS4 Negative supply 4

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

T

T

V

V

V

VDD

V

stg

oper

max

min

maxi

esd

Storage temperature -40 , +125 °C

Operative ambient temperature -20 , +85 °C

Maximum voltage on any pin (with the exception of CE, SDA, SDL)

VDD+0.3 V

Minimum voltage on any pin GND-0.3 V

Maximum voltage on pins CE, SDA, SDL VDD+0.6 V

Minimum/Maximum power supply between VDD

max

VSS

1,2,3,4

1,2,3,4

and

-0.3/5.5 V

Electrostatic Discharge Voltage (ESD) 2 KV

OPERATING CONDITIONS

Symbol Parameter Value Unit

VDD Opera ting voltage 2.7, 3.3 V

T

jun

Junction temperature -30, +95 °C

3/20

STA001

THERMA L D ATA

Symbol Parameter Value Unit

R

Th j-amb

(1) According to JEDEC specific ation on a 4 layers board

Thermal Resistance Junction to Ambient

(1)

45 °C/W

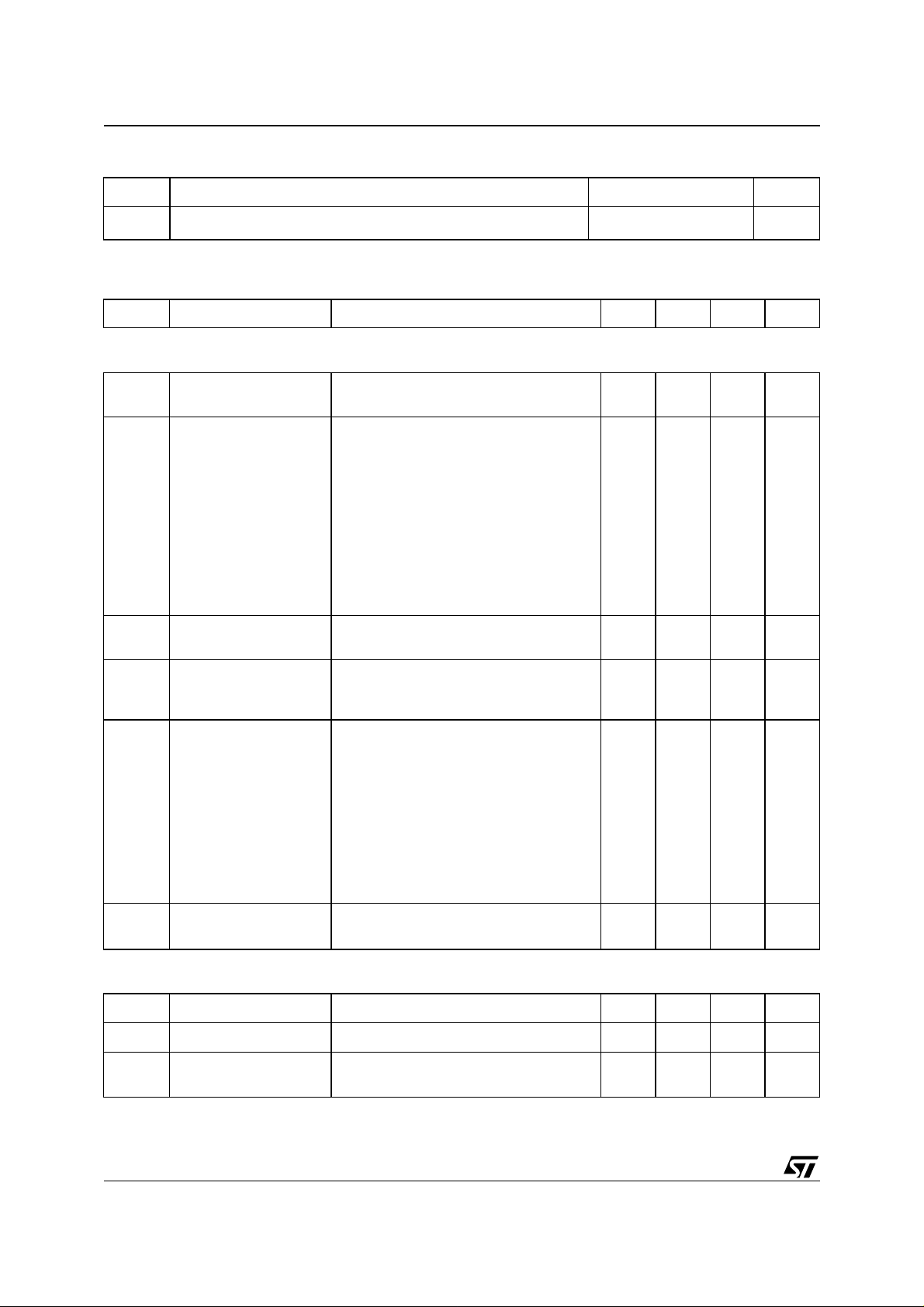

ELECTRICAL CHARACTERISTCS

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY CURRENTS (T

I

CC1

Current supplied by

VDD1

CC2

Current supplied by

I

VDD2

I

CC3

Current supplied by

VDD3

= 25°, VDD = 3V)

amb

Powered circuits: LNA, RF mixer, IF buffer 9.5 14 17 mA

Powered circuits: RF pll, Crystal Oscillator.

ENRFOSC=high (IC RF Osc. Enabled),

8.5

10

12

XOSEL=high (IC XO Enabled)

ENRFOSC=low (IC RF Osc. Disabled),

3

5

6

XOSEL=high (IC XO Enabled)

ENRFOSC=high (IC RF Osc. Enabled),

7.5

9

11

XOSEL=low (IC XO Disabled)

ENRFOSC=low (IC RF Osc. Disabled),

2

4

5

XOSEL=low (IC XO Disabled)

Powered circuits: Digital cells 12 15 18 mA

mA

mA

mA

mA

I

CC4

Current supplied by

VDD4

Powered circuits: VGA, IF mixer, output

buffer, IF pll.

V(AGC1)=V(AGC2)=1.2 (IF

I

TOTICC1

+ I

CC2

+ I

CC3

+ I

ENRFOSC=high (IC RF Osc. Enabled),

CC4

XOSEL=high (IC XO Enabled)

ENRFOSC=low (IC RF Osc. Disabled),

XOSEL=high (IC XO Enabled)

ENRFOSC=high (IC RF Osc. Enabled),

XOSEL=low (IC XO Disabled)

ENRFOSC=low (IC RF Osc. Disabled),

XOSEL=low (IC XO Disabled)

I

TOTSB

Standby I

I

+ I

CC3

CC4

CC1

+ I

CC2

+

CE=GND 100 µA

LNA, RF MIXER AND IF1 BUFFER (T = 25°, VDD-VSS = 3V)

BW

BW

Input signal BW 1452 1492 MHz

i

Output signal BW 114 116.5 MHz

o

G

Voltage Gain Input LNI, NLNI pins; output SIP, NIP pins.

V

= 200Ω, PADJ1, PADJ2 floating

R

L

gain

=75dB)

71114mA

40

34

39

34

50

45

49

44

61

55

60

54

mA

mA

mA

mA

28 30 33 dB

4/20

STA001

ELECTRICAL CHARACTERISTCS

(continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

G

Minimum Voltage Gain Input LNI, NLNI pins; output SIP, NIP pins.

Vtrim

Z

Input impedance R || C Balanced, LNI, NLNI pins 75

i

= 200Ω, R

R

L

ext

=0

22 25 28 dB

0.2

Output impedance Balanced, SIP, SIN pins 50 Ω

Z

o

R

Input Return Loss LNI, NLNI pins 14 dB

l

IIP3 Input IP3 Input LNI, NLNI pins; output SIP, NIP pins,

R

=200Ω, PADJ1, PADJ2 floating

l

IIP3

1dBcp Input 1 dB compression

1dBcp

Input IP3 minimum gain Input LNI, NLNI pins; output SIP, NIP pins,

trim

=200Ω, R

R

l

=0 on PADJ1, PADJ2

ext

Input LNI, NLNI pins; output SIP, NIP pins,

point

Input 1 dB compression

tri

m

point

R

=200Ω, PADJ1, PADJ2 floating

l

Input LNI, NLNI pins; output SIP, NIP pins,

=200Ω, P ADJ1, P ADJ2 R

R

l

=0 on PADJ1,

ext

-20 -15 dBm

-19.5 -11.5 dBm

-26 dBm

-24 dBm

PADJ2

NF Noise figure contribution Measurement conditions: Input LNI, NLNI

5dB

pins; output SIP, NIP pins. Rs=50Ω,

Rl=200Ω, DSB, PADJ1, PADJ2 floating

Ω

pF

NF

IF1

RF

V

Noise figure contribution

trim

minimum gain

LO1 to IF1 leakage -100 -25 dBm

leak

LO1 to RF leakage -100 -30 dBm

leak

LNI, NLNI common mode

DC

Measurement conditions: Input LNI, NLNI

pins; output SIP, NIP pins. R

Rl=200Ω, DSB, R

=0 on PADJ1, PADJ2

ext

=50Ω,

s

AC coupled to the Balun VDD-

DC voltage

V

SIP, SIN common mode

DC

AC coupled to the SAW filter VDD-

DC voltage

IF VGA AMPLIFIER, IF MIXER AND OUTPUT BUFFER (T = 25°, VDD-VSS = 3V)

BW

BW

G

G

I

AGC

Input signal BW 114 116.5 MHz

i

Output signal BW 0.6 3.1 MHz

o

Minimum gain Input LNI, NLNI pins; output SIP, NIP pins.

min

Rl=high impedance V(AGC

Maximum gain Input LNI, NLNI pins; output SIP, NIP pins.

max

Rl=high impedance V(AGC

1,2

1,2

)=0V

)=3V

Input current in AGC

control pin

Z

AGC

AGC pin input

impedance

6.5 dB

VDD-1 VDD-

1.2

1.3

VDD-

1.1

0.8

VDD-

0.9

32 37 dB

71 86 dB

10 µA

600 KΩ

V

V

5/20

STA001

ELECTRICAL CHARACTERISTCS

(continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

NF Noise figure contribution Measurement conditions: Input SIP, NIP

pins; output SOP, NOP pins. R

=50Ω,

s

9dB

Rl=200Ω, DSB, Gain = 65dB

1dBcp Input 1 dB compression

Gain = 65dB -50 dBm

point

1dBcp

Input 1 dB compression

fg

Gain = 81dB -66 dBm

point full gain

IIP3 Input IP3 Gain = 65dB -41 dBm

IIP3

Z

V

V

V

Input IP3 full gain Gain = 81dB -57 dBm

fg

Z

Input impedance Balanced, SOP, SON pins 50 Ω

in

Output impedance Balanced, RXI, NRXI pins (see fig. 9) 200 Ω

out

SOP, SON common

DC

mode DC voltage

RXI, NRXI common

DC

mode DC voltage

GADJ1, GADJ2 common

DC

mode DC voltage

AC coupled to the SAW filter VDD-

1.2

VDD-

2.1

VDD-

0.15

VDD-1 VDD-

0.8

VDD-

1.36

VDD-

V

DD

0.12

V

V

V

Z

Gain adjustment pins

adj

Balanced, GADJ1, GADJ2 pins 800 Ω

impedance

BB

IF2

LO2 to BB leakage Obtained using low pass filter at the output -45 dBm

leak

LO2 to IF2 leakage Obtained with SAW filter connected to IF

leak

port

IM3 Third order IM product V

out

=1V

DDp

Figure 1. Typical IF Overall Gain vs Control Voltage

IF TOTAL VOLTAGE GAIN (dB)

input SOP,NOP output RXI,NRXI

60

55

50

45

40

IF TOTAL VOLTAGE GAIN (dB)

35

30

0.7 0.75 0.77 0.79 0.8 0.82 0.84 0.86 0.88 0.9

V(AGC1, AGC2) (Volt)

IF gain (dB)

-100 -30 dBm

-30 dBc

IF TOTAL VOLTAGE GAIN (dB)

input SOP,NOP output RXI,NRXI

90

85

80

75

70

IF TOTAL VOLTAGE GAIN (dB)

65

60

1

1.2

1.4

1.6

1.1

1.3

1.5

1.8

1.7

1.922.1

V(AGC1, AGC2) (Volt)

IF gain (dB)

2.2

2.4

2.3

2.6

2.5

2.7

6/20

Loading...

Loading...