SGS Thomson Microelectronics ST95040M6, ST95040M3TR, ST95040M3, ST95040M1TR, ST95040M1 Datasheet

...

ST95040

ST95020, ST95010

4K/2K/1K Serial SPI EEPROM with Positive Clock Strobe

June 1998 1/18

1 MILLIONERASE/WRITE CYCLES

40 YEARSDATARETENTION

SINGLE SUPPLYVOLTAGE

– 4.5Vto 5.5V forST950x0

– 2.5Vto 5.5V forST950x0W

SPI BUS COMPATIBLE SERIALINTERFACE

2 MHzCLOCK RATE MAX

BLOCKWRITEPROTECTION

STATUSREGISTER

16 BYTE PAGEMODE

WRITEPROTECT

SELF-TIMEDPROGRAMMINGCYCLE

E.S.D.PROTECTIONGREATERthan 4000V

SUPPORTSPOSITIVECLOCK SPI MODES

DESCRIPTION

The ST950x0 is a family of Electrically Erasable

Programmable Memories (EEPROM) fabricated

with STMicroelectronics’s High EnduranceSingle

Polysilicon CMOS technology. Each memory is

accessed by a simple SPI bus compatible serial

interface. The bus signals are a serial clock input

(C),a serial data input(D) and a serialdata output

(Q).

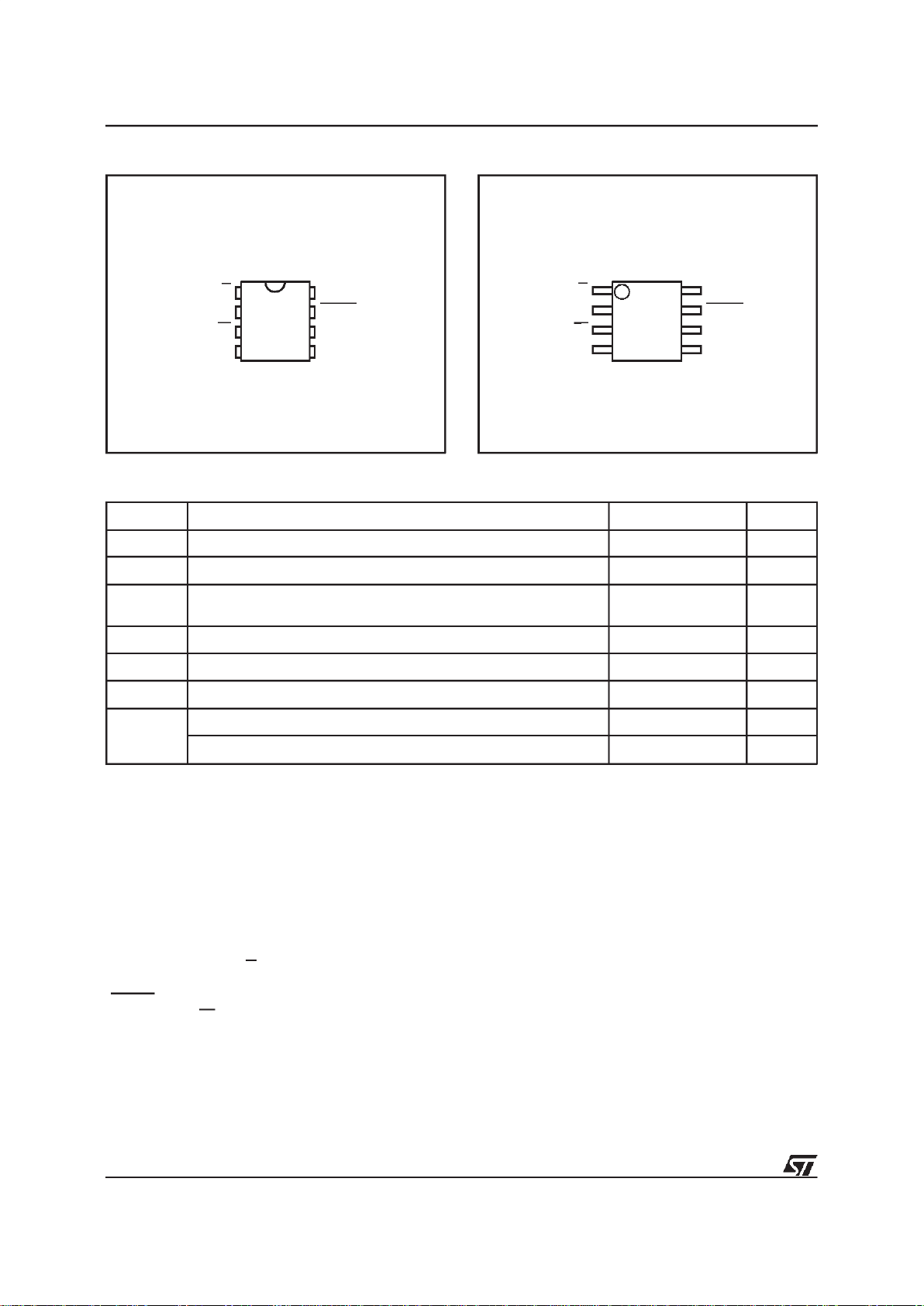

AI01435B

S

V

CC

ST950x0

HOLD

V

SS

W

Q

C

D

Figure1. Logic Diagram

C Serial Clock

D Serial Data Input

Q Serial Data Output

S Chip Select

W Write Protect

HOLD Hold

V

CC

Supply Voltage

V

SS

Ground

Table1. SignalNames

8

1

SO8 (M)

150mil Width

8

1

PSDIP8 (B)

0.25mm Frame

Symbol Parameter Value Unit

T

A

Ambient Operating Temperature –40 to 125 °C

T

STG

Storage Temperature –65 to 150

°

C

T

LEAD

Lead Temperature, Soldering (SO8 package)

(PSDIP8 package)

40 sec

10 sec

215

260

°

C

V

O

Output Voltage –0.3 to VCC+0.6 V

V

I

Input Voltage with respect to Ground –0.3 to 6.5 V

V

CC

Supply Voltage –0.3 to 6.5 V

V

ESD

Electrostatic Discharge Voltage (Human Body model)

(2)

4000 V

Electrostatic Discharge Voltage (Machine model)

(3)

500 V

Notes: 1. Except for the rating ”Operating Temperature Range”, stressesabove those listedin theTable ”Absolute Maximum Ratings”

may cause permanent damage to thedevice. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the Operating sections of this specification is not implied.Exposure to Absolute Maximum

Rating conditions for extended periods may affectdevice reliability.Refer also to the STMicroelectronics SURE Programand

other relevantquality documents.

2. MIL-STD-883C, 3015.7 (100pF, 1500Ω)

3. EIAJ IC-121 (Condition C) (200pF, 0Ω)

Table2. AbsoluteMaximum Ratings

(1)

Thedevice connectedto the bus is selected when

thechipselectinput(S) goeslow.Communications

with the chip can be interrupted with a holdinput

(HOLD). The write operation is disabled by a write

protectinput (W).

Datais clockedin during the low to high transition

of clock C, data is clocked out during the high to

lowtransitionof clockC.

SIGNALSDESCRIPTION

SerialOutput(Q). Theoutputpin is usedtotrans-

fer data seriallyout of the Memory.Data is shifted

out on the falling edge of theserial clock.

Serial Input (D). The input pin is used to transfer

dataseriallyintothedevice.Itreceivesinstructions,

addresses, and the data to be written. Input is

latchedon the risingedge of the serialclock.

DV

SS

C

HOLDQ

SV

CC

W

AI01436B

ST950x0

1

2

3

4

8

7

6

5

Figure2A. DIPPin Connections

1

AI01437B

2

3

4

8

7

6

5DV

SS

C

HOLDQ

SV

CC

W

ST950x0

Figure2B. SO Pin Connections

DESCRIPTION

(cont’d)

2/18

ST95040, ST95020, ST95010

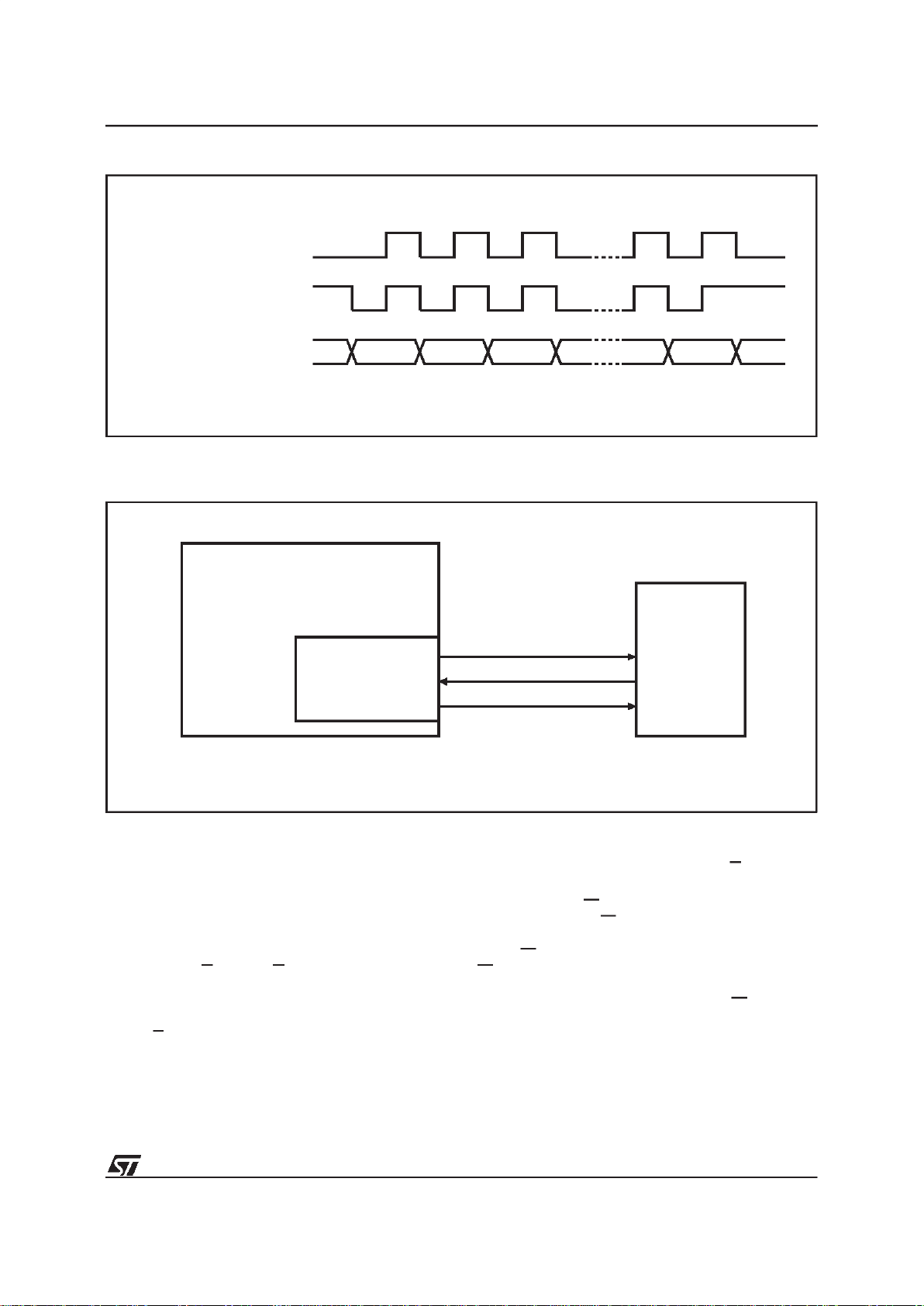

AI01438

C

C

MSB LSB

CPHA

DorQ

0

1

CPOL

0

1

Figure3. Data and Clock Timing

AI01439B

SPI Interface with

(CPOL, CPHA) =

(’0’, ’0’) or (’1’, ’1’)

MICROCONTROLLER

(ST6, ST7, ST9, ST10, OTHERS)

ST95xx0

SCK

SDI

SDO

C

Q

D

Figure4. Microcontrollerand SPI Interface Set-up

Serial Clock (C).

The serial clock provides the

timing of the serial interface. Instructions, addresses,ordatapresentat theinputpinare latched

on the rising edge of the clock input, while data on

theQ pin changesafterthe fallingedgeof theclock

input.

Chip Select (S).

When S is high, the Memory is

deselectedand the Q output pin is at high impedance and, unless an internal write operation is

underwaythe Memorywill bein the standbypower

mode. S low enables the Memory,placingit in the

active power mode. It should be noted that after

power-on,a high to low transition on S is required

priorto the start of any operation.

Write Protect (W).

This pin is for hardwarewrite

protection. When W is low, writes to the Memory

aredisabledbutanyotheroperationsstayenabled.

WhenWishigh,all writesoperationsareavailable.

W going low at any time before the last bit D0 of

thedata streamwillresetthewriteenablelatchand

prevent programming. No action on W or on the

writeenable latchcan interrupta writecycle which

hascommenced.

3/18

ST95040, ST95020, ST95010

Hold (HOLD).

The HOLD pin is used to pause

serial communications with the Memory without

resetting the serial sequence. To take the Hold

condition into account, the product must be selected (S = 0). Then the Hold stateis validatedby

a high tolowtransitionon HOLDwhenC islow. To

resumethecommunications,HOLDisbroughthigh

whileC is low.During the Hold conditionD, Q, and

C are at a highimpedancestate.

Whenthe Memoryis underthe Holdcondition,itis

possibletodeselectthedevice.However,theserial

communications will remain paused after a reselect, and the chip will be reset.

TheMemorycanbedrivenbyamicrocontrollerwith

its SPI peripheral running in either of the two followingmodes:(CPOL, CPHA)= (’0’, ’0’)or (CPOL,

CPHA)= (’1’, ’1’).

Forthesetwo modes,inputdatais latchedinby the

lowto high transitionof clockC, andoutputdatais

available from the high to low transition of Clock

(C).

Thedifferencebetween(CPOL, CPHA)=(0,0)and

(CPOL,CPHA) = (1,1) is the stand-bypolarity:C

remains at ’0’ for (CPOL, CPHA) = (0, 0) and C

remainsat’1’for(CPOL,CPHA)=(1,1)whenthere

is no data transfer.

OPERATIONS

All instructions,addresses and data are shifted in

and out of the chip MSB first. Data input (D) is

sampled on the first rising edge of clock (C) after

thechip select(S) goeslow.Priorto any operation,

a one-byte instructioncode must be enteredin the

chip. This code is enteredvia the data input (D),

and latched on the rising edge of the clock input

(C).Toenter an instructioncode, the productmust

have been previously selected (S = low). Table 3

shows the instruction set and format for device

operation. If an invalid instructionis sent (one not

contained in Table 3), the chip is automatically

deselected.For operations that read or write data

in the memoryarray,bit 3 of the instruction is the

MSB of the address,otherwise,it is a don’t care.

WriteEnable(WREN) and WriteDisable (WRDI)

The Memory contains a write enable latch. This

latch must be set prior to every WRITE or WRSR

operation.The WREN instructionwill set the latch

and the WRDI instruction will reset the latch. The

latchis reset under the following conditions:

– W pin is low

– Power on

– WRDI instruction executed

– WRSR instruction executed

– WRITE instruction executed

As soon as the WREN or WRDI instruction is

received by the memory, the circuit executes the

instructionand enters a wait mode until it is deselected.

Read Status Register (RDSR)

TheRDSRinstructionprovidesaccesstothestatus

register. The status register may be read at any

time,evenduring a writeto thememoryoperation.

If a ReadStatusregister reaches the 8thbit of the

Status register, an additional 9th clock pulse will

wrap around to read the 1st bit of theStatus Register

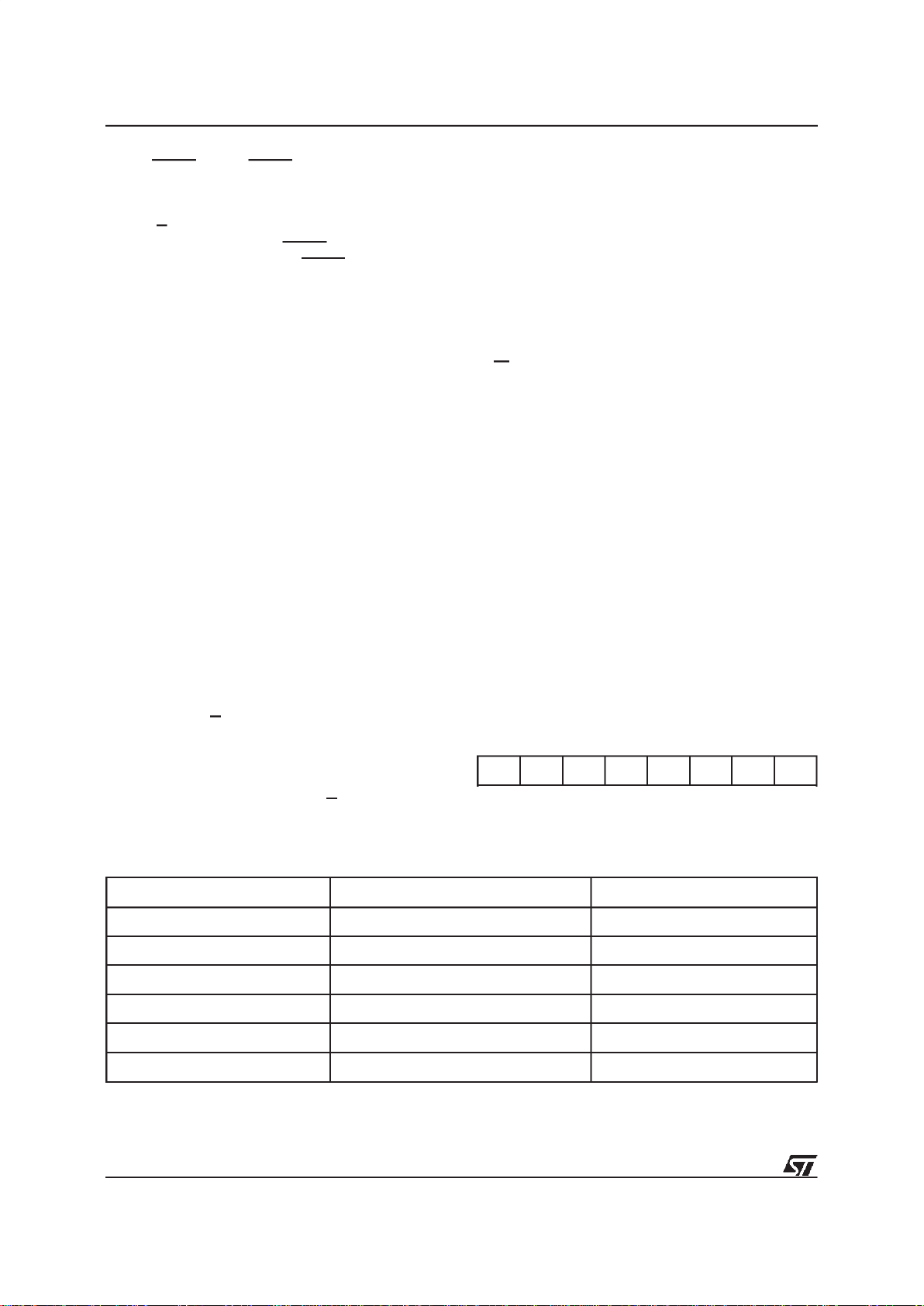

Thestatus register format is as follows:

b7 b0

1 1 1 1 BP1 BP0 WEL WIP

BP1, BP0: Read and write bits

WEL, WIP: Read only bits.

b7 to b4: Readonly bits.

Instruction Description Instruction Format

WREN Set Write Enable Latch 0000 0110

WRDI Reset Write Enable Latch 0000 0100

RDSR Read Status Register 0000 0101

WRSR Write Status Register 0000 0001

READ Read Data fromMemory Array 0000 A

8

011

WRITE Write Data to Memory Array 0000 A

8

010

Notes: A8= 1, Upper page selected on ST95040.

A

8

= 0, Lower page selected on ST95040.

Table3. InstructionSet

4/18

ST95040, ST95020, ST95010

AI01272

HOLD

S

W Control Logic

High

Voltage

Generator

I/O Shift Register

Address

Register

and Counter

Data

Register

16 Bytes

X Decoder

Y Decoder

Block

Protect

C

D

Q

Status

Figure5. Block Diagram

During a write to the memory operation to the

memory array, all bits BP1, BP0, WEL, WIP are

valid and can be read. Duringa writeto thestatus

register, only the bits WEL and WIP are valid and

can be read. The values of BP1 and BP0 read at

thattimecorrespondtothepreviouscontentsofthe

statusregister.

TheWrite-In-Process(WIP)read-onlybit indicates

whethertheMemoryis busywith a writeoperation.

Whenset to a ’1’a writeis in progress,when set to

a ’0’no write is in progress.

The Write Enable Latch (WEL) read-only bit indicatesthe statusofthe writeenablelatch.Whenset

toa ’1’the latchis set,when set to a ’0’the latch is

reset. The Block Protect (BP0 and BP1) bits indicate the extent of the protectionemployed. These

bitsare set by the userissuing the WRSR instruction. These bits are non-volatile.

5/18

ST95040, ST95020, ST95010

WriteStatus Register (WRSR)

TheWRSR instructionallowsthe user toselectthe

size of protected memory. The user may read the

blocks but will be unable to write within the protected blocks. The blocks and respective WRSR

controlbits are shown in Table4.

When the WRSR instruction and the 8 bits of the

Status Register are latched-in, the internal write

cycleis then triggered by therising edge of S.

Thisrising edge of S must appearno laterthanthe

16th clock cycle of the WRSR instruction of the

StatusRegistercontent (it must not appeara 17th

clockpulse before the rising edge of S), otherwise

the internal writesequence is not performed.

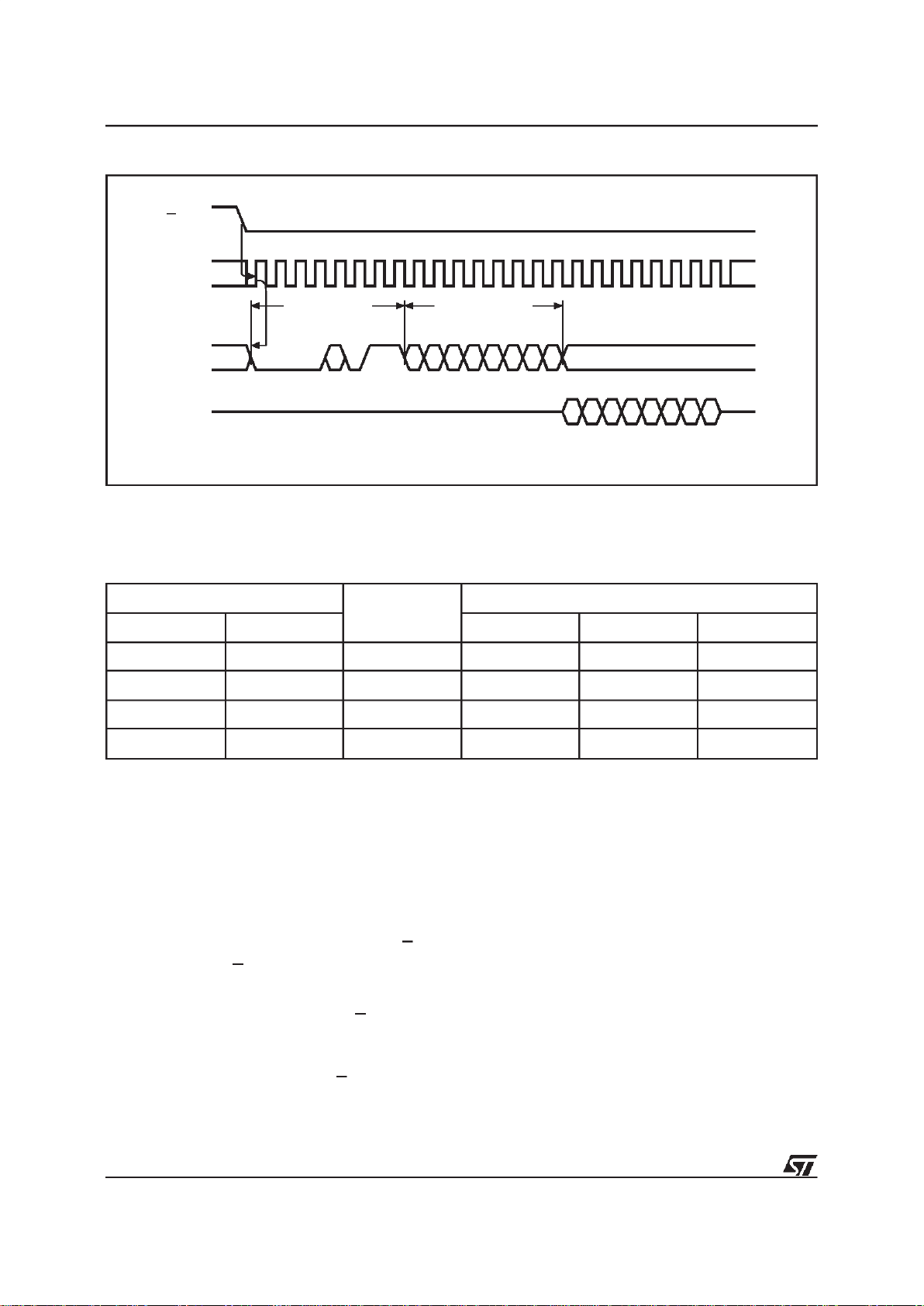

ReadOperation

Thechipis firstselectedby puttingS low.Theserial

one byte read instructionis followedby a one byte

address (A7-A0), each bit being latched-induring

the rising edge of the clock(C). Bit 3 (seeTable3)

of the read instruction contains address bit A8

(mostsignificantaddressbit). Thenthe datastored

inthememoryat theselectedaddressis shiftedout

on the Q output pin; each bit being shifted out

during the falling edge of the clock (C). The data

stored in the memory at the next addresscan be

read in sequence by continuing to provide clock

pulses. The byte address is automatically incrementedto the next higher addressafter each byte

of data is shiftedout. When the highestaddressis

reached,theaddresscounterrollsover to 0hallowing the read cycle to be continuedindefinitely.The

read operation is terminated by deselecting the

chip.Thechip canbe deselectedat anytimeduring

dataoutput. Any read attemptduring a write cycle

will be rejected and willdeselect the chip.

C

D

AI01440

S

Q

A7

21 3 4 5 6 7 8 9 10111213141516171819

A6 A5 A4 A3 A2 A1 A0A8

20 21 22 23

765432 0

1

HIGH IMPEDANCE

DATA OUT

INSTRUCTION BYTE ADDRESS

0

Figure 6. Read Operation Sequence

Status Register Bits

Protected Block

Array AddressProtected

BP1 BP0 ST95040 ST95020 ST95010

0 0 none none none none

0 1 Upper quarter 180h - 1FFh C0h - FFh 60h -7Fh

1 0 Upper half 100h - 1FFh 80h - FFh 40h - 7Fh

1 1 Whole memory 000h - 1FFh 00h - FFh 00h - 7Fh

Table4. WriteProtected Block Size

Notes: A8= A7 = 0 onST95010; A8 = 0 on ST95020; A8is only activeon ST95040.

6/18

ST95040, ST95020, ST95010

Loading...

Loading...