SGS Thomson Microelectronics ST52E440, ST52T440, ST52T400 Datasheet

®

ST52T400/T440/E440

8-BIT INTELLIGENT CONTROLLER UNIT (ICU)

Timer/PWM, Analog Comparator, Triac/PWM Timer, WDG

Memories

■ Upto8KbytesEPROM/OTP

■ 128/256 bytes of RAM

■ Readout Protection

Core

■ Register File Based Architecture

■ 55 instructions

■ Hardware multiplication and division

■ Decision Processor for the implementation of

Fuzzy Logic algorithms

Clock and Power Supply

■ Up to 20 M H z clock frequency.

■ On-c hip Power On Reset (POR) andBrown Out

Detector (BOD)

■ P ower Saving features

ST52T400/T440/E440/T441

PRELIMINARY DATASHEET

Interrupts

■ 6 interrupt vectors

■ Top Level External Interrupt (INT)

I/O Ports

■ 13 or 21 I /O PINs configurable in Input and

Output mode

■ High current sink/source in all pins. Triac Driver

output can supply 50 mA

Peripherals

■ Programmable 8-bit Timer/PWMs wi th internal

16-bit Prescaler featuring:

– PWM outp ut

– Input capture

– Output compare

– Pulse generator mode

■ Watchdog timer

■ 6-channels Analog Comparator with 16-bit

Timer (not available in ST52T400)

■ Triac/PWM Driver Timer with zero crossing

detector and high current capability for:

– PWM mode

–BurstMode

– Phase Angle Partialization mode

Development tools

■ High level Software to ols

■ Emulator

■ Low cost Programmer

■ Gang Programmer

Rev. 2.9 - November 2002 1/94

This ispreliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

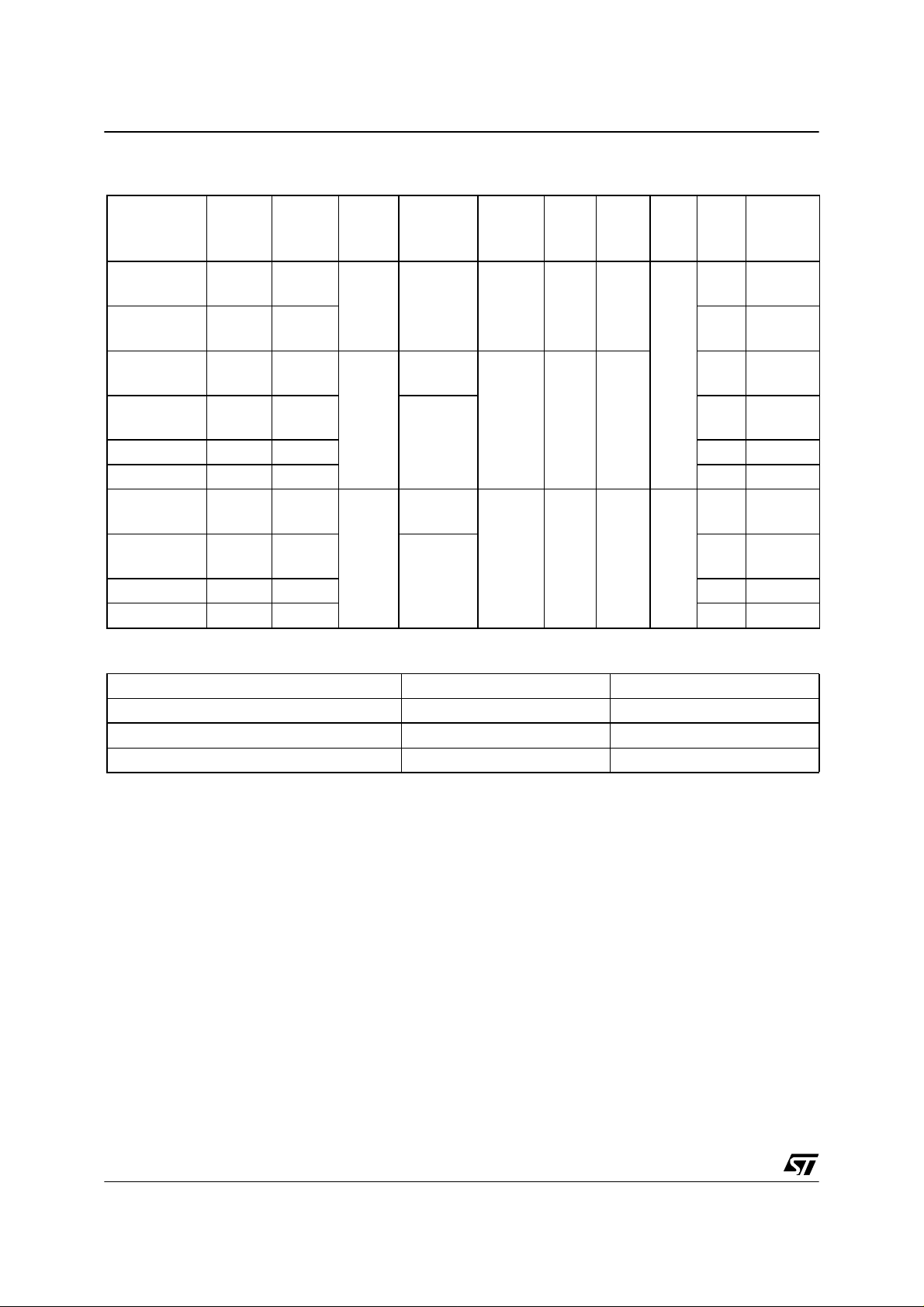

ST52T400/T440/E440/T441

ST52T400/T440/E440/T441 Type List

ST52 Device

ST52T400Fmpy 1/2/4/8K 128/256

ST52T400Gmpy 1/2/4/8K 128/256 21

ST52T440Fmpy 1/2/4/8K 128/256

ST52T440Gmpy 1/2/4/8K 128/256

ST52E440F3D6 8K 256 13 CDIP20W

ST52E440G3D6 8K 256 21 CDIP28W

ST52T441Fmpy 1/2/4/8K 128/256

ST52T441Gmpy 1/2/4/8K 128/256

ST52E441F3D6 8K 256 13 CDIP20W

ST52E441G3D6 8K 256 21 CDIP28W

Note: devices with 1-2K NVM have 128 RAM; devices with 4-8K NVM have 256 RAM

NVM

(bytes)

RAM

(bytes)

TIMER/

PWM

1No 1YesYes

1

1

Analog

Comparator

4ch

6ch

4ch

6ch

Triac

Driver/

PWM

1YesYes

1YesYesNo

WDT

POR,

Pull up I/Os Package

BOD

Yes

13

13

21

13

21

SO20,

PDIP20

SO28,

PDIP28

SO20,

PDIP20

SO28,

PDIP28

SO20,

PDIP20

SO28,

PDIP28

COMMON FEATURES ST52T400 ST52x440/ST52x441

Temperature Range -40 to + 85 °C -40 to + 85 °C

Operating Supply 2.7 to 5.5 V 4.5 to 5.5 V

CPU Frequency Up to 20 MHz Up to 20 MHz

Legend:

Sales code: ST52tnnncmpy

Memory type (t): F=FLASH, T=OTP, E=EPROM

Subfamily (nnn): 400, 410, 420, 430, 440, 441

Pin Count (c): Y=16 pins, F=20 pins, G=28 pins, K=32/34 pins, J=42/44 pins

Memory Size (m): 0=1 Kb, 1=2 Kb, 2=4 Kb, 3=8 Kb

Packages (p): B=PDIP, D=CDIP, M=PSO, T=TQFP

Temperature (y): 0=+25, 1=0 +70, 3=-40 +125, 5=-10 +85, 6=-40 +85, 7=-40 +105

2/94

TABLE OF CONTENTS

ST52T400/T440/E440/T441

TABLE OF CONTENTS

1GENERALDESCRIPTION......................................... 7

1.1Introduction...................................................................7

1.2 Operational Description .........................................................8

1.2.1MemoryProgrammingPhase................................................ 8

1.2.2WorkingMode............................................................ 8

1.3 PinDescription...............................................................18

2INTERNALARCHITECTURE...................................... 19

2.1ControlUnitandDataProcessingUnit.............................................19

2.1.1ProgramCounter ........................................................ 19

2.1.2Flags.................................................................. 21

2.2AddressSpaces..............................................................21

2.2.1RamandStack.......................................................... 22

2.2.2 Input Registers Bench . . . ................................................. 22

2.2.3ConfigurationRegisters ................................................... 23

2.2.4OutputRegisters......................................................... 23

2.3FuzzyComputation............................................................25

2.3.1FuzzyInference ......................................................... 25

2.3.2FuzzyficationPhase...................................................... 25

2.3.3InferencePhase......................................................... 26

2.3.4Defuzzyfication.......................................................... 26

2.3.5 Input Membership Function ................................................ 27

2.3.6OutputSingleton......................................................... 27

2.3.7FuzzyRules............................................................ 27

2.4 Arithmetic Logic Unit. . . ........................................................30

2.4.1 Address ing Modes ....................................................... 30

2.4.2InstructionTypes ........................................................ 30

3EPROMProgramming........................................... 33

3.1EPROMProgrammingPhaseProcedure...........................................34

3.1.1EPROMOperation....................................................... 35

3.1.2EPROMLocking......................................................... 35

3.1.3EPROMWriting ......................................................... 35

3.1.4EPROMReading/VerifyMarginMode........................................ 35

3.1.5StandbyMode.......................................................... 36

3.1.6IDcode................................................................ 36

3.2EpromErasure...............................................................36

4INTERRUPTS.................................................. 37

4.1InterruptOperation............................................................37

4.2 Global Interrupt Request Enabling ................................................38

4.3InterruptSources .............................................................38

4.4 Interrupt Maskability . . . ........................................................38

3/94

ST52T400/T440/E440/T441

4.5InterruptPriority ..............................................................40

4.6InterruptsandLowpowermode..................................................41

4.7InterruptRESET..............................................................41

5CLOCK,RESET&POWERSAVINGMODE.......................... 42

5.1ClockSystem................................................................42

5.2Reset.......................................................................43

5.2.1ExternalReset .......................................................... 43

5.2.2ResetOperation......................................................... 43

5.2.3Power-onReset(POR).................................................... 43

5.2.4Brown-OutDetector(BOD)................................................. 44

5.3PowerSavingModes..........................................................44

5.3.1WaitMode.............................................................. 44

5.3.2HaltMode.............................................................. 44

6I/OPORTS.................................................... 46

6.1Introduction..................................................................46

6.2 Input Mode ..................................................................47

6.3OutputMode.................................................................47

6.4AlternateFunctions............................................................48

6.5I/OPortConfigurationRegisters..................................................48

7 ANALOG COMPARATOR (ST52x440/441)........................... 50

7.1AnalogModuleOverview.......................................................50

7.2ComparatorMode.............................................................50

7.3A/DConverterMode...........................................................50

7.3.1OperatingModes........................................................ 51

8WATCHDOGTIMER............................................. 54

8.1 Functional Desc ript ion . ........................................................54

8.2RegisterDescription...........................................................55

9PWM/TIMER................................................... 56

9.1TimerMode..................................................................56

9.2PWMMode..................................................................57

9.3TimerInterrupt ...............................................................59

10TRIAC/PWMDRIVER........................................... 63

10.1TRIAC/PWMDriverSetting.....................................................64

10.2PWMModeSettings..........................................................65

10.3BurstMode.................................................................66

10.4PhaseAnglePartializationWorkingMode.........................................68

11ELECTRICALCHARACTERISTICS............................... 72

11.1ParameterConditions.........................................................72

11.1.1MinimumandMaximumvalues ............................................ 72

11.1.2Typicalvalues.......................................................... 72

11.1.3Typicalcurves.......................................................... 72

11.1.4 Loading c apac it or ....................................................... 72

11.1.5Pininputvoltage........................................................ 72

11.2AbsoluteMaximumRatings ....................................................72

4/94

ST52T400/T440/E440/T441

TABLE OF CONTENTS

11.3 Recommended Operating Condition. . . ...........................................74

11.4SupplyCurrentCharacteristics..................................................75

11.5Brown-OutDetectorcharacteristics ..............................................76

11.6ClockandTimingCharacteristics................................................77

11.7MemoryCharacteristics .......................................................78

11.8ESDPinProtectionStrategy....................................................79

11.8.1 Standard Pi n Protection . ................................................. 79

11.9PortPinCharacteristics .......................................................80

11.9.1 General Charact eristics . ................................................. 80

11.10..........................................................................82

11.11ControlPinCharacteristics ....................................................84

11.11.1RESET pin ........................................................... 84

11.11.2Poweronreset........................................................ 84

11.11.3VPPpin.............................................................. 84

11.12AnalogComparatorCharacteristics.............................................85

11.13TriacDriverCharacteristics....................................................85

ORDERINGINFORMATION........................................ 92

5/94

ST52T400/T440/E440/T441

6/94

ST52T400/T440/E440/T441

1 GENERAL DESCRIPTION

1.1 Introduction

ST52x400/440/441 are 8-bit Intelligent Control

Units (ICU) of th e ST Five Family, w hich are able

to perform both boolean and fuz z y al gorithms in

an efficient manner, in order to reac h the best performances that the two methodologies allow.

ST52x400/440/441 is produced by STM icroelectronics using the reliable high performa nce CMOS

process, including integrated-on-chip peripherals

that allow maximization of system reliability,

decreasing system costs and minimizing the

number of externa l components.

The flexible I/O configuration of ST52x400/440/

441 allows for an interface with a wide range of

external devices, like D /A converters or power

control devices.

ST52x400/440/441 pins are configurable, allowing

the user to set the input or output signals on each

single pin.

A hardware multiplier (8 bit by 8 bit with 16 bit

result) and divider (16 bit over 8 bit with 8 bit

result and 8 bit remainder) is available to implement complex functions by using a s ingle inst ruction, optimizing program memory utilization and

computational speed.

Fuzzy Logic dedicated structures in ST52x400/

440/441 ICU’s c an be exploited to model complex

sys

tems with high accuracy in a useful and easy way.

Fuzzy Expert Systems for overall system manage ment and fuzzy Real time Controls can be

designed to increas e performances at highly com petitive costs.

The linguistic approach charac terizing Fuzzy

Logic is based on a set of IF-THEN rules, which

describe the control behavior, as well as on Membership Functions, which are associated to input

and output variables .

Up to 334 Membership Functions, with triangular

and t ra pez oidal sh apes , or singleton value s are

available to describe fuzzy variables.

The T IMER/PWM peripheral allows the management of pow er devices and timing signals, implementing different operating modes and high

frequency PWM (Pulse W ith Modulation) c ontrols.

Input Capture and Out put Compare functions are

available on the TIMER.

The programmable Timer has a 16 bit Internal

Prescaler and an 8 bit Counter.It can use internal

or external START/STOP signals and clock.

An internal programmable WATCHDOG is available to avoid loop errors and to res et the ICU.

An Anal og Comparator with a 6 channel multiplexer is a vailable on ST52x440/441 family

devices. This analog peripheral allows easy implementation of a high resolution A /D conversion. By

using only an ex ternal capacitor this peripheral

may b e configured in order to achieve up to 12 bit

A/D converter resolution. It includes a 2.5 V bandgap reference for A/D conversion calibration,

which can be used externally for s ignal conditioning.

An on-chip TRIAC driver peripheral allows the

direct management of power devices, implementing two different operating modes: Burs t Mode

(i.e. Thermal Applications), Phas e Angle Partialization (i.e. Motors Control by Triacs). The TRIAC

Driver also generates a PWM signal.

The ST52x400/440/441 family also includes an

on-chip Power-on-Reset (POR), which provides

an internal chip res et during power up situation

and a Brown-Out Detector (BOD), which resets

the ICU if the vol tage source V

dips below a

DD

minimum value.

In order to op timize energy consumption, two different power saving modes are available: Wait

mode and Halt mode.

Program Memory (EPROM/OTP) addressing

capability addresses up to 8 Kbytes of memory

locations to store both program instructions and

permanent data.

EPROM can be locked by the user to prevent

external undesired operations.

Operations may be performed on data stored in

RAM, allowing the direct combination of new input

and feedback data. All bytes of RAM are used like

Register File.

OTP (One Time Programmable) version devices

are fully compatible with t he EPROM windowed

version, which may be used for prototyping and

pre-production phases of development.

A powerful development environment consisting

of a board a nd software tools allows an easy c onfiguration and use of ST52x400/440/ 441.

The VISUAL FIVE

TM

software tool allows development of projects through a user-friendly graphical interface and optimization of generated code.

7/94

ST52T400/T440/E440/T441

1.2 Operational Description

ST52x400/440/441 IC U can work in two modes:

■ Memory Programming P has e

■ Work ing Phase

according to RESET and Vpp signals levels (see

pins description) .

Note: When RESET=0 it is advisable not to use

the sequence “101010“ to port PA ( 7 : 2 ).

1.2.1 M emory Programmi ng Phase.

The ST52x400/440/441 memory is loaded in the

Memory Programming Phase. All fuzzy and standard instructions are written inside the memory.

This phase starts by setting the control signa ls as

illustrated in (see Table 1.1).

When t his phase starts, the ST52x400/440/441

core is set to RESET status; then 12V are

applied to the Vpp pin in order to start EPR OM

programming. A signal applied to PB1 is used to

increment the memory address; the data is supplied to PORT A (see E PROM programming for

further details).

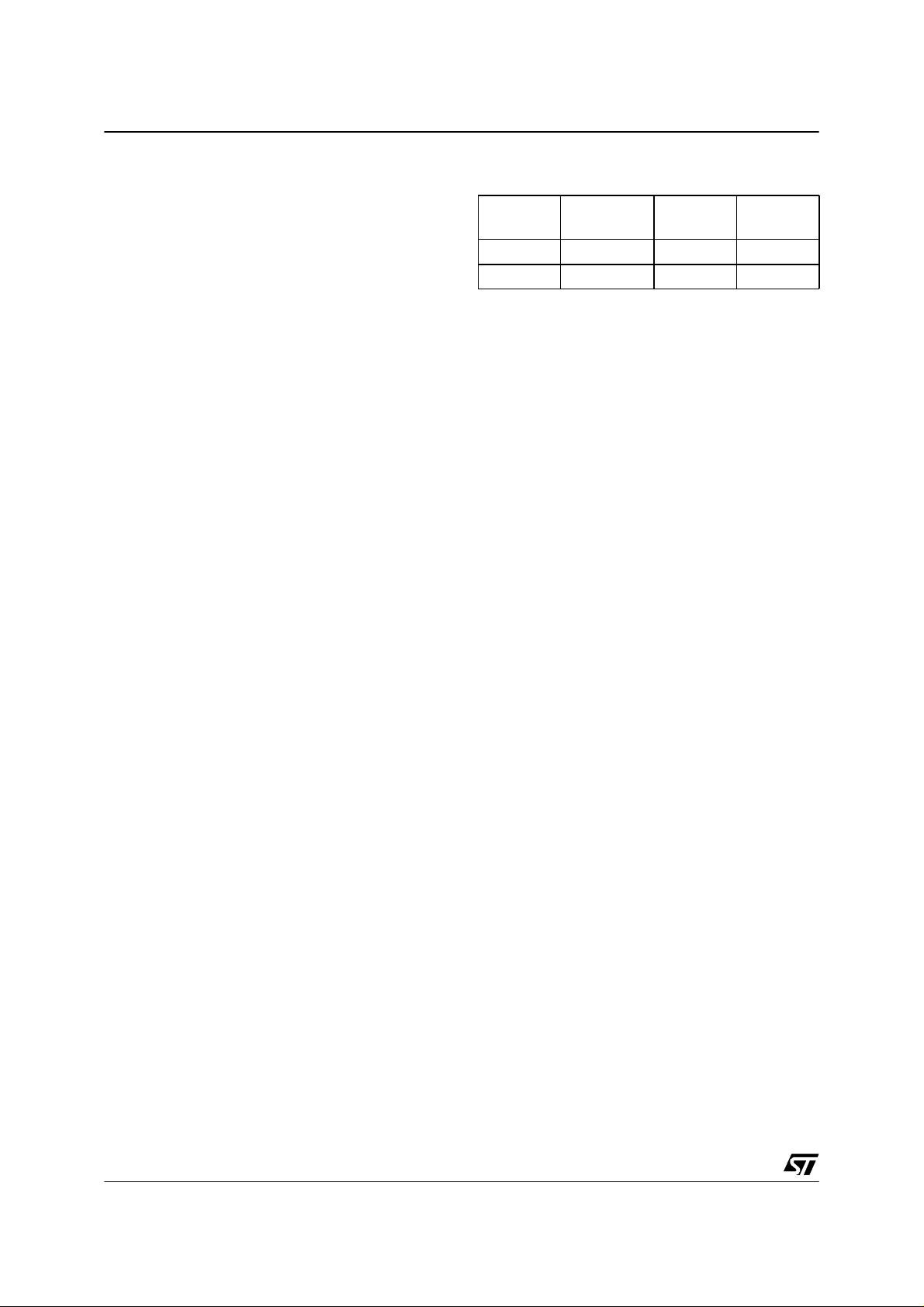

Table 1.1 Control Signals Setting

Control

Signal

RESET 0 0 1

Vpp 5V /12V 0 0

Pro-

gramming

Reset Working

1.2.2 Working Mode.

The processor starts the work ing phase following

the inst ructions, which have been previously

loaded in the memory.

ST52x400/440/441’s internal structure includes a

computational block, CO NTRO L UNIT (CU)/DATA

PROCESSING UNIT (DPU), which allows processing of boolean functions and fuzzy algorithms.

The CU/DPU can manage up to 334 different

Membership Functions for the fuzzy ru les antecedent part. The rule consequents are “crisp” val ues (real numbe r s). The maximum number of

rules that can be defined is limited by the dimensions of the implemented standard algorithm.

EPROM is then shared between fuzzy and standard algorithms. The Membership Function data is

stored inside the f irst 1024 memory locations. The

Fuzzy rules are parts of the program instructions.

The Control Unit (CU) reads the in format ion and

the status deriving from the peripherals.

Arithmetic calculus can be performed on these

values by using the internal CU and the 128/256

bytes of RAM, which supports all computations.

The peripheral input can be fuzzy and/or arith metic output, or the values contained in Data RAM

and EPROM locations.

8/94

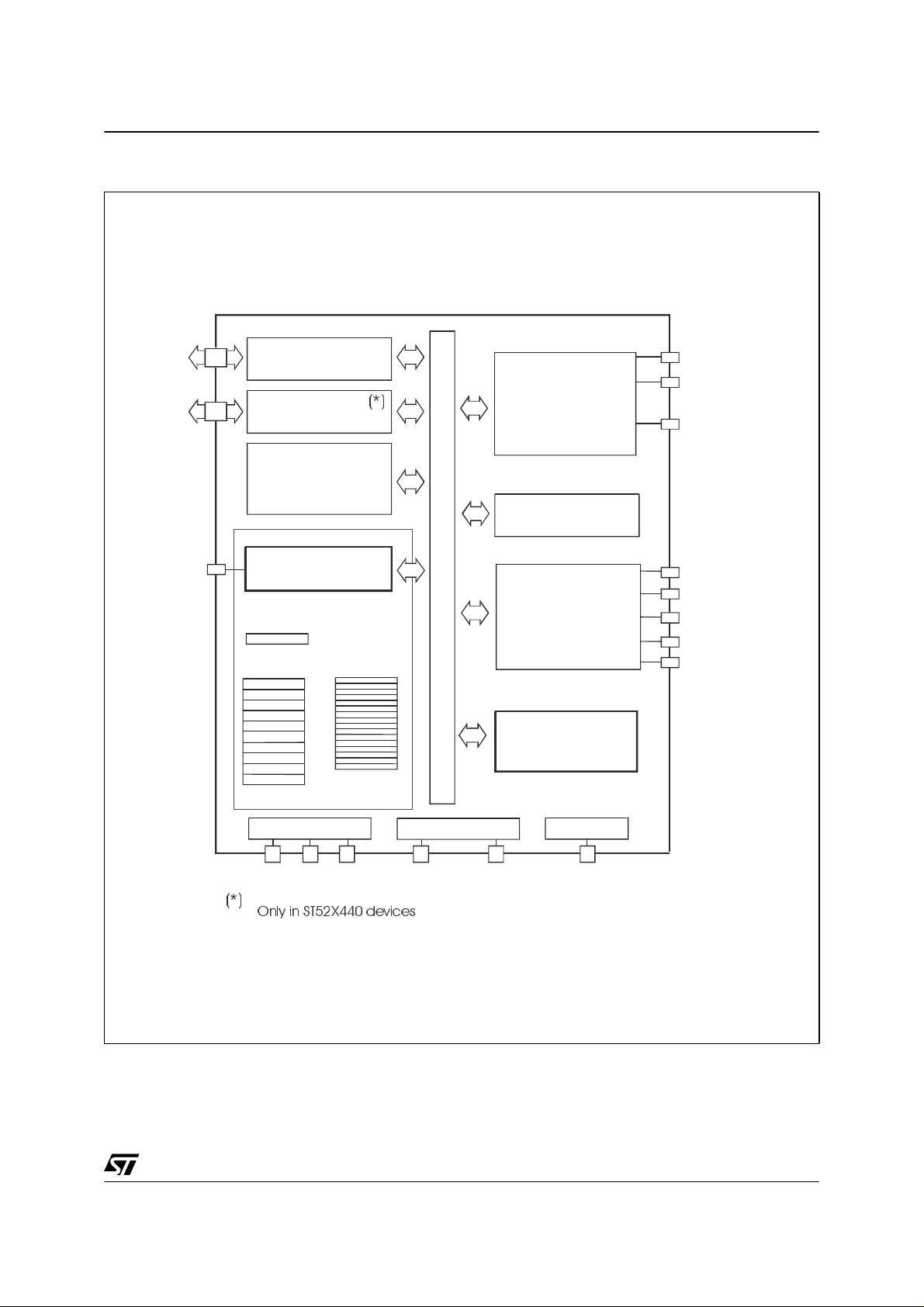

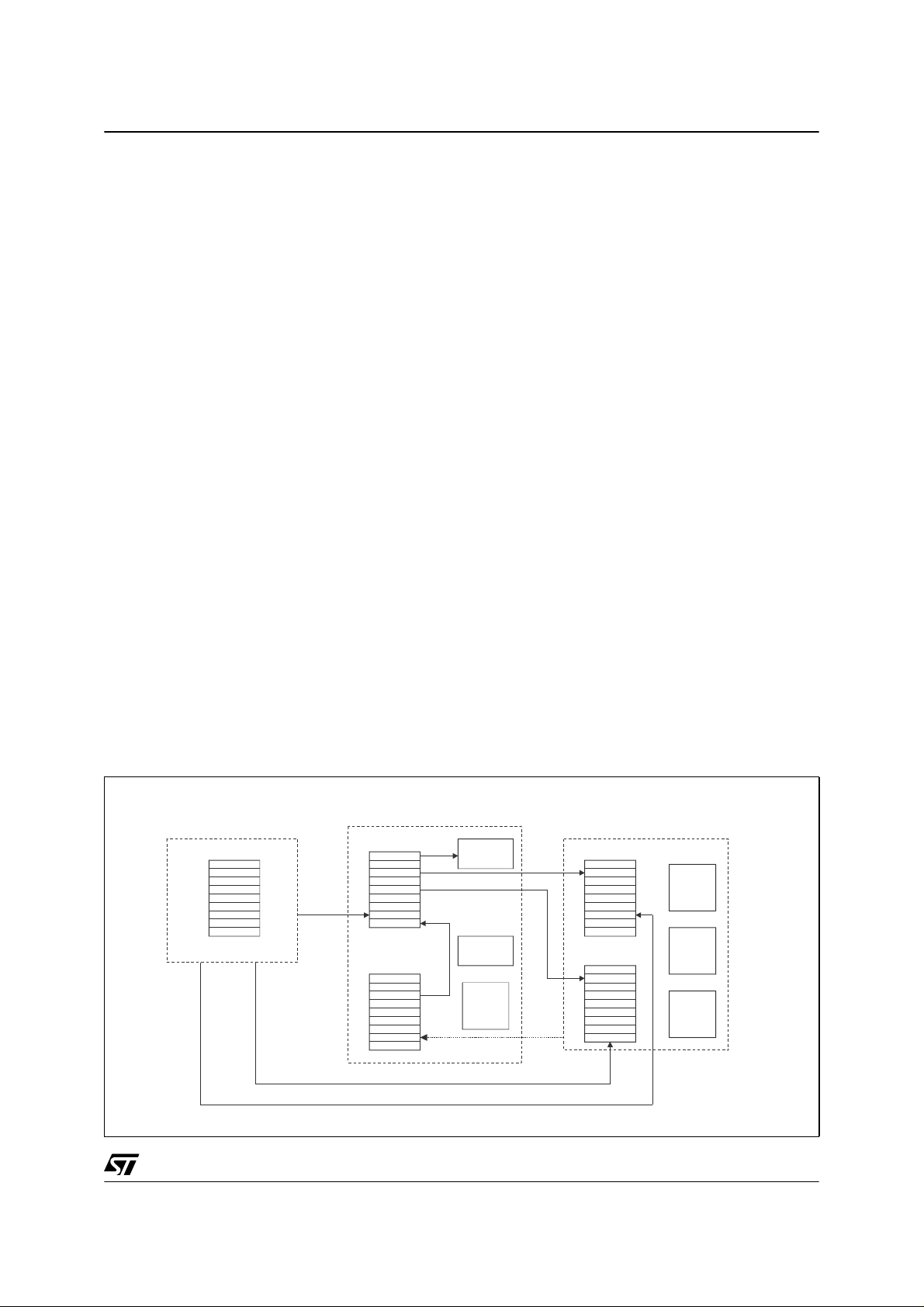

Figure 1.1 ST52x400/440/441 Block Diagram

E

R

TCL

K

TOUTTS

M

A

M

A

ROUT

TOUT

Pow

erOn

t

ST52T400/T440/E440/T441

INT

I/O PORT

ANALOG

COMPARATOR

USER PROGRAM

EPROM

8 KBytes

CONTROL

UNIT

PC

CU Input

Registers

256 Bytes

(*)

RAM

IN1

IN2

TRIAC DRIV

T

WATCHDOG

TRT

TRES

TIMER/PWM

N

ALU &

DECISION

PROCESSOR

POWER SUPPLY and BOD

VPP

(*)

Only in ST52X440 devices

OSCILLATOR

Rese

RESETOSCOUTOSCINVSSVDD

9/94

ST52T400/T440/E440/T441

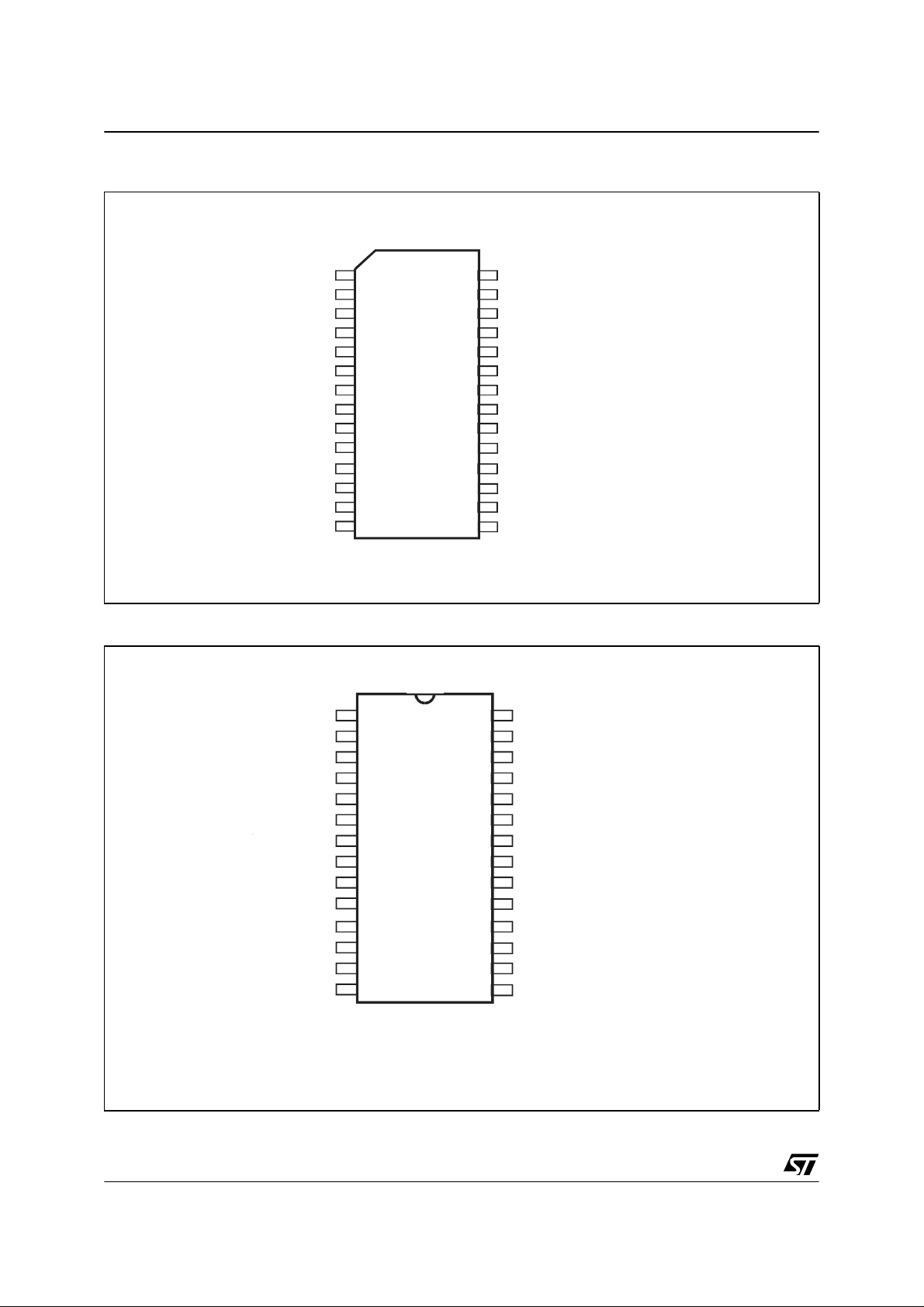

Figure 1.2 ST52x400 SO28 P in Configuration

OSCOUT

OSCIN

Vpp

PC4

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Figure 1.3 ST52x400 PDIP28 Pin Configuration

OSCOUT

OSCIN

Vpp

PC4

PC3

PB7

PB6

PB5

PB4

PB3

PB2

PB1

PB0

Vss

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Vdd

Vss

RESET

PC0

PC1PC3

PC2

PA7/INT

PA6/TRES/TOUT

PA5/TCLK

PA4/TSTRT

PA3

PA2/MAIN2/TOUTN

PA1/MAIN1

PA0/TROUT

Vdd

Vss

RESET

PC0

PC1

PC2

PA7/INT

PA6/TRES/TOUT

PA5/TCLK

PA4/TSTRT

PA3

PA2/MAIN2/TOUTN

PA1/MAIN1

PA0/TROUT

10/94

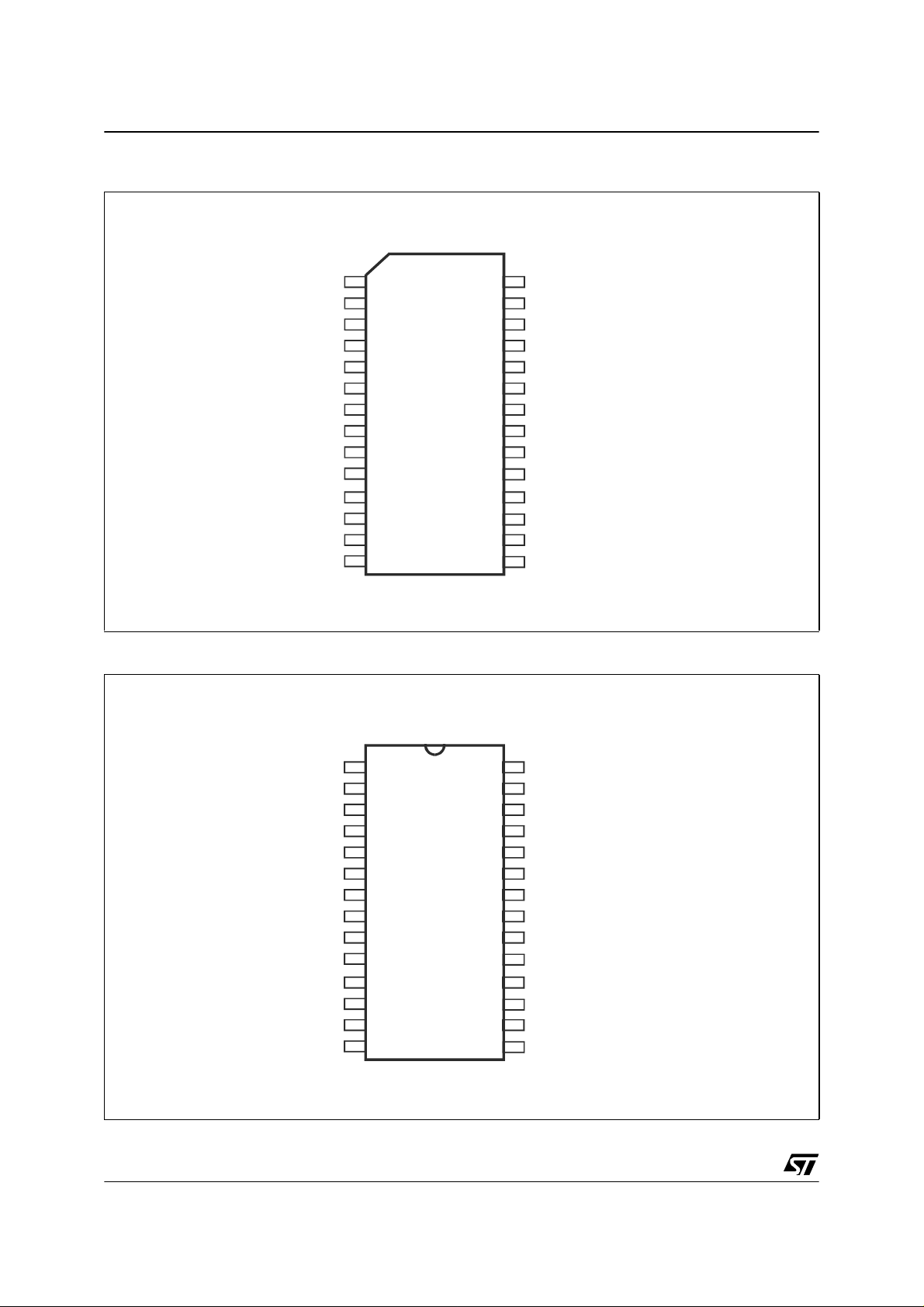

Figure 1.4 ST52x400 SO20 P in Configuration

ST52T400/T440/E440/T441

Figure 1.5 ST52x400 PDIP20 Pin Configuration

11/94

ST52T400/T440/E440/T441

Figure 1.6 ST52x440/441 SO2 8 Pin Configuration

OSCOUT

OSCIN

Vpp

PC4

PB7/CS

PB5/AC5

PB4/AC4

PB3/AC3

PB2/AC2

PB1/AC1

PB0/AC0

GNDA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Figure 1.7 ST52x440/441 PDIP28 Pin Configuration

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Vdd

Vss

RESET

PC0

PC1PC3

PC2

PA7/INT/ACSYNCPB6/BG

PA6/TRES/TOUT

PA5/TCLK

PA4/TSTRT

PA3/ACSTRT

PA2/MAIN2/TOUTN

PA1/MAIN1

PA0/TROUT

12/94

OSCOUT

OSCIN

Vpp

PC4

PC3

PB7/CS

PB6/BG

PB5/AC5

PB4/AC4

PB3/AC3

PB2/AC2

PB1/AC1

PB0/AC0

GNDA

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

Vdd

Vss

RESET

PC0

PC1

PC2

PA7/INT/ACSYNC

PA6/TRES/TOUT

PA5/TCLK

PA4/TSTRT

PA3/ACSTRT

PA2/MAIN2/TOUTN

PA1/MAIN1

PA0/TROUT

Figure 1.8 ST52x440/441 SO2 0 Pin Configuration

ST52T400/T440/E440/T441

Figure 1.9 ST52x440/441 PDIP20 Pin Configuration

13/94

ST52T400/T440/E440/T441

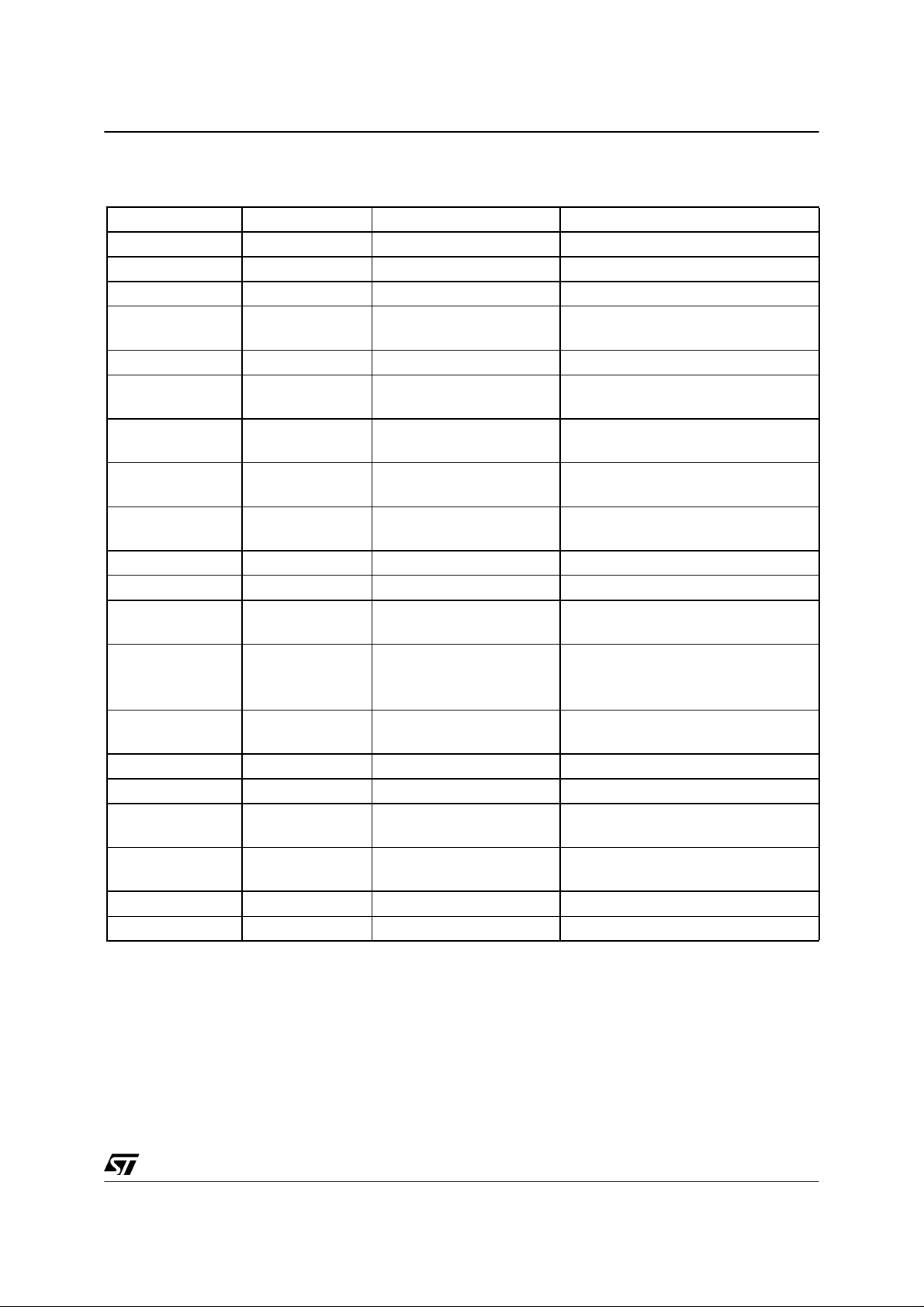

Table 1.2 SO28 and DIP28 Pin Configuration - ST52x400

PIN SO28/DIP28 NAME Programming Phase Working Phase

1 OSCOUT Oscillator Output

2 OSCIN Oscillator Input

3 Vpp

EPROM Programming

Power supply (12V±5%)

4 PC4 Digital I/O

5 PC3 Digital I/O

6 PB7 PHASE signal (PHASE) Digital I/O

7 PB6 Digital I/O

8 PB5 Digital I/O

9 PB4 Digital I/O

10 PB3

Configuration INCREMENT

(INC_CONF)

EPROM V

Digital I/O

DD

or Vss

11 PB2

12 PB1

13 PB0

Configuration RESET

(RST_CONF)

Address INCREMENT

(INC_ADD)

Address Reset

(RST_ADD)

Digital I/O

Digital I/O

Digital I/O

14 Vss This pin must be tied to Digital Ground

15 PA0/TROUT I/O EPROM Data Digital I/O - TRIAC Driver Output

16 PA1/MAIN1 I/O EPROM Data

17

PA2/MAIN2/

TOUTN

I/O EPROM Data

Zero Crossing Detection pin 1

Zero Crossing Detection pin 2

Complementary Timer Output

Digital I/O

Digital I/O

18 PA3 I/O EPROM Data Digital I/O

19 PA4/TSTRT I/O EPROM Data Digital I/O - Timer external start

20 PA5/TCLK I/O EPROM Data Digital I/O - Timer external clock

21 PA6/TRES/TOUT I/O EPROM Data

22 PA7/INT I/O EPROM Data

Timer external reset - Timer output

Digital I/O

Digital I/O

External Interrupt

23 PC2 Digital I/O

24 PC1 Digital I/O

25 PC0 Digital I/O

26 RESET General Reset General Reset

27 V

28 V

SS

DD

Digital Ground Digital Ground

Digital Power Supply Digital Power Supply

14/94

ST52T400/T440/E440/T441

Table 1.3 SO20 and DIP20 Pin Configuration - ST52x400

PIN SO20/DIP20 NAME Programming Phase Working Phase

1V

DD

2 OSCOUT Oscillator Output

3 OSCIN Oscillator Input

4 Vpp

5 PB7 PHASE signal (PHASE) Digital I/O

6 PB3

Digital Power Supply Digital Power Supply

EPROM Programming

Power supply (12V±5%)

Configuration INCREMENT

(INC_CONF)

EPROM V

Digital I/O

DD

or Vss

7 PB2

8 PB1

9 PB0

Configuration RESET

(RST_CONF)

Address INCREMENT

(INC_ADD)

Address Reset

(RST_ADD)

Digital I/O

Digital I/O

Digital I/O

10 Vss This pin must be tied to Digital Ground

11 PA0/TROUT I/O EPROM Data Digital I/O - TRIAC Driver Output

12 PA1/MAIN1 I/O EPROM Data

13

PA2/MAIN2/

TOUTN

I/O EPROM Data

Zero Crossing Detection pin 1

Zero Crossing Detection pin 2

Complementary Timer Output

Digital I/O

Digital I/O

14 PA3 I/O EPROM Data Digital I/O

15 PA4/TSTRT I/O EPROM Data Digital I/O - Timer external start

16 PA5/TCLK I/O EPROM Data Digital I/O - Timer external clock

17 PA6/TRES/TOUT I/O EPROM Data

18 PA7/INT I/O EPROM Data

Timer external reset - Timer output

Digital I/O

Digital I/O

External Interrupt

19 RESET General Reset General Reset

20 V

SS

Digital Ground Digital Ground

15/94

ST52T400/T440/E440/T441

Table 1.4 SO28 and DIP28 Pin Configuration - ST52x440/441

PIN SO28/DIP28 NAME Programming Phase Working Phase

1 OSCOUT Oscillator Output

2 OSCIN Oscillator Input

3 Vpp

EPROM Programming

Power supply (12V±5%)

4 PC4 Digital I/O

5 PC3 Digital I/O

6 PB7/CS PHASE signal (PHASE) Digital I/O - Capacitor connection

7 PB6/BG Digital I/O - Bandgap reference

8 PB5/AC5

EPROM V

Digital I/O

Analog Comparator Channel 5

DD

or Vss

9 PB4/AC4

10 PB3/AC3

11 PB2/AC2

12 PB1/AC1

13 PB0/AC0

Configuration INCREMENT

(INC_CONF)

Configuration RESET

(RST_CONF)

Address INCREMENT

(INC_ADD)

Address Reset

(RST_ADD)

Analog Comparator Channel 4

Analog Comparator Channel 3

Analog Comparator Channel 2

Analog Comparator Channel 1

Analog Comparator Channel 0

Digital I/O

Digital I/O

Digital I/O

Digital I/O

Digital I/O

14 GNDA Analog Ground Analog Ground

15 PA0/TROUT I/O EPROM Data Digital I/O - TRIAC Driver Output

16 PA1/MAIN1 I/O EPROM Data

Digital I/O

Zero Crossing Detection pin 1

17

PA2/MAIN2/

I/O EPROM Data

TOUTN

18 PA3/ACSTRT I/O EPROM Data

Zero Crossing Detection pin 2

Digital I/O

Digital I/O

Analog Comp. counter external start

19 PA4/TSTRT I/O EPROM Data Digital I/O - Timer external start

20 PA5/TCLK I/O EPROM Data Digital I/O - Timer external clock

21 PA6/TRES/TOUT I/O EPROM Data

Timer external reset - Timer output

Digital I/O

16/94

22

PA7/INT/

ACSYNC

I/O EPROM Data

Digital I/O - External Interrupt

Analog Comparator counter ready

23 PC2 Digital I/O

24 PC1 Digital I/O

25 PC0 Digital I/O

26 RESET General Reset General Reset

27 V

28 V

SS

DD

Digital Ground Digital Ground

Digital Power Supply Digital Power Supply

ST52T400/T440/E440/T441

Table 1.5 SO20 and DIP20 Pin Configuration - ST52x440/441

PIN SO20/DIP20 NAME Programming Phase Working Phase

1V

DD

2 OSCOUT Oscillator Output

3 OSCIN Oscillator Input

4 Vpp

5 PB7/CS PHASE signal (PHASE) Digital I/O - Capacitor connection

6 PB3/AC3

Digital Power Supply Digital Power Supply

EPROM Programming

Power supply (12V±5%)

Configuration INCREMENT

(INC_CONF)

EPROM V

Digital I/O

Analog Comparator Channel 3

DD

or Vss

7 PB2/AC2

8 PB1/AC1

9 PB0/AC0

Configuration RESET

(RST_CONF)

Address INCREMENT

(INC_ADD)

Address Reset

(RST_ADD)

Analog Comparator Channel 2

Analog Comparator Channel 1

Analog Comparator Channel 0

Digital I/O

Digital I/O

Digital I/O

10 GNDA Analog Ground Analog Ground

11 PA0/TROUT I/O EPROM Data Digital I/O - TRIAC Driver Output

12 PA1/MAIN1 I/O EPROM Data

13

PA2/MAIN2/

TOUTN

I/O EPROM Data

14 PA3/ACSTRT I/O EPROM Data

Zero Crossing Detection pin 1

Zero Crossing Detection pin 2

Complementary Timer Output

Analog Comp. counter external start

Digital I/O

Digital I/O

Digital I/O

15 PA4/TSTRT I/O EPROM Data Digital I/O - Timer external start

16 PA5/TCLK I/O EPROM Data Digital I/O - Timer external clock

17 PA6/TRES/TOUT I/O EPROM Data

18

PA7/INT/

ACSYNC

I/O EPROM Data

Timer external reset - Timer output

Digital I/O - External Interrupt

Analog Comparator counter ready

Digital I/O

19 RESET General Reset General Reset

20 V

SS

Digital Ground Digital Ground

17/94

ST52T400/T440/E440/T441

1.3 Pin Description

ST52x400/440/441 pins can be set in digital input

mode, digital output mode or in Alternate Functions. The pin configuration is ac hieved by means

of the configuration registers. The functions of the

ST52x400/440/441 pins are described bel ow:

V

Main Power Supply Voltage (5V ± 10%).

DD.

. Digital circuit Ground. All Vss pins must be

V

SS

connected to ground (see ST52 T400 pin-out).

ACSTRT, ACSYNC(*). These pins are us ed to

synchronize the 16-bit counter of the Analog Comparator with an external ramp generator. The

ACSTRT input is us ed to start the counter. The

ACSYNC output is set when the counter is ready

to start a new count.

BG(*). A Bandgap Reference value of 2.5V is

available on this p in. It can be used for analog signal conditioning.

GNDA. Analog c ircuit ground of the Analog Comparator. Must be tied to V

. Main Power Supply for internal E PROM pro-

V

PP

SS

.

gramming and MODE selector. During the Programming phase V

Working phase V

must be set at 12V. In the

PP

must be equal to VSS.

PP

OSCin and OSCout. These pins are internally

connected to the on-chip osc illator circuit. A quartz

crystal or a ceramic resonator can be connected

between these t wo pins in order to allow the correct operations of ST52x400/440/441 with various

stability/cost trade-offs. An external clock signal

canbeappliedtoOSCin:inthiscaseOSCout

must be grounded.

RESET. This signal is used to reset the

ST52x400/440/441 and re-initialize the regist ers

and control signals. It also allows the user to

select the working mode of the device.

PA0-PA7, PB0-PB7,PC0-PC4. These lines are

organized as I/O ports. Each pin can be configured as an input or output. During the Programming phase the ports are used for EP R OM data

read/write operations.

TOUT, TOUTN.These pins output the signal generated by the TIMER peripheral. The T0OUTN

signal is the complement of the T0OUT one.

TRES, TSTRT, TCLK . These pins are related to

the TIMER peripheral and are used for Input Capture and event counting. The TRES pin is used to

set/reset theTimer; theTSTRT pin is used to start/

stop the counter. The Timer can be driven by the

internal clock or by an external signal connected

to the TCLK pin.

TROUT, MAIN1,MAIN2. These pins are related to

the TRIAC DRIVER peripheral. TROUT outputs

the signal generated by t he peripheral. In order to

drive a TRIA C directly w it hout the use of additional c omponents, the TROUT pin can supply up

to 50 mA (2V voltage drop). MAIN1 and MAIN2

pins are used to detect the zero crossing of the

Power Line voltage.

(*) Not available in ST52x400 devices

AC0-AC5(*). These pins are used to input the

analog signals to the Analog Comparator. An analog multiplexer is available to switch these inputs

to the Analog Comparator.

CS(*). This pin outputs the current generated in

the Analog Comparator peripheral by a current

generator, allowing charging of an external capacitor to obtain a v oltage ramp for the A / D conversion.

18/94

ST52T400/T440/E440/T441

Signals

2 INTERNAL ARCHITECTURE

ST52x400/440/441 is composed of the following

blocks and peripherals:

■ Cont rol Unit (CU)

■ Dat a P roc es sing Unit (DPU)

■ ALU

■ Decision Processor (DP)

■ EPROM

■ 256 Byte RAM

■ Clock Oscillator

■ Analog Multiplexer and Analog Comparator

■ 1PWM/Timer

■ 1 Triac/PWM Driver

■ Digital I/O port

2.1 Control Unit and Data Processi ng Unit

The Control Unit (CU) formally includes five m ain

blocks. Each block decodes a set of instructions,

generating the appropriate control signals. The

mainpartsoftheCUareshowninFigure2.1.

The five different parts of the CU manage Loading, Logic/Arithmetic, Jump, Control and Decision

Processor (DP) instructions s ets.

The block called “Collector” manages the signals

deriving from the different parts of the CU then

defines the signals fo r the Data Processing Unit

(DPU) and for the different peripherals of the ICU.

The block called “Arbiter” manages the different

parts of the CU in order to have only one part of

the system activat ed during working mode.

The CU structure is highly flexible, designed with

the objective of easily adapt ing the core of the

microcontroller to market needs. New instructions

sets or new peripherals can be easily included

without changing the structure of the microcontroller, maintaining code compatibility.

The C U reads and decodifies the instructions

stored on the EPROM (Fetch). According to the

instructions type, the Arbiter activates one of the

main blocks of the CU. Afterwards, all the control

signals for the DPU are generat ed.

A set of 55 d ifferent arithmetic, DP and logic

instructions is available. T he arithmetic instructions operate to all the RAM addresses without the

need of using special registers.

The DPU receives, stores and sends the instructions coming from the EPROM, RAM or from the

peripherals in order to execute them .

2.1.1 Program Counter .

The Program Counter (PC) is a 13-bit regi ster that

contains the address of t he next memory location

to be proc es s ed by the core. This memory location may be an opcode, an operand or an address

of an operand.

Figure 2.1 CU Block Diagram

MicroCode

A

R

B

I

T

E

R

Clock Master

Loading

Instruction Set

Logic Arithmetic

Instruction Set

Jump

Instruction Set

Control

Instruction Set

Decision Processor

Instruction Set

C

O

L

L

E

C

T

O

R

Control

19/94

ST52T400/T440/E440/T441

add_EPR

S

C

Figure 2.2 Data Processing Unit (DPU )

U

EPROM

INPUTS

PERIPHERALS

M

U

X

ADDRESS RAM

STACK POINT

PROGRAM COUNTER

RAM

128 Bytes

ACCUMULATOR

FLAGS REG.

PERIPHERAL

REGISTERS

MULTIPLEXER

ALU

Figure 2.3 CU/DPU Block Diagram

E

P

R

Microcode

O

M

RAM

C

U

Con tr ol S ig n a ls

EPR OM Address

RAMData8Bit

RAM A ddr.

8Bit

RAM

Data Out

8Bit

D

P

U

To Peripherals

From

P erip he ra ls

20/94

ST52T400/T440/E440/T441

P

ERIPHERALBLO

ONCHIP

RAL

E

ONF

I

REG

IST

ERS

P

ERIPHERAL

P

ERIPHERALBLO

D

C

LDPR

The 13-bit length allows the direct addressing of

8192 bytes in the program space: jump and call

instruction support the absolute addressing in all

the memory.

After having read the curren t instruction address,

the PC value is incremented. Th e result of this

operation is shifted back into the PC.

The PC can be changed in the following ways:

■ J P (Jump) instruction PC = Jump Address

■ Interrupt PC = Interrupt Vector

■ RETI instruction PC = Pop (stack)

■ Reset PC = Reset Vector

■ Norm al Instruction PC = PC + 1

2.1.2 Flags.

The ST52x400/440/ 441 core includes different

sets of flags that correspond to 2 different modes:

normal mode and interrupt mode. Each set of

flags consist of a CARRY flag (C), ZERO flag (Z)

and SIGN f lag (S). One set of f lags (CN, ZN, SN)

is used during normal operation and one is used

during interrupt mode (CI, ZI, SI). Formally, the

user has to manage only one set of flags: C, Z and

S.

The ST52x400/440/441 core uses the flags that

correspond to the actual mode: as soon as an

interrupt is gen erated , the ST FIVE core uses the

interrupt flags instead of the normal flags.

Each interrupt lev el has its own set of flag s, which

is saved in the Flag Stack during interrupt servic-

ing.

These flags are restored from th e Flag Stack automatically when a RETI instruction i s executed.

If the ICU was in the normal mode before an interrupt, a fter the RETI instruction is executed, the

normal flags are restored.

Note:

A CALL subroutine is a normal mode execution. For this reason a RET instruction, consequent to a CALL instruction, doesn’t affect the

normal mode set of flags.

Flags are not cleared during context switchin g and

remain in the state they were located in at the end

of the last i nterrupt routine switching.

The Carry flag is set when an overflow o ccurs during arithmetic operations, otherwise it is cleared.

The Sign flag is set when an und erflow occurs

during arithmetic operations, otherwise it is

cleared.

2.2 Address Spaces

ST52x400/440/441 has four separate address

spaces:

■ RAM: 128 or 256 Bytes

■ 20 Input Registers

■ 6 Output Registers

■ 21 Configuration Registers

■ Program memory:up to 8K Bytes

The Program Memory will be described in further

details in the EPROM section

Figure 2.4 Address Spaces Description

PROGRAM MEMORY

NON VOLATILEMEMORY

LDRE

LDCE

LDPE

DATARAM

INPUT REGISTERS

ST FIVE CORE

LDFR

LDRI

DP

REGISTERS

PROGRAM

COUNTER

CU

DPU

ALU

PERIPHE

OUTPUT

R

GISTER

GURATION

C

L

R

S

CK

CK

BLOCK

21/94

ST52T400/T440/E440/T441

2.2.1 Ram and Stack.

RAM consists of 128 (G0/G1/F0/F1 types) or 256

(G2/G3/F2/F3 t y pes ) general purpos e 8-bit regis ters.

All the registers in RAM can be specified by using

a decimal address, e.g. 0 identifies the first register of RAM.

To read or write in the RAM registers, the LOAD

instructions must be used (see Table 2.5).

When the instructions like Interrupt request or

CALL are executed, a STACK is us ed to push the

PC. The STACK is push directly in the RAM. For

each level of stack 2 bytes of RAM are used. The

values of this stack are stored from the last RAM

register (address 255). The maximum level of

stack must be less than 128. When a subroutine

call or interrupt request occurs, the c ontents of

each level is shifted into the next level while the

content of the PC is shifted into the first level.

When a subroutine or interrupt return o ccurs (RE T

or RETI instructions), the first level register is

shifted back into the PC and the value of each

level is popped back into the previous level. These

operating modes are illustrated in Figure 2.5.

2.2.2 Input Registers Benc h.

The Input Registers (IR) bench c ons ists of 20 8-bit

registers containing data derivi ng from the peripherals and parallel p orts.

All the registers can be sp ecified by using a decimal address, e.g. 0 identifies th e first regist er of

the IR.

The assembler instruction:

the value in the

inp

LDRI reg,inp_teg

loads

IR to the register (RAM location) identified by the address reg.

The first input register is dedicated to store the

value of t he stack pointer. The next 12 registers of

the IR are dedicated to the 6 (for ST52X440G/

441G) or the 4 converted values (for ST52X440F/

441F) in c as e of converted values coming from

the Analog Comparator (in S T52x400 devices

these registers are not used ). Each of these values are s tored on two bytes because of the resolution of the A/D conv ersion process. The last 7

registers contain data from t he I/O ports and

PWM/Timers. Table 2.1 summarizes the IR

address and the relative peripheral. In order to

simplify the concept a mnemonic name is

assigned to the registers. The s ame name is used

in VISUAL FI VE development tools.

Figure 2.5 S tack Operation

WHEN RETI OR RET

OCCURS

REG 0

REG 1

REG 2

REG 3

REG 4

REG 5

REG 252

REG 253

REG 254

REG 255

PROGRAM COUNTER

RAM

WHENCALLOR

INTERRUPT REQ.

OCCURS

Stack

Pointer

STACK LEVEL n

..........................

STACK LEVEL 2

STACK LEVEL 1

22/94

ST52T400/T440/E440/T441

2.2.3 Co nfi gu ration Registers.

The ST52x400/440/441 Configuration Registers

allow the configuration of all the blocks of the ICU.

Table 2.2 describes the functions and the related

peripherals of t he 21 C onfiguration Registers

available: in o rder to simplify the concept a mnemonic name is assigned to each Configuration

Register. The same name is used in VISUAL

TM

FIVE

development tools. By using the load

instructions the Configuration R egisters may be

set by using values stored in the Program Memory

(EPROM) or in the RA M.

The assembler instruction

the Configuration Register

of memory location

LDCE conf,mem

conf

with the contents

mem

, inside the currently set

loads

memory page.

The assembler instructions

the Configuration Register

of the register (RAM location)

LDCR conf,reg

conf

with the contents

reg

.

loads

Use and meaning of e ach register will be

described in further details in the corresponding

section.

2.2.4 Output Registers.

The O utpu t Registers (OR) consist of 6 registers

containing data for the ICU peripherals including I/

OPorts.

All registers can be specified by using a decimal

address, e.g. 1 identifies the second OR.

By using the LOA D type inst ruc ti ons the Output

Registers (OR) may be set with values st ored in

the Program Memory (LDPE) or in the RAM

(LDPR).

The assembler instruction

the OutputRegister

ory location

mem

out

, inside the currently set memory

page. The assembler instruction

LDPE out,mem

with the cont ents of mem-

LDPR out,reg

loads the Output Register out with the contents of

reg

register (RAM location)

.

Table 2. 3 des c ribes the OR: in order to simplify the

concept a mnemon ic name is assigned to e ach of

the Output Registers. The same name is us ed in

VISUAL FIVE

TM

development tools. Use and

meaning of each register will b e described in further details in t he c orresponding section.

Table 2.1 Input Registers

IR MNEMONIC NAME PERIPHERAL REGISTER ADDRESS

STACK_POINTER STACK POINTER 0

AC_CHAN0H(*) Analog Comparator CHANNEL 0 High Byte 1

AC_CHAN0L(*) Analog Comparator CHANNEL 0 Low Byte 2

AC_CHAN1H(*) Analog Comparator CHANNEL 1 High Byte 3

AC_CHAN1L(*) Analog Comparator CHANNEL 1 Low Byte 4

AC_CHAN2H(*) Analog Comparator CHANNEL 2 High Byte 5

AC_CHAN2L(*) Analog Comparator CHANNEL 2 Low Byte 6

AC_CHAN3H(*) Analog Comparator CHANNEL 3 High Byte 7

AC_CHAN3L(*) Analog Comparator CHANNEL 3 Low Byte 8

AC_CHAN4H (*)(**) Analog Comparator CHANNEL 4 High Byte 9

AC_CHAN4L (*)(**) Analog Comparator CHANNEL 4 Low Byte 10

AC_CHAN5H (*)(**) Analog Comparator CHANNEL 5 High Byte 11

AC_CHAN5L (*)(**) Analog Comparator CHANNEL 5 Low Byte 12

AC_STATUS(*) Analog Comparator Status Register 13

PORT_A PORT A INPUT REGISTER 14

PORT_B PORT B INPUT REGISTER 15

PORT_C (**) PORT C INPUT REGISTER 16

TRIAC_COUNT TRIAC DRIVER COUNTER Value 17

PWM_COUNT PWM/TIMER COUNTER Value 18

PWM_STATUS TIMER STATUS REGISTER 19

(*) Not used on ST52x400xx versions

(**) Not used on ST52x400F/440F441F versions

loads

23/94

ST52T400/T440/E440/T441

Table 2.2 Configuration Registers Description

CONFIGURATION REGISTER PERIPHERAL DESCRIPTION

REG_CONF 0 INTERRUPT MASK Interrupts mask setting, Polarity, Brown Out

REG_CONF 1(*) ANALOG COMPARATOR AC Configuration Register 1

REG_CONF 2 WATCHDOG TIMER Watchdog Timer Configuration

REG_CONF 3(*) ANALOG COMPARATOR AC Configuration Register 2

REG_CONF 4 PORT A PORT A digital pin I/O direction

REG_CONF 5 PWM/TIMER PWM/TIMER Working mode Configuration

REG_CONF 6 PWM/TIMER

REG_CONF 7 PWM/TIMER PWM/TIMER Prescaler settings

REG_CONF 8 PWM/TRIAC PWM/TRIAC Prescaler settings

REG_CONF 9 PWM/TRIAC

REG_CONF 10 PWM/TRIAC PWM/TRIAC Working mode Configuration

REG_CONF 11 PORT C PORT C digital pin I/O direction

REG_CONF 12 PORT A PORT A Alternate function settings

REG_CONF 13 PORT B PORT B digital pin I/O direction

REG_CONF 14(*) PORT B PORT B settings for digital or analog pin

REG_CONF 15(*) ANALOG COMPARATOR Analog Comparator Prescaler settings

REG_CONF 16(*) ANALOG COMPARATOR Analog Comparator in A/D working mode

REG_CONF 17 INTERRUPT Interrupt priorities

REG_CONF 18 INTERRUPT Interrupt priorities

REG_CONF 19 TRIAC TRIAC Pulses Width Configuration

REG_CONF 20 TRIAC TRIAC Pulses Width Configuration

(*) Not used on ST52x400xx versions

PWM/TIMER Prescaler configuration and

output waveform selection.

PWM/TRIAC Prescaler configuration and

output waveform selection.

Table 2.3 Output Registers

OR MNEMONIC NAME PERIPHERAL REGISTER ADDRESS

PORT_A PORT A OUTPUT REGISTER 0

PORT_B PORT B OUTPUT REGISTER 1

PORT_C (**) PORT C OUTPUT REGISTER 2

PWM_COUNT TIMER/PWM COUNTER Value 3

PWM_RELOAD (*) PWM/TIMER RELOAD Value 4

not used 5

not used 6

not used 7

not used 8

TRIAC_COUNT TRIAC DRIVER COUNTER Value 9

(*)Used if Peripheral has beenprogrammed inPWM Mode (**) Not used onST52x400F/440F/441Fversions

24/94

2.3 Fu zzy Computation

ST FIVE’s Fuzzy main features are:

■ Up to 8 Inputs with 8-bit resolution;

■ 1 Kbyte of Program/Data Memory available to

store more than 300 to Membership Functions

(Mbfs) for each Input;

■ Up to 128 Outpu ts with 8-bit resolution;

■ Possibility to process fuzzy rules with an

UNLIMITED number of antecedents

■ UNLIMITED number of Rules and FuzzyBlocks.

The limits on the number of Fu zzy Rules and

fuzzy Blocks are only related to the program memory size.

2.3.1 Fuzzy Inference .

The block diagram illustrated in Figure 2.7

describes the different steps performed during a

fuzzy algo rithm. The ST FIVE Core allows the

implementation of a MAMDANI type fuzzy inference with crisp consequents. Inputs for fuzzy

inference are stored in 8 dedicated Fuzzy input

registers. The instruction LDFR is used to set the

input fuzzy registers with values stored in the Register File. The result of a fuzzy inference is stored

directly in a location of the Register File.

ST52T400/T440/E440/T441

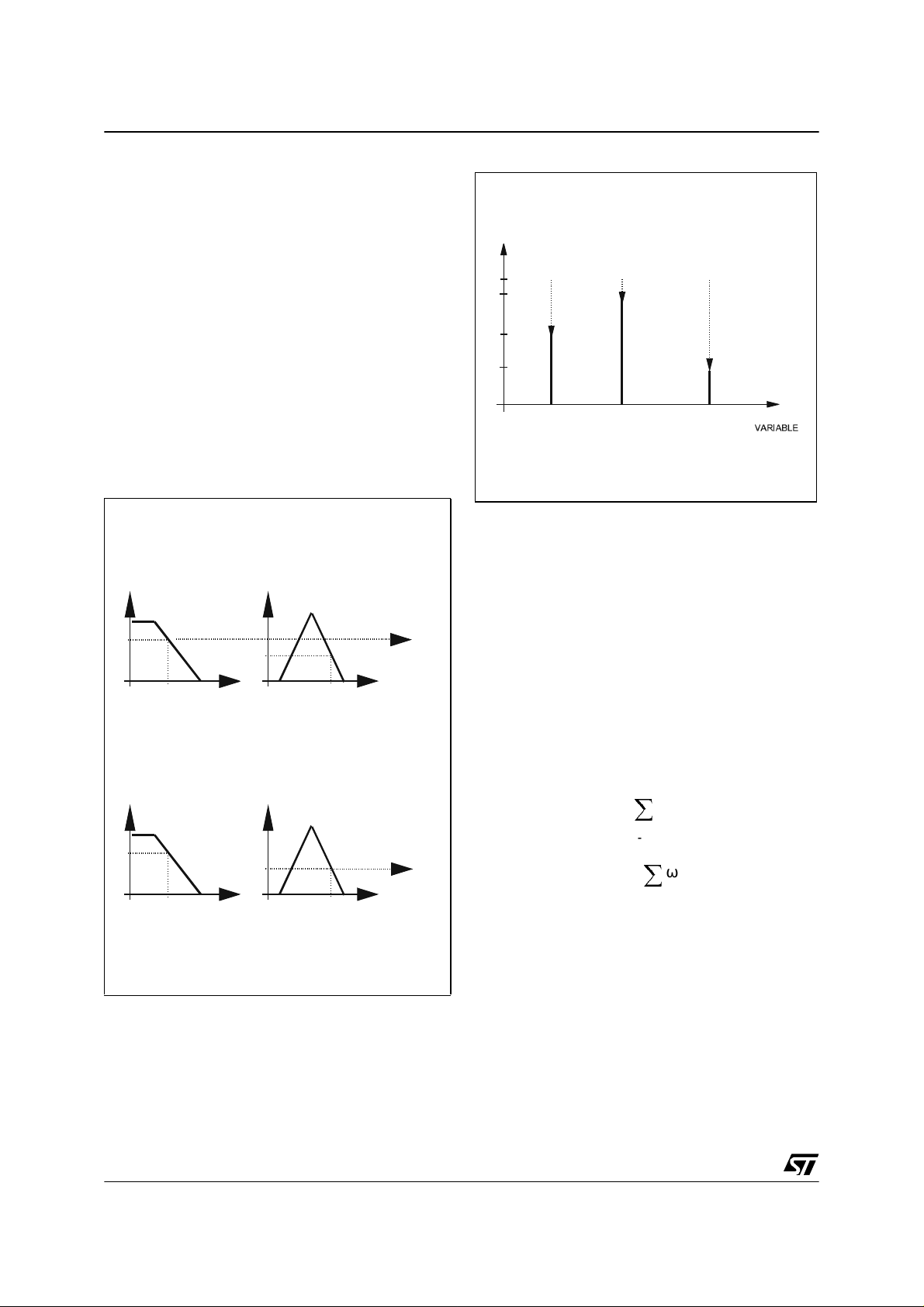

Figure 2.6 Alpha Weight Calculation

1

ij

α

2.3.2 Fuzzyfication Phase.

In this phase the in tersection (alpha weight)

between the input values and the related Mbfs is

performed (Figure 2.6).

8 Fuzzy input regist ers are available for fuzzy

inferences.

After loading the input values by using the LDFR

assembler instruction, the user can start fuzzynference by using the assembler instructionFUZZY.

During fuzzyfication: input data is transformed in

the activation level (alpha weight) ofthe Mbfs. i

j-th Mbf

i-th INPUT VARIABLE

Input Value

Figure 2.7 Fuzzy Inference

FUZZYFICATION

Input Values

11

1m

INFERENCE

n1

nm

PHASE

1

2

DEFUZZYFICATION

N rules -1

Nrules

Output Values

25/94

ST52T400/T440/E440/T441

X

2.3.3 Inference Phase.

The Inference Phase manages the alpha weights

obtained during the fuzzyfication phase to c ompute the truth value (

Ω) for each rule.

This is a calculation of th e maximum (for the OR

operator) and/or minimum (for the AND operator)

performed on alpha values according to the logical

connectives of fuzzy rules.

Several conditions may be linked together by linguistic con nec tive s AND/OR, NOT operator and

brackets.

The truth value ω and the related output singletonmove t o the Defuzzyfication phase in order to

complete the inferenc e calculation.

Figure 2.8 Fuzzyfication

IF

INPUT 1

1

IF

INPUT 1

1

IS X1 OR

X1

IS X1 AND

X1

Input 1

Input 1

INPUT 2

α2

OR = Max

INPUT 2

α2

IS X2 THEN .......

X2

Input 2

IS X2 THEN ......

X2

Input 2

Figure 2.9 Output Membership Functions

i0

j-th Singleton

ij

X

i-th OUTPUT

in

1

ω

ij

ω

i0

ω

in

0

X

2.3.4 Defuzzyfication.

In this phase the output crisp values are determined by implementing the conseq uent part of the

rules.

Each consequent Singleton X

weight values ω

, calculated by the Fuzzy Infer-

i

is multiplied by its

i

ence Unit, in order to compute the upper part of

the defuzzification.

Each output value is deduced from the consequent crisp values (X

) by carrying out the follow-

i

ing defuzzification formula:

where:

N

Xijω

j

N

∑

j

ij

ω

ij

Y

=

i

∑

--------------------- -

i = 0,1 ident ifies t he current output variable

N = number of the active rules on the current output

=weight of th e j-t h singleton

ω

ij

Xij = abscissa of the j-th singleton

Fuzzy outputs are stored in the RAM location i-th

specified in the assembler instruction OUT i.

26/94

ST52T400/T440/E440/T441

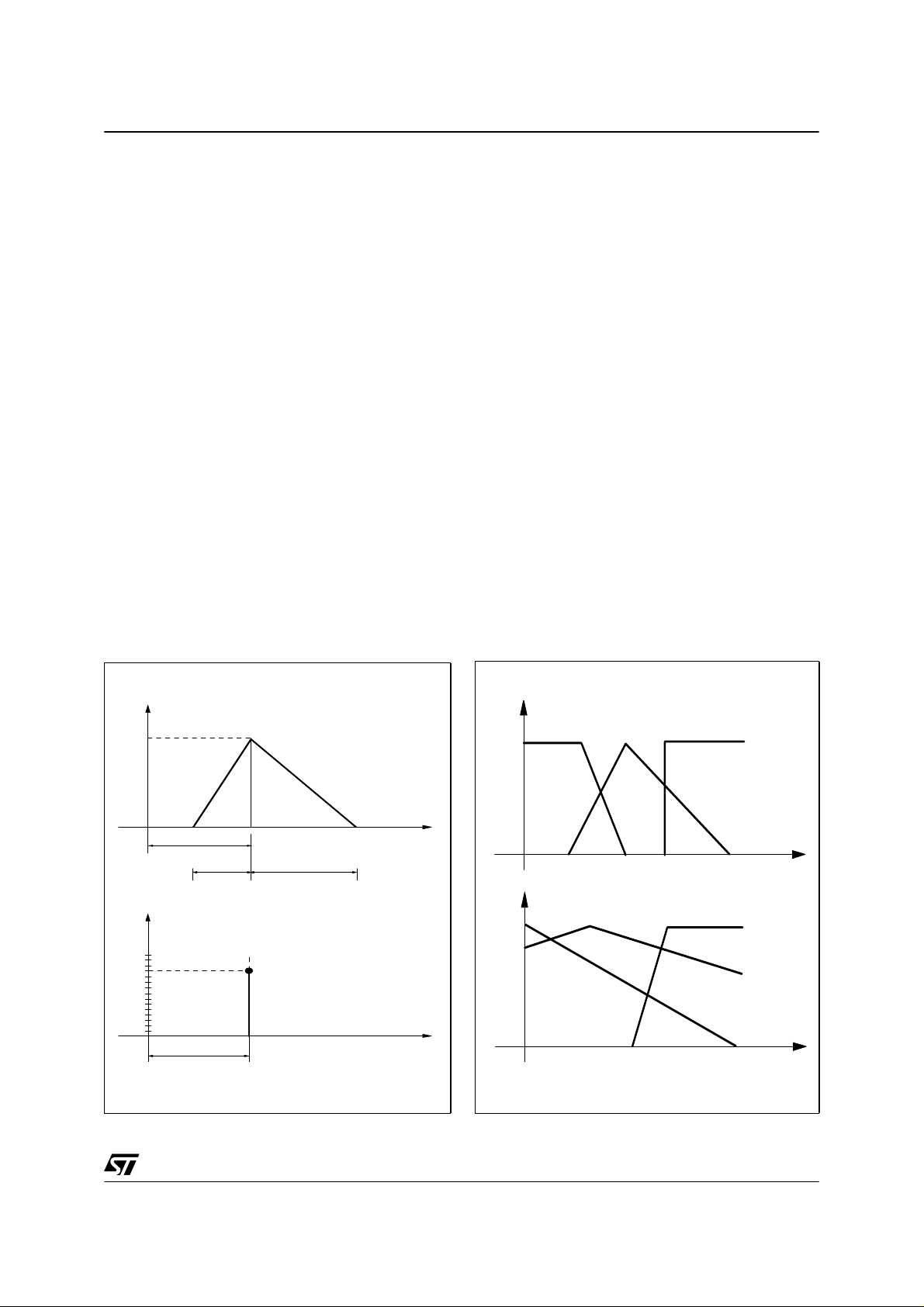

2.3.5 Input Membership Function.

ST FIVE allows the management of triangular

Mbfs. In order to define an Mbf, three different

types of data must be stored on the Program/Data

Memory:

the vertex of the Mbf: V;

the length of the left semi-base: LVD;

the length of the right semi-base: RVD;

In order to reduce the size of the memory area

and the computational effort the v ertical dimension

of the vertex is set to 15 (4 bits).

By using the previous memorization method different kinds of triangular Membership Functions ma y

be stored. Figure 4.6 illustrates a typical example

of Mbfs that c an be defined in ST FIVE.

Each Mbf is then defined storing 3 bytes in the first

1 Kbyte of the programmemory.

The Mbf is memorized by using the following

instruction:

MBF n_mbf lvd v rvd

where

n_mbf identifies Mbf, l v d, v, and rvd, which are the

parameters that describe the Mbf’s shape.

2.3.6 Output Singleton.

ST FIVE uses a particular kind of membership

function called Singleton for its output variables. A

Singleton doesn’t have a shape, like a traditional

Mbf, and is characterized by a single point identified by the coup le (X, w), where the w is calculated by the Inference Unit as described before.

Often, a Singleton is simply identified with its Crisp

Value X.

2.3.7 Fuzzy Rules.

Rules can have the following structures:

if A op B op C...........then Z

if (A op B) op (C op D op E...)...........then Z

where op is one of the possible linguistic operators (AND/OR)

In the first cas e the rule operators are managed

sequentially; in the second one, the priority of the

operator is fixed by the brackets.

Each rule is codified by using an instruction set,

the inference time for a rule with 4 antecedents

and 1 consequent is about 3 microseconds.

Figure 2.10 Mbfs Parameters

15

0

15

w

0

V

LVD R VD

X

Figure 2.11 Example of valid Mbfs

Input M bf

Input V ariable

Output S ingleton

Output Variable

27/94

ST52T400/T440/E440/T441

The assembler Instruction S et, which manages fu zzy instructions is reported in the following table:

Table 2.4 F uz z y Instruction Set

Instruction Description

MBF

n_mbf Ivd v rvd

LDP

nm

Stores the Mbf

Fixes the alpha value of the inputnwith the Mbfmand stores it in internal registers

n_mbf

with the shape identified by the parameters

Ivd,v

and

rvd

nm

LDN

FZAND

FZOR

LDK Stores the result of the last Fuzzy operation executed in internal registers

SKM

LDM Copies the value of register M in the data stack

crisp

CON

OUT

n_out

FUZZY Starts the Fuzzy algorithm

Calculates the complementary alpha value of the inputnwith the Mbfm. and stores the

result in internal registers

Implements the Fuzzy operation AND between the last two values stored in internal

registers

Implements the Fuzzy operation OR between the last two values stored in internal registers

Loads the result of the last performed Fuzzy operation (stored in the temporary register

K) in the temporary buffer M.

Multiplies the

Performs Defuzzyfication and stores the currently Fuzzy output in the RAM

crisp

value with the last ω weight

n_out

location

28/94

ST52T400/T440/E440/T441

Example 1:

IF Input

is codified by the foll owing instructions:

LDN 1 1 calculates the NOT α value of Input

LDP 4 12 fixes the α value of Input

FZAND adds the NO T α and α val ues obtained with the operations LDN1 1 and LDP 4 12

LDK stores th e r es ult of the operation FZAND in internal registers

LDP 3 8 fixes the α value of Input

FZOR implements the operation OR between the results obtained with the operations LDK and

LDP

CON crisp

Example 2, the priority of the operat or is fixed by the b rackets:

IF (Input

LDP 3 fixes the α value of Input3 with Mbf1 and stores the result in internal registers

LDN 4 15 calculates the NOT α value of Input

FZAND adds NOT α and α v alues obtained with the operations LDP 3 1 and LDN 4 15 SKM

LDP 1 6 fixes the α value of Input

LDN 2 14 calculates the NOT α value of Input

FZOR implements the operation OR between the α and NOT α values obtained with the two previ-

LDK stores th e r es ult of the operation OR in internal registers

LDM copies the value of the memory register M in internal registers

FZOR implements t he operation OR between the last two values stored in internal registers (LDK

CON crisp

IS NOT Mbf1AND Input4is Mbf12OR Input3IS Mbf8THEN Crisp

1

with Mbf1and stores the result in internal registers

1

with M12and stores the result in internal registers

4

with Mbf8and stores the result in internal registers

3

multiplies the result of the last Ω operation with the crisp value Crisp

1

IS Mbf1AND Input4IS NOT Mbf15)OR(Input1IS Mbf6OR Input6IS NOT Mbf14)THENCrisp

3

with Mbf15and stores the res ult in internal registers

4

1

1

stores the result of the operation FZAND in internal registers

with Mbf6and stores the result in internal registers

1

with Mbf14and stores the result in internal registers

6

ous operations (LDP 1 6 and LDN 2 14)

and LDM)

multiplies the result of the last Ω operation with the crisp value Crip

2

2

2

At the end of the fuzzy rul e, by using the instruction OUT RAM_reg, a byte is written. Afterwards, the control of the algorithm goes returns to the CU.

29/94

Loading...

Loading...