SGS Thomson Microelectronics ST19SF64 Datasheet

®

2

2

2

2

■

8 BIT ARCHITECTURE CPU

■

32 KBytes of USER ROM WITH

PARTITIONING

■

SYST EM ROM FO R L IBRAR I ES

■

960 Bytes of RAM WITH PARTITIONING

■

64 KBytes of EEPROM WITH PARTITIONING

– Highly reliable CMOS EEPROM technology

– 10 year data retention

– 100,000 Erase/Write cycle endurance

– Separate Write and Erase cycles for fast “1”

programming

– 1 to 64 bytes Erase or Program in 1 ms

■

SECURITY FIREWALLS FOR MEMORIES

■

VERY HIGH SECURITY FEATURES

INCLUDING EEPROM FLASH PROGRAM

AND RAM FLASH CLEAR

■

8 BIT TIMER

■

SERIAL ACCESS, ISO 7816-3 COMPATIBLE

■

3V ± 10% or 5V ± 10% SUPPLY VOLTAGE

■

POWER SAVING STANDBY MODE

■

UP TO 10 MHz INTERNAL OPERATING

FREQUENCY

■

CONTACT ASSIGNMENT COMPATIBLE ISO

7816-2

■

ESD PROTECTION GREATER THAN 5000V

ST19SF64

Smar tcard MCU

With 64 KBytes EEPROM

DATA BRIEFING

Micromodule (D4)

Wafer

*CRT: Chinese Remainder Theorem

BD.SF64/9809VP3

This is Brief Data from STMicroelectronics. Details are subject to change without notice. For complete data, please contact

your nearest Sales Office or SmartCard Products Divison, Rousset, France. Fax: (+33) 4 42 25 87 29

1/2

ST19SF64

HARDWARE DESCRIPTION

The ST19SF64, a member of the ST19 device

family, is a serial access microcontroller especially

designed for very large volume and cost competitive secure portable objects.

The ST19SF64 is based on a S TMicroelectronics

8 bit CPU core including on-chip memories: 960

Bytes of RAM, 32 KBytes of USER ROM and 64 K

Bytes of EEPROM.

RAM, ROM and EEPROM m em ories can be configured into partitions. Access rules from any

memory partition to another partition are s etup by

the user defined Memory Access Control Logic.

It is manufactured using the highly reliable ST submicron technology.

As all o ther ST19 f am ily m emb ers, it is fully com patible with the ISO standards for Smartcard applications.

SOFTWARE DEVELOPMENT

Software development and firmware (ROM code/

options) generation are completed by the ST16-19

HDS development system.

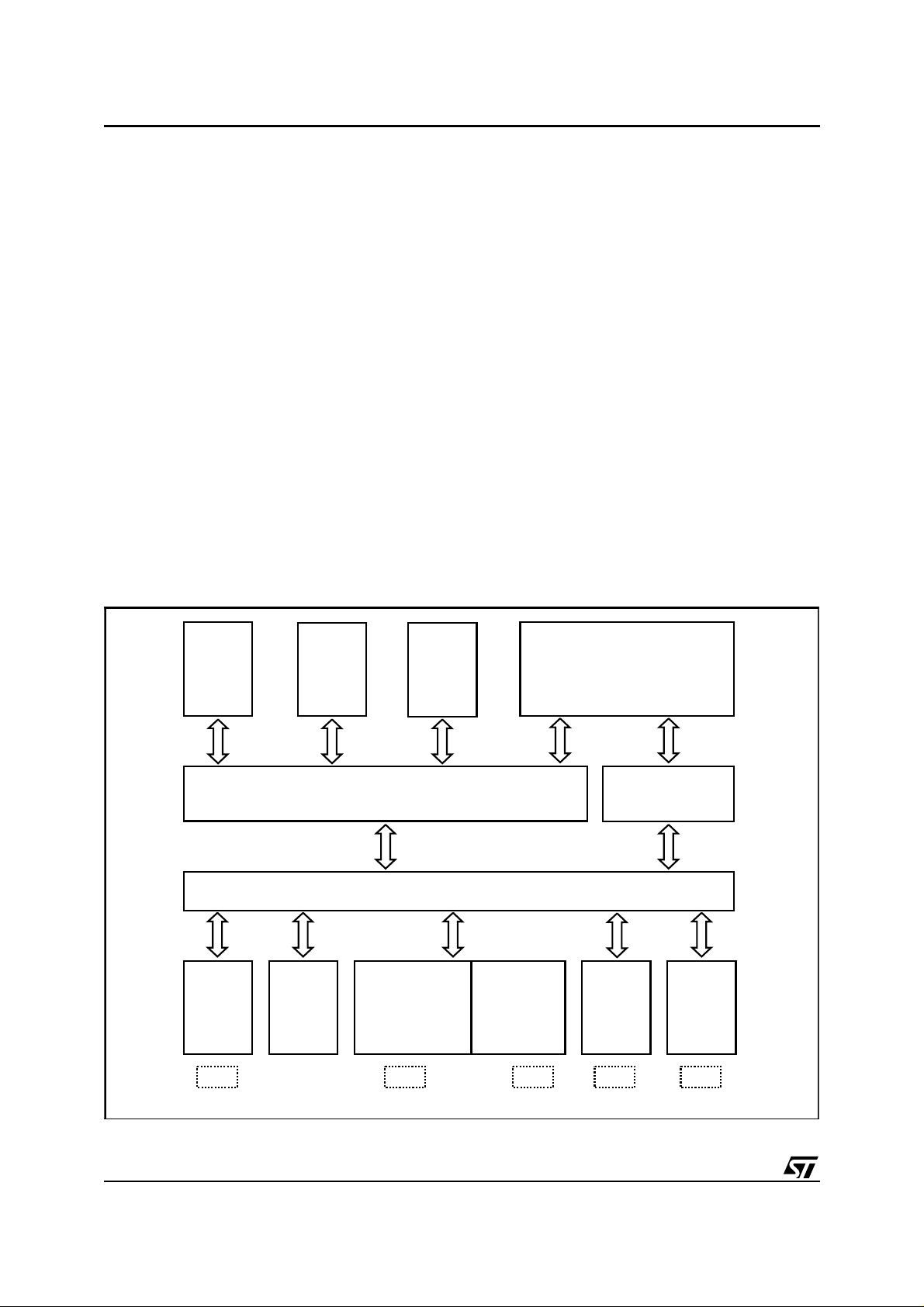

Figure 1. Bloc k D ia gram

RAM EEPROM

960

Bytes

CLOCK

GENERATOR

MODULE

USER

64 K

Bytes

MEMORY ACCESS FIREWALL

8 BIT

TIMER

SECURITY

ADMINISTRATOR

ROM

32 K

Bytes

INTERNAL BUS

UNPREDICTABLE

NUMBER

GENERATOR

SYSTEM ROM

SYSTEM ROM

FIREWALL

8 BIT

CPU

SERIAL

I/O

INTERFACE

2/2

CLK

RESET

I/OGNDVcc

SCP 101b/DS

Loading...

Loading...