SGS Thomson Microelectronics ST10F269 Datasheet

ST10F269

16-BIT MCU WITH MAC UNIT, 256K BYTE FLASH MEMORY AND 12K BYTE RAM

PRELIMINARY DATA

■

HIGH PERFORMANCE 40MHz CPU WITH DSP

FUNCTION

– 16-BIT CPU WITH 4-STAGE PIPELINE

– 50ns INSTRUCTION CYCLE TIME AT 40MHz MAX

CPU CLO CK

– MULTIPLY/ACCUMULATE UNIT (MAC) 16 x 16-BIT

MULTIPLICATION, 40-BIT ACCUMULATOR

– REPEAT UNIT

– ENHANCED BOOLEAN BIT MANIPU LATION FA-

CILITIE S

– ADDITIONAL IN STRUCTIONS TO SUPPORT HLL

■

AND OPERATING SYSTEMS

– SINGLE-CYCLE CONTEXT SWITCHING SUP-

PORT

■

MEMORY ORGANIZATION

– 256K BYTE ON-CHIP FLASH MEMORY SINGLE

VOLTAG E WITH E RASE/ PROG RAM CONTR OL LER.

– 100K ERASING/PROGRAMMING CYCLES.

– UP TO 16M BYTE LINEA R ADDRE SS SPACE FO R

CODE AN D DATA (5M BYTES WI TH CAN)

– 2K BY TE ON-CHIP INTERNAL RAM (IRAM)

– 10K BYTE ON-CHIP EXTENSION RAM (XRAM)

■

FAST AND FLEXIBLE BUS

– PROG RAMMABLE EXTERNAL BUS CHARACTE-

RISTICS FOR DIFFERENT ADDRESS RANGES

– 8-BIT OR 16-BIT EXTERNAL DATA BUS

– MULTIPLEXED OR DEMULTIPLEXED EXTERNAL

ADDRESS/DATA BUSES

– FIVE PROGRAMMABLE CHIP-SELECT SIGNALS

– HOLD-ACK NOW LEDGE BUS AR BITRATION SUP-

PORT

■

INTERRUPT

TWO CAN 2.0B INTERFACES OPERATING ON ONE

OR TWO CAN BUSSES (30 OR 2x15 MESSAGE

OBJECTS)

■

FAIL-SAFE PROTECTION

– PROGRAMMABLE WATCHDOG TIMER

– OSCILLATOR WATCHDOG

■

ON-CHIP BOOTST RAP LOADER

■

CLOCK GENERATION

– ON-CHIP PLL

– DIRECT OR PRESCALED CLOCK INPUT

■

REAL TIME CLO CK

■

UP TO 111 GENERAL PURPOSE I/O LINES

– INDIVIDUALLY PROGRAMMABLE AS INPUT,

OUTPUT OR SPECIAL FUNCTION

– PROGRAMMABLE THRESHOLD (HYSTERESIS)

■

IDLE AND POWER DOWN MODES

■

SINGLE VOLTAGE SUPPLY: 5V ±10% (EMBEDDED

REGULATOR FOR 3.3 V CORE SUPPLY).

■

TEMPERATURE RANGE: -40 +125°C

■

144-PIN PQFP PACKAGE

– 8-CHANNEL PERIPHERAL EVENT CONTROLLER

FOR SINGLE CYCLE INTERRUPT DRIVEN DATA

TRANSFER

– 16-PRIORITY-LEVEL INTERRUPT SY STEM WITH

Flash Memory

56 SOURCES, SAMPLING RATE DOWN TO 25ns

■

TIMERS

– TWO MULTI-FUNCTIONAL GENERAL PURPOSE

TIMER UNITS WI TH 5 TIMERS

■

TWO 16- CHANNEL CAPTU RE / COMPARE UNITS

■

A/D CONVERTER

CAN1_RXD

CAN1_TXD

CAN2_RXD

CAN2_TXD

10K Byte

XRAM

– 16-CHANNEL 10-BIT

µ

s CONVERSION TIME AT 40MHz CPU CLOCK

– 4.85

■

4-CHANNEL PWM UNIT

■

SERIAL CHANNELS

– SYNC HRONOUS / ASYN CHRONOUS SERIAL

CHANNEL

– HIGH-SPEED SYNCHRONOUS CHANNEL

June 2002

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

PQFP144 (28 x 28 mm)

(Plastic Quad Flat Pack)

ORDE R CODE:

256K Byte

CAN1

CAN2

16

16

8

32

16

Port 0

Port 1Por t 4

Controller

10-Bit ADC

External Bus

Port 6 Port 5 Port 3

8

16 15

ST10F 269-Q3

CPU-Core and MAC Unit

Interrupt Controller

GPT1

ASC usart

BRG

GPT2

BRG

PEC

SSC

PWM

Port 7 Port 8

16

2K Byte

16

Internal

RAM

Watchdog

Oscillator

and PLL

XTAL1 XTAL2

16

Voltage

3.3V

Regulator

Port 2

CAPCOM2

CAPCOM1

16

8

8

1/160

ST10F269

TABLE OF CONTENTS PAGE

1 - INTRODUCTION .................. ................. ........................ ................ ........................ ..... 6

2 - PIN DATA ................................................................................................................... 7

3 - FUNCTIONAL DESCRIPTION ................ ................. ................ .......... ................ ........ 13

4 - MEMORY ORGANIZATION ....................................................................................... 14

5 - INTERNAL FLASH MEMORY .... .......... ................ ................. ......... ................. .......... 17

5.1 - OVERVIEW ................................................................................................................ 17

5.2 - OPERATIONAL OVERVIEW ...................................................................................... 17

5.3 - ARCHITECTURAL DESCRIPTION ............................................................................ 19

5.3.1 - Read Mode ................................................................................................................. 19

5.3.2 - Command Mode ......................................................................................................... 19

5.3.3 - Ready/Busy Signal ..................................................................................................... 19

5.3.4 - Flash Status Register ................................................................................................. 19

5.3.5 - Flash Protection Register ........................................................................................... 21

5.3.6 - Instructions Description .............................................................................................. 21

5.3.7 - Reset Processing and Initial State .............................................................................. 25

5.4 - FLASH MEMORY CONFIGURATION ........................................................................ 25

5.5 - APPLICATION EXAMPLES ....................................................................................... 25

5.5.1 - Handling of Flash Addresses . ..................................................................................... 25

5.5.2 - Basic Flash Access Control ........................................................................................ 26

5.5.3 - Programming Examples ............................................................................................. 27

5.6 - BOOTSTRAP LOADER ............................................................................................ 30

5.6.1 - Entering the Bootstrap Loader .................................................................................... 30

5.6.2 - Memory Configuration After Reset ............................................................................. 31

5.6.3 - Loading the Startup Code ........................................................................................... 32

5.6.4 - Exiting Bootstrap Loader Mode .................................................................................. 32

5.6.5 - Choosing the Baud Rate for the BSL ......................................................................... 33

6 - CENTRAL PROCESSING UNIT (CPU) ..................................................................... 34

6.1 - MULTIPLIER-ACCUMULATOR UNIT (MAC) ............................................................. 35

6.1.1 - Features ..................................................................................................................... 36

6.1.1.1 - Enhanced Addressing Capab ilit ies.............................................................................. 36

6.1.1.2 - Multiply-Accumulate Unit............................................................................................. 36

6.1.1.3 - Program Control........................... ................. ........................ ................ ...................... 36

6.2 - INSTRUCTION SET SUMMARY ................................................................................ 37

6.3 - MAC COPROCESSOR SPECIFIC INSTRUCTIONS ................................................. 38

7 - EXTERNAL BUS CONTROLLER ............................ ......... ................. ................ ........ 42

7.1 - PROGRAMMABLE CHIP SELECT TIMING CONTROL ............................................ 42

7.2 - READY PROGRAMMABLE POLARITY ..................................................................... 42

2/160

ST10F269

TABLE OF CONTENTS PAGE

8 - INTERRUPT SYSTEM ....................... ........................ ................. ....................... ........ 44

8.1 - EXTERNAL INTERRUPTS ......................................................................................... 44

8.2 - INTERRUPT REGISTERS AND VECTORS LOCATION LIST .................................. 45

8.3 - INTERRUPT CONTROL REGISTERS ....................................................................... 46

8.4 - EXCEPTION AND ERROR TRAPS LIST ................................................................... 47

9 - CAPTURE/COMPARE (CAPCOM) UNITS ................................................................ 48

10 - GENERAL PURPOSE TIMER UNIT .......................................................................... 51

10.1 - GPT1 .......................................................................................................................... 51

10.2 - GPT2 .......................................................................................................................... 52

11 - PWM MODULE ...... .......... ....................... ................. ....................... ................. .......... 54

12 - PARALLEL PORTS ...... ................. ................ ........................ ................. ................... 55

12.1 - INTRODUCTION ........................................................................................................ 55

12.2 - I/O’S SPECIAL FEATURES ....................................................................................... 57

12.2.1 - Open Drain Mode ....................................................................................................... 57

12.2.2 - Input Threshold Control ............................................................................................ 57

12.2.3 - Output Driver Control ................................................................................................58

12.2.4 - Alternate Port Functions ............................................................................................. 60

12.3 - PORT0 ........................................................................................................................ 61

12.3.1 - Alternate Functions of PORT0 .................................................................................... 62

12.4 - PORT1 ........................................................................................................................ 64

12.4.1 - Alternate Functions of PORT1 .................................................................................... 64

12.5 - PORT 2 ....................................................................................................................... 66

12.5.1 - Alternate Functions of Port 2 ...................................................................................... 66

12.6 - PORT 3 ....................................................................................................................... 69

12.6.1 - Alternate Functions of Port 3 ...................................................................................... 70

12.7 - PORT 4 ....................................................................................................................... 73

12.7.1 - Alternate Functions of Port 4 ...................................................................................... 74

12.8 - PORT 5 ....................................................................................................................... 77

12.8.1 - Alternate Functions of Port 5 ...................................................................................... 78

12.8.2 - Port 5 Schmitt Trigger Analog Inputs .......................................................................... 79

12.9 - PORT 6 ....................................................................................................................... 79

12.9.1 - Alternate Functions of Port 6 ...................................................................................... 80

12.10 - PORT 7 .......... ................ ................. ....................... ................. ........................ ............ 83

12.10.1 - Alternate Functions of Port 7 ...................................................................................... 84

12.11 - PORT 8 .......... ................ ................. ....................... ................. ........................ ............ 87

12.11.1 - Alternate Functions of Port 8 ...................................................................................... 88

3/160

ST10F269

TABLE OF CONTENTS PAGE

13 - A/D CONVERTER .......................... ....................... ................. ........................ ............ 90

14 - SERIAL CHANNELS ......................... ................. ........................ ................ ............... 91

14.1 - ASYNCHRONOUS / SYNCHRONOUS SERIAL INTERFACE (ASCO) .................... 91

14.1.1 - ASCO in Asynchronous Mode .................................................................................... 91

14.1.2 - ASCO in Synchronous Mode ...................................................................................... 93

14.2 - HIGH SPEED SYNCHRONOUS SERIAL CHANNEL (SSC) ......................... ......... ... 95

15 - CAN MODULES ............................. ................ ................. ........................ ................ ... 97

15.1 - CAN MODULES MEMORY MAPPING ...................................................................... 97

15.1.1 - CAN1 .......................................................................................................................... 97

15.1.2 - CAN2 .......................................................................................................................... 97

15.2 - CAN BUS CONFIGURATIONS .................................................................................. 97

16 - REAL TIME CLOCK .................................................................................................. 99

16.1 - RTC REGISTERS ...................................................................................................... 100

16.1.1 - RTCCON: RTC Control Register ................................................................................ 100

16.1.2 - RTCPH & RTCPL: RTC PRESCALER Registers ....................................................... 101

16.1.3 - RTCDH & RTCDL: RTC DIVIDER Counters .............................................................. 101

16.1.4 - RTCH & RTCL: RTC Programmable COUNTER Registers ....................................... 102

16.1.5 - RTCAH & RTCAL: RTC ALARM Registers ................................................................ 103

16.2 - PROGRAMMING THE RTC ....................................................................................... 103

17 - WATCHDOG TIMER ............ .......... ................ ........................ ................. ................ ... 105

18 - SYSTEM RESET ........................................................................................................ 107

18.1 - LONG HARDWARE RESET ...................................................................................... 107

18.1.1 - Asynchronous Reset .................................................................................................. 107

18.1.2 - Synchronous Reset (RSTIN pulse > 1040TCL and RPD pin at high level) ................ 108

18.1.3 - Exit of Long Hardware Reset ...................................................................................... 109

18.2 - SHORT HARDWARE RESET .................................................................................... 109

18.3 - SOFTWARE RESET .................................................................................................. 110

18.4 - WATCHDOG TIMER RESET ..................................................................................... 110

18.5 - RSTOUT, RSTIN, BIDIRECTIONAL RESET ............................................................ 111

18.5.1 - RSTOUT Pin ............................................................................................................... 111

18.5.2 - Bidirectional Reset ...................................................................................................... 111

18.5.3 - RSTIN pin ................................................................................................................... 111

18.6 - RESET CIRCUITRY ................................................................................................... 111

19 - POWER REDUCTION MODES ................................................................................. 114

19.1 - IDLE MODE ................................................................................................................114

19.2 - POWER DOWN MODE .............................................................................................. 114

19.2.1 - Protected Power Down Mode ..................................................................................... 114

19.2.2 - Interruptable Power Down Mode ................................................................................ 114

4/160

ST10F269

TABLE OF CONTENTS PAGE

20 - SPECIAL FUNCTION REGISTER OVERVIEW ......................................................... 117

20.1 - IDENTIFICATION REGISTERS ................................................................................. 123

20.2 - SYSTEM CONFIGURATION REGISTERS ................................................................ 124

21 - ELECTRICAL CHARACTERISTICS ......................... .......... ................ ................. ..... 131

21.1 - ABSOLUTE MAXIMUM RATINGS ............................................................................. 131

21.2 - PARAMETER INTERPRETATION ............................................................................. 131

21.3 - DC CHARACTERISTICS ........................................................................................... 131

21.3.1 - A/D Converter Characteristics .................................................................................... 134

21.3.2 - Conversion Timing Control ....................................................................................... 135

21.4 - AC CHARACTERISTICS ............................................................................................ 136

21.4.1 - Test Waveforms .......................................................................................................136

21.4.2 - Definition of Internal Timing ........................................................................................ 136

21.4.3 - Clock Generation Modes ............................................................................................ 137

21.4.4 - Prescaler Operation ....................................................................................................138

21.4.5 - Direct Drive ................................................................................................................. 138

21.4.6 - Oscillator Watchdog (OWD) ....................................................................................... 138

21.4.7 - Phase Locked Loop .................................................................................................... 1 38

21.4.8 - External Clock Drive XTAL1 ....................................................................................... 139

21.4.9 - Memory Cycle Variables ............................................................................................. 140

21.4.10 - Multiplexed Bus .......................................................................................................... 141

21.4.11 - Demultiplexed Bus ...................................................................................................... 147

21.4.12 - CLKOUT and READY ................................................................................................. 153

21.4.13 - External Bus Arbitration ..............................................................................................155

21.4.14 - High-Speed Synchronous Serial Interface (SSC) Timing ........................................... 157

21.4.14.1 Master Mode................................................................................................................ 157

21.4.14.2 Slave mode.................................................................................................................. 158

22 - PACKAGE MECHANICAL DATA ........... ......... ................. ......... ................. ............ 159

23 - ORDERING INFORMATION ...................................................................................... 159

5/160

ST10F269

1 - INTRODUCTION

The ST10F269 is a derivative of the

STMicroelectronics ST10 family of 16-bit

single-chip CMOS microcontrollers. It combines

high CPU performance (up to 20 million

instructions per second) with high peripheral

functionality and enhanced I/O-capabilities. It also

provides on-chip high-speed single voltage Flash

memory, on-chip high-speed RAM, and clock

generation via PLL.

ST10F269 is processed in 0.35µm CMOS

technology. The MCU core and the logic is

supplied with a 5V to 3.3V on chip voltage

regulator. The part is supplied with a single 5V

supply and I/Os work at 5V.

The device is upward compatible with the

ST10F168 device, with the following set of

differences:

– The Multiply/Accumulate unit is available as

standard. This MAC unit adds powerful DSP

functions to the ST10 architecture, but maintains

full compatibility for existing code.

– Flash control interface is now based on

STMicroelectronics third generation of

stand-alone Flash memories, with an embedded

Erase/Program Controller. This completely

frees up the CPU during programming or

erasing the Flash.

– Two dedicated pins (DC1 and DC2) on the

PQFP-144 package are used for decoupling the

internally generated 3.3V core logic supply.

Do

not connect these two pins to 5.0V exter nal

supply.

Instead, these pins should be

connected to a decoupling capacitor (ceramic

type, value ≥ 330 nF).

– The A/D Converter characteristics are different

from previous ST10 derivatives ones. Refer to

Section 21.3.1 - A/D Converter Characteristics.

– The AC and DC pa rameters are adapt ed to the

40MHz maximum CPU frequency. The

characterization is performed with C

= 50pF

L

max on output pins. Ref er to Section 21.3 DC

Characteristics.

– In order to reduce EMC, the rise/fall time and the

sink/source capability of the drivers of the I/O

pads are programmable. Refer to Section 12.2 I/

O’s Special Features.

– The Real Time Clock functionnality is added.

– The external interrupt sources can be selected

with the EXISEL register.

– The reset source is identified by a dedicated

status bit in the WDTCON register.

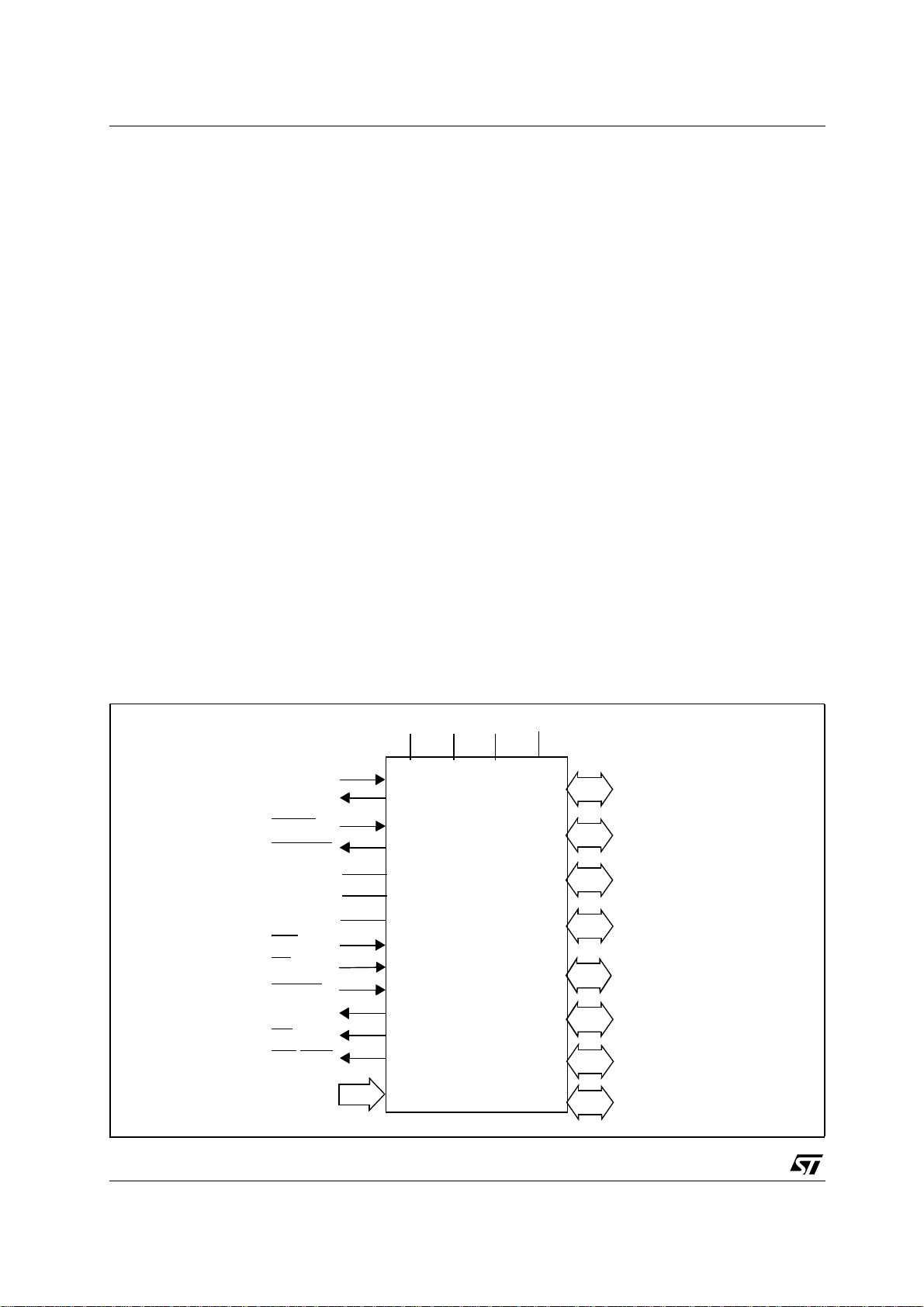

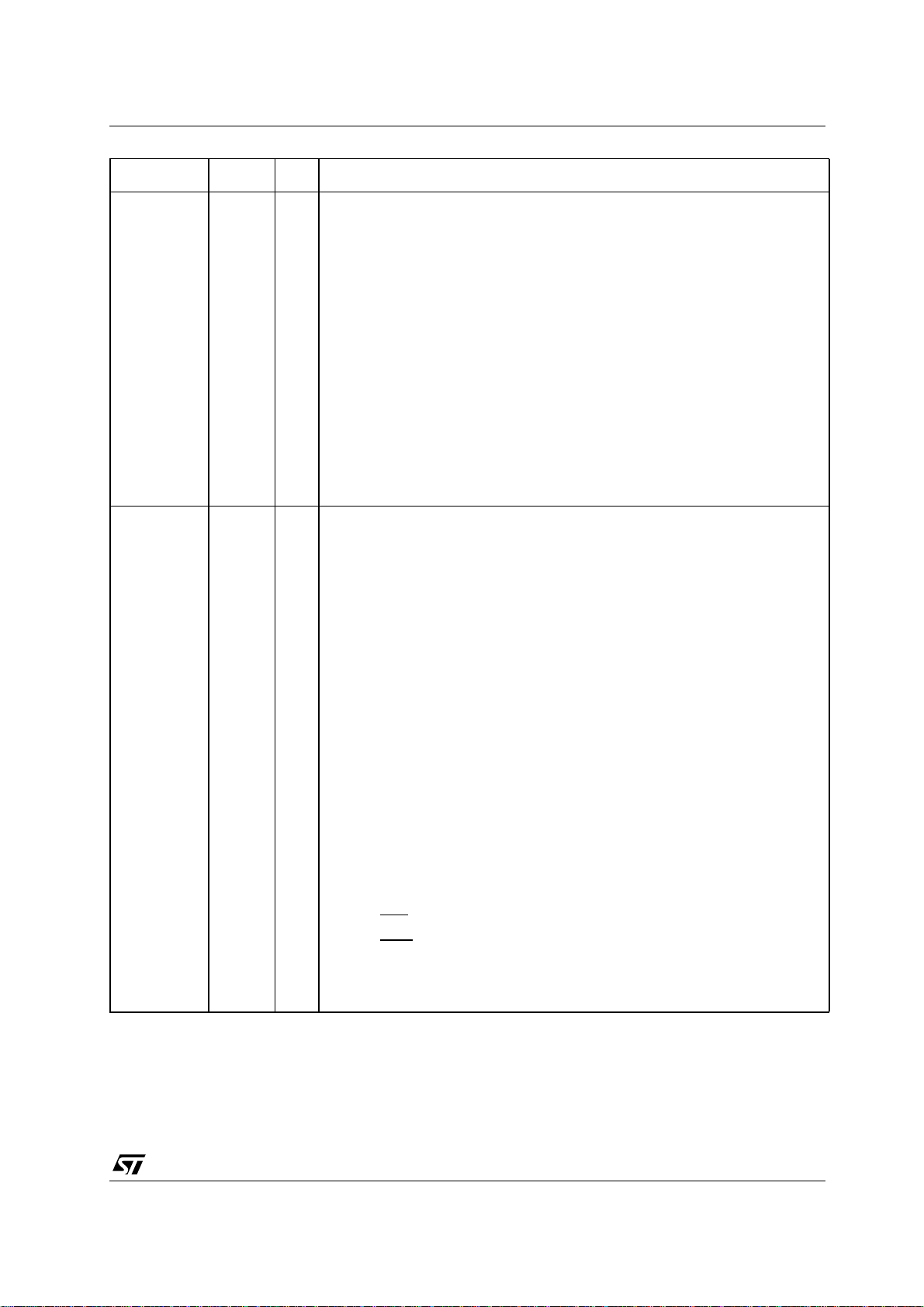

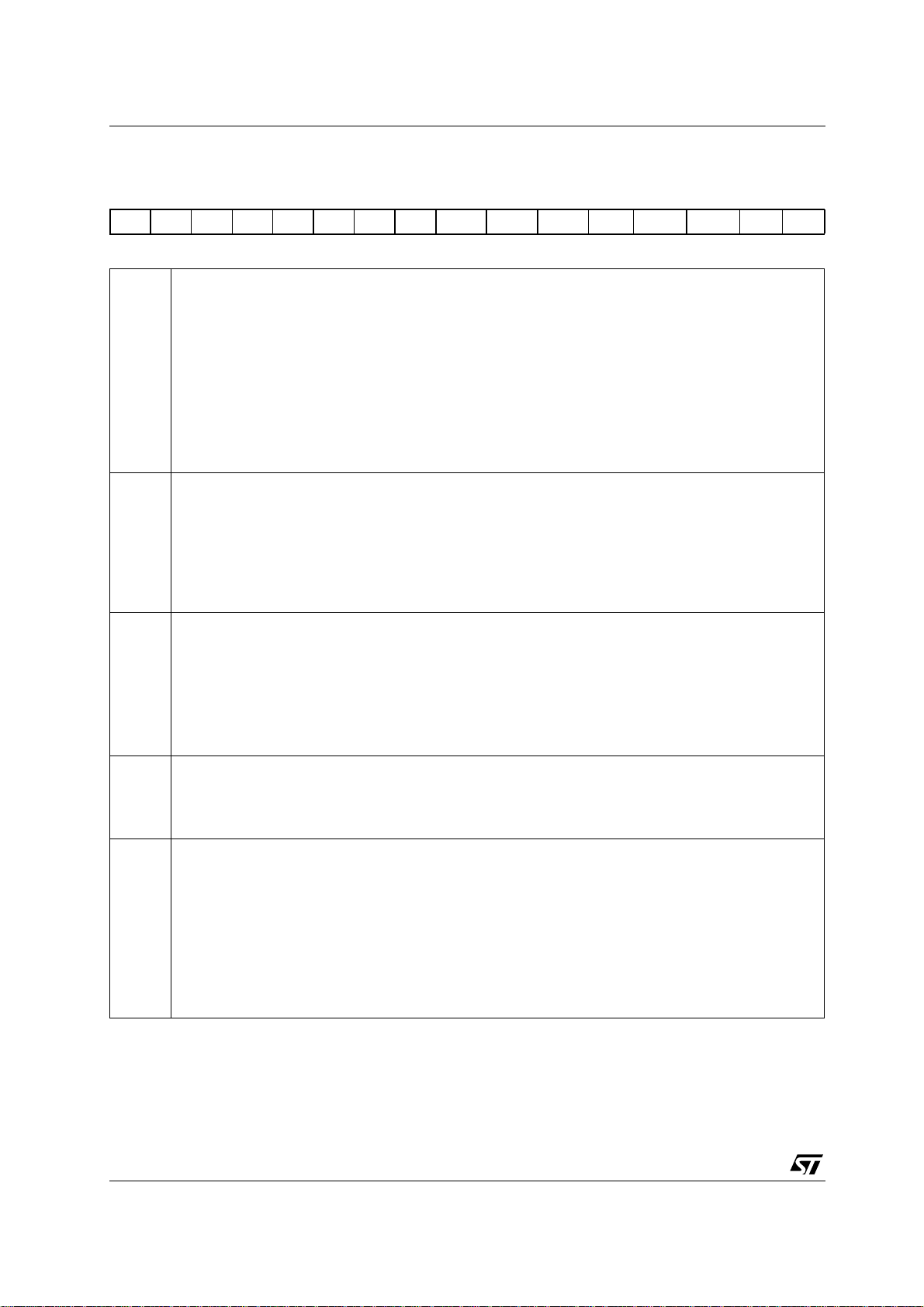

Figure 1 :

Logic Symbol

XTAL1

XTAL2

RSTIN

RSTOUT

RPD

V

AREF

V

AGND

NMI

EA

READY

ALE

RD

WR/WRL

Port 5

16-bit

V

DD

DC1 DC2

ST10F269

V

SS

Port 0

16-bit

Port 1

16-bit

Port 2

16-bit

Port 3

15-bit

Port 4

8-bit

Port 6

8-bit

Port 7

8-bit

Port 8

8-bit

6/160

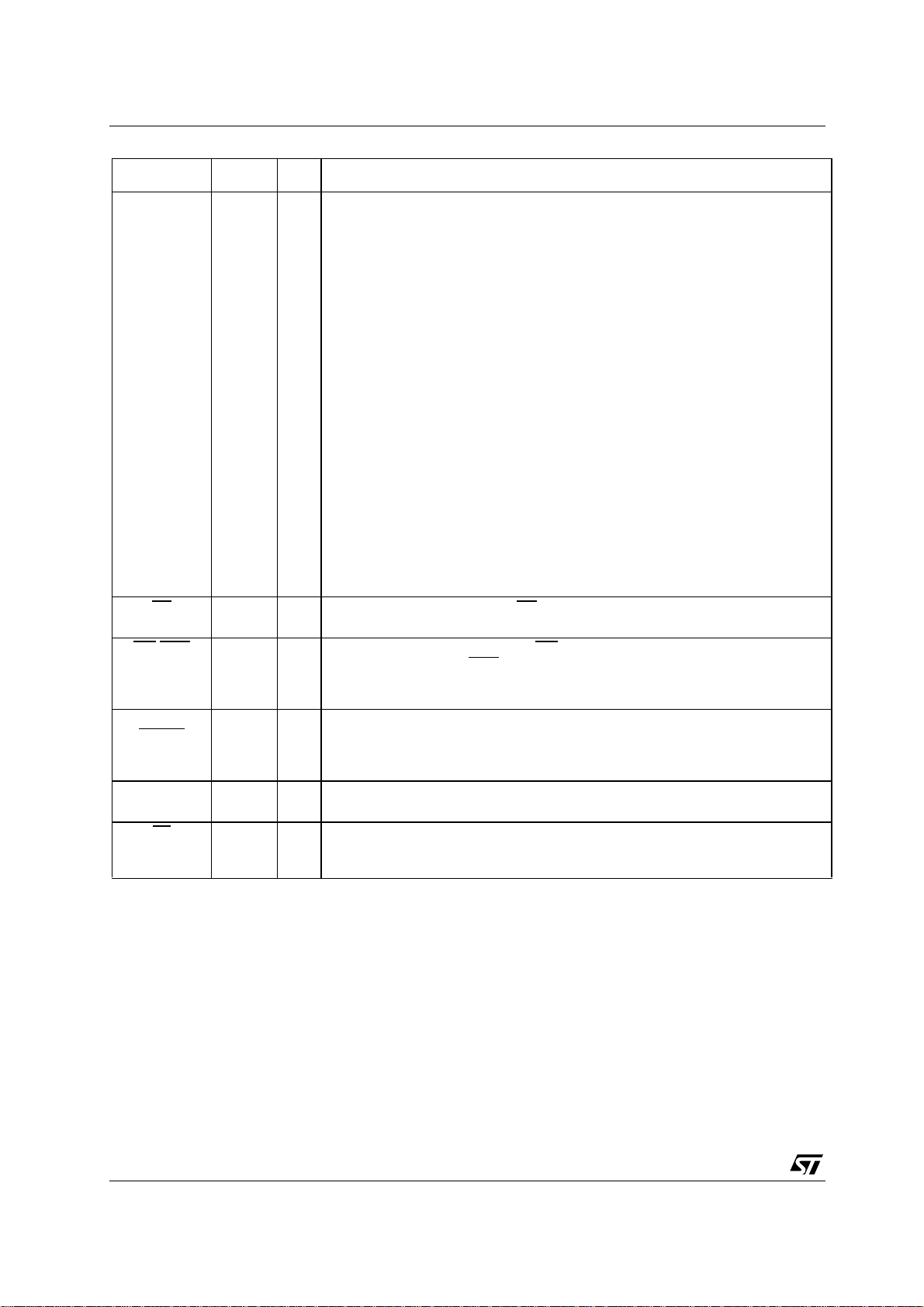

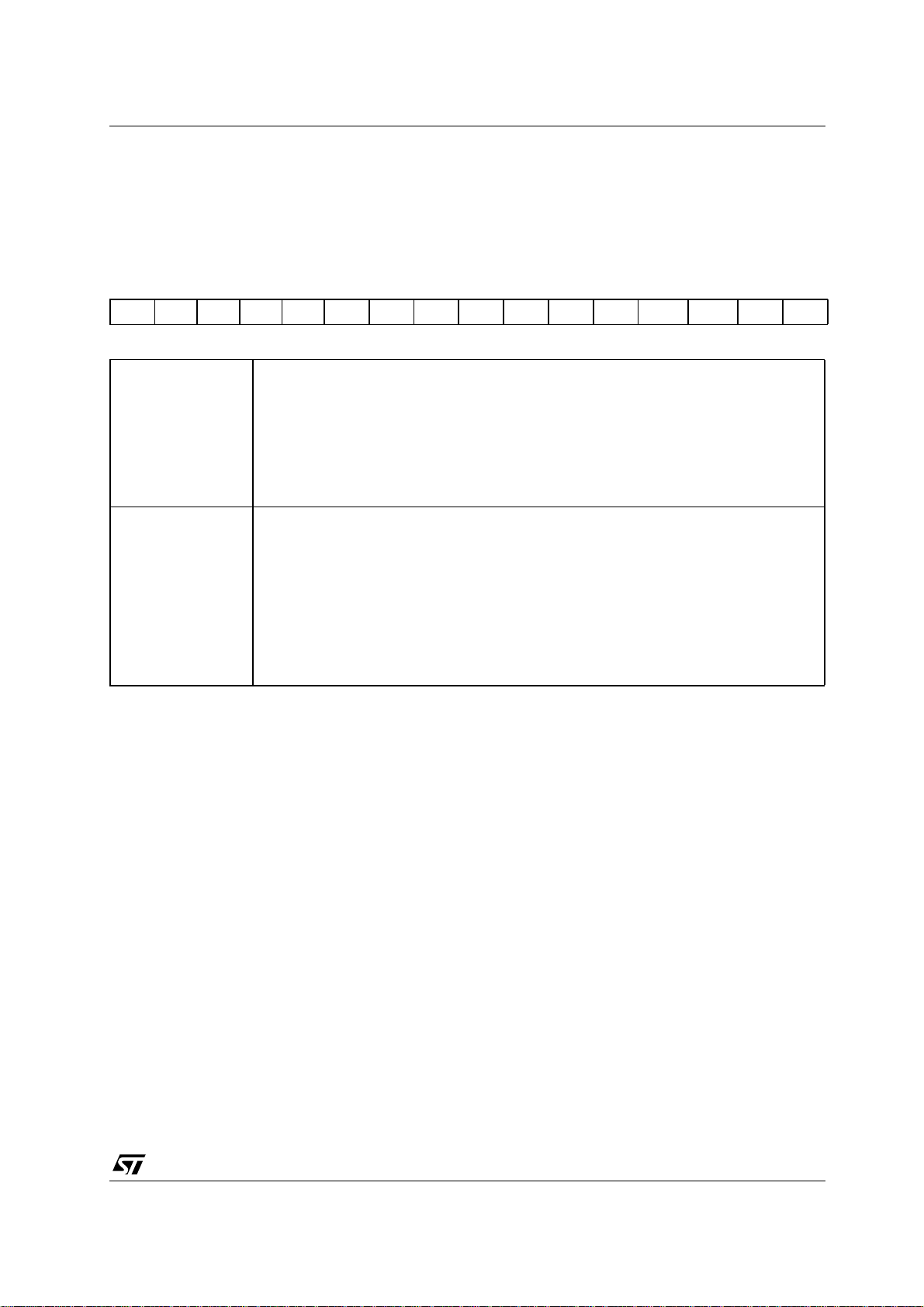

2 - PIN DATA

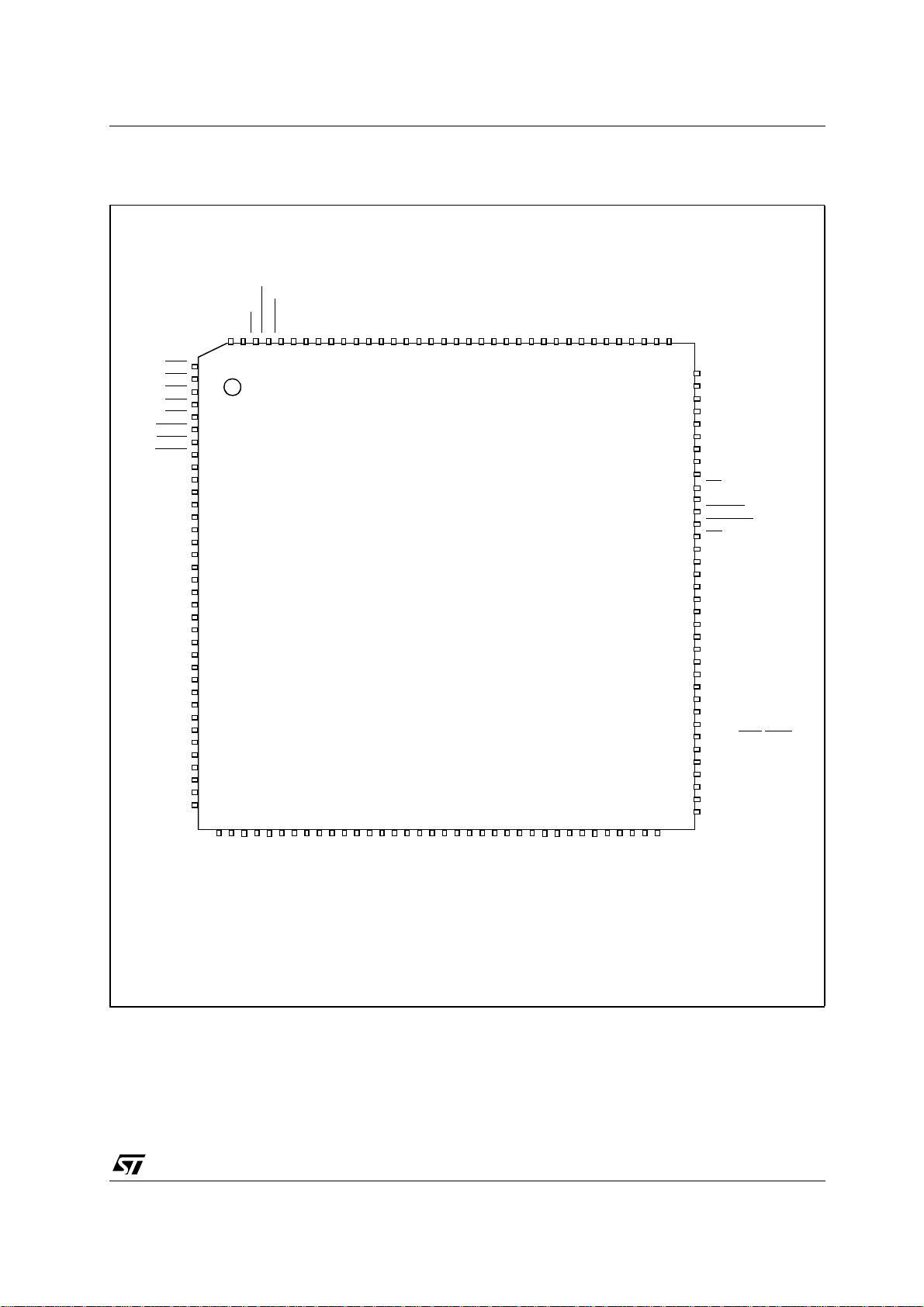

Figure 2 :

Pin Configuration (top view)

ST10F269

P6.0/CS0

P6.1/CS1

P6.2/CS2

P6.3/CS3

P6.4/CS4

P6.5/HOLD

P6.6/HLDA

P6.7/BREQ

P8.0/CC16IO

P8.1/CC17IO

P8.2/CC18IO

P8.3/CC19IO

P8.4/CC20IO

P8.5/CC21IO

P8.6/CC22IO

P8.7/CC23IO

DC2

V

P7.0/POUT0

P7.1/POUT1

P7.2/POUT2

P7.3/POUT3

P7.4/CC28I0

P7.5/CC29I0

P7.6/CC30I0

P7.7/CC31I0

P5.0/AN0

P5.1/AN1

P5.2/AN2

P5.3/AN3

P5.4/AN4

P5.5/AN5

P5.6/AN6

P5.7/AN7

P5.8/AN8

P5.9/AN9

VSSNMI

1

2

3

VDDRSTOUT

144

RSTIN

VSSXTAL1

XTAL2

VDDP1H.7/A15/CC27IO

P1H.6/A14/CC26IO

P1H.5/A13/CC25IO

P1H.4/A12/CC24IO

P1H.3/A11

P1H.2/A10

P1H.1/A9

P1H.0/A8

VSSVDDP1L.7/A7

P1L.6/A6

P1L.5/A5

P1L.4/A4

P1L.3/A3

P1L.2/A2

P1L.1/A1

P1L.0/A0

P0H.7/AD15

P0H.6/AD14

P0H.5/AD13

P0H.4/AD12

P0H.3/AD11

141

143

142

137

140

139

138

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

136

135

113

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

SS

19

20

21

22

ST10F269-Q3

23

24

25

26

27

28

29

30

31

32

33

34

35

36

3738394041424344454647484950515253545556575859606162636465666768697071

P0H.2/AD10

112

DD

P0H.1/AD9

VSSV

111

110

109

P0H.0/AD8

108

P0L.7/AD7

107

P0L.6/AD6

106

P0L.5/AD5

105

P0L.4/AD4

104

P0L.3/AD3

103

102

P0L.2AD2

101

P0L.A/AD1

100

P0L.0/AD0

EA

99

ALE

98

READY

97

96

WR/WRL

95

RD

94

V

SS

93

V

DD

92

P4.7A23/CAN2_TxD

91

P4.6A22/CAN1_TxD

90

P4.5A21/CAN1_RxD

89

P4.4A20/CAN2_RxD

88

P4.3/A19

87

P4.2/A18

86

P4.1/A17

85

P4.0/A16

RPD

84

V

83

SS

82

V

DD

81

P3.15/CLKOUT

80

P3.13/SCLK

72

79

78

77

76

75

74

73

P3.12/BHE

P3.11/RXD0

P3.10/TXD0

P3.9/MTSR

P3.8/MRST

P3.7/T2IN

P3.6/T3IN

/WRH

SS

DD

V

AREF

AGND

V

V

P5.12/AN12/T6IN

P5.13/AN13/T5IN

P5.10/AN10/T6EUD

P5.11/AN11/T5EUD

V

P2.0/CC0IO

P2.1/CC1IO

P2.2/CC2IO

P2.3/CC3IO

P2.4/CC4IO

P5.14/AN14/T4EUD

P5.15/AN15/T2EUD

SS

V

DC1

P2.5/CC5IO

P2.6/CC6IO

P2.7/CC7IO

P2.8/CC8IO/EX0IN

P2.9/CC9IO/EX1IN

P2.10/CC10IOEX2IN

P2.11/CC11IOEX3IN

P2.12/CC12IO/EX4IN

P3.0/T0IN

P3.2/CAPIN

P3.1/T6OUT

P2.13/CC13IO/EX5IN

P2.14/CC14IO/EX6IN

SS

DD

V

V

P3.5/T4IN

P3.3/T3OUT

P3.4/T3EUD

P2.15/CC15IO/EX7IN/T7IN

7/160

ST10F269

Table 1 :

P6.0 - P6.7 1 - 8 I/O 8-bit bidirec tional I/O por t, bit-wise programma ble for input or output via direction

P8.0 - P8.7 9 -16 I/ O 8-bit bidirectional I/O port, bit-w ise programmable for input or ou tput via direction

P7.0 - P7.7 19-26 I/O 8-bit bidirec tional I/O por t, bit-wise programma ble for input or output via direction

P5.0 - P5.9

P5.10 - P5.15

Pin Description

Symbol Pin Type Function

bit. Programmin g a n I/ O p in a s inp ut forces the corr espon ding out put dr iver to h igh

impedance state. Port 6 outputs can be configured as push-pull or open drain

drivers. The following Port 6 pins have alternate functions:

1 O P6.0 CS0

... ... ... ... ...

5 O P6.4 CS4

6 I P6.5 HOLD

7 O P6.6 HLDA

8 O P6.7 BREQ

bit. Programmin g a n I/ O p in a s inp ut forces the corr espon ding out put dr iver to h igh

impedance state. Port 8 outputs can be configured as push-pull or open drain

drivers. The input threshold of Port 8 is selectable (TTL or special).

The following Port 8 pins have alternate functions:

9 I/O P8.0 CC16IO CAPCOM2: CC16 Capture Input / Compare Output

... ... ... ... ...

16 I/O P8.7 CC23IO CAPCOM2: CC23 Capture Input / Compare Output

bit. Programmin g a n I/ O p in a s inp ut forces the corr espon ding out put dr iver to h igh

impedance state. Port 7 outputs can be configured as push-pull or open drain

drivers. The input threshold of Port 7 is selectable (TTL or special).

The following Port 7 pins have alternate functions:

19 O P7.0 POUT0 PWM Channel 0 Output

... ... ... ... ...

22 O P7.3 POUT3 PWM Channel 3 Output

23 I/O P7.4 CC28IO CAPCOM2: CC28 Capture Input / Compare Output

... ... ... ... ...

26 I/O P7.7 CC31IO CAPCOM2: CC31 Capture Input / Compare Output

27-36

39-44

39 I P5.10 T6EUD GPT2 Timer T6 External Up / Down Control Input

40 I P5.11 T5EUD GPT2 Timer T5 External Up / Down Control Input

41 I P5.12 T6IN GPT2 Timer T6 Count Input

42 I P5.13 T5IN GPT2 Timer T5 Count Input

43 I P5.14 T4EUD GPT1 Timer T4 External Up / Down Control Input

44 I P5.15 T2EUD GPT1 Timer T2 External Up / Down Control Input

II16-bit input-o nly port with Schmitt-Trigger characteristics. The pins of Port 5 ca n be

the analog inp ut c hann els ( up to 1 6) for the A/D co nverter, where P5.x equ als A Nx

(Analog input channel x), or they are timer inputs:

Chip Select 0 Output

Chip Select 4 Output

External Master Hold Request Input

Hold Acknowledge Output

Bus Request Output

8/160

Symbol Pin Type Function

ST10F269

P2.0 - P2.7

P2.8 - P2.15

P3.0 - P3.5

P3.6 - P3.13,

P3.15

47-54

57-64

47 I/O P2.0 CC0IO CAPCOM: CC0 Capture Input / Compare Output

... ... ... ... ...

54 I/O P2.7 CC7IO CAPCOM: CC7 Capture Input / Compare Output

57 I/O P2.8 CC8IO CAPCOM: CC8 Capture Input / Compare Output

... ... ... ... ...

64 I/O P2.15 CC15IO CAPCOM: CC15 Capture Input / Compare Output

65-70,

73-80,

81

65 I P3.0 T0IN CAPCOM Timer T0 Count Input

66 O P3.1 T6OUT GPT2 Timer T6 Toggle Latch Output

67 I P3.2 CAPIN GPT2 Register CAPREL Capture Input

68 O P3.3 T3OUT GPT1 Timer T3 Toggle Latch Output

69 I P3.4 T3EUD GPT1 Timer T3 External Up / Down Control Input

70 I P3.5 T4IN GPT1 Timer T4 Input for Count / Gate / Reload / Capture

73 I P3.6 T3IN GPT1 Timer T3 Count / Gate Input

74 I P3.7 T2IN GPT1 Timer T2 Input for Count / Gate / Reload / Capture

75 I/O P3.8 MRST SSC Master-Receiver / Slave-Transmitter I/O

76 I/O P3.9 MTSR SSC Master-Transmitter / Slave-Receiver O/I

77 O P3.10 TxD0 ASC0 Clock / Data Output (Asynchronous /

78 I/O P3.11 RxD0 ASC0 Data Input (Asynchronous) or I/O (Synchronous)

79 O P3.12 BHE

80 I/O P3.13 SCLK SSC Master Clock Output / Slave Clock Input

81 O P3.15 CLKOUT System Clock Output (=CPU Clock)

I/O 16-bit bidirectio nal I/O port, bit-wi se programmable for input or output via direction

bit. Programmin g a n I/ O p in a s inp ut forces the corr espon ding out put dr iver to h igh

impedance state. Port 2 outputs can be configured as push-pull or open drain

drivers. The input threshold of Port 2 is selectable (TTL or special).

The following Port 2 pins have alternate functions:

I EX0IN Fast External Interrupt 0 Input

I EX7IN Fast External Interrupt 7 Input

I T7IN CAPCOM2 Timer T7 Count Input

I/O

15-bit (P3.14 is missing) bidirectional I /O port, bit-wis e programmable for input or

I/O

output via direc tion bit. Programming an I/O pin as input forces the corre sponding

I/O

output driver to high impedance state. Port 3 outputs can be configured as push-pull

or open drain drivers. The input threshold of Port 3 is selectable (TTL or special).

The following Port 3 pins have alternate functions:

Synchronous)

External Memory High Byte Enable Signal

WRH

External Memory High Byte Write Strobe

9/160

ST10F269

Symbol Pin Type Function

P4.0 –P4.7 85-92 I/O Port 4 is an 8-bit bidirectional I/O port. It is bit-wise programmable for input or output

via direction bit. Pro gramming an I/O pin as inp ut forces the corresponding output

driver to high im pedance state. The input threshold is selectable (TTL or special).

Port 4.6 & 4.7 outputs can be configured as push-pull or open drain drivers.

In case of an extern al bus confi guration , Port 4 can be used to o utpu t the se gmen t

address lines:

85 O P4.0 A16 Segment Address Line

86 O P4.1 A17 Segment Address Line

87 O P4.2 A18 Segment Address Line

88 O P4.3 A19 Segment Address Line

89 O P4.4 A20 Segment Address Line

I CAN2_RxD CAN2 Receive Data Input

90 O P4.5 A21 Segment Address Line

I CAN1_RxD CAN1 Receive Data Input

91 O P4.6 A22 Segment Address Line

O CAN1_TxD CA N1 Transmit Data Output

92 O P4.7 A23 Most Significant Segment Address Line

O CAN2_TxD CA N2 Transmit Data Output

RD

/WRL 96 O Exte rnal M emor y Write Str obe. In WR- mode this pin is a ctivated for every external

WR

READY/

READY

ALE 98 O Address Latc h Enable Output. In case of use of external ad dressing or of multi-

EA

95 O External Memory Read Strobe. RD is activated for every external instruction or data

read access.

data write access. In WRL

accesses on a 16-bit bus, and for every data write access on an 8-bit bus. See

WRCFG in the SYSCON register for mode selection.

97 I Ready Input. The active level is programmable. When the Ready function is

enabled, the sele cted inact ive level at this pin, dur ing an exter nal me mory access,

will force the inser tio n of wait state c ycles until t he pin returns to the selected active

level.

plexed mode, this signal is the latch command of the address lines.

99 I Exter nal Access Ena ble pin. A low level applied to this pin du ring and after Reset

forces the ST10F2 69 t o st art the program fro m t he exter na l me mory space. A high

level forces the MCU to start in the internal memory space.

mode this pin is activated for low Byte data write

10/160

Symbol Pin Type Function

ST10F269

P0L.0 - P0L.7,

P0H.0

P0H.1 - P0H.7

100-107,

108,

111-117

I/O Two 8-bit bidirectional I/O po rts P0L and P0H, bit-wise programmable for input or

output via direc tion bit. Programming an I/O pin as input forces the corre sponding

output driver to high impedance state.

In case of an external bus configu ration, PORT0 ser ves as the address (A) and as

the address / data (AD) bus in multiplexed bus modes and as the data (D) bus in

demultiplexed bus modes.

Demultiplexed bus modes

Data Path Width: 8-bit 16-bit

P0L.0 – P0L.7: D0 – D7 D0 - D7

P0H.0 – P0H.7 I/O D8 - D15

Multiplexed bus modes

Data Path Width: 8-bit 16-bit

P0L.0 – P0L.7:

P0H.0 – P0H.7

P1L.0 - P1L.7

P1H.0 - P1H.7

XTAL1 138 I XTAL1 Oscillator amplifier and/or external clock input.

XTAL2 137 O XTAL2 Oscillator amplifier circuit output.

RSTIN

RSTOUT

NMI

V

AREF

V

AGND

RPD 84 - Timing pin for the retur n from interruptible powerdown mode and synchronous /

118-125

128-135

132 I P1H.4 CC24IO CAPCOM2: CC24 Capture Input

133 I P1H.5 CC25IO CAPCOM2: CC25 Capture Input

134 I P1H.6 CC26IO CAPCOM2: CC26 Capture Input

135 I P1H.7 CC27IO CAPCOM2: CC27 Capture Input

140 I Reset Input with Schmitt-T rigger characteristics. A low level at this pin for a specified

141 O Interna l Reset Indication Out put. This pin is driven to a low level during hardware,

142 I Non-Maskable Interrupt Input. A high to low transition at this pin causes the CPU to

37 - A/D converter reference voltage.

38 - A/D converter reference ground.

I/O Two 8-bit bidirectional I/O po rts P1L and P1H, bit-wise programmable for input or

output via direc tion bit. Programming an I/O pin as input forces the corre sponding

output driver to high impedance state. PORT1 is used as the 16-bit address bus (A)

in demultiplexed bus modes and also after switching from a demultiplex ed bus mode

to a multiplexed bus mode.

The following PORT1 pins have alternate functions:

To clock the device from an external source, drive XTAL1 while leaving XTAL2

unconnected. Minimum and maximum high / low and rise / fall times specified in the

AC Characteristics must be observed.

duration while the oscillator is r unning resets the ST10F2 69. An internal pull-up

resistor permits power-on reset using only a capacitor connected to V

tional reset mode (enabled by setting bit BDRSTEN in SYSCON register), the

RSTIN line is pulled low for the duration of the internal reset sequence.

software or watchdog timer res et.

tialization) instruction is executed.

vector to the NM I trap routin e. If bit PW DCFG = ‘ 0’ in SYS CON regis ter, when the

PWRDN ( power d own) i nstr uction is executed, the NMI

force the ST10F269 to go into power down mode. If NMI

when PWRDN is executed, the part will continue to run in normal mode.

If not used, pin NMI

asynchronous reset selection.

D0 – AD7AD0 - AD7

A

8 – A15

A

should be pulled high externally.

D8 - AD15

A

RSTOUT

remains low until the EINIT (end of ini-

SS

pin mu st b e low in or der to

is high and PWDCFG =’0’,

. In bidirec-

11/160

ST10F269

Symbol Pin Type Function

V

DD

V

SS

DC1

DC2

46, 72,

82,93,

109,

126,

136, 144

18,45,

55,71,

83,94,

110,

127,

139, 143

56

17

- Digital Supply Voltage:

= + 5V during normal operation and idle mode.

- Digital Ground.

--3.3V Decoupling pin: a decoupling capacitor of ≥ 330 nF must be connected

between this pin and nearest V

SS

pin.

12/160

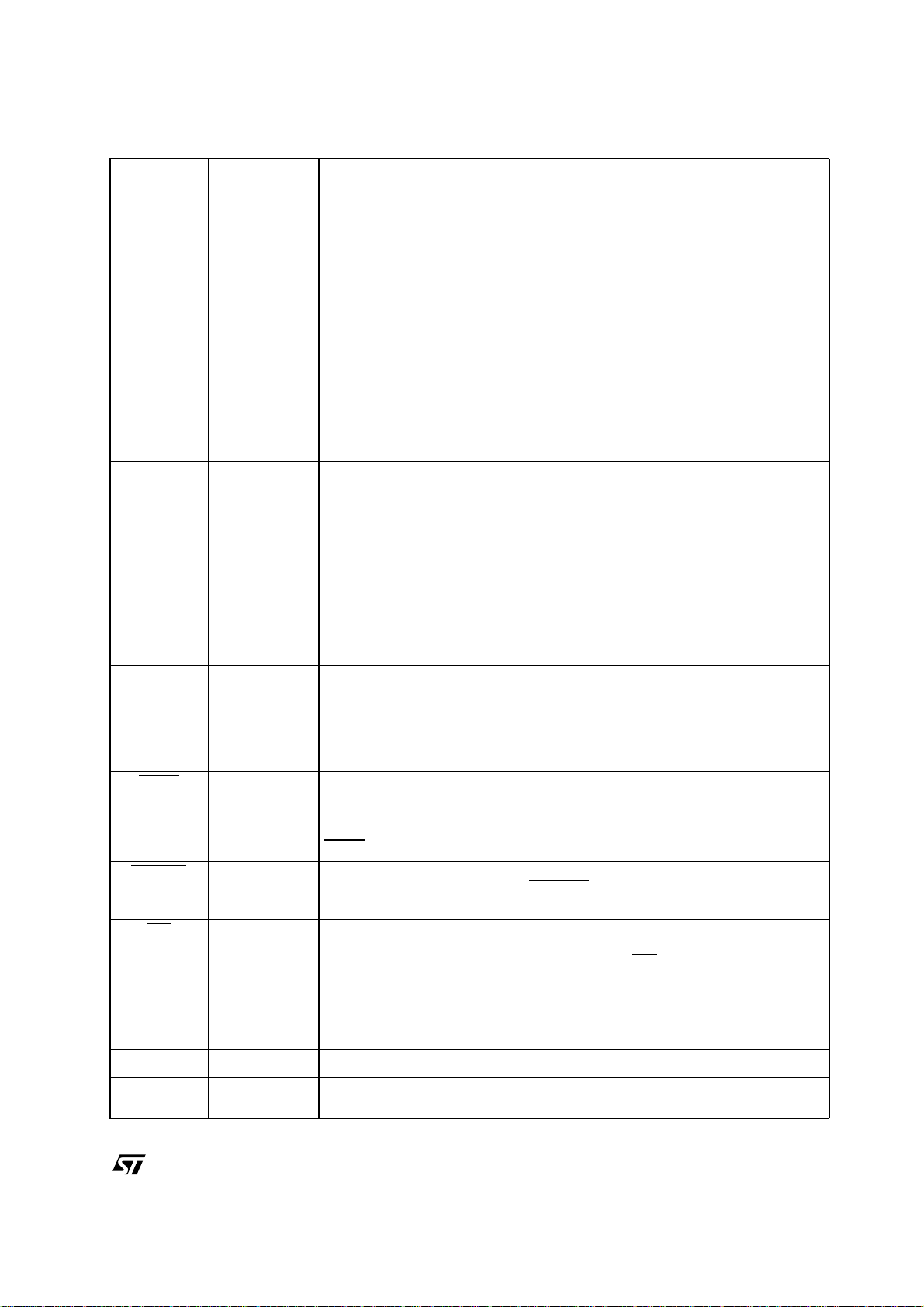

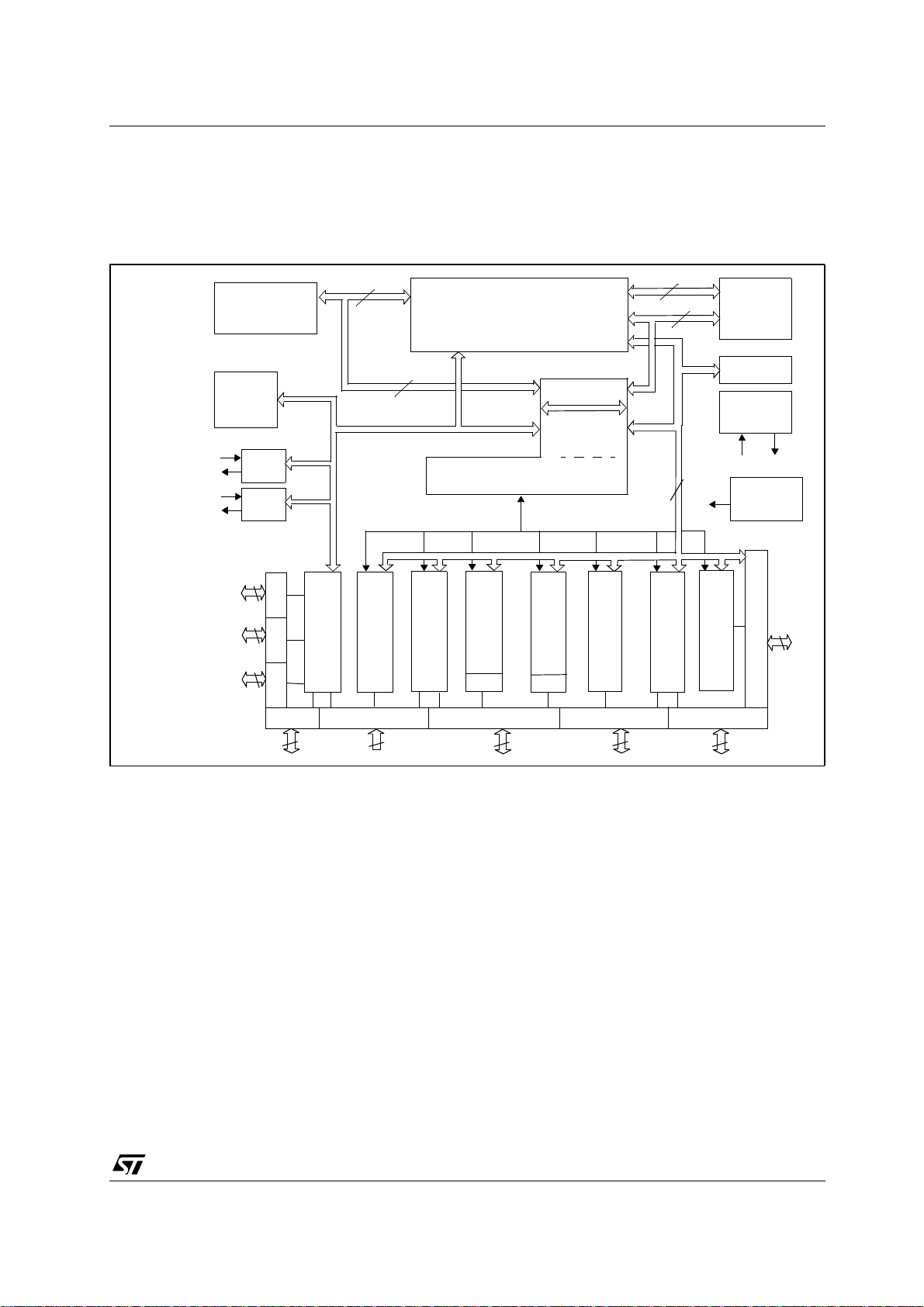

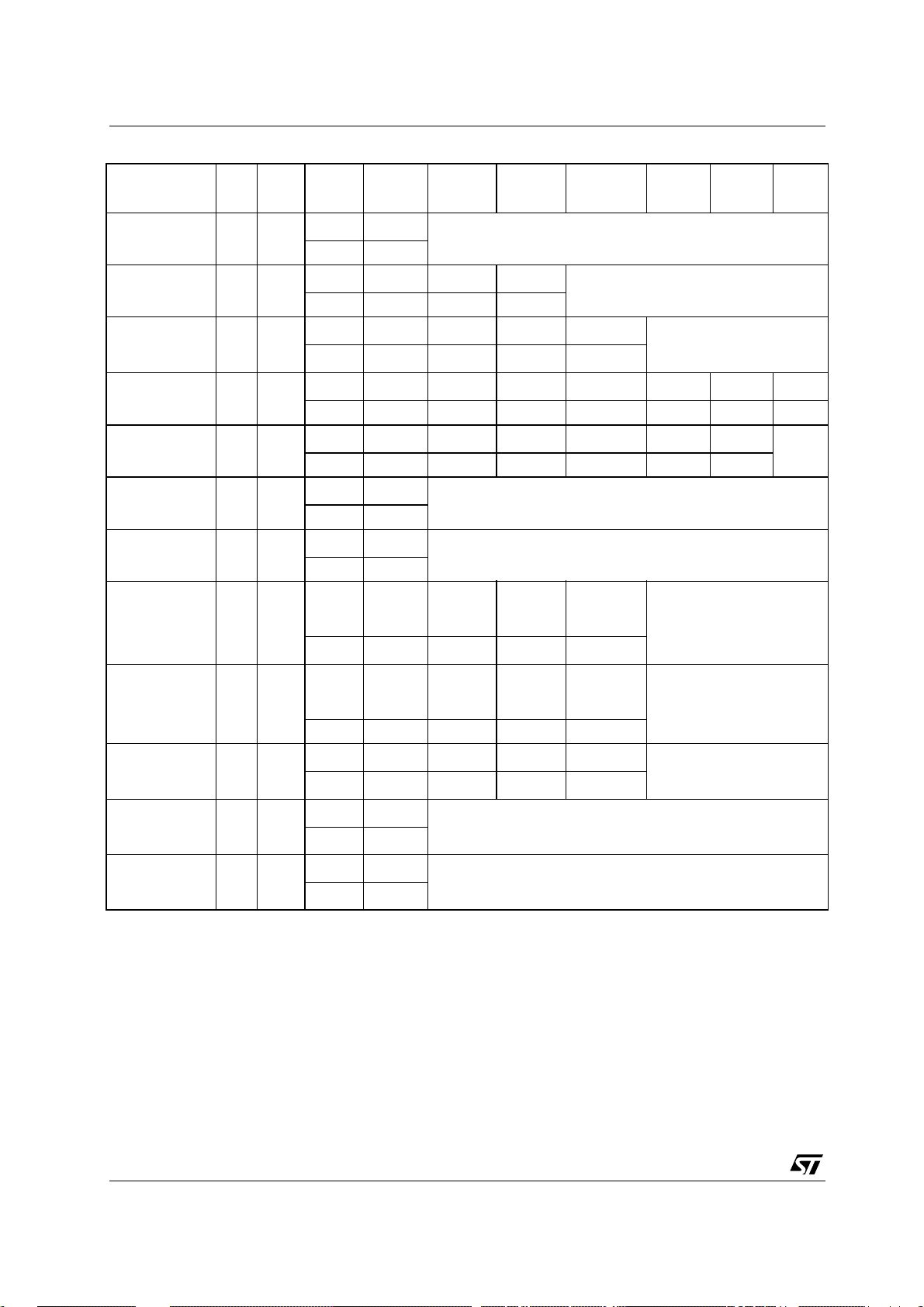

3 - FUNCTIONAL DESCRIPTION

The architecture of the ST10F269 combines

advantages of both RISC and CISC processors

and an advanced peripheral subsystem. The

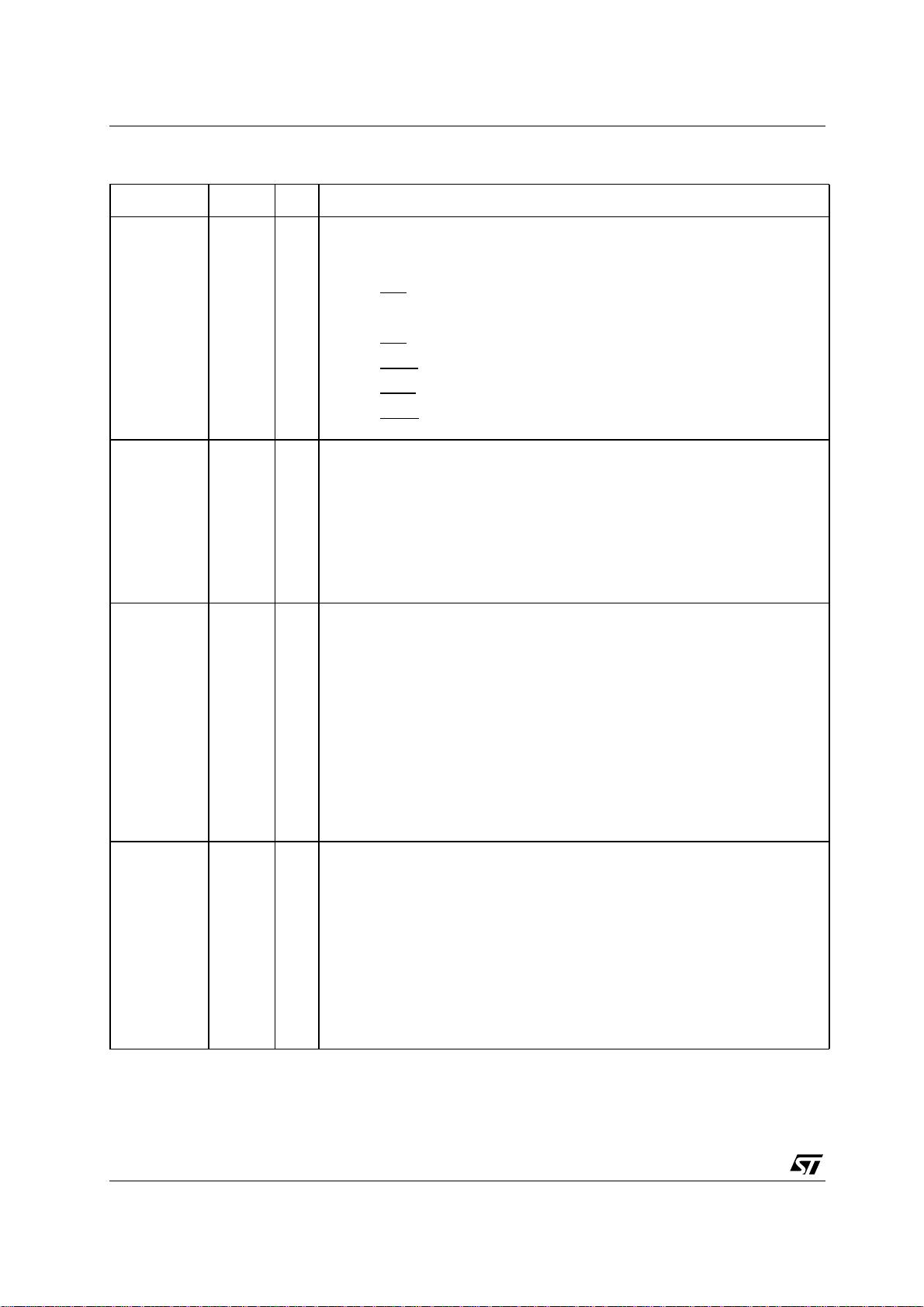

Figure 3 :

Block Diagram

ST10F269

block diagram g ives an overview of the different

on-chip components and the high bandwidth

internal bus structure of the ST10F269.

P4.5 C AN1_RXD

P4.6 CAN1_TXD

P4.4 C AN2_RXD

P4.7 CAN2_TXD

256K Byte

Flash Memory

10K Byte

XRAM

CAN1

CAN2

16

Port 0

16

Port 1Port 4

8

Port 6

32 16

CPU-Core and MAC Unit

16

PEC

Interrupt Controller

GPT1

ASC usar t

Controller

External Bus

8

10-Bit ADC

GPT2

Port 5

16 15

BRG

Port 3

SSC

BRG

PWM

Port 7

16

16

CAPCOM2

8

2K Byte

Inter n al

RAM

Watchdog

Oscillator

and PLL

XTAL1 XTAL2

3.3V Voltage

Regulator

Port 2

CAPCOM1

Port 8

16

8

13/160

ST10F269

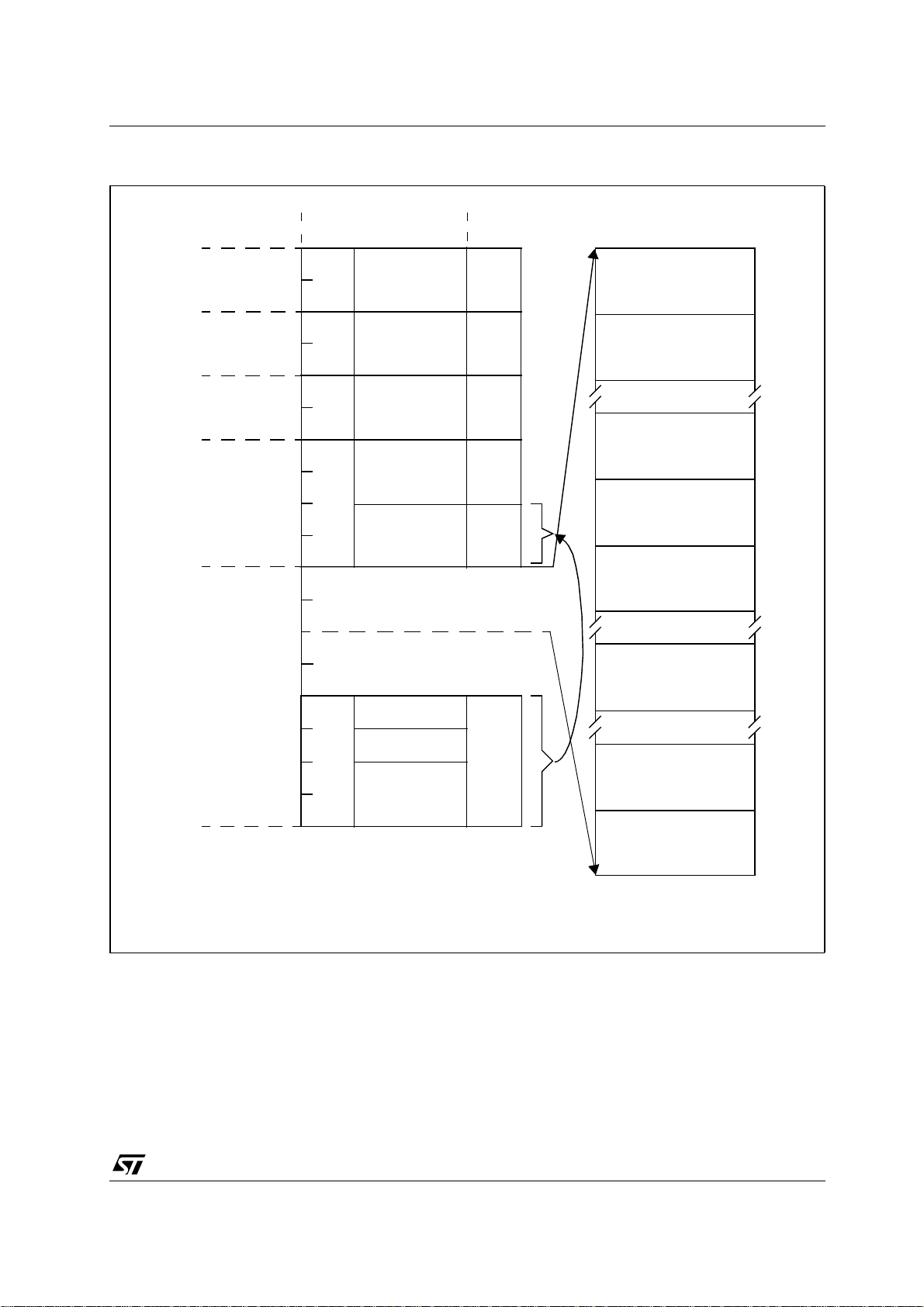

4 - MEMOR Y ORGA NI ZA T IO N

The memory space of the ST10F269 is configured

in a unified m emory architecture. Code memor y,

data memory, registers and I/O ports are

organized within the same linear address space of

16M Bytes. The entire memory space can be

accessed Byte wise or Word wise. Particular

portion s of the on-chip memory have additionally

been made directly bit addressable.

Flash:

IRAM:

(dual-port) is provided as a storage for data,

system stack, g e ner a l purpose register banks and

code. A register bank is 16 Wordwide (R0 to R15)

and / or Bytewide (RL0, RH0, …, RL7, RH7)

general purpose registers.

XRAM:

(single port XRAM) is provided as a storage for

data, user stack and code.

The XRAM is divided into 2 areas, the first 2K

Bytes named XRAM1 and the second 8K Bytes

named XRAM2, conn ected to the internal XBUS

and are accessed like an external memory in

16-bit demultiplexed bus-mode without wait state

or read/write delay (50ns access at 40MHz CPU

clock). Byte and Word accesses are allowed.

The XRAM1 address range is 00’E000h

- 00’E7FFh if XPEN (bit 2 of SYSCON register),

and XRAM1EN (bit 2 of XPERCON register) are

set. If XRAM1EN or XPEN is cleared, then any

access in the address range 00’E000h - 00’E7FFh

will be directed to external memory interface,

using the BUSCONx register corresponding to

address matching ADDRSELx register

The XRAM2 address range is 00’C000h

- 00’DFFFh if XPEN (bit 2 of SYSCON register),

and XRAM2 (bit 3 of XPERCON register are set).

If bit XRAM2EN or XPEN is cleared, then any

access in the address range 00’C000h

- 00’DFFFh will be directed to external memory

interface, using the BUSCONx register

corresponding to address matching ADDRSELx

register.

As the XRAM appears like external memory, it

cannot be used as system stack or as register

banks. The XRAM is not provided for single bit

storage and therefore is not bit addressable.

256K Bytes of on-chip Flash memory.

2K Bytes of on-chip internal RAM

10K Bytes of on-chip extension RAM

SFR/ESFR

: 1024 Bytes (2 x 512 Bytes) of

addr ess sp ace is r eserved for the spec ial fun ctio n

register areas. SFRs are Wordwide registers

which are used to control and to monitor the

function of the different on-chip units.

CAN1:

Address range 00’EF00h - 00’EFFFh is

reserved for the CAN1 Module access. The CAN1

is enabled by setting XPEN bit 2 of the SYSCON

register and by setting CAN1EN bit 0 of the new

XPERCON register. Accesses to the CAN Module

use demultiplexed addresses and a 16-bit data

bus (Byte accesses are possible). Two wait states

give an access time of 100ns at 40MHz CPU

clock. No tri-state wait states are used.

CAN2:

Address range 00’EE00h - 00’EEFFh is

reserved for the CAN2 Module access. The CAN2

is enabled by setting XPEN bit 2 of the SYSCON

register and by setting CAN2EN bit 1 of the new

XPERCON register. Accesses to the CAN Module

use demultiplexed addresses and a 16-bit data

bus (Byte accesses are possible). Two wait states

give an access time of 100ns at 40MHz CPU

clock. No tri-state wait states are used.

In order to meet the needs of designs where more

memory is required than is provided on chip, up to

16M Bytes of external RAM and/or ROM can be

connected to the microcontroller.

Note If one or the two CAN modules are used,

Port 4 cannot be programmed to output all

8 segment address lines. Thus, only 4

segment address lines can be used,

reducing the external memory space to 5M

Bytes (1M Byte per CS

line).

Visi bi lity of X B US Periphe rals

In order to keep the ST10F269 compatible with

the ST10C167 and with the ST10F167, the XBUS

peripherals can be sel ected to be visible and / or

accessible on the external address / data bus.

CAN1EN and CAN2EN bits of XPERCON register

must be set. If these bits are cleared before the

global enabling with XPEN-bit in SYSCON

register, the corresponding address space, port

pins and interrupts are not occupied by the

peripheral, thus the peripheral is not visible and

not available. Refer to Chapter 20 - Special

Function Register Overview.

14/160

ST10F269

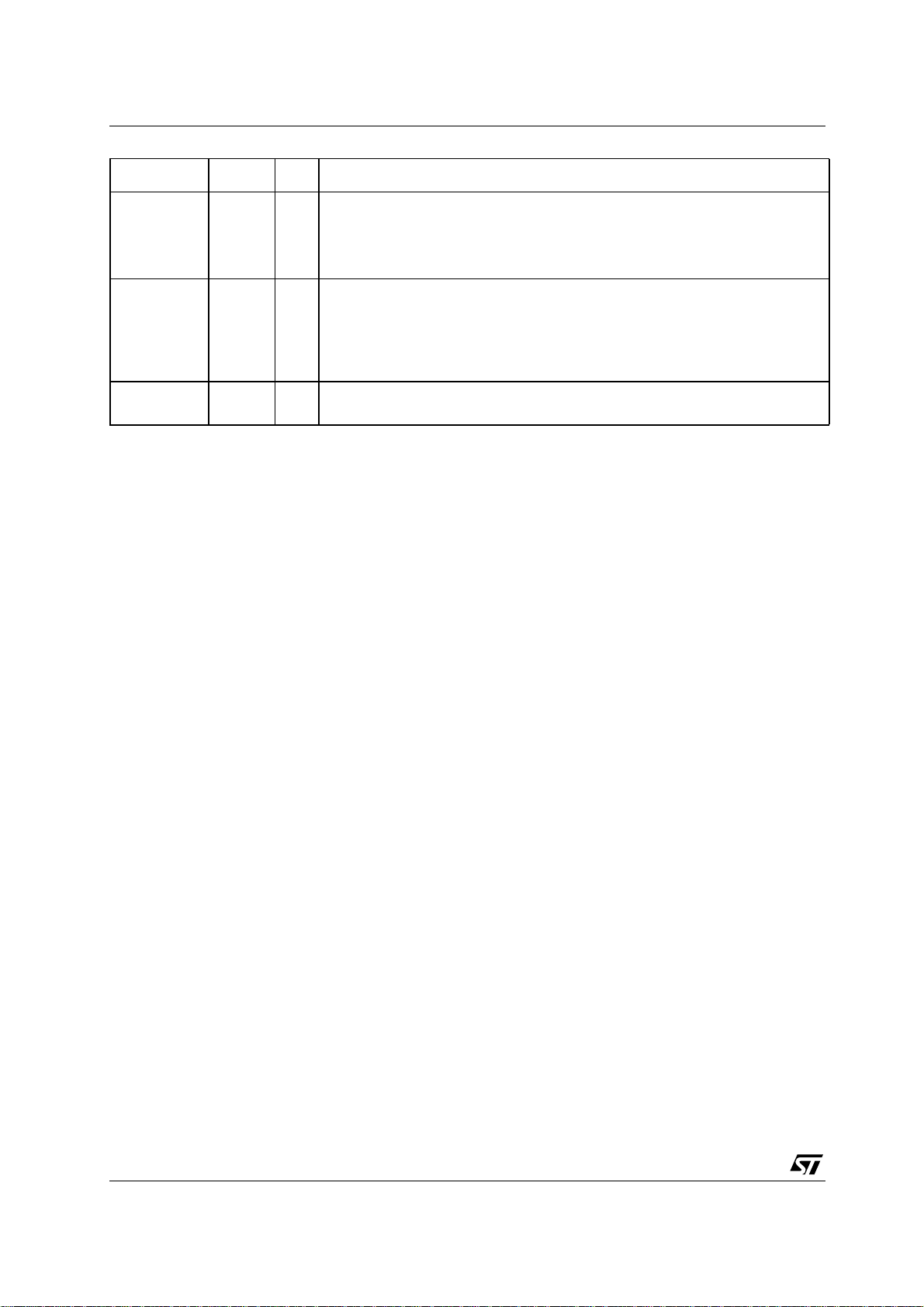

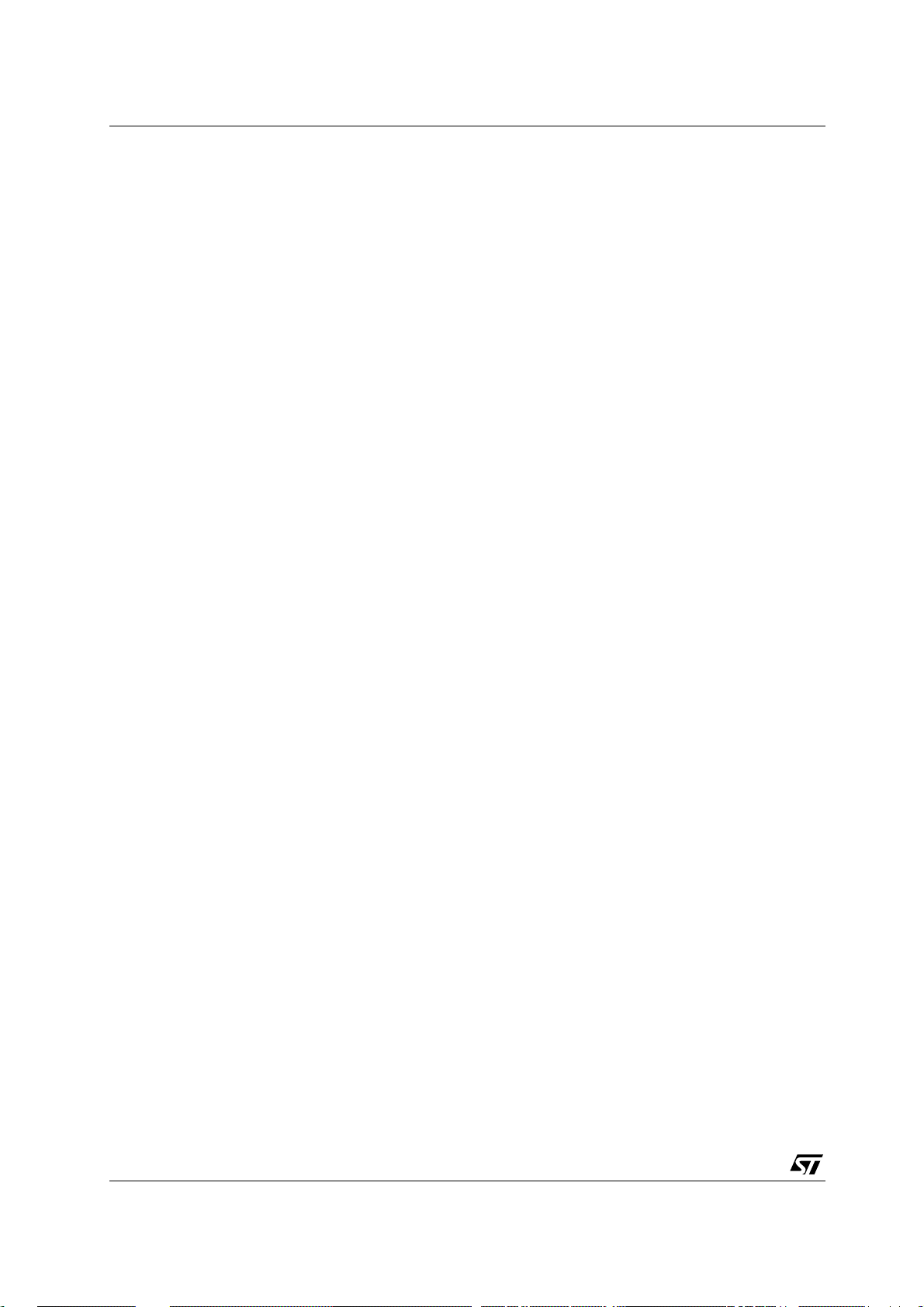

Figure 4 :

ST10F269 On-chip Memo ry Mapping

14

05’0000

Block6 = 64K Bytes

04’0000

10

Segment 4Segment 3Segment 2Segment 1Segment 0

Block5 = 64K Bytes

0C

03’0000

Block4 = 64K Bytes

02’0000

08

07

06

05

04

03

01’8000

01’0000

00’C000

Block3 = 32K Bytes

Block2*

Block1*

Block0*

Bank 1H

Bank 1L

RAM, SFR and X-pheripherals are

mapped i nt o the addres s sp ace.

00’FFFF

SFR : 512 B yt es

00’FE00

00’FDFF

IRAM : 2K Bytes

00’F600

00’F1FF

ESFR : 51 2 By tes

00’F000

00’EFFF

CAN1 : 256 Bytes

00’EF00

00’EEFF

CAN2 : 256 Bytes

00’EE00

02

00’6000

01

00’4000

00

00’0000

Data

Page

Number

* Bank 0L ma y be remapped fr om segment 0 to s egm ent 1 (Bank 1L) by setting SY SC ON-ROMS1 (before EINIT)

Data Page Num ber and Absol ute Memory A ddress are hexadecimal va l ues.

Absolu te

Memory

Address

Block2 = 8K Bytes

Block1 = 8K Bytes

Bank OL

Block0 = 16K Bytes

Internal

Flash

Memory

00’EC14

Real Time Clock

00’EC00

00’E7FF

XRAM1 : 2K Bytes

00’E000

00’DFFF

XRAM2 : 8K Bytes

00’C000

15/160

ST10F269

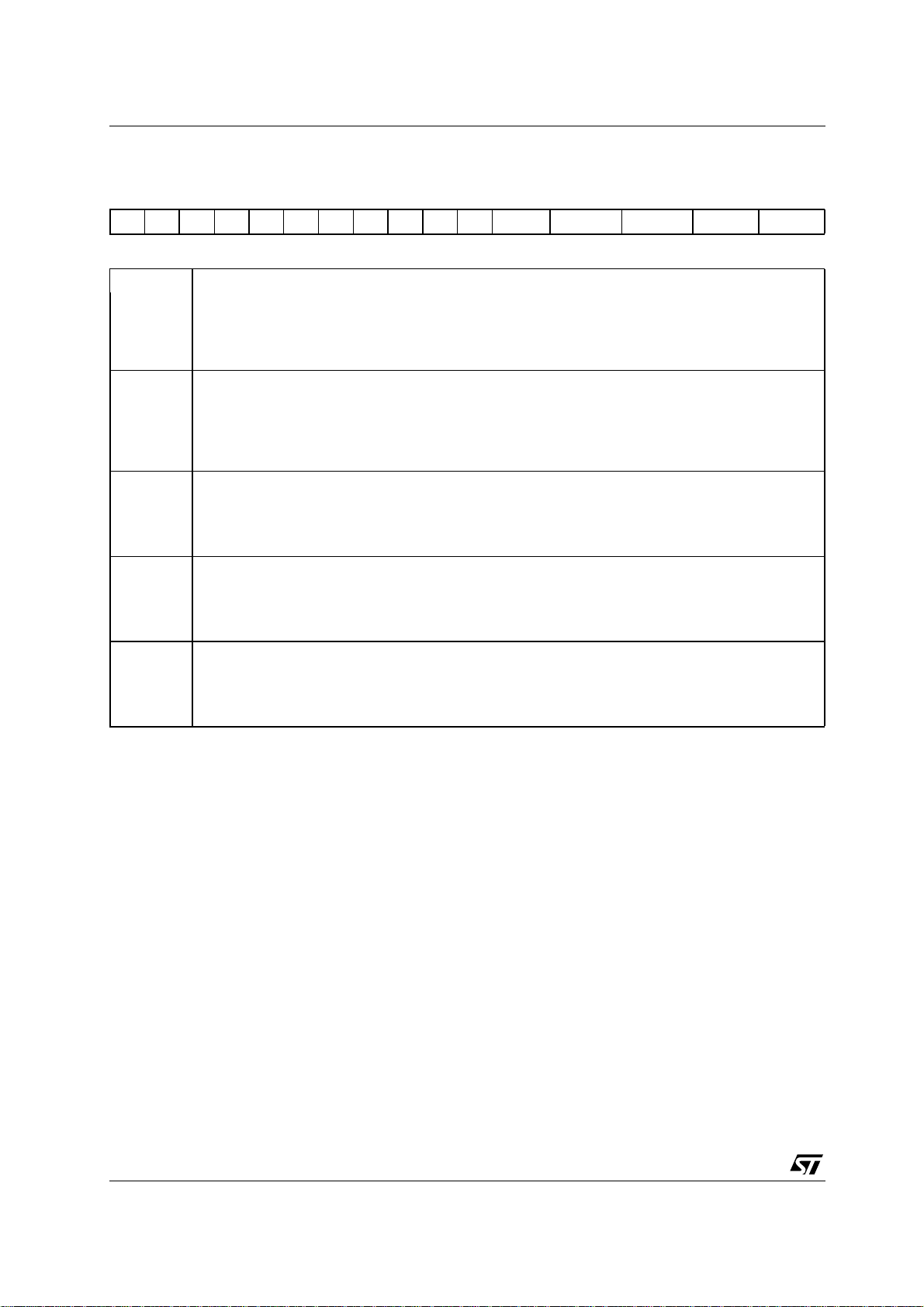

XPERCON (F024h / 12h)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

--------

-

CAN1EN

CAN2EN

XRAM1EN

XRAM2EN

RTCEN

CAN1 Enable Bit

‘0’: Accesses to the on-chip CAN1 XPeripheral and its functions are disabled. P4.5 and P4.6 pins can be

used as general purpose I/Os. Address range 00’EF00h-00’EFFFh is only directed to external memory if

CAN2EN is also ‘0’.

‘1’: The on-chip CAN1 XPeripheral is enabled and can be accessed.

CAN2 Enable Bit

‘0’: Accesses to the on-chip CAN2 XPeripheral and its functions are disabled. P4.4 and P4.7 pins can be

used as general purpose I/Os. Address range 00’EE00h-00’EEFFh is only directed to external memory if

CAN1EN is also ‘0’.

‘1’: The on-chip CAN2 XPeripheral is enabled and can be accessed.

XRAM1 Enable Bit

‘0’: Accesses to external memory within space 00’E000h to 00’E7FFh. The 2K Bytes of internal XRAM1

are disabled.

’1’: Accesses to the internal 2K Bytes of XRAM1.

XRAM2 Enable Bit

‘0’: Accesses to the external memory within space 00’C000h to 00’DFFFh. The 8K Bytes of internal

XRAM2 are disabled.

’1’: Accesses to the internal 8K Bytes of XRAM2.

RTC Enable Bit

’0’: Accesses to the on-chip Real Time Clock are disabled, external access is performed. Address range

00’EC00h-00’ECFFh is only directed to external memory if CAN1EN and CAN2EN are ’0’ also

’1’: The on-chip Real Time Clock is enabled and can be accessed.

ESFR Reset Value: - - 05h

--

RTCEN

RW RW RW RW RW

XRAM2EN XRAM1EN CAN2EN CAN1EN

Note: - When both CAN are disabled via XPER-

CON setting, then any access in the

address range 00’EE00h - 00’EFFFh will

be directed to external memor y interface,

using the BUSCONx reg ister corresponding to address matching ADDRSELx register. P4.4 and P4.7 can be used as General

Purpose I/O when CAN2 is disabled, and

P4.5 and P4.6 can be used as General

Purpose I/O when CAN1 is disabled.

- The default XPER selection after Reset is

identical to XBUS configuration of

ST10C167: XCAN1 is enabled, XCAN2 is

disabled, XRAM1 (2K Byte compatible

XRAM) is enabled, XRAM 2 (new 8K Byte

XRAM) is disab led.

16/160

- Register XPERCON cannot b e changed

after the global enabling of XPeripherals,

i.e. after the setting of bit XPEN in the

SYSCON register.

- In EMUlation mode, all the XPERipherals

are enabled (XPERCON bit are all set).

The access to external memory and/or

XBus is controlled by the bondout chip.

- When the Real Time Clock is disabled

(RTCEN = 0), the clock oscillator is

switch-off if the ST10 enters in

power-down mode. Otherwise, when the

Real Time Clock is enabled, the bit

RTCOFF of the RTCCON register allows

to choose the power-down mode of the

clock oscillator (See Chapter 16 - Real

Time Clock).

5 - INTERNAL FLASH MEMORY

ST10F269

5.1 - Overview

– 256K Byte on-chip Flash memory

– Two possibilities of Flash mapping into the CPU

address space

– Flash memory can be used for code and data

storage

– 32-bit, zero waitstate read ac cess (50ns cycle

time at f

= 40MHz)

CPU

– Erase-Program Controller (EPC) similar to

M29F400B STM’s stand-alone Flash memo ry

• Word-by-Word Programmable (16µs typ ical)

• Data polling and Toggle Protocol for EPC

Status

• Ready/Busy signal connected on XP2INT

interrupt line

• Internal Power-On detection circuit

– Memory Erase in blocks

• One 16K B yte, t wo 8K Byte, o ne 32K Byte,

three 64K Byte blocks

• Each block can be erased separately

(1.5 second typical)

• Chip erase (8.5 second typical)

• Each block can be separately protected

against programming and erasing

• Each protected block can be temporary unprotected

• When enabled, the read protection prevents

access to data in Flash memory using a program running out of the Flash memory space.

Access to data of internal Flash can only be performed with an inner protected program

– Erase Suspend and Res um e Modes

• Read and Program another Block during erase

suspend

– Single Voltage operat ion , no need of dedicat ed

supply pin

– Low Power Consumption:

• 45mA max. Read current

• 60mA max. Program or Erase current

• Automatic Stand-by-mode (50µA maximum)

– 100,000 Erase-Program Cycles per block,

20 years of data retention time

– Operating tempe rature: -40 to +125

o

C

5.2 - Operational Overview

Read M ode

In standard mode (the normal operating mode)

the Flash ap pears like an on-chip ROM with the

same timing and fu nctionality. The Flash m odule

offers a fast access time, allowing zero waitstate

access with CPU frequency up to 40MHz.

Instruction fetches and data operand reads are

performed with all addressing modes of the

ST10F269 instructi on set.

In order to optimize the programming tim e of the

internal Flash, blocks of 8K Bytes, 16K Bytes,

32K Bytes, 64K Bytes can be used. But the size of

the blocks does not apply to the whole memory

space, see details in Table 2.

Table 2 :

256K Byte Flash Memor y Block Organisation

Block Addresses (Segment 0) Addresses (Segment 1) Size (byte)

0

1

2

3

4

5

6

00’0000h to 00’3FFFh

00’4000h to 00’5FFFh

00’6000h to 00’7FFFh

01’8000h to 01’FFFFh

02’0000h to 02’FFFFh

03’0000h to 03’FFFFh

04’0000h to 04’FFFFh

01’0000h to 01’3FFFh

01’4000h to 01’5FFFh

01’6000h to 01’7FFFh

01’8000h to 01’FFFFh

02’0000h to 02’FFFFh

03’0000h to 03’FFFFh

04’0000h to 04’FFFFh

16K

8K

8K

32K

64K

64K

64K

17/160

ST10F269

Instructions and Commands

All operations besides normal read operations are

initiated and controlled by command sequences

written to the Flash Com mand Inte rface (CI). The

Command Interface (CI) interprets words written

to the Flash memory and enables one of the

following operations:

– Read memory array

– Program Word

– Block Erase

– Chip Erase

– Erase Suspend

– Erase Resume

– Block Protection

– Block Temporary Unprotection

– Code Protection

Commands are composed of several write cycles

at specific addresses of the Flash memor y. The

different write cycles of such command

sequences offer a fail-safe feature to protect

against an inadvertent write.

A command only starts when the Command

Interface has decoded the last write cycle of an

operation. Until that last write is performed, Flas h

memory remains in Read Mode

Notes: 1. As it is not possible to perform write

operations in the Flash while fetching code

from Flash, the Fl ash commands m ust be

written by instructions executed from

internal RAM or external memory.

one block in parallel. When a time-out period

elaps (96µs) after the last cycle, the

Erase-Program Controller (EPC) automatically

starts and times the erase pulse and executes the

erase operation. There is no need to program the

block to be erased with ‘0000h’ before an erase

operation. Termination of operation is indicated in

the Flash status register. After erase operation,

the Flash memor y locations are read as 'FFFFh’

valu e.

Erase Suspend

A block erase operation is typically executed

within 1.5 second for a 64K Byte block. Erasure of

a memory block may be suspended, in order to

read data from another block or to program data in

another block, and then resumed.

In-System Programming

In-system programming is fully supported. No

special programming voltage is required. Because

of the automatic execution of erase and

programming algorithms, write operations are

reduced to transferring commands and data to the

Flash and reading the status. Any code that

programs or erases Flash memory lo cations (that

writes data to the Flash) must be executed from

memory out side the on-chip Flash memory its elf

(on-chip RAM or external memory).

A boot mechanism is provided to support

in-system programming. It works using seria l link

via USART interface and a PC compatible or other

programming host.

2. Command write c ycles do not need to

be consecutively received, pauses are

allowed, save for Block Erase command.

During this operation all Erase Confirm

commands mus t be sent to c omplete any

block erase operation before time-out

period expires (typically 96µs). Command

sequencing must be followed exactly. Any

invalid combination of commands will reset

the Command Interface to Read Mode.

Status R egister

This register is used to flag the status of the

memory and the result of an operation. This

register can be accessed by read cycles during

the Erase-Program Controller (EPC) operation.

Erase Operation

This Flash memory features a block erase

architecture with a chip erase capability too. Erase

is accomplished by executing the six cycle erase

command sequence. Additional command write

cycles can then be performed to erase more than

18/160

Read/Write Protection

The Flash module supports read and write

protection in a very comfortable and advanced

protection functionality. If Read Protection is

installed, the whole Flash memory is protected

against any "external" read access; read

accesses are only possible with instructions

fetched directly from program Flash memory. For

update of the Flas h memory a temporar y disable

of Flash Read Protection is supported.

The device also features a block write protection.

Software locking of selectable memory blocks is

provided to protect code and data. This feature

will disable both program and erase operations in

the selected block(s) of the memory. Block

Protection is accomplished by block specific

lock-bit which are programmed by executing a

four cycle command sequence. The locked state

of blocks is indicated by specific flags in the

according block status registers. A block may only

be temporarily unlocked for update (write)

operations.

ST10F269

With the two possibilities for write protection whole memory or block specific - a flexible

installation of write protection is supported to

protect the Flash memory or parts of it from

unauthorized programming or erase accesses

and to provide virus-proof protection for all system

code blocks. All write protection also is enabled

during boot operation.

Power Supply, Reset

The Flash module uses a single power supply for

both read and write functions. Internally generated

and regulated voltages are provided for the

program and erase operations from 5V supply.

Once a program or erase cycle has been

completed, the device resets to the standard read

mode. At po wer-on, the Flash memory has a setup

phase of some microseconds (dependent on the

power supply ramp-up). During this phase, Flash

can not be read. Thus, if EA

pin is high (execution

will start from Flash memory), the CPU will remains

in reset state until the Flash ca n be ac cessed.

5.3 - Architectural Description

The Flash module distinguishes two basic

operating modes, the standard read mode and the

command mode. The initial state after power-on

and after reset is the standard read mode.

5.3.1 - Read Mode

The Flash modul e enters the standard operating

mode, the read mode:

– After Reset command

– After every completed erase operation

– After every completed programming operation

– After every other completed command

execution

– Few microseconds after a CPU-reset has

started

– After incorrect address and data values of

command sequences or writing them in an

improper sequence

– After incorrect write access to a read protected

Flash memory

The read mode remains active until the last

command of a command sequence is decoded

which start s directly a Flash array operation, such

as:

– erase one or several blocks

– program a word into Flash array

– protect / temporary unprotect a block.

In the standard read mode read accesses are

directly controlled by the Flash memory array,

delivering a 32-bit double Word from the

addressed position. Read accesses are always

aligned to double Word boundaries. Thus, both

low order address bit A1 and A 0 are not used in

the Flash array for read accesses. The high order

address bit A17/A 16 d efi ne the physical 64K Byte

segment being accessed within the Flash array.

5.3.2 - Command Mode

Every operation besides standard read operations

is initiated by commands written to the Flash

command register. The addresses used for

command cycles define in conjunction with the

actual state the specific step within command

sequences. With the last command of a command

sequence, the Erase-Program Controller (EPC)

starts the execution of the command. The EPC

status is indicated during command execution by:

– The Status Register,

– The Ready/Bu sy signal.

5.3.3 - Ready/Busy Signal

The Ready/Busy (R

XPER2 interr u pt node (XP2IC). When R

/B) signal is connected to the

/B is high,

the Flash is busy with a Program or Erase

operation and will not accept any additional

program or erase instruction. When R

/B is Low,

the Flash is ready for any Read/Write or Erase

operation. The R

/B will also be low when the

memory is put in Erase Suspend mo de.

This signal can be polled by reading XP2IC

register, or can be used to trigger an interrupt

when the Flash goes from Busy to Ready.

5.3.4 - Flash Status Register

The Flash Status register is used to flag the status

of the Flash memory and the result of an

operation. This register can be accessed by Read

cycles during the program-Erase Controller

operations. The program or erase operation can

be controlled by data polling on bit FSB.7 of

Status Register, detection of Toggle on FSB.6 and

FSB.2, or Error on FSB.5 and Erase Timeout on

FSB.3 bit. Any read at tempt in Flash du ring EPC

operation will a utomatic ally ou tput thes e five bits.

The EPC sets bit FSB.2, FSB.3, FSB.5, FSB.6

and FSB.7. Other bits are reserved for future use

and should be masked.

19/160

ST10F269

Flash Status (see note for address)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

-------

FSB.7

Flash Status bit 7: Data Polling Bit

- FSB.7 FSB.6 FSB.5 - FSB.3 FSB.2 -

RRR R R

Programming Operation: this bit outputs the complement of the bit 7 of the word being

programmed, and after completion, will output the bit 7 of the word programmed.

Erasing Operation: outputs a ‘0’ during erasing, and ‘1’ after erasing completion.

If the block selected for erasure is (are) protected, FSB.7 will be set to ‘0’ for about 100 µs, and

then return to the previous addressed memory data value.

FSB.7 will also flag t he Erase Suspend Mode by switching from ‘0’ t o ‘1’ at the start of the

Erase Suspend.

During Program operation in Erase Suspend Mode, FSB.7 will have the same behaviour as in

normal Program execution outside the Suspend mode.

FSB.6

Flash Stat us bi t 6: Toggle Bit

Programming or Erasing Operations: successive read operations of Flash Status register will

deliver complementary values. FSB.6 will toggle each time the Flash Status register is read.

The Program operation is completed wh en two successive reads yield the same value. The

next read will output the bit last programmed, or a ‘1’ after Erase operation

FSB.6 will be set to‘1’ if a read operation is attempted on an Erase Suspended block. In

addition, an Erase Suspend/Resume command will cause FSB.6 to toggle.

-

FSB.5

Flash Status bit 5: Error Bit

This bit is set to ‘1’ when there is a failure of Program, block or chip erase operations.This bit

will also be set if a user tries to program a bit to ‘1’ to a Flash location that is currently

programmed with ‘0’.

The error bit resets after Read/Reset instruction.

In case of success, the Err or bit wil l be s et to ‘0’ during Program or Eras e and then will output

the bit last programmed or a ‘1’ after erasing

FSB.3

Flash Status bit 3: Erase Time-out Bit

This bit is cleared by the EPC when the l ast Block Erase command has been en tered to the

Command Interface and it is awaiting the Erase star t. When the time-out period i s finished,

after 96 µs, FSB.3 returns back to ‘1’.

FSB.2

Flash Stat us bi t 2: Toggle Bit

This toggle bit, together with FSB.6, can be used to determine the chip status during the Erase

Mode or Erase Suspend Mode. It can be used also to identify the block being Erased

Suspended. A Read operation will cause FSB.2 to Toggle during the Erase Mode. If the Flash

is in Erase Suspend Mode, a Read operation from the Erase suspended block or a Program

operation into the Erase suspended block will cause FSB.2 to toggle.

When the Flash is in Program Mode during Erase Suspend, FSB.2 will be read as ‘1’ if address

used is the address of the word being programmed.

After Erase completion with an Error status, FSB.2 will toggle when reading the faulty sector.

Note: The Address of Flash Status Register is the address of the word being programmed when

Programming operation is in progress, or an address within block being erased when Erasing

operation is in progress.

20/160

ST10F269

5.3.5 - Flash Protection Register

The Flash Protection register is a non-volatile register that contains the protection status. This register

can be read by using the Read Prote ction Status (RP) command, and programmed by using the de dicated Set Protection command.

Flash Protection Register (PR)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CP - - - - - - - - BP6 BP5 BP4 BP3 BP2 BP1 BP0

BPx

CP

Block x Protection Bit (x = 0...6)

‘0’: the Block Protection is enabled for block x. Programming or erasing the block is not

possible, unless a Block Temporary Unprotection command is issued.

1’: the Block Protection is disabled for block x.

Bit is ‘1’ by default, and can be programmed permanently to ‘0’ using the Set Protection

command but then cannot be set to ‘1’ again. It is therefore possible to temporally disable the

Block Protection using the Block Temporary Unprotection instruction.

Code Protection Bit

‘0’: the Flash Code Protection is enabled. Read accesses to the Flash for execution not

performed in the Flash itself are not allowed, the returned value will be 009Bh, whatever the

content of the Flash is.

1’: the Flash Code Protection is disabled: read accesses to the Flash from external or internal

RAM are allowed

Bit is ‘1’ by default, and can be programmed permanently to ‘0’ using the Set Protection

command but then cannot be set to ‘1’ again. It is therefore possible to temporally disable the

Code Protection using the Code Temporary Unprotection instruction.

5.3.6 - Instructions Description

Twelve instructions dedicated to Flash memory

accesses are defined as follow:

Read/Reset (RD).

The Read/Reset instruction

consist of one write cycle with data XXF0h . it can

be optionally preceded by two CI enable

coded

cycles (data xxA8h at address 1554h + data

xx54h at address 2AA8h). Any successive read

cycle following a Read/Reset instruction will read

the memory array. A Wait cycle of 10µs is

necessary after a Read/Reset command if the

memory was in program or Erase mode.

Program Word (PW).

This instruction uses four

write cycles. After the two Cl enable coded cycles ,

the Program Word command xxA0 h is written at

address 1554h. The following write cycle will latch

the address and data of the word to be

programmed. Memor y programming can be do ne

only by writing 0's instead of 1's, otherwise an

error occurs. During programming, the Flash

Status is checked by reading the Flash Status bit

FSB.2, FSB.5, FSB.6 and FSB.7 which show the

status of the EPC. FSB.2, FSB.6 and FSB.7

determine if programming is on going or has

completed, and FSB.5 allows a check to be made

for any possible error.

Block Erase (BE).

This instruction uses a

minimum of six command cycles. The erase

enable command xx80h is written at address

1554h after the two-cycle CI enable sequence.

The erase confirm code xx30h must be written at

an address related to the block to be erased

preceded by the execution of a second CI enable

sequence. Additional erase confirm codes must

be given to erase more than one block in parallel.

Additional erase confirm commands must be

written within a defined time-ou t peri od. The input

of a new Block Erase command will restart the

time-out period.

When this time-out period has elapsed, the erase

starts. The status of the internal timer can be

monitored through the level of FSB.3, if FSB.3 is

‘0’, the Block Erase command has been given and

the timeout is running ; if FSB.3 is ‘1’, the timeout

has expired and the EPC is erasing the block(s).

21/160

ST10F269

If the second command given is not an erase

confirm or if the coded cycles are wrong, the

instruction aborts, and the device is reset to Read

Mode. It is not necessary to progr am the bloc k wi th

0000h as the EPC will do this automatically before

the erasing to FFFFh. Read operations after the

EPC has started, output the Flash Status Register .

During the execution of the erase by the EPC, the

device accepts only the Erase Suspend and

Read/Reset instructions. Data Polling bit FSB.7

returns ‘0’ while the erasure is in progress, and ‘1’

when it has completed. The Toggle bit FSB.2 and

FSB.6 toggle during the erase operation. They

stop when erase is completed. After completion,

the Error bit FSB.5 returns ‘1’ if there has been an

erase failure because erasure has not comp leted

even after the maximum number of erase cycles

have been executed by the EPC, in this case, it

will be necessary to input a Read/Reset to the

Command Interface in order to reset the EPC.

Chip Erase (CE)

. This instruction uses six write

cycles. The Erase Enable command xx80h, must

be written at address 1554h after CI-Enable

cycles. The Chip Erase command xx10h must be

given on the sixth cycle after a second CI-Enable

sequence. An error in command sequence will

reset the CI to Read mode. It is NOT necessary to

program the block with 0000h as the E PC will do

this automatically before the erasing to FFFFh.

Read operations after the EPC has star ted out put

the Flash Status Register. During the execution of

the erase by the EPC, Data Polling bit FSB.7

returns ‘0’ while the erasure is in progress, and ‘1’

when it has completed. The FSB.2 and FSB.6 bit

toggle during the erase operation. They stop when

erase is finished. The FSB.5 error bit returns "1" in

case of failure of the erase operation. The error

flag is set after the maximum number of erase

cycles have been executed by the EPC. In this

case, it will be necessary to input a Read/Reset to

the Command Interface in order to reset the EPC.

Erase Suspend (ES).

This instruction can be

used to suspend a Block Erase operation by

giving the command xxB0h without any specific

address. No CI-Enable cycles is required. Erase

Suspend operation allows reading of data from

another block and/or the programming in another

block while erase is in progress. If this com mand

is given during the time-out period, it will terminate

the time-out period in addition to erase Suspend.

The Toggle bit FSB.6, when monitored at an

address that b elongs to the block being erased,

stops toggling when Erase Suspend Command is

effective, It happens between 0.1µs and 15µs

after the Erase Suspend Command has been

written. The Flash will then go in normal Read

Mode, and read from blocks not being erased is

valid, while read from block being erased will

output FSB.2 toggling. Dur ing a Suspend phase

the only instructions valid are Erase Resume and

Program Word. A Read / Reset instruction d uring

Erase suspend wi ll definitely abor t t he Erase a nd

result in invalid data in the block being erased.

Erase Resume (ER).

This instruction can be

given when the memory is in Erase Suspend

State. Erase can be resumed by writing the

command xx30h at any address without any

Cl-enable sequence.

Program during Erase Sus pend.

The Program

Word instruction during Erase Suspend is allowed

only on blocks that are not Erase-suspended. This

instruction is the same than the Program Word

instruction.

Set Prote c t ion (SP).

This instruction can be used

to enable both Block Protection (to protect each

block independently from accidental Erasing-Programming Operation) and Code Protection (to

avoid code dump). The Set Protection Com mand

must be given after a s pecial CI -Protection Enab le

cycles (see instruction table). The following Write

cycle, will pr ogram the Protecti on Regist er. To protect the block x (x = 0 to 6), the data bit x must be

at ‘0’. To protect the code, b it 15 of the data must

be ‘0’. Enabling Block or Code Protec tion is

manent

and can be cleared only by STM. Block

per-

Temporary Unprotection and Code Temporary

Unprotection instructions are available to allow the

customer to update the code.

Notes: 1. The new value programmed i n prot ectio n

register will only become active after a reset.

2. Bit that are already at ’0’ in protection

register must be confirmed at ’0’ also in

data latched during the 4th cycle of set

protection command, otherwise an error

may occur.

Read Protection Status (RP).

This in struct ion is

used to read the Block Protection status and the

Code Protection status. To read the protection

register (see Table 3), the CI-Protection Enable

cycles must be executed followed by the

command xx90h at address x2A54h. The

following Read Cycles at any odd word address

will output the Block Protection Status. The Read/

Reset command xxF0h must be written to reset

the protection interface.

Note: After a modification of protection register

(using Set Protection command), the Read

Protection Status will return the new PR

value only after a reset.

22/160

ST10F269

Block Temporary Unprotection (BTU).

This Instruction can be used to temporary unprotect all the

blocks from Program / Erase protection. The Unprotection is disabled after a Reset cycle. The Block

Tem porary Unprotection command xxC 1h must be given to enable Block Temporar y Unprotection. The

Command must be preceded by the CI-Protection Enable cycles and followed by the Read/Reset

command xxF0h.

Set Code Protec tion ( SCP).

This kind of protection allows the customer to protect the proprietary code

written in Flash. If installed and active, Flash Code Protection prevents data operand accesses and

program branches into the on-chip Flas h area from any location outside the Flash memor y itself. Data

operand accesses and branches to Flash locations are only and exclusively allowed for instructions

ex ecuted from the Flash memory itself. Every read or jump to Flash performed from another memory (like

internal RA M , external m emory) while C ode Protec t ion is enabled, w ill give the opc od e 009B h related to

TRAP #00 illegal instruction. The CI-Protection Enable cycles must be sent to set the Code Protection. By

writing data 7FFFh at any odd word addre ss, the Code Protec ted status is stored in the Flash Pr otec tion

Register (PR). Protection is permanent and canno t be cleared by the user. It is possible to temporarily

disable the Code Protection using Code Temporary Unprotection instruction.

Note: Bits that are already at ’0’ in protection register must be confirmed at ’0’ also in data latched during

the 4th cycle of set protection command, otherwise an error may occur.

Code Temporary Unprotection (CTU).

This instruction must be used to temporary disable Code

Protection. This instruction is effective only if executed from Flash memory space. To restore the

protection status, without using a reset, it is necessary to use a Code Tempo rary Protection instruct ion.

System reset will res et also t he Code Temporary Unprotected status. The Code Temporary Unprot ecti on

command consists of the following write cycle:

MOV MEM, Rn ; This instruction MUST be executed from Flash memory space

Where MEM is an absolute address inside memor y spa ce, Rn is a register loaded with data 0FFFFh.

Code Temporary Protection (CTP).

This instruction allows to restore Code Protection. This operation is

effective only if executed from Flash memory and is necessar y to restore the protection status after the

use of a Code Temporary Unprotection instruction.

The Code Temporary Protection command consists of the following write cycle:

MOV MEM, Rn ; This instruction MUST be executed from Flash memory space

Where MEM is an absolute address inside memor y spa ce, Rn is a register loaded with data 0FFFBh.

Note that Code Temporary Unprotection instruction must be used when it is necessar y to modify the

Flash with protected code (SCP), since the write/erase routines must be executed from a memory

external to Flash space. Usually, the write/erase routines, executed in RAM, ends with a retur n to Flash

space where a CTP instruction restore the protection.

23/160

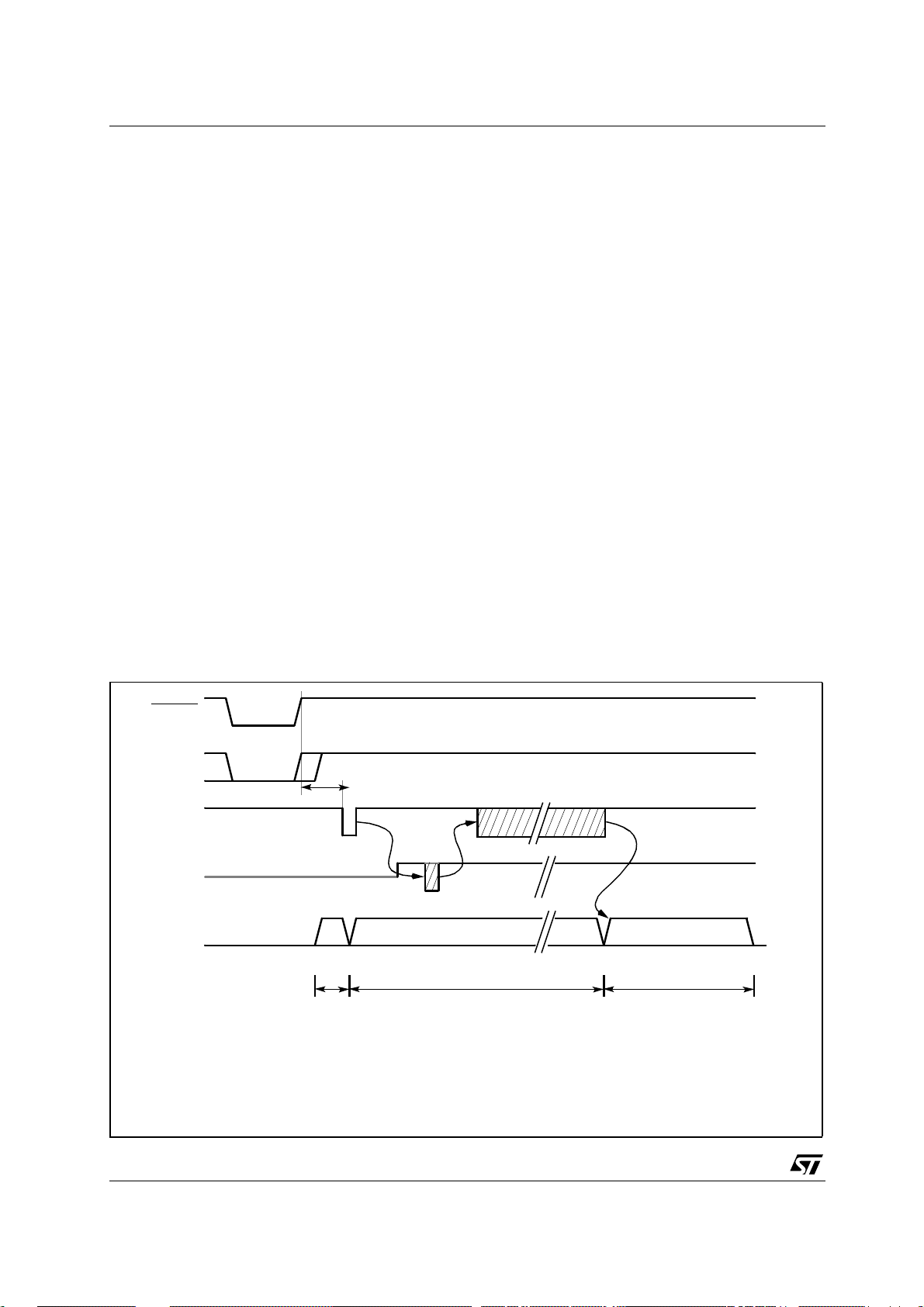

ST10F269