16 Mbit (1Mb x16, Boot Block) Flash Memory

and 4Mbit (256Kb x16) SRAM, Multiple Memory Product

FEATURES SUMMARY

■ MULTIPLE MEMORY PRODUCT

– 16 Mbit (1Mb x 16) Boot Block Flash Memory

– 4 Mbit (256Kb x 16) SRAM

■ SUPPLY VOLTAGE

–V

–V

–V

■ ACCESS TIME: 70ns, 85ns

■ LOW POWER CONSUMPTION

■ ELECTRONIC SIGNATURE

= V

DDF

DDQF

= 12V for Fast Program (optional)

PPF

– Manufacturer Code: 20h

– Top Device Code, M36W416TG: 88CEh

– Bottom Device Code, M36W416BG: 88CFh

FLASH MEMORY

■ MEMORY BLOCKS

– Parameter Blocks (Top or Bottom location)

– Main Blocks

■ PROGRAMMING TIME

– 10µs typical

– Double Word Programming Option

■ BLOCK LOCKING

– All blocks locked at Power up

– Any combination of blocks can be locked

–WP

■ AUTOMATIC STAND-BY MODE

■ PROGRAM and ERASE SUSPEND

■ 100,000 PROGRAM/ERASE CYCLES per

for Block Lock-Down

F

BLOCK

■ COMMON FLASH INTERFACE

– 64 bit Security Code

■ SECURITY

– 64 bit user programmable OTP cells

– 64 bit unique device identifier

– One parameter block permanently lockable

= 2.7V to 3.3V

DDS

= V

DDS

= 2.7V to 3.3V

M36W416TG

M36W416BG

PRELIMINARY DATA

SRAM

■ 4 Mbit (256Kb x 16)

■ ACCESS TIME: 70ns

■ LOW V

■ POWER DOWN FEATURES USING TWO

CHIP ENABLE INPUTS

Figure 1. Packages

DATA RETENTION: 1.5V

DDS

FBGA

Stacked LFBGA66 (ZA)

12 x 8mm

November 2002

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/62

M36W416TG, M36W416BG

TABLE OF CONTENTS

SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

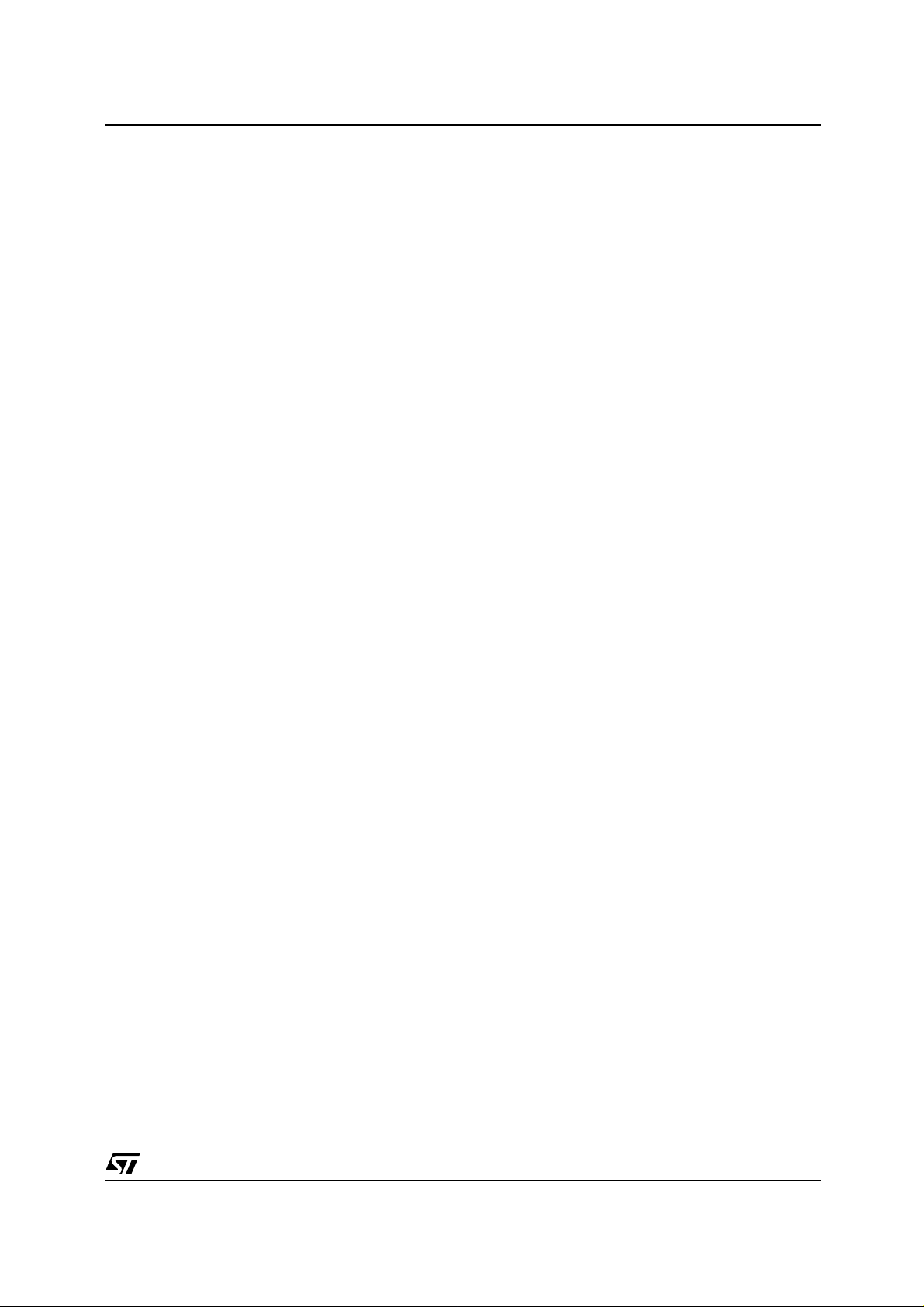

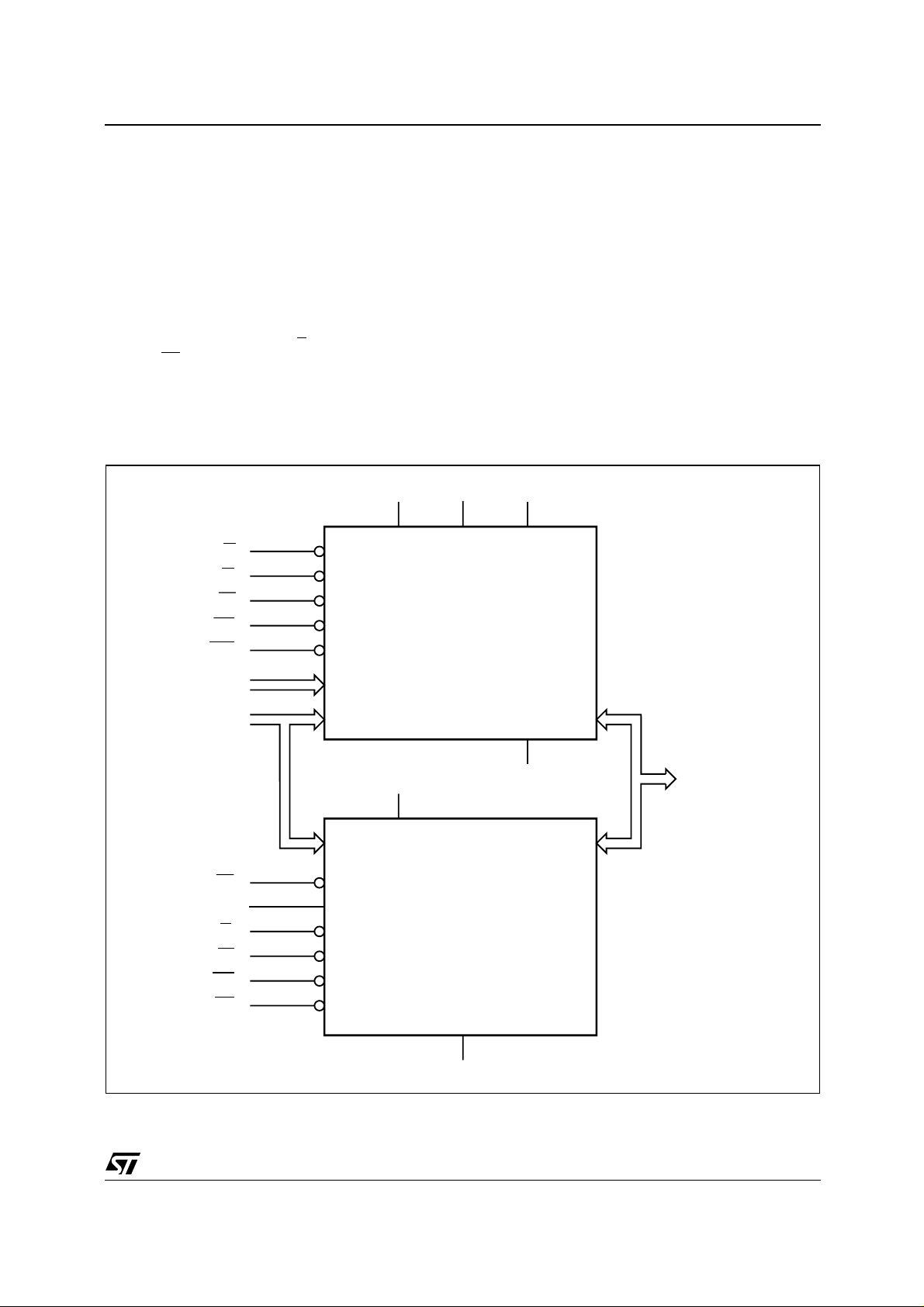

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

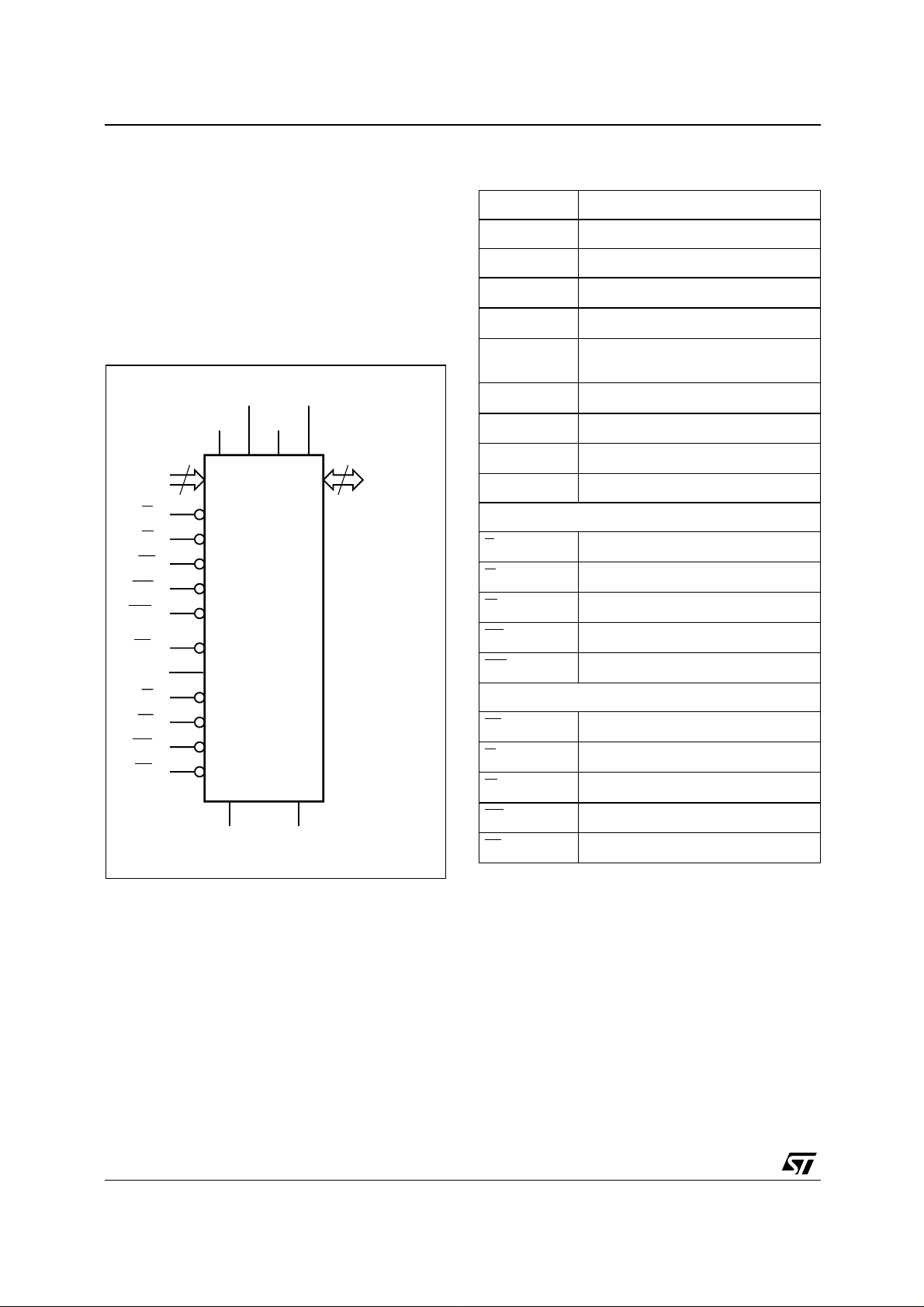

Figure 3. LFBGA Connections (Top view through package). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Address Inputs (A0-A17). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Address Inputs (A18-A19). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Data Inputs/Outputs (DQ0-DQ15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Flash Chip Enable (EF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Flash Output Enable (GF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Flash Write Enable (WF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Flash Write Protect (WPF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Flash Reset (RPF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SRAM Chip Enable (E1S, E2S). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SRAM Write Enable (WS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SRAM Output Enable (GS).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SRAM Upper Byte Enable (UBS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

SRAM Lower Byte Enable (LBS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

V

and VDDS Supply Voltages.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

DDF

and V

V

DDQF

V

Program Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

PPF

V

and V

SSF

Supply Voltage (2.7V to 3.3V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

DDS

Ground.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

SSS

FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

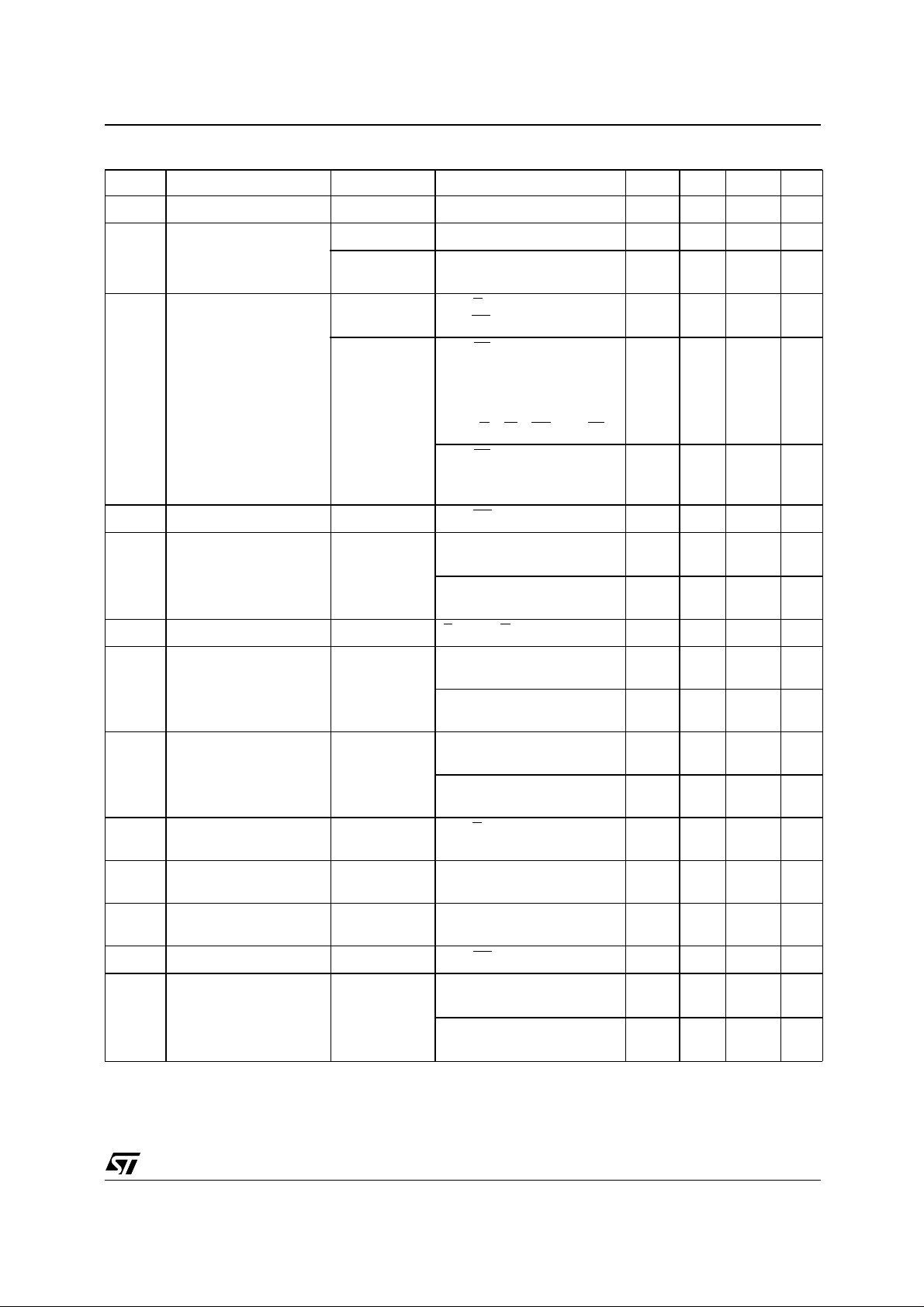

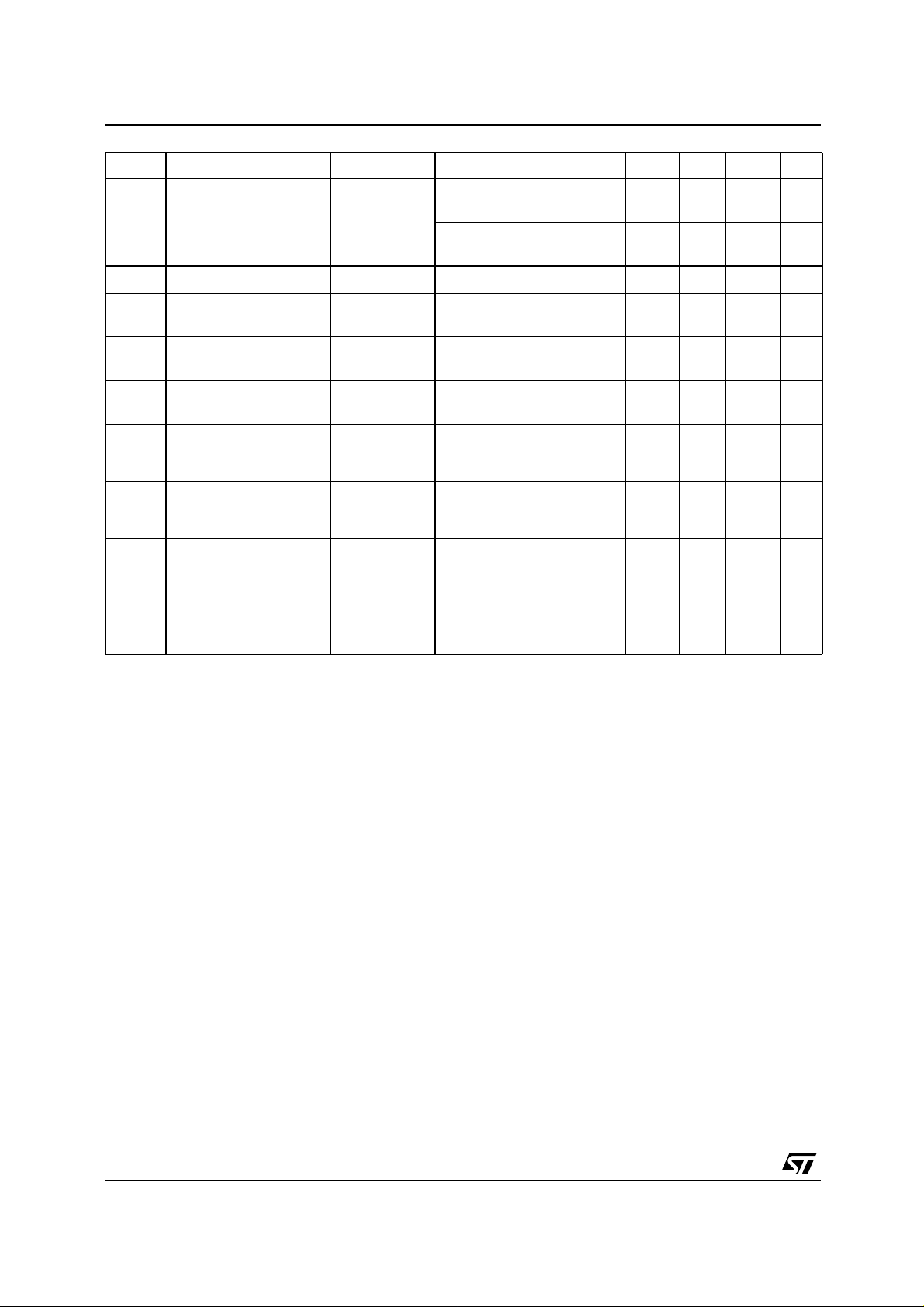

Figure 4. Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

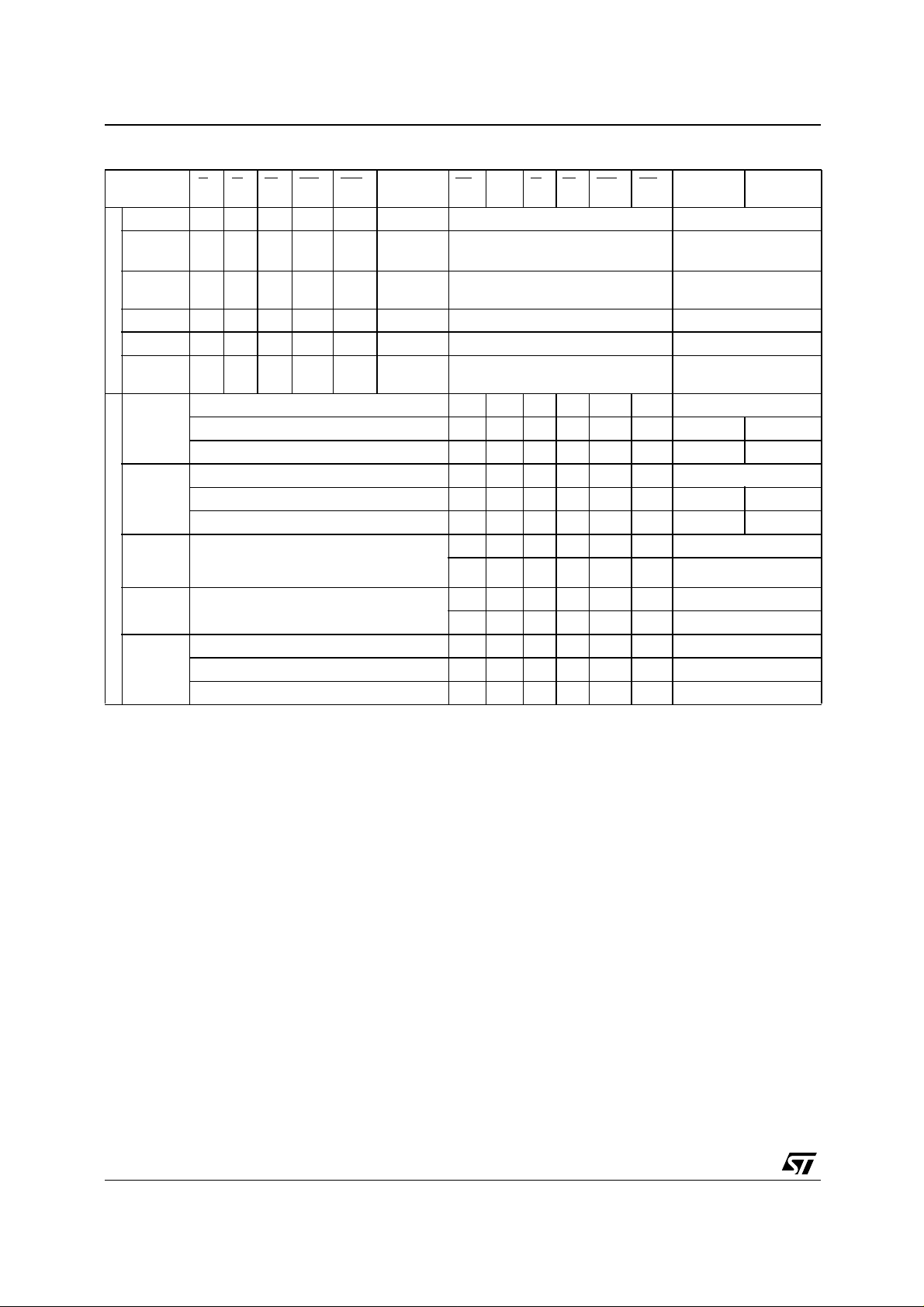

Table 2. Main Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 3. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

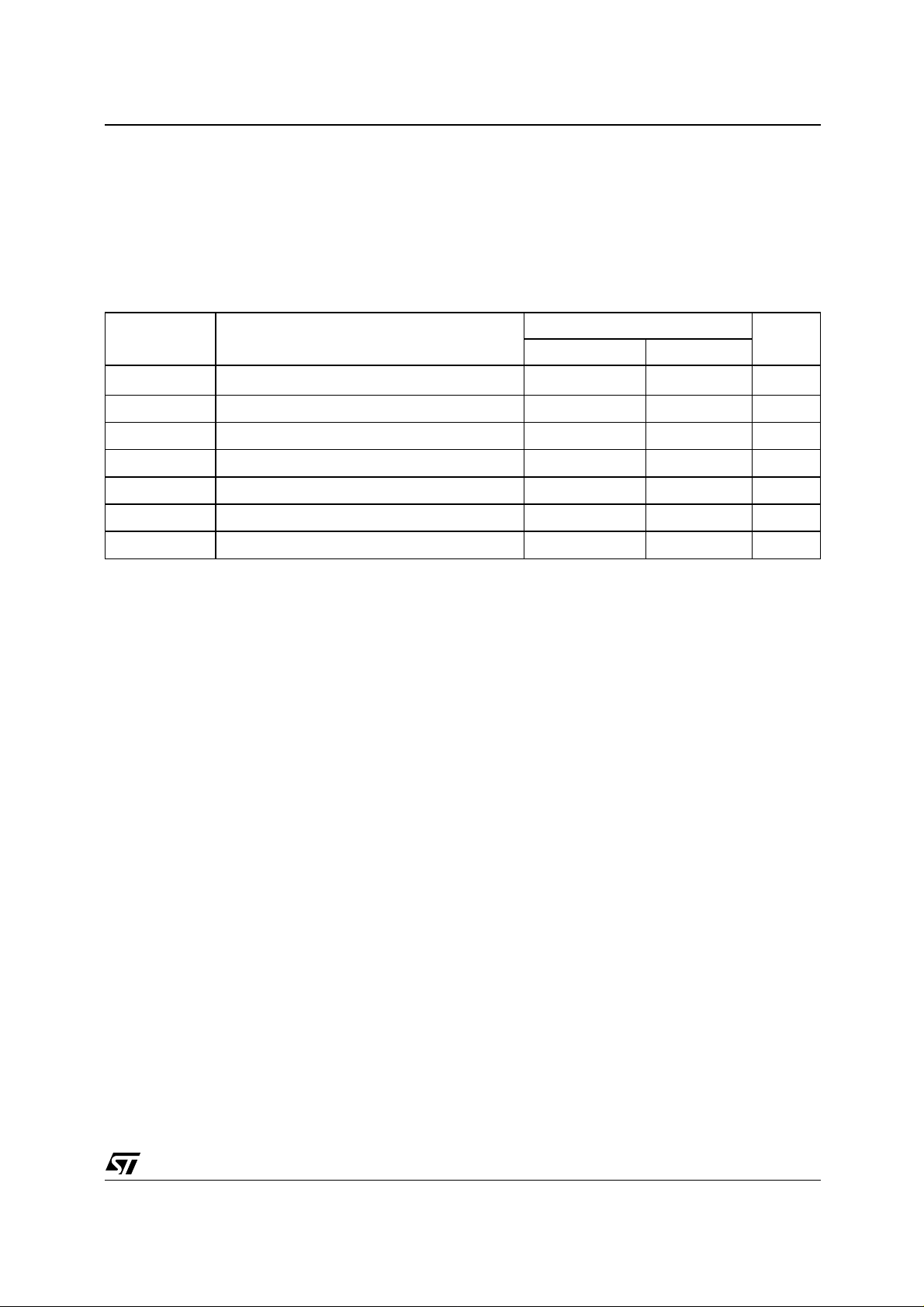

DC AND AC PARAMETERS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 2

Table 4. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 5. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Figure 6. AC Measurement Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 5. Device Capaci ta n ce. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 6. DC Character i stics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

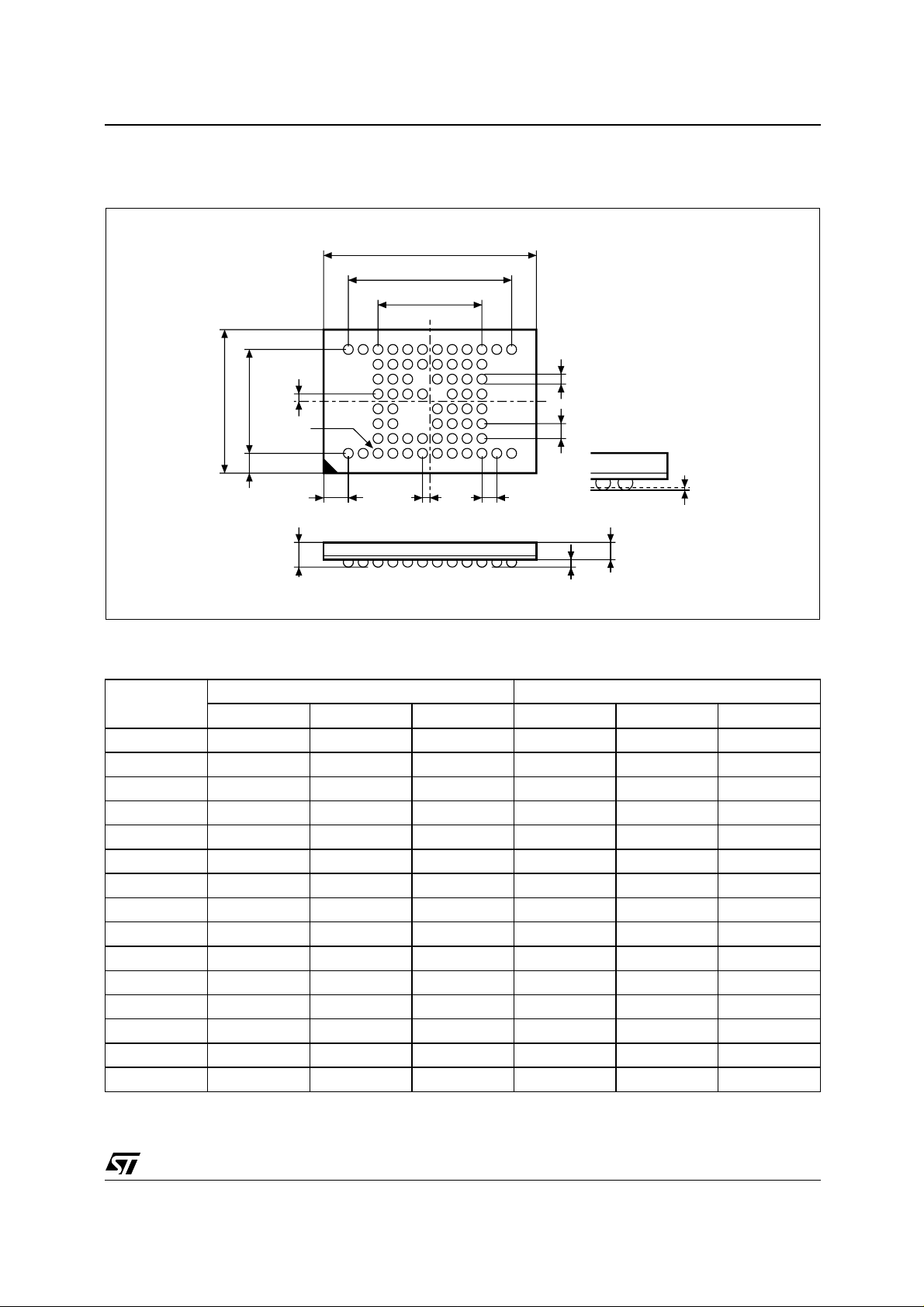

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 7. Stacked LFBGA66-12x8mm , 8x8 ball array, 0.8mm pitch, Bottom Vi ew Package Ou tline15

Table 7. Stacked LFBGA66 - 12x8mm, 8x8 ball array, 0.8 mm pitch, Package Mechanical Data . 15

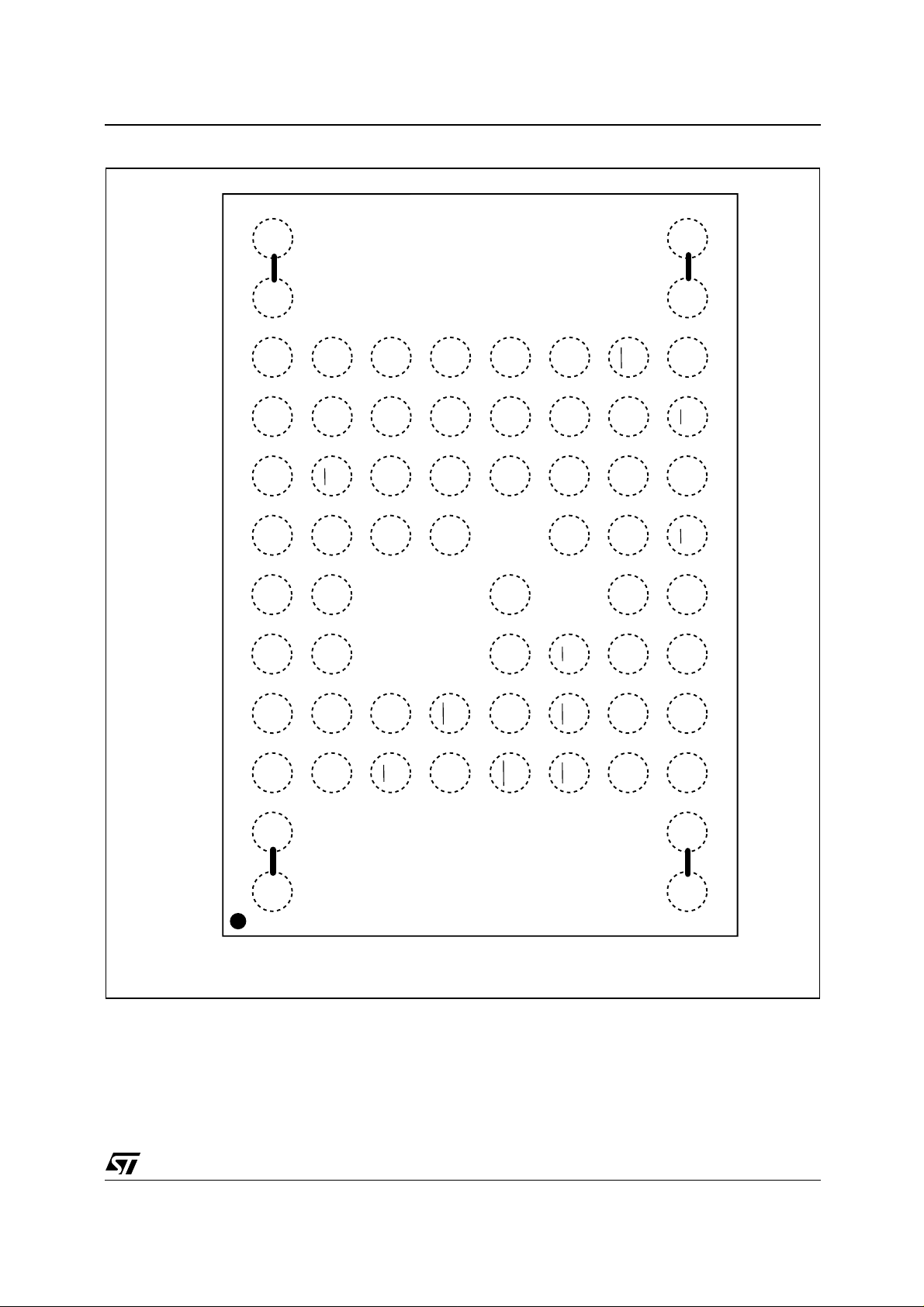

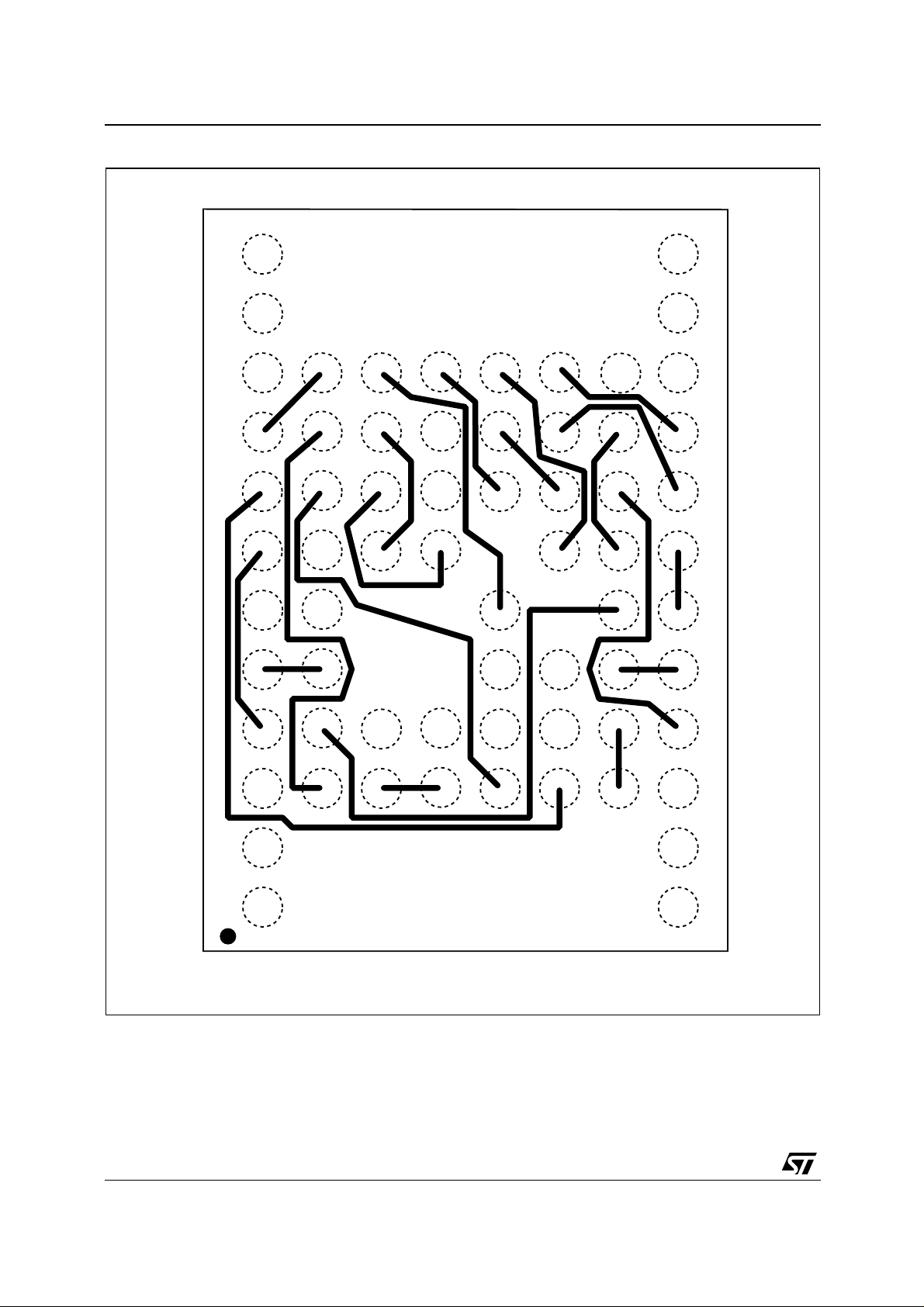

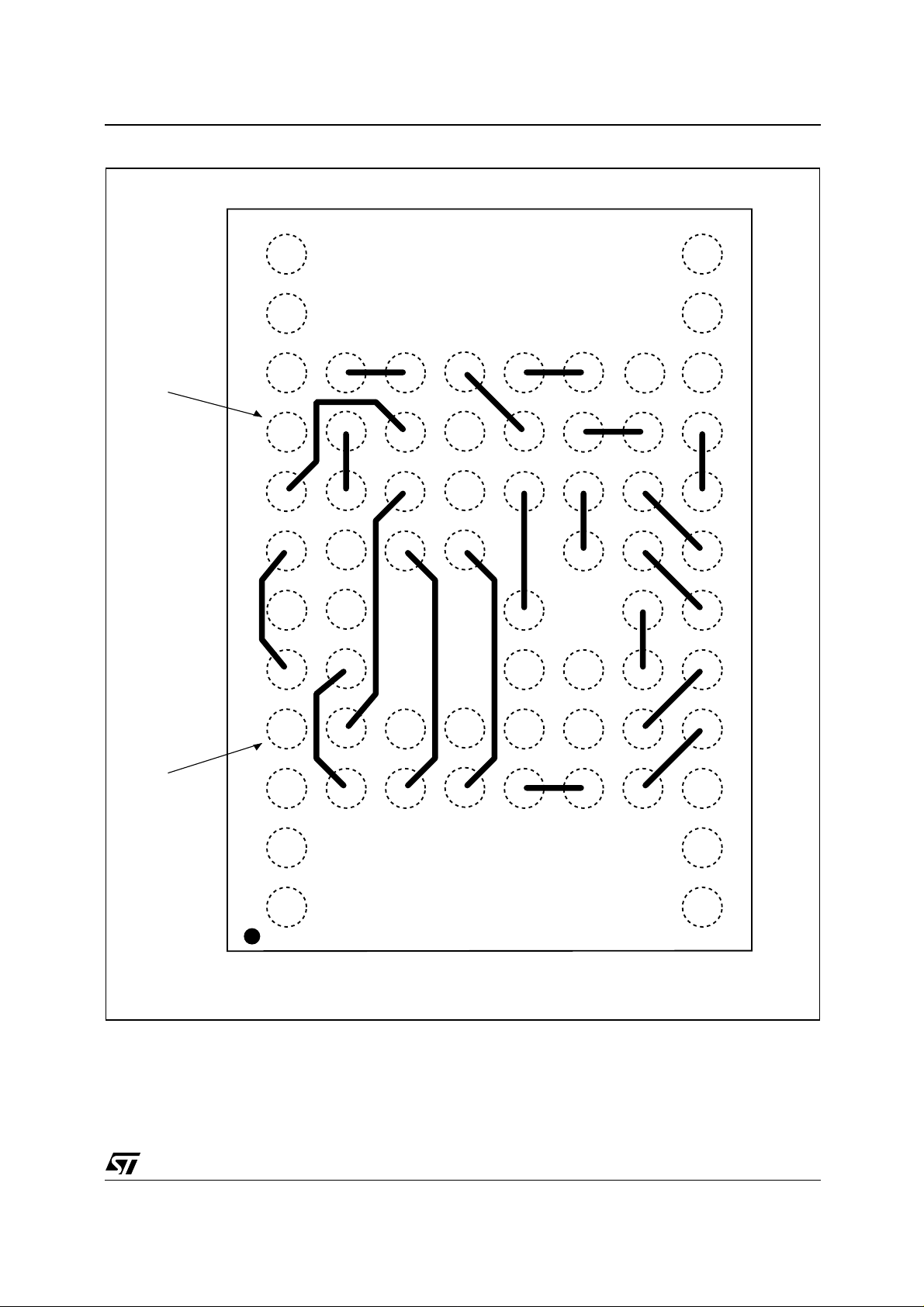

Figure 8. Stacked LFBGA66 Daisy Chain - Package Connections (Top view through package) . . 16

Figure 9. Stac k ed LFBGA6 6 Daisy C hain - PC B Connect ions proposal (Top view through package).17

2/62

M36W416TG, M36W416BG

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 8. Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 9. Daisy Chain Orde r ing Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

FLASH DEVICE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

FLASH SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 10. Flash Block Ad d re sse s . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 11. Flash Security Block and Protection Register Memory Map . . . . . . . . . . . . . . . . . . 20

FLASH BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Read.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 1

Write.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Output Disable.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Automatic Standby.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

FLASH COMMAND INTERFACE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Read Memory Array Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Read Status Register Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Read Electronic Signature Comma nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Read CFI Query Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2

Block Erase Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Program Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Double Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Clear Status Regist e r Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Program/Erase Suspend Comm and . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Program/Eras e Resume Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Protection Regi ste r Pr o g ra m Comman d . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Block Lock Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Block Unlock Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 4

Block Lock-Down Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 10. Flash Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 11. Read Electronic Signature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 12. Read Block Lock Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 13. Read Protection Register and Lock Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 14. Program, Erase Times and Program/E rase Endu ranc e Cycles . . . . . . . . . . . . . . . . 26

FLASH BLOCK LOCKING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

Reading a Block’s Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Locked State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Unlocked State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Lock-Down State. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Locking Operatio n s Durin g Erase Su sp e nd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 15. Block Lock Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

Table 16. Protection Status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

3/62

M36W416TG, M36W416BG

FLASH STATUS REGISTER . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Program/Erase Controller Status (Bit 7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Erase Suspend Status (Bit 6) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

Erase Status (Bit 5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Program Status (Bit 4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

V

Status (Bit 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

PP

Program Suspend Status (Bit 2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Block Protection Status (Bit 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Reserved (Bit 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 0

Table 17. Status Register Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Figure 12. Flash Read Mode AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Table 18. Flash Read AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Figure 13. Flash Write AC Wavefo r ms, Write Enable Control l e d . . . . . . . . . . . . . . . . . . . . . . . 32

Table 19. Flash Write AC Chara cte ristics, Write En a ble Controlled. . . . . . . . . . . . . . . . . . . . . 33

Figure 14. Flash Write AC Waveforms, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . 34

Table 20. Flash Write AC Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . 35

Figu r e 1 5 . Flash Power -Up an d R e set AC W a veforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Table 21. Flash Power-Up and Reset AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

SRAM DEVICE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 7

SRAM SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 16. SRAM Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

SRAM OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 8

Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Standby/Power-Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

Data Retention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Output Disable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 8

Figure 17. SRAM Read Mode AC Waveforms, Address Controlled with UBS = LBS = V

. . . 39

IL

Figure 18. SRAM Read AC Waveforms, GS Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 19. SRAM Standby AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Table 22. SRAM Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

Figure 20. SRAM Write AC Waveforms, WS Controlled. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figu r e 2 1 . SRAM Write A C Wav e forms, E1S Con trolle d . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 22. SRAM Write AC Waveforms, WS Controlled with GS Low . . . . . . . . . . . . . . . . . . . 43

Figure 23. SRAM Write Cycle Waveform, UBS and LBS Controlled, GS Low . . . . . . . . . . . . . 43

Table 23. SRAM Write AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Figure 24. SRAM Low V

Table 24. SRAM Low V

Data Retention AC Waveforms, E1S or UBS / LBS Controlled . . 45

DDS

Data Retention Characte r i stic. . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

DDS

APPENDIX A. BLOCK ADDRESS TABLES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 25. Top Boot Block Addresses, M36W416TG. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Table 26. Botto m Boo t Bl oc k Addre sse s, M36W416BG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4/62

M36W416TG, M36W416BG

APPENDIX B. COMMON FLASH INTERFACE (CFI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Table 27. Query Stru cture Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Table 28. CFI Query Identification String . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .47

Table 29. CFI Query System Interface Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Table 30. Device Geome try Definition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

Table 31. Primary Algorithm-Specific Extended Query Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 32. Security Code Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

APPENDIX C. FLOWCHARTS AND PSEUDO CODES. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 25. Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 26. Double Word Program Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Figure 27. Program Suspend & Resume Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . 54

Figure 28. Erase Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 29. Erase Suspend & Resume Flowchart and Pseudo Code. . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 30. Locking Operations Flowchart and Pseudo Code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

APPENDIX D. COMMAND INTERFACE AND PROGRAM/ERASE CONTROLLER STATE . . . . . . . 59

Table 33. Write State Machine Current/Next, sheet 1 of 2.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 34. Write State Machine Current/Next, sheet 2 of 2.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 35. Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61

5/62

M36W416TG, M36W416BG

SUMMARY DESCRIPTION

The M36W416TG is a low voltage Multiple Memory Product which combines two me mory devices;

a 16 Mbit boot block F lash memory and a 4 Mbit

SRAM. Recommended operating conditions do

not allow both the F lash memory and the S RAM

memory to be active at the same time.

The memory is offered in a Stacked LFBGA66

(12x8mm, 8 x 8 active ball, 0.8 mm pitch) package

and is supplied with all the bits erased (set to ‘1’).

Table 1. Signal Names

A0-A17 Flash and SRAM Address Inputs

A18-A19 Address Inputs for Flash Chip only

DQ0-DQ15 Data Input/Output

V

DDF

V

DDQF

Flash Power Supply

Flash Power Supply for I/O Buffers

Figure 2. Logic Diagram

V

DDQF

V

M36W416TG

M36W416BG

A0-A19

E

G

W

RP

WP

E1

E2

G

W

UB

LB

V

DDF

20

F

F

F

F

F

S

S

S

S

S

S

PPF

V

DDS

16

DQ0-DQ15

V

V

V

V

PPF

SSF

DDS

SSS

Flash Optional Supply V oltage for Fast

Program & Erase

Flash Ground

SRAM Power Supply

SRAM Ground

NC Not Connected Internally

Flash control functions

E

F

G

W

RP

WP

F

F

F

F

Chip Enable input

Output Enable input

Write Enable input

Reset input

Write Protect input

SRAM control functions

, E2

E1

G

W

S

S

S

S

Chip Enable inputs

Output Enable input

Write Enable input

6/62

V

SSF

V

SSS

AI07940

UB

LB

S

S

Upper Byte Enable input

Lower Byte Enable input

Figure 3. LFBGA Connections (Top view through package)

#4#387

NCNC

M36W416TG, M36W416BG

AI90254

NC

NCNCGF

654321#2#1

DDQF

V

SSF

V

A12

A13A11NCNCNC

A15 A14

DQ7

DQ14

WS

DQ15A9A16

A8 A10

DQ5

DQ4

DQ6DQ13NCWF

DDF

V

DDS

V

E2SDQ12V

RPF

SSS

DQ3DQ2

DQ10

DQ11A19WPF

PPF

V

DQ1DQ0

DQ8DQ9GSLBS

UBS

E1SA1

A2A3A6A7A18

A17

SSF

EFA0A4NCNC

A5

NC V

A

B

C

D

E

F

G

H

7/62

M36W416TG, M36W416BG

SIGNAL DESCRIPTION

See Figure 2 Logic Diagram and Table 1, Sign al

Names, for a brief overview of the signals connected to this de vice.

Address Inputs (A0-A17). Addresses A0-A17

are common inputs for the Flash an d the SRAM

components. The Address Inputs select the cells

in the memory array to access during Bu s Read

operations. During Bus Write operations they control the commands sent to the Command Interface

of the internal state machine. The Flash memory is

accessed through the Chip Enable (

Enable (W

) signals, while the SRAM i s acce sse d

F

through two Chip Enable ( ES

(W

) signals.

S

Address Inputs (A18-A19). Addresses A18-A19

are inputs for the Flash component only. The

Flash memory is acc essed through the Chip E n-

E

able (

) and Write Enable (WF) signals

F

Data Inputs/Outputs (DQ0-DQ15). The Data I/

O output the d ata stored at the selected addres s

during a Bus Read operation or in put a c om m and

or the data to be programmed durin g a Write Bus

operation.

E

Flash Chip Enable (

). The Chip Enable input

F

activates the Flash memory control logic, input

buffers, decoders and sense amplifiers. When

Chip Enable is at V

and Reset is at VIH the device

IL

is in active mode. When Chip Enable is at V

memory is deselected, the outputs are high impedance and the power consumption is reduced to the

standby level.

Flash Output Enable (G

). The Output Enable

F

controls the data outputs during the Bus Read operation of the Flash memory.

W

Flash Write Enable (

). The Write Enable con-

F

trols the Bus Write operation of the Flash m emory’s Command Interface. The data and address

inputs are latched on the rising e dge of Chip Enable,

E

, or Write Enable, WF, whichever occurs

F

first .

Flash Write Protect (WP

). Write Protect is an

F

input that gives an additional hardware protection

for each block. When Write Protect is at V

Lock-Down is enabled and the protection status of

the block cannot be changed. When Write Protect

is at V

, the Lock-Down is disabled and the block

IH

can be locked or unlocked. (refer to T able 6, Read

Protection Register and Protection Register Lock).

Flash Reset (RP

). The Reset input provides a

F

hardware reset of the Flash memory. When Reset

is at V

, the memory is in reset mode: the outputs

IL

are high impedance and the current c onsumption

is minimized. After Reset all blocks are in the

Locked state. When Reset is at V

in normal operation. Exiting reset mode the device

enters read array mode, but a negative t ransition

E

) and Write

F

) and Write Enable

the

IH

, the

IL

, the device is

IH

of Chip Enable or a change of the address is required to ensure valid data outputs.

SRAM Chip Enable (E1

, E2S). The Chip En-

S

able inputs activate the SRAM memory control

logic, input buffers and decoders. E1

E2

at VIL deselects the memory and reduces the

S

power consumption to the standby level. E1

can also be used to control writing to the

E2

S

SRAM memory array, while W

is not allowed to set

E2

at VIL at the same time.

S

SRAM Write Enable (W

E

at VIL and, E1S at VIL or

F

S

rema in s at V

S

). The Write Enable in-

at VIH or

S

S

IL.

or

It

put controls writing to the SRA M memory array.

is active low .

W

S

SRAM Output E nable (G

). The Output Enable

S

gates the outputs through the data buffers during

a read operation of the SRAM m emory. G

is ac-

S

tive low.

SRAM Upper Byte Enable (UB

). The Upper

S

Byte Enable enables the upper bytes for SRAM

(DQ8-DQ15). UB

SRAM Lower Byte Enable (LB

is acti v e low.

S

). The Lower

S

Byte Enable enables the lower bytes for SRAM

(DQ0-DQ7). LB

and V

V

DDF

is active low.

S

Supply Voltages. V

DDS

DDF

provides the power supply to the internal core of the

Flash Memory device. It is the main power s upply

for all operations (Read, Program and Erase).

and V

V

DDQF

provides the power supply for the Flash

V

DDQF

memory I/O pins and V

Supply Voltage (2.7V to 3.3V).

DDS

provides the power

DDS

supply for t he SRAM control pins. This a llows all

Outputs to be powered independently of the Flash

core power supply, V

V

DDS.

V

Program Supp ly Vol tage. V

PPF

DDF

. V

can be tied to

DDQF

PPF

is both a

control input and a power suppl y pin for t he F lash

memory. The two functions are selected by the

voltage range applied to the pin. The Supply Voltage V

and the Program Supply Vol tage V

DDF

PPF

can be applied in any order.

If V

V

age lower than V

against program or erase, while V

is kept in a low voltage range (0V t o 3.6V)

PPF

is seen as a control input. In this case a volt-

PPF

gives an absolute protection

PPLK

PPF

> V

PP1

enables these functions (see Table 6, DC Characteristics for the relevant values). V

is only

PPF

sampled at the beginning of a program or erase; a

change in its value after the operation has started

does not have any effect and program or erase operations continue.

If V

power supply pin. In this condition V

is in the range 11.4V to 12.6V it acts as a

PPF

PPF

must be

stable until the Program/Erase algorithm i s completed (see Table 19 and 20).

8/62

M36W416TG, M36W416BG

V

SSF

and V

Ground. V

SSS

SSF

and V

SSS

are the

ground reference for all voltage measurements in

the Flash and SRAM chips, respectively.

Note: Each device in a system should have V

DF

, V

DDQF

and V

decoupled with a 0.1µF ca-

PPF

D-

FUNCTIONAL DESCRIPTION

The Flash and SRAM components have separate

power supplies and grounds and are distinguished

E

by three chip enable inputs:

ory and E1

and E2S for the SRAM.

S

for the Flash mem-

F

Recommended operating conditions do not allow

both the Flash and the SRAM to be in active mode

at the same time. The most common example is

Figure 4. Func ti onal Block Di a gram

V

DDF

E

F

G

F

W

F

RP

WP

F

F

Flash Memory

16 Mbit (x16)

pacitor close to the pin. See Figure 9, AC

Measurement Load Circuit. The PCB trace

widths should be sufficient to carry the required V

program and erase currents.

PPF

simultaneous read operations on the Flash and

the SRAM which would resul t in a data bus contention. Therefore it is recommended to put the

SRAM in the h igh impedance state whe n reading

the Flash and vice versa (see Table 2 Main Operation Modes for details).

V

DDQF

V

PPF

A18-A19

A0-A17

E1

E2

G

W

UB

LB

V

V

DDS

S

S

S

S

S

S

SRAM

4 Mbit (x16)

V

SSS

SSF

DQ0-DQ15

AI07941

9/62

M36W416TG, M36W416BG

Table 2. Main Operation Modes

Operation

Mode

Read

Write

Block

Locking

Standby

Flash Memory

Reset X X X

Output

Disable

E

FGFWF

V

ILVILVIHVIH

V

ILVIHVILVIH

V

XX

IL

V

XX

IH

V

ILVIHVIHVIH

Flash must be disabled

Read

Flash must be disabled

Flash must be disabled

Flash must be disabled

Write

Flash must be disabled

Flash must be disabled

Standby/

Power

SRAM

Down

Data

Retention

Any Flash mode is allowable

Any Flash mode is allowable

Any Flash mode is allowable

Output

Disable

Any Flash mode is allowable

Any Flash mode is allowable

Note: X = Don’t care = VIL or VIH, V

RPFWP

V

IH

V

IH

V

IL

= 12V ± 5%.

PPFH

V

F

PPF

E1SE2SGSWSUBSLB

DQ7-DQ0 DQ15-DQ8

S

X Don’t care SRAM must be disabled Data Output

V

or

X

V

DDF

V

PPFH

Don’t care SRAM must be disabled X

IL

SRAM must be disabled Data Input

X Don’t care Any SRAM mode is allowed Hi-Z

X Don’t care Any SRAM mode is allowed Hi-Z

X Don’t care Any SRAM mode is allowed Hi-Z

V

ILVIHVILVIHVIL

V

ILVIHVILVIHVIHVIL

V

ILVIHVILVIHVIL

V

ILVIH

V

ILVIH

V

ILVIH

V

IHVIL

XVILV

XVILV

XVILV

X X X X Hi-Z

XXXX

V

IHVIL

X X X X Hi-Z

XXXX

V

ILVIHVIHVIHVIL

V

ILVIHVIHVIHVIHVIL

V

ILVIHVIHVIHVIL

IL

IHVIL

IL

V

IHVIH

V

IHVIH

V

Data out Word Read

IL

Data out Hi-Z

V

V

Hi-Z Data out

IH

Data in Word Write

IL

Data in Hi-Z

V

V

V

Hi-Z Data in

IH

IL

IH

Hi-Z

Hi-Z

Hi-Z

Hi-Z

Hi-Z

10/62

MAXIMUM RATIN G

Stressing the device above the rating l isted in the

Absolute Maximum Ratings table m ay cause permanent damage to the device. These are stress

ratings only and operation of the device at t hese or

any other conditions ab ove those i ndicated in t he

Operating sections of this specificat ion is not im-

Table 3. Absolute Maximum Ratings

Symbol Parameter

T

A

T

BIAS

T

STG

V

IO

V

, V

DDF

DDQF

V

PPF

V

DDS

Note: 1. Depends on range.

Ambient Operating Temperature

Temperature Under Bias –40 125 °C

Storage Temperature –55 150 °C

Input or Output Voltage –0.5

Flash Supply Voltage –0.5 3.8 V

Program Voltage –0.6 13 V

SRAM Supply Voltage –0.5 3.8 V

(1)

M36W416TG, M36W416BG

plied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device

reliability. Refer also to the STMicroelectronics

SURE Program and other relevant quality documents.

Value

Min Max

–40 85 °C

V

+0.3

DDQF

Unit

V

11/62

M36W416TG, M36W416BG

DC AND AC PARAMETERS

This section summarizes the operat ing and measurement conditions, and the DC and AC characteristics of the device. The parameters in the DC

and AC characteristics Tables that follow, are derived from tests performed under the Measure-

Table 4. Operating and AC Measurement Conditions

ment Conditions summarized in Table 4,

Operating and AC Measurem ent Conditions. Designers should check that the operating conditions

in their circuit match the measurement conditions

when relying on the quoted parameters.

SRAM Flash Memory

Parameter

Min Max Min Max

V

Supply Voltage

DDF

= V

V

DDQF

DDS

Supply Voltage

– – 2.7 3.3 V

2.7 3.3 2.7 3.3 V

Ambient Operating Temperature – 40 85 – 40 85 °C

Load Capacitance (C

)

L

30 50 pF

Input Rise and Fall Times 1V/ns 5ns

Input Pulse Voltages

Input and Output Timing Ref. Voltages

Figure 5. AC Measurement I/O Waveform

V

DDQ

V

0V

AI90258

Note: V

DDQ

means V

DDQF

= V

DDS

DDQ

0 to V

DDQF

V

/2 V

DDQF

Figure 6. AC Me asureme nt Load Circuit

/2

V

DDQF

V

DDF

0 to V

DEVICE

UNDER

TEST

DDQF

DDQF

/2

V

DDQF

25kΩ

Units70 70/85

V

V

0.1µF

0.1µF

CL includes JIG capacitance

C

Table 5. Device Capacitance

Symbol Parameter Test Condition Typ Max Unit

V

C

IN

C

OUT

Note: Sampled o nl y, not 100% test ed.

Input Capacitance

Output Capacitance

12/62

= 0V, f=1 MHz

IN

V

= 0V, f=1 MHz

OUT

12 pF

15 pF

L

25kΩ

AI90259

M36W416TG, M36W416BG

Table 6. DC Characteristics

Symbol Parameter Device Test Condition Min Typ Max Unit

I

LI

I

LO

I

DDSVDD

I

DDD

I

DD

I

DDR

I

DDW

I

DDE

I

DDES

I

PP1

Input Leakage Current Flash & SRAM

Flash

Output Leakage Current

SRAM

Flash

Standby Current

SRAM

Supply Current (Reset) Flash

Supply Current SRAM

Supply Current (Read) Flash

Supply Current (Program)

Flash

Supply Current (Erase) Flash

Supply Current

(Program/Erase Suspend)

Program Current

(Read or Standby)

Flash

Flash

0V≤ V

0V≤V

0V ≤V

SRAM Outputs Hi-Z

E

= V

F

RP

F

E1

S

V

V

≥

IN

f = fmax (A0-A17 and DQ0-

DQ15 only)

f = 0 (G

S

E1

S

V

≥

IN

V

IN

RP

F

f = fmax = 1/

0.2V, I

V

≤

IN

0.2V, I

≤

V

IN

E

= VIL, G

F

Program in progress

V

PPF

Program in progress

V

Erase in progress

V

PPF

Erase in progress

V

EF = V

Erase suspended

V

V

≤

IN

DDQF

V

≤

OUT

DDQF

V

≤

OUT

DDQF,

± 0.2V

DDQF

= V

DDQ

V

≥

DDS

– 0.2V or V

DDS

0.2V

≤

± 0.2V

– 0.2V

IN

, WS, UBS and LBS)

V

≥

– 0.2V

DDS

V

– 0.2V or

DDS

0.2V, f = 0

≤

= V

SSF

OUT

± 0.2V

AVAV

= 0 mA

,

f = 1MHz,

= 0 mA

OUT

=

V

F

f = 5 MHz

IH,

= 12V ± 5%

= V

PPF

DDF

= 12V ± 5%

= V

PPF

DDF

± 0.2V,

DDQF

> V

PPF

DDF

±1 µA

±10 µA

±1 µA

15 50 µA

715µA

715µA

15 50 µA

5.5 12 mA

1.5 3 mA

10 20 mA

10 20 mA

10 20 mA

520mA

520mA

50 µA

400 µA

I

PP2

I

PPR

I

PPW

Program Current

(Read or Standby)

Flash

Program Current (Reset) Flash

Program Current

(Program)

Flash

V

V

≤

PPF

DDF

RP

= V

F

V

PPF

± 0.2V

SSF

= 12V ± 0.5V

Program in progress

V

= V

PPF

DDF

Program in progress

5µA

5µA

10 mA

5mA

13/62

M36W416TG, M36W416BG

Symbol Parameter Device Test Condition Min Typ Max Unit

V

= 12V ± 0.5V

I

PPE

Program Current (Erase) Flash

PPF

Erase in progress

V

= V

PPF

DDF

Erase in progress

10 mA

5µA

V

IL

V

IH

V

OL

V

OH

V

PP1

V

PPFH

V

PPLK

V

LKO

Input Low Voltage Flash & SRAM

Input High Voltage Flash & SRAM

Output Low Voltage Flash & SRAM

Output High Voltage Flash & SRAM

Program Voltage

(Program or Erase

Flash 1.65 3. 6 V

operations)

Program Voltage

(Program or Erase

Flash 11.4 12 .6 V

operations)

Program Voltage

(Program and Erase lock-

Flash 1 V

out)

V

Supply Voltage

DDF

(Program and Erase lock-

Flash 2 V

out)

V

DDQF

V

DDQF

V

DDQF

V

DDQF

= V

I

= V

I

OH

= V

= V

OL

≥

DDS

≥

DDS

= VDDmin

DDS

= 100µA

= VDDmin

DDS

= –100µA

2.7V

2.7V

–0.3 0.8 V

V

DDQF

0.7

V

+0.3

DDQF

0.1 V

V

DDQ

–0.1

V

V

14/62

M36W416TG, M36W416BG

PACKAGE MECHANICAL

Figure 7. Stacked LFBGA66-12x8mm, 8x8 ball arra y, 0.8mm pitch, Bottom View Package Outline

D

D2

D1

E

E1

Note: Drawing is not to scale.

SE

BALL "A1"

A

FDFE

SD

e

b

e

ddd

A2

A1

BGA-Z12

Table 7. Stacked LFBGA66 - 12x8mm, 8x8 ball array, 0.8 mm pitch, Pack age Mechanical Data

Symbol

Typ Min Max Typ Min Max

A 1.400 0.0551

A1 0.300 0.0118

A2 1.100 0.0433

b 0 .400 0.300 0.500 0.0157 0.0118 0.0197

D 12.000 – – 0.47 24 – –

D1 5.600 – – 0.2205 – –

D2 8.800 – – 0.3465 – –

ddd 0.100 0.0039

E 8.000 – – 0.3150 – –

E1 5.600 – – 0.22 05 – –

e 0 .800 – – 0.0315 – –

FD 1.600 – – 0.0630 – –

FE 1.200 – – 0.0472 – –

SD 0 .400 – – 0.0157 – –

SE 0.400 – – 0.0157 – –

millimeters inches

15/62

M36W416TG, M36W416BG

Figure 8. Stacked LFBGA66 Daisy Chain - Package Connections (Top view through package)

AI90273

#4#3

8761

5

4

32#1 #2

A

B

C

D

E

F

G

H

16/62

M36W416TG, M36W416BG

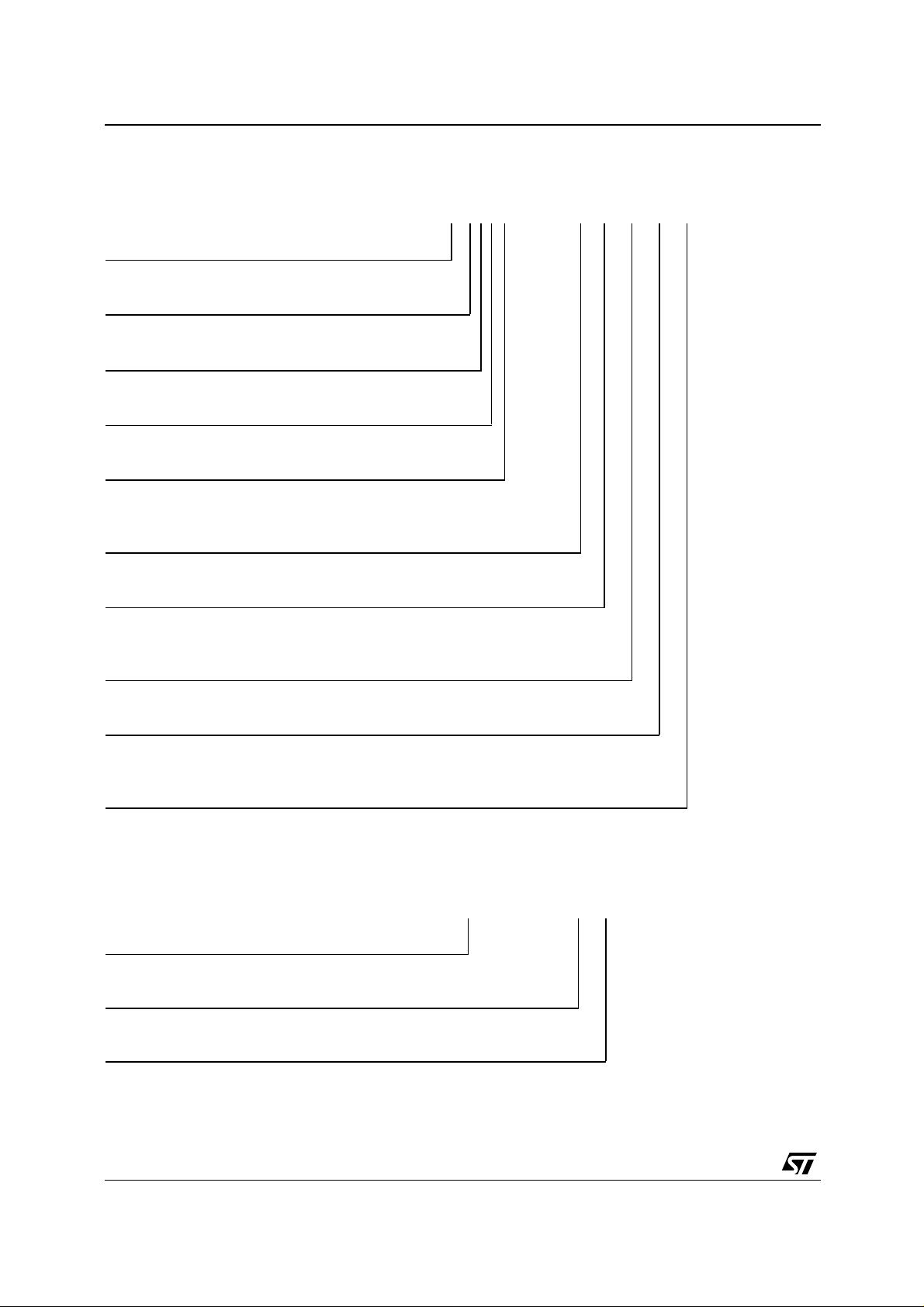

Figure 9. Stacked LFBGA66 Daisy Chain - PCB Connections proposal (Top view through package)

#4#3

AI90274

END

POINT

POINT

START

87615

4

32#2

#1

A

B

C

D

E

F

G

H

17/62

M36W416TG, M36W416BG

PART NUMBERING

Table 8. Ordering Information Scheme

Example: M36W416 T G 70 ZA 6 T

Device Type

M36 = MMP (Flash + SRAM)

Operating Voltage

W = V

SRAM Chip Size & Organization

4 = 4 Mbit (256Kb x 16 bit)

Flash Chip Size & Organization

16 = 16 Mbit (x16), Boot Block

Array Matrix

T = Top Boot

B = Bottom Boot

SRAM Component

G = 4Mb, 0.16µm, 70ns, 3V

= 2.7V to 3.3V, V

DDF

DDS

= V

= 2.7V to 3.3V

DDQF

Speed

70 = 70ns

85 = 85ns

Package

ZA = LFBGA66: 12x8mm, 0.8mm pitch

Temperature Range

1 = 0 to 70°C

6 = –40 to 85°C

Option

T = Tape & Reel packing

Devices are shipped from the factory with the memory content bits erased to ’1’.

Table 9. Daisy Chain Ordering Scheme

Example: M36W416TG -ZA T

Device Type

M36W416TG

Daisy Chain

-ZA = LFBGA66: 12x8mm, 0.8mm pitch

Option

T = Tape & Reel Packing

For a list of available options (Speed, Package, etc.) or for further information on any aspect of this device,

please contact the STMicroelectronics Sales Office nearest to you.

18/62

FLASH DEVICE

The M36W416TG contains one 16 Mbit Flash

memory. This section describes how to use the

FLASH SUMMARY DESCRIPTION

The Flash Memory is a 16 Mb it (1 Mb it x 16) nonvolatile device that can be erased electrically at

the block level and prog rammed in-system on a

Word-by-Word basis. These operations can be

performed using a single low voltage (2.7 to 3.6V)

supply. V

1.65V. An optional 12V V

vided to speed up customer programming.

The device features an asymmetrical blocked architecture with an array of 39 blocks: 8 Parameter

Blocks of 4 KWords and 31 Main Blocks of 32

KWords. The M36W416TG has the Parameter

Blocks at the top of the memory address space

while the M36W416BG locates the Parameter

Blocks starting from the bottom. The memory

maps are shown in Figure 10, Block Addresses.

The Flash Memory features an instant, individual

block locking scheme that allows any block to be

locked or unlocked with no latency, enabling instant code and data protection. All blocks have

three levels of protection. They can be locked and

locked-down individually preventing any accidental programming or erasure. There is an additional

hardware protection against program and erase.

When V

against program or erase. All blocks are locked at

Power Up.

is used to drive the I/O pin down to

DDQF

PPF

≤ V

PPLK

power supply is pro-

PPF

all blocks are protected

M36W416TG, M36W416BG

Flash device and all signals refer to the Flash device .

Each block can be erased separately. Erase can

be suspended in order to perform either read or

program in any other block and then resumed.

Program can be suspended to read data in any

other block and then resumed. Each block can be

programmed and erased over 100,000 cycles.

The device includes a 128 b it Protection Register

and a Security Block to increase the protection of

a system design. The Protection Register is divided into two 64 bit segments, the first one contains

a unique device number written by ST, while the

second one is one-time-programmable by the user. The user programmable segm ent can be permanently protected. The Security Block,

parameter block 0, can be permanentl y protected

by the user. Figure 11, shows the Flash Security

Block Memory Map.

Program and Erase command s are written to the

Command Interface of the memory. An on-chip

Program/Erase Controller takes care of the timings necessary for program and erase operations.

The end of a program or erase operation can be

detected and any error conditions identified. The

command set required to control the memory is

consistent with JEDEC standards.

19/62

Loading...

Loading...