256x 256 DIGITALSWITCHING MATRIX

.256 INPUT AND 256 OUTPUT CHANNEL

CMOS DIGITAL SWITCHING MATRIX COMPATIBLEWITHM088

.BUILDING BLOCK DESIGNED FOR LARGE

CAPACITYELECTRONICEXCHANGES,SUBSYSTEMSAND PABX

.NO EXTRA PIN NEEDED FOR NOT-BLOCK-

INGSINGLESTAGEAND HIGHERCAPACITY

SYNTHESIS BLOCKS(512 or 1024 channels)

.EUROPEAN TELEPHONE STANDARD COM-

PATIBLE(32serialchannelsperframe)

.PCM INPUTS AND OUTPUTS MUTUALLY

COMPATIBLE

.ACTUAL INPUT-OUTPUT CHANNEL CON-

NECTIONS STORED AND MODIFIED VIA AN

ON CHIP 8-BIT PARALLEL MICROPROCESSORINTERFACE

.TYPICALBITRATE : 2Mbit/s

.TYPICAL SYNCHRONIZATION RATE : 8KHz

(timeframe is 125µs)

.5VP0WER SUPPLY

.CMOS & TTL INPUT/OUTPUT LEVELS COM-

PATIBLE

.HIGH DENSITY ADVANCED 1.2µmHCMOS3

PROCESS

M3488

PRELIMINARY DATA

DIP40 PQFP44

ORDERING NUMBERS:

M3488B1 M3488Q1

Main instructionscontrolledby the microprocessor interface

.CHANNELCONNECTION/DISCONNECTION

.OUTPUT CHANNEL DISCONNECTION

.INSERTION OF A BYTE ON A PCM OUTPUT

CHANNEL/DISCONNECTION

.TRANSFERTO THE MICROPROCESSOROF

A SINGLEPCM OUTPUT CHANNELSAMPLE

.TRANSFERTO THE MICROPROCESSOROF

A SINGLE OUTPUT CHANNEL CONTROL

WORD

.TRANSFERTO THE MICROPROCESSOROF

A SELECTED0CHANNEL PCM INPUT DATA

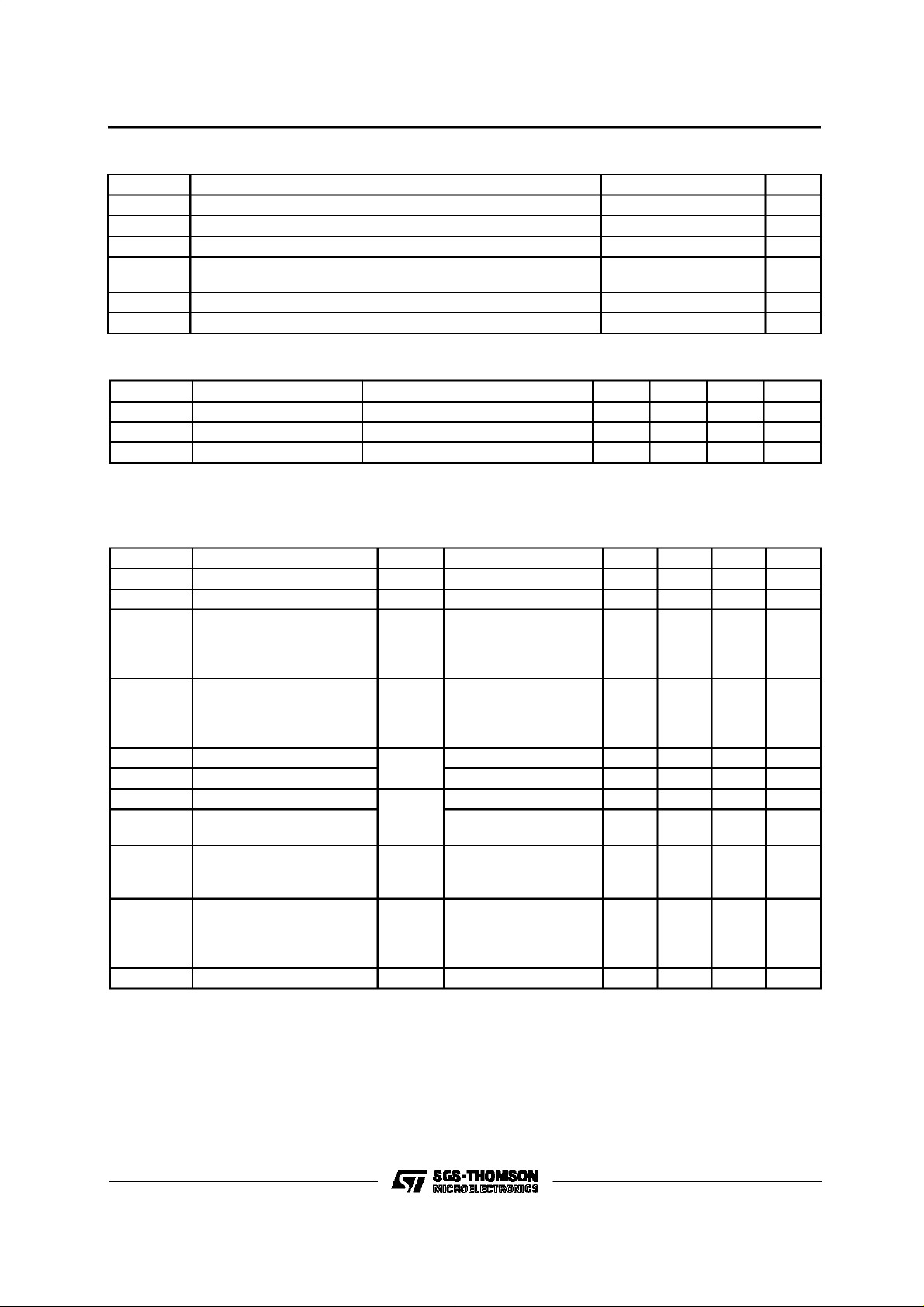

ABSOLUTE MAXI M UM RATI NG S

Symbol Parameter Test Conditions Unit

V

CC

V

V

I

O

P

T

stg

T

Str esses above t hose li st ed under ” Absolute Maximum Rati ngs” may cause per manent damage to the devi ce. This is a st r ess

rati ngs only and funct i onal operati on of the device at these or any other c ondit i ons above t hose ind icated in the operat i ng condition s of this specifi cation is not i mplied. Exposure to absolute maximum rati n g conditions for extended periods may affect device

reliability.

November 1994

This isadvanced informationon a newproduct now in development or undergoing evaluation. Details are subject to changewithout notice.

Supply Voltage -0.3 to 7 V

Input Voltage -0.3 to VCC+0.3 V

I

Off State Output Voltage -0.3 to VCC+0.3 V

O

Current at Digital Outputs 30 mA

Total Package Power Dissipation 1.5 W

tot

Storage Temperature Range -65 to 150 °C

Operating Temperature Range 0 to 70 °C

op

1/18

M348 8

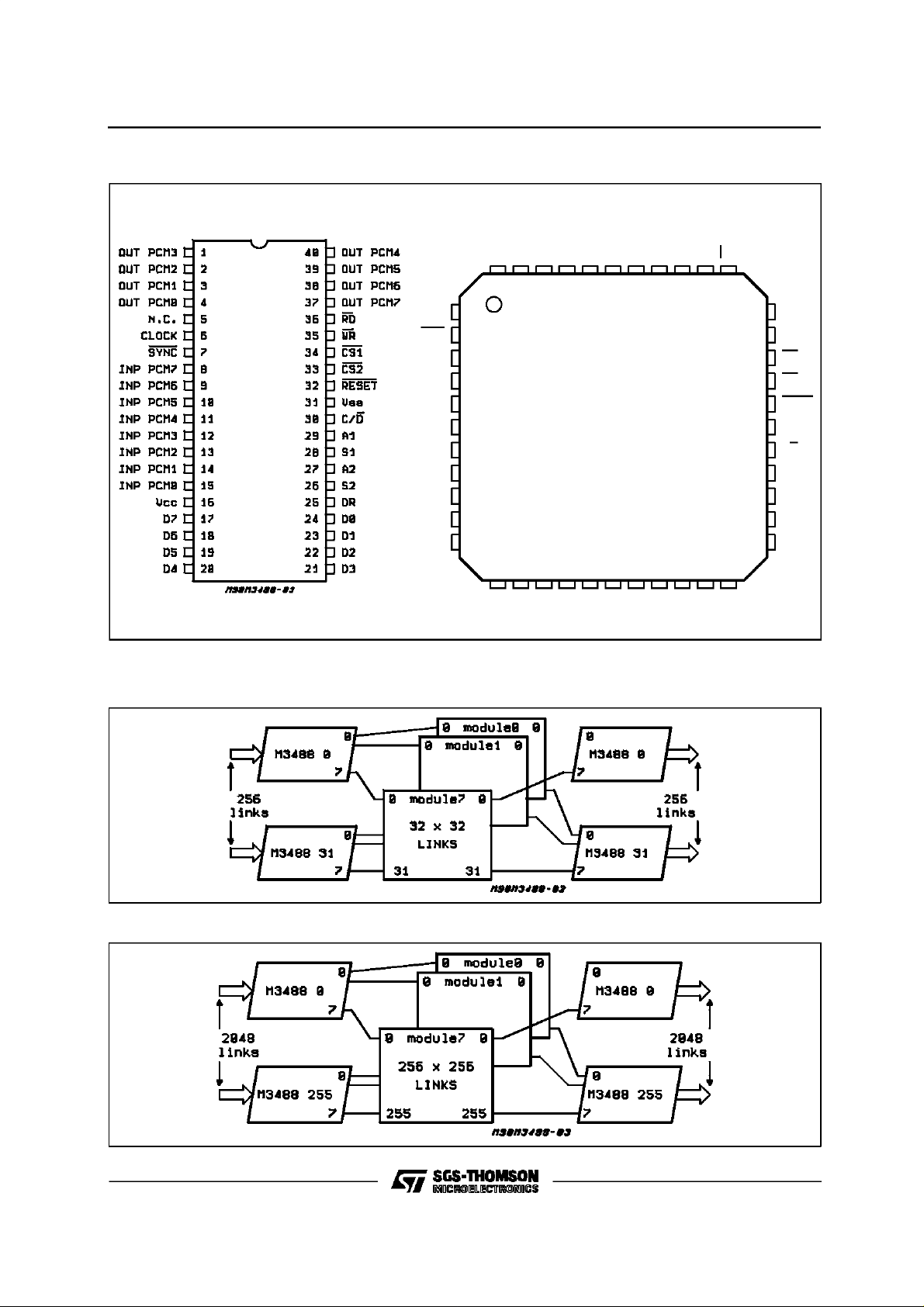

PIN CO NNE CTI O NS (Top views)

N.C.

44 43 42 41 3940 38 37 36 35 34

OUT PCM0

OUT PCM1

OUT PCM2

OUT PCM3

N.C.

OUT PCM4

OUT PCM7

OUT PCM6

OUT PCM5

RD

1

2

3

4

5

D6

PQFP44

171118 19 20 21 22

D5

D4

D3

N.C.

D2

D1

D0

6

7

8

9

10

V

CC

12 13 14 15 16

D7

N.C.

DIP40

CLOCK

SYNC

INP PCM7

INP PCM6

INP PCM5

INP PCM4

INP PCM3

INP PCM2

INP PCM1

INP PCM0

EXCHANGE NE TWORKS AP PLICATI O NS

256PCMlinks network (160or 192 DSM) : the 32 x 32 linkmoduleshown on the next page.

DR

33

32

31

30

29

28

27

26

25

24

23

D93TL040A

N.C.

WR

CS1

CS2

RESET

V

SS

C/D

A1

S1

A2

S2

2048PCM linksnetwork(1792or 2048 DSM) : the 256 x 256 link networkisshown above.

2/18

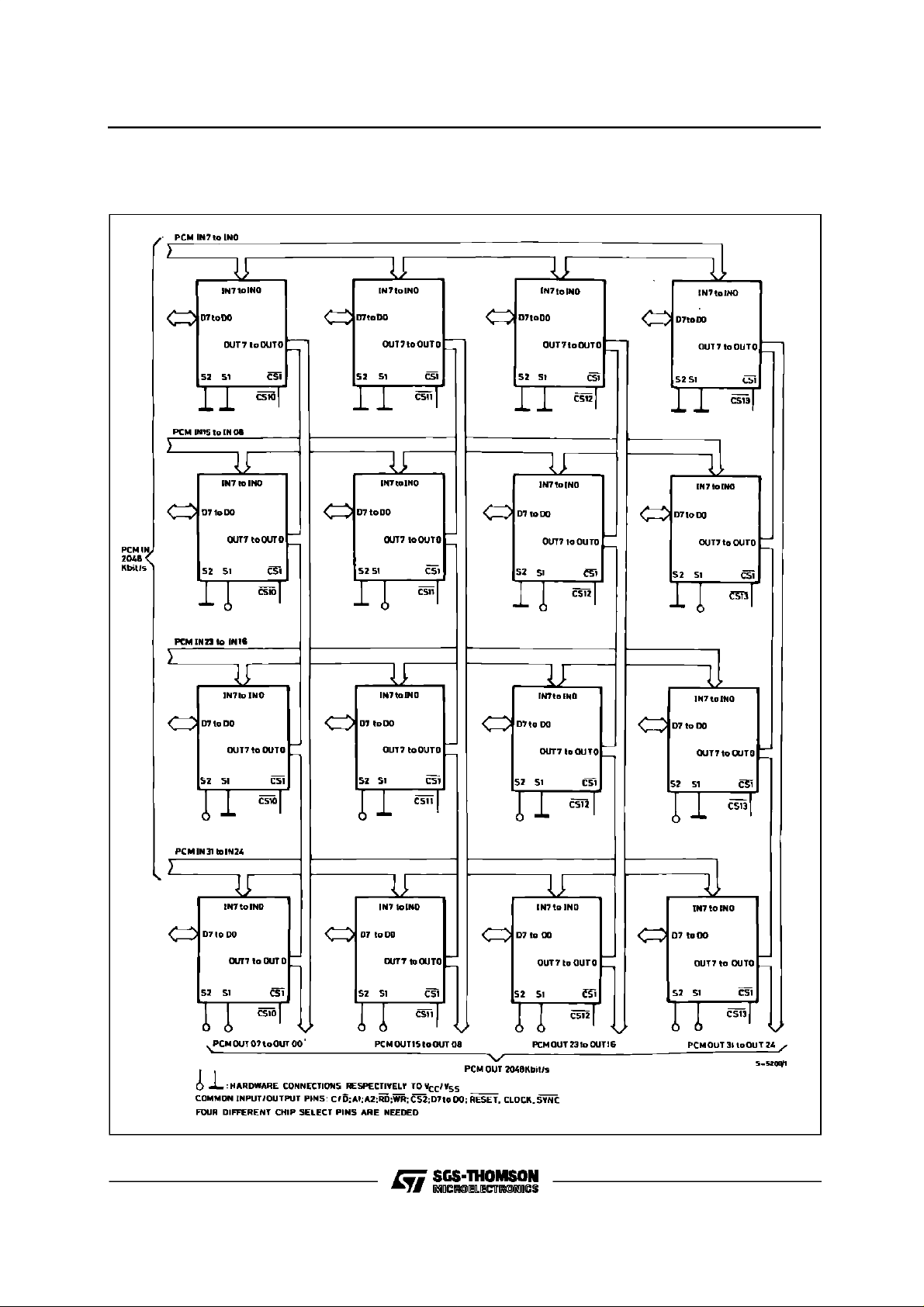

EXCHANGE NET WORKS APPLICAT IO NS (continued)

SingleStage/SixteenDevices Configuration(32 by 32 links or 1024channels).

M3488

3/18

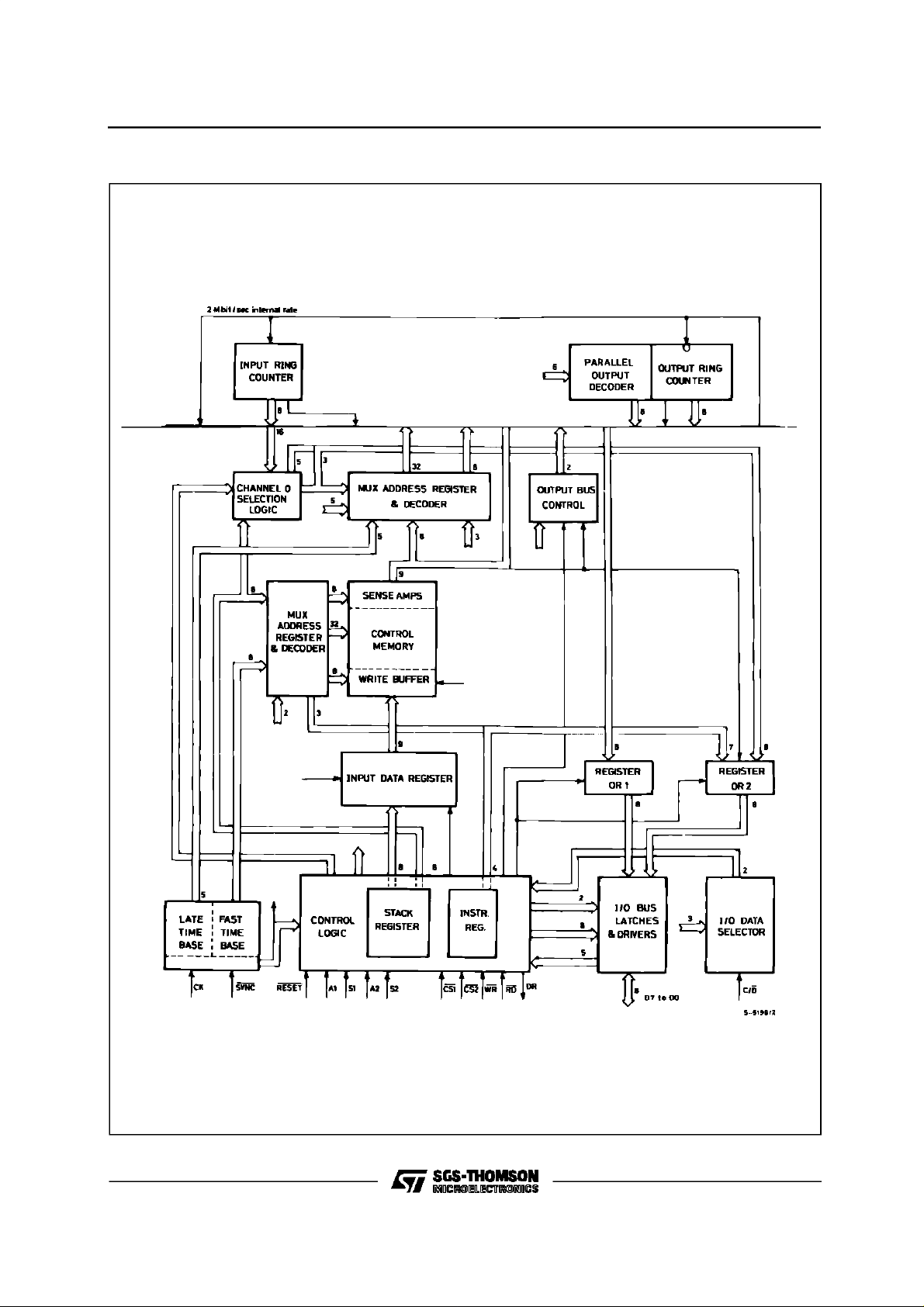

M348 8

BLOCK DIAGRAM

4/18

M3488

RECOMMENDEDOPERATING CONDITIONS

Symbol Parameter Value Unit

V

CC

V

V

O

CLOCK

Freq.

SYNC Freq. Input Synchronization Frequency 8 KHz

T

op

CAPACITANCES (measurement freq. = 1MHz; Top= 0 to 70°C; unused pins tied to VSS)

Symbol Parameter Pins (*) Min. Typ. Max. Unit

C

C

I/O

C

Supply Voltage 4.75 to 5.25 V

Input Voltage 0 to 5.25 V

i

Off State Input Voltage 0 to 5.25 V

Input Clock Frequency

4.096 MHz

Operating Temperature 0 to 70 °C

Input Capacitance 6 to 15; 26 to 30; 32 to 36 5 pF

I

I/O Capacitance 20 to 24 15 pF

O

Output Capacitance 1 to 4; 17 to 19; 25; 37 to 40 10 pF

D.C. ELECTRICAL CHARACTERISTICS (T

All D.C. characteristics are valid 250µs after V

= 0 to 70°C, VCC=5V±5%)

amb

and clock have been applied.

CC

Symbol Parameter Pins (*) Test Condition Min. Typ. Max. Unit

V

ILC

V

IHC

V

IL

Clock Input Low Level 6 -0.3 0.8 V

Clock Input High Level 6 2.4 V

Input Low Level 7 to 15

-0.3 0.8 V

CC

20 to 24

26 to 30

32 to 36

V

IH

Input High Level 7 to 15

2V

CC

20 to 24

26 to 30

32 to 36

V

OH

I

OH

V

OL

I

OL

I

IL

Output High Voltage (Level)

17 to 25

Output High Current VOH= 2.4V 5 mA

Output Low Voltage (Level) 1 to 4

Output Low Current VOL= 0.4V 5 mA

37 to 40

17 to 25

Input Leakage Current 6 to 15

IOH= 5mA 2.4 V

IOL= 5mA 0.4 V

VIN= 0 to V

CC

5 µA

26 to 30

32 to 36

I

DL

Data Bus Leakage Current 17 to 24 VIN= 0 to V

CC

±5 µA

VCCapplied; Pins 35

and 36 tied to V

CC

,

after Device Initialization

I

CC

Supply Current 16 Clock Freq. = 4.096MHz 15 30 mA

V

V

(*) T he pin number is r ef erred to the D I P40 version.

5/18

M348 8

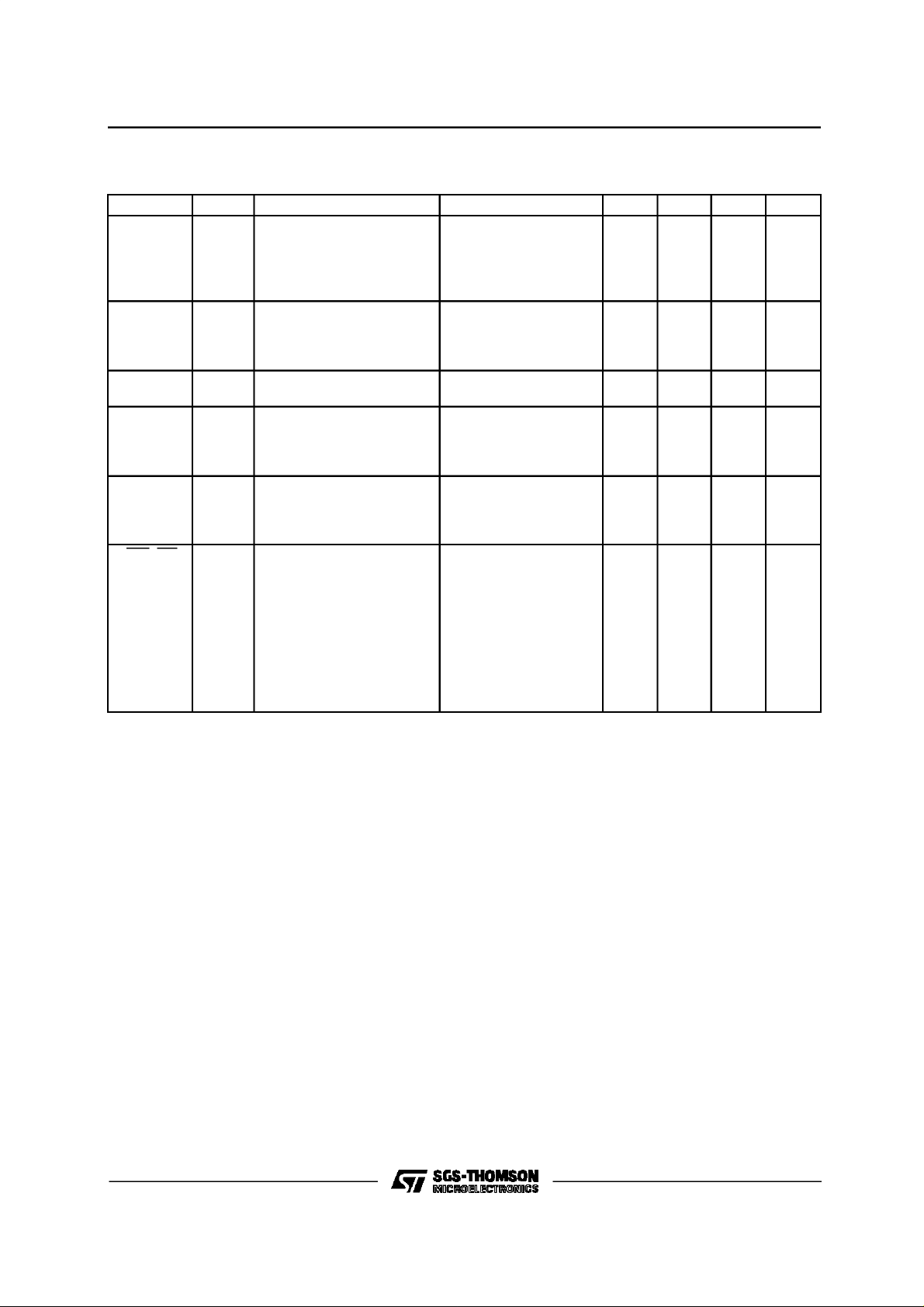

A.C. ELECTRICAL CHARACTERISTICS (T

AllA.C. characteristi c sare valid250µs afterV

= 0 to 70°C, VCC=5V±5%)

amb

andclockhavebeenapplied.CListhe max. capacitiveload.

CC

Signal Symbol Parameter Test Condition Min. Typ. Max. Unit

CK (clock) t

SYNC

(framepulse)

PCM Input

Busses

PCM Output

Busses

Open Drain

CK

t

WL

t

WH

t

R

t

F

t

SL

t

HL

t

SH

t

WH

t

S

t

H

t

PD min

t

PD max

Clock Period

Clock Low Level Width

Clock High Level Width

Rise Time

Fall Time

Low Level Setup Time

Low Level Hold Time

High Level Setup Time

High Level Width

Setup Time

Hold Time

Propagation time

referred to CK low level

Propagation time

C

L

R

= 150pF

=1K

L

230

244

100

100

60

30

80

t

CK

5

+40

45 110

110 140

25

25

referred to CK high level

RESET t

WR, RD t

t

t

t

t

t

t

Low Level Setup Time

SL

t

Low Level Hold Time

HL

High Level Setup Time

SH

High level Width

WH

Low Lvel Width

WL

High Level Width

WH

Repetition Interval

REP

between Active Pulses

High Level Setup Time

SH

to Active Read Strobe

High Level Hold Time

HH

40 + 2 tCK+t

t

REP

+t

WL(CK)

R(CK)

+

60

30

80

t

CK

100

t

CK

see

formula

0

15

from Active Write Strobe

t

R

t

F

Rise Time

Fall Time

60

60

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

6/18

Loading...

Loading...