SGS Thomson Microelectronics M29W800T, M29W800B Datasheet

8 Mbit (1Mb x8 or 512Kb x16, Boot Block)

Low Voltage Single Supply Flash Memory

M29W800T and M29W800B are replaced

respectivelyby the M29W800AT and

M29W800AB

2.7V to 3.6VSUPPLYVOLTAGEfor

PROGRAM,ERASEand READ OPERATIONS

FASTACCESS TIME: 90ns

FASTPROGRAMMING TIME

–10µsby Byte / 20µs by Word typical

PROGRAM/ERASECONTROLLER(P/E.C.)

– Program Byte-by-Byteor Word-by-Word

– StatusRegisterbits and Ready/BusyOutput

MEMORYBLOCKS

– Boot Block (Topor Bottom location)

– Parameterand Main blocks

BLOCK, MULTI-BLOCKand CHIPERASE

MULTIBLOCKPROTECTION/TEMPORARY

UNPROTECTIONMODES

ERASESUSPEND and RESUMEMODES

– Read and ProgramanotherBlockduring

Erase Suspend

LOW POWER CONSUMPTION

– Stand-byand AutomaticStand-by

100,000 PROGRAM/ERASECYCLES per

BLOCK

20 YEARSDATARETENTION

– Defectivity below 1ppm/year

ELECTRONICSIGNATURE

– ManufacturerCode: 0020h

– Device Code, M29W800T:00D7h

– Device Code, M29W800B:005Bh

DESCRIPTION

The M29W800 is a non-volatilememory that may

beerasedelectricallyat theblock or chipleveland

programmedin-systemonaByte-by-Byteor Wordby-Wordbasisusingonly a single2.7V to 3.6V V

supply. For Program and Erase operations the

necessary high voltages are generated internally.

The device can also be programmed in standard

programmers.

Thearraymatrixorganisationallowseach block to

be erased and reprogrammed without affecting

otherblocks.Blockscan be protectedagainst programing and erase on programming equipment,

CC

12 x 20 mm

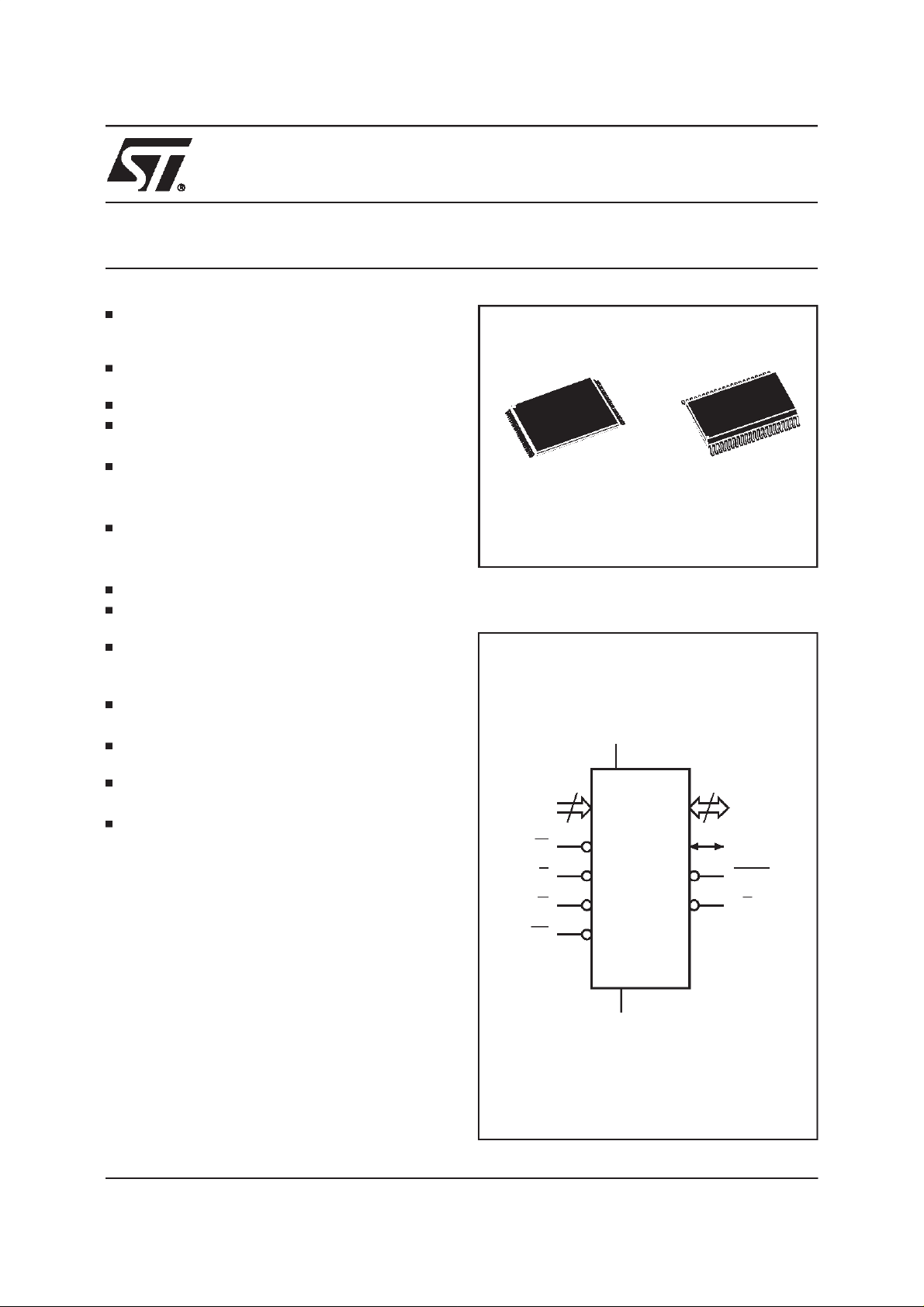

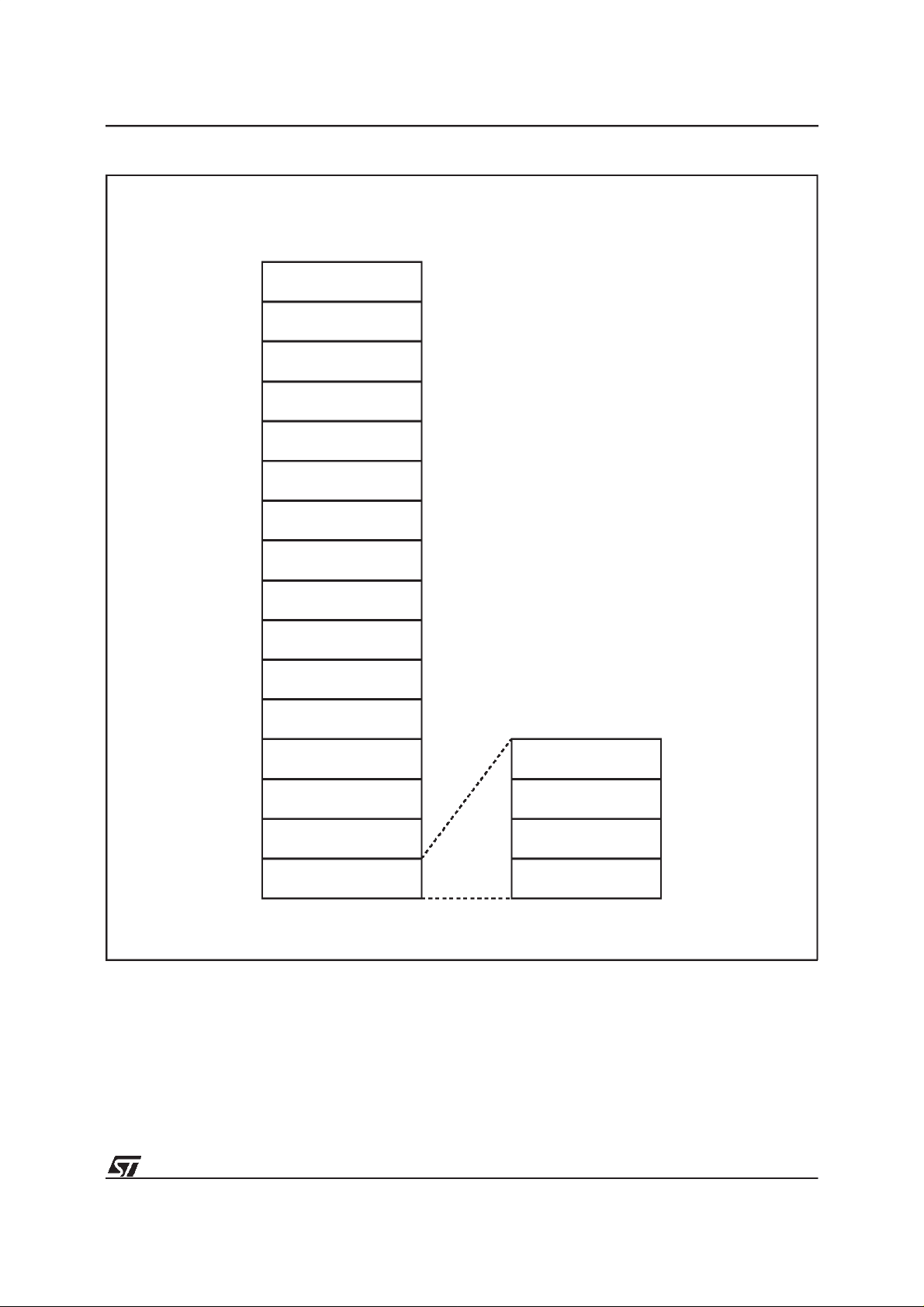

Figure1. LogicDiagram

V

CC

19

A0-A18

W

E

G

RP

M29W800T

M29W800B

V

SS

M29W800T

M29W800B

NOT FOR NEW DESIGN

44

1

SO44 (M)TSOP48 (N)

15

DQ0-DQ14

DQ15A–1

BYTE

RB

AI02178

June 1999 1/33

Thisis informationon a product stillin productionbutnotrecommended for newdesigns.

M29W800T, M29W800B

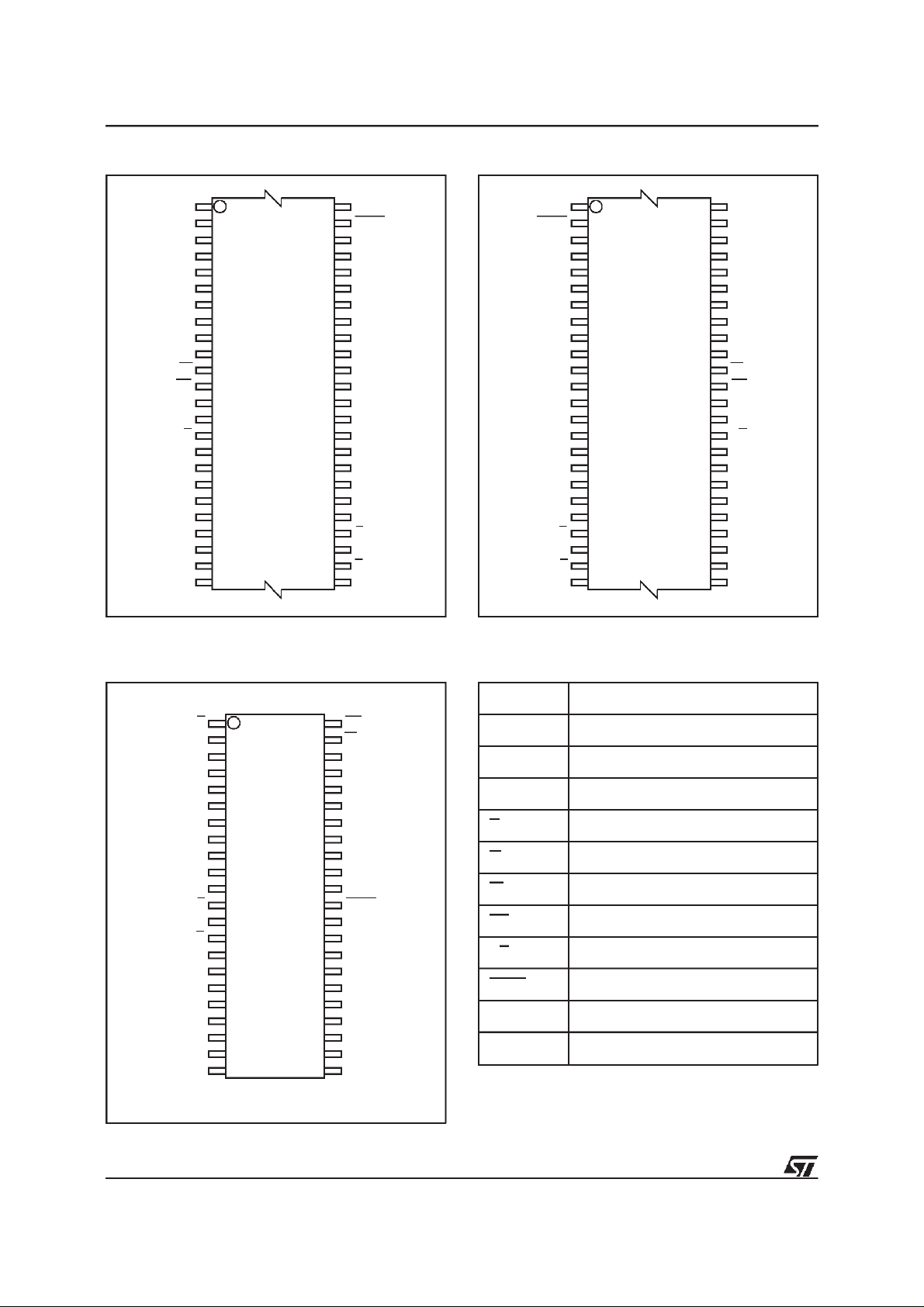

Figure2A. TSOPPin Connections

1

A15

A14

A13

A12

A11

A10 DQ14

A9

A8

NC

NC

W

RP

NC

NC

RB

A18

A17

A7

A6

A5

A4

A3

A2

A1

M29W800T

12

M29W800B

13

(Normal)

24 25

48

37

36

AI02179

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

E

A0

Figure2B. TSOPReverse Pin Connections

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

V

SS

A0

1

M29W800T

12

M29W800B

13

(Reverse)

G

E

24 25

AI02180

48

37

36

A15

A14

A13

A12

A11

A10

A9

A8

NC

NC

W

RP

NC

NC

RB

A18

A17

A7

A6

A5

A4

A3

A2

A1

Warning: NC = Not Connected. Warning: NC = Not Connected.

Figure2C. SO Pin Connections

Table 1. Signal Names

A0-A18 Address Inputs

RB

1

2

A18

3

A17 A8

A7

4

5

A6

6

A5

A4

7

A3

8

A2

9

A1

10

A0

11

M29W800T

M29W800B

12

13

14

15

16

17DQ1

18

19

20

21

AI02181

V

SS

DQ0

DQ8

DQ9

DQ10

DQ3

DQ11

E

G

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

RP

W

A9

A10

A11

A12

A13

A14

A15

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5DQ2

DQ12

DQ4

V

CC

DQ0-DQ7 Data Input/Outputs, Command Inputs

DQ8-DQ14 Data Input/Outputs

DQ15A–1 Data Input/Output or Address Input

E Chip Enable

G Output Enable

W Write Enable

RP Reset / Block TemporaryUnprotect

RB Ready/Busy Output

BYTE Byte/Word Organisation

V

CC

V

SS

Supply Voltage

Ground

2/33

M29W800T, M29W800B

Table2. AbsoluteMaximumRatings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

(2)

V

IO

V

CC

V

(A9, E, G, RP)

Notes: 1. Except for therating ”OperatingTemperature Range”, stresses above those listed in the Table ”AbsoluteMaximum Ratings”

may cause permanent damage to thedevice. These are stress ratings only and operation of the device at these or any other

conditions above those indicated in the Operatingsections of this specification is not implied.Exposure to Absolute Maximum

Rating conditions for extended periods may affect device reliability.Refer also tothe STMicroelectronics SURE Program and other

relevant quality documents.

2. Minimum Voltagemay undershootto –2V during transition and for less than 20ns.

3. Depends on range.

Ambient Operating Temperature

Temperature Under Bias –50 to 125

Storage Temperature –65 to 150

Input or Output Voltages –0.6to 5 V

Supply Voltage –0.6to 5 V

(2)

A9, E, G, RP Voltage –0.6to 13.5 V

DESCRIPTION(Cont’d)

and temporarily unprotected to make changes in

the application. Each block can be programmed

and erased over 100,000 cycles.

Instructionsfor Read/Reset, Auto Select for reading the Electronic Signature or Block Protection

status,Programming,BlockandChipErase,Erase

Suspend and Resume are written to the devicein

cyclesofcommandstoaCommandInterfaceusing

standardmicroprocessorwrite timings.

Thedevice is offered in TSOP48(12 x20mm)and

SO44packages.Both normal and reversepinouts

are available for the TSOP48package.

Organisation

TheM29W800is organisedas1 M x8 or512Kx16

bitsselectableby the BYTEsignal.WhenBYTE is

Low the Byte-wide x8 organisationis selectedand

the address lines are DQ15A–1and A0-A18. The

Data Input/Output signal DQ15A–1 acts as address line A–1 which selects the lower or upper

Byteof the memoryword for output on DQ0-DQ7,

DQ8-DQ14 remain at High impedance. When

BYTEis Highthe memoryuses the addressinputs

A0-A18 and the Data Input/Outputs DQ0-DQ15.

Memory control is provided by Chip Enable E,

OutputEnable G and WriteEnable W inputs.

AReset/BlockTemporaryUnprotection RPtri-level

input providesa hardware reset when pulled Low,

andwhen heldHigh(atV

)temporarily unprotects

ID

blocks previously protected allowing them to be

programedanderased.Erase andProgramoperations are controlled by an internal Program/Erase

Controller(P/E.C.). StatusRegisterdata output on

DQ7providesa DataPollingsignal,and DQ6 and

DQ2provideToggle signalstoindicatethe state of

(1)

(3)

–40 to 85

C

°

C

°

C

°

the P/E.C operations. A Ready/Busy RB output

indicatesthecompletionof theinternalalgorithms.

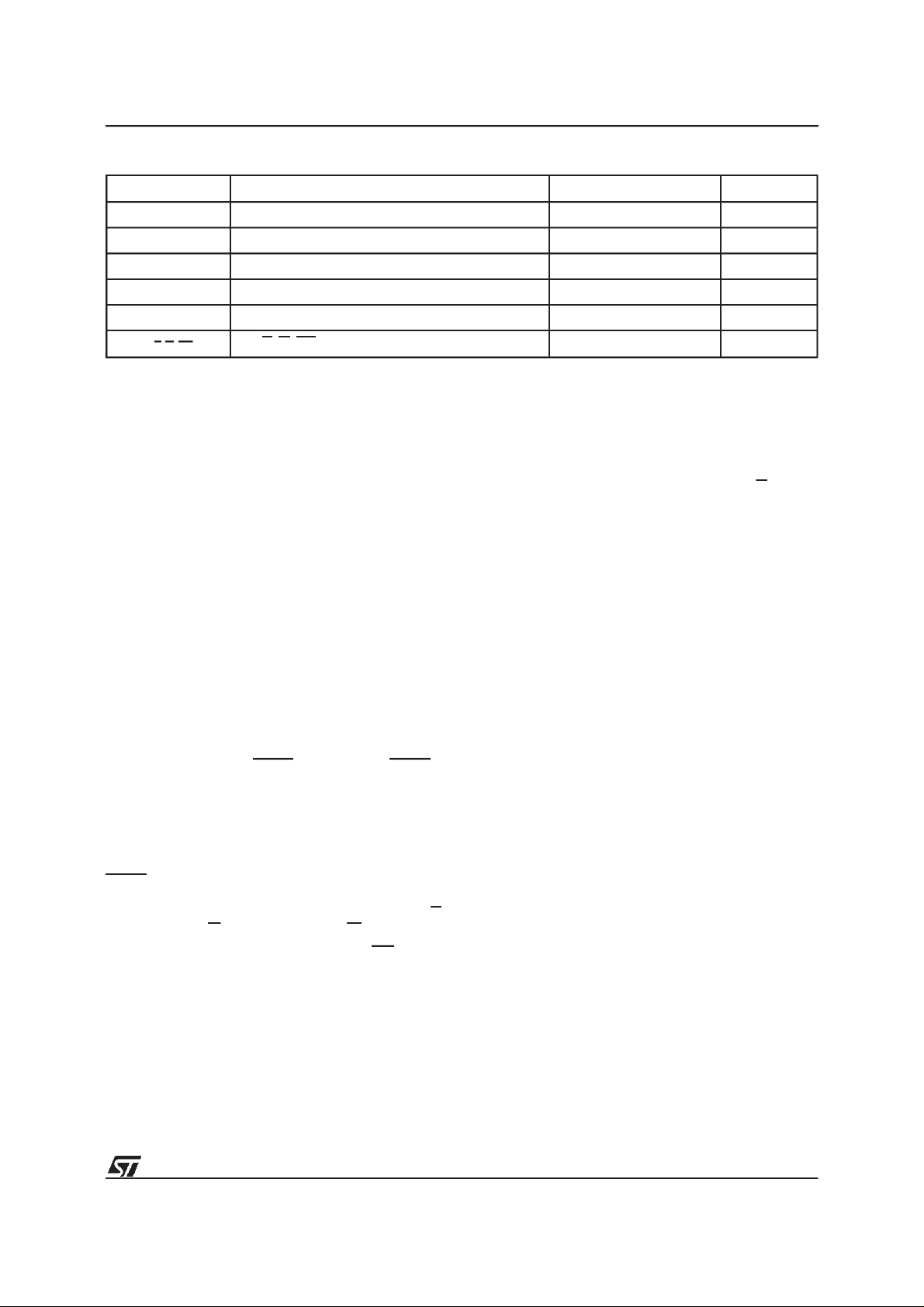

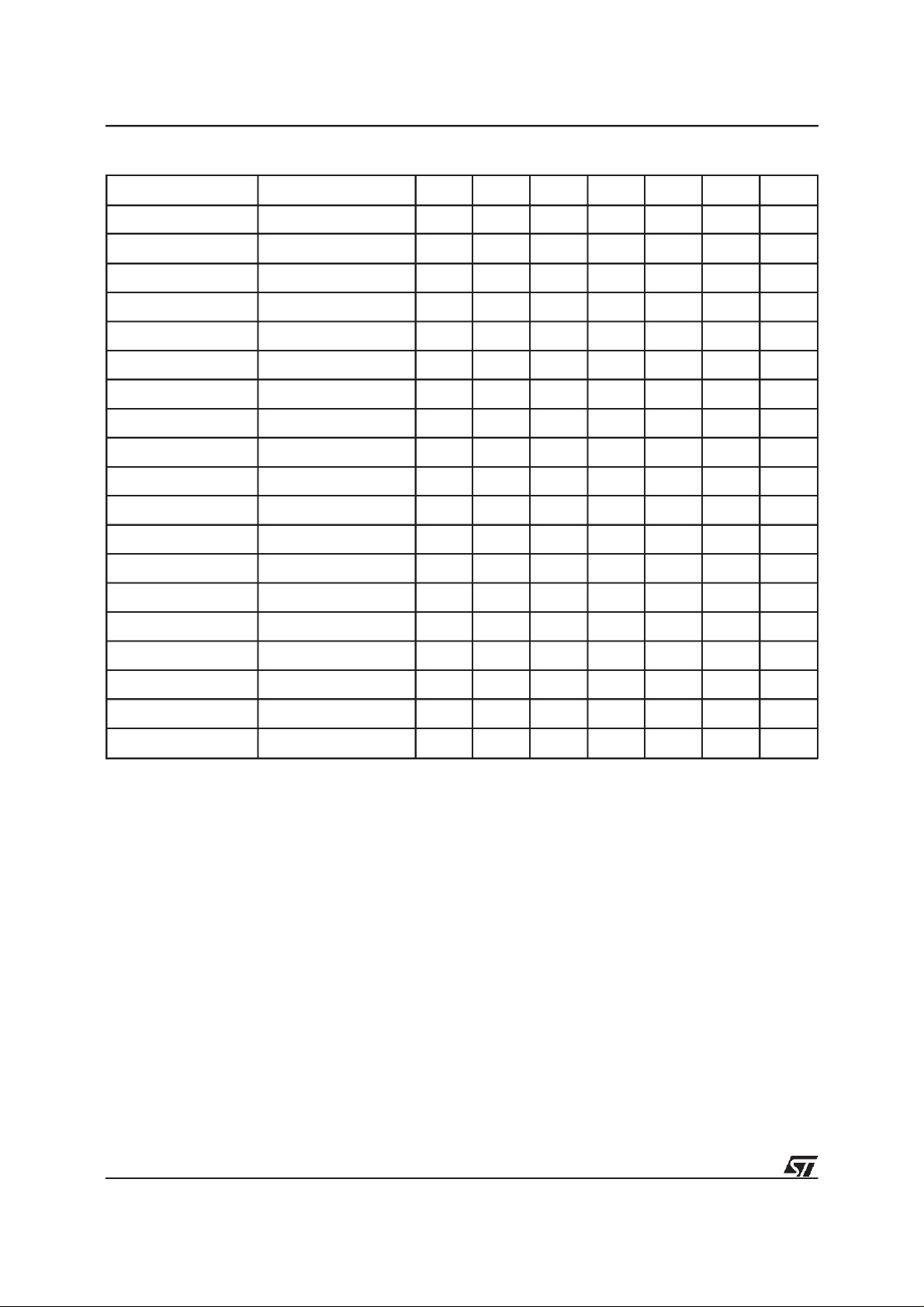

MemoryBlocks

Thedevicesfeatureasymmetrically blockedarchitectureprovidingsystem memory integration.Both

M29W800Tand M29W800Bdeviceshavean array

of 19 blocks, one Boot Block of 16 KBytes or 8

KWords, two Parameter Blocks of 8 KBytes or 4

KWords, one Main Block of 32 KBytes or 16

KWordsand fifteenMainBlocksof 64KBytesor 32

KWords.TheM29W800ThastheBoot Block atthe

top of the memory add ress space and the

M29W800Blocates the Boot Block starting at the

bottom. The memory maps are showed in Figure

3.

Each block can be erased separately, any combi-

nation of blocks can be specified for multi-block

eraseor the entirechip may beerased.TheErase

operations are managed automatically by the

P/E.C. The block erase operation can be suspended in order to read from or program to any

blocknot being ersased, and then resumed.

Block protection provides additionaldata security.

Each block can be separatelyprotected or unprotectedagainst Program or Erase on programming

equipment.All previously protected blocks can be

temporarilyunprotectedin the application.

Bus Operations

The following operations can be performed using

theappropriatebus cycles:Read(Array,Electronic

Signature, Block Protection Status), Write command, Output Disable,Standby,Reset, Block Protection, Unprotection, Protection Verify,

Unprotection Verifyand Block Temporary Unprotection.See Tables4 and5.

3/33

M29W800T, M29W800B

Figure3A. TopBootBlock Memory Map and Block Address Table

TOP BOOT BLOCK

7FFFFh

78000h

77FFFh

70000h

6FFFFh

68000h

67FFFh

60000h

5FFFFh

58000h

57FFFh

50000h

4FFFFh

48000h

47FFFh

40000h

3FFFFh

38000h

37FFFh

30000h

2FFFFh

28000h

27FFFh

20000h

1FFFFh

18000h

17FFFh

10000h

0FFFFh

08000h

07FFFh

00000h

Byte-WideWord-Wide

FFFFFh

F0000h

EFFFFh

E0000h

DFFFFh

D0000h

CFFFFh

C0000h

BFFFFh

B0000h

AFFFFh

A0000h

9FFFFh

90000h

8FFFFh

80000h

7FFFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

00000h

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

16K BOOT BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

32K MAIN BLOCK

AI01725B

Byte-Wide Word-Wide

FFFFFh

FC000h

FBFFFh

FA000h

F9FFFh

F8000h

F7FFFh

F0000h

7FFFFh

7E000h

7DFFFh

7D000h

7CFFFh

7C000h

7BFFFh

78000h

4/33

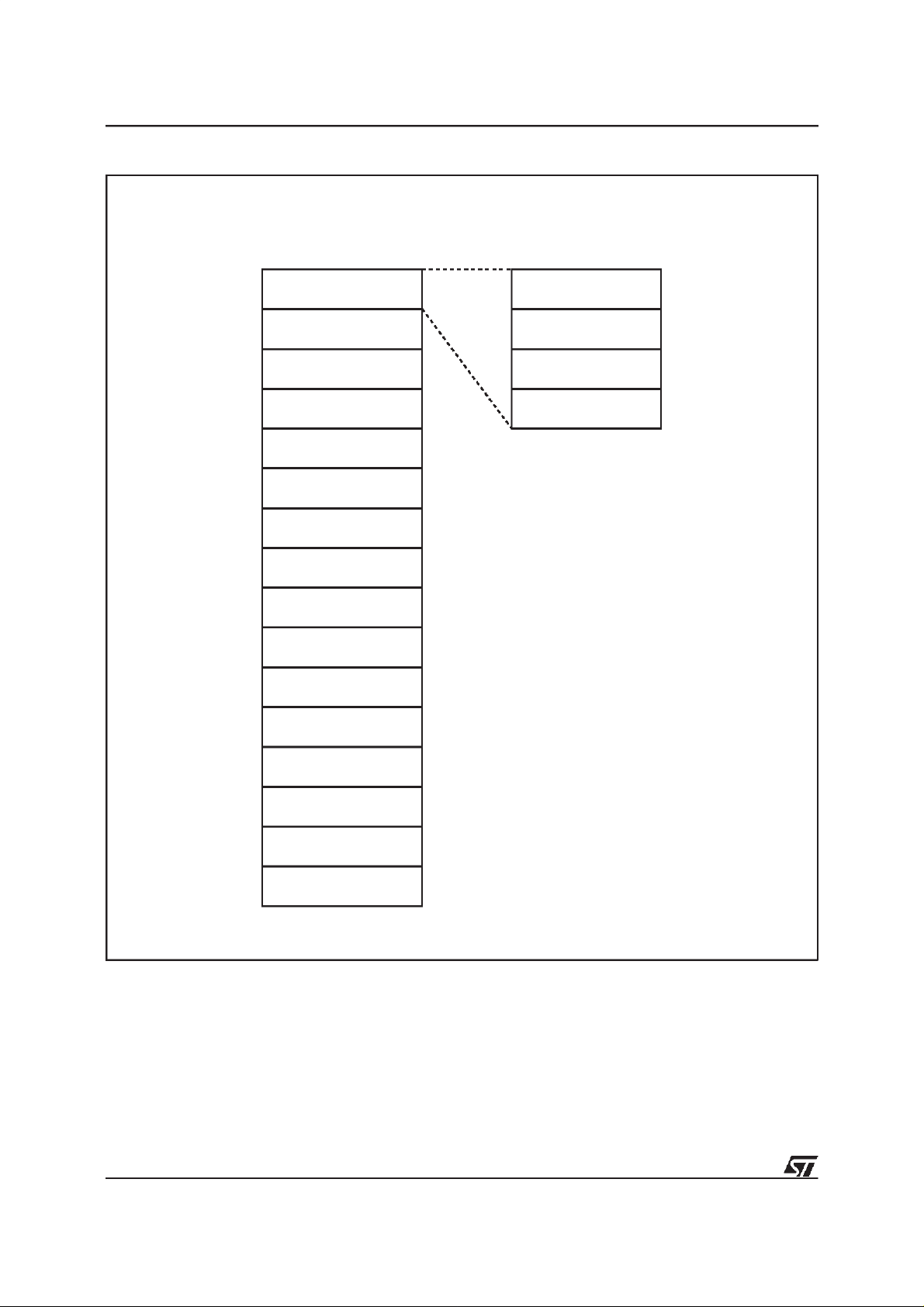

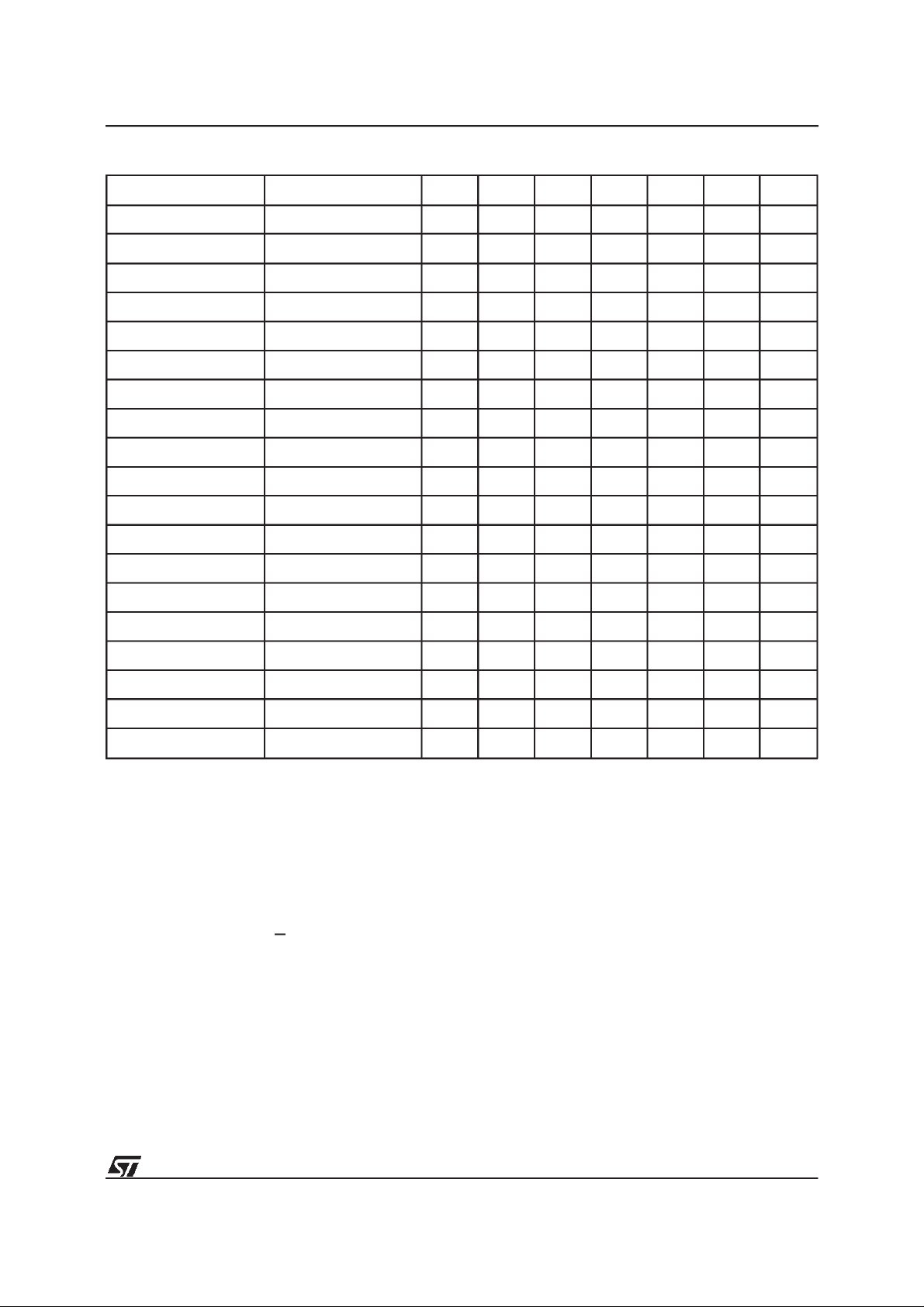

Figure3B. Bottom BootBlock MemoryMap andBlock Address Table

BOTTOM BOOT BLOCK

Byte-WideWord-Wide

FFFFFh

78000h

77FFFh

70000h

6FFFFh

68000h

67FFFh

60000h

5FFFFh

58000h

57FFFh

50000h

4FFFFh

48000h

47FFFh

40000h

3FFFFh

38000h

37FFFh

30000h

2FFFFh

28000h

27FFFh

20000h

1FFFFh

18000h

17FFFh

10000h

0FFFFh

08000h

07FFFh

00000h

FFFFFh7FFFFh

F0000h

EFFFFh

E0000h

DFFFFh

D0000h

CFFFFh

C0000h

BFFFFh

B0000h

AFFFFh

A0000h

9FFFFh

90000h

8FFFFh

80000h

7FFFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

00000h

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

32K MAIN BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

16K BOOT BLOCK

M29W800T, M29W800B

Byte-Wide Word-Wide

0FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

07FFFh

04000h

03FFFh

03000h

02FFFh

02000h

01FFFh

00000h

AI01731B

5/33

M29W800T, M29W800B

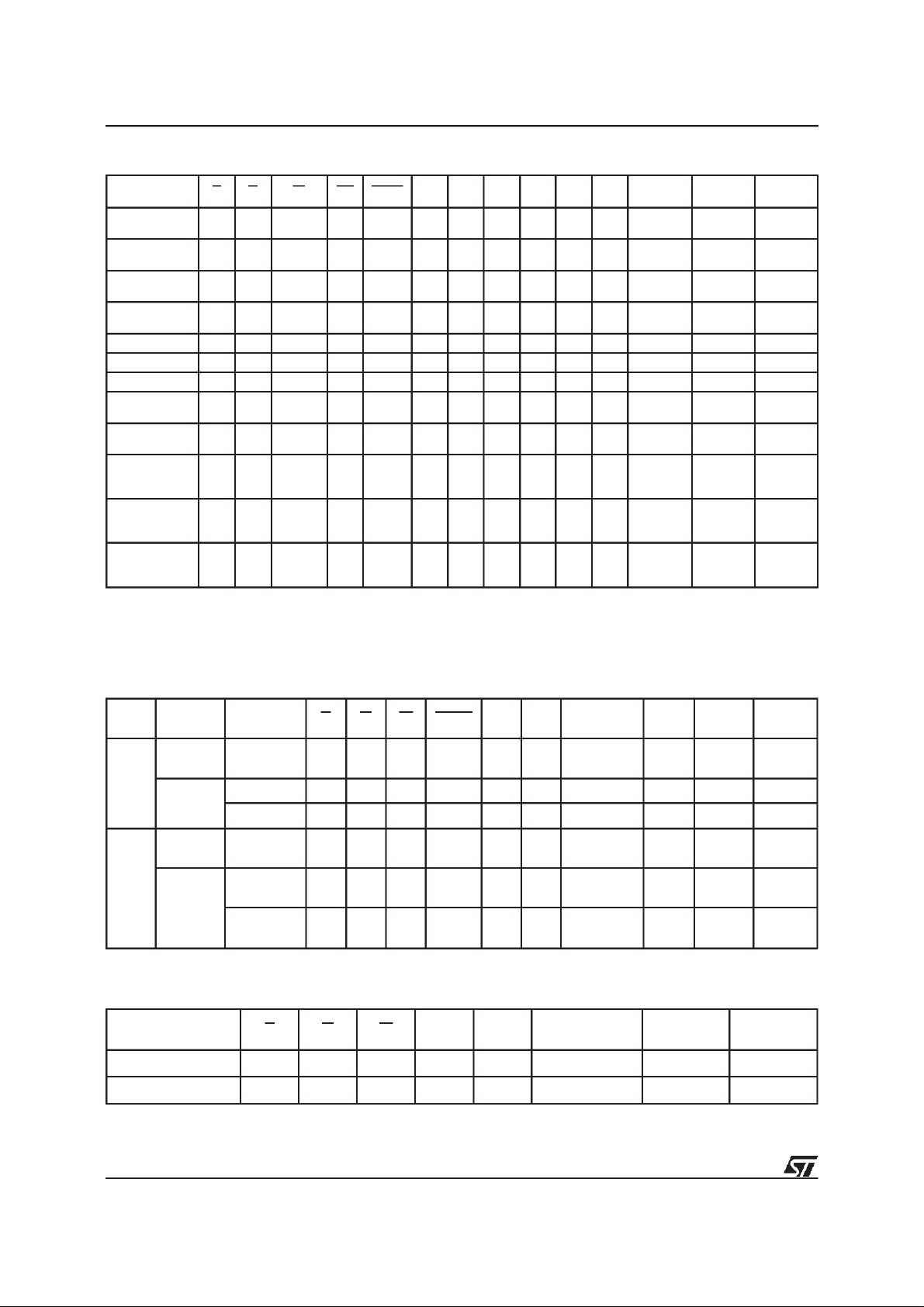

Table3A. M29W800TBlockAddress Table

Address Range (x8) Address Range (x16) A18 A17 A16 A15 A14 A13 A12

00000h-0FFFFh 00000h-07FFFh 0 0 0 0 X X X

10000h-1FFFFh 08000h-0FFFFh 0 0 0 1 X X X

20000h-2FFFFh 10000h-17FFFh 0 0 1 0 X X X

30000h-3FFFFh 18000h-1FFFFh 0 0 1 1 X X X

40000h-4FFFFh 20000h-27FFFh 0 1 0 0 X X X

50000h-5FFFFh 28000h-2FFFFh 0 1 0 1 X X X

60000h-6FFFFh 30000h-37FFFh 0 1 1 0 X X X

70000h-7FFFFh 38000h-3FFFFh 0 1 1 1 X X X

80000h-8FFFFh 40000h-47FFFh 1 0 0 0 X X X

90000h-9FFFFh 48000h-4FFFFh 1 0 0 1 X X X

A0000h-AFFFFh 50000h-57FFFh 1 0 1 0 X X X

B0000h-BFFFFh 58000h-5FFFFh 1 1 1 1 X X X

C0000h-CFFFFh 60000h-67FFFh 1 1 0 0 X X X

D0000h-DFFFFh 68000h-6FFFFh 1 1 0 1 X X X

E0000h-EFFFFh 70000h-77FFFh 1 1 1 0 X X X

F0000h-F7FFFh 78000h-7BFFFh 1 1 1 1 0 X X

F8000h-F9FFFh 7C000h-7CFFFh 1 1 1 1 1 0 0

FA000h-FBFFFh 7D000h-7DFFFh 1 1 1 1 1 0 1

FC000h-FFFFFh 7E000h-7FFFFh 1 1 1 1 1 1 X

CommandInterface

Instructions,made up of commands written in cycles,canbe givento theProgram/EraseController

through a Command Interface (C.I.). For added

dataprotection,programor eraseexecutionstarts

after4 or6cycles.The first,second,fourthandfifth

This Coded sequence is the same for all Program/Erase Controller instructions. The ’Command’itself and its confirmation,when applicable,

are given on the third, fourth or sixth cycles. Any

incorrectcommandor any impropercommandsequence will resetthe device to Read Array mode.

cycles are used to input Coded cycles to the C.I.

6/33

M29W800T, M29W800B

Table3B. M29W800BBlock Address Table

Address Range (x8) Address Range (x16) A18 A17 A16 A15 A14 A13 A12

00000h-03FFFh 00000h-01FFFh 0 0 0 0 0 0 X

04000h-05FFFh 02000h-02FFFh 0 0 0 0 0 1 0

06000h-07FFFh 03000h-03FFFh 0 0 0 0 0 1 1

08000h-0FFFFh 04000h-07FFFh 0 0 0 0 1 X X

10000h-1FFFFh 08000h-0FFFFh 0 0 0 1 X X X

20000h-2FFFFh 10000h-17FFFh 0 0 1 0 X X X

30000h-3FFFFh 18000h-1FFFFh 0 0 1 1 X X X

40000h-4FFFFh 20000h-27FFFh 0 1 0 0 X X X

50000h-5FFFFh 28000h-2FFFFh 0 1 0 1 X X X

60000h-6FFFFh 30000h-37FFFh 0 1 1 0 X X X

70000h-7FFFFh 38000h-3FFFFh 0 1 1 1 X X X

80000h-8FFFFh 40000h-47FFFh 1 0 0 0 X X X

90000h-9FFFFh 48000h-4FFFFh 1 0 0 1 X X X

A0000h-AFFFFh 50000h-57FFFh 1 0 1 0 X X X

B0000h-BFFFFh 58000h-5FFFFh 1 0 1 1 X X X

C0000h-CFFFFh 60000h-67FFFh 1 1 0 0 X X X

D0000h-DFFFFh 68000h-6FFFFh 1 1 0 1 X X X

E0000h-EFFFFh 70000h-77FFFh 1 1 1 0 X X X

F0000h-FfFFFh 78000h-7FFFFh 1 1 1 1 X X X

Instructions

Seven instructions are defined to perform Read

Array,AutoSelect(toreadthe ElectronicSignature

or BlockProtectionStatus),Program,BlockErase,

Chip Erase, Erase Suspend and Erase Resume.

The internal P/E.C. automatically handlesall timing and verification of the Program and Erase

operations.TheStatus Register Data Polling,Toggle, Error bits and the RB output may be read at

anytime, during programmingor erase, to monitor

the progress of theoperation.

Instructionsarecomposedof upto six cycles. The

first two cycles input a Coded sequence to the

CommandInterfacewhich iscommon toall instructions(see Table 8).

The third cycle inputs the instruction set-up com-

data, Electronic Signature or Block Protection

Status for Read operations.In order to give additional data protection,the instructionsforProgram

and Block or Chip Erase require further command

inputs. For a Programinstruction,the fourth command cycle inputs the address and data to be

programmed. For an Erase instruction (Block or

Chip), the fourth and fifth cycles input a further

Coded sequence before the Erase confirm commandonthesixthcycle.Erasureofamemoryblock

may be suspended, in order to read data from

anotherblock or to program data inanotherblock,

and then resumed.

When power is first applied or if V

, the command interface is reset to Read

V

LKO

CC

Array.

mand. Subsequent cycles output the addressed

falls below

7/33

M29W800T, M29W800B

SIGNALDESCRIPTIONS

See Figure 1 and Table1.

AddressInputs(A0-A18). The addressinputsfor

thememoryarray are latchedduringawriteoperation on the falling edge at Chip Enable E or Write

EnableW. In Word-wide organisation the address

lines are A0-A18, in Byte-wide organisation

DQ15A–1acts as an additional LSB address line.

WhenA9 israised to V

, eithera Read Electronic

ID

Signature Manufacturer or Device Code, Block

Protection Status or a Write Block Protection or

Block Unprotection is enabled depending on the

combinationof levelson A0,A1, A12andA15.

Data Input/Outputs (DQ0-DQ7). These Inputs/Outputsare used in the Byte-wideand Wordwide organisations. The inpu t is data to be

programmed in the memory array or a command

to be written to the C.I. Both are latched on the

rising edge of Chip Enable E or Write Enable W.

The output is data from the Memory Array, the

Electronic Signature Manufacturer or Device

codes, the Block Protection Status or the Status

registerData Polling bit DQ7, the ToggleBits DQ6

and DQ2, the Error bit DQ5 or the EraseTimer bit

DQ3. Outputs are valid when Chip Enable E and

Output Enable G are active. The output is high

impedance when the chip is deselected or the

outputsaredisabledandwhenRPis ataLowlevel.

Data Input/Outputs (DQ8-DQ14and DQ15A–1).

These Inputs/Outputsare additionally used in the

Word-wide organisation.WhenBYTEisHighDQ8DQ14 and DQ15A–1 act as the MSB of the Data

Inputor Output,functioningas described for DQ0DQ7 above, and DQ8 - DQ15 are ’don’t care’ for

commandinputs or statusoutputs. When BYTEis

Low,DQ0-DQ14arehighimpedance,DQ15A–1is

theAddressA–1input.

Chip Enable (E). The Chip Enable inputactivates

the memory control logic, input buffers, decoders

andsenseamplifiers.E Highdeselectsthememory

andreducesthe powerconsumptiontothestandby

level. E can also be used to control writing to the

commandregister and to the memory array, while

Wremainsata lowlevel.TheChipEnablemust be

forcedto V

duringthe BlockUnprotectionopera-

ID

tion.

Output Enable (G). The Output Enable gates the

outputs through the data buffers during a read

operation. When G is High the outputs are High

impedance. G must be forced to V

level during

ID

BlockProtectionand Unprotection operations.

WriteEnable(W).Thisinputcontrolswritingto the

CommandRegisterand Addressand Datalatches.

Byte/Word Organization Select (BYTE). The

BYTEinputselectstheoutputconfigurationfor the

device: Byte-wide (x8) mode or Word-wide (x16)

mode. When BYTEis Low,the Byte-widemode is

selectedand thedata isread and programmedon

DQ0-DQ7. In this mode, DQ8-DQ14 are at high

impedance and DQ15A–1 is the LSB address.

When BYTE is High, the Word-wide mode is selected and the data is read and programmed on

DQ0-DQ15.

Ready/Busy Output (RB). Ready/Busy is an

open-drainoutputandgivestheinternalstateofthe

P/E.C. of the device. When RB is Low, the device

is Busy with a Program or Erase operation and it

will not accept any additional program or erase

instructionsexcept theEraseSuspendinstruction.

WhenRB is High, thedeviceis readyforany Read,

Program or Erase operation. The RB will also be

Highwhen the memoryis put inEraseSuspendor

Standbymodes.

Reset/Block Temporary Unprotect Input (RP).

The RP Input provides hardware reset and protected block(s) temporary unprotection functions.

Resetof the memory is acheivedby pulling RP to

foratleastt

V

IL

. Whentheresetpulseisgiven,

PLPX

if the memoryis in Reador Standby modes, it will

be available for new operations in t

PHEL

after the

risingedgeofRP.If thememoryis in Erase,Erase

Suspend or Program modes the reset will take

duringwhichtheRBsignalwillbe held at VIL.

t

PLYH

The end of the memory reset will be indicated by

the rising edge of RB. A hardware reset during an

Erase or Program operation will corrupt the data

being programmed or the sector(s) being erased.

SeeTable 14 and Figure 9.

Temporary block unprotectionis made by holding

RP at V

. In this condition previously protected

ID

blockscan be programmed or erased.The transitionof RPfrom V

to VIDmustslowerthant

IH

PHPHH

See Table 15 and Figure 9. When RP is returned

from V

to VIHall blocks temporarily unprotected

ID

will be again protected.

V

Supply Voltage. The power supply for all

CC

operations(Read,Programand Erase).

Ground. VSSis the reference for all voltage

V

SS

measurements.

.

8/33

M29W800T, M29W800B

DEVICEOPERATIONS

See Tables 4, 5 and 6.

Read. Read operations are used to output the

contents of the Memory Array,the ElectronicSignature,theStatusRegisteror the BlockProtection

Status.Both Chip Enable E and Output Enable G

must be low in order to read the output of the

memory.

Write.WriteoperationsareusedtogiveInstruction

Commandstothe memory or to latch input data to

beprogrammed.Awrite operationis initiatedwhen

Chip Enable E isLow and Write Enable W is Low

withOutputEnableG High.Addressesarelatched

onthefallingedge of W or E whicheveroccurslast.

CommandsandInputDataarelatchedontherising

edgeof W or E whicheveroccursfirst.

OutputDisable. The data outputsarehighimpedancewhen the OutputEnable G is High with Write

EnableW High.

Standby. The memory is in standby when Chip

EnableE is Highand theP/E.C.is idle.The power

consumption is reduced to the standby level and

the outputs are high impedance, independent of

the Output Enable G or WriteEnable W inputs.

AutomaticStandby. After 150ns of bus inactivity

andwhen CMOS levels are drivingthe addresses,

the chip automatically enters a pseudo-standby

modewhereconsumptionis reducedto theCMOS

standbyvalue,while outputsstill drivethe bus.

ElectronicSignature. Two codes identifying the

manufacturer and thedevicecanbe read fromthe

memory. The manufacturer’s code for STMicroelectronicsis20h,thedevicecodeisD7hforthe

M29W800T(TopBoot)and 5BhfortheM29W800B

(Bottom Boot). These codes allow programming

equipment or applications to automatically match

their interface to the characteristics of the

M29W800.The ElectronicSignatureis outputby a

Read operationwhen the voltage applied to A9 is

andaddressinputsA1 isLow.The manufac-

atV

ID

turer code is output when the Address input A0 is

Low and the device code when this input is High.

Other Address inputs are ignored. The codes are

output on DQ0-DQ7.

TheElectronicSignaturecan alsobe read,without

raisingA9 to V

, bygiving the memorythe Instruc-

ID

tion AS. If the Byte-wide configuration is selected

thecodes areoutputonDQ0-DQ7with DQ8-DQ14

atHigh impedance;if the Word-wideconfiguration

isselectedthe codes are output on DQ0-DQ7with

DQ8-DQ15at 00h.

Block Protection. Each block can be separately

protected against Program or Erase on programming equipment. Block protection provides additional data security, as it disables all program or

eraseoperations.Thismodeisactivatedwhenboth

A9 and G are raised to V

and an address in the

ID

block is applied on A12-A18. Block protection is

initiatedon the edge of W falling to V

a delayof 100µs,the edge of W rising to V

. Then after

IL

IH

ends

theprotectionoperations.Blockprotectionverifyis

achievedby bringingG, E, A0and A6toV

, while W is atVIHandA9at VID. Underthese

toV

IH

andA1

IL

conditions,reading the data outputwill yield 01h if

the block defined by the inputs on A12-A18 is

protected.Any attempt to program or erasea protectedblockwill be ignoredby the device.

Block Temporary Unprotection. Any previously

protectedblock can be temporarilyunprotectedin

ordertochangestoreddata.Thetemporaryunprotection mode is activated by bringing RP to V

ID

During the temporary unprotection mode the previously protected blocks are unprotected. A block

can be selected and data can be modified by

executingtheEraseorPrograminstructionwiththe

RPsignalheldat V

. When RP is returnedto VIH,

ID

all the previously protected blocks are again protected.

Block Unprotection. All protected blocks can be

unprotected on programming equipment to allow

updating of bit contents. All blocks must first be

protectedbefore theunprotectionoperation.Block

unprotectionis activatedwhen A9, G and E are at

and A12, A15 at VIH. Unprotection is initiated

V

ID

bytheedgeofWfallingto V

. Afteradelayof10ms,

IL

the unprotection operation will end. Unprotection

verify is achievedby bringing G and E to V

A0 is at V

atV

ID

, A6 and A1 are at VIHand A9 remains

IL

. Inthese conditions,readingtheoutput data

IL

while

will yield 00h if the block defined by the inputs

A12-A18has been succesfully unprotected. Each

block must be separatelyverified by giving its address in order to ensure that it has been unprotected.

.

9/33

M29W800T, M29W800B

Table4. User Bus Operations

(1)

Operation E G W RP BYTE A0 A1 A6 A9 A12 A15

Read Word V

Read Byte V

Write Word V

Write Byte V

Output Disable V

Standby V

ILVIL

ILVIL

ILVIH

ILVIH

ILVIH

IH

Reset X X X V

Block

Protection

Blocks

Unprotection

Block

Protection

Verify

Block

Unprotection

Verify

Block

Temporary

Unprotection

Notes: 1. X = V

(2,4) V

(2,4)

(2,4)

ILVIDVIL

(4)VIDVIDVIL

VILV

VILV

XX X V

or V

IL

2. Block Address must be given on A12-A18bits.

3. See Table6.

4. Operation performed onprogramming equipment.

IH

V

V

V

IH

IH

V

V

IH

IH

V

V

IL

IH

V

V

IL

IH

V

V

IH

IH

A0 A1 A6 A9 A12 A15

IH

V

A0 A1 A6 A9 A12 A15

IL

V

A0 A1 A6 A9 A12 A15 Data Input Data Input

IH

V

A0 A1 A6 A9 A12 A15

IL

X X X X X X X Hi-Z Hi-Z Hi-Z

XXVIHX X X X X X X Hi-Z Hi-Z Hi-Z

X X X X X X X Hi-Z Hi-Z Hi-Z

IL

Pulse V

Pulse V

V

IL

IH

V

IL

IH

XXXXVIDXX X X X

IH

XXXXVIDVIHV

IH

V

XVILVIHVILVIDA12 A15 X X

IH

V

XVILVIHVIHVIDA12 A15 X X

IH

X XXXXXX X X X

ID

DQ15

A–1

Data

Output

Address

Input

Address

Input

XXX

IH

DQ8-

DQ14

Data

Output

Hi-Z

Hi-Z

DQ0-DQ7

Data

Output

Data

Output

Data

Input

Data

Input

Block

Protect

Status

Block

Protect

Status

(3)

(3)

Table5. Read Electronic Signature(followingAS instructionor with A9 = VID)

Org. Code Device E G W BYTE A0 A1

Word-

wide

Manufact.

Code

Device

Code

Manufact.

Code

M29W800T V

M29W800B V

V

VILV

IL

VILV

IL

VILV

IL

V

VILV

IL

V

IH

V

IH

V

IH

V

IH

VILVILDon’t Care 0 00h 20h

IH

V

IH

IH

IL

IHVIL

V

IHVIL

VILVILDon’t Care

Byte-

wide

Device

M29W800T V

IL

VILV

V

IH

V

IL

IHVIL

Code

M29W800B V

IL

VILV

V

IH

V

IL

IHVIL

Other

Addresses

Don’t Care 0 00h D7h

Don’t Care 0 00h 5Bh

Don’t Care

Don’t Care

DQ15

A–1

Don’t

Care

Don’t

Care

Don’t

Care

Table6. Read Block Protectionwith AS Instruction

Code E G W A0 A1 A12-A18

Protected Block V

Unprotected Block V

IL

IL

V

IL

V

IL

V

IH

V

IH

V

IL

V

IL

V

IH

V

IH

Block Address Don’t Care 01h

Block Address Don’t Care 00h

Addresses

Other

DQ8-

DQ14

DQ0-

DQ7

Hi-Z 20h

Hi-Z D7h

Hi-Z 5Bh

DQ0-DQ7

10/33

Loading...

Loading...