4 Mbit (512Kb x8 or 256Kbx16, Boot Block)

M29F400T and M29F400B are replaced

respectively by the M29F400BT and

M29F400BB

5V±10% SUPPLYVOLTAGEfor PROGRAM,

ERASEand READOPERATIONS

FASTACCESS TIME: 55ns

FASTPROGRAMMINGTIME

–10µs by Byte / 16µs by Word typical

PROGRAM/ERASE CONTROLLER(P/E.C.)

– ProgramByte-by-Byte or Word-by-Word

– StatusRegister bits and Ready/Busy Output

MEMORYBLOCKS

– BootBlock (Top or Bottomlocation)

– Parameterand Main blocks

BLOCK,MULTI-BLOCK and CHIPERASE

MULTI-BLOCKPROTECTION/TEMPORARY

UNPROTECTION MODES

ERASE SUSPEND and RESUMEMODES

– Readand Program another Block during

EraseSuspend

LOWPOWERCONSUMPTION

– Stand-byand Automatic Stand-by

100,000 PROGRAM/ERASECYCLES per

BLOCK

20 YEARS DATARETENTION

– Defectivity below 1ppm/year

ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– DeviceCode, M29F400T: 00D5h

– DeviceCode, M29F400B: 00D6h

DESCRIPTION

The M29F400 is a non-volatile memory that may

be erased electricallyat theblock or chip level and

programmed in-systemon a Byte-by-Byte orWordby-Word basis using only a single 5V VCCsupply.

For Program and Erase operations the necessary

high voltagesare generated internally. The device

can also be programmed in standard programmers.

The arraymatrix organisation allows each block to

be erased and reprogrammed without affecting

other blocks. Blocks canbe protected against pro-

M29F400T

M29F400B

Single Supply Flash Memory

NOT FOR NEW DESIGN

44

1

12 x 20mm

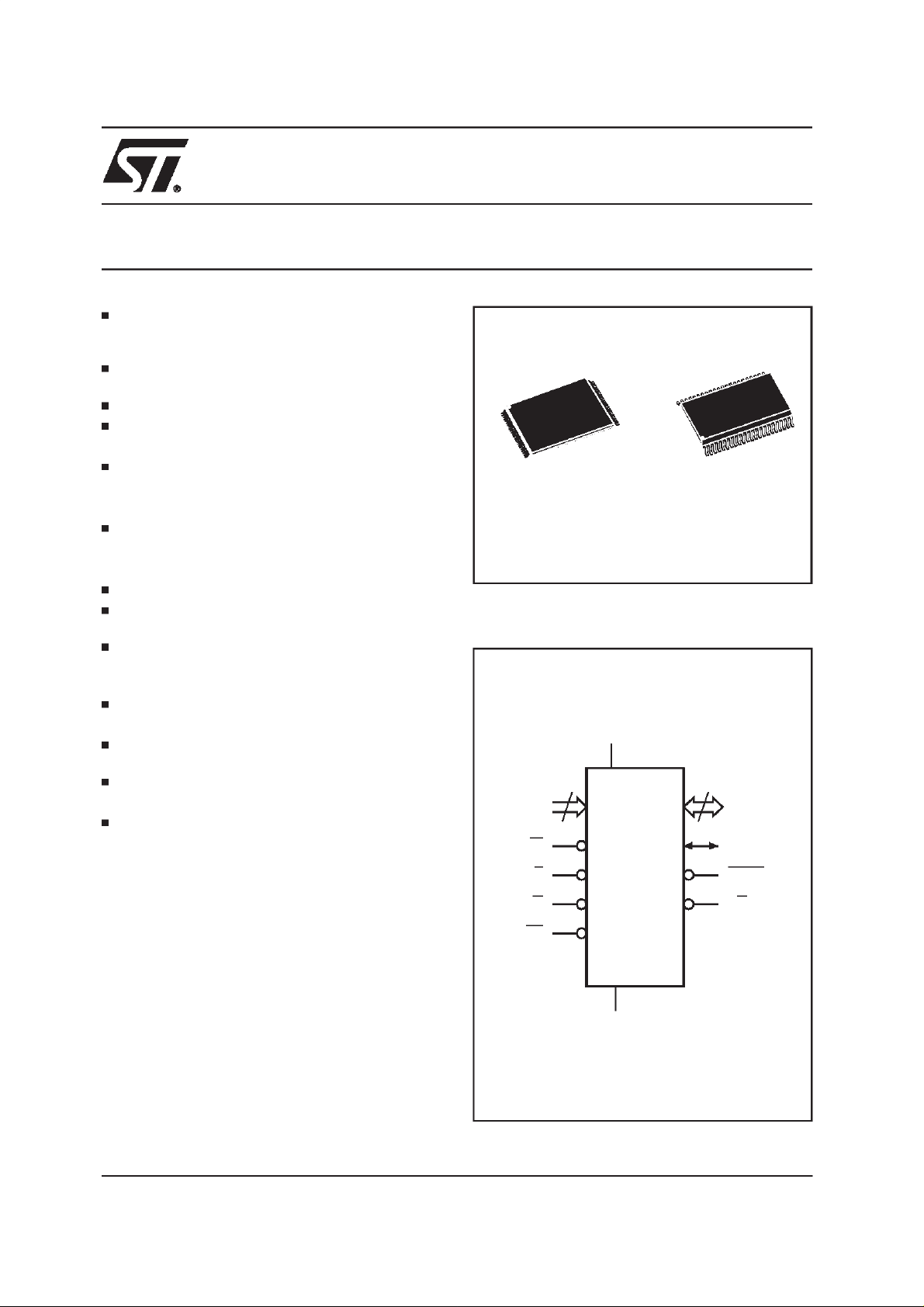

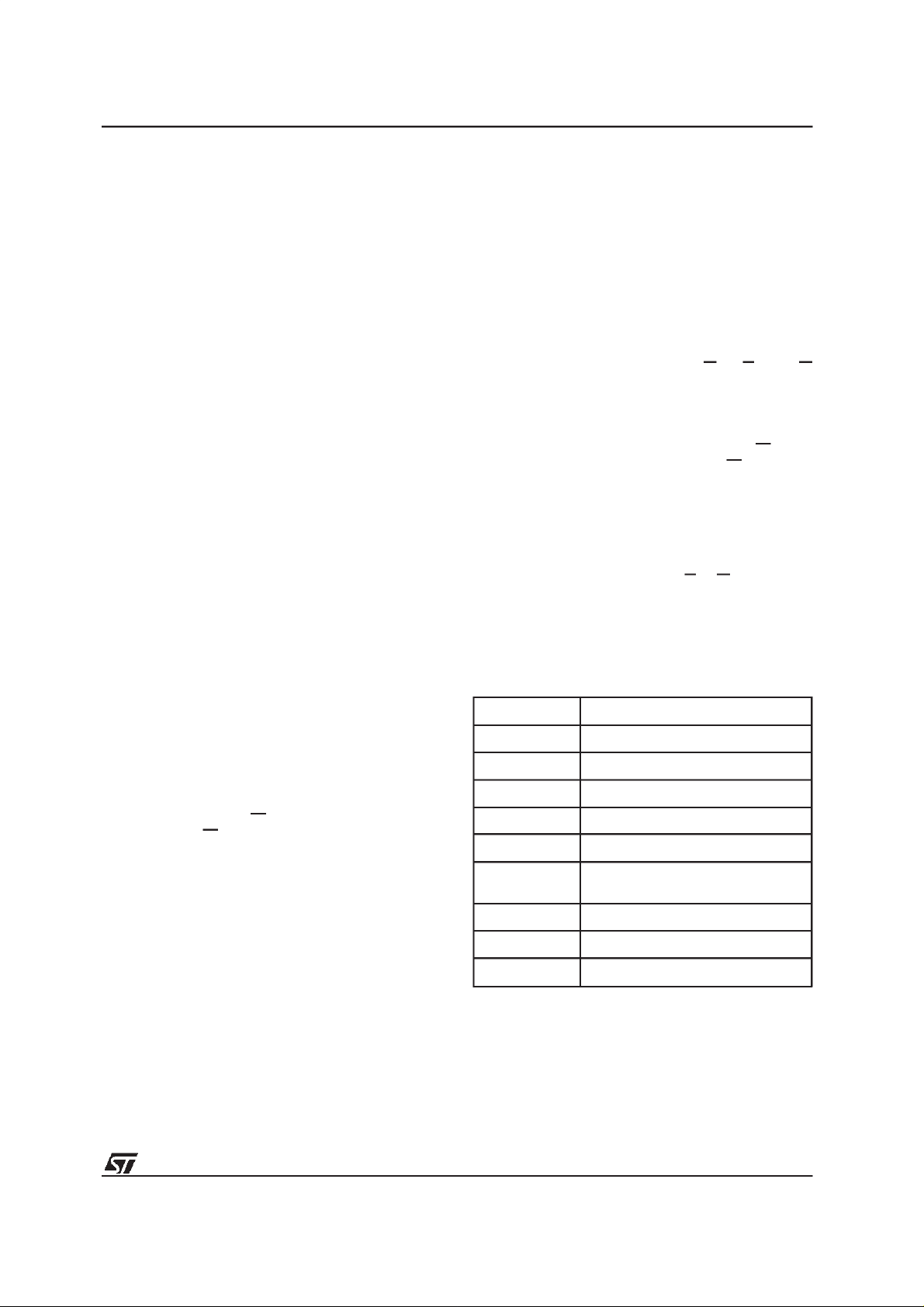

Figure1. Logic Diagram

V

CC

18

A0-A17

W

E

G

RP

M29F400T

M29F400B

V

SS

SO44 (M)TSOP48 (N)

15

DQ0-DQ14

DQ15A–1

BYTE

RB

AI01726B

November 1999 1/34

This is information on a productstil l in production but not recommendedfor new designs.

M29F400T, M29F400B

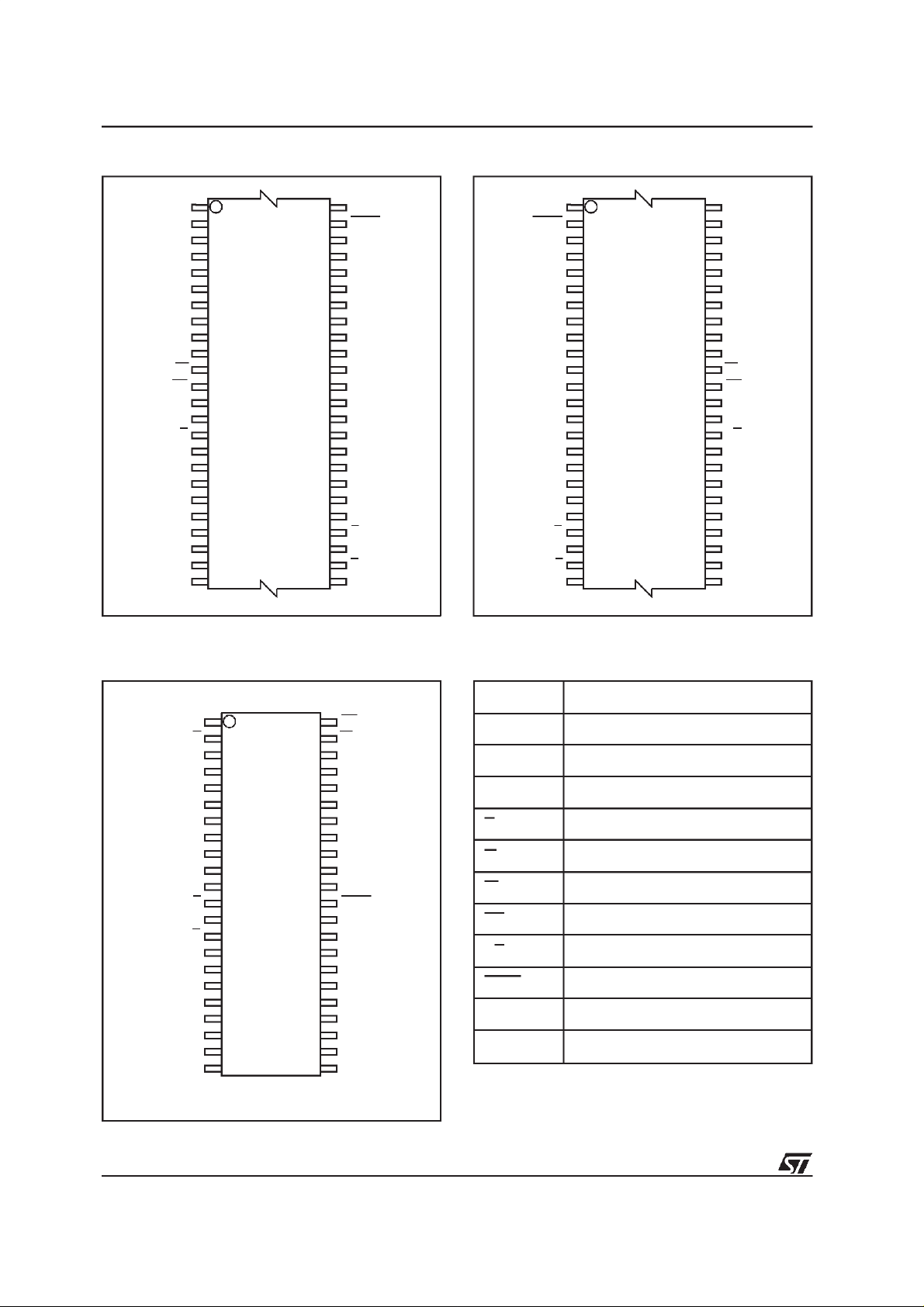

Figure 2A. TSOP Pin Connections

A15

1

A14

A13

A12

A11

A10 DQ14

A9

A8

NC

NC

W

RP

NC

NC

RB

NC

A17

A7

A6

A5

A4

A3

A2

A1

M29F400T

12

M29F400B

13

(Normal)

24 25

48

37

36

AI01727B

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

E

A0

Figure 2B. TSOP Reverse Pin Connections

A15

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

V

SS

A0

1

M29F400T

12

M29F400B

13

(Reverse)

G

E

24 25

48

37

36

AI01728B

A14

A13

A12

A11

A10

A9

A8

NC

NC

W

RP

NC

NC

RB

NC

A17

A7

A6

A5

A4

A3

A2

A1

Warning: NC = Not Connected. Warning: NC = Not Connected.

Figure 2C. SO Pin Connections

Table 1. Signal Names

A0-A17 Address Inputs

NC RP

1

2

3

A17 A8

A7

4

5

A6

6

A5

A4

7

A3

8

A2

9

A1

10

A0

11

M29F400T

M29F400B

12

13

14

15

16

17DQ1

18

19

20

21

V

SS

DQ0

DQ8

DQ9

DQ10

DQ3

DQ11

E

G

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

AI01729B

WRB

A9

A10

A11

A12

A13

A14

A15

A16

BYTE

V

SS

DQ15A–1

DQ7

DQ14

DQ6

DQ13

DQ5DQ2

DQ12

DQ4

V

CC

DQ0-DQ7 Data Input/Outputs, Command Inputs

DQ8-DQ14 Data Input/Outputs

DQ15A–1 Data Input/Output or Address Input

E Chip Enable

G Output Enable

W Write Enable

RP Reset / Block TemporaryUnprotect

RB Ready/Busy Output

BYTE Byte/Word Organisation

V

CC

V

SS

Supply Voltage

Ground

Warning: NC = Not Connected.

2/34

M29F400T, M29F400B

Table 2. AbsoluteMaximum Ratings

Symbol Parameter Value Unit

T

A

T

BIAS

T

STG

(2)

V

IO

V

CC

V

(A9, E, G, RP)

Notes: 1. Except for the rating ”Operating Temperature Range”, stresses above those listedin theTable ”Absolute Maximum Ratings”

may cause permanent damage to the device. These are stress ratings only andoperation of thedevice at these or any other

conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute Maximum

Rating conditions for extended periods may affect device reliability.Refer also to the STMicroelectronicsSUREProgram and other

relevant qualitydocuments.

2. Minimum Voltage may undershoot to –2V during transition and for less than 20ns.

3. Depends on range.

Ambient Operating Temperature

TemperatureUnder Bias –50 to 125

Storage Temperature –65 to 150 °C

Input or OutputVoltages –0.6 to 7 V

Supply Voltage –0.6 to 7 V

(2)

A9, E, G, RP Voltage –0.6 to 13.5 V

DESCRIPTION (Cont’d)

graming and erase on programming equipment,

and temporarily unprotected to make changes in

the application.

Instructions for Read/Reset, Auto Select for reading the Electronic Signature or Block Protection

status,Programming, BlockandChipErase,Erase

Suspend and Resume are written to the devicein

cyclesof commandstoa CommandInterfaceusing

standard microprocessor write timings.

The device is offeredin TSOP48 (12x 20mm) and

SO44packages. Both normal and reversepinouts

are available for the TSOP48 package.

Organisation

TheM29F400 is organisedas512Kx8or 256Kx16

bitsselectable by the BYTE signal. When BYTEis

Low the Byte-widex8 organisation is selectedand

the address lines are DQ15A–1 and A0-A17. The

Data Input/Output signal DQ15A–1 acts as address line A–1 which selects the lower or upper

Byte of the memory wordfor output on DQ0-DQ7,

DQ8-DQ14 remain at High impedance. When

BYTEis High the memoryuses theaddress inputs

A0-A17 and the Data Input/Outputs DQ0-DQ15.

Memory control is provided by Chip Enable E,

OutputEnable G and Write Enable W inputs.

AReset/Block TemporaryUnprotection RPtri-level

input provides a hardware reset when pulled Low,

andwhenheld High(atVID)temporarily unprotects

blocks previously protected allowing them to be

programed anderased.Eraseand Program operations are controlled by an internal Program/Erase

Controller (P/E.C.). Status Registerdata output on

DQ7provides a Data Pollingsignal, and DQ6 and

(1)

(3)

–40 to 125

DQ2provide Toggle signals to indicate thestate of

the P/E.C operations. A Ready/Busy RB output

indicates the completionof theinternal algorithms.

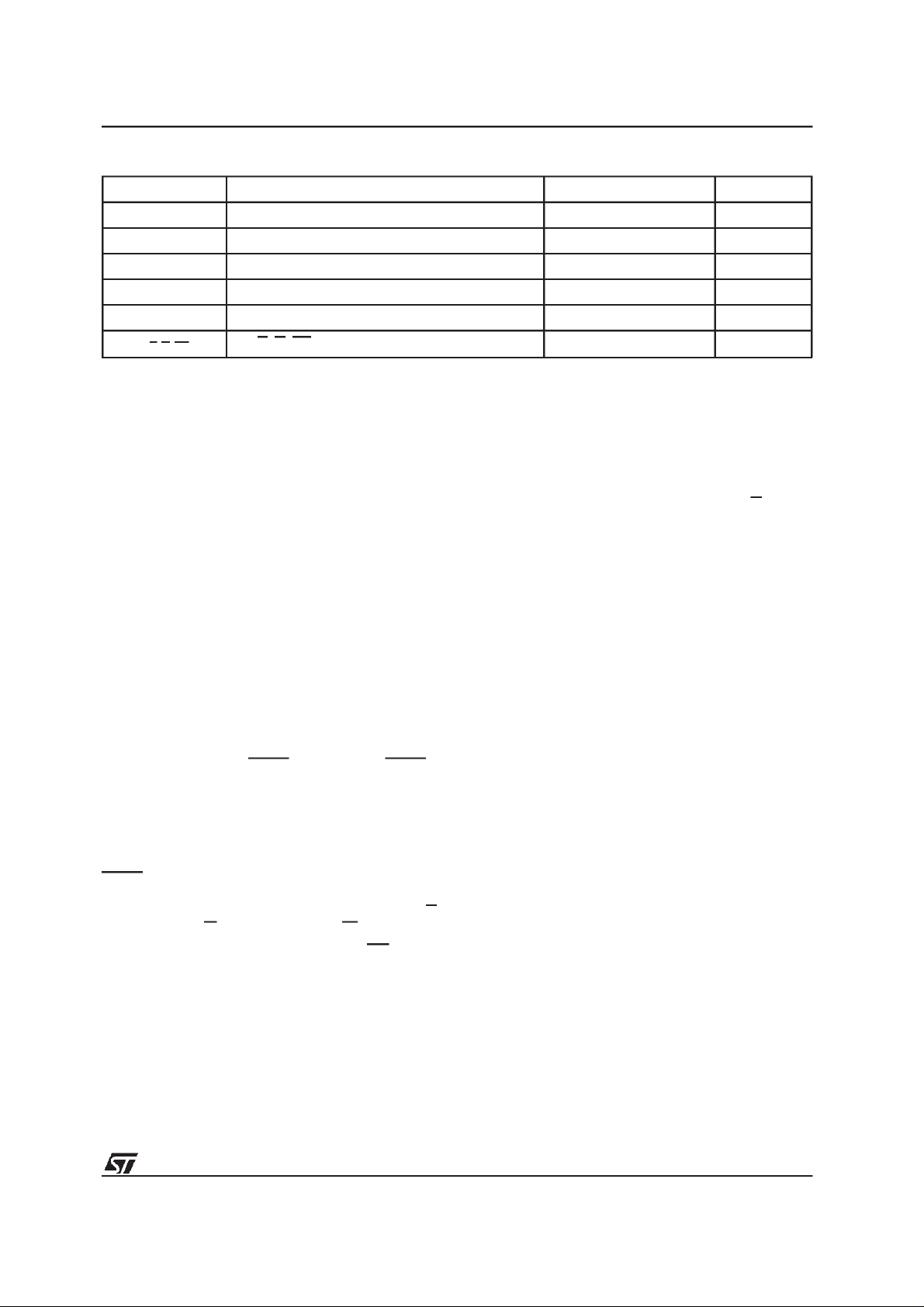

MemoryBlocks

The devices feature asymmetrically blocked architectureprovidingsystem memoryintegration.Both

M29F400Tand M29F400B devices have an array

of 11 blocks, one Boot Block of 16 KBytes or 8

KWords, two Parameter Blocks of 8 KBytes or 4

KWords, one Main Block of 32 KBytes or 16

KWords and sevenMainBlocksof 64KBytesor32

KWords. The M29F400T has the Boot Blockat the

top of the me mor y addre ss spac e and t he

M29F400B locates the Boot Block starting at the

bottom. The memory maps are showed in Figure

3. Eachblock can be erasedseparately, any combination of blocks can be specified for multi-block

eraseor the entire chip may be erased. The Erase

operations are managed automatically by the

P/E.C. The block erase operation can be suspended in order to read from or program to any

block not being ersased, and then resumed.

Block protection provides additional data security.

Each block can be separately protected or unprotected against Program or Erase on programming

equipment. All previously protected blocks can be

temporarily unprotected in the application.

Bus Operations

The following operations can be performed using

the appropriate bus cycles:Read(Array, Electronic

Signature, Block Protection Status), Write command,Output Disable, Standby, Reset, Block Protect ion, Unprotection, Protection Verify,

Unprotection Verify and Block Temporary Unpro-

C

°

C

°

tection. See Tables 4 and5.

3/34

M29F400T, M29F400B

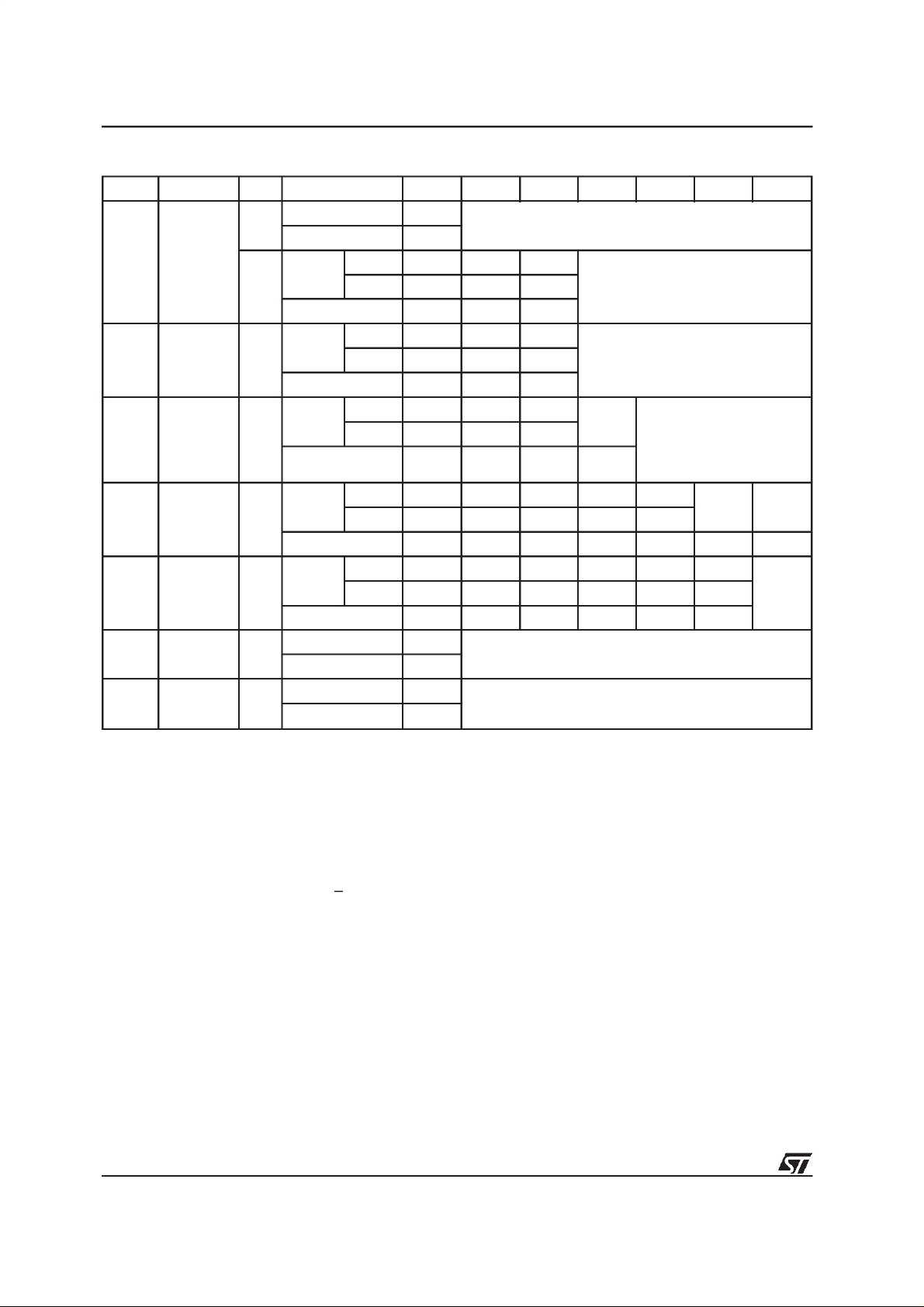

Figure 3. MemoryMap and Block Address Table (x8)

7FFFFh

7C000h

7BFFFh

7A000h

79FFFh

78000h

77FFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

00000h

M29F400T

16K BOOT BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

32K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

7FFFFh

70000h

6FFFFh

60000h

5FFFFh

50000h

4FFFFh

40000h

3FFFFh

30000h

2FFFFh

20000h

1FFFFh

10000h

0FFFFh

08000h

07FFFh

06000h

05FFFh

04000h

03FFFh

00000h

M29F400B

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

64K MAIN BLOCK

32K MAIN BLOCK

8K PARAMETER BLOCK

8K PARAMETER BLOCK

16K BOOT BLOCK

AI01730

CommandInterface

Instructions, made up of commands written in cycles,can be given to the Program/Erase Controller

through a Command Interface (C.I.). For added

data protection, program or erase execution starts

after4 or6 cycles.The first,second,fourthand fifth

cycles are used to input Coded cycles to the C.I.

This Coded sequence is the same for all Program/Erase Controller instructions. The ’Command’itself and its confirmation,when applicable,

are given on the third, fourth or sixth cycles. Any

incorrect command or any improper commandsequence will reset the device toRead Array mode.

Instructions

Seven instructions are defined to perform Read

Array, Auto Select(to readthe ElectronicSignature

or BlockProtection Status),Program, BlockErase,

Chip Erase, Erase Suspend and Erase Resume.

The internal P/E.C. automatically handles all timing and verification of the Program and Erase

operations. The StatusRegister Data Polling,Toggle, Error bits and the RB output may be read at

4/34

any time, duringprogramming or erase,to monitor

the progressof the operation.

Instructions are composed of upto six cycles. The

first two cycles input a Coded sequence to the

CommandInterfacewhichis commonto allinstructions (see Table 8). The third cycle inputs the

instruction set-up command. Subsequent cycles

outputthe addressed data, Electronic Signature or

Block Protection Status for Read operations. In

orderto giveadditional dataprotection, theinstructions for Program and Block or ChipErase require

furthercommand inputs.For a Programinstruction,

the fourth command cycle inputs the address and

data to be programmed. For an Erase instruction

(Block or Chip), the fourth and fifth cycles input a

further Coded sequence before the Erase confirm

commandon the sixth cycle. Erasureof a memory

blockmaybe suspended, inordertoreaddatafrom

anotherblock or to programdata in anotherblock,

and then resumed.

When power is first applied or if VCCfalls below

V

, the command interface is reset to Read

LKO

Array.

M29F400T, M29F400B

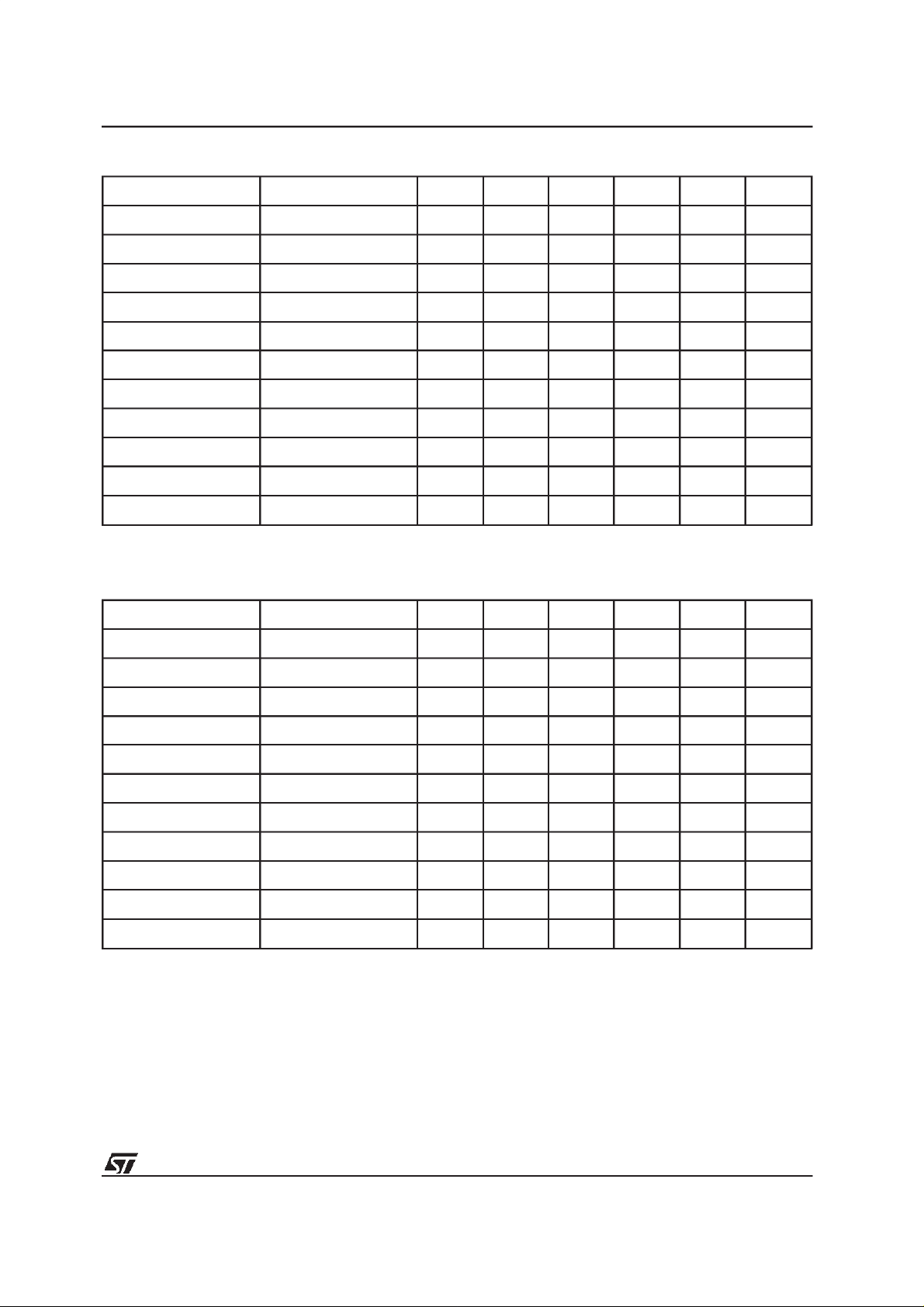

Table 3A. M29F400T Block Address Table

Address Range (x8) Address Range (x16) A17 A16 A15 A14 A13 A12

00000h-0FFFFh 00000h-07FFFh 0 0 0 X X X

10000h-1FFFFh 08000h-0FFFFh 0 0 1 X X X

20000h-2FFFFh 10000h-17FFFh 0 1 0 X X X

30000h-3FFFFh 18000h-1FFFFh 0 1 1 X X X

40000h-4FFFFh 20000h-27FFFh 1 0 0 X X X

50000h-5FFFFh 28000h-2FFFFh 1 0 1 X X X

60000h-6FFFFh 30000h-37FFFh 1 1 0 X X X

70000h-77FFFh 38000h-3BFFFh 1 1 1 0 X X

78000h-79FFFh 3C000h-3CFFFh 1 1 1 1 0 0

7A000h-7BFFFh 3D000h-3DFFFh 1 1 1 1 0 1

7C000h-7FFFFh 3E000h-3FFFFh 1 1 1 1 1 X

Table 3B. M29F400B Block Address Table

Address Range (x8) Address Range (x16) A17 A16 A15 A14 A13 A12

00000h-03FFFh 00000h-01FFFh 0 0 0 0 0 X

04000h-05FFFh 02000h-02FFFh 0 0 0 0 1 0

06000h-07FFFh 03000h-03FFFh 0 0 0 0 1 1

08000h-0FFFFh 04000h-07FFFh 0 0 0 1 X X

10000h-1FFFFh 08000h-0FFFFh 0 0 1 X X X

20000h-2FFFFh 10000h-17FFFh 0 1 0 X X X

30000h-3FFFFh 18000h-1FFFFh 0 1 1 X X X

40000h-4FFFFh 20000h-27FFFh 1 0 0 X X X

50000h-5FFFFh 28000h-2FFFFh 1 0 1 X X X

60000h-6FFFFh 30000h-37FFFh 1 1 0 X X X

70000h-7FFFFh 38000h-3FFFFh 1 1 1 X X X

5/34

M29F400T, M29F400B

SIGNALDESCRIPTIONS

See Figure 1 and Table1.

AddressInputs (A0-A17). The addressinputs for

thememoryarrayare latchedduringa writeoperation on the falling edge of Chip Enable E or Write

Enable W. In Word-wide organisation the address

lines are A0-A17, in Byte-wi de organisation

DQ15A–1 acts as an additional LSB address line.

WhenA9 is raised to VID, either a Read Electronic

Signature Manufacturer or Device Code, Block

Protection Status or a Write Block Protection or

Block Unprotection is enabled depending on the

combination of levelson A0, A1,A6, A12 and A15.

Data Input/Outputs (DQ0-DQ7). These Inputs/Outputsare used in theByte-wide and Wordwide or ganisatio ns. The i nput is data to be

programmed in the memory array or a command

to be written to the C.I. Both are latched on the

rising edge of Chip Enable E or Write Enable W.

The output is data from the Memory Array, the

Electronic Signature Manufacturer or Device

codes, the Block Protection Status or the Status

register Data Pollingbit DQ7, the Toggle Bits DQ6

and DQ2, the Error bit DQ5 or the Erase Timer bit

DQ3. Outputs are valid when Chip Enable E and

Output Enable G are active. The output is high

impedance when the chip is deselected or the

outputsaredisabledandwhen RP isata Lowlevel.

Data Input/Outputs (DQ8-DQ14 and DQ15A–1).

These Inputs/Outputs are additionally used in the

Word-wideorganisation.When BYTEisHighDQ8DQ14 and DQ15A–1 act as the MSB of the Data

Input or Output, functioning as describedforDQ0DQ7 above, and DQ8-DQ15 are ’don’t care’ for

command inputs or status outputs. When BYTEis

Low,DQ8-DQ14are highimpedance, DQ15A–1is

the Address A–1input.

Chip Enable (E). The Chip Enable input activates

the memory control logic, input buffers, decoders

andsenseamplifiers.EHighdeselectsthememory

andreducesthe powerconsumptionto thestandby

level. E can also be used to control writing to the

command register and to the memoryarray, while

Wremainsat a lowlevel.The ChipEnablemustbe

forcedto VIDduringtheBlockUnprotection operation.

Output Enable (G). The Output Enable gates the

outputs through the data buffers during a read

operation. When G is High the outputs are High

impedance. G must be forced to VIDlevel during

BlockProtection and Unprotectionoperations.

WriteEnable(W). This input controlswriting tothe

CommandRegisterandAddressand Datalatches.

Byte/Word Organization Select (BYTE). The

BYTEinput selectstheoutputconfiguration forthe

device: Byte-wide (x8) mode or Word-wide (x16)

mode. When BYTEis Low, the Byte-wide mode is

selectedand the data is read andprogrammed on

DQ0-DQ7. In this mode, DQ8-DQ14 are at high

impedance and DQ15A–1 is the LSB address.

When BYTE is High, the Word-wide mode is selected and the data is read and programmed on

DQ0-DQ15.

Ready/Busy Output (RB). Ready/Busy is an

open-drainoutputandgivestheinternalstateof the

P/E.C.of the device. When RB is Low,the device

is Busy with a Program or Erase operation and it

will not accept any additional program or erase

instructionsexcept the Erase Suspendinstruction.

WhenRB isHigh, thedeviceis readyfor anyRead,

Program or Erase operation. The RB will also be

High when the memory is put in EraseSuspend or

Standbymodes.

Reset/Block Temporary Unprotect Input (RP).

The RP Input provides hardware reset and protected block(s) temporary unprotection functions.

Reset of the memory is acheived by pulling RP to

VILfor at least 500ns. When the reset pulse is

given,if the memoryis in Reador Standby modes,

it will be available for new operations in 50ns after

the rising edge of RP. If the memory is in Erase,

Erase Suspend or Program modes the reset will

take 10µs during which the RB signal will be held

atVIL.Theendofthe memoryresetwillbeindicated

by the rising edge of RB.A hardware reset during

anEraseor Program operationwill corruptthe data

being programmed or the sector(s)being erased.

Temporary block unprotection is made by holding

RP at VID. In this condition previously protected

blocks can be programmed or erased. The transition of RP from VIHto VIDmust slower than 500ns.

When RP is returned from VIDto VIHall blocks

temporarily unprotected will be again protected.

VCCSupply Voltage. The power supply for all

operations (Read, Program and Erase).

VSSGround. VSSis the reference for all voltage

measurements.

6/34

M29F400T, M29F400B

DEVICE OPERATIONS

See Tables 4, 5 and 6.

Read. Read operations are used to output the

contents of the Memory Array, the Electronic Signature,the Status Register or the BlockProtection

Status. Both Chip Enable E andOutputEnable G

must be low in order to read the output of the

memory.

Write.Writeoperationsare used to giveInstruction

Commands to the memory or to latch input datato

be programmed. Awrite operationis initiatedwhen

Chip Enable E is Low and Write Enable W is Low

withOutput Enable G High.Addresses arelatched

onthe fallingedge of W or E whicheveroccurs last.

CommandsandInputDataarelatchedontherising

edge of W or E whicheveroccurs first.

OutputDisable. Thedataoutputs are highimpedancewhen the Output Enable G isHigh withWrite

EnableW High.

Standby. The memory is in standby when Chip

Enable E isHigh and the P/E.C.is idle. The power

consumption is reduced to the standby level and

the outputs are high impedance, independent of

the OutputEnable G or WriteEnable W inputs.

Automatic Standby. After 150ns of bus inactivity

andwhen CMOSlevels are drivingthe addresses,

the chip automatically enters a pseudo-standby

modewhereconsumptionis reducedto theCMOS

standbyvalue, while outputs still drive the bus.

Electronic Signature. Two codes identifying the

manufacturer andthe device canbe read fromthe

memory. The manufacturer’s code for STMicroelectronics is20h,the devicecodeisD5hforthe

M29F400T (TopBoot) and D6h for the M29F400B

(Bottom Boot). These codes allow programming

equipment or applications to automatically match

their inter f ace t o t he c har acteri s t ic s of t he

M29F400. The Electronic Signature is output by a

Read operation when the voltage applied to A9 is

atVIDandaddressinputsA1 isLow.The manufacturer code is output when the Address input A0 is

Low and the device code when this input is High.

Other Address inputs are ignored. The codes are

output on DQ0-DQ7.

The ElectronicSignature can alsobe read,without

raisingA9 to VID, by giving the memory the Instruction AS. If the Byte-wide configuration is selected

thecodes areoutputonDQ0-DQ7with DQ8-DQ14

at High impedance; if the Word-wide configuration

is selected the codes are outputonDQ0-DQ7with

DQ8-DQ15at 00h.

Block Protection. Each block can be separately

protected against Program or Erase on programming equipment. Block protection provides additional data security, as it disables all program or

eraseoperations. Thismodeisactivatedwhenboth

A9 and G are raised to VIDand an address in the

blockis applied on A12-A17. The Block Protection

algorithm is shownin Figure 14. Blockprotectionis

initiated on the edge of W fallingto VIL. Then after

a delay of 100µs, the edge of W rising to VIHends

the protectionoperations. Blockprotectionverify is

achieved by bringingG, E, A0 and A6to VILandA1

to VIH, whileW isat VIHandA9 at VID. Underthese

conditions, reading the data output will yield 01h if

the block defined by the inputs on A12-A17 is

protected. Any attempt to program or erase a protected block will be ignored by the device.

Block Temporary Unprotection. Any previously

protected block can be temporarily unprotected in

orderto change storeddata.The temporaryunprotection mode is activated by bringing RP to VID.

During the temporary unprotection mode the previously protected blocks are unprotected. A block

can be selected and data can be modified by

executingtheEraseor Programinstructionwiththe

RPsignalheld at VID. When RP isreturned to VIH,

all the previously protected blocks are again protected.

Block Unprotection. All protected blocks can be

unprotected on programming equipment to allow

updating of bit contents. All blocks must first be

protected before the unprotection operation. Block

unprotection is activatedwhen A9, G and E are at

VIDand A12, A15 at VIH. The Block Unprotection

algorithm is shown in Figure 15. Unprotection is

initiatedbytheedge of Wfallingto VIL.Aftera delay

of 10ms, the unprotection operation will end. Unprotection verify is achievedbybringing G and E to

VILwhileA0 is at VIL, A6 and A1 are at VIHand A9

remains at VID. In these conditions, reading the

outputdata willyield 00h if the blockdefined by the

inputsA12-A17 has beensuccesfullyunprotected.

Eachblockmustbe separatelyverifiedbygiving its

addressin order to ensure that it has been unprotected.

7/34

M29F400T, M29F400B

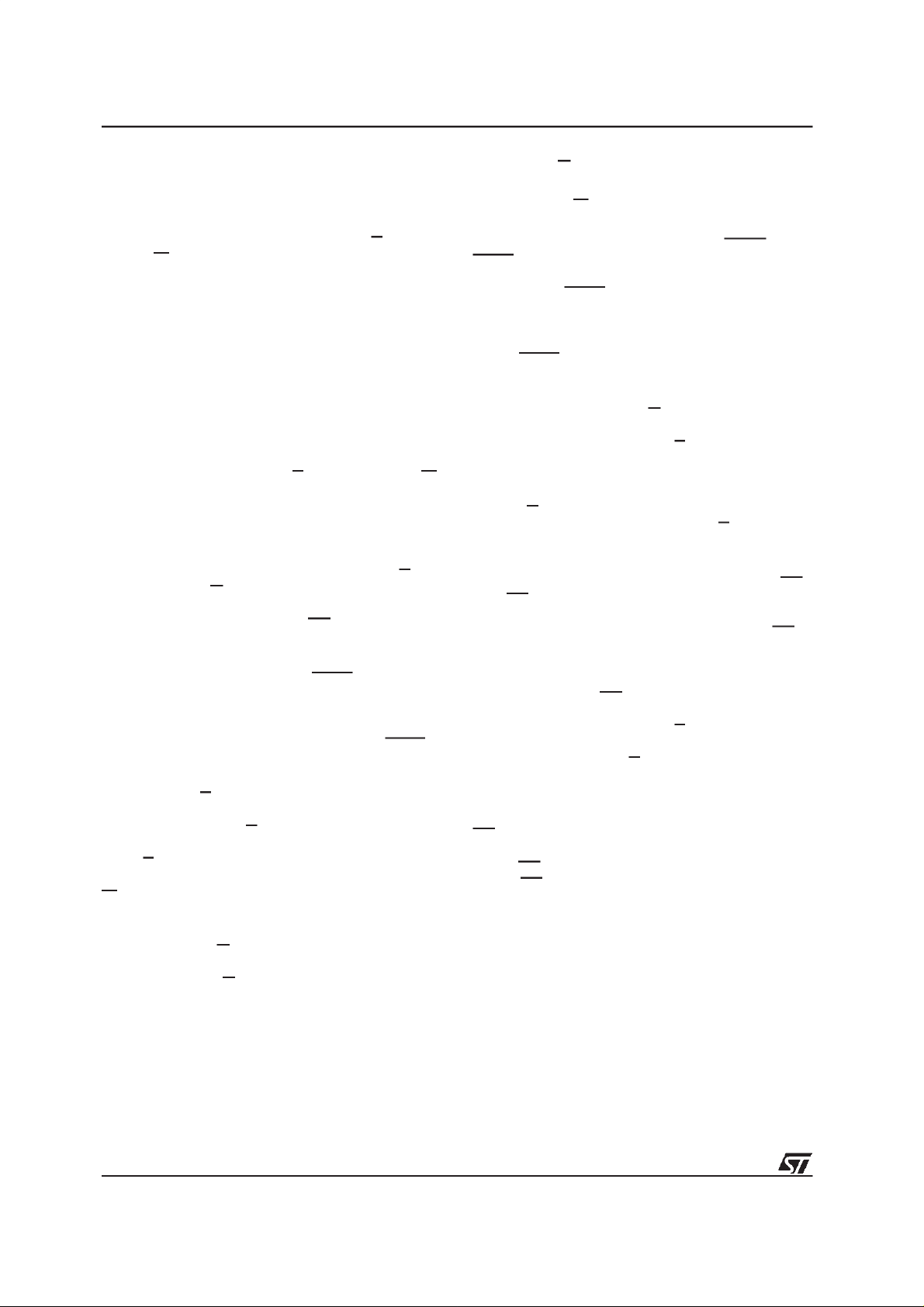

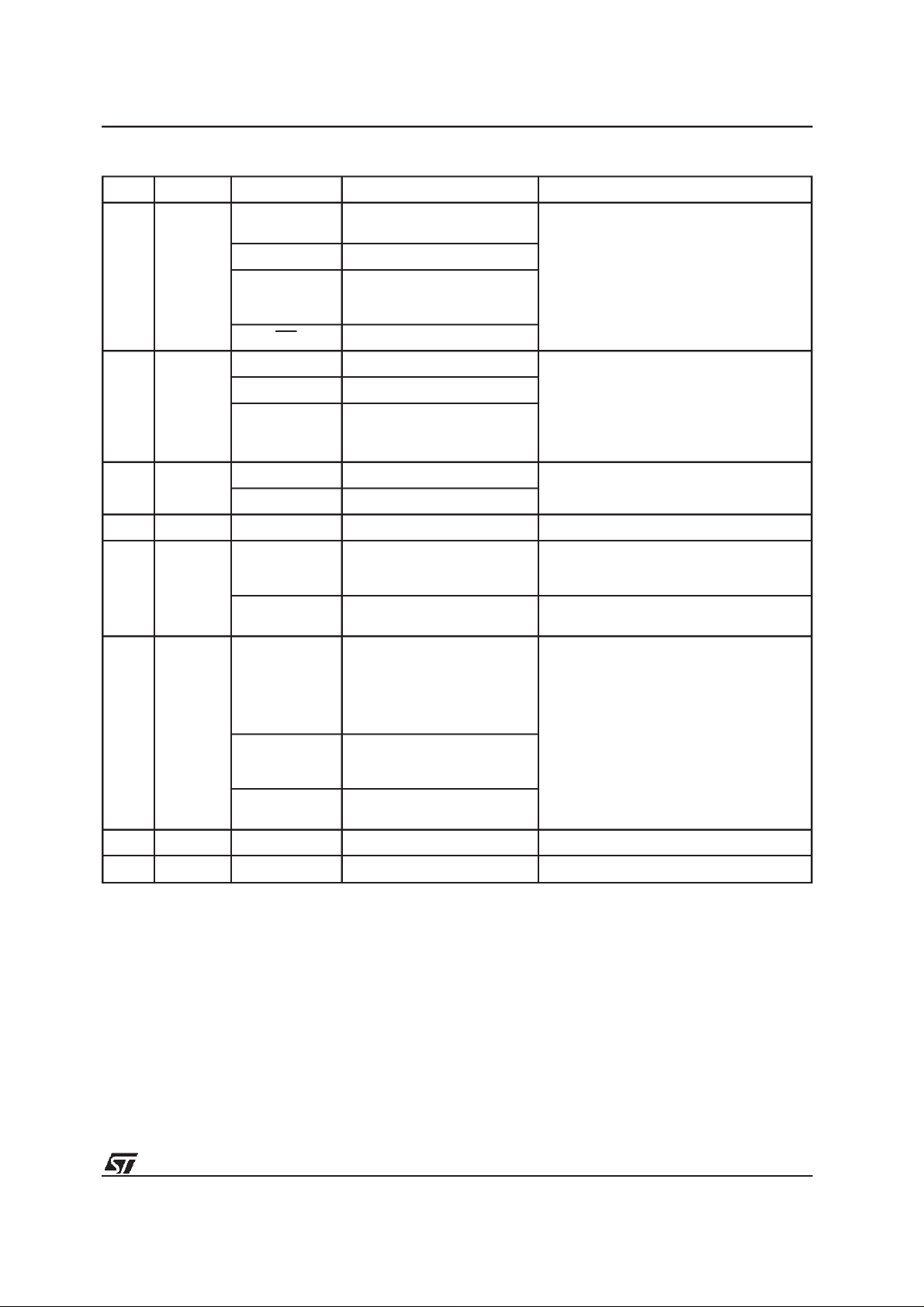

Table 4. User Bus Operations

(1)

Operation E G W RP BYTE A0 A1 A6 A9 A12 A15

Read Word V

Read Byte V

Write Word V

Write Byte V

Output Disable V

Standby V

ILVIL

ILVIL

ILVIH

ILVIH

ILVIH

IH

Reset X X X V

Block

Protection

Blocks

Unprotection

Block

Protection

(2,4)

Verify

Block

Unprotection

(2,4)

Verify

Block

Temporary

Unprotection

Notes: 1. X = V

2. Block Address must be givenon A12-A17bits.

3. See Table6.

VILVIDVILPulse V

(2,4)

VIDVIDVILPulse V

(4)

VILV

VILV

XX X V

or V

IL

IH

V

V

V

IH

IH

V

V

IH

IH

V

V

IL

IH

V

V

IL

IH

V

V

IH

IH

A0 A1 A6 A9 A12 A15

IH

V

A0 A1 A6 A9 A12 A15

IL

V

A0 A1 A6 A9 A12 A15 Data Input Data Input

IH

V

A0 A1 A6 A9 A12 A15

IL

X XXXXXX Hi-Z Hi-Z Hi-Z

XXVIHX XXXXXX Hi-Z Hi-Z Hi-Z

X XXXXXX Hi-Z Hi-Z Hi-Z

IL

XXXXVIDXX X X X

IH

XXXXVIDVIHV

IH

V

V

IL

IH

V

IL

IH

XVILVIHVILVIDA12 A15 X X

IH

V

XVILVIHVIHVIDA12 A15 X X

IH

X XXXXXX X X X

ID

4. Operation performed on programming equipment.

IH

DQ15

A–1

Data

Output

Address

Input

Address

Input

DQ8-

DQ14

Data

Output

Hi-Z

Hi-Z

DQ0-DQ7

Data

Output

Data

Output

Data

Input

Data

Input

XXX

Block

Protect

Status

Block

Protect

Status

(3)

(3)

Table5. ReadElectronic Signature (following AS instruction or with A9 = VID)

Org. Code Device E G W BYTE A0 A1

Word-

wide

Manufact.

Code

Device

Code

Manufact.

Code

M29F400T V

M29F400B V

VILV

V

IL

VILV

IL

VILV

IL

VILV

V

IL

V

IH

V

IH

V

IH

V

IH

VILVILDon’t Care 0 00h 20h

IH

V

IH

IH

IH

V

IH

VILVILDon’t Care

IL

Byte-

wide

Device

M29F400T V

IL

VILV

V

IH

V

IL

IH

Code

M29F400B V

IL

VILV

V

IH

V

IL

IH

Other

Addresses

VILDon’t Care 0 00h D5h

VILDon’t Care 0 00h D6h

VILDon’t Care

VILDon’t Care

DQ15

A–1

Don’t

Care

Don’t

Care

Don’t

Care

Table6. Read Block Protection with AS Instruction

Code E G W A0 A1 A12 - A17

Protected Block V

Unprotected Block V

IL

IL

V

IL

V

IL

V

IH

V

IH

V

IL

V

IL

V

IH

V

IH

BlockAddress Don’t Care 01h

BlockAddress Don’t Care 00h

Addresses

Other

DQ8 DQ14

DQ0 -

DQ7

Hi-Z 20h

Hi-Z D5h

Hi-Z D6h

DQ0 - DQ7

8/34

M29F400T, M29F400B

INSTRUCTIONSAND COMMANDS

The Command Interface latches commands written to the memory. Instructions are made up from

one or more commandsto perform Read Memory

Array, Read Electronic Signature, ReadBlockProtection, Program, Block Erase, Chip Erase, Erase

Suspend and Erase Resume. Commands are

made of address and data sequences. The instructionsrequirefrom 1 to6 cycles,the firstor first

three of which are alwayswrite operations used to

initiatetheinstruction.They are followed by either

furtherwrite cycles to confirmthe first commandor

executethe commandimmediately. Commandsequencing must be followed exactly. Any invalid

combination of commands will reset the device to

Read Array. The increased number of cycles has

been chosen to assure maximum data security.

Instructions are initialised by twoinitial Coded cycleswhich unlock theCommand Interface.In addition, for Erase, instruction confirmation is again

preceded by the two Coded cycles.

StatusRegister Bits

P/E.C.statusis indicatedduringexecutionby Data

Polling on DQ7, detection of Toggle on DQ6 and

DQ2, or Error on DQ5 and Erase Timer DQ3 bits.

Any read attempt during Program or Erase commandexecutionwillautomatically output thesefive

StatusRegisterbits.The P/E.C.automatically sets

bits DQ2, DQ3, DQ5, DQ6 and DQ7. Other bits

(DQ0, DQ1 and DQ4) are reserved for future use

and should be masked. See Tables 9 and 10.

Data Polling Bit (DQ7). When Programming operations are in progress, this bit outputs the complement of the bit being programmed on DQ7.

DuringErase operation, it outputs a ’0’.After completionof the operation, DQ7 will outputthebit last

programmed or a ’1’ after erasing. Data Polling is

valid and only effective during P/E.C. operation,

that is after the fourth W pulse for programming or

after the sixth W pulse for erase. It must be performed at theaddress being programmed or at an

address within the block being erased. If all the

blocksselectedfor erasureare protected, DQ7will

be setto ’0’for about100µs, and thenreturn to the

previous addressed memory data value. See Figure 11for the Data Pollingflowchart and Figure 10

for the Data Polling waveforms. DQ7 will also flag

the Erase Suspend mode by switching from ’0’ to

’1’ at the start of the Erase Suspend. In order to

monitor DQ7 in the Erase Suspend mode an address within a block being erased must be provided. For a Read Operation in Erase Suspend

mode, DQ7 will output ’1’ if the read is attempted

onablockbeing erasedandthedatavalueon other

blocks. During Program operation in Erase SuspendMode, DQ7 will have the same behaviour as

in the normal program execution outside of the

suspend mode.

ToggleBit (DQ6). When Programming or Erasing

operations are in progress,successiveattemptsto

readDQ6will outputcomplementarydata.DQ6 will

toggle following toggling of either G, or E when G

is low. The operation is completed when two successivereadsyieldthe sameoutput data.The next

readwilloutputthe bitlastprogrammed ora’1’after

erasing. The toggle bit DQ6 is valid only during

P/E.C.operations, that is after the fourth W pulse

for programming or after the sixth W pulse for

Erase. If the blocks selected for erasure are protected, DQ6 will toggle for about 100µs and then

returnbackto Read. DQ6willbe setto’1’if a Read

operation is attemptedonan EraseSuspend block.

When erase is suspended DQ6 will toggle during

programming operations in a blockdifferent to the

block in Erase Suspend. Either E or G toggling will

cause DQ6 to toggle.See Figure 12 for Toggle Bit

flowchartand Figure 13 for Toggle Bit waveforms.

Table 7. Commands

Hex Code Command

00h Invalid/Reserved

10h Chip Erase Confirm

20h Reserved

30h Block Erase Resume/Confirm

80h Set-up Erase

90h

A0h Program

B0h Erase Suspend

F0h Read Array/Reset

Read Electronic Signature/

Block Protection Status

9/34

M29F400T, M29F400B

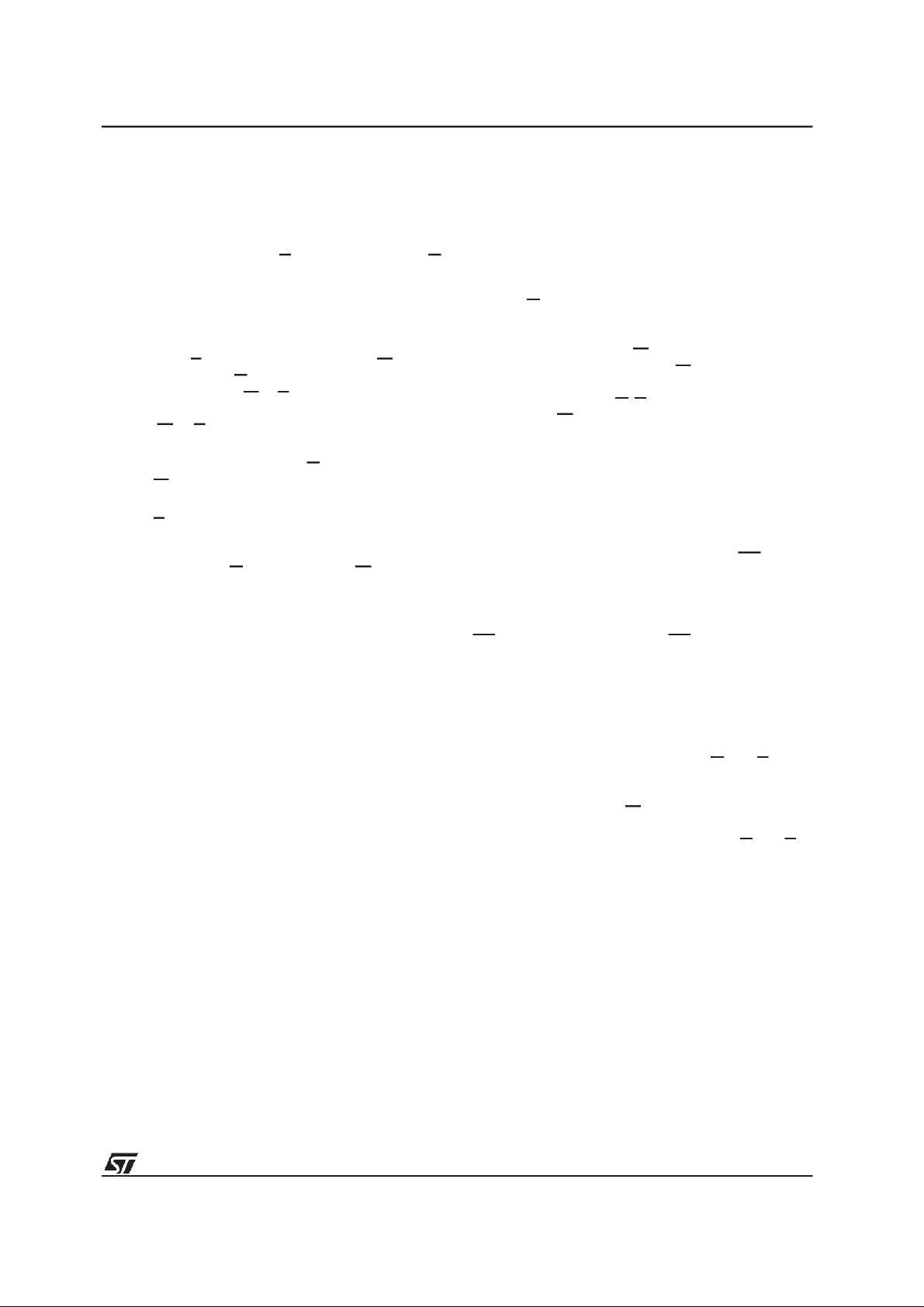

Table 8. Instructions

(1)

Mne. Instr. Cyc. 1st Cyc. 2ndCyc. 3rdCyc. 4th Cyc. 5th Cyc. 6th Cyc. 7th Cyc.

(3,7)

RD

Read/Reset

(2,4)

Memory Array

Addr.

1+

Data F0h

Byte

(3,7)

Addr.

3+

Word 5555h 2AAAh 5555h

X

Read Memory Array until a new write cycle is initiated.

AAAAh 5555h AAAAh

Read Memory Array until a new write cycle

is initiated.

Data AAh 55h F0h

(4)

Auto Select 3+

AS

Addr.

(3,7)

Word 5555h 2AAAh 5555h

Read Electronic Signature or Block

Protection Status until a new write cycle is

initiated. See Note 5 and 6.

Byte AAAAh 5555h AAAAh

Data AAh 55h 90h

PG Program 4

BE Block Erase 6

Byte AAAAh 5555h AAAAh

(3,7)

Addr.

Word 5555h 2AAAh 5555h

Data AAh 55h A0h

Byte AAAAh 5555h AAAAh AAAAh 5555h

(3,7)

Addr.

Word 5555h 2AAAh 5555h 5555h 2AAAh

Program

Address

Program

Data

Read Data Polling or Toggle Bit

until Program completes.

Block

Address

Additional

Data AAh 55h 80h AAh 55h 30h 30h

CE Chip Erase 6

Addr.

Word 5555h 2AAAh 5555h 5555h 2AAAh 5555h

Byte AAAAh 5555h AAAAh AAAAh 5555h AAAAh

(3,7)

Data AAh 55h 80h AAh 55h 10h

(3,7)

(10) Erase

ES

Notes: 1. Commands not interpreted in this table will defaulttoread array mode.

Suspend

Erase

ER

Resume

2. Await of t

before startingany new operation (seeTable14 and Figure9).

3. X = Don’t Care.

4. The first cycles of the RD or AS instructions are followed by read operations. Any number of readcycles canoccur after

the command cycles.

5. SignatureAddress bits A0,A1 at V

Device code.

6. Block Protection Address: A0 atV

7. For Coded cycles address inputs A15-A17 are don’t care.

8. Optional, additional Blocks addresses must be entered within the erase timeout delayafter last write entry,

timeout status can be verified through DQ3 value (see Erase TimerBit DQ3 description).

When full command is entered, read DataPolling or Togglebit until Erase is completed or suspended.

9. Read Data Polling, Togglebits or RB until Erase completes.

10.During Erase Suspend,Readand DataProgram functions are allowedin blocks not being erased.

is necessary after a Read/Resetcommand if the memory was in an Erase or Program mode

PLYH

Addr.

1

Data B0h

(3,7)

Addr.

1

Data 30h

will output Manufacturer code (20h).Address bits A0 at VIHandA1 at VILwill output

IL

,A1atVIHand A12-A17 within the Blockwill output the Block Protection status.

IL

X

Read until Toggle stops, then read all the data needed from any

Block(s) not being erased then ResumeErase.

X

Read Data Polling or ToggleBits until Erase completes or Erase is

suspended another time

Block

Note 9

(8)

10/34

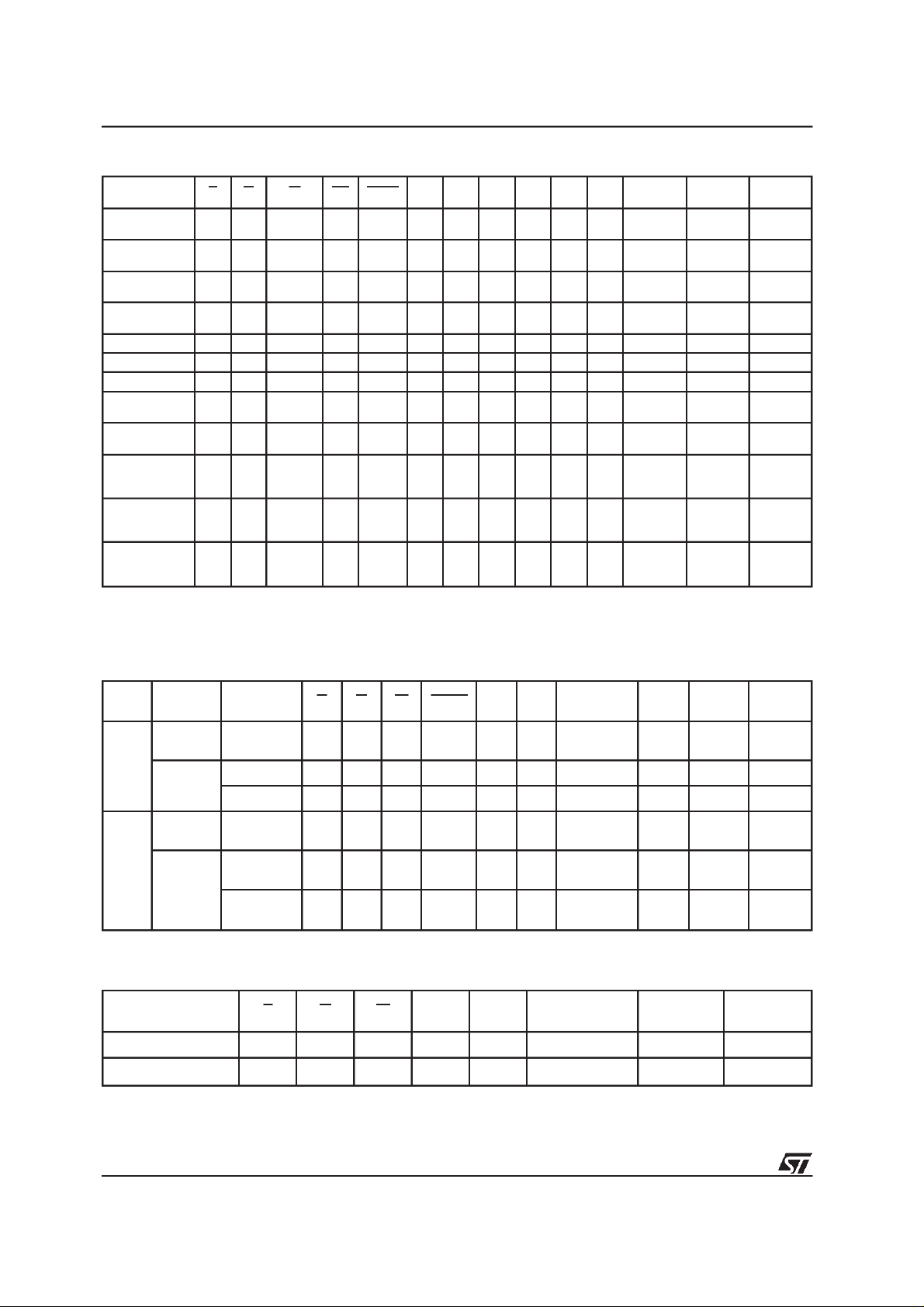

M29F400T, M29F400B

Table9. Status RegisterBits

DQ Name Logic Level Definition Note

Erase Complete or erase

block in Erase Suspend

Program Complete or data

of non erase block during

Erase Suspend

Erase Complete or Erase

Suspend on currently

addressed block

Indicates the P/E.C. status, check during

Program or Erase, and on completion

before checking bits DQ5 for Program or

Erase Success.

data on DQ6 while Programming or Erase

operations are on-going. DQ6 remains at

constant level when P/E.C. operations are

completed or Erase Suspend is

acknowledged.

Data

7

Polling

6 ToggleBit

’1’

’0’ Erase On-going

DQ

DQ Program On-going

’-1-0-1-0-1-0-1-’ Erase or Program On-going Successive reads output complementary

DQ Program Complete

’-1-1-1-1-1-1-1-’

5 Error Bit

4 Reserved

Erase

3

TimeBit

2 ToggleBit

1 Reserved

0 Reserved

Note:

Logic level ’1’ is High, ’0’ is Low. -0-1-0-0-0-1-1-1-0- represent bit value in successive Read operations.

’1’ Program or Erase Error

’0’ Program or Erase On-going

’1’ Erase Timeout Period Expired

’0’

’-1-0-1-0-1-0-1-’

1

DQ

Erase Timeout Period

On-going

Chip Erase, Erase or Erase

Suspend on the currently

addressed block.

Erase Error due to the

currently addressed block

(when DQ5 = ’1’).

Program on-going, Erase

on-going on another block or

Erase Complete

Erase Suspend read on

non Erase Suspend block

This bit is set to ’1’ in the case of

Programming or Erase failure.

P/E.C. Erase operation has started. Only

possible command entry is Erase Suspend

(ES).

An additional block to be erased in parallel

can be entered to the P/E.C.

Indicates the erase status and allows to

identify the erased block

11/34

Loading...

Loading...