64 Mbit (4Mb x16) 3V Supply FlexibleROM™ Memory

FEATURES SUMMARY

■ ONE TIME PROGRAMMABLE

■ SUPPLY VOLTAGE

–V

–V

■ ACCESS TIME

– 90ns at V

– 10 0, 110ns at V

■ PROGRAMMING TIME

– 9µs per Word typical

– Multiple Word Programming Option

■ SUITABLE FOR ON-BOARD PROGRAMMING

■ PROGRAM CONTROLLER

– Embedded Word Program algorithms

■ ELECTRONIC SIGNATURE

– Manufacturer Code: 0020h

– Device Code : 888Ah

=2.7 to 3.6V for Read

CC

= 11.4 to 12.6V for Program

PP

=3.0 to 3.6V

CC

= 2.7 to 3.6V

CC

(8s typical Chip Program)

M27W064

PRELIMINARY DATA

Figure 1. Packages

SO44 (M)

TSOP48 (N)

12 x 20mm

November 2002

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

1/23

M27W064

TABLE OF CONTENTS

FEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 1. Packages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Figure 2. Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 1. Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Figure 3. SO Connect ions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 4. TSOP Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

SIGNAL DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Address Inputs (A0-A21). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Data Inputs/Outputs (DQ0-DQ7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Data Inputs/Outputs (DQ8-DQ15). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

Chip Enable (E). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Output Enable (G). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

V

Supply Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

CC

V

Program Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

PP

Vss Ground.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

BUS OPERATIONS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Bus Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Bus Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Output Disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Automatic Standby. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Electronic Signature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 2. Bus Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

COMMAND INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Read/Reset Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Auto Select Command. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Word Program Command.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Multiple Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Setup Phase.. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Program Phase. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Verify Phase. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Exit Phase. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 3. Standard Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 4. Multiple Word Program Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 5. Program Times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 5. Multiple Word Program Flowchart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

2/23

M27W064

STATUS REGISTER. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Data Polling Bit (DQ7). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Toggle Bit (DQ6).. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Error Bit (DQ5). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

V

Status Bit (DQ4). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

PP

Multiple Word Program Bit (DQ0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Multiple Word Program Bit (DQ0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 6. Status Re gister Bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 6. Data Polling Fl ow ch ar t. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. Data Toggle Fl owchar t. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 7. Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 8. Operating and AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 8. AC Measurement I/O Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Figure 9. AC Measurement Load Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 9. Device Capaci ta n ce. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 10. DC Characte r i stics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 10. Read AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 7

Table 11. Read AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 11. Chip Enable Controlled, Write AC Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Table 12. Chip Enable Controlled, Write AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 9

SO44 - 44 lead Plastic Small Outline, 500 mils body width, Package Outline . . . . . . . . . . . . . . . . 19

SO44 - 44 lead Plastic Small Outline, 500 mils body width, Package Mechanical Data. . . . . . . . . 19

TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Outline . . . . . . . . . . . . . . . . . 20

TSOP48 - 48 lead Plastic Thin Small Outline, 12 x 20mm, Package Mech anical Data . . . . . . . . . 20

PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Table 15. Ordering Information Scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Table 16. Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3/23

M27W064

SUMMARY DESCRIPTION

The M27W064 is a 64 Mbit (4Mb x16) non-volatile,

One Time Programmable (OT P), FlexibleROM™

Memory. Read operations can be performed using

a single low voltage (2.7 to 3.6V) supply. Program

operations require an additional V

(11.4 to

PP

12.6V) power supply. On power-up the memory

defaults to Read mode where it can be read in the

same way as a ROM or EPROM.

Program commands are written to t he Command

Interface of the memory. An on-chip Program Controller (PC) simplifies the process of programming

the memory by taking care of all of the special operations that are required to update the memory

conte nts.

The M27W064 features an in novative command,

Multiple Word Program, used to program large

streams of data. It greatly reduces the total pro-

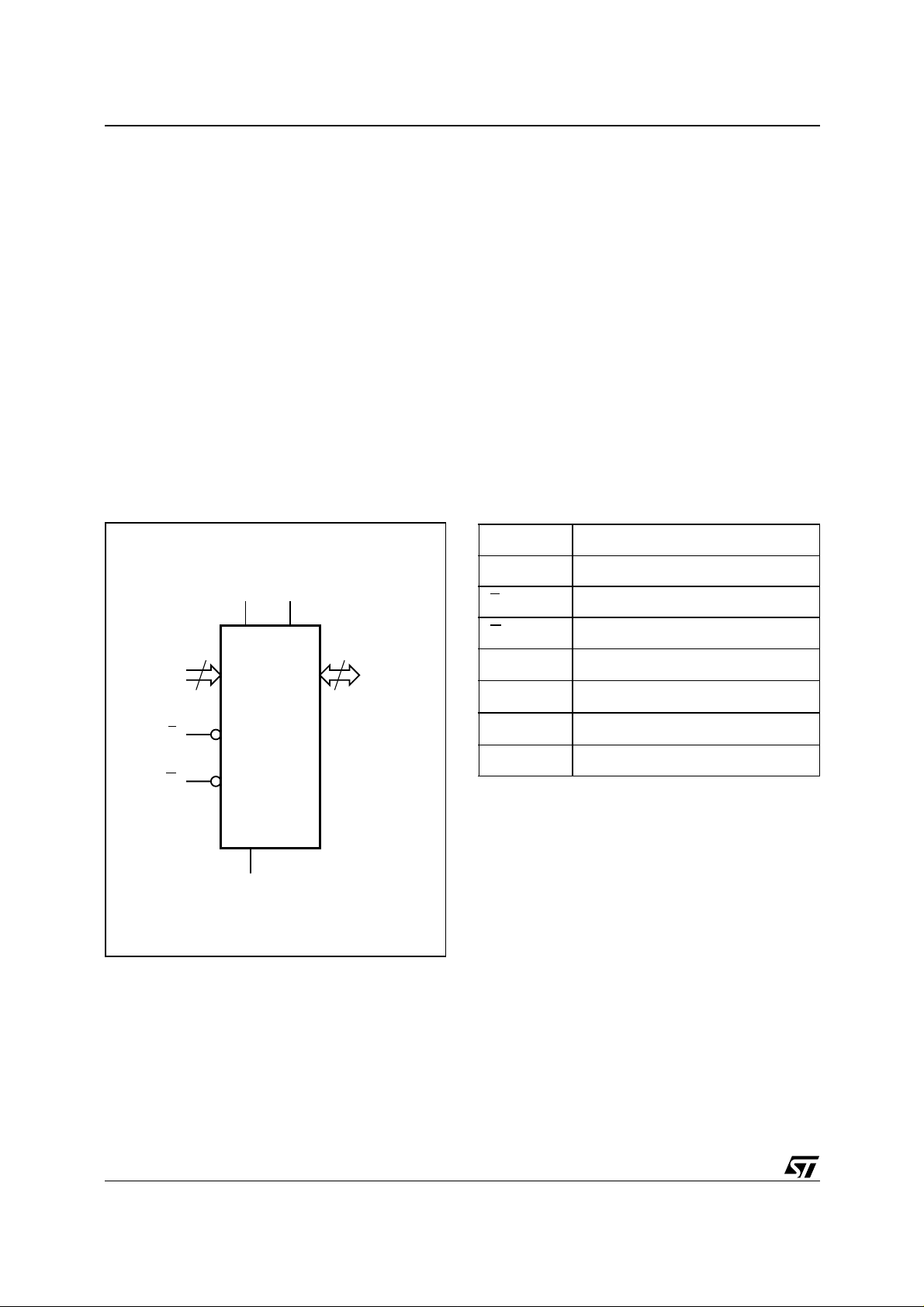

Figure 2. Logic Diagram Table 1. Signal Names

gramming time when a large number of Words are

written to the memory at any one time. Using this

command the entire memory can be program m ed

in 8s, compared to 36s us ing the standard Word

Progra m.

The end of a program operation can be de tected

and any error conditions identified. The command

set required to control the memory is consistent

with JEDEC standards.

Chip Enable and Output Enable signals control the

bus operation of the memory. They allo w simple

connection to most microprocessors, often without

additional logic.

The memory is offered in SO44 a nd TS OP48 (12

x 20mm) packages. T he mem ory is supplied with

all the bits set to ’1’.

A0-A21 Address Inputs

V

V

22

A0-A21 DQ0-DQ15

E

G

M27W064

V

CC

SS

PP

16

AI05960

DQ0-DQ15 Data Inputs/Outputs

E

G

V

CC

V

PP

V

SS

NC Not Connected Internally

Chip Enable

Output Enable

Supply Voltage read

Supply Voltage program

Ground

4/23

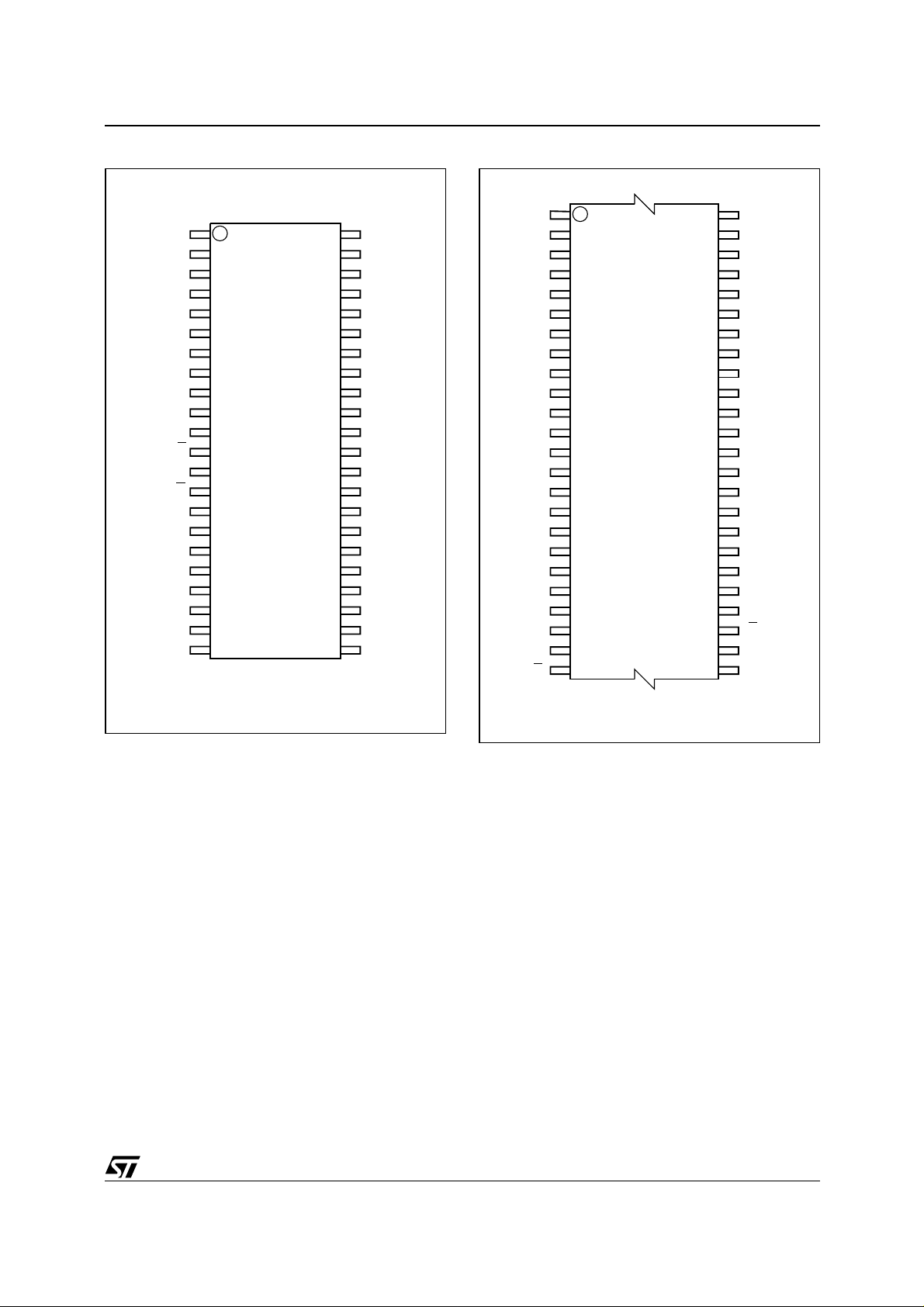

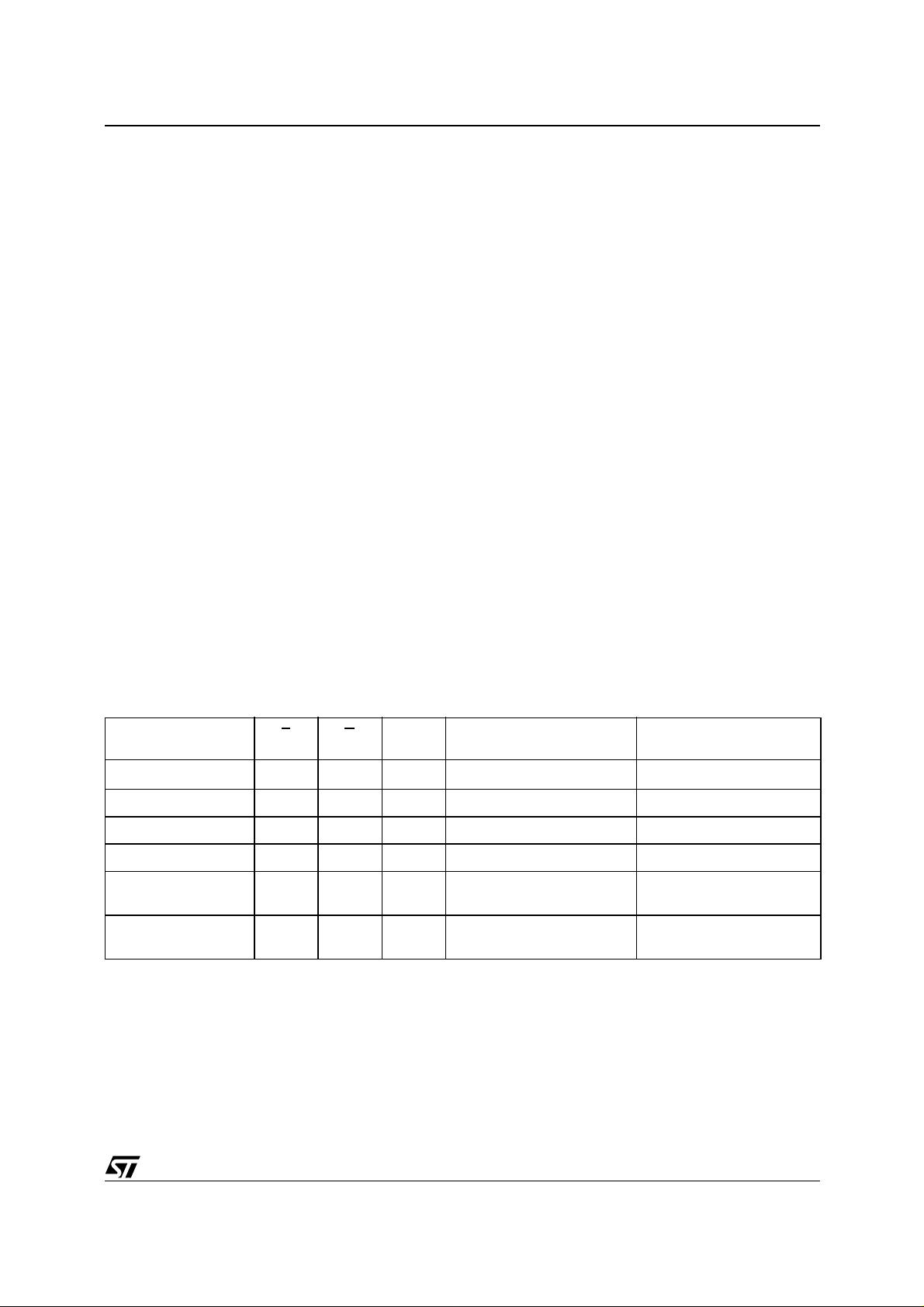

Figure 3. SO Connecti ons Figure 4. TSOP Con nections

M27W064

A21

A18

A17 A8

A7

A6

A5

A4

A3

A2

A1

A0

V

SS

DQ0

DQ8

1

2

3

4

5

6

7

8

9

10

11

M27W064

12

E

13

14

G

15

16

17DQ1

DQ9

18

19

DQ10

DQ3

20

21

DQ11

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

2322

A20

A19

A9

A10

A11

A12

A13

A14

A15

A16

V

PP

V

SS

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5DQ2

DQ12

DQ4

V

CC

AI05961

V

PP

A16

A15

A14

A13

A12

A11

A10

A9

A8

A19

A21

A20

A18

A17

A5

A0

A7

A6

A4

A3

A2

A1

1

12

M27W064

13

24 25

E

48

37

36

V

SS

V

SS

DQ15

DQ7

DQ14

DQ6

DQ13

DQ5

DQ12

DQ4

V

CC

V

CC

NC

DQ11

DQ3

DQ10

DQ2

DQ9

DQ1

DQ8

DQ0

G

V

SS

V

SS

AI05962

5/23

M27W064

SIGNAL DESCRIPTIONS

See Figure 2, Logic Diagram, and Table 1, Sign al

Names, for a brief overview of the signals connected to this de vice.

Address Inputs (A0-A21). The Address Inputs

select the cell s in th e memory array to a ccess during Bus Read operations. During Bus Write operations they control the commands sent to the

Command Interface of the Program Controller.

Data Inputs/Outputs (DQ0-DQ7). The Data Inputs/Outputs output the data stored at the selected

address during a Bus Read operation. During Bus

Write operations they represent the command

sent to the Command Interface of the Program

Controller. When reading the Status Register they

report the status of the ongoing algorithm.

Data Inputs/Outputs (DQ8-DQ15). The Data Inputs/Outputs output the data stored at the selected

address during a Bus Read operation. During Bus

Write operations the Command Interface does not

use these bits. When reading t he Status Register

these bits should be ignored.

Chip Enable (E

the memory, allowing Bus Read operat ions to be

performed. It also controls the B us Write operations, when V

Output Enable (G

trols the Bus Read operations of the memory. It

). The Chip Enable, E, activates

is in the VHH range.

PP

). The Ou tput Enable, G, con-

also allows Bus Write operations, when V

the V

V

range.

HH

Supply Voltage. The VCC Supply Voltage

CC

PP

is in

supplies the power for Read operations.

A 0.1µF capacitor should be connec ted between

the V

Supply Voltage pin and the VSS Ground

CC

pin to decouple the current surges from the power

supply. The PCB track widths must be sufficient to

carry the currents required during program operations, I

V

PP

.

CC3

Program Supply Voltage. VPP is both a

power supply and Write Protect pin. The two functions are selected by t he voltage range applie d t o

the pin.

When the V

is in the VHH range (see Table 10,

PP

DC Characteristic, for the relevant values) the Program operation is enabled. During such operations the V

If the V

must be stable in the VHH range.

PP

is kept under the VHH range, particularly

PP

in the voltage range 0 to 3.6V, any Program operation is disabled or stopped.

Note that V

must not be left floating o r uncon-

PP

nected as the device may become unreliable.

Vss Ground. The V

Ground is the reference

SS

for all voltage measurements.

6/23

BUS OPERATIONS

There are six standard bus operations that control

the device. These are Bus Read, Bus Wri te, Output Disable, Standby, Automatic Standby and

Electronic Signature. See Tables 2, Bus Operations, for a summary. Typically glitches of less

than 5ns on Chip Enable or Write Enable are ignored by the memory and do not affect bus operations.

Bus Read. Bus Read operations read from the

memory cells, or specific registers in the Command Interface. A valid Bus Read operation involves setting the desired address on the Address

Inputs and applying a Low signal, V

, to Chip En-

IL

able and Output Enable. The Data Inputs/Outpu ts

will output the value, see Figure 10, Read AC

Waveforms, and Table 11, Read AC Ch aracteristics, for details of when the output becomes valid.

Bus Write. Bus Write operations write to the

Command Interface. Bus Write is enabled only

when V

is set to VHH. A valid Bus W rite opera-

PP

tion begins by setting the desired addres s on the

Address Inputs. The Address Inputs are latched by

the Command Interface on the falling edge of Chip

Enable. The Data I nputs/Outputs are latched by

the Command Interface on the rising edge of Chip

Enable. Output Enable must remain High, V

IH

during the whole Bus W rite operat ion . See Figure

11, Write AC Waveforms, and Table 12, Write AC

Characteristics, for details of the timing requirements.

Output Disa bl e . The Data Inputs/Outputs are in

the high impedance s tate when Output Enable is

High, V

.

IH

Standby. When Chip Enable is High, V

memory enters Standby mode and the Data Inputs/Outputs pins are placed in the high-impedance state. To reduce the S upply Current to the

Standby Supply Current, I

be held within V

± 0.2V. For the Standby current

CC

, Chip Enable should

CC2

level see Table 10, DC Characteristics.

During program operation the memory will cont in-

ue to use the Program Supply Current, I

Program operation until the operation completes.

Automatic Standby. If CMOS levels (V

are used to drive the bus and the bus is inactive for

150ns or more the memory enters Automatic

Standby where the internal Supply Current is reduced to the Standby Supply Current, I

Data Inputs/Outputs will still output data if a Bus

Read operation is in progress.

Electronic Signature. The memory has two

codes, the manufacturer code and the device

code, that can be read to identify the memory.

These codes can be read by applying t he signals

listed in Tables 2, Bus Operat ions, once the A uto

,

Select Command is executed. To exit Electronic

Signature mode, the Read/Reset command must

be issued.

M27W064

, the

IH

, for

CC3

± 0.2V)

CC

. The

CC2

Table 2. Bus Operations

Operation E G

HH

V

IL

V

IL

V

IH

V

IL

V

IL

Bus Read

Bus Write

Output Disable X

Standby

Read Manufacturer

Code

Read Device Code

Note: 1. X = VIL or VIH.

2. XX = V

3. When readin g Status Register during Program algorithm execution VPP must be kept at VHH.

, VIHor V

IL

V

IL

V

IH

V

IH

X X X Hi-Z

V

IL

V

IL

V

PP

(3)

XX

V

HH

X X Hi-Z

V

HH

V

HH

Address Inputs

A0-A21

Cell Address Data Output

Command Address Data Input

A0 = VIL, A1 = VIL,

Others VIL or V

A0 = VIH, A1 = VIL,

Others VIL or V

IH

IH

Data Inputs/Outputs

DQ15-DQ0

0020h

888Ah

7/23

Loading...

Loading...