PUSH-PULLFOUR CHANNEL DRIVER WITH DIODES

600mA OUTPUT CURRENT CAPABILITY

PER CHANNEL

1.2A PEAK OUTPUT CURRENT (non repetitive) PER CHANNEL

ENABLEFACILITY

OVERTEMPERATUREPROTECTION

LOGICAL ”0” INPUT VOLTAGE UP TO 1.5 V

(HIGH NOISE IMMUNITY)

INTERNALCLAMPDIODES

L293D

L293DD

SO(12+4+4) Powerdip (12+2+2)

DESCRIPTION

The Device is a monolithic integrated high voltage, high current four channel driver designed to

accept standard DTL or TTL logic levels and drive

inductive loads (such as relays solenoides, DC

and stepping motors) and switching power transistors.

To simplify use as two bridges each pair of channels is equippedwith an enable input. A separate

supply input is provided for the logic, allowing operation at a lower voltage and internal clamp diodes are included.

This device is suitable for use in switching applications at frequenciesup to 5 kHz.

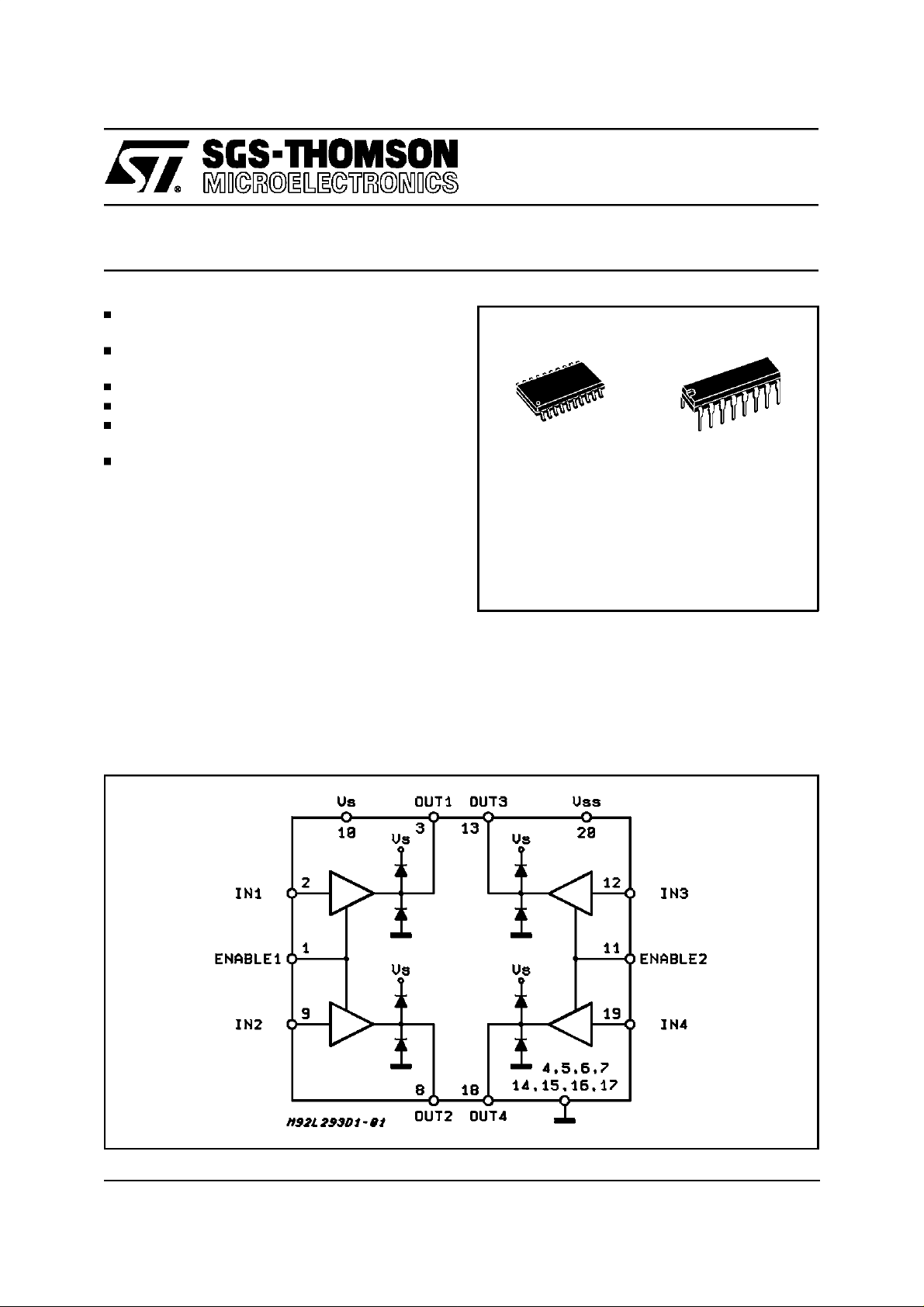

BLOCK DIAGRAM

ORDERING NUMBERS:

L293DD L293D

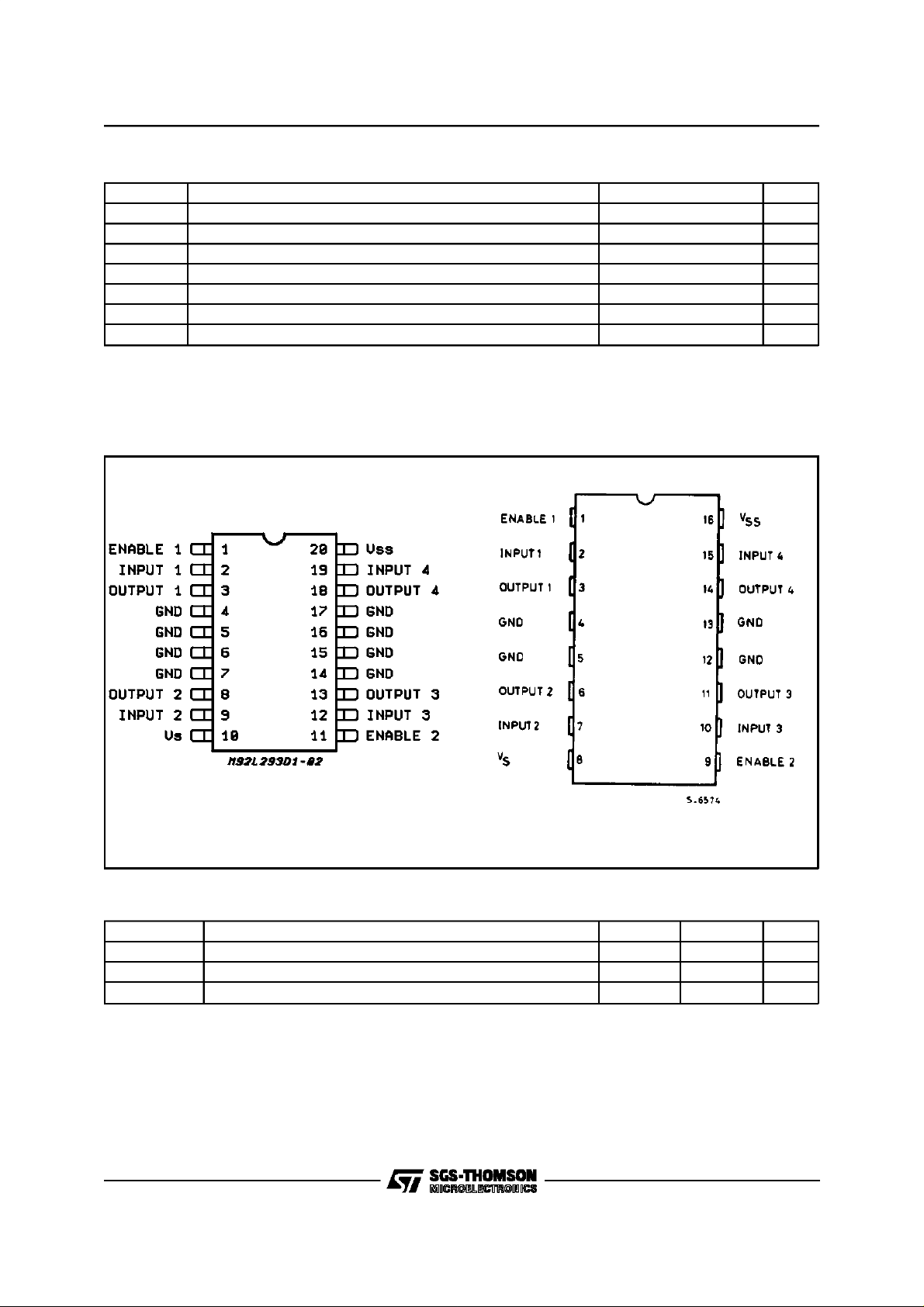

The L293D is assembled in a 16 lead plastic

packaage which has 4 center pins connected togetherand usedfor heatsinking

The L293DD is assembled in a 20 lead surface

mount which has 8 center pins connected togetherand usedfor heatsinking.

June 1996

1/7

L293D - L293DD

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

V

SS

V

i

V

en

I

o

P

tot

T

stg,Tj

PIN CONNECTIONS (Top view)

Supply Voltage 36 V

Logic Supply Voltage 36 V

Input Voltage 7 V

Enable Voltage 7 V

Peak Output Current (100µs non repetitive) 1.2 A

Total Power Dissipation at T

=90°C4W

pins

Storage and Junction Temperature – 40 to 150

C

°

SO(12+4+4)

Powerdip(12+2+2)

THERMAL DATA

Symbol Decription DIP SO Unit

R

th j-pins

R

th j-amb

R

th j-case

(*) With 6sq. cm on board heatsink.

2/7

Thermal Resistance Junction-pins max. – 14

Thermal Resistance junction-ambient max. 80 50 (*)

Thermal Resistance Junction-case max. 14 –

C/W

°

C/W

°

L293D - L293DD

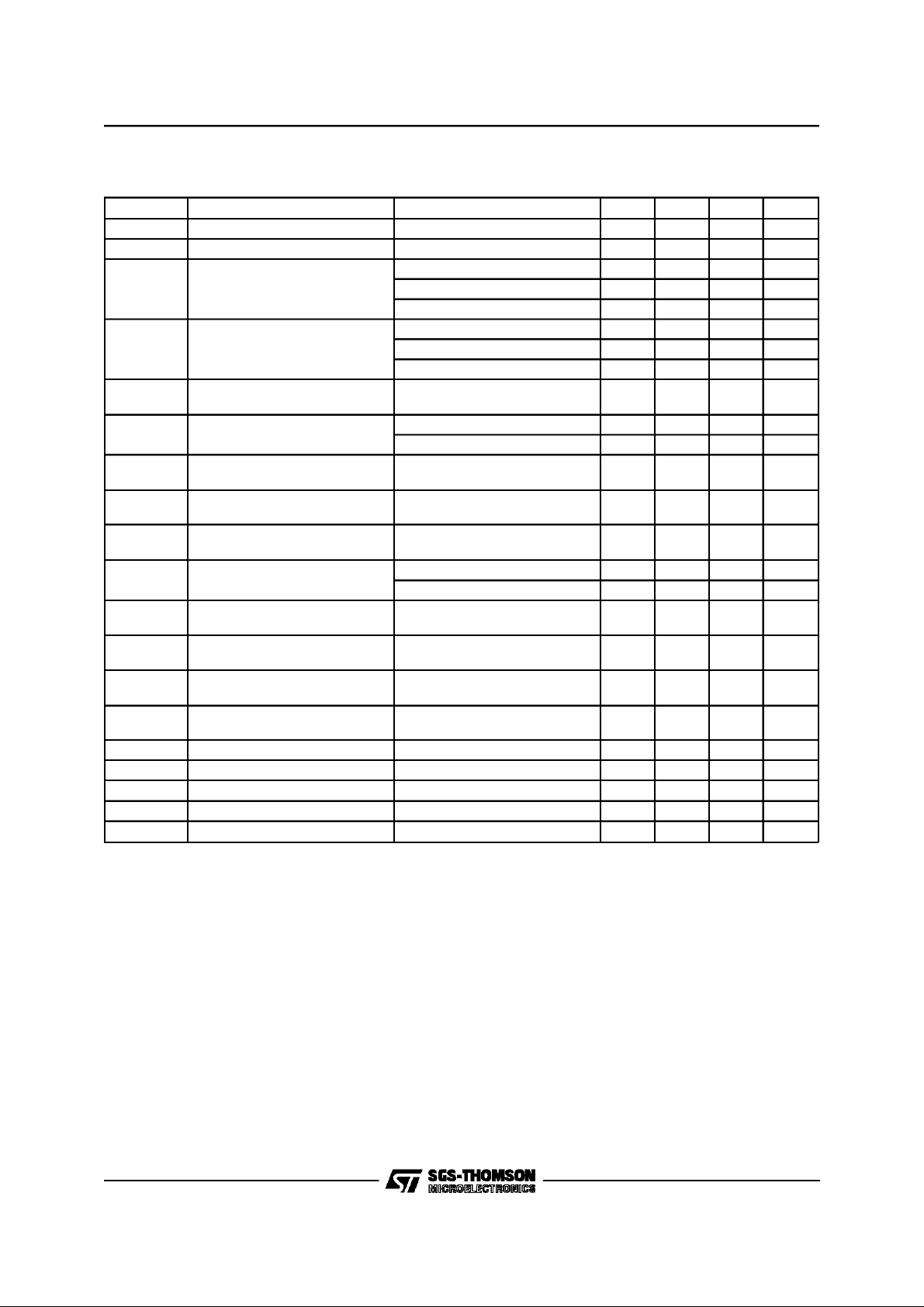

ELECTRICAL CHARACTERISTICS

(for each channel, V

=24V, VSS= 5 V, T

S

=25°C, unless

amb

otherwise specified)

Symbol Parameter Test Conditions Min. Typ. Max. Unit

V

S

V

SS

I

S

I

SS

V

IL

V

IH

I

IL

I

IH

V

en L

V

en H

I

en L

I

en H

V

CE(sat)H

V

CE(sat)L

V

F

t

r

t

f

t

on

t

off

(*) See fig. 1.

Supply Voltage (pin 10) V

SS

Logic Supply Voltage (pin 20) 4.5 36 V

Total Quiescent Supply Current

(pin 10)

Total Quiescent Logic Supply

Current (pin 20)

Input Low Voltage (pin2, 9, 12,

Vi=L; IO=0; Ven=H 2 6 mA

=H; IO=0; Ven= H 16 24 mA

V

i

=L 4 mA

V

en

Vi=L; IO=0; Ven= H 44 60 mA

=H; IO=0; Ven= H 16 22 mA

V

i

= L 16 24 mA

V

en

– 0.3 1.5 V

19)

Input High Voltage (pin 2, 9,

12, 19)

Low Voltage Input Current(pin

7 V 2.3 V

V

≤

SS

> 7 V 2.3 7 V

V

SS

VIL= 1.5 V – 10 µA

2, 9, 12, 19)

High Voltage Input Current (pin

2.3 V ≤ VIH≤ VSS– 0.6 V 30 100 µA

2, 9, 12, 19)

Enable Low Voltage

– 0.3 1.5 V

(pin 1, 11)

Enable High Voltage

(pin 1, 11)

Low Voltage Enable Current

VSS≤ 7 V 2.3 V

> 7 V 2.3 7 V

V

SS

V

= 1.5 V – 30 – 100 µA

en L

(pin 1, 11)

High Voltage Enable Current

2.3 V ≤ V

≤ VSS– 0.6V ± 10 µA

en H

(pin 1, 11)

Source Output Saturation

IO= – 0.6A 1.4 1.8 V

Voltage (pins 3, 8, 13, 18)

Sink Output Saturation Voltage

IO= + 0.6 A 1.2 1.8 V

(pins 3, 8, 13, 18)

Clamp Diode Forward Voltage IO= 600nA 1.3 V

Rise Time (*) 0.1 to 0.9 V

Fall Time (*) 0.9 to 0.1 V

O

O

Turn-on Delay (*) 0.5 Vito 0.5 V

Turn-off Delay (*) 0.5 Vito 0.5 V

O

O

250 ns

250 ns

750 ns

200 ns

36 V

SS

SS

V

V

3/7

L293D - L293DD

TRUTH TABLE(one channel)

Input Enable (*) Output

H

L

H

L

Z = High output impedance

(*) Relative to the considered channel

Figure 2:

Junctionto ambient thermal resistance vs. area on board heatsink(SO12+4+4package)

H

H

L

L

Figure1:

H

L

Z

Z

SwitchingTimes

4/7

POWERDIP16PACKAGE MECHANICAL DATA

L293D - L293DD

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.51 0.020

B 0.85 1.40 0.033 0.055

b 0.50 0.020

b1 0.38 0.50 0.015 0.020

D 20.0 0.787

E 8.80 0.346

e 2.54 0.100

e3 17.78 0.700

F 7.10 0.280

I 5.10 0.201

L 3.30 0.130

Z 1.27 0.050

mm inch

5/7

L293D - L293DD

SO20 PACKAGEMECHANICAL DATA

DIM.

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.2 0.004 0.008

a2 2.45 0.096

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45 1.772

D 1 12.6 0.039 0.496

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 11.43 0.450

F 1 7.4 0.039 0.291

G 8.8 9.15 0.346 0.360

L 0.5 1.27 0.020 0.050

M 0.75 0.030

mm inch

S8°(max.)

6/7

L293D - L293DD

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the

consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No

license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specification mentioned

in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronics products are notauthorized foruse as criticalcomponentsin lifesupportdevicesor systemswithout express

written approval of SGS-THOMSON Microelectronics.

1996SGS-THOMSON Microelectronics – Printedin Italy – All Rights Reserved

SGS-THOMSON Microelectronics GROUPOF COMPANIES

Australia - Brazil - Canada- China - France - Germany - HongKong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands-

Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

7/7

Loading...

Loading...