Primary Side PWM

Controller for Low Power

Offline SMPS

NCP1362

The NCP1362 is a highly integrated primary side quasi−resonant

flyback controller capable of controlling rugged and

high−performance off−line power supplies.

Thanks to a Novel Method this new controller saves the secondary

feedback circuitry for Constant Voltage and Constant Current

regulation, achieving excellent line and load regulation without

traditional opto coupler and TL431 voltage reference.

The NCP1362 operates in valley lockout quasi−resonant peak

current mode control mode at high load to provide high efficiency.

When the power on the secondary side starts to diminish, the

controller automatically adjusts the duty−cycle then at lower load the

controller enters in pulse frequency modulation at fixed peak current

with a valley switching detection. This technique allows keeping the

output regulation with tiny dummy load. Valley lockout at the first 4

valleys prevent valley jumping operation and then a valley switching

at lower load provides high efficiency.

Features

• Constant Voltage Primary−Side Regulation < ±5%

• Constant Current Primary−Side Regulation < ±5%

• LFF and BO Feature on a Dedicated Pin:

♦ BO Detection

♦ LFF for CC Regulation Improvement

• Quasi−Resonant with Valley Switching Operation

• Optimized Light Load Efficiency and Stand−by Performance

• Maximum Frequency Clamp (No Clamp, 80, 110 and 140 kHz)

• Cycle by Cycle Peak Current Limit

• Output Voltage Under Voltage and Over Voltage Protection

(UVP or OVP)

• Secondary Diode or Winding Short−Circuit Protection

• Wide Operation V

• Low Start−up Current

• CS & V

/ZCD Pin Short and Open Protection

S

• Internal Temperature Shutdown

• Internal and Fixed Frequency Jittering for Better EMI Signature

• Dual Frozen Peak Current to Both Optimize Light Load Efficiency

(10% Load) and Stand−by Performance (No−load)

• Fault Input for Severe Fault Conditions, NTC Compatible for OTP

• These are Pb−Free Devices

Applications

• Low Power ac−dc Adapters for Routers and Set−Top Box

• Low Power ac−dc Adapters for Chargers

Range (up to 28 V)

CC

www.onsemi.com

8

1

SOIC−8

CASE 751AZ

MARKING DIAGRAM

8

P1362yy

ALYW

G

1

IC (Pb−Free)

P1362yy = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

Vs/ZCD

COMP

Fault

ORDERING INFORMATION

See detailed ordering and shipping information on page 28 of

this data sheet.

(See page 28)

PINOUT DIAGRAM

1

CS

(Top View)

BO/LFF

VCC

GND

DRV

© Semiconductor Components Industries, LLC, 2019

March, 2021 − Rev. 3

1 Publication Order Number:

NCP1362/D

NCP1362

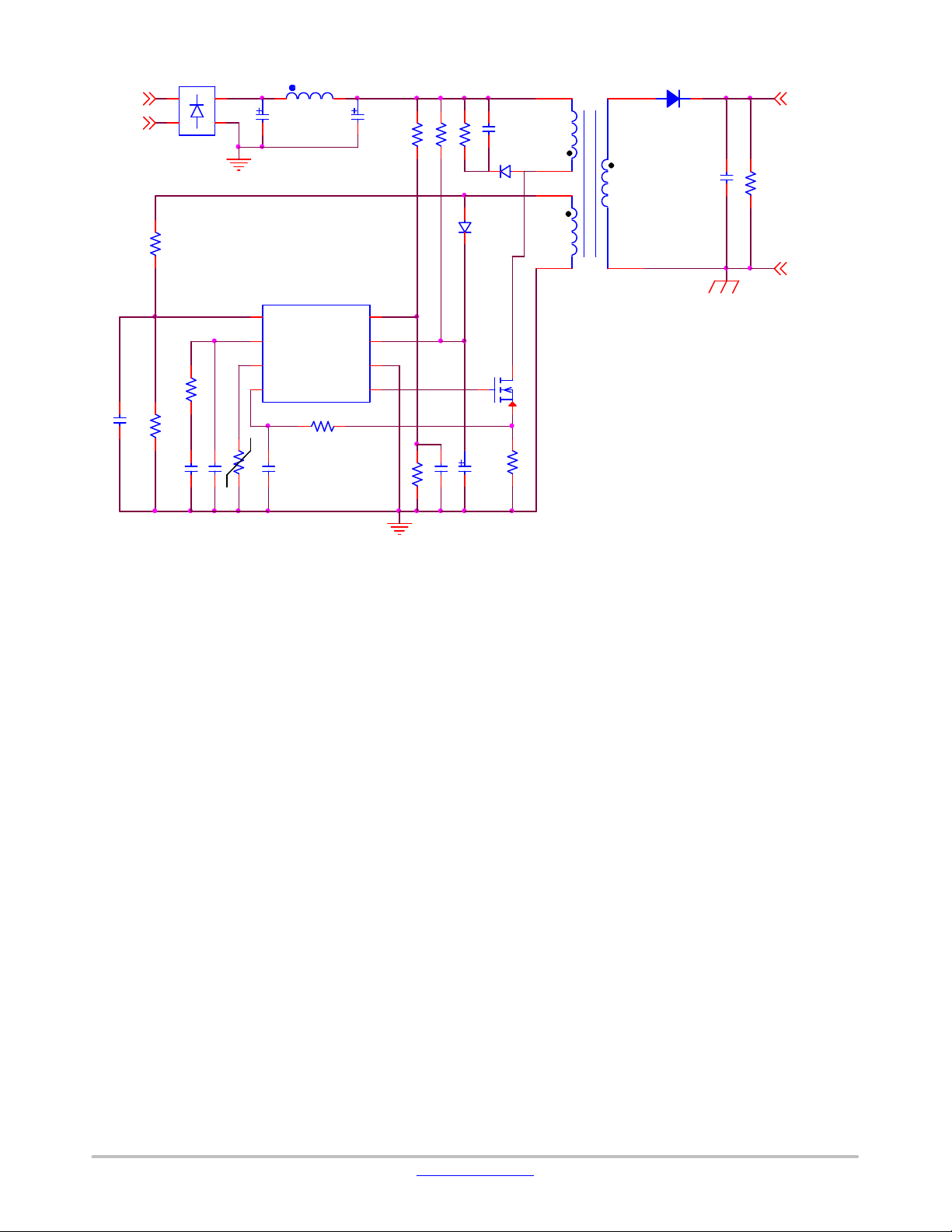

Ac

Ac

0

1

2

3

4

NCP1362

VS/ZCD

COMP

Fault

CS

BO/LFF

VCC

GND

DRV

2

3

5

4

8

7

6

5

3

2

1

0

1

Out

RTN_Out

0

Figure 1. NCP1362 Typical Application Schematic for AC Input Voltage

www.onsemi.com

2

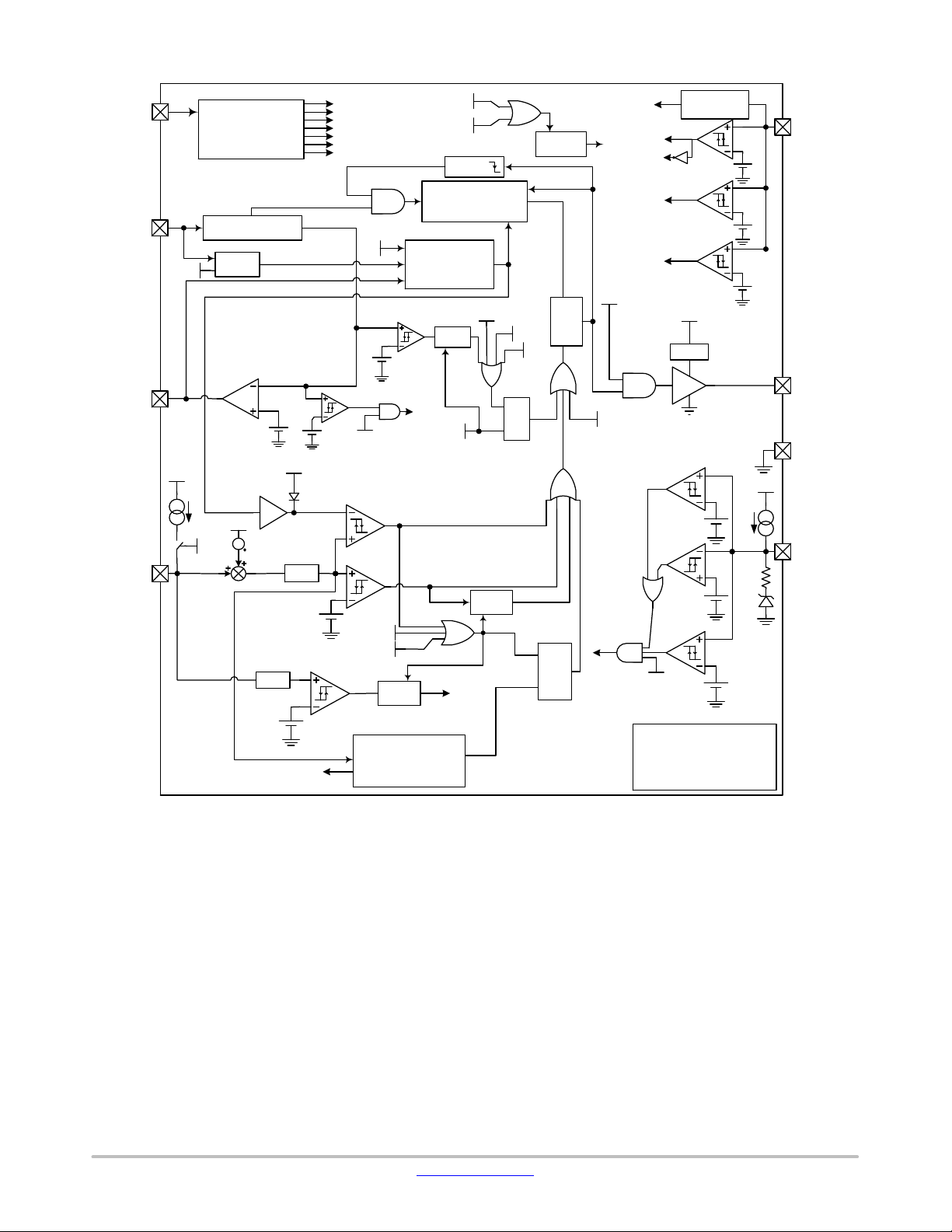

NCP1362

V

Vs /

ZCD

Comp

CS

UVLO

V

cc

V

ref_CC

VCC and Logic

Management of

double hiccup

Zero Crossing &

Signal Sampling

CC

Control

V

V

DbleHiccup

POReset

EN_UVP

Sampled V

dd

CC (Reset)

CC (OVP)

out

SS

FB_CC

FB _CV

126% V

V

UVP

UVP_Cmp

EN_UVP

OTA

V

ref_CV1

Peak current

V

DD

I

CS

V

I

CS_EN

Control

1/Kcomp

DD

V

Jitter

LEB 1

V

ILIM

POReset

DbleHiccup

LEB2

Counter

V

CS(Stop )

CS pin Open (VCS>1.2

V) & Short ( V

I

CS_EN

mV) detection is

activated at each startup

POReset

Double_Hiccup_ends

Blanking

QR multi−mode

Valley lockout &

Valley Switching &

VCO management

Control Law

&

Primary Peak

Current Control

OVP_Cmp

4 clk

Counter

OVP

ref_CV1

UVP

DbleHiccup

FB Reset

Max_Ipk reset

Count

Reset

Counter

4 clk

SCP

<50

CS

V

CC(OVP )

OCP

Timer

Reset Timer

FB

UVP

SCP

S

Q

R

OCP

CS pin Fault

Reset

Soft Start

R

S

I

%VBO

SS

BO_EN

BO_DIS

BO_OK

High_Line

UVLO

S

Q

R

POReset

Fault

Q

SS

end

Note:

OVP: Over Voltage Protection

UVP: Under Voltage Protection

OCP : Over Current Protection

SCP: Short Circuit Protection

t

LEB1>tLEB2

FeedForward

V

cc

Clamp

V

fault( OVP)

V

Fault (OTP)

V

fault(EN )

Line

V

V

V

BO (EN)

BO (ON)

HL( on)

BO/LFF

DRV

GND

V

DD

fault(OTP)

I

Fault

fault(clamp)

R

fault(clamp)

V

Figure 2. Functional Block Diagram

www.onsemi.com

3

NCP1362

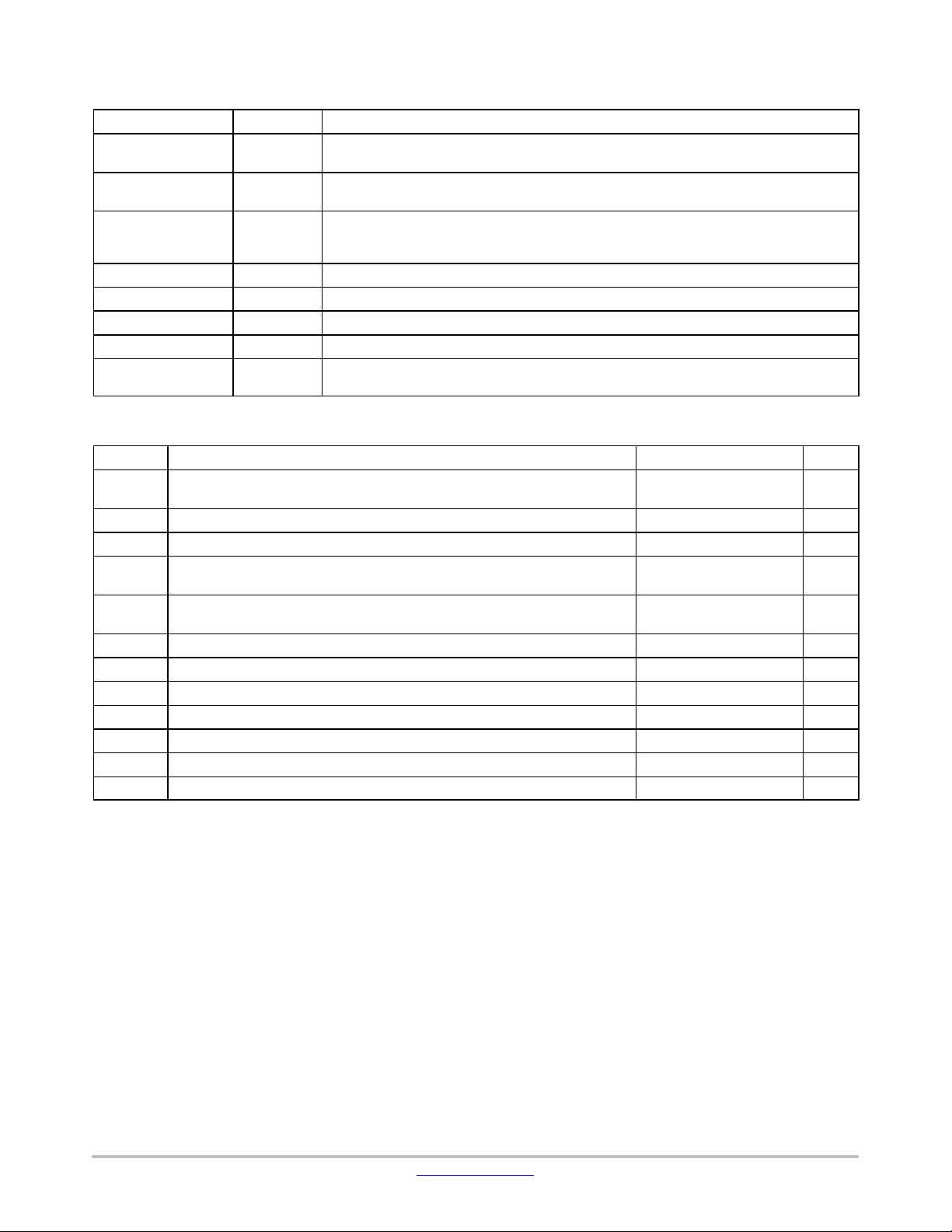

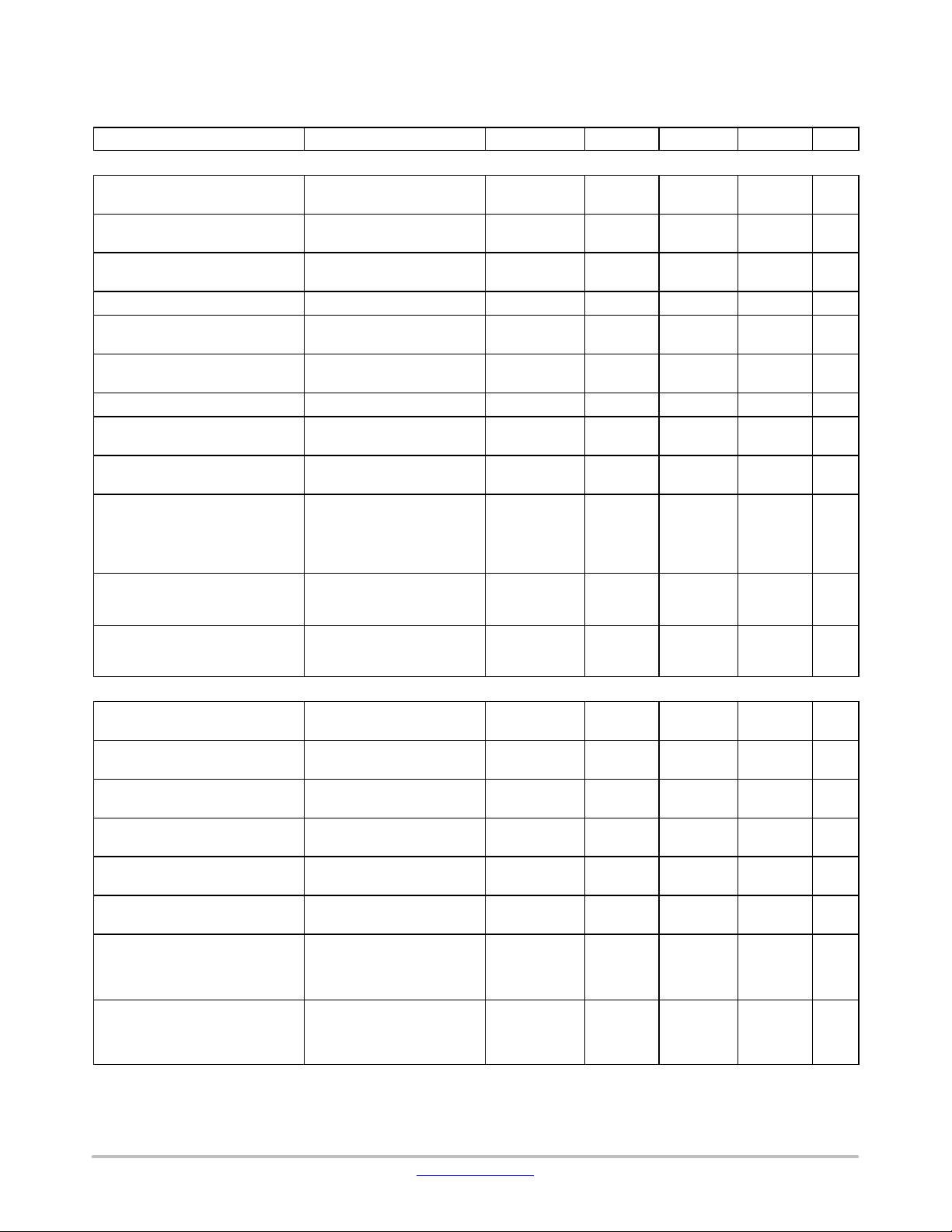

Table 1. PIN FUNCTION DESCRIPTION

Pin Name Function

1 Vs/ZCD Connected to the auxiliary winding; this pin senses the voltage output for the primary regula-

2 Comp This is the error amplifier output. The network connected between this pin and the ground

3 Fault The controller enters in fault mode if the voltage of this pin is pulled above or below the fault

4 CS This pin monitors the primary peak current.

5 DRV The driver’s output to an external MOSFET gate.

6 GND Ground reference.

7 V

CC

8 BO/LFF Detects too low input voltage conditions (Brown−Out). Also voltage pin level is used for build-

Table 2. MAXIMUM RATINGS (Note 1)

Symbol

V

CC(MAX)

I

CC(MAX)

DVCC/Dt

E

V

MAX

I

MAX

V

DRV(MAX)

I

DRV(MAX)

R

θ

T

J(MAX)

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality

should not be assumed, damage may occur and reliability may be affected.

1. This device contains latch−up protection and exceeds 100 mA per JEDEC Standard JESD78.

2. V

DRV

Maximum Power Supply voltage, VCC pin, continuous voltage

Maximum current for V

Maximum slew rate on V

Single Pulse Avalanche Rating 120 mJ

as

Maximum voltage on low power pins (except pins DRV and VCC)

Current range for low power pins (except pins DRV and VCC)

Maximum driver pin voltage, DRV pin, continuous voltage

Maximum current for DRV pin

Thermal Resistance Junction−to−Air, 2.0 oz Printed Circuit Copper Clad 190 °C/W

J−A

Maximum Junction Temperature 150 °C

Operating Temperature Range −40 to +125 °C

Storage Temperature Range −60 to +150 °C

Human Body Model ESD Capability per JEDEC JESD22−A114F 2 kV

Machine Model ESD Capability (All pins except DRV) per JEDEC JESD22−A115C 200 V

Charged−Device Model ESD Capability per JEDEC JESD22−C101E 500 V

is the DRV clamp voltage V

tion and detects the core reset event for the Quasi−Resonant mode of operation.

adjusts the regulation loop bandwidth.

thresholds. A precise pullup current allows direct interface with an NTC thermistor. Fault detection triggers a latch.

This pin is connected to an external auxiliary voltage and supplies the controller.

ing Line FeedForward compensation for improving Constant Current regulation tolerance.

Rating Value Unit

−0.3 to 28

pin

CC

pin during start−up phase +0.4

CC

Internally limited

−0.3, 5.5

−2, +5

DRV(high)

when VCC is higher than V

DRV(high)

. V

is VCC otherwise.

DRV

−0.3, V

(Note 2)

DRV

−300, +500

V

mA

V/ms

V

mA

V

mA

www.onsemi.com

4

NCP1362

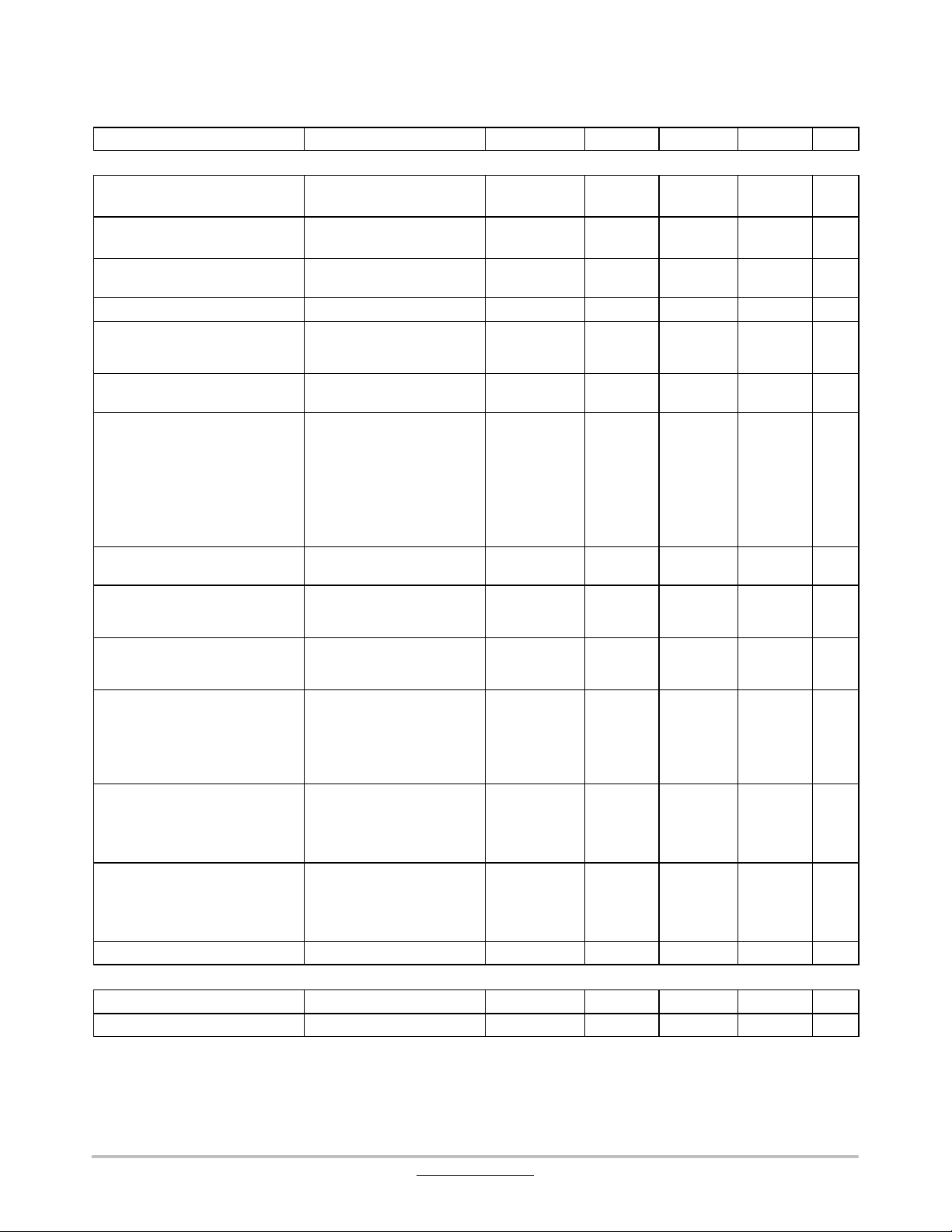

Table 3. ELECTRICAL CHARACTERISTICS

(V

= 12 V, For typical values Tj = 25°C, for min/max values Tj = −40°C to +125°C, Max Tj = 150°C, unless otherwise noted)

CC

Characteristics

SUPPLY SECTION AND VCC MANAGEMENT

Level at which Driving Pulses

V

CC

are Authorized

VCC Level at which Driving Pulses

VCC increasing V

VCC decreasing V

are Stopped

Internal Latch/Logic Reset

Level

Internal Autorecovery Reset Level (Note 4) V

Hysteresis above V

Hiccup in Latch Mode

Hysteresis below V

before Latch Reset

CC(off)

CC(off)

for Fast

Over Voltage Protection Over Voltage threshold V

Start−up Supply Current,

Controller Disabled or Latched

Internal IC Consumption, Steady

State

Internal IC Consumption in

Minimum Frequency Clamp

Internal IC Consumption in Fault

VCC < V

increasing from 0 V

FSW = 65 kHz

C

VCO mode, FSW = f

V

Autorecovery mode I

Mode (after a fault when VCC

decreasing to V

Internal IC Consumption in Fault

Mode (after a fault when V

decreasing to V

CC(off)

CC(off)

)

Latch mode I

CC

)

CURRENT COMPARATOR

Current Sense Voltage

Threshold

V

V

Cycle by Cycle Leading Edge

Blanking Duration

Cycle by Cycle Current Sense

Propagation Delay

Timer Delay before Detecting an

Overload Condition

VCS > (V

DRV turn−off

When CS pin w V

(Note 3)

Threshold for Immediate Fault

Protection Activation

Leading Edge Blanking

Duration for V

Maximum Peak Current Level at

which VCO Takes Over or Frozen

Peak Current

CS(stop)

V

0.6 V < V

(other possible options on

demand)

Minimum Peak Current Level V

V

(other possible options on

demand)

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. The timer can be reset if there are 4 DRV cycles without overload or short circuit conditions.

4. Guaranteed by Design.

Condition Symbol Min Typ Max Unit

16.5 18 19.5 V

6.0 6.5 7.0 V

− 6.25 − V

0.6 − − V

− 0.2 − V

0.15 0.30 0.50 V

24 26 28 V

– 5.4 7.0

– 1.6 2.3 mA

–

–

325

210

– 2.0 2.2 mA

– 1.0 1.2 mA

0.76 0.8 0.84 V

250 320 380 ns

– 50 110 ns

50 70 90 ms

1.10 1.20 1.30 V

− 120 − ns

− 250 − mV

− 65 − mV

= 1 nF

L

Comp

f

VCO(min)

f

VCO(min)

C

= 1 nF

L

Comp

increasing

CS

increasing

CS

increasing

CS

Comp

CC(on)

= GND

= 1 kHz

= 200 Hz

= V

Comp(max)

ILIM

Comp

< 0.2 V

& V

CC

VCO(min)

,

+ 100 mV) to

ILIM

< 1.9 V

,

CC(on)

CC(off)

V

CC(reset)

CC(reset_auto)

V

CC(latch_hyst)

V

CC(reset_hyst)

CC(OVP)

I

CC(start)

I

CC(steady)

I

CC(VCO)

CC(auto)

CC(latch)

V

ILIM

t

LEB1

t

ILIM

T

OCP

V

CS(stop)

t

LEB2

V

CS(VCO)

V

CS(STB)

mA

mA

430

370

www.onsemi.com

5

NCP1362

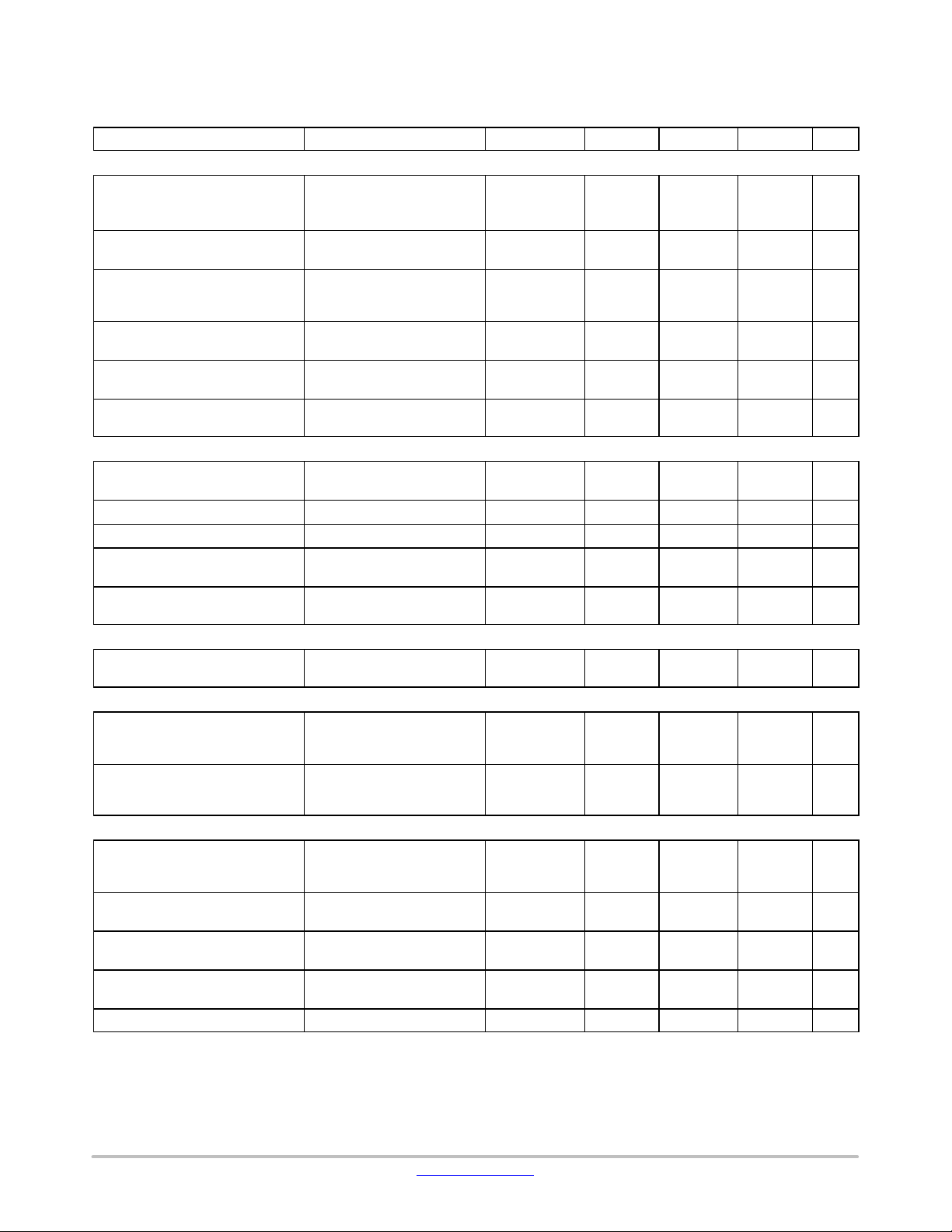

Table 3. ELECTRICAL CHARACTERISTICS

(VCC = 12 V, For typical values Tj = 25°C, for min/max values Tj = −40°C to +125°C, Max Tj = 150°C, unless otherwise noted)

Characteristics UnitMaxTypMinSymbolCondition

REGULATION BLOCK

Internal Voltage Reference for

Constant Current Regulation

Internal Voltage Reference for

Constant Voltage Regulation

TJ = 25°C

−40°C < T

TJ = 25°C

−40°C < T

< 125°C

J

< 125°C

J

Error Amplifier Current

Capability

Error Amplifier Gain G

Error Amplifier Output Voltage Internal offset on Comp pin V

Internal Current Setpoint

Division Ratio

Valley Thresholds

Transition from 1

Transition from 2nd to 3rd Valley

Transition from 3rd to 4th Valley

Transition from 4

Transition from VCO to 4th Valley

Transition from 4th to 3rd Valley

Transition from 3rd to 2nd Valley

Transition from 2nd to 1st Valley

Minimal Difference between any

Two Valleys

Internal Dead Time Generation for

VCO Mode

Internal Dead Time Generation for

VCO Mode

Internal Dead Time Generation for

VCO Mode

Minimum Switching Frequency in

VCO Mode

st

to 2nd Valley

th

Valley to VCO

V

decreasing

Comp

V

decreasing

Comp

V

decreasing

Comp

V

decreasing

Comp

V

increasing

Comp

V

increasing

Comp

V

increasing

Comp

V

increasing

Comp

V

increasing or V

Comp

decreasing

Comp

Entering in VCO when

V

is decreasing and

Comp

crosses V

HVCOD

Leaving VCO mode when

V

is increasing and

Comp

crosses V

HVCOI

When in VCO mode –

1−kHz option

V

= 1.8 V

Comp

V

= 1.4 V

Comp

V

= 0.9 V

Comp

V

< 0.2 V

Comp

V

= GND

Comp

Option 1

Option 2

(other possible options on

demand)

Maximum Switching Frequency

Option 1

Option 2

Option 3

Option 4

Maximum On Time T

DEMAGNETIZATION INPUT – ZERO VOLTAGE DETECTION CIRCUIT and VOLTAGE SENSE

Threshold Voltage V

V

ZCD

V

Hysteresis V

ZCD

decreasing V

ZCD

increasing V

ZCD

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. The timer can be reset if there are 4 DRV cycles without overload or short circuit conditions.

4. Guaranteed by Design.

V

ref_CC

V

ref_CV1

I

EA

EA

Comp(max)

V

Comp(min)

V

Comp(offset)

K

Comp

V

H2D

V

H3D

V

H4D

V

HVCOD

V

HVCOI

V

H4I

V

H3I

V

H2I

DV

H

T

DT(start)

T

DT(ends)

T

DT

f

VCO(MIN)

f

MAX

on(max)

ZCD(TH)

ZCD(HYS)

0.98

0.97

2.450

2.425

1.00

1.00

2.500

2.500

1.02

1.03

2.550

2.575

− ±40 −

150 200 250

−

−

−

4.9

1.1

0

−

−

−

− 4 − –

−

−

−

−

−

−

−

−

2.50

2.30

2.10

1.90

2.50

2.70

2.90

3.10

−

−

−

−

−

−

−

−

176 − − mV

− 1.15 −

− 650 − ns

−

−

−

−

0.8

0.16

−

72

99

127

1.6

11

110

1000

1.0

0.200

No Clamp

80

110

140

−

−

−

−

1.2

0.24

−

88

121

153

32 36 40

25 45 70 mV

15 30 45 mV

V

V

mA

mS

V

V

ms

ms

kHz

kHz

ms

www.onsemi.com

6

NCP1362

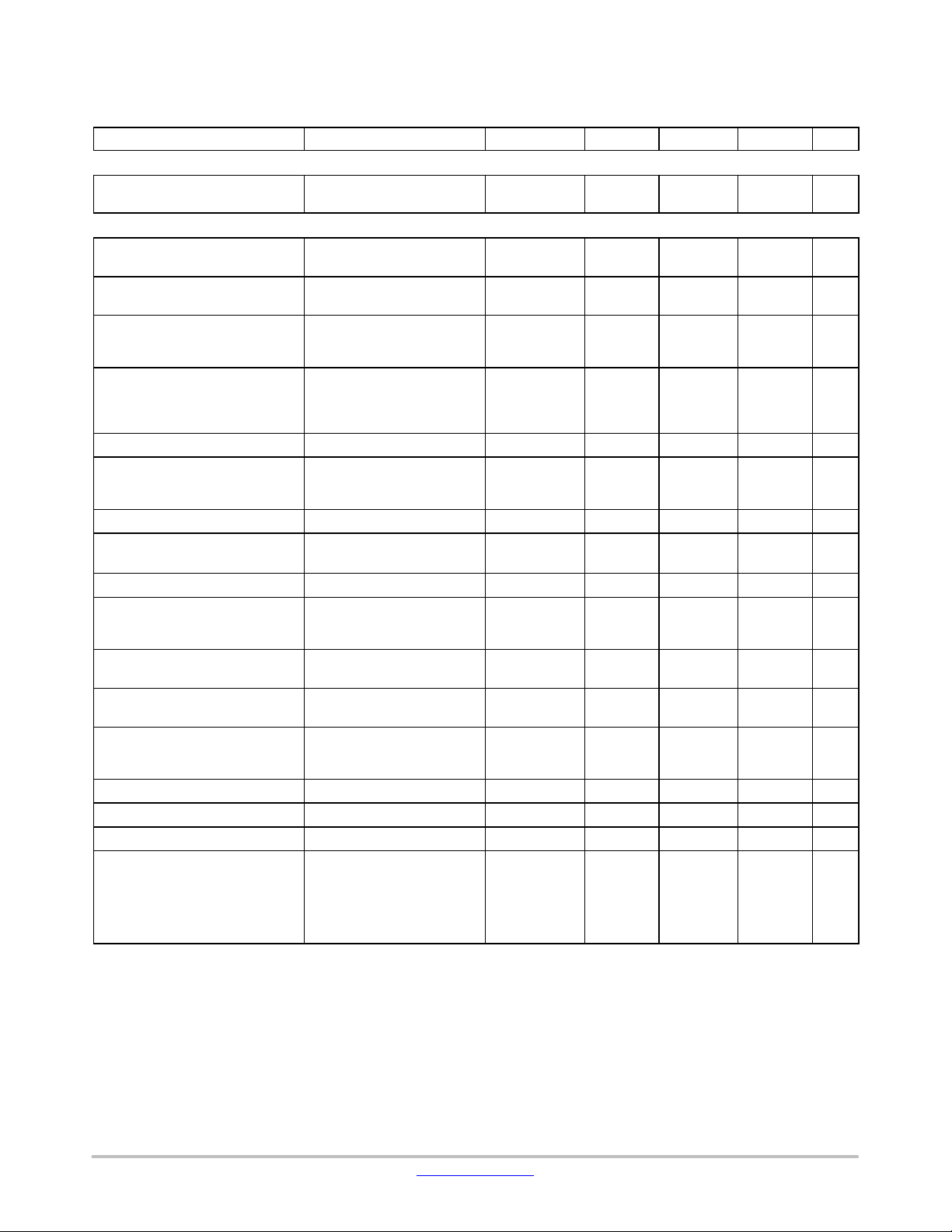

Table 3. ELECTRICAL CHARACTERISTICS

(VCC = 12 V, For typical values Tj = 25°C, for min/max values Tj = −40°C to +125°C, Max Tj = 150°C, unless otherwise noted)

Characteristics UnitMaxTypMinSymbolCondition

DEMAGNETIZATION INPUT – ZERO VOLTAGE DETECTION CIRCUIT and VOLTAGE SENSE

Threshold Voltage for Output

Short Circuit or Aux. Winding

Short Circuit Detection

After t

V

ZCD

BLANK_ZCD

< V

ZCD(short)

if

V

ZCD(short)

30 50 75 mV

Delay after On−time that the

V

/ZCD is still Pulled to Ground

S

Blanking Delay after On−time

(V

/ZCD Pin is Disconnected from

S

the Internal Circuitry)

Timeout after Last

Demagnetization Transition

Input Leakage Current VCC > V

Delay from Valley Detection to

DRV Low

When V

Comp

When V

Comp

When V

Comp

When V

Comp

CC(on) VZCD

DRV is low

> 1.7 V

< 1.7 V

> 1.7 V

< 1.7 V

= 4 V,

t

short_ZCD

t

BLANK_ZCD

t

out

I

ZCD

t

ZCD_delay

−

−

−

−

0.750

0.350

1.450

0.750

−

−

−

−

4.0 4.5 5.0

− − 0.1

− 290 − ns

ms

ms

ms

mA

DRIVE OUTPUT − GATE DRIVE

Drive resistance

DRV Sink − VCC = 8 V

DRV Source − V

Rise time C

Fall time C

= 1 nF, from 10% to 90% t

DRV

= 1 nF, from 90% to 10% t

DRV

DRV Low voltage VCC = V

= 220 pF, R

DRV High voltage VCC = V

= 220 pF, R

CC(off)

DRV

CC(OVP)

DRV

= 8 V

CC

+ 0.2 V, C

= 33 kW

− 0.2 V, C

= 33 kW

DRV

DRV

R

SNK

R

SRC

V

DRV(low)

V

DRV(high)

−

−

r

f

− 45 85 ns

− 30 65 ns

10

8

−

W

−

6.0 − − V

− 12.0 13.0 V

SOFT START

Internal Fixed Soft Start Duration

Current Sense peak current

rising from V

CS(VCO)

to V

ILIM

t

SS

3 4 5 ms

JITTERING

Frequency of the Jittering CS Pin

Source Current

Option 1

(other possible options on

f

jitter

1.2 1.5 1.8 kHz

demand)

Peak Jitter Voltage Added to

PWM Comparator

Option 1

(other possible options on

V

jittter

− 60 − mV

demand)

BROWN−OUT & LINE FEED FORWARD

Brown−out Function is Disabled

below this Level (before the 1

st

V

BO(en)

80 100 120 mV

DRV pulse only)

Pull−down Current Source on BO

Pin for Open Detection

Brown−out Level at which the

Controller Starts Pulsing

Brown−out Level at which the

Controller Stops Pulsing

Brown−out Filter Time t

V

BO(on)

V

BO(off)

I

BO

− 300 − nA

0.75 0.80 0.85 V

0.65 0.70 0.75 V

BO

− 50 −

ms

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. The timer can be reset if there are 4 DRV cycles without overload or short circuit conditions.

4. Guaranteed by Design.

www.onsemi.com

7

NCP1362

Table 3. ELECTRICAL CHARACTERISTICS

(VCC = 12 V, For typical values Tj = 25°C, for min/max values Tj = −40°C to +125°C, Max Tj = 150°C, unless otherwise noted)

Characteristics UnitMaxTypMinSymbolCondition

BROWN−OUT & LINE FEED FORWARD

Line Feed Forward Compensation

Gain

FAULT PROTECTION

Controller Thermal Shutdown

Device switching

(F

∼ 65 kHz) – Tj rising

SW

Thermal Shutdown Hysteresis Device switching

(F

∼ 65 kHz) − Tj falling

SW

Fault Level Detection for OVP Internal sampled V

increasing

V

= V

OVP

ref_CV1

Fault Level Detection for UVP →

Double Hiccup Autorecovery

Internal sampled V

decreasing

out

+ 26%

out

(UVP detection is disabled during

T

EN_UVP

)

Blanking Time for UVP Detection Starting after the Soft start T

Pull−up Current Source on CS Pin

for Open or Short Circuit Detec-

When VCS > V

CS_min

tion

CS Pin Open Detection CS pin open V

K

LFF

T

SHTDN(on)

T

SHTDN(off)

V

OVP

V

UVP

EN_UVP

I

CS

CS(open)

16 20 24

− 150 − °C

− 120 − °C

2.95 3.15 3.35 V

1.40 1.50 1.60 V

− 36 − ms

− 60 −

− 1.2 − V

mA/

V

mA

CS Pin Short Detection V

CS pin Short Detection Timer (Note 4) T

Fault Pin is Disabled below this

Level (before the 1

st

DRV pulse

V

CS_min

CS_short

Fault(EN)

− 50 75 mV

− 3 −

ms

80 100 120 mV

only)

Overvoltage Protection (OVP)

Threshold

Overtemperature Protection

(OTP) Threshold

OTP Pull−up Current Source V

Fault Input Clamp Voltage I

Fault Input Clamp Voltage I

Fault Filter Time t

Number of Drive Cycle before

Latch Confirmation

V

increasing V

Fault

V

decreasing V

Fault

= 0 V

Fault

T

= 25°C

j

= 110°C

T

j

= 0 mA (V

Fault

= 1 mA V

Fault

V

= V

Comp

V

CS

or Internal rebuilded

V

out

or 0.40 V < V

or V

> V

CS(stop)

> V

OVP

ZCD(short)

Comp(max)

Fault

Fault

< 3.00 V

= open) V

,

Fault(OVP)

Fault(OTP)

I

Fault(OTP)

I

Fault(OTP_110)

Fault(clamp)0

Fault(clamp)1

Fault(filter)

t

latch(count)

2.79 3.00 3.21 V

0.38 0.40 0.42 V

42.5

42.9

45.0

45.0

47.5

46.5

1.10 1.35 1.60 V

2.2 2.7 3.2 V

− 2 −

− 4 − −

mA

ms

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. The timer can be reset if there are 4 DRV cycles without overload or short circuit conditions.

4. Guaranteed by Design.

www.onsemi.com

8

NCP1362

)

)

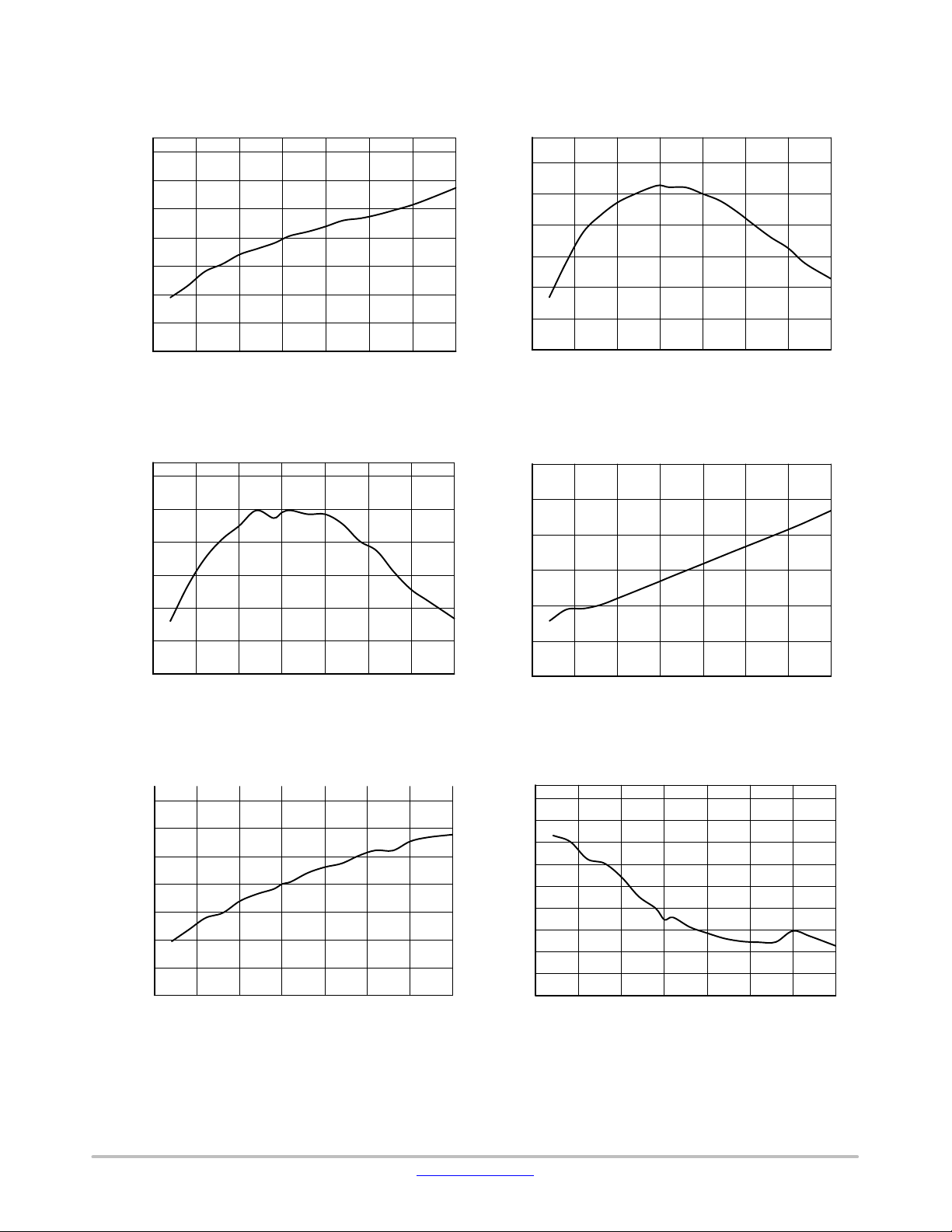

TYPICAL CHARACTERISTICS

18.09

18.07

18.05

(V)

18.03

CC(on)

18.01

V

17.99

17.97

17.95

−50 −25 0 25 50 75 100 125

TEMPERATURE (5C)

(V)

CC(reset)

V

6.292

6.287

6.282

6.277

6.272

Figure 3. V

vs. Junction Temperature Figure 4. V

CC(on)

6.59

6.585

6.58

(V)

6.575

CC(off)

V

6.57

6.565

6.56

−50 −25 0 25 50 75 100 125

TEMPERATURE (5C)

vs. Junction Temperature

CC(off)

5.2

4.7

4.2

(mA)

3.7

CC(start)

I

3.2

6.267

6.262

−50 −25 0 25 50 75 100 125

TEMPERATURE (5C)

Figure 5. V

0.808

0.806

0.804

(V)

0.802

ILIM

V

0.8

0.798

0.796

0.794

−50 −25 0 25 50 75 100 125

CC(reset

vs. Junction Temperature Figure 6. I

TEMPERATURE (5C)

Figure 7. V

vs. Junction Temperature Figure 8. t

ILIM

2.7

2.2

−50 −25 0 25 50 75 100 125

TEMPERATURE (5C)

vs. Junction Temperature

(ns)

LEB1

t

CC(start

316.5

316

315.5

315

314.5

314

313.5

313

312.5

312

−50 −25 0 25 50 75 100 125

TEMPERATURE (5C)

vs. Junction Temperature

LEB1

www.onsemi.com

9

Loading...

Loading...