SANYO STK311-010 Datasheet

Overview

The STK311-010 is a hybrid integrated circuit (HIC) for

Radio Data System (RDS) applications which must

conform to European Broadcasting Union (EBU) enforced

recommendations. Since the Radio Data System (RDS)

subjects every kind of data to multiplex broadcasting for

FM broadcasts, the STK311-010 functions as a hybrid IC

which demodulates the modulated signal’s data,

previously multiplexed to a RDS signal, matches

synchronization and performs error detection and

correction. By combining SC system and photoresist

technology with folded board construction and

incorporating Sanyo’s unique insulated metal substrate

technology (IMST) to the base, the STK311-010 has

successfully been contained within a low-profile package.

Applications

• Car stereos

• Home stereos

Features

• On-chip 57 kHz BPF provides adjustment-free

performance

• On-chip 4 MHz ceramic oscillator

• Supports RDS data demodulation system designs

incorporating fewer external components

• On-chip ARI-SK/DK decoder

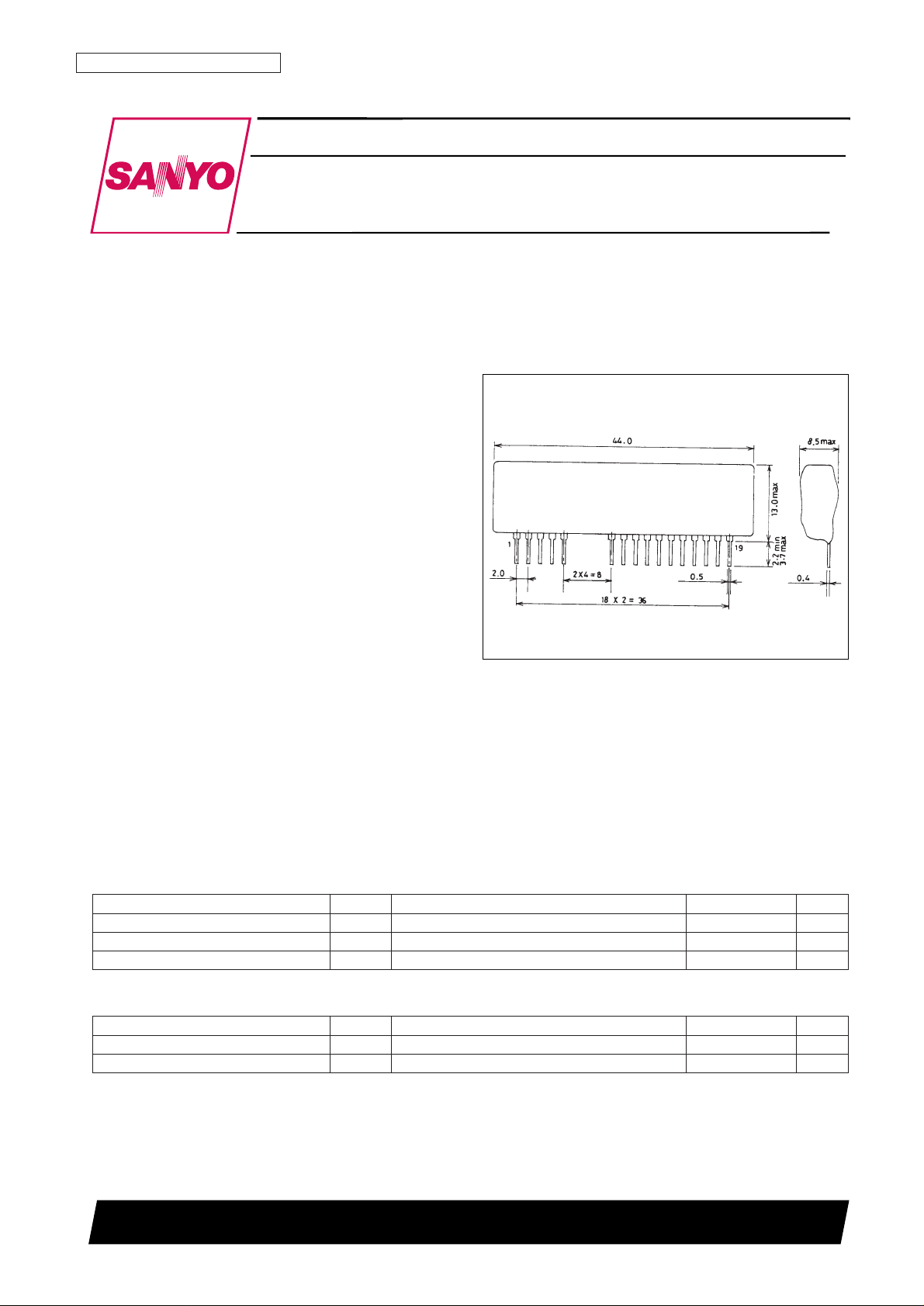

Package Dimensions

unit: mm

4132

Thick-Film Hybrid IC

N3096HA(OT)/10293YO 5-3279No. 4374-1/7

[STK311-010]

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110 JAPAN

RDS Demodulation + Synchronization and

Error Correction

STK311-010

Ordering number : EN4374A

Parameter Symbol Conditions Ratings Unit

Maximum supply voltage V

CC

max 6.3 V

Operating temperature Topr –30 to +85 °C

Storage temperature Tstg –40 to +100 °C

Specifications

Absolute Maximum Ratings at Ta = 25°C

Parameter Symbol Conditions Ratings Unit

Supply voltage V

CC

5V

Power supply voltage operating range V

CC OP

4.7 to 5.5 V

Recommended Operational Voltage at Ta = 25°C

t

Operating Characteristics at Ta = 25°C, VCC= 5V

No. 4374-2/7

STK311-010

Parameter Symbol Conditions min typ max Unit

Quiescent current I

CCO

26 38 mA

Band-pass filter gain VG

BPF

f = 57 Hz 9 12.5 17 dB

f = 60 kHz (57 kHz = 0 dB) –6 –2.5 0 dB

Band-pass filter selectivity f = 54 kHz (57 kHz = 0 dB) –6 –3.5 0 dB

f = 38 kHz (57 kHz = 0 dB) –39 –33 dB

PLL capture range CR 5 mVrms, CW input

–0.9 %

+1.5 %

RDS detection seisitivity 4 pin input voltage which sets 12 pin to low 0.4 1.0 mVrms

SK detection seisitivity 4 pin input voltage which sets 11 pin to low 1.0 2.0 mVrms

DK detection seisitivity 4 pin input voltage which sets 10 pin to low 1.7 2.6 mVrms

4 pin maximum input signal (ARI + RDS)

RDS input dynamic range

which sets 12 pin to low

30 50 mVrms

DK input dynamic range

4 pin maximum input signal (ARI)

75 100 mVrms

which sets 10 pin to low

VCO free-run frequency f

OSC

453 456 459 kHz

Output high level voltage V

OH

*1 IOH= –50 µA VCC– 1.2 V

*1 I

OH

= –10 µA VCC– 0.5 V

Output low level voltage V

OL

*2 IOL= 10 mA 1.5 V

*2 I

OL

= 1.8 mA 0.4 V

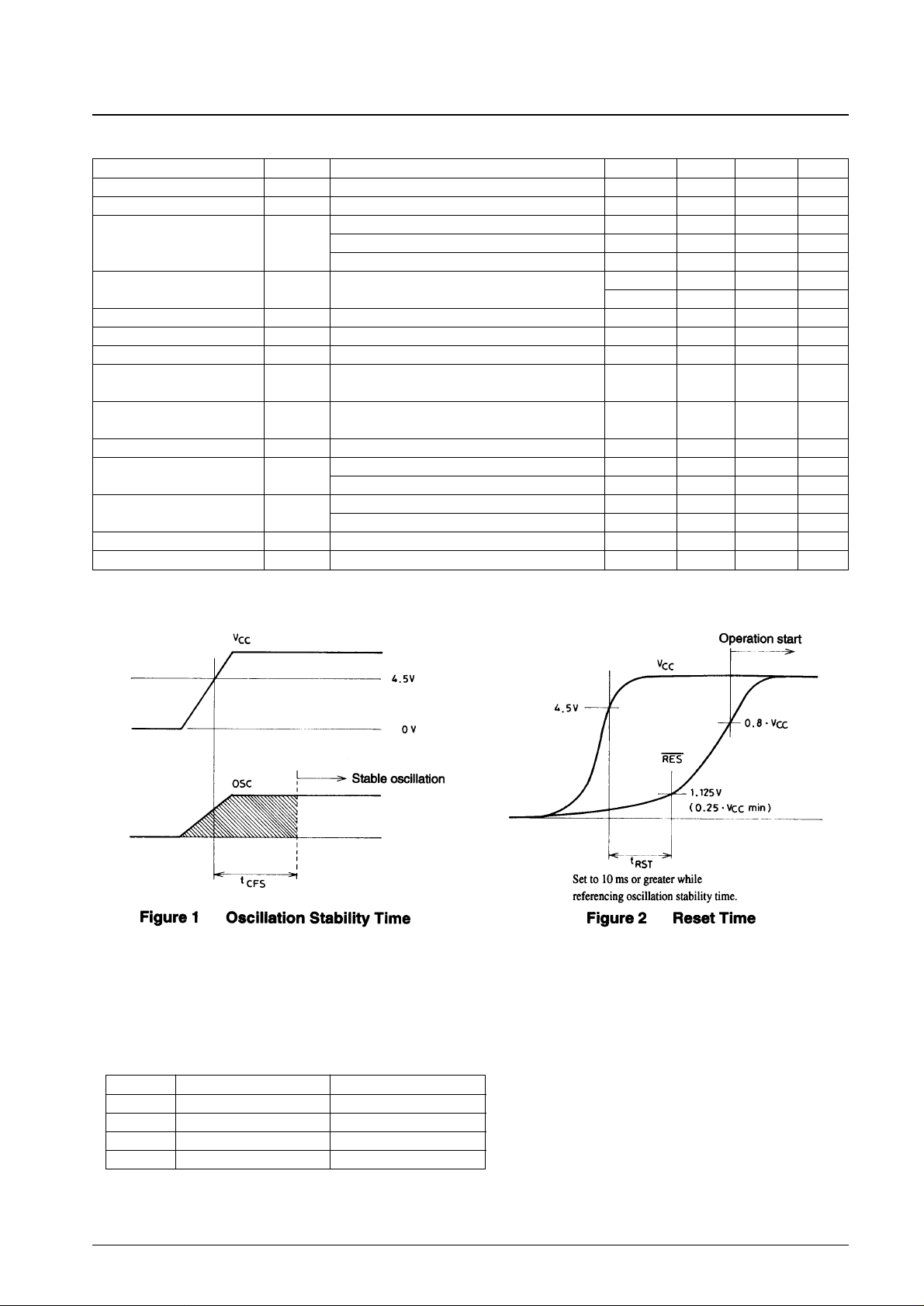

Ceramic oscillator stability time t

CFS

Refer to Figure 1 10 ms

Reset time t

RST

Refer to Figure 2

Note: 1. DATA START, DATA OUT, CLOCK OUT

2. RECEIVE, CORRECTION, ERROR, DATA START, DATA OUT, CLOCK OUT

Note: STK311-010 defaults to setting 1 though other settings are supported.

Other

The STK311-010 supports HIC internal settings for all output signals of CLK OUT and DATA START. These are

shown in the following table.

Table 1 Output Signal Settings

Setting Polarity of CLK OUT DATA START Output

1 Negative edge trigger Every block

2 Negative edge trigger Only 2nd block

3 Positive edge trigger Every block

4 Positive edge trigger Only 2nd block

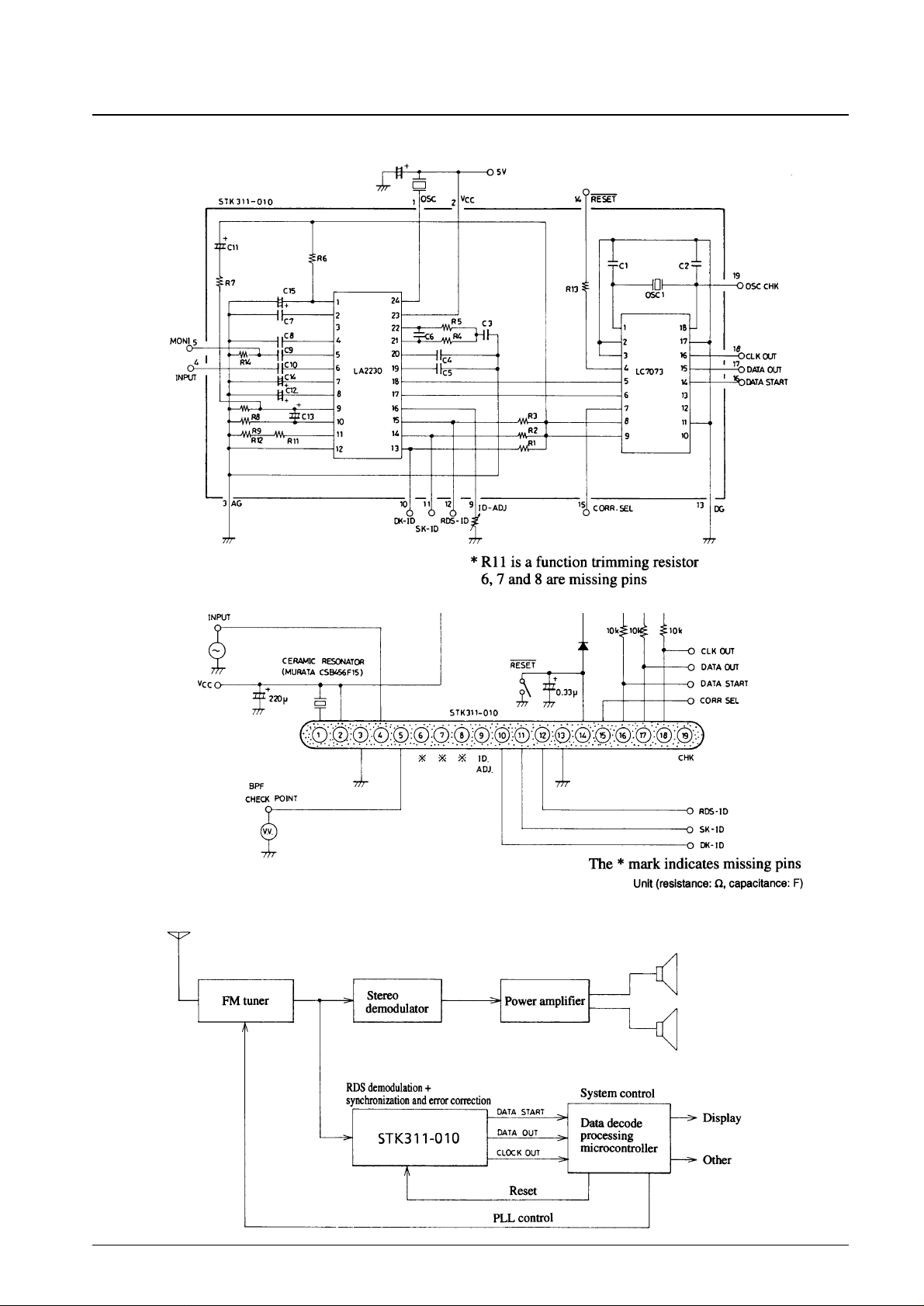

Internal Equivalent Circuit

No. 4374-3/7

STK311-010

Sample System Configuration

Sample Application Circuit

Loading...

Loading...