Page 1

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft’s

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

Monolithic Linear IC

82198RM (OT) No.6000-1/21

SANYO Electric Co.,Ltd. Semiconductor Bussiness Headquarters

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

LV4124W

Ordering number : EN6000

Overview

The LV4124W is a LCD panel driver for use in lowtemperature polysilicon TFT LCDs that integrates an RGB

decoder, a driver, and a timing controller in a single chip.

This IC is manufactured in Bi-CMOS process and

supports the ALP202 2.0-inch color LCD panel.

Functions

• Analog block: RGB decoder/driver

• Digital block: Timing generator

Features

• Supports NTSC/PAL standard

• Supports composite, Y/C, and Y/color difference inputs

• Built-in BPF, TRAP, and DL circuits

• Sharpness function

• Dual point γ correction circuit

• Pre-charge circuit

• R and B outputs delay time correction circuit

(Supports up and down and right and left inversions)

• Polarity reverse circuit

• External RGB input supported

• Line inversion supported

• Supports AC drive for the LCD panel during no signal

• Serial bus for mode setting and electric VR

Package

• SQFP-64 plastic package

Package Dimensions

unit: mm

SQFP-64

[LV4124W]

SANYO: SQFP64

Single-chip LCD panel driver IC

(Supports the ALP202 LCD panel)

Page 2

No.6000-2/21

LV4124W

Electrical Characteristics at VCC1 = 4.5 V, VCC2 = VCCPCD = 12.0 V, GND1 = GND2 = GNDPCD = 0 V, VDD=

3.0 V VSS1 = VSS2 = 0 V, and Ta = 25°C

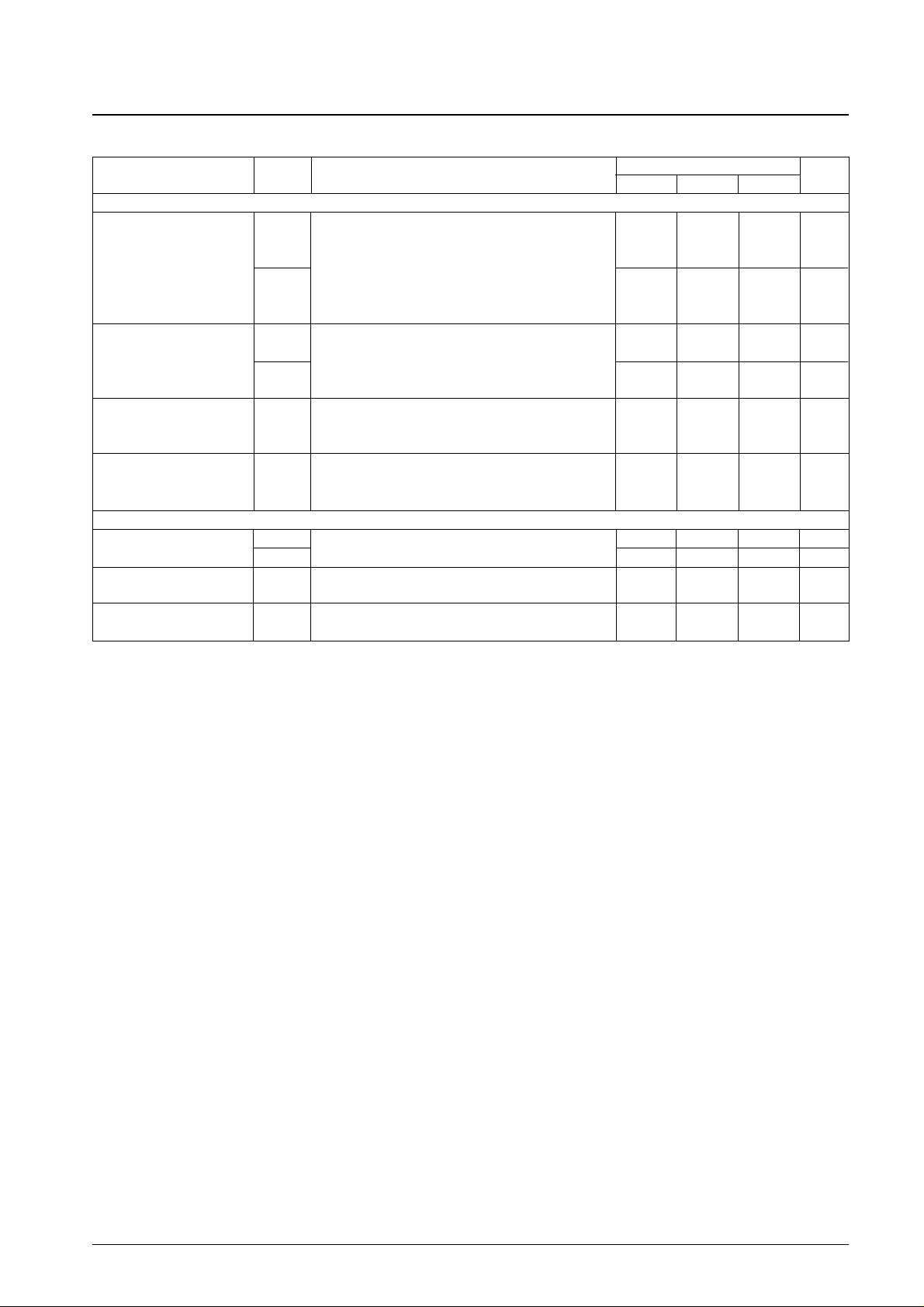

DC Characteristics

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Current Characteristics]

ICC11

Input SIG4 to (A) and SIG2 (0 dB) to (B).

Composite input 22 29 35 mA

Current drain: V

CC

1

ICC12

Measure the ICC1 current.

Y/C input 21 28 34 mA

4.5V system

ICC13

Input SIG4 to (A), (D), and (E). Y/color difference

18 23 28 mA

Measure the ICC1 current. input

Current drain: V

CC

2

ICC2

Input SIG4 to (A) and SIG2 (0 dB) to (B).

4.5 6.5 8.5 mA

12V system Measure the ICC2 current.

Current drain: V

DD

IDD

Input SIG4 to (A) and SIG2 (0 dB) to (B).

4.5 6.0 7.5 mA

MOS circuit blocks Measure the IDD current.

[Digital Block Input and Output Characteristics]

Input current

II1 Input pins with built-in pull-up resistors *

1

VIN= V

SS

–24 –60 –145 µA

II2 Input pins with built-in pull-down resistors *

2

VIN= V

DD

24 60 145 µA

High-level output voltage V

OH

1 Ioh = –1 mA *

3

VDD– 0.2 V

Low-level output voltage V

OL

1 Iol = 1 mA *

3

0.3 V

CKO pin high-level output voltage V

OH

2 Ioh = –3 mA 0.5V

DD

V

CKO pin low-level output voltage V

OL

2 Iol = 3 mA 0.5V

DD

V

RPD pin high-level output voltage V

OH

3 Ioh = –0.5 mA VDD– 1.2 V

RPD pin low-level output voltage V

OL

3 Ioh = 0.7 mA 1.0 V

RPD pin output off leakage current IOFF In the high-impedance state, V

OUT

= VSSor VDD. –40 40 µA

Input voltage threshold (high) VTDH Input pins *

1

, *

2

0.7V

DD

V

Input voltage threshold (low) VTDL Input pins *

1

, *

2

0.3V

DD

V

Notes: 1. Input pins with built-in pull-up resistors: VDIN, CSH, CSV, SCLK, DATA, and LOAD

2. Input pins with built-in pull-down resistors: PANEL and TEST

3. Output pins other than CKO and RPD: XSTH, STH, CKH2, CKH1, PCG2, PCG1, HD, XSTV, STV, CKV2, CKV1, XENB, ENB, and VD.

Specifications

Maximum Ratings at Ta = 25°C

Note *: When mounted on a printed circuit board (30 × 30 mm, t = 1.6 mm, material: glass/epoxy)

Operating Conditions at Ta = 25°C

Parameter Symbol Conditions Rating Units

V

CC

1 max Analog 4.5V system 6 V

Maximum supply voltage V

CC

2 max Analog 12V system 14 V

V

DD

max Digital system 4.5 V

Allowable power dissipation Pd max With Ta ≤ 75°C* 350 mV

Operating temperature Topr –15 to +75 °C

Storage temperature Tstg –40 to +125 °C

Input pin voltage

VINA Analog input pins –0.3 to V

CC

1 V

VIND Digital input pins –0.3 to V

DD

+0.3 V

Parameter Symbol Conditions Rating Units

V

CC

1 Analog 4.5V system 4.5 V

Recommended supply voltage V

CC

2 Analog 12V system 12.0 V

V

DD

Digital system 3.0 V

V

CC

1op Analog 4.5V system 4.25 to 5.25 V

Operating supply voltage range V

CC

2op Analog 12V system 11 to 13.5 V

V

DD

op Digital system 2.7 to 3.6 V

Page 3

No.6000-3/21

LV4124W

AC Characteristics (1) when the T41, T44, and T46 outputs are measured at the noninverted outputs.

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Luminance Signal System]

Contrast characteristics (typ.) GCNTTP

Input SIG4 to (A) and measure the ratio of the T44 output

13 17 21 dB

amplitude (white - black) to the input amplitude.

Contrast characteristics (min.) GCNTMN

Input SIG4 to (A) and measure the ratio of the T44 output

–9 –5 –1 dB

amplitude (white - black) to the input amplitude.

Maximum video gain GV

Input SIG4 to (A) and measure the ratio of the T44 output

19 22 25 dB

amplitude (white - black) to the input amplitude.

[Luminance Signal Frequency Characteristics]

Y/C input FCYYC

Take the T44 output amplitude with SIG7 (0 dB, no burst,

5.0

100 kHz) input to (A) as 0 dB. Modify the input frequency

FCYCMN 2.5 MHz

Composite input

NTSC

and determine the frequency such that the output is down

FCYCMP 2.5

PAL

–3 dB.

GSHP1X Take the T44 output amplitude with SIG7 MAX 12 16

Image quality adjustment (100 kHz) input to (A) as 0 dB. Determine

range 1 (Y/C input)

GSHP1N

the ratio of the output amplitude with a

MIN 0 2

dB

2.5-MHz SIG7 input.

GSHP3X Take the T44 output amplitude with SIG7 MAX 6 10

Image quality adjustment (100 kHz) input to (A) as 0 dB. Determine the

range 3 (composite input)

GSHP3N

ratio of the output amplitude with a 2.0-MHz

MIN –2 3

dB

SIG7 input.

Input SIG2 (0 dB) to (A) and using a spectrum analyzer,

measure the 3.58 and 4.43 MHz components in the input and

Chrominance signal leakage CRLEKY in T44. Let ∆CLK be that difference. Use that value to 30 mV

determine CRLEKY from the following formula:

CRLEKY

= 150 mV × 10

∆CLK/20

[Luminance Signal Input to Output Delay]

Y/C input TDYYC 250 350 450 ns

Input SIG5 (VL = 150 mV) to (A).Measure the delay time

TDYCMN

between a rising edge in the input and the corresponding

500 600 700 ns

Composite input

NTSC

rising edge in the T44 noninverted output.

PAL TDYCMP 500 600 700 ns

[Color Difference Signal System]

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

GEXCMX

no burst) to (D). Let VC0 be the T41 output amplitude

+4 +6 dB

(100 kHz) when COL = 128. Let VC2 be the T41 output

Color difference input color amplitude (100 kHz) when COL = 0. Let VC1 be the T41

adjustment output amplitude (100 kHz) when SIG1 is set to -10 dB and

GEXCMN

COL = 255. Then calculate the following formulas.

–15 –11 dB

GEXCMX = 20log (VC1/VC0) +10

GEXCMN = 20log (VC2/VC0)

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

no burst) to (D) and (E).

Color difference balance VEXCBL Let VB be the T41 output amplitude (100 kHz), and let VR 0.85 1 1.15 –

be the T46 output amplitude (100 kHz).

Calculate VEXCBL = VR/VB.

Continued on next page.

Page 4

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Chrominance Signal System]

NTSC –3 0 +3

ACC amplitude characteristics 1 ACC1

PAL –3 0 +3

dB

VTSC –3 0 +3

ACC amplitude characteristics 2 ACC2

PAL –3 0 +3

NTSC ±500

APC pull-in range FAPC Hz

PAL ±500

No.6000-4/21

LV4124W

Continued from preceding page

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Color Difference Signal System]

GEXRMX +2 +3 dB

Color difference input balance

adjustment R

GEXRMN –3 –4.5 dB

GEXBMX –3 –4.5 dB

Color difference input balance

adjustment B

GEXBMN +2 +3 dB

VEXGBN 0.21 0.24 0.27 –

G-Y matrix characteristics

(NTSC)

VEXGRN 0.46 0.51 0.56 –

VEXGRP 0.17 0.19 0.21 –

G-Y matrix characteristics

(PAL)

VEXGRP 0.46 0.51 0.56 –

Continued on next page.

Input SIG5 (VL = 150 mV) to (A) and SIG1 (–6 dB, 100 kHz,

no burst) to (D) and (E).

When TINT = 128, let VR0 be the T46 output amplitude

(100 kHz) and let VB0 be the T41 output amplitude (100 kHz).

When TINT = 255, let VR1 be the T46 output amplitude and

let VB1 be the T41 output amplitude.

When TINT = 0, let VR2 be the T46 output amplitude and let

VB2 be the T41 output amplitude.

Then calculate the following formulas.

GEXRMX = 20log (VR1/VR0) GEXRMN = 20log (VR2/VR0)

GEXBMX = 20log (VB1/VB0) GEXBMN = 20log (VB2/VB0)

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

no burst) to (D).

Let VEXB be the T41 output amplitude (100 kHz) and

VEXBG be the T44 output amplitude (100 kHz).Calculate

VEXGB = VEXBG/VEXB.

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

no burst) to (E).

Let VEXR be the T46 output amplitude (100 kHz) and

VEXRG be the T44 output amplitude (100 kHz).

Calculate VEXGR = VEXRG/VEXR.

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

no burst) to (E).

Let VEXR be the T46 output amplitude (100 kHz) and

VEXRG be the T44 output amplitude (100 kHz).

Calculate VEXGR = VEXRG/VEXR.

Input SIG5 (VL = 150 mV) to (A) and SIG1 (0 dB, 100 kHz,

no burst) to (D).

Let VEXB be the T41 output amplitude (100 kHz) and

VEXBG be the T44 output amplitude (100 kHz).Calculate

VEXGB = VEXBG/VEXB.

AC Characteristics (2)

Input SIG5 (VL = 150 mV) to (A), and to (B),

input SIG2 (0 dB, 3.58 MHz, burst/chrominance

phase = 180°, and also 4.43 MHz,

burst/chrominance phase = ±135°).

Measure the T44 output amplitude. Modify the

SIG2 burst frequency, until the killer is

released. Measure the frequency f1 that

appears in the T41 output.

NTSC f1 = 3579545 Hz

PAL f1 = 4433619 Hz

Input SIG5 (VL = 150 mV) to (A), and to (B),

input SIG2 (0, +6, and –20 dB, 3.58 MHz,

burst/chrominance phase = 180°, and also

4.43 MHz, burst/chrominance phase = ±135°).

Measure the T53 output amplitude, and let V0,

V1, and V2 correspond to 0 dB, +6 dB, and

–20 dB, respectively.

ACC1 = 20log (V1/V0)

ACC2 = 20log (V2/V0)

Page 5

No.6000-5/21

LV4124W

Continued from preceding page

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Chrominance Signal System]

Color adjustment

characteristics (maximum)

GCOLMX +4 +6 dB

Color adjustment

characteristics (minimum)

GCOLMN –20 –15 dB

Tint adjustment range

(maximum)

TNTMX –30 –40 deg

Tint adjustment range

(minimum)

TNTMN 30 40 deg

ACKN NTSC –36 30 dB

Killer operating input level

ACKP PAL –33 –27 dB

VRBN 0.53 0.63 0.73 –

Demodulator output

amplitude ratio (NTSC)

VGBN 0.25 0.32 0.39 –

θ RBN 99 109 119 deg

Demodulator output phase

difference (NTSC)

θ GBN 230 242 254 deg

VRBP 0.65 0.75 0.85 –

Demodulator output

amplitude ratio (PAL)

VGBP 0.33 0.40 0.47 –

θ RBP 80 90 100 deg

Demodulator output phase

difference (PAL)

θ GBP 232 244 256 deg

Input SIG5 (VL = 150 mV) to (A), and input SIG2 (0 dB,

burst/chrominance phase = 180°) to (B).

Let V0, V1, and V2 be the chrominance signal amplitude

when COL = 128, COL = 255, and COL = 0, respectively.

Calculate GCOLMX = 20log (V1/V0), and GCOLMN = 20log

(V2/V0).

Input SIG5 (VL = 150 mV) to (A), and input SIG2 (0 dB, with

a variable burst/chrominance phase) to (B).

Let θ 0, θ 1, and θ2 be the phases when the T41 output

amplitude is minimum when TINT = 128, TINT = 255, and

TINT = 0, respectively.

Calculate TNTMX = θ1 – θ0, and TNTMN = θ2 – θ0.

Input SIG5 (VL = 150 mV) to (A), and to (B),

input SIG2 (with a variable level,

burst/chrominance phase = 180°, and also

burst/chrominance phase = ±135°).

Measure the T41 output amplitude.

Gradually lower the SIG3 level (amplitude) until

the killer function operates and measure that

level.

Input SIG5 (VL = 150 mV) to (A), and input SIG3 (0 dB) to

(B).

Modify the chrominance signal phase, let VB be the

maximum amplitude of the T41 chrominance demodulated

signal, let VG be the maximum amplitude of the T44

chrominance demodulated signal, and let VR be the

maximum amplitude of the T46 chrominance demodulated

signal

Calculate VRBN = VR/VB and VGBN = VG/VB.

Input SIG5 (VL = 150 mV) to (A), and input SIG3 (0 dB) to

(B).

Modify the chrominance signal phase, let θ B be the phase

at the maximum amplitude of the T41 chrominance

demodulated signal, let θ G be the phase at the maximum

amplitude of the T44 chrominance demodulated signal, and

let θ R be the phase at the maximum amplitude of the T46

chrominance demodulated signal.

Calculate θ RBN = θ R – θ B and θ GBN = θ G – θ B.

Input SIG5 (VL = 150 mV) to (A), and input SIG3 (0 dB) to

(B).

Modify the chrominance signal phase, let VB be the

maximum amplitude of the T41 chrominance demodulated

signal, let VG be the maximum amplitude of the T44

chrominance demodulated signal, and let VR be the

maximum amplitude of the T46 chrominance demodulated

signal

Calculate VRBP = VR/VB and VGBP = VG/VB.

Input SIG5 (VL = 150 mV) to (A), and input SIG3 (0 dB) to

(B).

Modify the chrominance signal phase, let θ B be the phase

at the maximum amplitude of the T41 chrominance

demodulated signal, let θ G be the phase at the maximum

amplitude of the T44 chrominance demodulated signal, and

let θ R be the phase at the maximum amplitude of the T46

chrominance demodulated signal.

Calculate θ RBP = θ R – θ B and θ GBP = θ G – θ B.

Page 6

No.6000-6/21

LV4124W

Parameter Symbol Conditions

Ratings

Unit

min typ max

[RGB Signal and PCD Output Systems]

RGB signal and PCD output

Input SIG5 (VL = 0 mV) to (A), adjust the BRIGHT parameter

DC voltage

VOUT with the serial bus data so that T44 is 9 Vp-p, and measure 5.85 6.00 6.15 V

the DC voltages on T39, T41, T44, and T46.

RGB signal and PCD output

Determine the maximum value of the differences in the

DC voltage difference

∆VOUT measured values of VOUT in the previous item for T39, T41, 0 100 mV

T44, and T46.

VLIMMX 9.0 Vpp

RGB signal and PCD output

Color difference input balance

VLIMMN 5.2 Vpp

BRTMX 9.0 Vpp

Brightness variation

BRTMN 4.0 Vpp

PCD variation

PCDMX 9.0 Vpp

PCDMN 3 Vpp

Sub-brightness variation SBBRT ±2.0 ±3.0 V

Input SIG4 to (A) and determine the level difference between

RGB inter-signal gain difference ∆GRGB the largest and the smallest of the noninverted output –0.5 0 0.5 dB

amplitudes (white - black) for T41, T44, and T46.

RGB inverted/noninverted gain

Input SIG4 to (A) and determine the difference between

difference

∆GINV the inverted output amplitude and the noninverted output –0.5 0 0.5 dB

amplitude (white - black) for T41, T44, and T46.

RGB inter-signal black level

Input SIG4 to (A) and determine the difference between the

potential difference

∆VBL highest and lowest black levels in the inverted and 300 mV

noninverted T41, T44, and T46 outputs.

Gγ1 23.0 26.0 29.0 dB

Gamma gain Gγ2 12.0 15.0 18.0 dB

Gγ3 18.0 21.0 25.0 dB

Vγ1MN 0 IRE

Gamma 1 adjustment range

Vγ1MX 70 IRE

Vγ2MN 100 IRE

Gamma 2 adjustment range

Vγ2MX 30 IRE

tPCDH

The transition time for a load of 8000 pF and an amplitude of

2.5 µs

PCD transition time 9 V p-p.

tPCDL

tPCDH: For rising edges. tPCDL: For falling edges.

2.5 µs

Input SIG3 to (A), and measure the maximum value

(VLIMMX) and minimum value (VLIMMN) of the voltage

range (black - black) over which the black limiter operates

when V54 is varied for T39, T41, T44, and T46.

Measure VLIMMX when V54 = 0 V, and measure VLIMMN

when V54 = 4.5 V.

Input SIG5 (VL = 0 mV) to (A) and set BRT to 0. Measure

the T41, T44, and T46 outputs (black - black).

Input SIG5 (VL = 0 mV) to (A) and measure the T39 output

(black - black) when P-BRT is set to 255.

Input SIG5 (VL = 0 mV) to (A) and measure the T44 output

(black - black) with respect to the T41 and T46 outputs

(black - black) when R-BRT = B-BRT = 0, and when R-BRT

= B-BRT = 255.

Input SIG8 to (A), adjust the T44 inverted output black level

to be 1.5 V with BRT, and adjust the amplitude (black white) to be 3.5 V with CONT. Measure VG1, VG2, and VG3

and calculate the following formulas.

Gγ1 = 20log (VG1/0.0357)

Gγ2 = 20log (VG2/0.0357)

Gγ3 = 20log (VG3/0.0357)

Input SIG8 to (A) and set the T44 output (black - black) to 9

V p-p with the BRIGHT adjustment. Read the gamma gain

transition point at the input signal IRE level when γ1 = 0 and

when γ1 = 255.

V γ1MN is when γ1 = 0, and Vγ1MX is when γ1 = 255.

Input SIG8 to (A) and set the T44 output (black - black) to 9

V p-p with the BRIGHT adjustment. Read the gamma gain

transition point at the input signal IRE level when γ2 = 0 and

when γ2 = 255.

V γ2MN is when γ2 = 0, and Vγ2MX is when γ2 = 255.

Input SIG5 (VL = 0 mV) to (A) and set BRT to 255. Measure

the T41, T44, and T46 outputs (black - black).

Input SIG5 (VL = 0 mV) to (A) and measure the T39 output

(black - black) when P-BRT is set to 0.

AC Characteristics (3)

Page 7

No.6000-7/21

LV4124W

Parameter Symbol Conditions

Ratings

Unit

min typ max

[Filter Characteristics]

NTSC 1.50 MHz –15 –10 dB

Bandpass filter attenuation ATBPF

PAL 2.00 MHZ –15 –10 dB

NTSC 5.50 MHz –7 –2 dB

PAL 6.80 MHz –8 –3 dB

ATRAPN NTSC –40 –30 dB

Trap attenuation

ATRAPP PAL –40 –30 dB

R-Y and B-Y low-pass filter DEMLPF 0.7 0.9 1.1 MHz

[Sync Separator Circuit and TG System]

Input synchronizing signal

amplitude sensitivity

WSSEP 2.0 µs

Sync separator circuit input

sensitivity

VSSEP 40 60 mV

TDSYL 430 630 830 ns

Sync separator circuit output

delay

TDSYH 4.7 5.0 5.3 µs

HPLLN NTSC ±500 Hz

Horizontal pull-in range

HPLLP PAL ±500 Hz

Continued on next page.

Input SIG5 (VL = 0 mV) to (A) and SIG1

(0 dB) to (B). Take the T53 chrominance

amplitude when the center frequency

(3.58 and 4.43 MHz) is input to be 0 dB,

and measure the T53 output attenuation

for the frequencies listed at the right.

Input SIG7 (0 dB, 3.58 and 4.43 MHz) to (A)

and measure the T44 output with a spectrum

analyzer. Taking the T44 amplitude in Y/C

mode to be 0 dB, determine the attenuation in

composite input mode.

Input SIG5 (VL = 150 mV) to (A) and SIG2 (0 dB, 3.58 MHz

+ 100 kHz) to (B). Take the T44 output 100 kHz component

am plitude at this time to be 0 dB, and determine the

frequency at which the output beat component is reduced by

3 dB when the SIG2 frequency is increased from 3.58 MHz.

Input SIG5 (VL = 0 mV, VS = 143 mV, variable WS) to (A)

and verify synchronization with the T23 HD output.

Determine the value of WS at the point synchronization with

the T23 HD output is lost when the SIG5 WS is gradually

made narrower starting at 4.7 µs.

Input SIG5 (VL = 0 mV, WS = 4.7 µs, variable VS) to (A) and

verify synchronization with the T23 HD output. Determine the

value of VS at the point synchronization with the T23 HD

output is lost when the SIG5 VS is gradually reduced starting

at 143 mV.

Input SIG5 (VL = 0 mV, WS = 4.7 µs, VS = 143 mV) to (A)

and measure the delay time with respect to the T12 RPD

output. Here, TDSYL is the delay from the fall of the input

HSYNC signal to the fall of the T12 RPD output, and TDSYH

is the delay from the rise of the input HSYNC signal to the

rise of the T12 RPD output.

Input SIG5 (VL = 0 mV, WS = 4.7 µs, VS =

143 mV, variable horizontal frequency) to (A)

and verify synchronization withthe T23 HD

output. Determine the frequency fH at which

synchronization is achieved when the SIG5

horizontal frequency is varied starting from the

state where I/O synchronization is lost.

Calculate HPLLN = fH – 15734 and HPLLP =

fH – 15625.

AC Characteristics (4)

Page 8

No.6000-8/21

LV4124W

Continued from preceding page

Parameter Symbol Conditions

Ratings

Unit

min typ max

[External I/O Characteristics]

VTEXTB 0.8 1 1.2 V

External RGB input threshold

voltage

VTEXTW 1.8 2.0 2.2 V

TDEXTH 70 100 120 ns

External RGB input to output

transmission delay time

TDEXTL 70 100 120 ns

External RGB input to output

Input SIG5 (VL = 0 mV) to (A) and SIG6 (VL = 1.7 V) to (C)

blanking level difference

EXTBK and measure the difference from the T41, T44, and T46 0 V

black levels.

External RGB input to output

Input SIG5 (VL = 0 mV) to (A) and SIG6 (VL = 2.7 V) to (C)

white level difference

EXTWT and measure the difference from the T41, T44, and T46 3.5 V

black levels.

[Digital Block Output Characteristics]

Output transition time

tTLH

Input SIG5 (VL = 0 mV) to (A). Use a load of 30 pF.

30 ns

(For the pins *

3

.)

tTHL 30 ns

Cross point time difference ∆T

Input SIG5 (VL = 0 mV) to (A). Use a load of 30 pF.

10 ns

CKH1/CKH2

CKH duty DTYHC

Input SIG5 (VL = 0 mV) to (A). Use a load of 30 pF.

47 50 53 %

Measure the CKH1 and CKH2 duty.

Input SIG5 (VL = 0 mV) to (A) and SIG6 (variable VL) to (C).

Let VEXTB be the voltage at which the T41, T44, and T46

outputs reach the black level when the amplitude (VL) is

raised starting at 0 V. Then, let VTEXTW be the voltage at

which the outputs reach the white level as the amplitude is

increased further.

Input SIG5 (VL = 0 mV) to (A) and SIG6 (VL = 3 V) to (C).

Measure TDEXTH, the delay in the T41, T44, and T46

output rise, and TDEXTL, the delay in the output fall time.

Page 9

No.6000-9/21

LV4124W

Block Diagram

SERIAL

BUS I/F

Page 10

No.6000-10/21

LV4124W

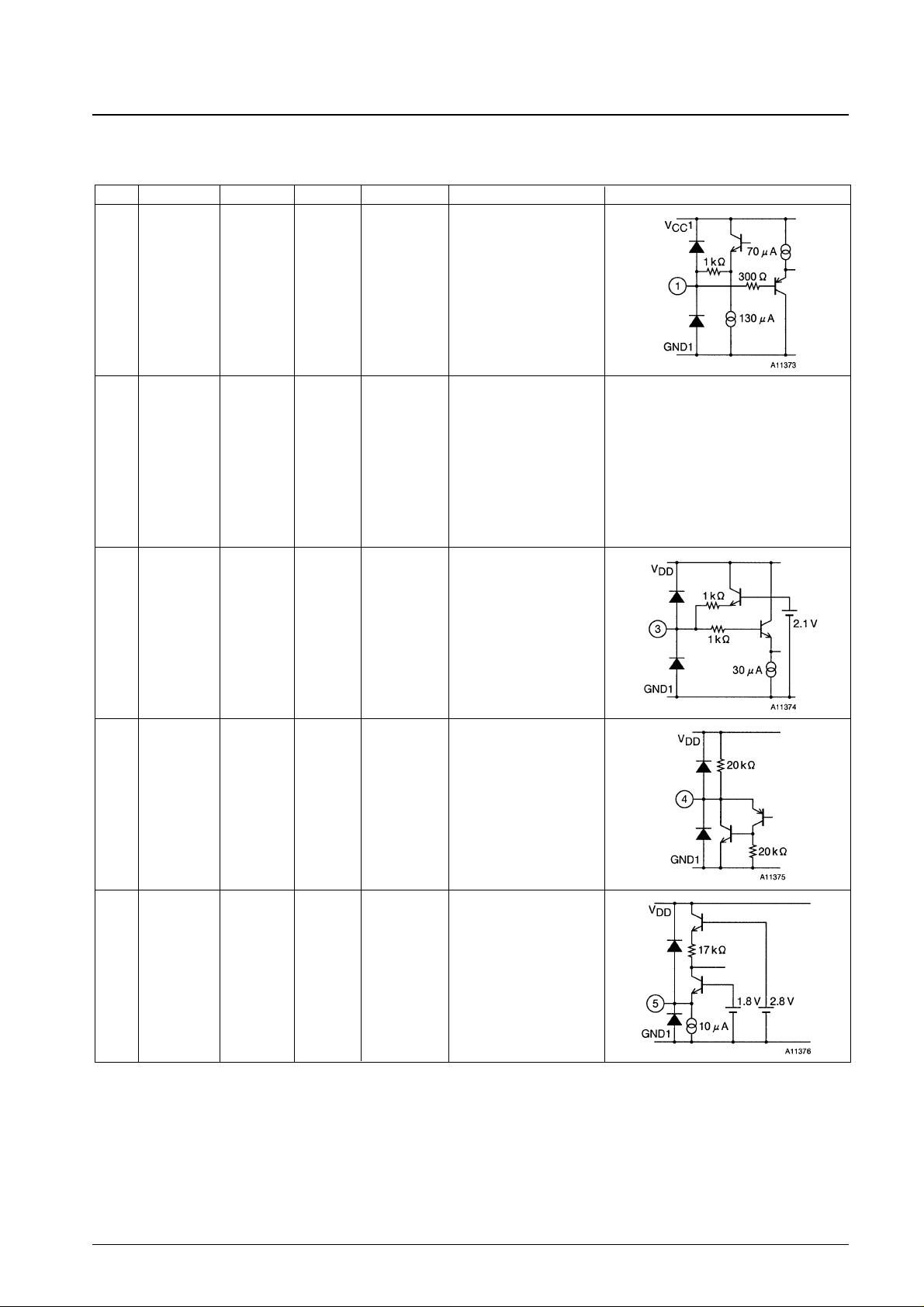

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

1 TRAP

2 GND1

3 SYNCIN

4 H.FILOUT

5 S.SEPIN

–

External trap circuit

connection.

Chrominance components are

excluded by a series LC

circuit (inductor and capacitor)

connected to ground.

(This pin is left open in Y/color

difference input mode.)

0 V

Analog 4.5V system ground

1.5 V

Sync separator circuit lowpass filter input.

The standard input signal

level is 0.5 Vp-p (sync tip to

100% white level). The input

should be provided with low

impedance (under 75 Ω).

2.3 V

Sync separator circuit lowpass filter output

1.0 V

Sync separator circuit input.

Input the waveform that

results from passing the input

signal through the sync

separator circuit low-pass

filter to this pin.

Analog Block Pin Functions

Units (Capacitors: F, Resistors: Ω)

Continued on next page.

I

O

I

Page 11

No.6000-11/21

LV4124W

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

6 EXTR

37 FBPCD

38 GNDPCD

39 PCD

40

VCCPCD

Continued on next page.

–

These pins are used to input

external digital signals.

There are two threshold

levels: Vth1 (about 1.0 V) and

Vth2 (about 2.0 V). If one of

the RGB signal exceeds Vth1,

then all of the RGB outputs

are set to the black level, and

the output only goes to the

white level when the input

exceeds Vth2.

2.5 V

Feedback circuit smoothing

capacitor connections. These

circuits are used to control the

DC levels in the RGB and

PCD outputs.

Since these are highimpedance circuits, capacitors

with low leakage must be

used.

0 V

Ground for the PCD circuit

6.0 V

PCD output

12 V

12V system power supply

used for the PCD circuit.

Use the same potential as

used for V

CC

2.

7 EXTG

8

EXTB

42 FBB

45 FBG

47 FBR

I

O

O

Page 12

No.6000-12/21

LV4124W

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

41 BOUT

43 GND2

48

VCC2

49

VCC1

50

SIG

CENTER

Continued on next page.

6.0 V

RGB signal outputs

0 V

Analog 12V system ground

12 V

Analog 12V system power

supply

4.5 V

Analog 4.5V power supply

6.0 V

RGB output DC level setting

44 GOUT

46

ROUT

O

I

Page 13

No.6000-13/21

LV4124W

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

51 BYIN

53 COUT

54 BLKLIM

55

APC

56

VXOOUT

Continued on next page.

–

These pins are used for the

color difference signal inputs

in Y/color difference input

mode. The clamp level in this

mpde is 2.8 V.

In other modes, the signal

from pin 53 is input to these

pins. In those modes the pin

voltage will be about 1.6 V.

The standard input signal

level is 0.3 V p-p for a 75%

color bar signal.

1.6 V

Provides the ACC output.

(This pin is left open in Y/color

difference input mode.)

–

Sets the RGB output

amplitude (black to black)

clipping level

2.7 V

APC filter connection.

(This pin is left open in Y/color

difference input mode.)

2.9 V

VXO output

(This pin is left open in Y/color

difference input mode.)

52 RYIN

I

O

I

O

O

Page 14

No.6000-14/21

LV4124W

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

57 VXOIN

58 VREG

59 CIN

60 START-UP

61 Y-IN

Continued on next page.

3.2 V

VXO input

(This pin is left open in Y/color

difference input mode.)

3.6 V

Regulator output

Connect a 1-µF or larger

external capacitor to this pin.

–

Inputs the video signal if a

composite input is used.

Inputs the chrominance signal

if separate Y and C signals

are used.

(This pin is left open in Y/color

difference input mode.)

–

Connection for the capacitor

that determines the time that

the RGB outputs are held at

the black level when power is

first applied.

Connect this pin to V

CC

1

through a resistor of about

22 KΩ if this function is not

used.

(Threshold level: 2.3 V)

3.1 V

Luminance (Y) signal input.

The standard input signal

level is 0.5 Vp-p (from the

sync tip to the 100% white

level.) The input should be

provided with low impedance

(under 75 Ω).

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

I

O

I

I

I

Page 15

No.6000-15/21

LV4124W

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

62 PICT

63

FOADJ

64

PWRST

–

Used to adjustment the

luminance signal frequency

characteristics.

Outlines are emphasized as

the voltage is increased.

3.0 V

Filter adjustment resistor

connection.

The reference current is

created by a 15-kΩ resistor

connected to ground.

–

Reset pin for the IC internal

CMOS circuits. A capacitor

should normally be connected

between this pin and ground.

(Threshold level: 2.2 V)

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

I

O

I

Page 16

No.6000-16/21

LV4124W

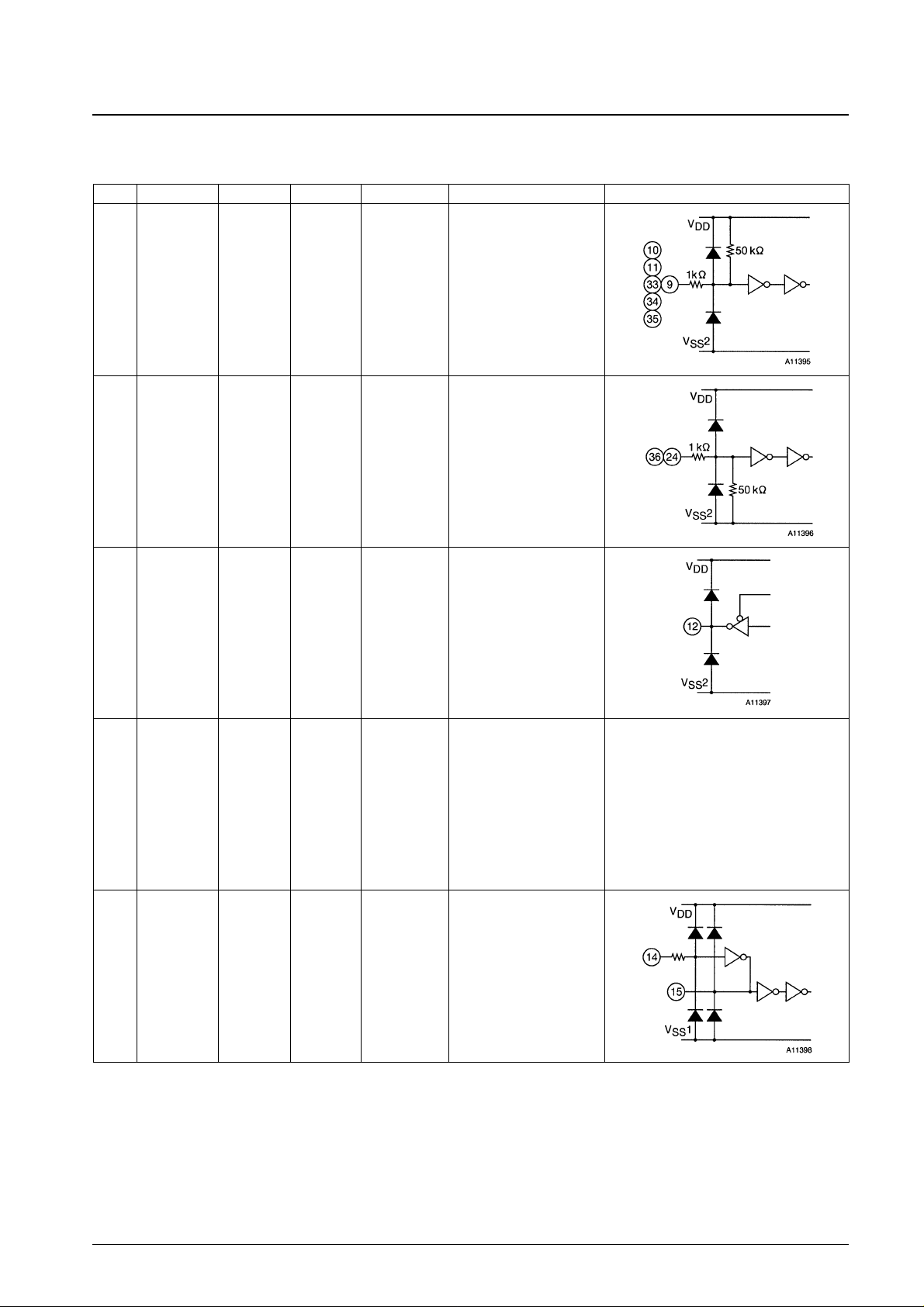

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

9

10

11

33

34

35

VDIN

CSH

CSV

SCLK

DATA

LOAD

24

36

PANEL

TEST

12 RPD

13

VSS1

14

15

CKI

CKO

Continued on next page.

V

DD

These input pins include

internal pull-up resistors

V

SS

2

These input pins include

internal pull-down resistors

–

Phase comparator output

(tristate)

–

VCO circuit digital system

ground

–

Oscillator cell input and output

Digital Block Pin Functions

Units (Capacitors: F, Resistors: Ω)

I

I

O

I/O

H

L

(L: Pulled down, H: Pulled up)

Page 17

No.6000-17/21

LV4124W

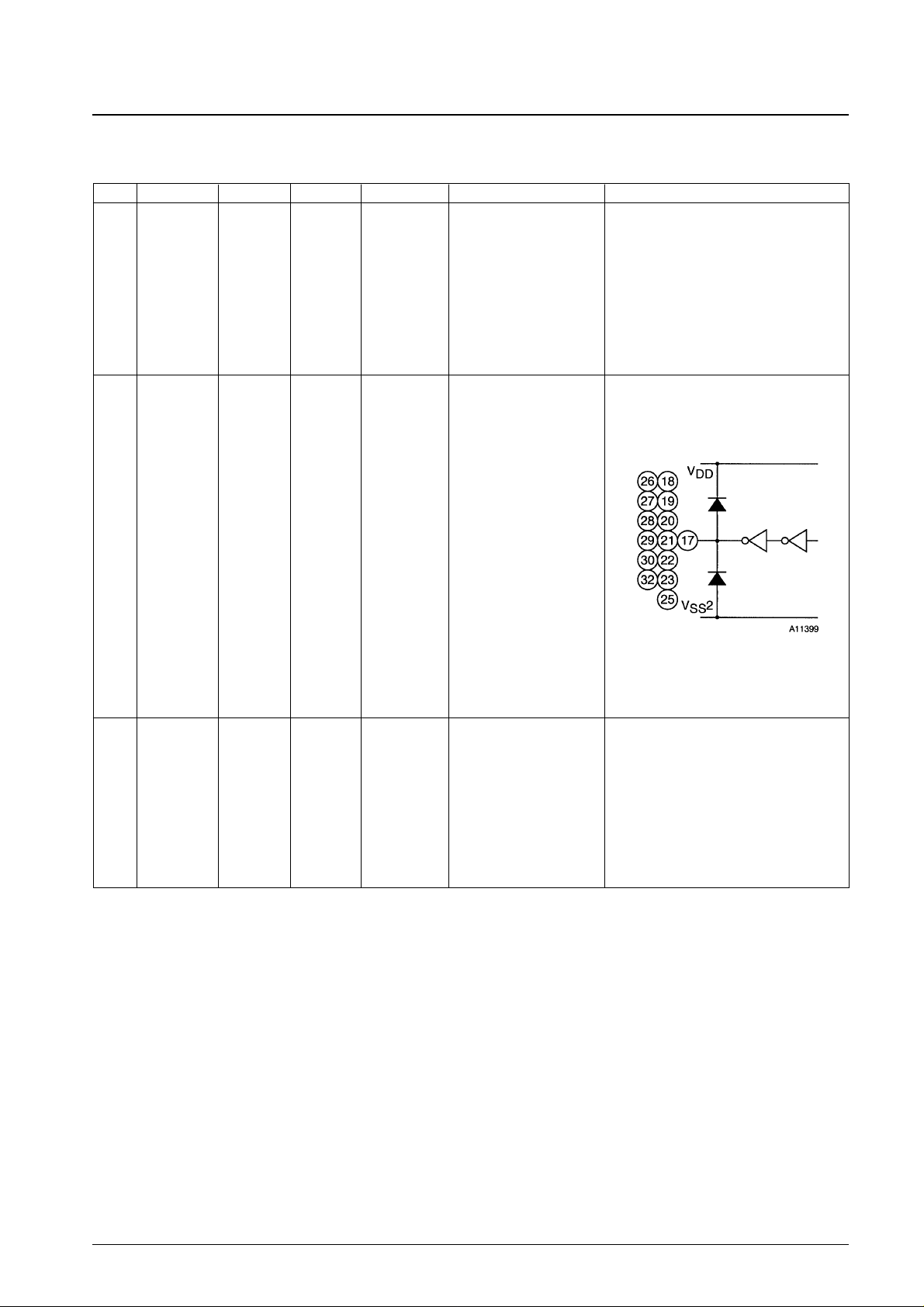

Pin No. Pin Pin voltage I/O Input handling Pin function Equivalent circuit

16

V

DD

17

18

19

20

21

22

23

25

26

27

28

29

30

32

XSTH

STH

CKH2

CKH1

PCG2

PCG1

HD

XSTV

STV

CKV2

CKV1

XENB

ENB

VD

31

VSS2

– Digital system power supply

–

Digital block outputs

0 V

Digital system ground

Continued from preceding page.

Units (Capacitors: F, Resistors: Ω)

O

Page 18

No.6000-18/21

LV4124W

Electrical Characteristics Test Circuit

Units (Capacitors: F, Resistors: Ω)

Notes: 1. The crystal used is the Kinseki, Ltd. CX-5F

Frequency deviation: Under ±30 ppm, Frequency temperature

characteristics: ±30 ppm

NTSC: 3.579545 MHz

PAL: 4.433619 MHz

2. Variable capacitance diode: 1T369 (Sony Corporation)

3. Inductance: 10 µH

4. Trap (TDK)

NTSC: NLT4532-S3R6B

PAL: NLT4532-S4R4

5. Resistor tolerance: ±2%, temperature coefficient: Under ±200 ppm.

220 pF

Page 19

No.6000-19/21

LV4124W

Measurement Waveforms

SG No. Waveform

SIG1

SIG2

SIG3

SIG4

SIG5

Continued on next page.

Sine wave video signal; with or

without burst.

(Variable amplitude, variable

frequency)

← The value at the left is 0 dB.

Chrominance signal: burst and chrominance frequency (3.579545 or 4.433619 MHz)

Variable chrominance phase, variable burst frequency

← The value at the left is 0 dB.

Five-step staircase wave

The VL amplitude is variable.

Variable VS: 143 mV unless

otherwise specified.

Variable WS: 4.7 µs unless otherwise

specified.

Variable fH: NTSC: 15.734 kHz or

PAL: 15.625 kHz unless

otherwise specified.

0.15 V

Page 20

No.6000-20/21

LV4124W

Continued from preceding page

SG No. Waveform

SIG6

SIG7

SIG8

SIG9

Variable frequency

2T pulse

The VL amplitude is variable.

Variable VS: 143 mV unless

otherwise specified.

Variable WS: 4.7 µs unless otherwise

specified.

Variable fH: NTSC: 15.734 kHz or

PAL: 15.625 kHz unless

otherwise specified.

SYNC timing

The VL amplitude is variable.

Ten-step staircase wave

Page 21

PS No. 6000-21/21

LV4124W

This catalog provides information as of August, 1998. Specifications and information herein are subject to

change without notice.

Specifications of any and all SANYO products described or contained herein stipulate the performance,

characteristics, and functions of the described products in the independent state, and are not guarantees

of the performance, characteristics, and functions of the described products as mounted in the customer’s

products or equipment. To verify symptoms and states that cannot be evaluated in an independent device,

the customer should always evaluate and test devices mounted in the customer’s products or equipment.

SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all

semiconductor products fail with some probability. It is possible that these probabilistic failures could

give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire,

or that could cause damage to other property. When designing equipment, adopt safety measures so

that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective

circuits and error prevention circuits for safe design, redundant design, and structural design.

In the event that any and all SANYO products described or contained herein fall under strategic

products (including services) controlled under the Foreign Exchange and Foreign Trade Control Law of

Japan, such products must not be exported without obtaining export license from the Ministry of

International Trade and Industry in accordance with the above law.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or

mechanical, including photocopying and recording, or any information storage or retrieval system,

or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

Any and all information described or contained herein are subject to change without notice due to

product/technology improvement, etc. When designing equipment, refer to the “Delivery Specification”

for the SANYO product that you intend to use.

Information (including circuit diagrams and circuit parameters) herein is for example only; it is not

guaranteed for volume production. SANYO believes information herein is accurate and reliable, but

no guarantees are made or implied regarding its use or any infringements of intellectual property rights

or other rights of third parties.

Loading...

Loading...