Page 1

FILE NO.

SERVICE MANUAL

LCD TV

LCD-46XZ10FH

PRODUCT CODE No.

PRODUCT CODE No.

1 682 349 56: PAL-BG(TV) DTV

REFERENCE No.:SM0915098

Page 2

CONTENTS

Safety precautions………………………………………………………………………..…

Alignment instructions …………………………….…….…………………………………

Method of software upgrading……………………………………………………………..

Working principle analysis of the unit……………………………….………….………….

Block diagram…………………………………..………………………………….…………

IC block diagram and instruction…………………………………………………………..……

Wiring diagram …………………………………………………………………………….

Troubleshooting guide ………………………………………………………………..……

Schematic diagram…………………………………………………………………………

APPENDIX-A: Main assembly list

APPENDIX-B: Exploded View

Assemble & Disassemble the Pedestal Base

Wall mounting instructions

3

5

11

15

18

19

23

24

27

Page 3

Attention: This service manual is only for service personnel to take reference with. Before

servicing please read the following points carefully.

Safety precautions

1. Instructions

Be sure to switch off the power supply before replacing or welding any components or

inserting/plugging in connection wire Anti static measures to be taken (throughout the entire

production process!):

a) Do not touch here and there by hand at will;

b) Be sure to use anti static electric iron;

c) It’s a must for the welder to wear anti static gloves.

Please refer to the detailed list before replacing components that have special safety requirements.

Do not change the specs and type at will.

2. Points for attention in servicing of LCD

2.1 Screens are different from one model to another and therefore not interchangeable. Be sure to

use the screen of the original model for replacement.

2.2 The operation voltage of LCD screen is 700-825V. Be sure to take proper measures in

protecting yourself and the machine when testing the system in the course of normal operation or

right after the power is switched off. Please do not touch the circuit or the metal part of the module

that is in operation mode. Relevant operation is possible only one minute after the power is

switched off.

2.3 Do not use any adapter that is not identical with the TV set. Otherwise it will cause fire or

damage to the set.

2.4 Never operate the set or do any installation work in bad environment such as wet bathroom,

laundry, kitchen, or nearby fire source, heating equipment and devices or exposure to sunlight etc.

Otherwise bad effect will result.

2.5 If any foreign substance such as water, liquid, metal slices or other matters happens to fall into

the module, be sure to cut the power off immediately and do not move anything on the module lest it

should cause fire or electric shock due to contact with the high voltage or short circuit.

2.6 Should there be smoke, abnormal smell or sound from the module, please shut the power off at

once. Likewise, if the screen is not working after the power is on or in the course of operation, the

power must be cut off immediately and no more operation is allowed under the same condition.

2.7 Do not pull out or plug in the connection wire when the module is in operation or just after the

power is off because in this case relatively high voltage still remains in the capacitor of the driving

circuit. Please wait at least one minute before the pulling out or plugging in the connection wire.

2.8 When operating or installing LCD please don’t subject the LCD components to bending, twisting

or extrusion, collision lest mishap should result.

2.9 As most of the circuitry in LCD TV set is composed of CMOS integrated circuits, it’s necessary

to pay attention to anti statics. Before servicing LCD TV make sure to take anti static measure and

ensure full grounding for all the parts that have to be grounded.

2.10 There are lots of connection wires between parts behind the LCD screen. When servicing or

moving the set please take care not to touch or scratch them. Once they are damaged the screen

Page 4

would be unable to work and no way to get it repaired.

If the connection wires, connections or components fixed by the thermotropic glue need to

disengage when service, please soak the thermotropic glue into the alcohol and then pull them out

in case of dagmage.

2.11 Special care must be taken in transporting or handling it. Exquisite shock vibration may lead to

breakage of screen glass or damage to driving circuit. Therefore it must be packed in a strong case

before the transportation or handling.

2.12 For the storage make sure to put it in a place where the environment can be controlled so as to

prevent the temperature and humidity from exceeding the limits as specified in the manual. For

prolonged storage, it is necessary to house it in an anti-moisture bag and put them altogether in one

place. The ambient conditions are tabulated as follows:

o

Temperature Scope for operation

5

~ +35

C

Scope for storage -15~ +45 oC

Humidity Scope for operation 20% ~ 80%

Scope for storage <= 80%

2.13 Display of a fixed picture for a long time may result in appearance of picture residue on the

screen, as commonly called “ghost shadow”. The extent of the residual picture varies with the

maker of LCD screen. This phenomenon doesn’t represent failure. This “ghost shadow” may remain

in the picture for a period of time (several minutes). But when operating it please avoid displaying

still picture in high brightness for a long time.

3. Points for attention during installation

3.1 The front panel of LCD screen is of glass. When installing it please make sure to put it in place.

3.2 For service or installation it’s necessary to use specified screw lest it should damage the screen.

3.3 Be sure to take anti dust measures. Any foreign substance that happens to fall down between

the screen and the glass will affect the receiving and viewing effect

3.4 When dismantling or mounting the protective partition plate that is used for anti vibration and

insulation please take care to keep it in intactness so as to avoid hidden trouble.

3.5 Be sure to protect the cabinet from damage or scratch during service, dismantling or mounting.

Page 5

Alignment instructions

Test equipment

VG-848 (VGA, YPbPr signal generator)

VG-849 (HDMI digital video signal generator)

CA210 (color analyzer)

1 Alignment flow

1.1 Voltage of power supply test

According to the wiring diagram “9232KE6302JL”, connect power board, digital board, IR board

correctly; then power on and press key “standby” .

a) Test voltage of socket X801 each pin in turn listed as Table 1.

Table 1 Voltage of X801 each pin

X801 Pin1 2 3 4 5 6 7 、8 9 、10 11 12 13

8.55

Voltage >2.5 V 0

4.85 V ~

5.35 V

4.85 V ~

0

5.35 V

V~

9.45

V

0

11.4 V ~

12.6 V

0

3.2V~

3.4V

4.9V~

5.1V

b) Test voltage of socket XV03 each pin in turn listed as Table 2.

Table 2 Voltage of XV03 each pin

XV03

Voltage

Pin1、2 3、4、5

23.8 V~25.2 V

0

Page 6

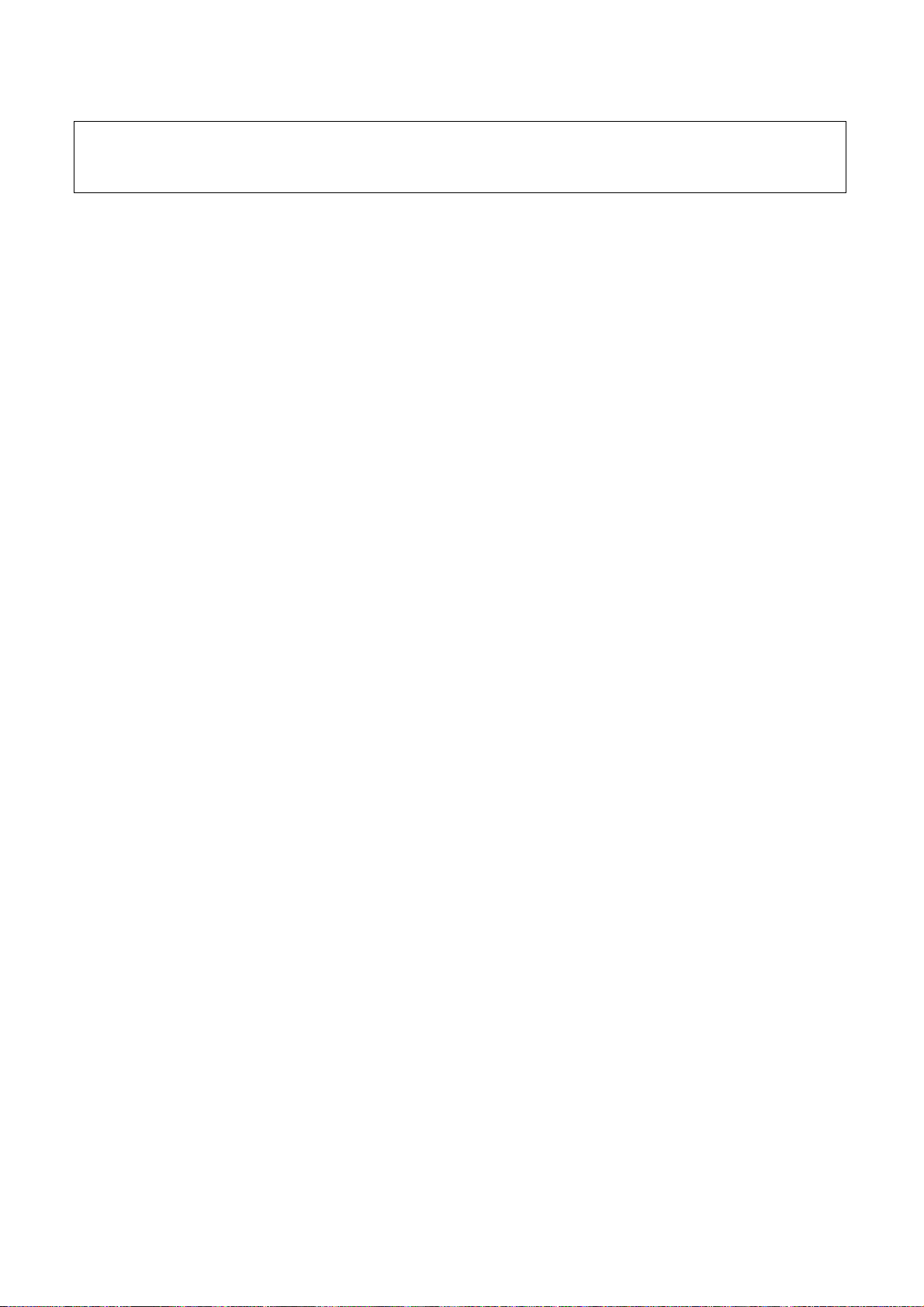

1.2 Adjustment flow chart as Fig.1

Check if DDC、、HDCP KEY and FLASH

have been burned.

combination adjustment for general

assembly

white balance adjustment

Connect to central signal source, check if

TV functions are normal -omitted channel,

analog parameters control, etc; check if

output of earphone and speaker are

normal.

Input AV/SVIDEO/SCART signal,check if

functions of every channel are normal.

Input high-definition component signal

(mode), check if every YPbPr function is

normal.

Check accessories and packing.

setup before leaving factory

Input HDMI signal,check if the display is normal;

check if every function is normal –analog

parameter control, horizontal/vertical center, etc.

Input VGA signal,check if the display is normal;

check if every function is normal -analog

parameter control, horizontal/vertical center, etc.

Fig.1 Adjustment flow chart

2 Alignment instruction

2.1 Unit adjustment

2.1.1 According to the wiring diagram “9232KE5201JL”, connect power board, main board,

IR board, key board correctly; then power on,

check if the display is normal.

2.1.2 Using method of factory menu

a) First press key “SOURCE”,then press number key “2、5、8、0” in turn to enter into initial

factory menu;

b) Press keys “CH+” and “CH-” can move cursor to each page of initial factory menu, then press

key “OK” can enter into adjustment menu of each page;

c) Press keys “CH+” and “CH-” can move cursor upwards and downwards within one adjustment

page;

d) Move cursor to one adjustment item, then press keys “VOL-” and “VOL+” can adjust it;

e) Press key “MENU” can exit adjustment menu of one page to its superior factory menu;

f) Press key “EXIT” can exit factory menu at any time;

g) Press key “OK” can enter into inferior factory menu;

Page 7

h) Factory menu item “ADC Calibrate” is used to correct ADC of VGA and Component

channel;

i) Factory menu item “W/B ADJUST” is used to adjust white balance;

j) Factory menu item “POWER MODE” is used to set power-on mode, “Standby” means the

set will be in standby state after power-on; “MEM” means the set will be in the state before

the last power-off; “ForceOn” means the set will be working automatically after power-on,

this mode is also used for factory-machine-aging; default setting should be “Standby” mode

unless specified by customer requirement;

k) Factory menu item “ISP MODE” is used to upgrade unit software from VGA port when the

item is set as “ON” and the set is connected to ISP adjustment equipment; DDC function of

VGA port will be recovered when the item is set as “OFF”; the value of the item can not be

kept in the memory, that is to say the item is reset as “OFF” after power-on again;

l) Factory menu item “RESET ALL” is used to reset factory menu data and user menu data;

after execute the item, the set will be started up again and the startup guided picture will be

displayed;

m) Factory menu item “FACTORY CHANNEL PRESET” is used to preset factory programs

data; it is necessary to connect to central signal source for DTV searching programs. Now

digital frequency of central signal CH28(529.5 MHz) and CH33(564.5 MHz) are distributed

to Australia programs. Primary preset programs would not be modified along with the

changing of central signals, so please select item DTV in menu Channel to manual search

digital programs, the process will spend about 15s;

n) Factory menu item “CUSTOM CHANNEL PRESET” : first delete all DTV/ATV programs for

factory adjustment, then preset ATV channel data according to customer order requirements;

please execute the item to clear out all programs for factory adjustment before leaving

factory;

o) Factory menu item “MST Debug” :default setting “OFF” is used for engineering models

whose RS232 functions can measure up to design specifications; setting “ON” is convenient

for debugging by developing tools; the value of the item can not be kept in the memory, that

is to say the item is reset as “OFF” after power-on again;

p) Factory menu item “BACKLIGHT” is used to adjust backlight brightness, adjust the item and

test voltage of X801-12# (PWM) to measure up to the maximum PWM voltage in panel

specification;

q) Factory menu item “SSC ADJUST” is used to adjust expended functions of frequency

content, the software having been preset according to model need not be adjusted again;

r) Factory menu item “AUDIO Curve” is used to adjust audio curve; without special customer

requirements, the software having been preset according to model need not be adjusted

again;

If the software has been upgraded or EEPROM has data already, please execute item

“RESET ALL” before adjustment for the first time.

2.1.3 ADC calibration

ADC calibration of VGA channel

a) Switch to VGA channel;

b) Press key “SOURCE”, then press number keys “2、5、8、0” to enter into initial factory menu;

c) Move cursor to item “ADC ADJUST” and press key “OK” to enter into interior factory menu;

d) Input VGA signal (VG-848 Timing:856(1024×768/60 Hz),Pattern 920 Gray 8 step(H)),

Page 8

move cursor to item “MODE”,press keys “▲” and “▼” to select item “RGB”, then move

cursor to item “AUTO ADC” and press key “OK” to begin adjustment automatically until

adjustment completion.

ADC calibration of YPbPr channel

a) Switch to YPbPr channel;

b) Press key “SOURCE”,then press number keys “2、5、8、0” to enter into initial factory menu;

c) Move cursor to item “ADC ADJUST” and press key “OK” to enter into interior factory menu;

d) Input YPbPr signal (VG848 Timing 976(720P),Pattern 918 SMPTE Color Bar), move

cursor to item “MODE”,press keys “▲” and “▼” to select item “YPbPr(HD)”, then move

cursor to item “AUTO ADC” and press key “ENTER” to begin adjustment automatically, a

prompt “success” displayed under “AUTO ADC” means auto-adjustment completed

successfully;

e) Input YPbPr signal (VG848 Timing 968(408I),Pattern 918 SMPTE Color Bar), move

cursor to item “MODE”,press keys “▲” and “▼” to select item “YPbPr(SD)”, then move

cursor to item “AUTO ADC” and press key “ENTER” to begin adjustment automatically, a

prompt “success” displayed under “AUTO ADC” means auto-adjustment completed

successfully;

2.2 White balance adjustment

Unless specified by customer, default COOL color temperature is

12000K, chromaticity

coordinates is ( 272 、 278 ); default Normal color temperature is 9300K, chromaticity

coordinates is(285、293); default Warm color temperature is 6500K, chromaticity coordinates

is (323、329).

2.3 White balance adjustment processes

The set should be working above 30 minutes before white balance adjustment for it would be in

a stabler state. Use white balance apparatus CA-210 and switch to any channel have checked.

a) Switch to HDMI channel;

b) Press key “SOURCE”, then press number keys “2、5、8、0” in turn to enter into initial factory

menu;

c) Move to item “W/B ADJUST” and press key “OK” to enter into interior factory menu;

d) Input DVI/HDMI signal (VG-848 Timing: 856(1024×768/60 Hz),Pattern:921 16 step

Gray), move cursor to item “MODE”, press keys “▲” and “▼” to select item “HDMI1” or

other HDMI channels, then move cursor to item “TEMPERTURE”, press keys “▲” and “▼”

to select item “COOL”;

e) Adjust items “R GAIN、G GAIN、B GAIN” to set chromaticity coordinates of the 14

is (272、278);

f) Adjust item “R Offset、G Offset、B Offset” to set chromaticity coordinates of the 4

th

(272、278);

g) During adjustment , make sure that color temperature of bright step is (X=272±10 Y=278±10)

and color temperature of dark step is (X=272±10 Y=278±10);

h) Then move cursor to item “COPY ALL” to copy white balance data to the other channels

except DTV channel;

i) Check if color temperature of HDMI NORMAL and WARM meet requirements as below:

bright step: allowable error is ±10, dark step: allowable error is ±10;

otherwise adjust items “R_GAIN /B_GAIN/R_OFF/B_OFF” to meet requirements and then

save data;

th

step

step is

Page 9

j) Switch to other channels ATV, AV,COMPONENT and D-SUB , check if color temperature of

COOL,NORMAL and WARM meet requirements; otherwise adjust them respectively with

16 step Gray signal and the same adjustment method as HDMI channel’s; exit menu “W/B

ADJUST” after adjustment and the data would be saved automatically;

k) DTV channel adjustment: switch to DTV channel, input 16 step Gray signal, enter into

factory menu, then begin adjustment followed by steps “e, f, g”;

l) Adjustment rules for reference as below:

adjust B gun: adjust B gun value downwards , then coordinates of X、Y will rise;

adjust B gun value upwards , then coordinates of X、Y will descent;

adjust R gun will effect the coordinate of X , and effect the value of Lv a little:

adjust R gun value upwards , then coordinate of X will rise;

adjust R gun value downwards , then coordinate of X will descent;

adjust G gun will effect the coordinate of Y , and effect the value of Lv a lot:

adjust G gun value upwards , then coordinate of Y will rise;

adjust G gun value downwards , then coordinate of Y will descent;

note: default color temperature for SANYO customer is Normal; change to picture mode

Dynamic, adjust chromaticity coordinates of color temperature Normal and Cool;

only adjust chromaticity coordinates of color temperature Cool for other customers when

picture mode is Dynamic.

3 Performance check

3.1 TV functions

Connect RF port to central signal source, first enter into menu

programs automatically, check if there is any omitted program, check if the output of speakers is

normal, check if the picture is normal.

3.2 AV/S-Video port

Input AV/S-Video signal respectively, check if the picture, the sound and other functions are

normal;

3.3 VGA port

Input VGA signal from signal generator VG-848 with VGA formats as Tab le 5 respectively, check

if the display and the sound are normal; if there is any deviation of line or field, enter into main

menu, select and execute items “Picture->Screen->Auto Adjusting” in turn to correct them

automatically.

CHANNEL, then search

Page 10

Table 5 VGA receiving signal formats

Horizontal

No. Definition

1 640×480 31.469 59.94 25.175 IBM

2 720×400 31.469 70.086 28.322 IBM

3 640×480 37.861 72.809 31.5 VESA

4 640×480 37.5 75 31.5 VESA

5 800×600 35.156 56.25 36 VESA

6 800×600 37.879 60.317 40 VESA

7 800×600 48.077 72.188 50 VESA

8 800×600 46.875 75 49.5 VESA

9 1024×768 48.363 60.004 65 VESA

10 1024×768 56.476 70.069 75 VESA

11 1024×768 60.023 75.029 78.75 VESA

12 1152×864 67.5 75 108 VESA

13 1280×960 60 60 108 VESA

14 1280×1024 63.98 60.02 108 VESA

15 1280×1024 80 75 135 SXGA

16 1440×900 - 60 - -

17 1680×1050 - 60 - -

18 1360×768 47.7 60 85.5 -

frequency

(kHz)

Vertical

frequenvy

(Hz)

Dot-pulse

frequency

(MHz)

Remark

3.4 HDMI port

Input HDMI signal from signal generator VG-849 with the formats as Table 4 and Tab le 5

respectively, check if the display and the sound(32 KHz、44.1 KHz、48 KHz)are normal under

the circumstances of power-on/off, switching channel, switching signal format, etc.

3.5 Other functions check

a) Check if the functions are normal —timing turn-on/off 、turn-off of sleeping time 、

picture/sound mode、OSD、stereo and digital audio interface, etc.;

b) Check if audio only digital programs (RADIO) are normal;

c) For UK models, check if MHEG function of digital programs are normal;

d) Check if common interface(CI:Common Interface)is normal;

e) For New Zealand models, check if function of logic channel number (LCN) is normal, check

if function of Over Air Download(OAD)is normal;

f) For France, UK and Italy models, check if function of logic channel number (LCN) is

normal.

Page 11

4 User menu setup before leaving factory

Enter into page “LOCK” of user menu, select submenu item “Restore Factory Default” to preset

items before leaving factory as below:

a) Clear out all programs information;

b) Clear out information of parental control (VCHIP);

c) Default setup of user analog data;

d) Set Menu Language as English;

e) Set Power on MODE as Off.

Method of software upgrading

Instruction of factory software burning as Table 6

Table 6 Instruction of factory software burning

Instruction of

No. Part No. Part type

N111 5272564002 EN25Q64-104HIP FLASH Yes

N108 5272404002 AT24C04 HDMI KEY Yes

NA04 5272402002 AT24C02 HDMI EDID Yes

NA05 5272402002 AT24C02 HDMI EDID Yes

NA06 5272402002 AT24C02

N106 5272402002 AT24C02 VGA EDID Yes

software

function

HDMI EDID

(supporting

the 3rd HDMI)

Burned

before

SMT

Yes

Burning method

burned with program

ALL11, write-protect setup,

refer to Note 1 in detail

burned with program ALL11

burned with program ALL11

burned with program ALL11

burned with program ALL11

burned with program ALL11

Note 1: Write-protect setup method

Enter into burning interface of

program ALL-100, select item “Config”, press item “config

Setting”, set item “Protect” as “All Protect”; be sure to select item “Config” before burning

software, and write-protect must be re-set after burning program ALL-100 startup every time.

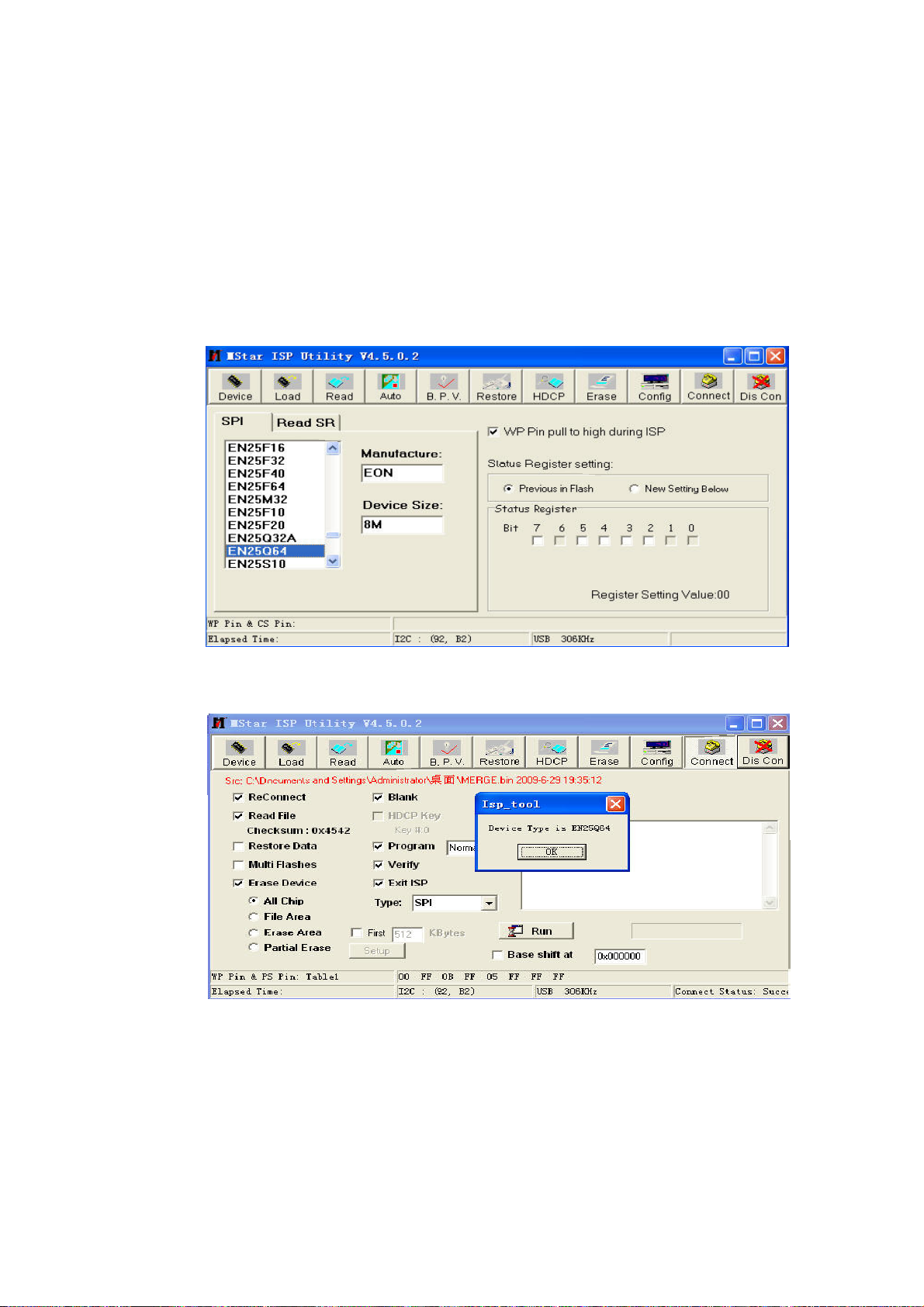

Note 2: Burning and upgrading software method with burning tool ISP

Page 12

1) Main board upgrading: connect the cable of burning tool ISP to Debug port(location No. X807)

of main board;

Unit upgrading: connect both VGA ports between burning tool ISP and main board, then enter

into factory menu and set item “ISP Mode” as “ON”;

2) Use on-line burning tool of Mstar, enter into menu “Device”, select item “WP Pin pull to high

during ISP” as Fig. 2; for the normal erasing process, make sure hardware write-protect of Flash

is canceled;

Fig. 2 Write-protect setup

3) Select menu “Connect”, a dialog “Device Type is EN25Q64” will be displayed as Fig. 3 , that is

Fig. 3 Device EN25Q64 successful connection

If failing to connecting, select the first menu “Device” and select item “EN25Q64” manually, then

press key “Connect”.

Page 13

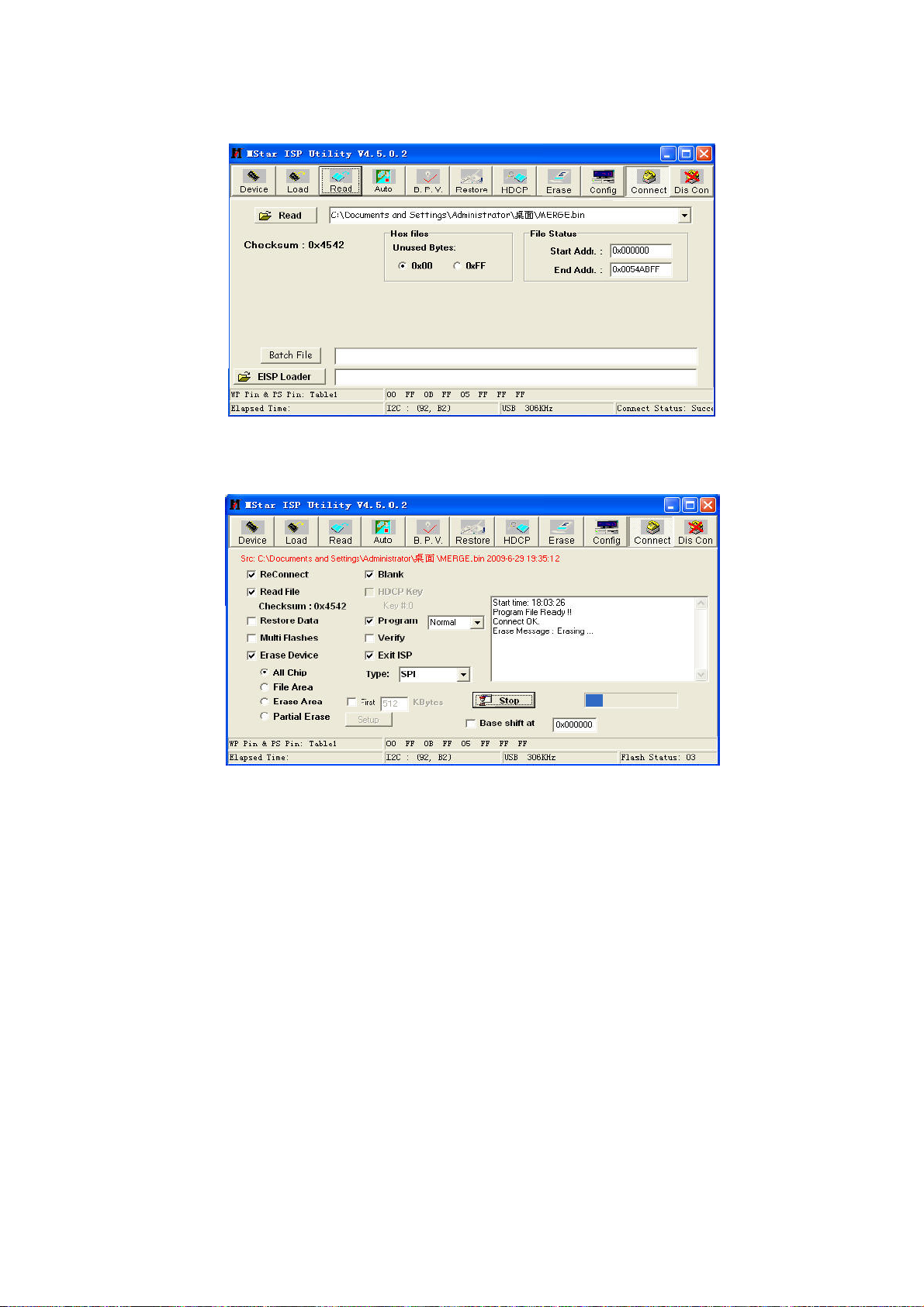

4) Press key “Read”,select burning file (for example MERGE.bin) as Fig. 4.

Fig. 4 Burning file

5) Select menu “Auto”, then select items “All chip”, “program” and other configuration as Fig. 5

Fig. 5 Burning Configuration

6) Press key “Run” as Fig. 4 to begin burning software, there are two steps for the process: Erase

and Program

normal burning steps are as follows:

the first step “Erasing…, Flash Status: 03” will be lasting for a moment, otherwise skipping over

means unsuccessful erasing; please confirm process (2) and then burn software again;

the following step “Programming…,Flash Status:00” will be done until a prompt “Pass” is

displayed.

Page 14

7) A prompt “Pass” will be displayed beside the key “Run” for successful burning as Fig. 6

Fig. 6 A prompt “Pass” beside the key “Run” for successful burning

8) Need not exit ISP burning interface and only repeat the process 3)and 5)to go on burning

software for other sets.

Note 3: On-line burning and upgrading method from USB port

1) Be sure to format a U disk as FAT32;

2) Copy program file to the U disk with the name “Merge.bin”;

3) Power on, be sure to switch to ATV or DTV channel and not to display OSD interface; insert the U

disk into a USB port, then USB upgrading process will begin automatically;

4) Upgrading processes:

A、Reading data from the U disk:

A prompt “Searching USB” is displayed and an indicating light of U disk is twinkling;

B、Burning Flash:

A prompt “Updating! Please don’t power off!!!” is displayed and an indicating bar is showing

upgrading schedule; the set will be in Standby mode after the burning process completed;

5) Start up the set again, enter into factory menu to verify software version and time parameters;

then execute item “RESET ALL” to complete the whole burning process.

*** Method of burning from USB could not be sure to be suitable for all kinds of U disks, so please try

other U disks if necessary.

Page 15

Working principle analysis of the unit

1、 PAL/SECAM signal flow

PAL/SECAM signal from antenna is inputted into TUNER FQD1116 which is

an analog-digital-integrative model, the analog RF signal is demodulated by the

TUNER, then CVBS signal and

outputted. TUNER FQD1116 is controlled by main chip MSD209(with embedded

CPU) through I2C bus.

TV CVBS signal is inputted into main chip MSD209 directly to be processed

by modules “VIDEO DECODER、DEINTERLACE and SCALER”, then LVDS

signal is outputted to drive LCD panel.

SIF audio signal is inputted into main chip MSD209 directly and processed

by modules of demodulation, pre-amplification, acoustic effect processing and

volume control, then the audio signal are inputted into left and right sound tracks

of earphone amplifier BH3547F to be amplified and then are divided to two

signals, one is outputted to earphone jack, the other is inputted into class D audio

power amplifier R2A15112 to be amplified and then be outputted to speakers.

2、 DVB-T signal flow

DVB-T signal from antenna is inputted into TUNER FQD1116 to be tuned,

RF amplified, IF amplified and SAW FILTER inside, then IF signal is outputted to

demodulating chip CE6353 to be demodulated and then be inputted into main

chip MSD209 with format of standard serial or parallel TS stream for demultiplexing

and decoding.

Video route: demultiplexed video signal is decoded by main chip MSD209

and then digital video signal is outputted; in the end LVDS signal is outputted to

drive LCD panel after a series of digital processes and OSD addition within main

chip MSD209.

Audio route: demultiplexed audio signal is decoded into Dolby AC-3

signal or MPEG multi-sound-track digital audio signal by inner decoder of main

chip MSD209, then one is outputted through SPDIF directly; after the process of

“sub-transform and DAC”, the other is outputted as analog audio signal, the analog

audio signal is inputted into the rear part of main chip MSD209 for acoustic effect

processing and volume control, then inputted into left and right sound tracks of

earphone amplifier BH3547F respectively to be amplified, now the audio signal is

divided into two, one is outputted to earphone jack directly, the other is inputted into

class D audio power amplifier R2A15112 to be amplified and then outputted to speakers.

3、 AV signal flow

After processed by impedance matching, AV video signal is inputted into

main chip MSD209 directly and processed by modules of “VIDEO DECODER、

DEINTERLACE and SCALER”, then LVDS signal is outputted to drive LCD

panel.

AV audio signal is processed by circuits of “voltage divided, impedance

matching and AC coupling”, then inputted into main chip MSD209 directlyfor acoustic

effect processing and volume control, then inputted into left and right sound tracks of

earphone amplifier BH3547F respectively to be

SIF(sound intermediate frequency) signal are

Page 16

amplified, now the audio signal is divided into two, one is outputted to earphone

jack directly, the other is inputted into

to be amplified and then outputted to speakers.

4、 PC/YPbPr signal flow

After processed by impedance matching, PC/YPbPr video signal is inputted

into main chip MSD209 to be processed by modules of “A/D transform, digital

video processing and OSD addition”, then LVDS signal is outputted to drive LCD

panel.

PC/YPbPr audio signal is processed by circuits of “voltage divided,

impedance matching and

for acoustic effect processing and volume control, afterwards the audio signal is

inputted into left and right sound tracks of earphone amplifier BH3547F directly to be

amplified, now the audio signal is divided into two, one is outputted to earphone jack

directly, the other is inputted into class D audio power amplifier R2A15112 to be

amplified and then outputted to speakers.

5、 HDMI signal flow

HDMI video signal is inputted into main chip MSD209 to be processed by

modules of “digital video processing and OSD addition”, then LVDS signal is

outputted to drive LCD panel.

HDMI audio signal is decoded into Dolby AC-3 signal or MPEG multi-soundtrack digital audio signal by inner decoder of main chip MSD209, then one is

outputted through SPDIF directly; after the process of “sub-transform and DAC”,

the other is outputted as analog audio signal

the rear part of main chip MSD209 for acoustic effect processing and volume control,

then inputted into left and right sound tracks of earphone amplifier BH3547F

respectively to be amplified, now the audio signal is divided into two, one is outputted

to earphone jack directly, the other is inputted into class D audio power amplifier

R2A15112 to be amplified and then outputted to speakers.

6、 Brief instruction on unit functions

MPEG-2 MP@HL、H.264 Main and High profile up to Leve4.0 Decoding

MPEG、

3D comb filter

Wide-range power supply、low consumed power in standby mode(≤1W)

Class D audio power amplifier with HI-FI acoustic effect output

High quality transformation from interleaved scanning to progressive scanning

Realizing integrative functions really

- build integration

- integrative TUNER(integrating analog with digital)

- integrative searching-program function

- integrative OSD interface

Main parts of the unit:

46 inch LCD panel(1920X1080)

Dolby Digital(AC-3)、AAC Digital Audio Decoding

AC coupling”, then inputted into main chip MSD209 directly

class D audio power amplifier R2A15112

, the analog audio signal is inputted into

Page 17

Main chip:MStar MSD209FG-LF

Demodulating chip:Intel CE6353

TUNER:NXP FQD1116ME/IV

DDR:SAMSUNG K4T51163QC-HCF7

Two groups of Video input and RCA L/R input

One group of S-VIDEO input

One group of VGA input

One group of audio input for VGA and DVI(Mini Phone Jack)

One group of RF

One group of RS232(Mini Phone Jack)

One group of audio output(Mini Phone Jack)

One group of Video output and RCA L/R output

One group of SPDIF(coaxial)output

One group of USB(for upgrading)

Class D audio power amplifier:RENESAS R2A15112

FLASH :EN25Q64-104HIP

External ports of the unit:

Three groups of HDMI input

Two groups of YPBPR input and RCA L/R input

Page 18

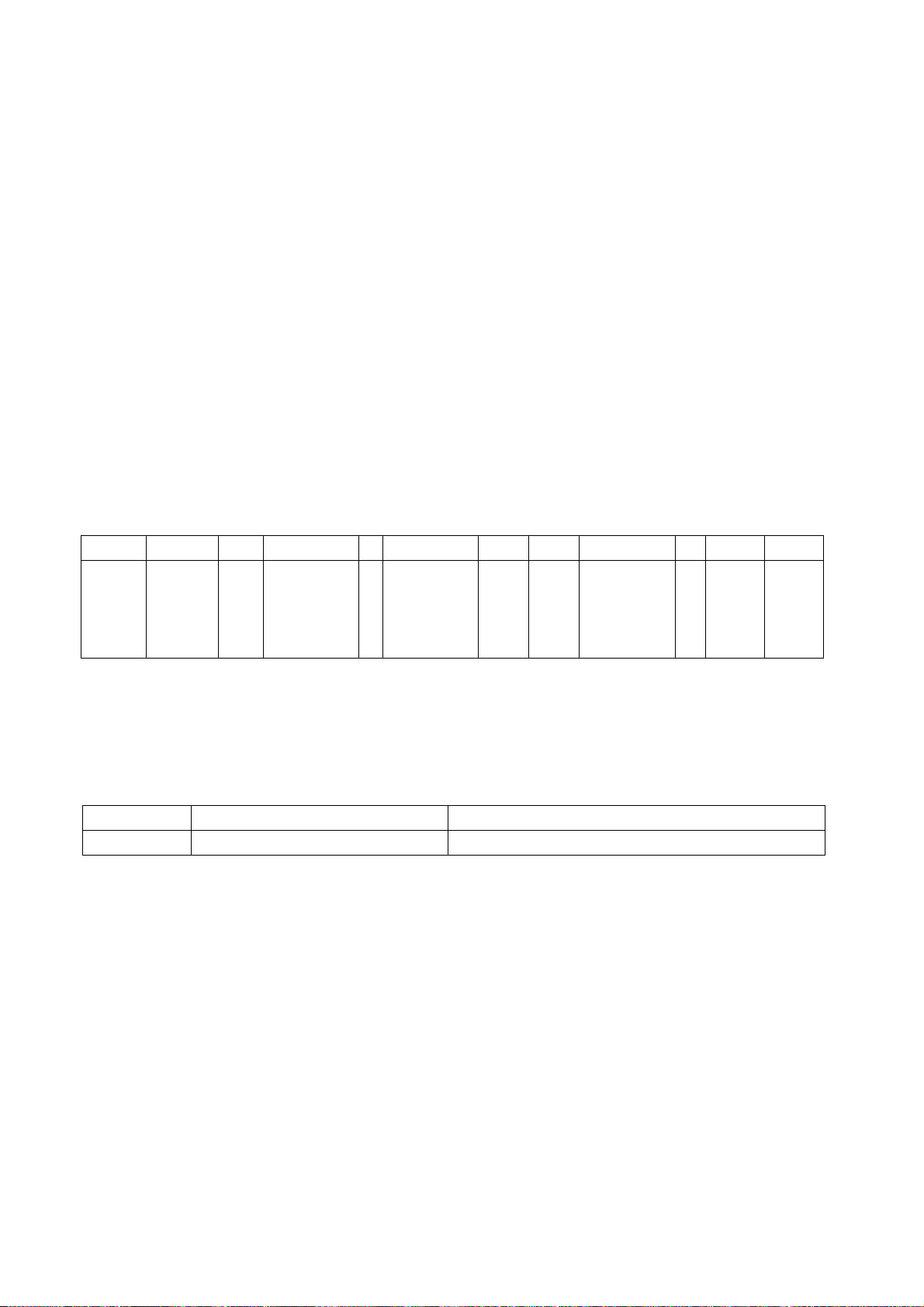

Block diagram

TUNER

HDMI1

HDMI2

HDMI3

VGA

YPbPr

SV

AV

USB

DEMODULATOR

CE6353

CVBS

HDMI1.3 X3

VIDEO SIGNALS

AUDIO SIGNALS

USB2.0

SIF

LVDS

TSTS

PANEL

1080P

HP AMP

BH3547

MSD209

AMP

FLASH

8MB

DDR2 512MbitX2

AV OUT

R2A15112

Page 19

IC block diagram and instruction

1、 Main chip MSD209FG-LF:

GENERAL DESCRIPTION

The MSD209FG is a highly integrated controller IC for LCD/PDP DTV applications with

resolutions up to full-HD (1920 x 1080). It is configured with an integrated triple-ADC/PLL,

a multi-standard TV video and audio decoder, a motion adaptive video de-interlacer, a

scaling engine, the MStarACE-3 color engine, an advanced 2D graphics engine, a

transport processor, a high-definition (HD) MPEG video decoder, a 24-bit DSP for MPEG

audio decoding, a DVI/HDCP/HDMI receiver, and a peripheral control unit providing a

variety of HDTV control functions.

For digital TV application, the MSD209FG comprises an MPEG-2 transport processor with

advanced section filtering capability, an MPEG-2 (MP@HL profile) video decoder, an

MPEG layer I and II digital audio decoder with analog audio outputs that are designed to

support existing and future DVB-T programs while handling conditional access.

Furthermore, it is also possible to decode MPEG-4, JPEG, MP3 formats from external

sources such as USB interfaces.

For analog TV, the MSD209FG includes NTSC/PAL/SECAM multi-standard video

decoder comprising a 3-D motion adaptive comb filter and time-based correction, and a

NICAM/A2 audio decoder to support worldwide television standards. The MSD209FG is

also configured with a VBI processor to decode digital information such as Close Caption /

V-chip / teletext / WSS / CGMS-A / VPS. In addition, the MStar advanced LCD TV

processor enhances video quality, motion adaptive de-interlacer, picture quality

adjustment units, and MStarACE-3 color engine.

By integrating peripherals including two USB 2.0 host controllers, UARTs, IR, SPI, I2C,

and PWM, the MSD209FG fulfills all requirements in advanced DTV sets. To further

reduce system costs, the MSD209FG also integrates intelligent power management

control capability for green-mode requirements and spread-spectrum support for EMI

management.

MSD209FG Features:

Analog RGB Compliant Input Ports

Three analog ports support up to 1080P

Supports PC RGB input up to SXGA@75Hz

Supports HDTV RGB/YPbPr/YCbCr

Supports Composite Sync and SOG (Sync-on-Green) separator

Automatic color calibration

VIF Input Support

Multi-standard analog TV receiver applications

Digital low IF architecture

Page 20

Stepped-gain PGA with 25 dB tuning range and 1 dB tuning resolution

Maximum IF gain of 37 dB

Programmable TOP to accommodate different tuner gain to optimize noise and linearity

performance

DVI/HDCP/HDMI Compliant Input Port

Three DVI/HDCP/HDMI input ports support up to 225MHz @ 1080P 60Hz with 12-bit

deep-color resolution

Single link on-chip DVI 1.0 compliant receiver

High-bandwidth Digital Content Protection (HDCP) 1.1 compliant receiver

High Definition Multimedia Interface (HDMI) 1.3 compliant receiver with CEC (Consumer

Electronics Control) support

Long-cable tolerant robust receiving

High -Performance Scaling Engine

Fully Programmable shrink/zoom capabilities

Nonlinear video scaling supports various

modes including Panorama

Auto -Configuration/Auto-Detection

Auto input signal format and mode detection

Auto-tuning function including phasing, positioning, offset, gain, and jitter detection

Sync Detection for H/V Sync

Video Processing & Conversion

3-D motion adaptive video de-interlacers with edge-oriented adaptive algorithm for

smooth low-angle edges

Automatic 3:2 pull-down & 2:2 pull-down detection and recovery

MStar 3rd Generation Advanced Color Engine (MStarACE-3) automatic picture

enhancement gives:

Brilliant and fresh color

Intensified contrast and details

Vivid skin tone

Sharp edge

Enhanced depth of field perception

Accurate and independent color control

sRGB compliance allows end-user to experience the same colors as viewed on CRTs and

other displays

10-bit internal data processing

Programmable 12-bit RGB gamma CLUT

3-D video noise reduction

MPEG artifact removal including de-blocking and mosquito noise reduction

Frame rate conversion

MFC (Motion Frame Conversion) supports:

Judder-free motion video

Output frame rate 50/60/100/120 f/sec

Up to 60Hz full HD or 120Hz HD panels

Output Interface

Page 21

Supports up to 10-bit dual LVDS full-HD (1920 x 1080) panel interface

Supports 2 data output formats: Thine & TI data mappings

Compatible with TIA/EIA

With 6/8 bits optional dithered output

Spread spectrum output frequency for EMI suppression

CVBS Video Output

Supports two CVBS bypass output ports

2D Graphics Engine

Point draw, line draw, rectangle draw/fill and text draw

BitBlt and stretch BitBlt

Raster Operation (ROP)

Miscellaneous

DRAM controller to support up to 32-bit DDR2 interface

Supports Common Interface for conditional access

SPI bus for external flash

Two ports of USB 2.0 host controller with the flexibility for connecting external storage

devices

375-ball LFBGA package

Operating at 1.26V (core), 1.9V (DDR2), and 3.3V (I/O and analog)

2、 Digital demodulating chip CE6353

The chip comprises 8MHz bandwidth SAW and supports demodulation of 6MHz,

7MHz and 8MHz, 2K/8K carrier and supports both serial and parallel TS stream

output.

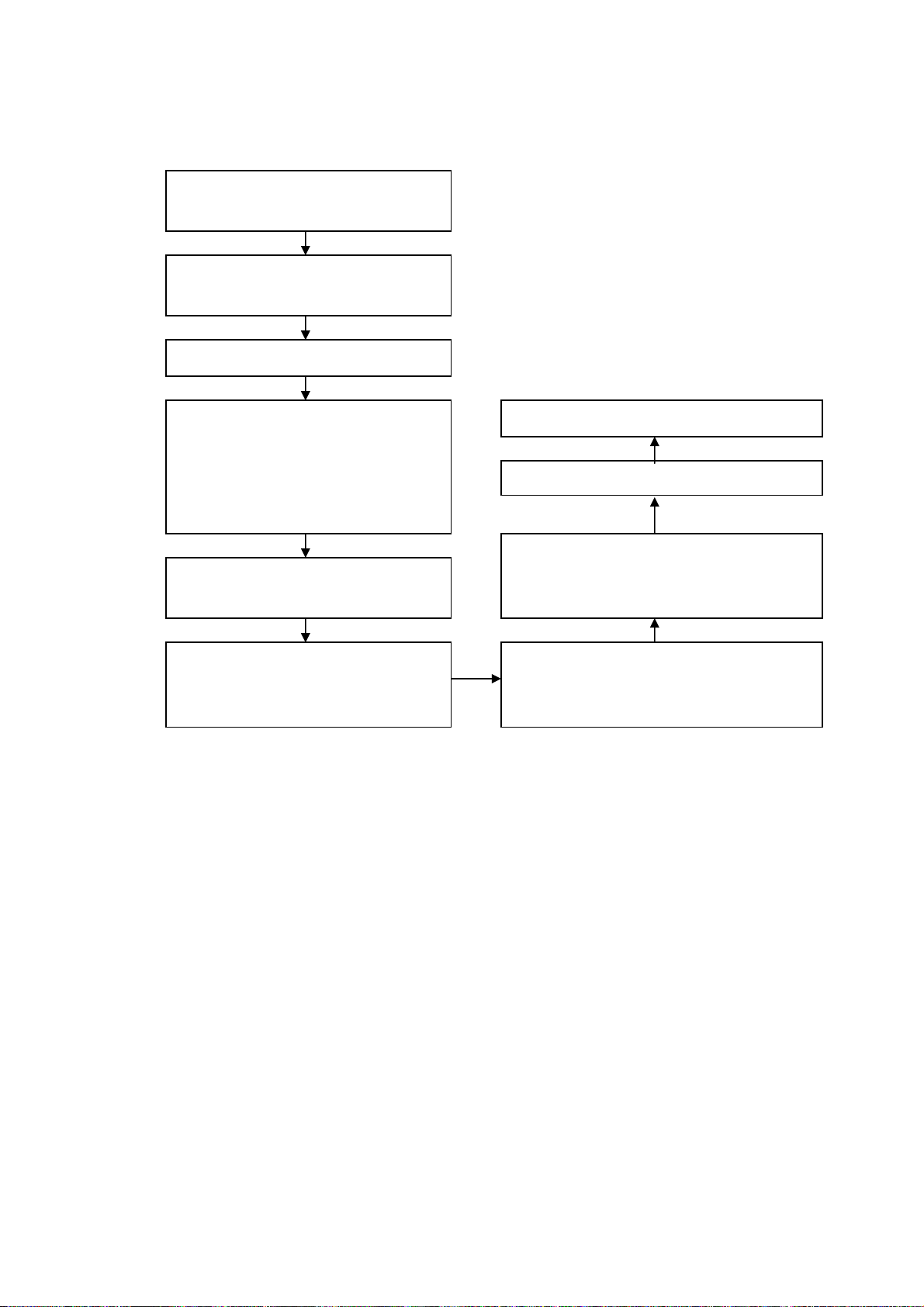

3、 Audio power amplifier RENESAS R2A15112

R2A15112FP is a Digital Power Amplifier IC developed for TV.

R2A15112FP has a maximum power of 15W(typ) × 2ch.

(VD = 24V,THD = 1%, SE) at a 4 Ω load.

It is possible to replace a conventional analog amplifier

with a digital amplifier easily.

●Maximum power out put (No external heat sink)

(note) These apply when the thermal pad is soldered to

the printed-circuit board directly.

Recommended Power Condition

SE operation mode :15Wx2ch(VD=24V,4Ω load,THD+N:1%)

BTL operation mode:30Wx1ch(VD=21V,8Ω load,THD+N:10%)

●Highly efficient, low noise, and low distortion

●Popless

●Built-in protection - Overcurrent, overheat, and undervoltage

●Built-in Mute and Standby function

●The gain can be changed to four settings by two terminals.

Page 22

●Power supply voltage : 11V to 25V

●Speaker Impedance : from 4 to 8Ω

GAIN1 GAIN2

HB1

L

R

IN1

IN2

CBIAS

ROSC

CLOCK

MUTEL

STBYL

SE/BTL

Selector

Oscillator

Under Voltage

Detection

A

A

Control

PROT

Logic

PWM

Gen.

PWM

Gen.

Over Current

Detection

Over Temp.

Detection

GND

10V

5V

VD1

OUT1

VS1

HB2

VD2

OUT2

VS2

DVDD

AVCC

VREF

4、 Tuner:FQD1116ME/IV

The FQD1116 belongs to the new family of highly-featured hybrid frontends, which are

designed to meet a wide range of RF applications. The FQD1116 combines the functions

of a DVB-T digital tuner and a multi-standard TV IF demodulation unit for both positive and

negative modulated TV systems. The unit includes a 7 MHz digital SAW filter with an IF

AGC amplifier for connection to the DVB-T channel decoder. The FQD1116 is intended

for CCIR L/L’ (France), B/G, I and D/K systems and DVB-T broadcast.

The frontends have a built-in digital (I2C) PLL tuning system. A DC-DC converter circuit is

built into the FQD1116 to synthesize the tuning voltage required, thus making the frontend

a true 5V device.

♪

♪

♪

♪

Page 23

WIRING DIAGRAM

BACKLIGHT

POWER BOARD

SPEAKER

PANEL

MAIN BOARD

POWER SWITCH

KEY BOARD

IR BOARD

Page 24

Troubleshooting guide LCD-32XZ10

1.Panel is dark.

Power on main

power supply, check

if the red indicator

light in STANDBY

mode is bright ?

Red

Check if the voltage

of X801-3# (STB)

on main board is

inputted 5V ?

Check if STANDBY

Yes

circuits on power

board are normal ?

No

No

No

Yes

Press key “POWER” of

remote control or the unit

to power on,check what

color of indicator light is?

Blue

Check if the voltage of

X801-13# on main board

is high level ?

Check if backlight circuits

on power board and

backlight board are

normal ?

Yes

Check if circuits about

backlight control on

main board are normal?

Check if the voltage of

X801-1 # on main board

is high level?

Check if power board

assembly is normal ?

Page 25

2.Backlight is normal, but there is no picture

Check if operations

of remote control or

Yes Yes

keys on the unit are

normal ?

No

No Yes

TV

有

No

No

Change another

main board

Enter into factory menu ,

initialize EEPROM, then

power off and power on

again, check if there is

picture ?

Adjust main board again

Check if OSD menu is

displayed normally

after pressing key

“menu”?

Check if there

is no picture of

all channels ?

Yes

Page 26

3.There is picture but no sound.

Yes Yes Yes

No No No

Check 24V power supply

circuits on power board and

power supply circuits from

Yes

XV03 to NV02 on main board

are normal ?

No sound

Check if the voltage

of NV02-4/5/32/33#

is 24V ?

Check if circuits from

NS01-F6/H16# to

NV02-10/27# are

normal?

Check if the voltage

of NV02-10/27# is

high level ?

Check if the

voltage of

NS01-F16/H16#

is low level?

Yes

No

Check if

there is

sound from

earphones?

Touch CV04

and CV05

with probe,

check if there

is sound from

earphones?

No

Check if circuits

about earphone

amplifier are

normal ?

Change

another

NV02

Check if

audio

output

circuits

of main

chip are

normal?

Change

another

NS01

Page 27

ABCDEFGH

CM08

GND-D

100n

GND-D

17

51

18

52

47

48

49

50

53

54

55

56

20

19

46

36

43

16

59

7

61

9

15

44

45

58

30

31

32

2

3

4

5

6

29

28

27

26

25

24

23

22

12

11

8

10

64

65

66

37

38

39

40

41

57

62

63

33

42

67

60

21

13

14

1

34

35

68

CM03

220u

XM01

PCMCIA-0070210PA8C

VCC1

VCC2

VPP1

VPP2

MDI0(A18)

MDI1(A19)

MDI2(A20)

MDI3(A21)

MDI4(A22)

MDI5(A23)

MDI6(A24)

MDI7(A25)

MCLK(A15)

MVAL(A16)

MISTRT(A17)

CD1

VS1

IREQ

WAIT

CE1

REG

OE

WE

IORD

IOWR

RESET

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

MD0(D8)

MD1(D9)

MD2(D10)

MD3(D11)

MD4(D12)

MD5(D13)

MD6(D14)

MD7(D15)

VS2/MCLKO

MOVAL(SPKR)

MOSTRT(STSCHG)

IOIS_16

CE2

CD2

INPACK

A12

A13

A14

GND

GND1

GND2

GND3

CARD_SHDN#

+VCC_CARD

100n

CM04

16V

GND-D

+VCC_CARD

NS01

E

TS_MDO[0]

33

10K

RJ28

10K

RJ29

GND-D

003:D4

TS_MICLK

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MIVAL

TS_MISTRT

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MICLK

TS_MIVAL

TS_MISTRT

003:D2;003:D2;007:C3

SDA

003:D2;003:D2;007:C3

SCL

R108

TS_MICLK

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MIVAL

TS_MISTRT

+3.3V_DE

RJ21

RJ22

GND-D

15p

GND-D

GND-D

RJ26

RJ27

CJ08

CVBS_TUNER

CJ35

10p

15p

CJ10

100n

CJ09

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MICLK

TS_MIVAL

TS_MISTRT

GND-D

100

100

+3.3V_DE

1

+5V_TUNER2

2.2u

L101

STBH2012-501PT

2

STBH2012-501PT

STBH2012-501PT

GND-A

L102

L103

GND-D

MOPLL I2C

ADDRESS

SELECTION

3

330nH

0

0

CJ01

100n

56p

CJ34

LJ05

39nH

GND-A

CJ02

100n

22n

CJ03

GND-A

GND-A

+3.3V_DE

4.7K

4.7K

RJ03

RJ01

100

100

RJ02

RJ32

RJ33

SDA

220

TV_FAT_IFP

TV_FAT_IFN

RJ30

220

RJ31

TV_IF_AGC

4

TUNER_SCL

TUNER_SDA

TUNER_SCL

TUNER_SDA

TUNER1

RF2Ant_Pwr

VT

RF_AGC6GND67VP(TUN)

NC4

GND3

1

8

5

4

3

100n

C214

C215

R101

10K

GND-A

R102

10K

GND-A

AS ADDRESS

0-0.5V C0/C1

1-1.5V/OPEN C2/C3

2-3V C4/C5

4.5-5V C6/C7

+5V_TUNER2

C102

100u

10V

GND-A

22p

CJ04

22p

CJ05

+3.3V_DE

1K

RJ07

RJ05

10K

RJ06

1K

+1.8V_PDE

RJ04

003:D2;003:D2;007:C3

SCL

003:D2;003:D2;007:C3

GND9

9

10

L104

22uH

NC10

SCL

As

12

13

11

+5V

+1.8V_ADE+5V

GND-A

GND-D

FQD1116ME/IV

SDA

IF_AGC16DIF117DIF218Wout

REF

15

14

30

VIN

31

VIN

42

AGC1

41

AGC2/GPP2

28

AVdd

29

AGnd

32

AGnd

33

Vdd33

34

RFLEV

21

PLLVdd

26

PLL1TEST

22

PLLGnd

43

GPP3

35

CLK2/GPP0

36

DATA2/GPP1

+5V_IF202ndIF/Low_DIF1

2ndIF/Low_DIF2

19

21

22

L107

L108

+3.3V_DE

5

+3.3V_DE

LJ01 LJ02

+1.8V_DE +1.8V_CORE+1.8V_DE +1.8V_PDE

AS_IF24CVBS

NC

23

GND-A

2.2u

C216

GND-A

SGMI2012-2R2KT

SGMI2012-2R2KT

+1.8V_CORE

2

45

13

54

Vdd

Vdd

Vdd

Vdd

XTI24XTO

23

27

RJ08

2.2M

GND-D

GJ01

20.48MHz

33p

33p

CJ06

GND-D

IF PART I2C

ADDRESS

SELECTION

AS_IF ADDRESS

0 86/87

5V 84/85

100n

C217

R279

330

R280

330

7

19

37

CVdd

CVdd

CVdd

NJ01

CE6353

OSCMODE

0

RJ09

CJ07

GND-A

GND-A

39

CVdd

R103

10K

R104

10K

10p

C219

R107 0

C101

10n

59

64

CVdd

Vss

1

3

R105 330

R106 330

GND-D

CVdd

Vss

Vss

Vss

8

14

44

SMTEST

20

GND-D

Vss

+3.3V_DE

15

12

SADD4

Vss

Vss

40

38

25

+5V_TUNER1

GND-A

17

SADD316SADD2

SADD118SADD0

Vss

Vss

Vss

46

55

60

C104

100u

10V

TV_SIFP

TV_SIFM

TUNER_SCL

TUNER_SDA

TV_IF_AGC

TV_FAT_IFP

TV_FAT_IFN

RJ10

10K

MOSTRT

STATUS

Vss

+5V

L106

22uH

002:D3;003:C4

002:D3;003:C4

RJ11

10K

63

MICLK

61

MOCLK

49

MDO0

50

MDO1

51

MDO2

52

MDO3

53

MDO4

56

MDO5

57

MDO6

58

MDO7

48

MOVAL

47

62

BKERR

11

10

SLEEP

6

IRQ

5

DATA1

4

CLK1

9

RESET

GND-D

RJ24

RJ25 33

4.7K

LJ03

RJ12

4.7K

8.2K

75

GND-A

0

GND-D

RJ15

33

33

33

RJ16

RJ17

33

RJ20

0

RJ23

+1.8V_ADE+1.8V_DE

RST_6353

002:D4

RM44

TS_MDO[1]

33

RM45

TS_MDO[2]

33

RM46

TS_MDO[3]

33

RM47

TS_MDO[4]

33

RM48

TS_MDO[5]

33

RM49

TS_MDO[6]

33

RM50

TS_MDO[7]

33

RM51

TS_MOCLK

33

RM52

TS_MOVAL

33

RM53

TS_MOSTRT

33

RM54

MSD209FG

PCMCIA/CI

TS1_CLK/GPIO43

TS1_SYNC/GPIO42

TS1

TS1_VLD/GPIO41

TS1_DO/GPIO40

TS0_CLK/GPIO39

TS0_SYNC/GPIO38

TS0_VLD/GPIO37

TS0_D0/GPIO29

TS0_D1/GPIO30

TS0

TS0_D2/GPIO31

TS0_D3/GPIO32

TS0_D4/GPIO33

TS0_D5/GPIO34

TS0_D6/GPIO35

TS0_D7/GPIO36

PCM_IORD_N/CI_RD/GPIO87

PCM_IOWR_N/CI_WR/GPIO88

PCM_OE_N/GPIO89

PCM_WE_N/GPIO90

PCM_REG_N/CI_CLK/GPIO91

PCM_CE_N/CI_CS/GPIO92

PCM_IRQA_N/CI_INT/GPIO93

PCM_WAIT_N/CI_WACK/GPIO94

PCM_RESET/GPIO95

PCM_CD_N/GPIO96

PCM_A0/CI_A0/GPIO63

PCM_A1/CI_A1/GPIO64

PCM_A2/CI_A2/GPIO65

PCM_A3/CI_A3/GPIO66

PCM_A4/CI_A4/GPIO67

PCM_A5/CI_A5/GPIO68

PCM_A6/CI_A6/GPIO69

PCM_A7/CI_A7/GPIO70

PCM_A8/CI_A8/GPIO71

PCM_A9/CI_A9/GPIO72

PCM_A10/CI_A10/GPIO73

PCM_A11/CI_A11/GPIO74

PCM_A12/CI_A12/GPIO75

PCM_A13/CI_A13/GPIO76

PCM_A14/CI_A14/GPIO77

PCM_D0/CI_D0/GPIO79

PCM_D1/CI_D1/GPIO80

PCM_D2/CI_D2/GPIO81

PCM_D3/CI_D3/GPIO82

PCM_D4/CI_D4/GPIO83

PCM_D5/CI_D5/GPIO84

PCM_D6/CI_D6/GPIO85

PCM_D7/CI_D7/GPIO86

N18

P18

L17

M17

Y7

W5

V6

V4

U5

U6

R7

R8

T7

T8

V5

U18

T18

V18

V17

U17

T17

R17

R18

P17

N17

V13

U13

T13

R13

V12

U12

T12

R12

U11

V9

T11

T10

U10

V8

V7

R11

R10

P9

R9

T9

U9

U8

U7

CARD_5VEN

CARD_3.3VEN

CI_VS1#

CARD_OC

TS_PCLK

TS_PSTRT

TS_PVAL

TS_PD[0]

TS_PD[1]

TS_PD[2]

TS_PD[3]

TS_PD[4]

TS_PD[5]

TS_PD[6]

TS_PD[7]

PCM_A[0]

PCM_A[1]

PCM_A[2]

PCM_A[3]

PCM_A[4]

PCM_A[5]

PCM_A[6]

PCM_A[7]

PCM_A[8]

PCM_A[9]

PCM_A[10]

PCM_A[11]

PCM_A[12]

PCM_A[13]

PCM_A[14]

PCM_D[0]

PCM_D[1]

PCM_D[2]

PCM_D[3]

PCM_D[4]

PCM_D[5]

PCM_D[6]

PCM_D[7]

CJ36

10p

GND-D

TS_MICLK

TS_MISTRT

TS_MIVAL

TS_MDI[0]

RM01

RM05

RM04

33

RM02

33

RM03

CI_ADDR[0]

CI_ADDR[1]

CI_ADDR[2]

CI_ADDR[3]

CI_ADDR[4]

CI_ADDR[5]

CI_ADDR[6]

CI_ADDR[7]

CI_ADDR[8]

CI_ADDR[9]

CI_ADDR[10]

CI_ADDR[11]

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[14]

CI_DATA[0]

CI_DATA[1]

CI_DATA[2]

CI_DATA[3]

CI_DATA[4]

CI_DATA[5]

CI_DATA[6]

CI_DATA[7]

4.7K

RM06

+3.3AVDD

4.7K

RM08

TS_MOCLK

TS_MOSTRT

TS_MOVAL

TS_MDO[0]

TS_MDO[1]

TS_MDO[2]

TS_MDO[3]

TS_MDO[4]

TS_MDO[5]

TS_MDO[6]

TS_MDO[7]

CI_IORD#

CI_IOWR#

CI_OE#

CI_WE#

PC_REG#

CI_CE#

CI_IREQ#

CI_WAIT#

PC_RST

CI_CD#

+3.3AVDD

CM01

100n

GND-D

4.7K

RM07

RM10

4.7K

RM09

4.7K

STBH2012-221PT

+5V

STBH2012-221PT

GND-D

LM01

LM02

+3.3AVDD

1u

CM02

+VCC_CARD

CI_CE#

GND-D

33

33

33

100

RM25

RM17

100

RM18

100

RM19

100

RM20100

RM13

0

RM24

33

RM23

33

RM16

33

RM15

33

RM22

33

RM21

33

+3.3AVDD

RM12

100

+3.3AVDD

RM11

100

+VCC_CARD

10K

10K

RM27

RM26

CI_VS1#

+3.3AVDD

RM30 10K

RM31 10K

RM32 10K

RM33 1K

RM34 1K

RM35 10K

RM36 10K

RM37 10K

+VCC_CARD

CI_DECT

5

Vcc

4

Y

NM01

SN74LVC1G32DCKR

TPS2211AIDBR

1

VCCD0

2

VCCD1

3

3.3V_3

4

3.3V_4

5

5V_5

6

5V_6

7

GND

8

OC

10K

10K

RM29

A

B

GND

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MICLK

TS_MIVAL

TS_MISTRT

10K

RM28

10K

0

0

RM14

1

2

3

NM02

AVCC_13

AVCC_12

AVCC_11

RM38

CI_WE#

CI_IOWR#

CI_IORD#

CI_OE#

CI_VS1#

PC_C_DETECT1#

PC_C_DETECT2#

INPACK

CI_IREQ#

CI_WAIT#

PC_RST

RM39

RM40

RM41

PC_C_DETECT2#

PC_C_DETECT1#

GND-D

SHDN

VPPD0

VPPD1

AVPP

12V

IOIS

0

PC_REG#

CI_CE1#

CI_CE2#

16

15

14

13

12

11

10

9

CI_CD#

+3.3AVDD

CM05

100n

TS_MDI[0]

TS_MDI[1]

TS_MDI[2]

TS_MDI[3]

TS_MDI[4]

TS_MDI[5]

TS_MDI[6]

TS_MDI[7]

TS_MICLK

TS_MIVAL

TS_MISTRT

PC_C_DETECT1#

CI_VS1#

CI_IREQ#

CI_WAIT#

CI_CE1#

PC_REG#

CI_OE#

CI_WE#

CI_IORD#

CI_IOWR#

PC_RST

CI_DATA[0]

CI_DATA[1]

CI_DATA[2]

CI_DATA[3]

CI_DATA[4]

CI_DATA[5]

CI_DATA[6]

CI_DATA[7]

CI_ADDR[0]

CI_ADDR[1]

CI_ADDR[2]

CI_ADDR[3]

CI_ADDR[4]

CI_ADDR[5]

CI_ADDR[6]

CI_ADDR[7]

CI_ADDR[8]

CI_ADDR[9]

CI_ADDR[10]

CI_ADDR[11]

TS_MDO[0]

TS_MDO[1]

TS_MDO[2]

TS_MDO[3]

TS_MDO[4]

TS_MDO[5]

TS_MDO[6]

TS_MDO[7]

TS_MOCLK

TS_MOVAL

TS_MOSTRT

CI_CE2#

PC_C_DETECT2#

INPACK

CI_ADDR[12]

CI_ADDR[13]

CI_ADDR[14]

4.7K

RM43

RM42

100

CM07

CM06

100n

IOIS

100n

100n

100n

4.7u

CJ18

CJ16

GND-D

100n

CJ20

100n

CJ22

100n

CJ24

100n

CJ26

100n

CJ27

GND-D

2.2u

CJ11

100n

CJ14

GND-D

4.7u

CJ12

100n

CJ15

100n

CJ17

100n

CJ19

100n

CJ21

100n

CJ23

100n

CJ25

6

GND-D

CJ13

DRAWN BY

APPROVED BY

TITLE: DWG NO.

9232KE5201DL

TUNER+IF+PCMCIA

REV.

Sheet to

XOCECO

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

1.0

1

10

Page 28

ABCDEFGH

100n

GND-D

1

2

3

4

5

6

7

8

9

10

11

12

C113

1n

R273

75

AV_R_IN

003:C4

External_CVBS

1n

C115

100K

GND-D

C164

100K

R203

GND-D

AV1

SC2_VOUT

AV_OUTL

AV_OUTR

456

123

GND-D

YWR

X109

RCA-302A-01

AV_OUTL

100n

GND-D

C228

AV_OUTL

N110

PESD5V0L5UY

GND-D

Z104

10MHz

R139

Z115

10MHz

9232KE5201DL

REV.

2

Sheet to

XOCECO

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

TV_OUTL

AV13-06-526

X103

1.0

Y1R2

W1

R1

Y2

W2

10

X105

JY-3541L-01-030

L

1

2

3

W1 R1 W2 R2

R

G

X104

HC1038-15F-3.08

5

1015

4

9

14

3

8

13

2

7

12

1

6

11

GND-D VGA_R_IN

1

L1

3

R1

4

2

L2

6

R2

5

4

5

6

RCA-410A-10

X111

HJR-613/PB-1

G1

B1

R1

G2

B2

R2

X112

GND-D

GND-D

VCC-VGA

GND-D

N105

PESD5V0L5UY

123

GND-D

123

GND-D

123

456

100n

R113

10K

R114

10K

456

PESD5V0L5UY

100n

C106

R274 0

456

N101

PESD5V0L5UY

C118

G

B

@pinCo

R

@pinCo

AV3-14WD

X102

N103

R119

75

@pinCo

12345

GND-D

12K

Z116

470MHz

R122

100n

C114

47p

R121

R275 0

R276 0

75

GND-D

R117

10K

R118

10K

R296

10K

R297

10K

N109

PESD5V0L4UG

C221

R126

22K

Z117

470MHz

470MHz

R277 0

R278 0

R127

75

12K

R137

R138

22K

Z101

Z102

470MHz

Z103

470MHz

GND-D

GND-D

GND-D

GND-D

12345

GND-D

VGA_LIN

VGA_RIN

C119

47p

GND-D

12K

R124

12K

R125

12K

R298

12K

R299

100n

C105

R293 0

100p

C222

GND-D

R294 0

100p

C223

GND-D

R295 0

100p

C224

GND-D

VGA_B_IN

003:C3

VGA_G_IN

003:C3

003:C3

YUV_RIN

C116

47p

YUV_LIN

C117

47p

SC1_RIN

C225

47p

SC1_LIN

C226

47p

N102

PESD5V0L4UG

R290

75

R291

75

R292

75

R129 0

R128

100p

C110

GND-D

R130 0

R131

100p

C111

GND-D

R133 0

R132

100p

C112

GND-D

R140 33

R141 33

75

75

75

SCART1_G

SCART1_B

SCART1_R

VGA_VSYNC

003:C3

VGA_HSYNC

003:C3

N106

24LC21A/SN

1

NC1

2

NC2

NC3

VSS

VCLK

NS01

MSD209FG

3

4

AUDIO

LINE_OUT_0R(DACO_R)

LINE_OUT_0L(DACO_L)

LINE_OUT_1R(DACO_S)

I2S_OUT_MCK/GPIO50

I2S_OUT_BCK/GPIO51

I2S_OUT_MUTE/LHSYNC2/GPIO13

Y_INPUT

003:C3

Pb_INPUT

003:C3

Pr_INPUT

003:C3

SC2_ROUT

VCC-VGA

+5V

D101

MMBD1204

8

VCC

100n

7

6

SCL

5

SDA

GND-D

B

SIF_INP

SIF_INM

LINE_IN_0L

LINE_IN_0R

LINE_IN_1L

LINE_IN_1R

LINE_IN_2L

LINE_IN_2R

LINE_IN_3L

LINE_IN_3R

LINE_IN_4L

LINE_IN_4R

LINE_IN_5L

LINE_IN_5R

LINE_OUT_1L

LINE_OUT_2R

LINE_OUT_2L

SPDIF_IN/GPIO47

SPDIF_OUT/GPIO48

I2S_IN_BCK/GPIO45

I2S_IN_WS/GPIO44

I2S_IN_SD/GPIO46

I2S_OUT_WS/GPIO49

I2S_OUT_SD/GPIO52

AU_COM(VIM0)

AUVRM

AUVRP

AUVAG

+12V

BG2012D151T

R142

R145

R149

4.7K

4.7K

C120

R146

0

VCLK: 0=READ ONLY

Y2

W2

P5

P6

R3

R4

Y3

Y4

R5

R6

T3

T4

T5

T6

W4

Y6

U4

V3

W3

Y5

F15

E14

G16

H16

G15

E16

F16

E12

E11

E10

V2

N5

N4

U3

L110

47K

R143

10K

R144

8.2K

R152

R151

R147

4.7K

GND-D

R150

4.7K

1u

L111

GND-D

V102

MMBT3904

47

R15433

R15533

C127 2.2u

R159

100

100

13K

R156

GND-D

R15333

C124

C125

4.7u

SGMI2012M1R0KT

GND-D

16V

100n

C123

C121

4.7u

C122

2.2u

R148

R158

C1312.2u

C1322.2u

C1332.2u

C1342.2u

C1352.2u

C129

2.2n

100n

10u

+3.3VDD

1n

GND-D

R160

33

BC847AW

BC847AW

C128

C130

GND-D

C126

V103

V104

C137 2.2u

R163 100

100

100

13K

R161

100n

R269

10K

100K

R157

R162

100n

100n

GND-D

C136

+3.3VDD

RXD_UPDATE

007:F2

R164

470

R165

470

BC847AW

C144

C145

C1392.2u

C1402.2u

C1412.2u

C1422.2u

C1432.2u

100

C138

13K

2.2n

R166

RST_6353

MUTE_AMP

ISP_EN

STANDBY_AMP

SPI_CZ2

MUTE_AMP

Z105

10MHz

R167

10K

R168

200

R169

33

V105

TV_SIFP

001:C2;003:C4

TV_SIFM

001:C2;003:C4

C146

2.2n

GND-D

001:D5

008:C3

008:C1

008:C3

13K

R170

GND-D

AV_OUTR

ISP_EN

TXD_UPDATE

007:F2

AV_LIN

AV_RIN

SC2_LIN

SC2_RIN

SC1_LIN

SC1_RIN

VGA_LIN

VGA_RIN

YUV_LIN

YUV_RIN

AV2_LIN

AV2_RIN

C147

2.2n

R171

SC1_ROUT

13K

C148

2.2n

GND-D

SPDIF_OUT

+12V

C

G

13K

R173

GND-D

HJK-3.5-401

X101

Y

G

L112

BG2012D151T

R174

10K

C150

2.2n

L

R

G

S

G

2.2u

2.2u

GND-D

R176

R177

47K

8.2K

2.2u

2.2u

C152

C151

R179

GND-D

C154

C153

232_TXD

007:D4

232_RXD

007:D3

456

N104

PESD5V0L5UY

GND-D

+5V

16V

4.7K

GND-D

V106

MMBT3904

47

R180

PRIM_AUD_OUT_R

PRIM_AUD_OUT_L

SC1_ROUT

SC1_LOUT

SC2_ROUT

SC2_LOUT

123

AV_OUTR

R172

10K

100n

C149

100n

C157

C155

4.7u

C156

2.2u

R123

75

GND-D

100n

C108

R175 200

1n

C158

GND-D

008:C5

008:C4

R134 0

R136 0

R135

75

47

R110

GND-D

100K

R181

AV_R_IN

75

R178

Z106

10MHz

AV_R_IN

AV_LIN

AV_RIN

SC1_LIN

SC1_RIN

SC2_FS

007:B3

SC2_FS

SC2_LIN

SC2_RIN

AV2_LIN

AV2_RIN

External_YIN

003:C4

External_CIN

003:C4

RCA-103A-OR

X106

003:C4

External_CVBS

12K

12K

R187

GND-D

R263

2.2K

OR

TV_OUTR

C159

47p

R197

10K

R198

10K

R192

GND-D

12K

12K

R188

GND-D

SC1_LOUT

External_CVBS

C160

12K

47p

R182

R183

GND-D

Z111

10MHz

Z112

10MHz

GND-D

R265

8.2K

R199

10K

R200

10K

AV_OUTL

12K

R193

AV_OUTR

12K

SC2_LOUT

+12V

DRAWN BY

APPROVED BY

R184

10K

R185

10K

SCRTR2_FS

GND-D

AV2_VIN

12K

R189

+12V

BG2012D151T

BG2012D151T

R186

10K

Z109

10MHz

GND-D

R194

R109

10K

L113

47K

L109

10MHz

GND-D

R259

R201

10K

R202

10K

Z107

SC1_IN_L

SC1_IN_R

SC2_Y/CVBS

Z113

10MHz

47K

R261

47K

R111

R112

8.2K

47K

R190

R191

8.2K

Z108

10MHz

X108

TJC10S-12A

SC2_C

SC2_VOUT

SCART2

GND-D

75

R204

GND-D

Z110

10MHz

Z114

10MHz

GND-DGND-D

16V

C107

4.7u

R115

4.7K

GND-D

C109

2.2u

V101

MMBT3904

47

R116

GND-D

16V

100n

C163

C161

4.7u

R195

4.7K

GND-D

C162

2.2u

V107

MMBT3904

47

R196

GND-D

TITLE: DWG NO.

AUDIO IN/OUT

Page 29

ABCDEFGH

+3.3VDD

1%

GND-D

CEC_PM

820

10

10

C166

R205

100n

R272

100n

RA23

R206

75

0

390

1%

25V

C165

GND-D

+3.3VDD

47K

RA24

C1691n

C17047n

C17147n

C17247n

C1731n

C17447n

C17547n

C17647n

100n

100n

C17747n

C17847n

C17947n

C18047n

C18147n

C18247n

C18347n

C18447n

C18547n

C18647n

R270

R271

10u

100p

C218

C167

GND-D

C168

470

470

10u

16V

AVDD_DM

C1881n

C18947n

C19047n

C19147n

C19247n

C19347n

C19447n

10

10

10

10

10

10

C195

C196

C197100n

10

10

10

10

10

10

10

10

10

10

CEC

006:D4

HDMI_CEC

006:D4

HDMI-2_RXC+

HDMI-2_RXC-

HDMI-2_RX0+

HDMI-2_RX0-

HDMI-2_RX1+

HDMI-2_RX1HDMI-2_RX2+

HDMI-2_RX2SDA_HDMI-2

SCL_HDMI-2

HOTPLUG_HDMI-2_OUT

HDMI-1_RXC+

HDMI-1_RXCHDMI-1_RX0+

HDMI-1_RX0HDMI-1_RX1+

HDMI-1_RX1HDMI-1_RX2+

HDMI-1_RX2-

SDA_HDMI-1

SCL_HDMI-1

HOTPLUG_HDMI-1_OUT

HDMI-3_RXC+

HDMI-3_RXCHDMI-3_RX0+

HDMI-3_RX0HDMI-3_RX1+

HDMI-3_RX1HDMI-3_RX2+

HDMI-3_RX2SDA_HDMI-3

SCL_HDMI-3

HOTPLUG_HDMI-3_OUT

R233

470

47

R223

47

R224

R225

47

47

R226

47

R227

R228

47

GND-D

R229

R207

R208

R209

R230

R210

R211

R212

GND-D

R213

R214

R215

R216

R217

R218

R219

R220

R221

GND-D

R222

10u

25V

C187

C198

100n

470

39K

R231

R234

V108

MMBT3904

R236

220

75

15K

R232

R235

GND-D

+5V

MMBT3906LT1

V109

TO: PAGE6

External_YIN

External_CIN

AV2_VIN

External_CVBS

002:G1

TV_CVBS

TV_CVBS#

SCART1_B

SCART1_G

SCART1_R

51

R245

C199

2.2u

MMBT3906LT1

V110

SCL

SDA

Pb_INPUT

002:B3

Y_INPUT

002:B3

Pr_INPUT

002:B3

VGA_HSYNC

002:C1

VGA_VSYNC

002:C1

VGA_B_IN 002:B2

VGA_G_IN

002:B2

VGA_R_IN

002:B2

SCART1_B

SCART1_G

SCART1_R

SC2_Y/CVBS

002:B4

002:B5

SCART1_CVBS

SCART1_B

SCART1_G

SCART1_R

C200

100n

GND-D

C227

R237

470u

75

SC2_VOUT

16V

EEP_W_EN

SC1_FB

SC2_C

007:B2

SCL

SDA

NS01

A

1

2

3

4

MSD209FG

HDMI

RGB

S-Video

CVBS_IN

CVBS0

CVBS_OUT

CEC/UART_RX1

Share VCOM0

VIF

PM_CEC

RXCP1

RXCN1

RX0P1

RX0N1

RX1P1

RX1N1

RX2P1

RX2N1

DDCDB_DA

DDCDB_CK

HOTPLUGB

RXCP0

RXCN0

RX0P0

RX0N0

RX1P0

RX1N0

RX2P0

RX2N0

DDCDA_DA

DDCDA_CK

HOTPLUGA

RXCP2

RXCN2

RX0P2

RX0N2

RX1P2

RX1N2

RX2P2

RX2N2

DDCDC_DA

DDCDC_CK

HOTPLUGC

REXT

HSYNC0

VSYNC0

SOGIN0

BIN0P

BIN0M

GIN0P

GIN0M

RIN0P

RIN0M

HSYNC1

VSYNC1

SOGIN1

BIN1P

GIN1P

RIN1P

VSYNC2

SOGIN2

BIN2P

GIN2P

RIN2P

VCLAMP

REFP

REFM

Y0(CVBS4P)

C0(CVBS6P)

Y1(CVBS5P)

C1(CVBS7P)

CVBS1P

CVBS2P

CVBS3P

VCOM1

CVBS0P

VCOM0

VIFP

VIFM

VR12

VR27

TAGC

CVBS_OUT1

CVBS_OUT2

DACSVM

DREXT

W7

E3

C1

C2

D1

D2

E1

E2

F1

F2

E4

E6

E5

G1

G2

H1

H2

J1

J2

K1

K2

F6

G3

F4

Y8

W8

Y9

W9

Y10

W10

Y11

W11

T14

R14

N15

F5

L7

M7

J5

N2

N1

M2

M1

L2

L1

G7

G8

H4

H3

H5

H6

K6

L5

L3

L4

L6

G4

G5

G6

J3

J4

K3

K4

M4

P1

M3

R1

P2

R2

Y1

W1

N3

M6

M5

T1

K5

N16

M16

5

R242

100

R243

100

SC2_Y/CVBS

SC2_C

CVBS_TUNER

001:D2

SC2_VOUT

R238

33

+3.3VDD

C202

R244

100

100n

GND-D

10K

100

R249

GND-D

GND1

GND-D GND-D

C201

100n

GND-D

R240

R241

8

Vcc

7

WP

6

SCL

5

SDA

353.24040-10

0

WP: H=READ ONLY

R281

SC2_VOUT

GND21GND31GND41GND5

1

24C512

8

Vcc

7

WP

6

SCL

5

SDA

353.24512-00

24C04

N108

GND

SC2_Y/CVBS

SC2_C

+5V

L114

BG2012D151T

C204

220u

0

10V

GND-A GND-A

N107

1

AO

2

A1

3

A2

4

R247

4.7K

V112

BC847AW

R248

4.7K

GND-D

GND6

1

GND-SGND-S

GND-D

R251

220

1

AO

A1

A2

GND

+3.3VDD

10K

GND-D

R255

1

2

3

4

100n

GND-D

+3.3VDD

C206

C208

220u

10V

SPI_CZ2

SPI_CK

SPI_DI

SPI_DO

SPI_CZ1

10K

R257

R253

R252

0

0

R254

R256

75

0

GND-D

TV_OUT

TV_CVBS

TV_CVBS#

SC1_IN_L

SC1_IN_R

SCART1_B

SCART1_G

SCART1_R

SC1_FB

TV_OUT

SCART1_CVBS

R258

33

TV_OUTL

TV_OUTR

GND-D

SC1_FS

+3.3VDD +3.3VDD

100n

GND-D

+3.3VDD

R284

47K

GND-D

R282

R283

47K

47K

007:B3

SC1_FS

R262

0

R260

75

R28675R28775R288

GND-D

75

R289

GND-D

1

2

C209

3

4

5

6

7

8

EN25B32-100HIP

8

VCC

7

HOLD#

6

SCLK

5

SI

R285

47K

75

N111

EN25B64

HOLD

Vcc

SI/SIO0

NC3

NC4

NC5

NC6

S

SO/SIO19W/ACC

N115

CS#

WP#

GND

R266

8.2K

SCART1_FS

FB_SC1

2.2K

R264

PESD5V0L5UY

N114

SCLK

NC14

NC13

NC12

NC11

GND

SO

GND-D

1

2

3

4

+3.3VDD

100K

R267

R268

33K

100n

C210

6

5

6

5

FLASH_WP#

1

HOLD

2

Vcc

3

NC3

4

NC4

5

NC5

6

NC6

7

S

8

SO/SIO19W/ACC

N112

EN25B64

SI/SIO0

SCLK

NC14

NC13

NC12

NC11

1FUN_SEL

GND-D

GND

1R_OUT

1R_IN

1L_OUT

GND-D

GND-D

1L_IN

1B_IN

GND-D

@pinCo

1G_IN

@pinCo

GND-D

GND-D

1RED_IN

1RGB_SW

GND-D

GND-D

1TV_OUT

1TV_IN

GND-D

100n

C213

GND-D

16

15

22p

C211

14

GND-D GND-D

13

12

11

10

GND-D GND-D

GND-D

C220

100n

GND-D

PESD5V0L5UY

N113

1

2

34

1

2

34

GND-D

16

15

14

13

12

11

10

HJ-2105F

X110

1

3

5

7

9

11

13

15

17

19

21

22p

C212

2

4

6

8

10

12

14

16

18

20

SCART1 (CVBS+RGB)IN/TVOUT

TITLE: DWG NO.

9232KE5201DL

VIDEO IN/OUT

6

DRAWN BY

APPROVED BY

REV.

1.0

3

Sheet to

XOCECO

XIAMEN OVERSEAS CHINESE

ELECTRONIC CO., LTD.

10

Page 30

ABCDEFGH

NS01

C

1

2

3

4

5

MSD209FG

DDR/SDR

A-CKO/DDR2_MCLKZ

A-CKON/DDR2_MCLK

A-MVREF/DDR2_A-MVREF

SDR_CKE/DDR2_A-ODT

SDR_AD9/DDR2_A-CKE

SDR_AD8/DDR2_A-WEZ

SDR_AD11/DDR2_A-BA0

SDR_AD10/DDR2_A-BA1

DDR2_A-BA2

SDR_AD0/DDR2_A-RASZ

SDR_AD1/DDR2_A-CASZ

SDR_AD2/DDR2_ADR0

SDR_AD12/DDR2_A-ADR1

SDR_AD3/DDR2_A-ADR2

A-ODT/DDR2_A-ADR3

SDR_AD4/DDR2_A-ADR4

SDR_BA0/DDR2_A-ADR5

SDR_AD5/DDR2_A-ADR6

SDR_CASN/DDR2_A-ADR7

SDR_AD6/DDR2_A-ADR8

SDR_WEN/DDR2_A-ADR9

SDR_BA1/DDR2_A-AD10

SDR_AD7/DDR2_A-ADR11

SDR_RASN/DDR2_A-ADR12

A-UDQSN/DDR2_A-LDQS0M

A-UDQSP/DDR2_A-LDQS0P

A-DQM0/DDR2_A-DQM0

SDR_DQ2/DDR2_A-DQ0

SDR_DQ13/DDR2_A-DQ1

SDR_DQ1/DDR2_A-DQ2

SDR_DQ14/DDR2_A-DQ3

SDR_DQ15/DDR2_A-DQ4

SDR_DQ0/DDR2_A-DQ5

SDR_DQ12/DDR_A-DQ6

SDR_DQ3/DDR2_A-DQ7

A-LDQSM/DDR2_A-UDQS1M

A-LDQSP/DDR2_A-UDQS1P

A_DQM1/DDR2_A-DQM1

SDR_DQ6/DDR2_A-DQ8

SDR_DQ9/DDR2_A-DQ9

SDR_DQ5/DDR2_A-DQ10

SDR_DQ11/DDR2_A-DQ11

SDR_DQ10/DDR2_A-DQ12

SDR_DQ4/DDR2_A-DQ13

SDR_DQ8/DDR2_A-DQ15

SDR_DQ7/DDR2_A-DQ15

B-CK/DDR2_B-MCLKZ

B-CKN/DDR2_B-MCLK

B-CKE/DDR2_B-ODT

B-A8/DDR2_B-CKE

B-A7/DDR2_B-WEZ

B-A10/DDR2_B-BA0

B-A9/DDR2_B-BA1

DDR2_B-BA2

B-ODT/DDR2_B-RASZ

B-A0/DDR2_B-CASZ

B-A1/DDR2_B-ADR0

B-A11/DDR2_B-ADR1

B-A2/DDR2_B-ADR2

B-CASZ/DDR2_B-ADR3

B-A3/DDR2_B-ADR4

B-BA1/DDR2_B-ADR5

B-A4/DDR2_B-ADR6

B-RASZ/DDR2_B-ADR7

B-A5/DDR2_B-ADR8

B-BA0/DDR2_B-ADR9